#### Is Now Part of

## ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

June 2016

# FAN602F Offline Quasi-Resonant PWM Controller

#### **Features**

- High Efficiency Across Wide Input and Output Conditions in a Small Form Factor

- Quasi-Resonant Switching Operation with Two Step Maximum Blanking Frequency (140 kHz and 75 kHz)

- User Configurable Burst Mode Entry and Exit to Maximize Light-Load Efficiency and Minimize Audible Noise

- Adaptive Burst Mode Entry Level for Adaptive Charger Application

- mWSaver® Technology for Ultra Low Standby Power Consumption (<20 mW)</li>

- Forced and Inherent Frequency Modulation of Valley Switching for Low EMI Emissions and Common Mode Noise

- Built-In and User Configurable Over-Voltage Protection (OVP), Under-Voltage Protection (UVP) and Over-Temperature Protection (OTP)

- Fully Programmable Brown-In and Brownout Protection

- Precise Constant Output Current Regulation with Programmable Line Compensation

- Built-In High-Voltage Startup to Reduce External Components

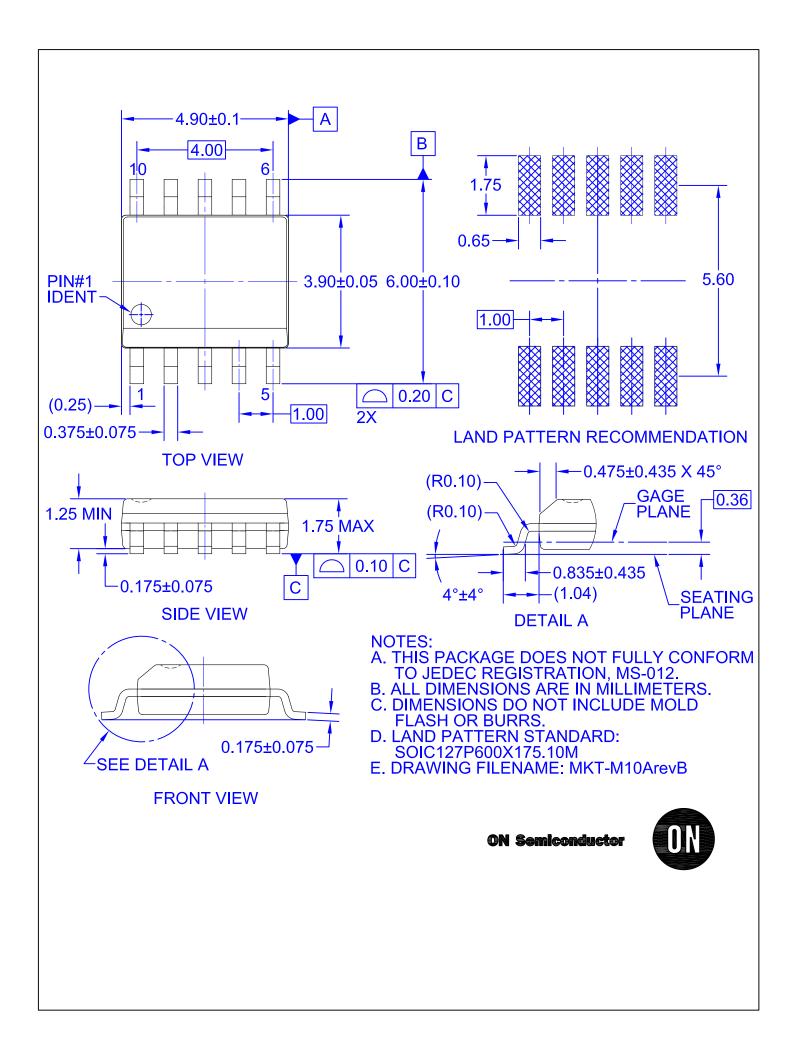

- 10 Lead SOIC JEDEC

## **Applications**

- Battery Charges for Smart Phones, Feature Phones, and Tablet PCs

- AC-DC Adapters for Portable Devices or Battery Chargers that Require CV/CC Control

## Description

The FAN602F is an advanced PWM controller aimed at achieving power density of ≥10W/in³ in universal input range AC/DC flyback isolated power supplies. It incorporates Quasi-Resonant (QR) control with proprietary Valley Switching with a limited frequency variation. QR switching provides high efficiency by reducing switching losses while Valley Switching with a limited frequency variation bounds the frequency band to overcome the inherent limitation of QR switching.

FAN602F features mWSaver® burst mode operation with extremely low operating current (300  $\mu$ A) and significantly reduces standby power consumption to meet the most stringent efficiency regulations such as Energy Star's 5-Star Level and CoC Tier II specifications.

FAN602F includes several user configurable features aimed at optimizing efficiency, EMI and protections. FAN602F has a programmable switching frequency range that provides flexibility in choosing noise rejection in targeted frequency zones. It incorporates user-configurable minimum peak current, which allows controlling the burst mode entry/exit power level, thereby enhancing light-load efficiency and eliminating audible noise. It also includes several rich programmable protection features such as Over-Voltage Protection (OVP), precise constant output current regulation (CC) and Over-Temperature Protection (OTP) through external thermistor.

## Ordering Information

| Part Number | Operating<br>Temperature Range | Package                                                                    | Packing<br>Method |

|-------------|--------------------------------|----------------------------------------------------------------------------|-------------------|

| FAN602FMX   | -40°C to +125°C                | 10-Lead, Small Outline Package (SOIC), JEDEC MS-012, .150-Inch Narrow Body | Tape & Reel       |

R<sub>SNS</sub> C<sub>SNP</sub>

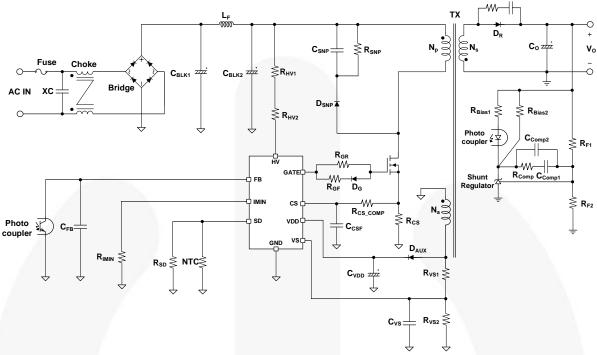

## **Typical Application**

Figure 1. FAN602F Typical Application

## **Marking Information**

F- Fairchild Logo

Z: Assembly Plant Code

X: Year Code

Y: Week Code

TT: Die Run Code

T: Package Type (M=SOIC)

M: Manufacture Flow Code

Figure 3. Top Mark

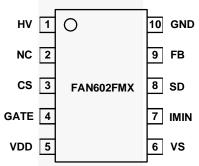

## **Pin Configuration**

Figure 4. Pin Assignment

## **Pin Definitions**

| Pin# | Name | Description                                                                                                                                                                                                                                                                           |  |  |  |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | HV   | High Voltage. This pin connects to DC bus for high-voltage startup.                                                                                                                                                                                                                   |  |  |  |

| 2    | NC   | No Connect.                                                                                                                                                                                                                                                                           |  |  |  |

| 3    | CS   | <b>Current Sense</b> . This pin connects to a current-sense resistor to sense the MOSFET current for Peak-Current-Mode control for output regulation. The current sense information is also used to estimate the output current for CC regulation.                                    |  |  |  |

| 4    | GATE | <b>PWM Signal Output</b> . This pin has an internal totem-pole output driver to drive the power MOSFET. The gate driving voltage is internally clamped at 7.5 V.                                                                                                                      |  |  |  |

| 5    | VDD  | <b>Power Supply</b> . IC operating current and MOSFET driving current are supplied through this pin. This pin is typically connected to an external V <sub>DD</sub> capacitor.                                                                                                        |  |  |  |

| 6    | VS   | <b>Voltage Sense</b> . The VS voltage is used to detect resonant valleys for quasi-resonant switching. This pin detects the output voltage information and diode current discharge time based on the auxiliary winding voltage. It also senses input voltage for Brownout protection. |  |  |  |

| 7    | IMIN | <b>Minimum V</b> <sub>cs</sub> . This pin connects to external resistor to program minimum VCS Threshold level for burst mode operating optimization.                                                                                                                                 |  |  |  |

| 8    | SD   | <b>Shut Down.</b> This pin is implemented for external over-temperature-protect by connecting NTC thermistor.                                                                                                                                                                         |  |  |  |

| 9    | FB   | <b>Feedback</b> . Typically Opto-Coupler is connected to this pin to provide feedback information to the internal PWM comparator. This feedback is used to control the duty cycle in CV regulation.                                                                                   |  |  |  |

| 10   | GND  | Ground.                                                                                                                                                                                                                                                                               |  |  |  |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol             |                                          | Parameter                                               | Min. | Max. | Unit |

|--------------------|------------------------------------------|---------------------------------------------------------|------|------|------|

| V <sub>HV</sub>    | HV Pin Input Voltage                     |                                                         |      | 500  | V    |

| $V_{VDD}$          | DC Supply Voltage                        |                                                         |      | 30   | V    |

| V <sub>VS</sub>    | VS Pin Input \                           | Voltage                                                 | -0.3 | 6.0  | V    |

| V <sub>CS</sub>    | CS Pin Input \                           | Voltage                                                 | -0.3 | 6.0  | V    |

| V <sub>FB</sub>    | FB Pin Input \                           | /oltage                                                 | -0.3 | 6.0  | V    |

| V <sub>IMIN</sub>  | IMIN Pin Inpu                            | t Voltage                                               | -0.3 | 6.0  | V    |

| V <sub>SD</sub>    | SD Pin Input                             | Voltage                                                 | -0.3 | 6.0  | V    |

| P <sub>D</sub>     | Power Dissipa                            | ation (T <sub>A</sub> =25°C)                            |      | 850  | mW   |

| $\theta_{JA}$      | Thermal Resistance (Junction-to-Ambient) |                                                         |      | 140  | °C/W |

| $\Psi_{JT}$        | Thermal Resistance (Junction-to-Top)     |                                                         |      | 13   | °C/W |

| TJ                 | Operating Jur                            | nction Temperature                                      | -40  | +150 | °C   |

| T <sub>STG</sub>   | Storage Temp                             | perature Range                                          | -40  | +150 | °C   |

| TL                 | Lead Tempera                             | ature, (Wave soldering or IR, 10 Seconds)               |      | +260 | °C   |

| ESD <sup>(3)</sup> | Electrostatic                            | Human Body Model, JEDEC:JESD22_A114 (Except HV Pin)     |      | 3.0  | 14/  |

| ESD                | Discharge<br>Capability                  | Charged Device Model, JEDEC:JESD22_C101 (Except HV Pin) |      | 2.0  | kV   |

#### Notes:

- 1. All voltage values, except differential voltages, are given with respect to GND pin.

- 2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

- 3. ESD ratings including HV pin: HBM=2.0 kV, CDM=2.0 kV.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol            | Parameter               | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------|------|------|------|------|

| $V_{HV}$          | HV Pin Supply Voltage   | 50   |      | 400  | V    |

| V <sub>VDD</sub>  | VDD Pin Supply Voltage  | 6    | 15   | 25   | V    |

| V <sub>VS</sub>   | VS Pin Supply Voltage   | 0.65 |      | 2.90 | V    |

| Vcs               | CS Pin Supply Voltage   | 0    |      | 0.9  | V    |

| $V_{FB}$          | FB Pin Supply Voltage   | 0    |      | 5.25 | V    |

| V <sub>SD</sub>   | SD Pin Supply Voltage   | 0    |      | 5    | V    |

| V <sub>IMIN</sub> | IMIN Pin Supply Voltage | 0    |      | 2.5  | V    |

| T <sub>A</sub>    | Operating Temperature   | -40  |      | +85  | °C   |

## **Electrical Characteristics**

$V_{DD}$ =15 V and  $T_J$ =-40~125°C unless noted.

| Symbol                   | Parameter                                            | Conditions                                                                                                                                                 | Min.  | Тур.  | Max.  | Unit |

|--------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| HV Section               |                                                      |                                                                                                                                                            | •     | •     | •     |      |

| I <sub>HV</sub>          | Supply Current Drawn from HV Pin                     | V <sub>HV</sub> =120 V, V <sub>DD</sub> =0 V                                                                                                               | 1.2   | 2.0   | 10    | mA   |

| I <sub>HV-LC</sub>       | Leakage Current Drawn from HV Pin                    | V <sub>HV</sub> =500 V, V <sub>DD</sub> =V <sub>DD-OFF</sub> +1 V                                                                                          | 0     | 0.8   | 10    | μA   |

| $V_{Brown-IN}$           | Brown-In Threshold Voltage.                          | $R_{HV}$ =150 k $\Omega$ , $V_{IN}$ =80 $V_{rms}$                                                                                                          | 100   | 110   | 120   | V    |

| V <sub>DD</sub> Section  |                                                      |                                                                                                                                                            | •     | •     | •     |      |

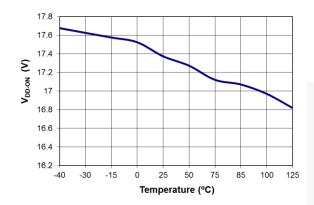

| $V_{\text{DD-ON}}$       | Turn-On Threshold Voltage                            | V <sub>DD</sub> Rising                                                                                                                                     | 15.3  | 17.2  | 18.7  | V    |

| $V_{DD\text{-}OFF}$      | Turn-Off Threshold Voltage                           | V <sub>DD</sub> Falling                                                                                                                                    | 5.0   | 5.5   | 5.7   | V    |

| $V_{\text{DD-HV-ON}}$    | Threshold Voltage for HV Startup                     | T <sub>J</sub> =25°C                                                                                                                                       | 4.1   | 4.7   | 5.4   | V    |

| I <sub>DD-ST</sub>       | Startup Current                                      | V <sub>DD</sub> =V <sub>DD-ON</sub> -0.16 V, T <sub>J</sub> =25°C                                                                                          |       | 300   | 400   | μA   |

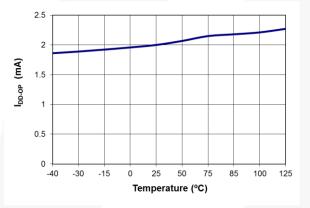

| I <sub>DD-OP</sub>       | Operating Supply Current                             | V <sub>CS</sub> =5.0 V, V <sub>S</sub> =3 V, V <sub>FB</sub> =3 V, V <sub>DD</sub> =15 V, C <sub>GATE</sub> =1 nF                                          |       | 2     | 3     | mA   |

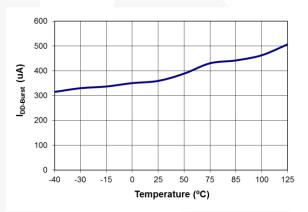

| I <sub>DD-Burst</sub>    | Burst-Mode Operating Supply Current                  | $V_{CS}=0.3 \text{ V}, V_{S}=0 \text{ V}, V_{FB}=0 \text{ V}; \\ V_{DD}=V_{DD-ON}\rightarrow V_{DD-OVP}\rightarrow 10 \text{ V}, \\ C_{GATE}=1 \text{ nF}$ |       | 300   | 600   | μA   |

| V <sub>VDD-OVP</sub>     | V <sub>DD</sub> Over-Voltage-Protection Level        | T <sub>J</sub> =25°C                                                                                                                                       | 27.5  | 29.0  | 29.5  | V    |

| t <sub>D-VDDOVP</sub>    | VDD Over-Voltage-Protection<br>Debounce Time         |                                                                                                                                                            |       | 70    | 105   | μs   |

| Oscillator Sec           | ction                                                |                                                                                                                                                            |       |       | ı     |      |

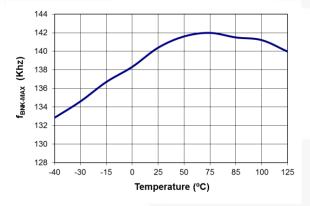

| f <sub>BNK-MAX</sub>     | Maximum Blanking Frequency                           | V <sub>FB</sub> > V <sub>FB-BNK-H</sub>                                                                                                                    | 130   | 140   | 150   | kHz  |

| f <sub>BNK-MIN</sub>     | Minimum Blanking Frequency                           | V <sub>FB</sub> < V <sub>FB-BNK-L</sub> , T <sub>J</sub> =25°C                                                                                             | 70    | 75    | 80    | kHz  |

| fosc-min-dcm             | Minimum Frequency for DCM                            | V <sub>VS</sub> =0 V                                                                                                                                       | 40    | 50    | 60    | kHz  |

| f <sub>OSC-MIN-CrM</sub> | Minimum Frequency for CrM                            | V <sub>VS</sub> =1 V, T <sub>J</sub> =25°C                                                                                                                 | 11    | 20    | 29    | kHz  |

| Δt <sub>FM-Range</sub>   | Forced Frequency Modulation Range                    | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                                                                      | 225   | 265   | 305   | ns   |

| $\Delta t_{FM-Period}$   | Forced Frequency Modulation Period                   | V <sub>FB</sub> > V <sub>FB-Burst</sub> H                                                                                                                  | 2.1   | 2.5   | 2.9   | ms   |

| V <sub>FB-BNK-H-H</sub>  | Frequency Jumping point V <sub>FB</sub>              | V - 24 V                                                                                                                                                   | 2.0   | 2.1   | 2.2   | V    |

| $V_{FB-BNK-L-H}$         | Frequency Jumping point V <sub>FB</sub>              | V <sub>S_SH</sub> > 2.1 V                                                                                                                                  | 1.8   | 1.9   | 2.0   | V    |

| $V_{FB-BNK-H-L}$         | Frequency Jumping point V <sub>FB</sub>              | V .20V                                                                                                                                                     | 1.55  | 1.65  | 1.75  | V    |

| $V_{FB-BNK-L-L}$         | Frequency Jumping point V <sub>FB</sub>              | V <sub>S_SH</sub> < 2.0 V                                                                                                                                  | 1.35  | 1.45  | 1.55  | V    |

| Feedback Inp             | ut Section                                           |                                                                                                                                                            |       |       |       |      |

| $Z_{FB}$                 | FB Pin Input Impedance                               |                                                                                                                                                            | 39    | 42    | 45    | kΩ   |

| A <sub>V-H</sub>         | Internal Voltage Attenuator of FB Pin <sup>(4)</sup> | V <sub>FB</sub> > V <sub>FB-BNK-H</sub>                                                                                                                    | 1/3   | 1/3.5 | 1/4   | V/V  |

| $A_{V-L}$                | Internal Voltage Attenuator of FB Pin <sup>(4)</sup> | $V_{FB} < V_{FB-BNK-L}$                                                                                                                                    | 1/2.1 | 1/2.6 | 1/3.1 | V/V  |

| V <sub>FB-Open</sub>     | FB Pin Pull-Up Voltage                               | FB Pin Open                                                                                                                                                | 4.75  | 5.25  | 5.90  | V    |

| $V_{FB-Burst-H}$         | FB Threshold to Enable/Disable Gate                  | V <sub>FB</sub> Rising                                                                                                                                     | 0.85  | 0.95  | 1.05  | V    |

| V <sub>FB-Burst-L</sub>  | Drive in Burst Mode                                  | V <sub>FB</sub> Falling                                                                                                                                    | 0.8   | 0.9   | 1.0   | V    |

Continued on the following page...

## **Electrical Characteristics**

$V_{DD}{=}15\ V$  and  $T_{J}{=}{-}40{\sim}125\ ^{\circ}C$  unless noted.

| Symbol                    | Parameter                                                       | Conditions                                                     | Min.  | Тур.  | Max.  | Unit  |

|---------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|-------|

| Voltage-Sens              | se Section                                                      |                                                                | •     | •     | •     | •     |

| I <sub>VS-MAX</sub>       | Maximum V <sub>S</sub> Source Current Capability                |                                                                |       |       | 3     | mA    |

| t <sub>VS-BNK1</sub>      | V <sub>S</sub> Sampling Blanking Time 1 after GATE Pin Pull-Low | V <sub>FB</sub> < V <sub>FB-BNK-L</sub>                        | 0.9   | 1.1   | 1.37  | μs    |

| t <sub>VS-BNK2</sub>      | V <sub>S</sub> Sampling Blanking Time 2 after GATE Pin Pull-Low | V <sub>FB</sub> > V <sub>FB-BNK-H</sub> , T <sub>J</sub> =25°C | 1.6   | 1.8   | 2.1   | μs    |

| t <sub>ZCD-to</sub> PWM   | Delay from VS Voltage Zero Crossing to PWM ON <sup>(4)</sup>    | V <sub>VS</sub> =0 V, C <sub>GATE</sub> =1 nF                  |       | 175   |       | ns    |

| I <sub>VS-Brownout</sub>  | V <sub>S</sub> Source Current Threshold to Enable Brownout      | Set $I_{VS}$ =2.4 mA at 264 $V_{rms}$ , Brownout=55 $V_{rms}$  | 370   | 450   | 520   | μA    |

| t <sub>D-Brownout</sub>   | Brownout Debounce Time                                          |                                                                | 12.5  | 16.5  | 21    | ms    |

| V <sub>VS-OVP</sub>       | Output Over-Voltage-Protection with Vs<br>Sampling Voltage      |                                                                | 2.8   | 2.9   | 3.0   | ٧     |

| N <sub>VS-OVP</sub>       | Output Over-Voltage-Protection Debounce Cycle Counts            |                                                                |       | 2     |       | Cycle |

| V <sub>VS-UVP-H</sub>     | Output Under-Voltage-Protection with Vs Sampling Voltage        | T <sub>J</sub> =25°C                                           | 0.76  | 0.80  | 0.84  | ٧     |

| V <sub>VS-UVP-L</sub>     | Output Under-Voltage-Protection with Vs Sampling Voltage        | T <sub>J</sub> =25°C                                           | 0.625 | 0.650 | 0.675 | V     |

| N <sub>VS-UVP</sub>       | Output Over-Voltage-Protection Debounce Cycle Counts            |                                                                |       | 2     |       | Cycle |

| t <sub>VS-UVP-BLANK</sub> | Output Under-Voltage Protection Blanking<br>Time at start-up    |                                                                | 25    | 40    | 55    | ms    |

| N <sub>VDD-Hiccup</sub>   | Auto-Restart 2 Cycles Mode Counts                               | V <sub>S_SH</sub> < V <sub>VS-UVP</sub>                        |       | 2     |       | Cycle |

| Over-Temper               | ature Protection Section                                        |                                                                |       |       |       |       |

| T <sub>OTP</sub>          | Threshold Temperature for Over-Temperatur                       | re-Protection <sup>(4)</sup>                                   | A     | 140   |       | °C    |

| Current-Sens              | e Section                                                       |                                                                | A     |       |       |       |

| V <sub>CS-LIM</sub>       | Current Limit Threshold Voltage                                 | FB Pin Open                                                    | 0.85  | 0.9   | 0.95  | V     |

| I <sub>IMIN</sub>         | IMIN Pin Current                                                |                                                                | 9     | 10    | 11    | μA    |

| V <sub>CS-IMIN-MIN</sub>  | Minimum Current Sense Voltage                                   | V <sub>S_SH</sub> =2.5 V,R <sub>IMIN</sub> =250 kΩ             | 0.050 | 0.100 | 0.150 | V     |

| V <sub>CS-IMIN-MAX</sub>  | Maximum Current Sense Voltage                                   | $V_{S\_SH}$ =2.5 $V_{S\_MIN}$ =0 $\Omega$                      | 0.185 | 0.225 | 0.255 | V     |

| t <sub>PD</sub>           | GATE Output Turn-Off Delay                                      |                                                                |       | 100   | 200   | ns    |

| $t_{LEB}$                 | Leading-Edge Blanking Time                                      |                                                                |       | 150   | 200   | ns    |

Continued on the following page...

## **Electrical Characteristics**

$V_{DD}{=}15\ V$  and  $T_{J}{=}{-}40{\sim}125\ ^{\circ}C$  unless noted.

| Symbol                   | Parameter                                                         | Conditions                                                            | Min. | Тур.  | Max. | Unit |

|--------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|------|-------|------|------|

| Shut-Down Fo             | unction Section                                                   |                                                                       | 1    |       | I    |      |

| I <sub>SD</sub>          | SD Pin Source Current                                             |                                                                       | 90   | 103   | 110  | μA   |

| $V_{\text{SD-TH}}$       | Threshold Voltage for Shut-Down Function Enable                   |                                                                       | 0.95 | 1.00  | 1.05 | V    |

| t <sub>D-SD</sub>        | Debounce Time for Shut-Down Function                              |                                                                       | 200  | 400   | 600  | μs   |

| V <sub>SD-TH-ST</sub>    | Hysteresis of Threshold Voltage for Shut-<br>Down Function Enable |                                                                       | 1.30 | 1.35  | 1.40 | V    |

| t <sub>SD-ST</sub>       | Duration of V <sub>SD-TH-ST</sub> at startup                      |                                                                       | 0.8  | 1.3   | 1.8  | ms   |

| Constant Cur             | rent Correction Section                                           | 1                                                                     |      |       |      |      |

| I <sub>COMP-H</sub>      | High Line Compensation Current                                    | V <sub>IN</sub> =264 V <sub>rms</sub>                                 | 90   | 100   | 110  | μΑ   |

| I <sub>COMP-L</sub>      | Low Line Compensation Current                                     | V <sub>IN</sub> =90 V <sub>rms</sub>                                  | 32   | 36    | 40   | μΑ   |

| Constant Cur             | rent Estimator                                                    |                                                                       |      |       |      |      |

| $V_{REF\_CC}$            | Constant Current Control Reference<br>Voltage <sup>(4)</sup>      |                                                                       |      | 1.2   |      | V    |

| A <sub>PK</sub>          | Peak Value Amplifying Gain <sup>(4)</sup>                         |                                                                       |      | 3.6   |      | V/V  |

| V <sub>FB-CC-Open</sub>  | FB CC Pull-Up Voltage <sup>(4)</sup>                              |                                                                       |      | 4.0   |      | V    |

| A <sub>V-CC</sub>        | Internal Voltage Attenuator of FB CC <sup>(4)</sup>               |                                                                       |      | 0.444 |      | V/V  |

| GATE Section             | 1                                                                 |                                                                       |      |       | •    |      |

| V <sub>GATE-L</sub>      | Gate Output Voltage Low                                           |                                                                       | 0    |       | 1.5  | V    |

| V <sub>DD-PMOS-ON</sub>  | Internal Gate PMOS Driver ON                                      |                                                                       | 7.0  | 7.5   | 8.0  | V    |

| V <sub>DD-PMOS-OFF</sub> | Internal Gate PMOS Driver OFF                                     |                                                                       | 9.0  | 9.5   | 10.0 | V    |

| t <sub>r</sub>           | Rising Time                                                       | V <sub>CS</sub> =0 V, V <sub>S</sub> =0 V,<br>C <sub>GATE</sub> =1 nF | 100  | 135   | 180  | ns   |

| t <sub>f</sub>           | Falling Time                                                      | V <sub>CS</sub> =0 V, V <sub>S</sub> =0 V,<br>C <sub>GATE</sub> =1 nF | 30   | 50    | 70   | ns   |

| V <sub>GATE-CLAMP</sub>  | Gate Output Clamping Voltage                                      | V <sub>DD</sub> =25 V                                                 | 6.8  | 7.5   | 8.2  | V    |

| t <sub>ON-MAX</sub>      | Maximum On Time                                                   | V <sub>FB</sub> =3 V, V <sub>CS</sub> =0.3 V                          | 18   | 20    | 23   | μs   |

#### Note:

4. Guaranteed by design.

## **Typical Performance Characteristics**

5.38 5.36  $\widehat{\mathbf{S}}$ 5.34 5.32 5.3 5.28 5.26 -40 -30 -15 25 50 75 100 125 Temperature (°C)

Figure 5. Turn-On Threshold Voltage (V<sub>DD-ON</sub>) vs. Temperature

Figure 6. Turn-Off Threshold Voltage (V<sub>DD-OFF</sub>) vs. Temperature

Figure 7. Operating Supply Current (I<sub>DD-OP</sub>) vs. Temperature

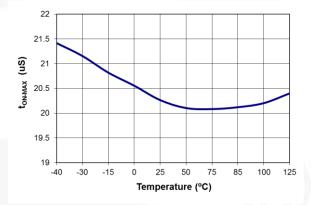

Figure 8. Burst-Mode Operating Supply Current (I<sub>DD-Burst</sub>) vs. Temperature

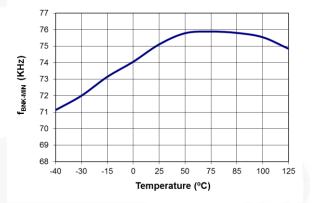

Figure 9. Maximum Blanking Frequency (f<sub>BNK-MAX</sub>) vs. Temperature

Figure 10. Minimum Blanking Frequency (f<sub>BNK-MIN</sub>) vs. Temperature

## **Typical Performance Characteristics** (Continued)

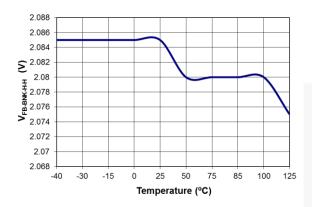

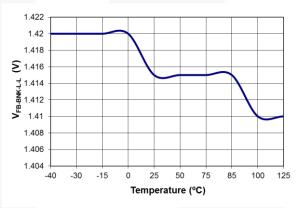

Figure 11. Frequency Jumping point (V<sub>FB-BNK-H-H</sub>) vs. Temperature

Figure 12. Frequency Jumping point (V<sub>FB-BNK-L-H</sub>) vs. Temperature

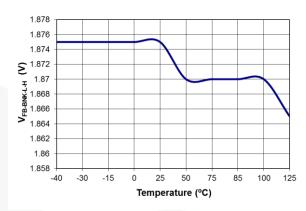

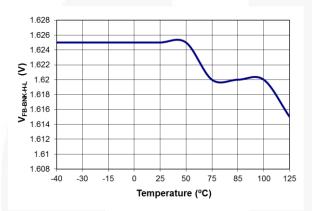

Figure 13. Frequency Jumping point (V<sub>FB-BNK-H-L</sub>) vs. Temperature

Figure 14. Frequency Jumping point (V<sub>FB-BNK-L-L</sub>) vs. Temperature

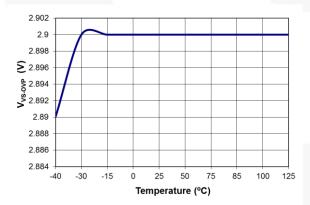

Figure 15. Output Over-Voltage-Protection V<sub>VS-OVP</sub>) vs. Temperature

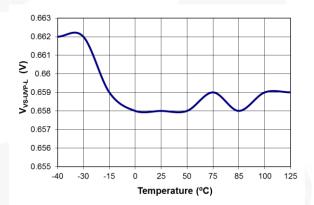

Figure 16. Output Under-Voltage Protection (V<sub>VS-UVP-L</sub>) vs. Temperature

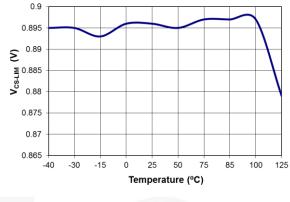

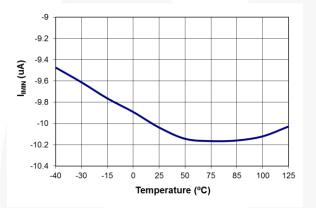

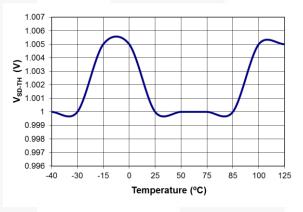

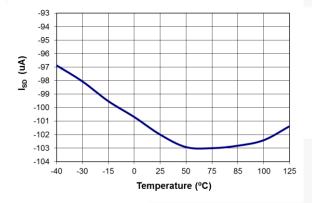

## **Typical Performance Characteristics** (Continued)

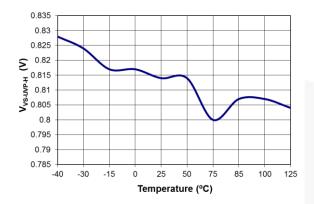

Figure 17. Output Under-Voltage Protection (V<sub>VS-UVP-H</sub>) vs. Temperature

Figure 18. Current Limit Threshold Voltage (V<sub>CS-LIM</sub>) vs. Temperature

Figure 19. IMIN Pin Current (I<sub>IMIN</sub>) vs. Temperature

Figure 20. Threshold Voltage for Shutdown Function Enable (V<sub>SD-TH</sub>) vs. Temperature

Figure 21. SD Pin Source Current (I<sub>SD</sub>) vs. Temperature

Figure 22. Maximum On Time (t<sub>ON-MAX</sub>) vs. Temperature

#### **Functional Description**

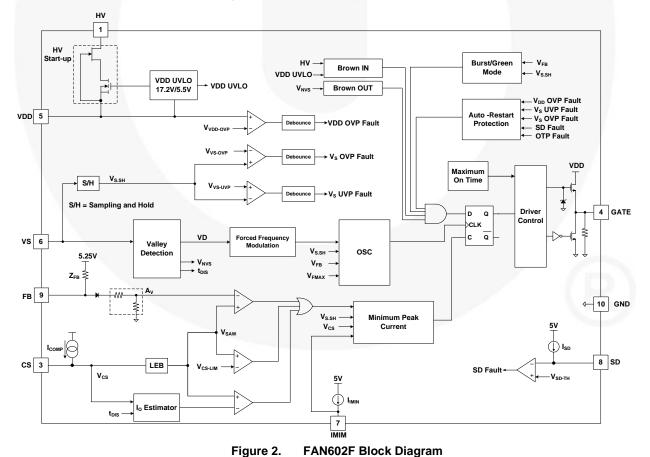

FAN602F is an offline PWM controller which operates in a quasi-resonant (QR) mode and significantly enhances system efficiency and power density. Its control method is based on the load condition (valley switching with the maximum blanking time at heavy load and valley switching with the minimum blanking time at medium load) to maximize the efficiency. It offers constant output voltage (CV) regulation through opto-coupler feedback circuitry.

Line voltage compensation gain can be programmed by using an external resistor to minimize the effect of line voltage variation on output current regulation due to turn-off delay of the gate drive circuit. FAN602F incorporates HV startup and accurate brown-in through HV pin. The brown-in voltage is programmed by using an external HV pin resistor. The minimum peak current (V<sub>CS-IMIN</sub>), which controls the burst mode entry/exit and improves light-load efficiency, is programmable via an external resistor connected to the IMIN pin.

#### **Basic Operation Principle**

Quasi-resonant switching is a method to reduce primary MOSFET switching losses especially in high line. In order to perform QR turn-on of the primary MOSFET, the valley of the resonance occurring between transformer magnetizing inductance ( $L_m$ ) and MOSFET effective output capacitance ( $C_{oss-eff}$ ) must be detected.

$$C_{OSS-eff} = C_{OSS-MOSFET} + C_{trans} + C_{parasitic}$$

(1)

$$t_{resonance} = 2\pi \cdot \sqrt{L_m \cdot C_{OSS-eff}}$$

(2)

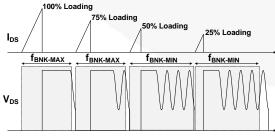

For heavy load condition (55%~100% of full load), the blanking time for the valley detection is fixed such that the switching time is between  $t_{BNK}$  and  $t_{BNK}+t_{resonance}$ . For the medium load condition (10%~55% of full load), the blanking time is changed by  $V_{FB}$  and output voltage such that the upper limit of the blanking frequency varies from  $f_{BNK-MAX}$  to  $f_{BNK-MIN}$ .

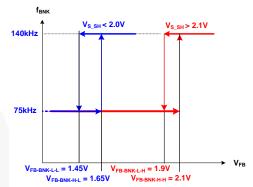

For adaptive output application, the blanking frequency jumping point will be changed by threshold voltage of V<sub>S-SH</sub>. At high output voltage, V<sub>FB-BNK-L</sub>= V<sub>FB-BNK-L</sub>+ H(1.9 V) and V<sub>FB-BNK-H</sub>= V<sub>FB-BNK-H</sub>+H(2.1 V) when V<sub>S-SH</sub> > H(1.9 V) and V<sub>FB-BNK-H</sub>= V<sub>FB-BNK-L</sub>= V<sub>FB-BNK-L</sub>+H(1.45 V) and V<sub>FB-BNK-H</sub>= V<sub>FB-BNK-H</sub>+H(1.45 V) when V<sub>S-SH</sub> < H(1.45 V) as shown in Figure 24.

Figure 23. Two Step Blanking Frequency

Figure 24. The Blanking Frequency Jumping Point with Variation of V<sub>S-SH</sub>

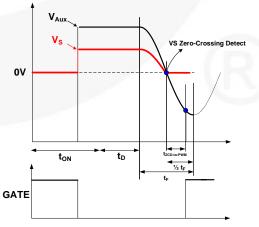

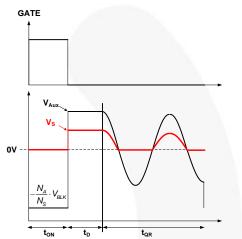

#### **Valley Detection**

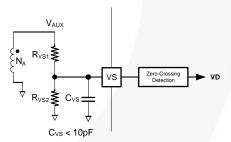

There will be a logic propagation delay from VS Zero-Crossing Detection ( $V_{S\text{-}ZCD}$ ) to IC GATE turn on and a MOSFET gate drives propagation delay from GATE pin to MOSFET turn on. We can assume the sum of these propagation delays to be  $t_{ZCD\text{-}to\text{-}PWM}$ , as shown in Figure 26. However, if 1/2  $t_F$  is larger than  $t_{ZCD\text{-}to\text{-}PWM}$ , the switching occurs away from the valley causing higher losses. The time period of resonant ringing is dependent on  $L_m$  and  $C_{oss\text{-eff}}$ . Typically, the time period of resonance ringing is around  $1{\sim}1.5~\mu s$  depending on the system parameters. Hence, the switching may occur at a point different from the valley depending on the system. When PCB layout is poor, it may cause noise on the VS pin. The VS pin needs to be in parallel with the capacitor ( $C_{VS}$ ) less than 10 pF to filter the noise.

Figure 25. The Valley Detection Circuit

Figure 26. Valley Detection Behavior

#### **Inherent and Forced Frequency Modulation**

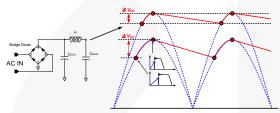

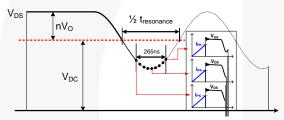

Typically, the bulk capacitor of flyback converter has a longer charging time in low line than in high line. Thus, the voltage ripple ( $\Delta$  V<sub>DC</sub>) in low line is higher as shown in Figure 27. This large ripple results in 4~6% variation of the switching frequency in low line for a valley switched converter. Hence, the EMI performance in low line is satisfied. However, in high line, the ripple is very small and consequent. The EMI performance for high line may suffer. In order to maintain good EMI performance for high line, forced frequency modulation is provided. FAN602F varies the valley switching point from 0 to  $\Delta t_{\text{FM-Range}}$  (265 ns) in every  $\Delta t_{\text{FM-Period}}$  (2.5 ms) as shown in Figure 28. Since the drain voltage at which the switching occurs does not change much with this variation, there is minimum impact on the efficiency.

Figure 27. Inherent Frequency Modulation

Figure 28. Forced Frequency Modulation

#### **Output Voltage Detection**

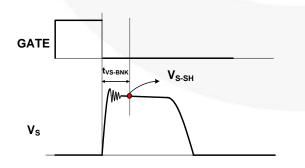

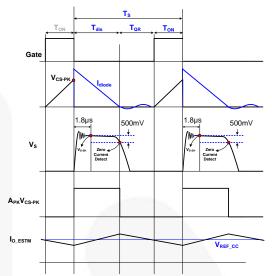

Figure 29 shows the VS voltage is sampled (V<sub>S-SH</sub>) after t<sub>VS-BNK</sub> of GATE turn-off so that the ringing does not introduce any error in the sampling. FAN602F dynamically varies t<sub>VS-BNK</sub> with load. At heavy load, t<sub>VS-BNK</sub>=t<sub>VS-BNK1</sub> (1.8  $\mu$ s) when V<sub>FB</sub> > V<sub>FB-BNK-H</sub>. At light-load, t<sub>VS-BNK</sub>=t<sub>VS-BNK2</sub> (1.1  $\mu$ s) when V<sub>FB</sub> < V<sub>FB-BNK-L</sub>. This dynamic variation ensures that VS sampling occurs after ringing due to leakage inductance has stopped and before secondary current goes to zero.

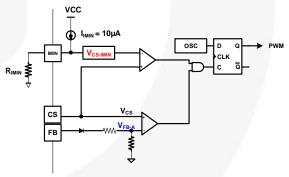

## **Burst Mode Operation**

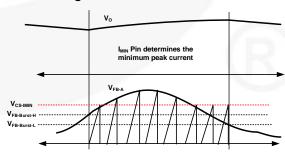

FAN602F features burst mode operation with a programmable burst mode entry load condition by using minimum peak current ( $V_{\text{CS-IMIN}}$ ) control which enables light-load efficiency to be optimized for a given application. The IMIN pin can be programmed with external resistor  $R_{\text{IMIN}}$  to select the minimum  $V_{\text{CS}}$  threshold level for burst mode entry. Figure 30 shows the implementation of IMIN in FAN602F.

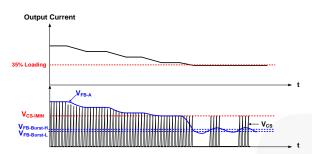

Figure 31 shows when  $V_{FB}$  drops below  $V_{FB-Burst-L}$ , the PWM output shuts off and the output voltage drops at a rate which is depended on the load current level. This causes the feedback voltage to rise. Once  $V_{FB}$  exceeds  $V_{FB-Burst-H}$ , FAN602F resumes switching. As shown in Figure 32, when the FB voltage drops below the corresponding  $V_{CS-IMIN}$ , the peak currents in switching cycles are fixed to  $V_{CS-IMIN}$  regardless of FB voltage. Thus, more power is delivered to the load than required and once FB voltage is pulled low below  $V_{FB-Burst-L}$ , switching stops again. In this manner, the burst mode operation alternately enables and disables switching of the MOSFET to reduce the switching losses.

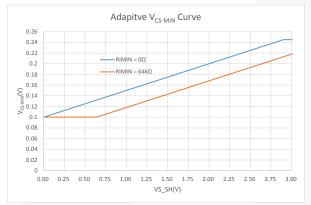

For adaptive output application, the minimum peak current is modulated in accordance with the  $V_{\text{S-SH}}$  such that the minimum peak current is proportional to the square root of output voltage. For easy circuit implementation, curve fitting is used as shown in Figure 33.

$$V_{CS-IMIN} = \frac{(V_{S-SH} - I_{MIN} \times R_{IMIN})}{20} + 0.1$$

(4)

Figure 30. IMIN Function Circuit

Figure 29. Output Voltage Detection

$$V_{S-SH} = V_O \cdot \frac{N_A}{N_S} \cdot \frac{R_{VS2}}{(R_{VS1} + R_{VS2})}$$

(3)

Figure 31. Burst-Mode Operation with IMIN

Figure 32. System enter Burst-Mode Behavior

Figure 33. V<sub>CS-IMIN</sub> as a Function of R<sub>IMIN</sub> with Variation of V<sub>S-SH</sub>

#### **Deep Burst Mode**

FAN602F enters deep burst mode if FB voltage stays lower than  $V_{\text{FB-Burst-L}}$  for more than  $t_{\text{Deep-Burst-Entry}}$  (640 µs). Once FAN602F enters deep burst mode, the operating current is reduced to  $I_{\text{DD-Burst}}$  (300 µA) to minimize power consumption. Once feedback voltage is more than  $V_{\text{FB-Burst-H}}$ , power-on-reset occurs within a time period of  $t_{\text{Deep-Burst-Exit}}$  (25 µs) and IC resumes switching with normal operating current,  $I_{\text{DD-OP}}$ .

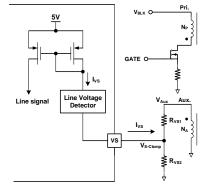

#### **Line Voltage Detection**

The FAN602F indirectly senses the line voltage through the VS pin while the MOSFET is turned on, as illustrated in Figure 34 and Figure 35. During MOSFET turn-on period, the auxiliary winding voltage,  $V_{\text{AUX}}$ , is proportional to the input bulk capacitor voltage,  $V_{\text{BLK}}$ , due to the transformer coupling between the primary and auxiliary windings. During the MOSFET conduction time, the line voltage detector clamps the VS pin voltage to  $V_{\text{S-Clamp}}$  (0 V), and then the current  $I_{\text{VS}}$  flowing out of VS pin is expressed as:

$$I_{VS} = \frac{V_{BLK}}{R_{VS1}} \cdot \frac{N_A}{N_S} \tag{5}$$

The  $I_{VS}$  current, reflecting the line voltage information, is used for brownout protection and CC control correction weighting.

Figure 34. Line Voltage Detection Circuit

Figure 35. Waveforms for Line Voltage Detection

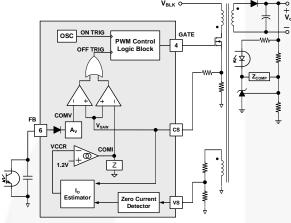

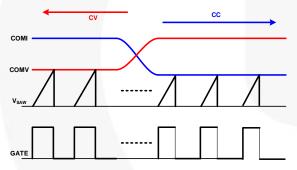

## CV / CC PWM Operation Principle

Figure 36 shows a simplified CV / CC PWM control circuit of the FAN602F. The Constant Voltage (CV) regulation is implemented in the same manner as the conventional isolated power supply, where the output voltage is sensed using a voltage divider and compared with the internal reference of the shunt regulator to generate a compensation signal. The compensation signal is transferred to the primary side through an optocoupler and scaled down by attenuator  $A_{\rm V}$  to generate a COMV signal. This COMV signal is applied to the PWM comparator to determine the duty cycle.

The Constant Current (CC) regulation is implemented internally with primary-side control. The output current estimator calculates the output current using the transformer primary-side current and diode current discharge time. By comparing the estimated output current with internal reference signal, a COMI signal is generated to determine the duty cycle.

These two control signals, COMV and COMI, are compared with an internal sawtooth waveform (V<sub>SAW</sub>) by two PWM comparators to determine the duty cycle. Figure 37 illustrates the outputs of two comparators, combined with an OR gate, to determine the MOSFET turn-off instant. Either of COMV or COMI, the lower signal determines the duty cycle. As shown in Figure 37, during CV regulation, COMV determines the duty cycle while COMI is saturated to HIGH level. During CC regulation, COMI determines the duty cycle while COMV is saturated to HIGH level.

Figure 36. Simplified PWM Control Circuit

Figure 37. PWM Operation for CV/CC Regulation

#### **Primary-Side Constant Current Operation**

Figure 38 shows the key waveforms of a flyback converter operating in DCM. The output current is estimated by calculating the average of output diode current in the one switching cycle:

$$I_{O} = \frac{1}{2} \frac{1}{R_{CS}} \frac{V_{CS-PK} \cdot T_{dis}}{T_{S}} \frac{N_{P}}{N_{S}} \eta = \frac{1}{2} \frac{1}{R_{CS}} \frac{V_{REF\_CC}}{A_{PK}} \frac{N_{P}}{N_{S}} \eta$$

(6)

When the diode current reaches zero, the transformer winding voltage begins to drop sharply and VS pin voltage drops as well. When VS pin voltage drops below the  $V_{S-SH}$  by more than 500 mV, zero current detection (ZCD) of diode current is obtained.

The output current can be programmed by setting the current sensing resistor as:

$$R_{CS} = \frac{1}{2} \cdot \frac{1}{I_O} \cdot \frac{V_{REF\_CC}}{A_{PK}} \cdot \frac{N_P}{N_S} \cdot \eta \tag{7}$$

Where  $V_{REF\_CC}$  is the internal voltage for CC control and  $A_{PK}$  is the IC design parameter, 3.6 for FAN602F.

Figure 38. Waveforms for Estimate Output

Current

#### **Line Voltage Compensation**

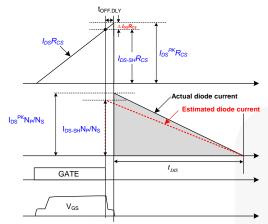

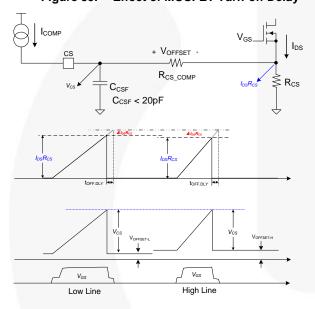

The output current estimation is also affected by the turn-off delay of the MOSFET as illustrated in Figure 39. The actual MOSFET's turn-off time is delayed due to the MOSFET gate charge and gate driver's capability, resulting in peak current detection error as

$$\Delta I_{DS}^{PK} = \frac{V_{BLK}}{L_m} \cdot t_{OFF.DLY} \tag{8}$$

Where  $L_m$  is the transformer's primary side magnetizing inductance. Since the output current error is proportional to the line voltage, the FAN602F incorporates line voltage compensation to improve output current estimation accuracy. Line information is obtained through the line voltage detector as shown in Figure 34.  $I_{COMP}$  is an internal current source, which is proportional to line voltage. The line compensation gain is programmed by using CS pin series resistor,  $R_{CS\_COMP}$ , depending on the MOSFET turn-off delay,  $t_{OFF.DLY}$ .  $I_{COMP}$  creates a voltage drop,  $V_{OFFSET}$ , across  $R_{CS\_COMP}$ . This line compensation offset is proportional to the DC link capacitor voltage,  $V_{BLK}$ , and turn-off delay,  $t_{OFF.DLY}$ . Figure 40 demonstrates the effect of the line compensation.

Figure 39. Effect of MOSFET Turn-off Delay

Figure 40. Line Voltage Compensation

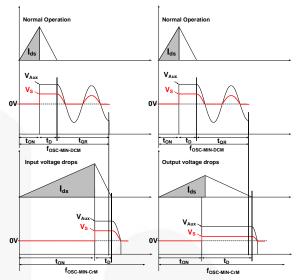

#### **CCM Prevention**

When input or output voltage drops, the secondary side current does not reduce to zero within  $t_{OSC-MIN-DCM}$  (time period for  $f_{OSC-MIN-DCM}$ ). FAN602F does not initiate turnon. FAN602F turns on the primary MOSFET after VS-ZCD and ensures boundary conduction mode switching. Thus FAN602F does not allow the converter to enter CCM. During CCM prevention, FAN602F can reduce the frequency down to  $f_{OSC-MIN-CrM}$  (20 kHz). This phenomenon is explained in Figure 41.

Figure 41. CCM Prevention Behavior

#### **HV Startup and Brown-In**

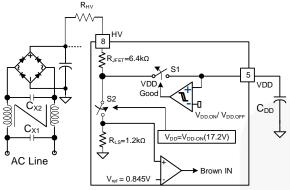

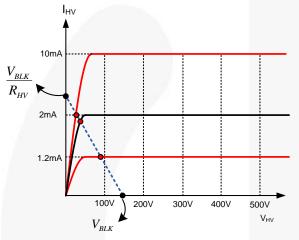

Figure 42 shows the high-voltage (HV) startup circuit. An Internal JFET provides a high voltage current source, whose characteristics are shown in Figure 43. To improve reliability and surge immunity, it is typical to use a  $R_{\rm HV}$  resistor between the HV pin and the bulk capacitor voltage. The actual current flowing into the HV pin at a given bulk capacitor voltage and startup resistor value is determined by the intersection point of characteristics I-V line and the load line as shown in Figure 43.

During startup, the internal startup circuit is enabled and the bulk capacitor voltage supplies the current,  $I_{HV}$ , to charge the hold-up capacitor,  $C_{VDD}$ , through  $R_{HV}$ . When the  $V_{DD}$  voltage reaches  $V_{DD\text{-}ON}$ , the sampling circuit shown in Figure 42 is turned on for  $t_{HV\text{-}det}$  (100  $\mu s$ ) to sample the bulk capacitor voltage. Voltage across  $R_{LS}$  is compared with reference which generates a signal to start switching. If brown-in condition is not detected within this time, switching does not start. Equation (9) can be used to program the brown-in of the system. If line voltage is lower than the programmed brown-in voltage, FAN602F goes in auto-restart mode.

$$V_{IN} = \frac{R_{LS} + R_{JEFT} + R_{HV}}{R_{LS}} \times V_{REF}$$

(9)

Once switching starts, the internal HV startup circuit is disabled. During normal switching, the line voltage information is obtained from the  $I_{VS}$  signal. Once the HV startup circuit is disabled, the energy stored in  $C_{VDD}$  supplies the IC operating current until the transformer auxiliary winding voltage reaches the nominal value. Therefore,  $C_{VDD}$  should be properly designed to prevent  $V_{DD}$  from dropping below  $V_{DD\text{-}OFF}$  threshold (typically 5.5 V) before the auxiliary winding builds up enough voltage to supply  $V_{DD}$ . During startup, the IC current is limited to  $I_{DD\text{-}ST}$  (300  $\mu\text{A}$ ).

Figure 42. HV Startup Circuit

Figure 43. Characteristics of HV pin

#### **Protections**

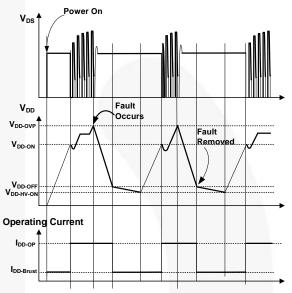

The FAN602F protection functions include VDD Over-Voltage Protection (VDD-OVP), brownout protection, VS Over-Voltage Protection (VS-OVP), VS Under-Voltage Protection (VS-UVP), and IC internal Over-Temperature Protection (OTP). The VDD-OVP, brownout protection VS-OVP and OTP are implemented with Auto-Restart mode. The VS-UVP is implemented with Extend Auto-Restart mode.

When the Auto-Restart Mode protection is triggered, switching is terminated and the MOSFET remains off, causing VDD to drop because of IC operating current  $I_{\text{DD-OP}}$  (2 mA). When VDD drops to the VDD turn-off voltage of  $V_{\text{DD-OFF}}$  (5.5 V), operation current reduces to  $I_{\text{DD-Deep-Burst}}$  (300  $\mu\text{A}$ ). When the VDD voltage drops further to  $V_{\text{DD-HV-ON}}$ , the protection is reset and the supply current drawn from HV pin begins to charge the VDD hold-up capacitor. When VDD reaches the turn-on voltage of  $V_{\text{DD-ON}}$  (17.2 V), the FAN602F resumes normal operation. In this manner, the Auto-Restart mode alternately enables and disables the switching of the MOSFET until the abnormal condition is eliminated as shown in Figure 44.

When the Extend Auto-Restart Mode protection is triggered via VS under-voltage protection (VS-UVP), switching is terminated and the MOSFET remains off, causing VDD to drop. While  $V_{\rm DD}$  drops to  $V_{\rm DD-HV-ON}$  for HV startup circuit enable, then IC enters Extend Auto-Restart period with two cycles as shown Figure 45. During Extend Auto-Restart period, VDD voltage swings between  $V_{\rm DD-ON}$  and  $V_{\rm DD-HVON}$  without gate switching, and IC operation current is reduced to  $I_{\rm DD-Burst}$  of 300  $\mu A$  for slowing down the VDD capacitor discharging slope. As Extend Auto-Restart period ends, normal operation resumes.

Figure 44. Auto-Restart Mode Operation

Figure 45. Extend Auto-Restart Mode Operation

#### **VDD Over-Voltage-Protection (VDD-OVP)**

VDD over-voltage protection prevents IC damage from over-voltage stress. It is operated in Auto-Restart mode. When the VDD voltage exceeds  $V_{\text{DD-OVP}}$  (29.0 V) for the de-bounce time,  $t_{\text{D-VDDOVP}}$  (70  $\mu s$ ), due to abnormal condition, the protection is triggered. This protection is typically caused by an open circuit of secondary side feedback network.

#### **Brownout Protection**

Line voltage information is also used for brownout protection. When the  $I_{VS}$  current out of the VS pin during the MOSFET conduction time is less than 450  $\mu A$  for longer than 16.5 ms, the brownout protection is triggered. The input bulk capacitor voltage to trigger brownout protection is given as

$$V_{BLK.BO} = 450\mu \cdot \frac{R_{VS1}}{N_A/N_P} \tag{10}$$

#### IC Internal Over-Temperature-Protection (OTP)

The internal temperature-sensing circuit disables the PWM output if the junction temperature exceeds 140°C ( $T_{\rm OTP}$ ) and the FAN602F enters Auto-Restart Mode protection.

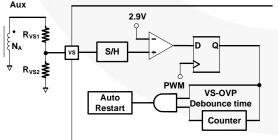

#### VS Over-Voltage-Protection (VS-OVP)

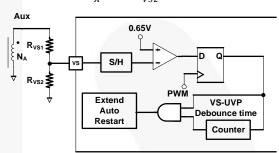

VS over-voltage protection prevents damage caused by output over-voltage condition. It is operated in Auto-Restart mode. Figure 46 shows the internal circuit of VS-OVP protection. When abnormal system conditions occur, which cause VS sampling voltage to exceed  $V_{\rm VS-OVP}$  (2.9V) for more than 2 consecutive switching cycles  $(N_{\rm VS-OVP})$ , PWM pulses are disabled and FAN602F enters. Auto-Restart protection. VS over-voltage conditions are usually caused by open circuit of the secondary side feedback network or a fault condition in the VS pin voltage divider resistors. For VS pin voltage divider design,  $R_{\rm VS1}$  is obtained from Equation (10), and  $R_{\rm VS2}$  is determined by the desired VS-OVP protection function as

Figure 46. VS-OVP Protection Circuit

#### VS Under-Voltage-Protection (VS-UVP)

In the event of an output short, output voltage will drop and the primary peak current will increase. To prevent operation for a long time in this condition, FAN602F incorporates under-voltage protection through VS pin. Figure 47 shows the internal circuit for VS-UVP. By

sampling the auxiliary winding voltage on the VS pin at the end of diode conduction time, the output voltage is indirectly sensed. When  $V_S$  sampling voltage is less than  $V_{VS-UVP}$  (0.65 V) and longer than de-bounce cycles  $N_{VS-UVP}$ , VS-UVP is triggered and the FAN602F enters Extend Auto-Restart Mode.

To avoid VS-UVP triggering during the startup sequence, a startup blanking time,  $t_{VS-UVP-BLANK}$  (45 ms), is included for system power on. For VS pin voltage divider design,  $R_{VS1}$  is obtained from Equation (10) and  $R_{VS2}$  is determined by Equation (11).  $V_{O-UVP}$  can be determined by Equation (12).

$$V_{O-UVP} = \frac{N_S}{N_A} \cdot \left(1 + \frac{R_{VS1}}{R_{VS2}}\right) \cdot V_{VS-UVP} \tag{12}$$

Figure 47. VS-UVP Protection Circuit

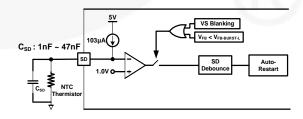

#### **Externally Triggered Shutdown (SD)**

By pulling down SD pin voltage below a threshold voltage  $V_{\text{SD-TH}}$  (1.0 V), shutdown can be externally triggered and the FAN602F will enter into Auto-Restart mode protection. It can be also used for external Over-Temperature-Protection by connecting a NTC thermistor between the shutdown (SD) programming pin and ground. An internal constant current source  $I_{\text{SD}}$  (103  $\mu$ A) creates a voltage drop across the thermistor. The resistance of the NTC thermistor becomes smaller as the ambient temperature increases, which reduces the voltage drop across the thermistor.

SD pin voltage is sampled every gate cycle when  $V_{FB} > V_{FB-Burst-H}$  and sampled continuously when  $V_{FB} < V_{FB-Burst-L}$ . When the voltage at SD pin is sampled to be below the threshold voltage,  $V_{SD-TH}$  (1.0 V), for a de-bounce time of  $t_{D-SD}$  (400  $\mu$ s), Auto-Restart protection is triggered. A capacitor may also be placed in parallel with the NTC thermistor to further improve the noise immunity. The capacitor should be designed such that SD pin voltage is more than  $V_{SD-TH}$  within the time period of  $t_{D-SD}$ .

Figure 48. External OTP using SD Pin

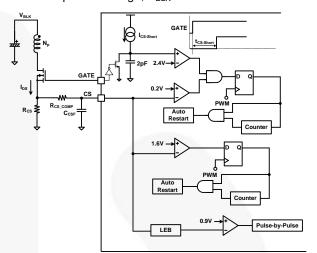

#### **Pulse-by-Pulse Current Limit**

During startup or overload condition, the feedback loop is saturated to high and is unable to control the primary peak current. To limit the current during such conditions, FAN602F has pulse-by-pulse current limit protection which forces the GATE to turn off when the CS pin voltage reaches the current limit threshold,  $V_{\text{CS-LIM}}$  (0.9 V).

#### **Secondary-Side Diode Shot Protection**

When the secondary-side diode is damaged, the slope of the primary-side peak current will be sharp within leading-edge blanking time. To limit the current during such conditions, FAN602F has secondary-side diode short protection which forces the GATE to turn off when the CS pin voltage reaches 1.6 V. After one switching cycle, it will operate in Auto-Restart mode as shown in Figure 49.

#### **Current Sense Short Protection**

Current sense short protection prevents damage caused by CS pin open or short to ground. After two switching cycle, it will operate in Auto-Restart mode. Figure 49 shows the internal circuit of current sense short protection. When abnormal system conditions occur, which cause CS pin voltage lower than 0.2 V after debounce time (t<sub>CS-short</sub>) for more than 2 consecutive

switching cycles, PWM pulses are disabled and FAN602F enters Auto-Restart protection. The  $I_{\text{CS-Short}}$  is an internal current source, which is proportional to line voltage. The debounce time ( $t_{\text{CS-short}}$ ) is created by  $I_{\text{CS-short}}$ , capacitor (2 pF) and threshold voltage (2.4 V). This debounce time ( $t_{\text{CS-short}}$ ) is inversely proportional to the DC link capacitor voltage,  $V_{\text{RI}}$  K.

Figure 49. Current Sense Protection Circuit

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor:

FAN602FMX

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А