## **KS8721B/BT**

#### 2.5V 10/100BasTX/FX MII Physical Layer Transceiver

Rev. 2.3

#### **General Description**

Operating at 2.5 volts to meet low voltage and low power requirements, the KS8721B/BT is a 10BaseT/100BaseTX/FX Physical Layer Transceiver, which provides an MII to transmit and receive data. It contains the 10BaseT Physical Medium Attachment (PMA), Physical Medium Dependent (PMD), and Physical Coding Sub-layer (PCS) functions. Moreover, the KS8721B/BT has on-chip 10BaseT output filtering, which eliminates the need for external filters and allows a single set of line magnetics to be used to meet requirements for both 100BaseTX and 10BaseT.

The KS8721B/BT can automatically configure itself for 100 or 10 Mbps and full or half duplex operation, using on-chip Auto-Negotiation algorithm. It is an ideal choice of physical layer transceiver for 100BaseTX/10BaseT applications.

Data sheets and support documentation can be found on Micrel's web site at www.micrel.com.

#### **Features**

- Single chip 100BaseTX/100BaseFX/10BaseT physical layer solution

- 2.5V CMOS design, power consumption <200mW (excluding output driver current)</li>

- Fully compliant to IEEE 802.3u standard

- Supports Media Independent Interface (MII) and Reduced MII (RMII)

- Supports 10BaseT, 100BaseTX and 100BaseFX with Far\_End\_Fault Detection

- · Supports power down mode and power saving mode

- Configurable through MII serial management ports or via external control pins

- Supports auto-negotiation and manual selection for 10/100Mbps speed and full/half-duplex mode

- On-chip built-in analog front end filtering for both 100BaseTX and 10BaseT

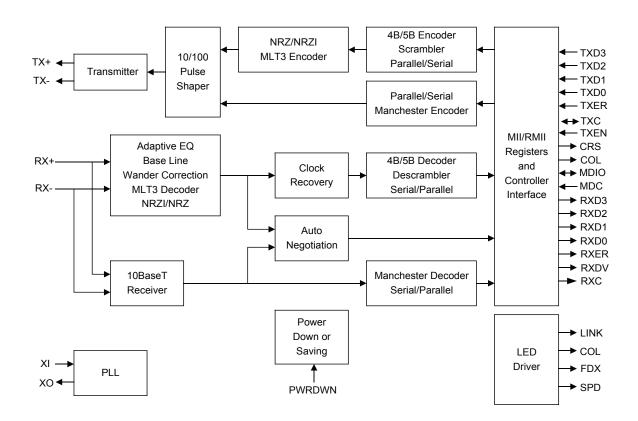

#### **Functional Diagram**

Micrel, Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

### Features (continued)

- LED outputs for link, activity, full/half duplex, collision and speed

- Supports back to back, FX to TX for media converter applications

- Supports MDI/MDI-X auto crossover

- 2.5V/3.3V tolerance on I/O

- Commercial temperature range: 0°C to +70°C

- Industrial temperature range: -40°C to +85°C

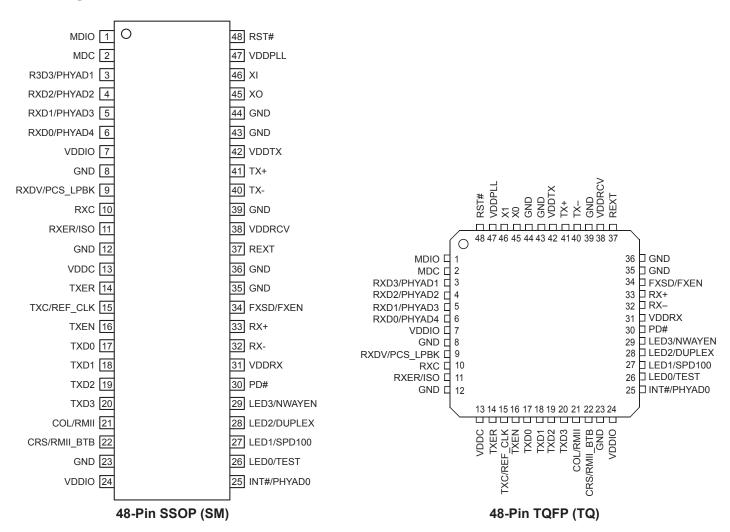

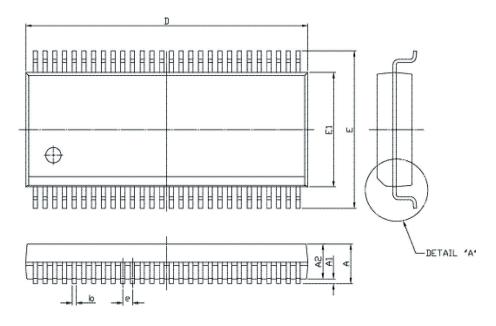

- Available in 48-pin SSOP and TQFP

## **Ordering Information**

| Part Number |           | Temperature    | Dookogo     |  |  |

|-------------|-----------|----------------|-------------|--|--|

| Standard    | Pb-Free   | remperature    | Package     |  |  |

| KS8721B     | KSZ8721B  | 0°C to +70°C   | 48-Pin SSOP |  |  |

| KS8721BT    | KSZ8721BT | 0°C to +70°C   | 48-Pin TQFP |  |  |

| _           | KSZ8721BI | –40°C to +85°C | 48-Pin SSOP |  |  |

#### **Revision History**

| Revision | Date    | Summary of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 2/29/02 | Document Origination (Preliminary)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.0      | 4/01/02 | Update timing Spec from page 33 to page 37 Change Revision ID from 1000 to 1001 Add new control register bit, Control Register 0 Bit 0, to control transmit enable/disable Add 8h register map on the table Editorial Change on FXSD/FXEN pin34 Change on duplex pin38 0=half and 1=full duplex Change on the 10BT MII transmit timing 1.0us to 2.5us and Tlat 2.5us to 4BT Add the TEST description mode on pin26                                                                                                                                                                                        |

| 2.1      | 1/31/03 | Add part number ordering information & remove pinout diagram Edited pin description on the IO cloumn Change the company logo, disclaimer, & contact info Editorial changes on Stapping option description Change on Register0h bit0, 1=disable and 0=enable Add remote fault register4h bit13. Add normal operating condition table & Thermal data for SSOP48 table Add Reset Timing table & Transformer Lists Add 48 TQFP pinout diagram & RMII AC Charateristics Add ordering info for 48 Pin TQFP package, KS8721B/BTI industrial temperature, KSY8721B/KSY8721BT environmentally friendly part number |

| 2.2      | 8/29/03 | Change part number from KS8721B to KS8721B/BT. Change ordering info. from "KSY" to "KSZ" for lead free. Change pin name from RMII_LPBK to RMII_BTB Convert to new format.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

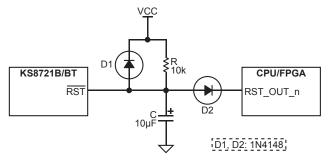

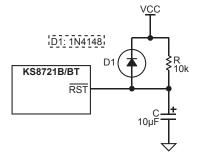

| 2.3      | 1/24/04 | MDIO pull-up resistor value changed to 4.7kΩ.  Added note on strapping option pins.  Updated bit 1b.0 - 1b.7 to self-clearing.  Updated Electrical Characteristic.  Updated bit 1f4:2 to resetted.  Added additional magnetics to qualified transformer.  Added reset reference circuit.                                                                                                                                                                                                                                                                                                                  |

| 2.3      | 3/16/05 | Added RMII timing specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## **Table Of Contents**

| Pin Description                                    | 6  |

|----------------------------------------------------|----|

| Strapping Option                                   | 9  |

| Pin Configuration                                  | 10 |

| Introduction                                       | 11 |

| 100BaseTX Transmit                                 | 11 |

| 100BaseTX Receive                                  | 11 |

| PLL Clock Synthesizer                              | 11 |

| Scrambler/De-scrambler (100BaseTX only)            | 11 |

| 10BaseT Transmit                                   | 11 |

| 10BaseT Receive                                    | 11 |

| SQE and Jabber Function (10Base only)              |    |

| Auto-Negotiation                                   |    |

| MII Management Interface                           |    |

| MII Data Interface                                 |    |

| Transmit Clock                                     |    |

| Receive Clock                                      |    |

| Transmit Enable                                    |    |

| Receive Data Valid                                 |    |

| Error Signals                                      |    |

| Carrier Sense                                      |    |

| Collision                                          |    |

| RMII Signal Definition                             |    |

| Reference Clock                                    |    |

| Carrier Sense/Receive Data Valid                   |    |

| Receive Data                                       |    |

| Transmit Enable                                    |    |

| Transmit Data                                      |    |

| Collision Detection                                |    |

| RX ER                                              |    |

| RMII AC Characteristics                            |    |

| Auto Crossover (Auto MDI/MDI-X)                    |    |

|                                                    |    |

| Power Management                                   |    |

| 100BT FX Mode                                      |    |

| Media Converter Option                             |    |

| Register Map                                       |    |

| Register 0h: Basic Conrol                          |    |

| Register 1h: Basic Status                          |    |

| Register 2h: PHY Identifier 1                      |    |

| Register 3h: PHY Identifier 2                      |    |

| Register 4h: Auto-Negotiation Advertisement        |    |

| Register 5h: Auto-Negotiation Link Partner Ability |    |

| Register 6h: Auto-Negotiation Expansion            |    |

| Register 7h: Auto-Negotiation Next Page            |    |

| Register 8h: Link Partner Next Page Ability        |    |

| Register 15h: RXER Counter                         |    |

| Register 1bh: Interrupt Control/Status Register    |    |

| Register 1fh: 100BaseTX PHY Controller             | 20 |

| Absolute Maximum Ratings            | 22 |

|-------------------------------------|----|

| Operating Ratings                   |    |

| Electrical Characteristics          |    |

| Timing Diagrams                     |    |

| Selection of Isolation Transformers |    |

| Selection of Reference Crystals     |    |

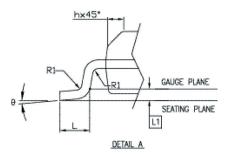

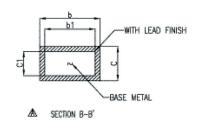

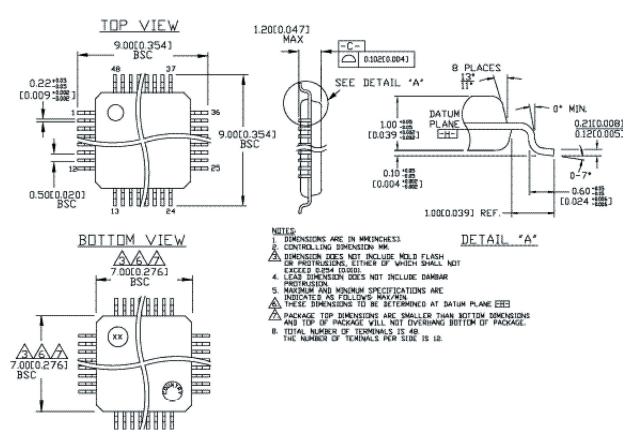

| Package Outline and Dimensions      |    |

## **Pin Description**

| Pin Number | Pin Name                    | Type <sup>(Note 1)</sup> | Pin Function                                                                                                                                                                                                                                                                                                         |

|------------|-----------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | MDIO                        | I/O                      | Management Interface (MII) Data I/O: This pin requires an external 4.7K pull-up resistor.                                                                                                                                                                                                                            |

| 2          | MDC                         | l                        | Management Interface (MII) Clock Input: This pin is synchronous to the MDIO data interface                                                                                                                                                                                                                           |

| 3          | RXD3/<br>PHYAD1             | lpd/O                    | MII Receive Data Output: RXD [30], these bits are synchronous with RXCLK. When RXDV is asserted, RXD [30] presents valid data to MAC through the MII. RXD [30] is invalid when RXDV is de-asserted. The pull-up/pull-down value is latched as PHYADDR [1] during reset. See "Strapping Options" section for details. |

| 4          | RXD2/<br>PHYAD2             | lpd/O                    | MII Receive Data Output: The pull-up/pull-down value is latched as PHYADDR [2] during reset. See "Strapping Options" section for details.                                                                                                                                                                            |

| 5          | RXD1/<br>PHYAD3             | lpd/O                    | MII Receive Data Output: The pull-up/pull-down value is latched as PHYADDR [3] during reset. See "Strapping Options" section for details.                                                                                                                                                                            |

| 6          | RXD0/<br>PHYAD4             | lpd/O                    | MII Receive Data Output: The pull-up/pull-down value is latched as PHYADDR [4] during reset. See "Strapping Options" section for details.                                                                                                                                                                            |

| 7          | VDDIO                       | Pwr                      | Digital IO 2.5 /3.3V tolerance power supply.                                                                                                                                                                                                                                                                         |

| 8          | GND                         | GND                      | Ground.                                                                                                                                                                                                                                                                                                              |

| 9          | RXDV/<br>CRSDV/<br>PCS_LPBK | lpd/O                    | MII Receive Data Valid Output: The pull-up/pull-down value is latched as pcs_lpbk during reset. See "Strapping Options' section for details.                                                                                                                                                                         |

| 10         | RXC                         | 0                        | MII Receive Clock Output: Operating at 25MHz = 100Mbps, 2.5MHz = 10Mbps.                                                                                                                                                                                                                                             |

| 11         | RXER/ISO                    | lpd/O                    | MII Receive Error Output: The pull-up/pull-down value is latched as ISOLATE during reset. See "Strapping Options" section for details.                                                                                                                                                                               |

| 12         | GND                         | GND                      | Ground.                                                                                                                                                                                                                                                                                                              |

| 13         | VDDC                        | Pwr                      | Digital core 2.5V only power supply.                                                                                                                                                                                                                                                                                 |

| 14         | TXER                        | lpd                      | MII Transmit Error Input.                                                                                                                                                                                                                                                                                            |

| 15         | TXC/<br>REFCLK              | lpu/O                    | MII Transmit Clock Output: RMII Reference Clock Input.                                                                                                                                                                                                                                                               |

| 16         | TXEN                        | lpd                      | MII Transmit Enable Input                                                                                                                                                                                                                                                                                            |

| 17         | TXD0                        | lpd                      | MII Transmit Data Input                                                                                                                                                                                                                                                                                              |

| 18         | TXD1                        | lpd                      | MII Transmit Data Input                                                                                                                                                                                                                                                                                              |

| 19         | TXD2                        | lpd                      | MII Transmit Data Input                                                                                                                                                                                                                                                                                              |

| 20         | TXD3                        | lpd                      | MII Transmit Data Input                                                                                                                                                                                                                                                                                              |

| 21         | COL/RMII                    | lpd/O                    | MII Collision Detect Output: The pull-up/pull-down value is latched as RMII select during reset. See "Strapping Options" section for details.                                                                                                                                                                        |

| 24         | VDDIO                       | Pwr                      | Digital IO 2.5/3.3V tolerance power supply.                                                                                                                                                                                                                                                                          |

**Note 1.** Pwr = power supply

GND = ground

I = input

O = output

I/O = bi-directional

Gnd = ground

Ipu = input w/ internal pull-up

lpd = input w/ internal pull-down

Ipd/O = input w/ internal pull-down during reset, output pin otherwise

Ipu/O = input w/ internal pull-up during reset, output pin otherwise

PU = strap pin pull-up

PD = strap pin pull-down

NC = No connect

| Pin Number | Pin Name                  | Type <sup>(Note 1)</sup> | Pin Function                                                                                                                                                       |                   |                                                                                |  |  |

|------------|---------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------|--|--|

| 25         | INT#/<br>PHYAD0           | lpu/O                    |                                                                                                                                                                    |                   | Interrupt Out: Latched as PHYAD[0] during power up ns'l section for details.   |  |  |

| 22         | CRS/<br>RMII_BTB          | lpd/O                    | MII Carrier Sense Output: The pull-up/pull-down value is latched as RMII BTB during reset when RMII mode is selected. See "Strapping Options' section for details. |                   |                                                                                |  |  |

| 23         | GND                       | GND                      | Ground.                                                                                                                                                            |                   |                                                                                |  |  |

| 26         | LED0/TEST                 | lpu/O                    | Link/Activity LED Output:                                                                                                                                          |                   |                                                                                |  |  |

| 1          |                           |                          | Lnk/Act                                                                                                                                                            | Pin State         | LED Definition                                                                 |  |  |

| 1          |                           |                          | No Link                                                                                                                                                            | Н                 | "off"                                                                          |  |  |

| }          |                           |                          | Link                                                                                                                                                               | L                 | "on"                                                                           |  |  |

| 1          |                           |                          | Act                                                                                                                                                                | _                 | "Toggle"                                                                       |  |  |

|            |                           |                          |                                                                                                                                                                    |                   | le test mode and only used for the factory test.                               |  |  |

| 27         | LED1/<br>SPD100/<br>noFEF | lpu/O                    | Speed LED Output: Latched as SPEED (Register 0, bit 13) during power-up/rese See "Strapping Options" section for details.                                          |                   |                                                                                |  |  |

| )          |                           |                          | Speed                                                                                                                                                              | Pin State         | LED Definition                                                                 |  |  |

|            |                           |                          | 10BT                                                                                                                                                               | Н                 | "off"                                                                          |  |  |

|            |                           |                          | 100BT                                                                                                                                                              | L                 | "on"                                                                           |  |  |

| 28         | LED2/<br>DUPLEX           | lpu/O                    |                                                                                                                                                                    |                   | ched as DUPLEX (register 0h, bit 8) during power-up/ os'l section for details. |  |  |

|            |                           |                          | Duplex                                                                                                                                                             | Pin State         | LED Definition                                                                 |  |  |

|            |                           |                          | Half                                                                                                                                                               | Н                 | "off"                                                                          |  |  |

|            |                           |                          | Full                                                                                                                                                               | L                 | "on"                                                                           |  |  |

| 29         | LED3/<br>NWAYEN           | lpu/O                    |                                                                                                                                                                    |                   | ed as ANEG_EN (register 0h, bit 12) during power-up/ as'l section for details. |  |  |

|            |                           |                          | Collison                                                                                                                                                           | Pin State         | LED Definition                                                                 |  |  |

|            |                           |                          | No Collision                                                                                                                                                       | Н                 | "off"                                                                          |  |  |

|            |                           |                          | Collision                                                                                                                                                          | L                 | "on"                                                                           |  |  |

| 30         | PD#                       | lpu                      | Power Down.                                                                                                                                                        | 1 = Normal ope    | eration, 0=Power down, Active low.                                             |  |  |

| 31         | VDDRX                     | Pwr                      | Analog 2.5V p                                                                                                                                                      | ower supply.      |                                                                                |  |  |

| 32         | RX-                       | I                        | Receive Input                                                                                                                                                      | : Differential re | ceive input pins for FX, 100BaseTX or 10BaseT.                                 |  |  |

| 33         | RX+                       | I                        | Receive Input                                                                                                                                                      | : Differential re | ceive input pin for FX, 100BaseTX or 10BaseT.                                  |  |  |

| 34         | FXSD/FXEN                 | lpd/O                    | Fiber Mode Enable / Signal Detect in Fiber Mode. If FXEN = 0, FX mode is disable. The default is "0". See "100BT FX Mode'l section for more details.               |                   |                                                                                |  |  |

| 35         | GND                       | GND                      | Ground.                                                                                                                                                            | Ground.           |                                                                                |  |  |

| 36         | GND                       | GND                      | Ground.                                                                                                                                                            |                   |                                                                                |  |  |

**Note 1.** Pwr = power supply

GND = ground

I = input

O = output

I/O = bi-directional

Ipu = input w/ internal pull-up

Ipd = input w/ internal pull-down

Ipd/O = input w/ internal pull-down during reset, output pin otherwise

Ipu/O = input w/ internal pull-up during reset, output pin otherwise

PU = strap pin pull-up

PD = strap pin pull-down

NC = No connect

| Pin Number | Pin Name | Type <sup>(Note 1)</sup> | Pin Function                                                                    |

|------------|----------|--------------------------|---------------------------------------------------------------------------------|

| 37         | REXT     | I                        | External resistor (6.49kΩ) connects to REXT and GNDRX.                          |

| 38         | VDDRCV   | Pwr                      | Analog 2.5V power supply.                                                       |

| 39         | GND      | GND                      | Ground                                                                          |

| 40         | TX-      | 0                        | Transmit Outputs: Differential transmit output for 100BaseTX/FX or 10BaseT.     |

| 41         | TX+      | 0                        | Transmit Outputs: Differential transmit output for FX, 100BaseTX/FX or 10BaseT. |

| 42         | VDDTX    | Pwr                      | Transmitter 2.5V power supply.                                                  |

| 43         | GND      | GND                      | Ground.                                                                         |

| 44         | GND      | GND                      | Ground.                                                                         |

| 45         | XO       | 0                        | XTAL feedback: Used with XI for Xtal application.                               |

| 46         | ΧI       | I                        | Crystal Oscillator Input: Input for a crystal or an external 25MHz clock        |

| 47         | VDDPLL   | Pwr                      | Analog PLL 2.5V power supply.                                                   |

| 48         | RST#     | lpu                      | Chip Reset: Active low, minimum of 50µs pulse is required                       |

**Note 1**. Pwr = power supply

GND = ground

I = input

O = output

I/O = bi-directional

Ipu = input w/ internal pull-up

lpd = input w/ internal pull-down

Ipd/O = input w/ internal pull-down during reset, output pin otherwise

Ipu/O = input w/ internal pull-up during reset, output pin otherwise

PU = strap pin pull-up

PD = strap pin pull-down

NC = No connect

# Strapping Options(Note 1)

| Pin Number        | Pin Name                   | Type <sup>(Note 2)</sup> | Description                                                                                                                                                                                                                                                              |

|-------------------|----------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6,5,<br>4,3       | PHYAD[4:1]/<br>RXD[0:3]    | lpd/O                    | PHY Address latched at power-up/reset. The default PHY address is 00001.                                                                                                                                                                                                 |

| 25                | PHYAD0/<br>INT#            | lpu/O                    |                                                                                                                                                                                                                                                                          |

| 9(3)              | PCS_LPBK/<br>RXDV          | lpd/O                    | Enables PCS_LPBK mode at power-up/reset. PD (default) = Disable, PU = Enable.                                                                                                                                                                                            |

| 11 <sup>(3)</sup> | ISO/RXER                   | lpd/O                    | Enables ISOLATE mode at power-up/reset. PD (default) = Disable, PU = Enable.                                                                                                                                                                                             |

| 21 <sup>(3)</sup> | RMII/COL                   | lpd/O                    | Enables RMII mode at power-up/reset. PD (default) = Disable, PU = Enable.                                                                                                                                                                                                |

| 22 <sup>(3)</sup> | RMII_BTB<br>CRS            | lpd/O                    | Enable RMII_BTB mode at power-up/reset. PD (default) = Disable, PU = Enable.                                                                                                                                                                                             |

| 27                | SPD100/<br>No FEF/<br>LED1 | lpu/O                    | Latched into Register 0h bit 13 during power-up/reset. PD = 10Mbps, PU (default) = 100Mbps. If SPD100 is asserted during power-up/reset, this pin also latched as the Speed Support in register 4h. (If FXEN is pulled up, the latched value 0 means no Far_End _Fault.) |

| 28                | DUPLEX/<br>LED2            | lpu/O                    | Latched into Register 0h bit 8 during power-up/reset. PD = Half duplex, PU (default) = Full duplex. If Duplex is pulled up during reset, this pin also latched as the Duplex support in register 4h.                                                                     |

| 29                | NWAYEN/<br>LED3            | lpu/O                    | Nway (auto-negotiation) Enable. Latched into Register 0h bit 12 during power-up/reset. PD = Disable Auto-Negotiation, PU (default) = Enable Auto-Negotiation.                                                                                                            |

| 30                | PD#                        | lpu                      | Power Down Enable. PU (default) = Normal operation, PD = Power down mode.                                                                                                                                                                                                |

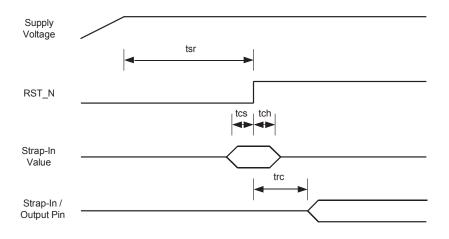

Note 1. Strap-in is latched during power-up or reset.

lpd = input w/ internal pull-down

Ipd/O = input w/ internal pull-down during reset, output pin otherwise

Ipu/O = input w/ internal pull-up during reset, output pin otherwise

PU = strap pin pull-up

PD = strap pin pull-down

Note 3. Some devices may drive MII pins that are designated as output (PHY) on power up, resulting in incorrect strapping values latched in at reset. It is recommended that an external pull down via 1kΩ resistor be used in these applications to augment the 8721's internal pull down.

## **Pin Configuration**

#### Introduction

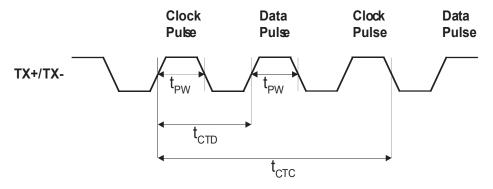

#### 100BaseTX Transmit

The 100BaseTX transmit function performs parallel to serial conversion, NRZ to NRZI conversion, MLT-3 encoding and transmission. The circuitry starts with a parallel to serial conversion, which converts the 25MHz, 4-bit nibbles into a 125 MHz serial bit stream. The incoming data is clocked in at the positive edge of the TXC signal. The serialized data is further converted from NRZ to NRZI format, and then transmitted in MLT3 current output. The output current is set by an external 1% 6.49k $\Omega$  resistor for the 1: 1 transformer ratio. It has a typical rise/fall times of 4 ns and complies to the ANSI TP-PMD standard regarding amplitude balance, overshoot and timing jitters. The wave-shaped 10BaseT output driver is also incorporated into the 100BaseTX driver.

#### 100BaseTX Receive

The 100BaseTX receive function performs adaptive equalization, DC restoration, MLT-3 to NRZI conversion, data and clock recovery, NRZI to NRZ conversion, and serial to parallel conversion. The receiving side starts with the equalization filter to compensate inter-symbol interference (ISI) over the twisted pair cable. Since the amplitude loss and phase distortion are a function of the length of the cable, the equalizer has to adjust its characteristic to optimize the performance. In this design, the variable equalizer will make an initial estimation based on comparisons of incoming signal strength against some known cable characteristics, then tunes itself for optimization. This is an ongoing process and can self adjust against the environmental changes such as temperature variations.

The equalized signal then goes through a DC restoration and data conversion block. The DC restoration circuit is used to compensate effect of base line wander and improve the dynamic range. The differential data conversion circuit converts the MLT3 format back to NRZI. The slicing threshold is also adaptive.

The clock recovery circuit extracts the 125MHz clock from the edges of the NRZI signal. This recovered clock is then used to convert the NRZI signal into the NRZ format. Finally, the NRZ serial data is converted to 4-bit parallel 4B nibbles. A synchronized 25MHz RXC is generated so that the 4B nibbles is clocked out at the negative edge of RCK25 and is valid for the receiver at the positive edge. When no valid data is present, the clock recovery circuit is locked to the 25MHz reference clock and both TXC and RXC clocks continue to run.

#### **PLL Clock Synthesizer**

The KS8721B/BT generates 125MHz, 25MHz and 20MHz clocks for system timing. An internal crystal oscillator circuit provides the reference clock for the synthesizer.

#### Scrambler/De-scrambler (100BaseTX only)

The purpose of the scrambler is to spread the power spectrum of the signal in order to reduce EMI and baseline wander.

#### 10BaseT Transmit

When TXEN (transmit enable) goes high, data encoding and transmission will begin. The KS8721B/BT will continue to encode and transmit data as long as TXEN remains high. The data transmission will end when TXEN goes low. The last transition occurs at the boundary of the bit cell if the last bit is zero, or at the center of the bit cell if the last bit is one. The output driver is incorporated into the 100Base driver to allow transmission with the same magnetics. They are internally wave-shaped and pre-emphasized into outputs with a typical 2.5V amplitude. The harmonic contents are at least 27dB below the fundamental when driven by an all-ones Manchester-encoded signal.

#### 10BaseT Receive

On the receive side, input buffer and level detecting squelch circuits are employed. A differential input receiver circuit and a PLL performs the decoding function. The Manchester-encoded data stream is separated into clock signal and NRZ data. A squelch circuit rejects signals with levels less than 300mV or with short pulse widths in order to prevent noises at the RX+ or RX- input from falsely trigger the decoder. When the input exceeds the squelch limit, the PLL locks onto the incoming signal and the KS8721B/BT decodes a data frame. This activates the carrier sense (CRS) ad RXDV signals and makes the receive data (RXD) available. The receive clock is maintained active during idle periods in between data reception.

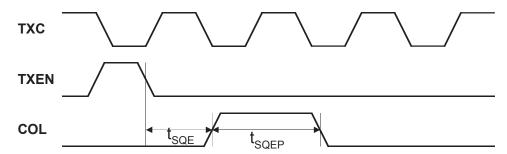

#### SQE and Jabber Function (10BaseT only)

In 10BaseT operation, a short pulse will be put out on the COL pin after each packet is transmitted. This is required as a test of the 10BaseT transmit/receive path and is called SQE test. The 10BaseT transmitter will be disabled and COL will go high if TXEN is High for more than 20ms (Jabbering). If TXEN then goes low for more than 250ms, the 10BaseT transmitter will be re-enabled and COL will go Low.

#### **Auto-Negotiation**

The KS8721B/BT performs auto-negotiation by hardware strapping option (pin 29) or software (Register 0.12). It will automatically choose its mode of operation by advertising its abilities and comparing them with those received from its link partner whenever auto-negotiation is enabled. It can also be configured to advertise 100BaseTX or 10BaseT in either full- or half-duplex mode (please refer to "Auto-Negotiation"). The auto-negotiation is disabled in the FX mode.

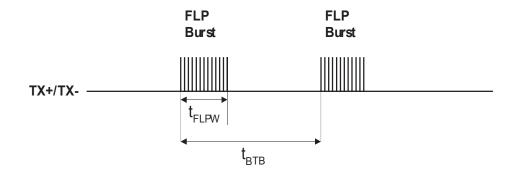

During auto-negotiation, the contents of Register 4, coded in Fast Link Pulse (FLP), will be sent to its link partner under the conditions of power-on, link-loss or re-start. At the same time, the KS8721B/BT will monitor incoming data to determine its mode of operation. Parallel detection circuit will be enabled as soon as either 10BaseT NLP (Normal Link Pulse) or 100BaseTX idle is detected. The operation mode is configured based on the following priority:

Priority 1: 100BaseTX, full-duplex

Priority 2: 100BaseTX, half-duplex

Priority 3: 10BaseT, full-duplex

Priority 4: 10BaseT, half-duplex

When the KS8721B/BT receives a burst of FLP from its link partner with 3 identical link code words (ignoring acknowledge bit), it will store these code words in Register 5 and wait for the next 3 identical code words. Once the KS8721B/BT detects the second code words, it then configures itself according to above-mentioned priority. In addition, the KS8721B/BT also checks 100BaseTX idle or 10BaseT NLP symbol. If either is detected, the KS8721B/BT automatically configures to match the detected operating speed.

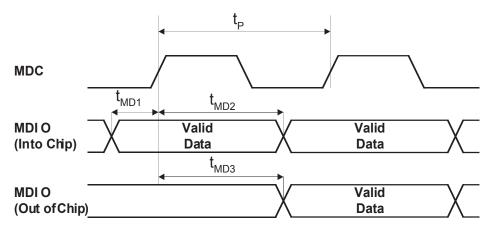

#### **MII Management Interface**

The KS8721B/BT supports the IEEE 802.3 MII Management Interface, also known as the Management Data Input / Output (MDIO) Interface. This interface allows upper-layer devices to monitor and control the state of the KS8721B/BT. The MDIO interface consists of the following:

- A physical connection including a data line (MDIO), a clock line (MDC) and an optional interrupt line (INTRPT)

- A specific protocol that runs across the above-mentioned physical connection and it also allows one controller to communicate with multiple KS8721B/BT devices. Each KS8721B/BT assigned an MII address between 0 and 31 by the PHYAD inputs.

- An internal addressable set of fourteen 16-bit MDIO registers. Register [0:6] are required and their functions are specified by the IEEE 802.3 specifications. Additional registers are provided for expanded functionality.

The INTPRT pin functions as a management data interrupt in the MII. An active Low or High in this pin indicates a status change on the KS8721B/BT based on 1fh.9 level control. Register bits at 1bh[15:8] are the interrupt enable bits. Register bits at 1bh[7:0] are the interrupt condition bits. This interrupt is cleared by reading Register 1bh.

#### **MII Data Interface**

The data interface consists of separate channels for transmitting data from a 10/100 802.3 compliant Media Access Controller (MAC) to the KS8721B/BT, and for receiving data from the line. Normal data transmission is implemented in 4B Nibble Mode (4-bit wide nibbles).

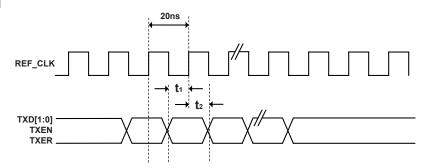

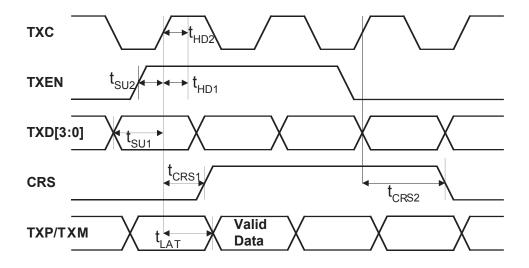

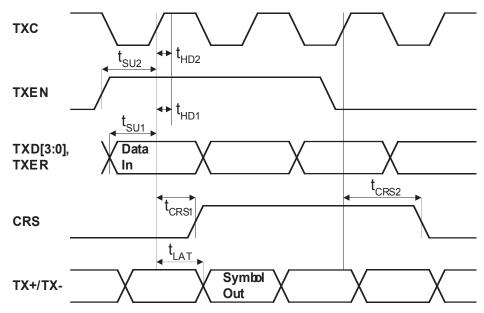

**Transmit Clock (TXC):** The transmit clock is normally generated by the KS8721B/BT from an external 25MHz reference source at the X1 input. The transmit data and control signals must always be synchronized to the TXC by the MAC. The KS8721B/BT normally samples these signals on the rising edge of the TXC.

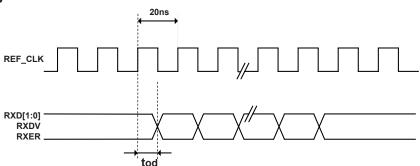

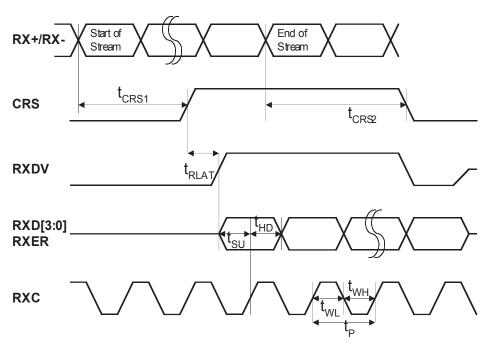

Receive Clock (RXC): For 100BaseTX links, the receive clock is continuously recovered from the line. If the link goes down, and auto-negotiation is disabled, the receive clock operates off the master input clock (X1 or TXC). For 10BaseT links, the receive clock is recovered from the line while carrier is active, and operates from the master input clock when the line is idle. The KS8721B/BT synchronizes the receive data and control signals on the falling edge of RXC in order to stabilize the signals at the rising edge of the clock with 10ns setup and hold times.

**Transmit Enable:** The MAC must assert TXEN at the same time as the first nibble of the preamble, and de-assert TXEN after the last bit of the packet.

**Receive Data Valid:** The KS8721B/BT asserts RXDV when it receives a valid packet. Line operating speed and MII mode will determine timing changes in the following way:

- For 100BaseTX link with the MII in 4B mode, RXDV is asserted from the first nibble of the preamble to the last nibble of the data packet.

- For 10BaseT links, the entire preamble is truncated. RXDV is asserted with the first nibble of the SFD " 5D" and remains asserted until the end of the packet.

*Error Signals:* Whenever the KS8721B/BT receives an error symbol from the network, it asserts RXER and drives "1110" (4B) on the RXD pins. When the MAC asserts TXER, the KS8721B/BT will drive "H" symbols (a Transmit Error define in the IEEE 802.3 4B/5B code group) out on the line to force signaling errors.

Carrier Sense (CRS): For 100TX links, a start-of-stream delimiter, or /J/K symbol pair causes assertion of Carrier Sense (CRS). An end-of-stream delimiter, or /T/R symbol pair causes de-assertion of CRS. The PMA layer will also de-assert CRS if IDLE symbols are received without /T/R, yet in this case RXER will be asserted for one clock cycle when CRS is de-asserted. For 10T links, CRS assertion is based on reception of valid preamble, and de-assertion on reception of an end-of-frame (EOF) marker.

**Collision:** Whenever the line state is half-duplex and the transmitter and receiver are active at the same time, the KS8721B/BT asserts its collision signal, which is asynchronous to any clock.

#### RMII (Reduced MII) Data Interface

RMII interface specifies a low pin count (Reduced) Media Independent Interface (RMII) intended for use between Ethernet PHYs and Switch or Repeater ASICs. It is fully compliant with IEEE 802.3u [2].

This interface has the following characteristics:

- It is capable of supporting 10Mbps and 100Mbps data rates.

- A single clock reference is sourced from the MAC to PHY (or from an external source).

- It provides independent 2-bit wide (di-bit) transmit and receive data paths.

- It uses TTL signal levels, compatible with common digital CMOS ASIC processes.

#### **RMII Signal Definition**

| Signal Name | Direction<br>(w/ respect to the PHY) | Direction<br>(w/ respect to the MAC) | Use                                                                     |

|-------------|--------------------------------------|--------------------------------------|-------------------------------------------------------------------------|

| REF_CLK     | Input                                | Input or Output                      | Synchronous clock reference for receive, transmit and control interface |

| CRS_DV      | Output                               | Input                                | Carrier Sense/Receive Data Valid                                        |

| RXD[1:0]    | Output                               | Input                                | Receive Data                                                            |

| TX_EN       | Input                                | Output                               | Transit Enable                                                          |

| TXD[1:0]    | Input                                | Output                               | Transit Data                                                            |

| RX_ER       | Output                               | Input (Not Required)                 | Receive Error                                                           |

Note 1. Unused MII signals, TXD[3:2], TXER need to tie to GND when RMII is using.

#### Reference Clock (REF\_CLK)

REF\_CLK is a continuous 50MHz clock that provides the timing reference for CRS\_DV, RXD[1:0], TX\_EN, TXD[1:0], and RX\_E. REF\_CLK is sourced by the MAC or an external source. Switch implementations may choose to provide REF\_CLK as an input or an output depending on whether they provide a REF\_CLK output or rely on an external clock distribution device. Each PHY device shall have an input corresponding to this clock but may use a single clock input for multiple PHYs implemented on a single IC.

#### Carrier Sense/Receive Data Valid (CRS\_DV)

CRS\_DV is asserted asynchronously on detection of carrier due to the criteria relevant to the operating mode. That is, in 10BASE-T mode, when squelch is passed or in 100BASE-X mode when 2 non-contiguous zeroes in 10 bits are detected carrier is said to be detected.

Loss of carrier shall result in the de-assertion of CRS\_DV synchronous to REF\_CLK. So long as carrier criteria are being met, CRS\_DV shall remain asserted continuously from the first recovered di-bit of the frame through the final recovered di-bit and shall be negated prior to the first REF\_CLK that follows the final di-bit.

The data on RXD[1:0] is considered valid once CRS\_DV is asserted. However, since the assertion of CRS\_DV is asynchronous relative to REF\_CLK, the data on RXD[1:0] shall be "00" until proper receive signal decoding takes place (see definition of RXD[1:0] behavior).

#### Receive Data [1:0] (RXD[1:0])

RXD[1:0] shall transition synchronously to REF\_CLK. For each clock period in which CRS\_DV is asserted, RXD[1:0] transfers two bits of recovered data from the PHY. In some cases (e.g. before data recovery or during error conditions) a pre-determined value for RXD[1:0] is transferred instead of recovered data. RXD[1:0] shall be "00" to indicate idle when CRS\_DV is de-asserted. Values of RXD[1:0] other than "00" when CRS\_DV is de-asserted are reserved for out-of-band signalling (to be defined). Values other than "00" on RXD[1:0] while CRS\_DV is de-asserted shall be ignored by the MAC/repeater. Upon assertion of CRS\_DV, the PHY shall ensure that RXD[1:0]=00 until proper receive decoding takes place.

#### Transmit Enable (TX EN)

Transmit Enable TX\_EN indicates that the MAC is presenting di-bits on TXD[1:0] on the RMII for trans-mission. TX\_EN shall be asserted synchronously with the first nibble of the preamble and shall remain asserted while all di-bits to be transmitted are presented to the RMII. TX\_EN shall be negated prior to the first REF\_CLK following the final di-bit of a frame. TX\_EN shall transition synchronously with respect to REF\_CLK.

#### **Transmit Data [1:0] (TXD[1:0])**

Transmit Data TXD[1:0] shall transition synchronously with respect to REF\_CLK. When TX\_EN is asserted, TXD[1:0] are accepted for transmission by the PHY. TXD[1:0] shall be "00" to indicate idle when TX\_EN is de-asserted. Values of TXD[1:0] other than "00" when TX\_EN is de-asserted are reserved for out-of-band signalling (to be defined). Values other than "00" on TXD[1:0] while TX\_EN is deasserted shall be ignored by the PHY.

#### **Collision Detection**

Since the definition of CRS\_DV and TX\_EN both contain an accurate indication of the start of frame, the MAC can reliably regenerate the COL signal of the MII by ANDing TX\_EN and CRS\_DV.

During the IPG time following the successful transmission of a frame, the COL signal is asserted by some transceivers as a self-test. The Signal Quality Error (SQE) function will not be supported by the reduced MII due to the lack of the COL signal. Historically, SQE was present to indicate that a transceiver located physically remote from the MAC was functioning. Since the reduced MII only supports chip-to-chip connections on a PCB, SQE functionality is not required.

#### RX ER

The PHY shall provide RX\_ER as an output according to the rules specified in IEEE 802.3u [2] (see Clause 24, Figure 24-11 - Receive State Diagram). RX\_ER shall be asserted for one or more REF\_CLK periods to indicate that an error (e.g. a coding error or any error that a PHY is capable of detecting, and that may otherwise be undetectable by the MAC sublayer) was detected somewhere in the frame presently being transferred from the PHY. RX\_ER shall transition synchronously with respect to REF\_CLK. While CRS\_DV is de-asserted, RX\_ER shall have no effect on the MAC.

#### **RMII AC Characteristics**

| Symbol          | Parameter                                                                  | Min | Тур | Max | Units |

|-----------------|----------------------------------------------------------------------------|-----|-----|-----|-------|

|                 | REF_CLK Frequency                                                          |     | 50  |     | MHz   |

|                 | REF_CLK Duty Cycle                                                         | 35  |     | 65  | %     |

| t <sub>SU</sub> | TXD[1:0]. TX_EN, RXD[1:0], CRS_DV, RX_ER Data Set-Up to REF_CLK Rising     | 4   |     |     | ns    |

| t <sub>H</sub>  | TXD[1:0]. TX_EN, RXD[1:0], CRS_DV, RXER Data Hold from REF_CLK Rising Edge | 2   |     |     | ns    |

#### **RMII Transmit Timing**

| Parameter                                                 | Min | Тур | Max | Units |

|-----------------------------------------------------------|-----|-----|-----|-------|

| REF_CLK Frequency                                         |     | 50  |     | MHz   |

| TXEN, TXD[1:0], TX_EN, Data Setup to REF_CLK rising edge  | 4   |     |     | ns    |

| TXEN, TXD[1:0], TX_EN, Data hold from REF_CLK rising edge | 2   |     |     | ns    |

#### **RMII Receive Timing**

| Parameter                                                     | Min | Тур | Max | Units |

|---------------------------------------------------------------|-----|-----|-----|-------|

| REF_CLK Frequency                                             |     | 50  |     | MHz   |

| RXD[1:0], CRS_DV, RX_ER Output delay from REF_CLK rising edge | 2.8 |     | 10  | ns    |

|                                                               |     |     |     |       |

| Auto Crossover (Auto MDI/MDI-X)                               |     |     |     |       |

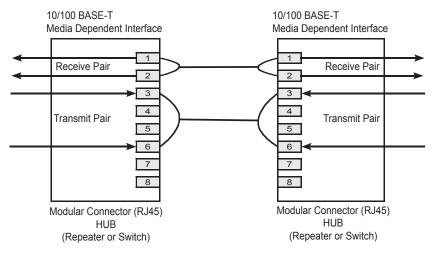

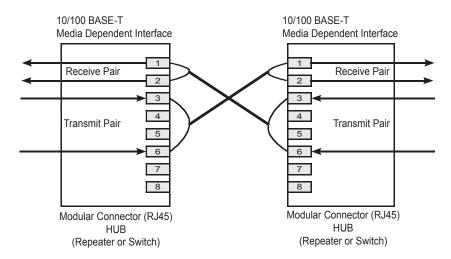

Automatic MDI/MDI-X configuration is intended to eliminate the need for crossover cables between similar devices. The assignment of pin-outs for a 10/100 BASE-T crossover function cable is shown below.

This feature can eliminate the confusion in real applications so both straight cable and crossover cable can be used. This feature is controlled by register 1f:13. See "Register 1fh–100BaseTX PHY Controller" section for details.

Figure 1. Straight Through Cable

Figure 2. Crossover Cable

#### **Power Management**

The KS8721B/BT offers the following modes for power management:

- Power Down Mode: This mode can be achieved by writing to Register 0.11 or pulling pin 30 PD# Low.

- Power Saving Mode: This mode can be disabled by writing to Register 1fh.10. The KS8721B/BT will then turn off everything except for the Energy Detect and PLL circuits when the cable is not installed. In other words, the KS8721B/BT will shutdown most of the internal circuits to save power if there is no link. Power saving mode will be in his most effective state when auto-negotiation mode is enable.

#### 100BT FX Mode

100BT FX mode is activated when FXSD/FXEN is higher 0.6V (This pin has a default pull down). Under this mode, the autonegotiation and auto-MDIX features are disabled.

In fiber operation FXSD pin should connect to the SD (signal detect) output of the fiber module. The internal threshold of FXSD is around  $1/2 \ V_{DD} \pm 50 mV$  (1.25V  $\pm 0.05 V$ ). Above this level, it is considered fiber signal detected, and the operation is summarized in the following table:

| FXSD/FXEN                                 | Condition                                |

|-------------------------------------------|------------------------------------------|

| Less than 0.6V                            | 100TX mode                               |

| Less than 1.25V,<br>but greater than 0.6V | FX mode No signal detected FEF generated |

| Greater than 1.25                         | FX mode signal detected                  |

Table 1. 100BT FX Mode

To ensure a proper operation, the swing of fiber module SD should cover the threshold variation. A resistive voltage divider is recommended to adjust the SD voltage range.

FEF (Far End Fault), repetition of a special pattern which consists of 84-one and 1-zero, is generated under "FX mode with no signal detected." The purpose of FEF is to notify the sender of a faulty link. When receiving a FEF, the LINK will go down to indicate a fault, even with fiber signal detected. The transmitter does not affect by receiving a FEF and still sends out its normal transmit pattern from MAC. FEF can be disabled by strapping pin 27 low. Refer to "Strapping Options' Isection."

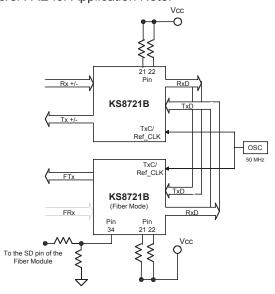

#### **Media Converter Operation**

KS8721B/BT is capable of performing media conversion with 2 parts in a back to back RMII loop-back mode as indicated in the diagram. Both parts are in RMII mode and with RMII BTB asserted (pin 21 and 22 strapped high). One part is operating at TX mode and the other in FX mode. Both parts can share a common 50MHz oscillator.

Under this operation, auto-negotiation on the TX side will prohibit 10baseT link up. TXD2, active High, can disable transmitter and set it at tri-state. RXD2 serves as energy detection can indicate if there is line signal detected. TXD3 should tied low and RXD3 let float. Please contact Micrel FAE for Application Note.

Figure 3. Fiber Module

**Register Map**

| Register No. | Description                                    |

|--------------|------------------------------------------------|

| 0h           | Basic Control Register                         |

| 1h           | Basic Status Register                          |

| 2h           | PHY Identifier I                               |

| 3h           | PHY Identifier II                              |

| 4h           | Auto-Negotiation Advertisement Register        |

| 5h           | Auto-Negotiation Link Partner Ability Register |

| 6h           | Auto-Negotiation Expansion Register            |

| 7h           | Auto-Negotiation Next Page Register            |

| 8h           | Link Partner Next Page Ability                 |

| 15h          | RXER Counter Register                          |

| 1bh          | Interrupt Control/Status Register              |

| 1fh          | 100BaseTX PHY Control Register                 |

| Address  | Name                     | Description Mode <sup>(Note 1)</sup>                                                                | Default |                  |

|----------|--------------------------|-----------------------------------------------------------------------------------------------------|---------|------------------|

| Register | Oh - Basic Control       |                                                                                                     | •       | •                |

| 0.15     | Reset                    | 1 = software reset. Bit is self-clearing                                                            | RW/SC   | 0                |

| 0.14     | Loop-back                | 1 = loop-back mode; 0 = normal operation                                                            | RW      | 0                |

| 0.13     | Speed Select (LSB)       | 1 = 100Mbps; 0 = 10Mbps<br>Ignored if Auto-Negotiation is enabled (0.12 = 1)                        | RW      | Set by<br>SPD100 |

| 0.12     | Auto-Negotiation Enable  | 1 = enable auto-negotiation process (override 0.13 and 0.8)<br>0 = disable auto-negotiation process | RW      | Set by<br>NWAYEN |

| 0.11     | Power Down               | 1 = power down mode; 0 = normal operation                                                           | RW      | 0                |

| 0.10     | Isolate                  | 1 = electrical isolation of PHY from MII and TX+/TX-<br>0 = normal operation                        | RW      | Set by ISO       |

| 0.9      | Restart Auto-Negotiation | 1 = restart auto-negotiation process 0 = normal operation. Bit is self-clearing                     | RW/SC   | 0                |

| 0.8      | Duplex Mode              | 1 = full duplex; 0 = half duplex                                                                    | RW      | Set by<br>DUPLEX |

| 0.7      | Collision Test           | 1 = enable COL test; 0 = disable COL test                                                           | RW      | 0                |

| 0.6:1    | Reserved                 |                                                                                                     | RO      | 0                |

| 0.0      | Disable<br>Transmitter   | 0 = enable transmitter<br>1 = disable transmitter                                                   | R/W     | 0                |

| Register | 1h - Basic Status        |                                                                                                     | •       |                  |

| 1.15     | 100BaseT4                | 1 = T4 capable; 0 = not T4 capable                                                                  | RO      | 0                |

| 1.14     | 100BaseTX Full Duplex    | 1 = capable of 100BaseX full duplex<br>0 = not capable of 100BaseX full duplex                      | RO      | 1                |

| 1.13     | 100BaseTX Half Duplex    | 1 = capable of 100BaseX half duplex<br>0 = not capable of 100BaseX half duplex                      | RO      | 1                |

| 1.12     | 10BaseT Full Duplex      | 1 = 10Mbps with full duplex<br>0 = no 10Mbps with full duplex capability                            | RO      | 1                |

| 1.11     | 10BaseT Half Duplex      | 1 = 10Mbps with half duplex<br>0 = no 10Mbps with half duplex capability                            | RO      | 1                |

Note 1. RW: Read/Write, RO: Read only, SC: Self clear, LH: Latch High, LL: Latch Low. Some of the default values are set by strap-in. See "Srap-ping Options."

| Address           | Name                       | Description                                                                                                         | Mode <sup>(Note 1)</sup> | Default                      |

|-------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------|

| 1.10:7            | Reserved                   |                                                                                                                     | RO                       | 0                            |

| 1.6               | No Preamble                | 1 = preamble suppression; 0 = normal preamble                                                                       | RO                       | 1                            |

| 1.5               | Auto-Negotiation Complete  | 1 = auto-negotiation process completed 0 = auto-negotiation process not completed                                   | RO                       | 0                            |

| 1.4               | Remote Fault               | 1 = remote fault; 0 = no remote fault                                                                               | RO/LH                    | 0                            |

| 1.3               | Auto-Negotiation Ability   | 1 = capable to perform auto-negotiation 0 = unable to perform auto-negotiation                                      | RO                       | 1                            |

| 1.2               | Link Status                | 1 = link is up; 0 = link is down                                                                                    | RO/LL                    | 0                            |

| 1.1               | Jabber Detect              | 1 = jabber detected; 0 = jabber not detected. Default is Low                                                        | RO/LH                    | 0                            |

| 1.0               | Extended Capability        | 1 = supports extended capabilities registers                                                                        | RO                       | 1                            |

| Register 2        | h - PHY Identifier 1       |                                                                                                                     |                          |                              |

| 2.15:0            | PHY ID Number              | Assigned to the 3rd through 18th bits of the Organizationally Unique Identifier (OUI). Micrel's OUI is 0010A1 (hex) | RO                       | 0022h                        |

| Register 3        | Sh - PHY Identifier 2      |                                                                                                                     |                          |                              |

| 3.15:10<br>000101 | PHY ID Number              | Assigned to the 19th through 24th bits of the Organizational Unique Identifier (OUI). Micrel's OUI is 0010A1 (hex)  | У                        | RO                           |

| 3.9:4             | Model Number               | Six bit manufacturer's model number                                                                                 | RO                       | 100001                       |

| 3.3:0             | Revision Number            | Four bit manufacturer's model number                                                                                | RO                       | 10001                        |

|                   | Ih - Auto-Negotiation Adve |                                                                                                                     | 110                      | 1001                         |

| 4.15              | Next Page                  | 1 = next page capable; 0 = no next page capability.                                                                 | RW                       | 0                            |

| 4.14              | Reserved                   |                                                                                                                     | RO                       | 0                            |

| 4.13              | Remote Fault               | 1 = remote fault supported; 0 = no remote fault                                                                     | RW                       | 0                            |

| 4.12 : 11         | Reserved                   |                                                                                                                     | RO                       | 0                            |

| 4.10              | Pause                      | 1 = pause function supported; 0 = no pause function                                                                 | RW                       | 0                            |

| 4.9               | 100BaseT4                  | 1 = T4 capable; 0 = no T4 capability                                                                                | RO                       | 0                            |

| 4.8               | 100BaseTX Full Duplex      | 1 = TX with full duplex; 0 = no TX full duplex capability                                                           | RW                       | Set by<br>SPD100 &<br>DUPLEX |

| 4.7               | 100BaseTX                  | 1 = TX capable; 0 = no TX capability                                                                                | RW                       | Set by<br>SPD100             |

| 4.6               | 10BaseT Full Duplex        | 1 = 10Mbps with full duplex<br>0 = no 10Mbps full duplex capability                                                 | RW                       | Set by<br>DUPLEX             |

| 4.5               | 10BaseT                    | 1 = 10Mbps capable; 0 = no 10Mbps capability                                                                        | RW                       | 1                            |

| 4.4:0             | Selector Field             | [00001] = IEEE 802.3                                                                                                | RW                       | 00001                        |

| Register 8        | h - Auto-Negotiation Link  | Partner Ability                                                                                                     |                          |                              |

| 5.15              | Next Page                  | 1 = next page capable; 0 = no next page capability                                                                  | RO                       | 0                            |

| 5.14              | Acknowledge                | 1 = link code word received from partner 0 = link code word not yet received                                        | RO                       | 0                            |

| 5.13              | Remote Fault               | 1 = remote fault detected; 0 = no remote fault                                                                      | RO                       | 0                            |

| 5.12              | Reserved                   |                                                                                                                     | RO                       | 0                            |

Note 1. RW: Read/Write, RO: Read only, SC: Self clear, LH: Latch High, LL: Latch Low. Some of the default values are set by strap-in. See "Srap-ping Options."

| Address    | Name                                  | Description                                                                                                                               | Mode <sup>(Note 1)</sup> | Default |

|------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------|

| 5.11:10    | Pause                                 | 5.10 5 .11                                                                                                                                | RO                       | 0       |

|            |                                       | 0 0                                                                                                                                       |                          |         |

|            |                                       | No PAUSE                                                                                                                                  |                          |         |

|            |                                       | Asymmetric PAUSE (link partner)                                                                                                           |                          |         |

|            |                                       | 1 0                                                                                                                                       |                          |         |

|            |                                       | Symmetric PAUSE                                                                                                                           |                          |         |

|            |                                       |                                                                                                                                           |                          |         |

| 5.9        | 100 BaseT4                            | 1 = T4 capable; 0 = no T4 capability                                                                                                      | RO                       | 0       |

| 5.8        | 100BaseTX Full Duplex                 | 1 = TX with full duplex; 0 = no TX full duplex capability                                                                                 | RO                       | 0       |

| 5.7        | 100BaseTX                             | 1 = TX capable; 0 = no TX capability                                                                                                      | RO                       | 0       |

| 5.6        | 10BaseT Full Duplex                   | 1 = 10Mbps with full duplex                                                                                                               | RO                       | 0       |

|            | ·                                     | 0 = no 10Mbps full duplex capability                                                                                                      |                          |         |

| 5.5        | 10BaseT                               | 1 = 10Mbps capable; 0 = no 10Mbps capability                                                                                              | RO                       | 0       |

| 5.4:0      | Selector Field                        | [00001] = IEEE 802.3                                                                                                                      | RO                       | 00001   |

| Register ( | 6h - Auto-Negotiation Exp             | ansion                                                                                                                                    |                          |         |

| 6.15:5     | Reserved                              |                                                                                                                                           | RO                       | 0       |

| 6.4        | Parallel Detection Fault              | 1 = fault detected by parallel detection                                                                                                  | RO/LH                    | 0       |

|            |                                       | 0 = no fault detected by parallel detection.                                                                                              |                          |         |

| 6.3        | Link Partner Next<br>Page Able        | 1 = link partner has next page capability     0 = link partner does not have next page capability                                         | RO                       | 0       |

| 6.2        | Next Page Able                        | 1 = local device has next page capability 0 = local device does not have next page capability                                             | RO                       | 1       |