# 3.75 kV, 6-Channel, SPIsolator Digital Isolator for SPI with Delay Clock

Data Sheet ADuM3150

#### **FEATURES**

Supports up to 40 MHz SPI clock speed in delay clock mode Supports up to 17 MHz SPI clock speed in 4-wire mode 4 high speed, low propagation delay, SPI signal isolation channels

2 data channels at 250 kbps Delayed compensation clock line 20-lead SSOP with 5.1 mm creepage High temperature operation: 125°C

High common-mode transient immunity: >25 kV/μs

Safety and regulatory approvals

UL recognition per UL 1577

3750 V rms for 1 minute

CSA Component Acceptance Notice 5A

VDE certificate of conformity

DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

V<sub>IORM</sub> = 565 V peak

## **APPLICATIONS**

Industrial programmable logic controllers (PLC)

Sensor isolation

#### **GENERAL DESCRIPTION**

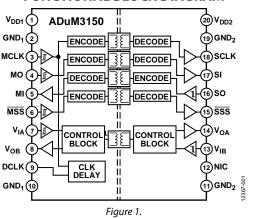

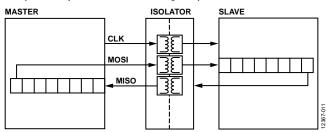

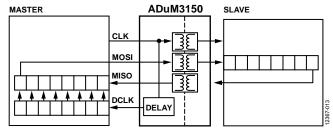

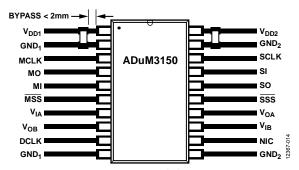

The ADuM3150¹ is a 6-channel SPIsolator™ digital isolator optimized for isolated serial peripheral interfaces (SPIs). Based on the Analog Devices, Inc., *i*Coupler® chip scale transformer technology, the low propagation delay in the CLK, MO/SI, MI/SO, and SS SPI bus signals supports SPI clock rates of up to 17 MHz. These channels operate with 14 ns propagation delay and 1 ns jitter to optimize timing for SPI.

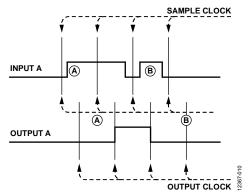

The ADuM3150 isolator also provides two additional independent low data rate isolation channels, one channel in each direction. Data in the slow channels is sampled and serialized for a 250 kbps data rate with  $2.5~\mu s$  of jitter.

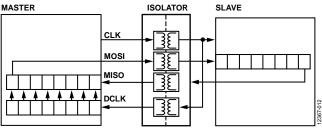

The ADuM3150 supports a delay clock output on the master side of the device. This output can be used with an additional clocked port on the master to support 40 MHz clock performance. See the Delay Clock section for more information.

## **FUNCTIONAL BLOCK DIAGRAM**

**Table 1. Related Products**

| Product                        | Description                                   |

|--------------------------------|-----------------------------------------------|

| ADuM3151/ADuM3152/<br>ADuM3153 | 3.75 kV, multichannel SPI isolator            |

| ADuM3154                       | 3.75 kV, multiple slave SPI isolator          |

| ADuM4150                       | 5 kV, high speed, clock delayed<br>SPIsolator |

| ADuM4151/ADuM4152/             | 5 kV, multichannel SPI isolator               |

| ADuM4153                       |                                               |

| ADuM4154                       | 5 kV, multiple slave SPI isolator             |

<sup>&</sup>lt;sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; 6,262,600; and 7,075,329. Other patents are pending.

## **TABLE OF CONTENTS**

| Features                                               |

|--------------------------------------------------------|

| Applications                                           |

| Functional Block Diagram                               |

| General Description                                    |

| Revision History                                       |

| Specifications                                         |

| Electrical Characteristics—5 V Operation               |

| Electrical Characteristics—3.3 V Operation             |

| Electrical Characteristics—Mixed 5 V/3.3 V Operation   |

| Electrical Characteristics—Mixed 3.3 V/5 V Operation   |

| Package Characteristics1                               |

| Regulatory Information1                                |

| Insulation and Safety Related Specifications           |

| DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 Insulation |

| Characteristics                                        |

|                                                        |

| REVISION HISTORY                                       |

|                                                        |

| Recommended Operating Conditions            | 12 |

|---------------------------------------------|----|

| Absolute Maximum Ratings                    | 13 |

| ESD Caution                                 | 13 |

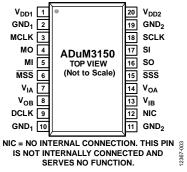

| Pin Configuration and Function Descriptions | 14 |

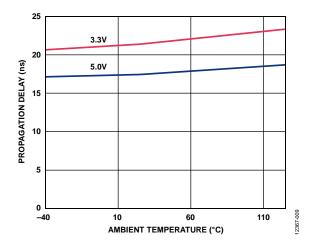

| Typical Performance Characteristics         | 15 |

| Applications Information                    | 16 |

| Introduction                                | 16 |

| Printed Circuit Board (PCB) Layout          | 17 |

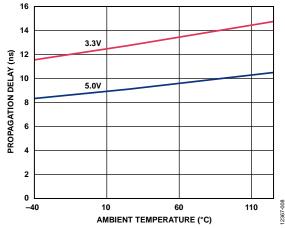

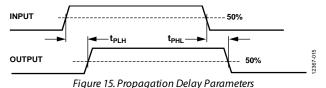

| Propagation Delay Related Parameters        | 18 |

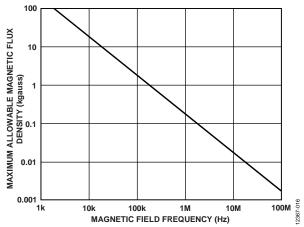

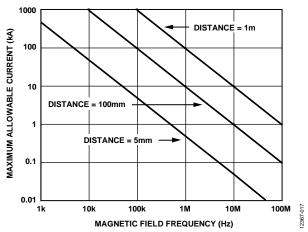

| DC Correctness and Magnetic Field Immunity  | 18 |

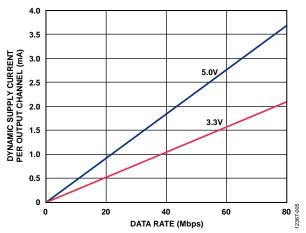

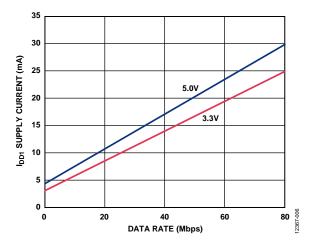

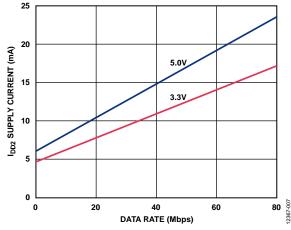

| Power Consumption                           | 19 |

| Insulation Lifetime                         | 19 |

| Outline Dimensions                          | 21 |

| Ordering Guide                              | 21 |

## F

#### 7/2017—Rev. B to Rev. C

Changes to Output Voltages, Logic High Parameter, Table 5 and Output Voltages, Logic Low Parameter, Table 5......6 Changes to Output Voltages, Logic High Parameter, Table 7 and Output Voltages, Logic Low Parameter, Table 7......8 Changes to Output Voltages, Logic High Parameter, Table 9 and Output Voltages, Logic Low Parameter, Table 9......10 Change to Pin 3, Direction Column, Table 17.....14

## 8/2016-Rev. A to Rev. B

| 3/2015—Rev. 0 to Rev. A                 |   |

|-----------------------------------------|---|

| Changes to Features Section and Table 1 | 1 |

Changes to Figure 11......17

| Changes to Features Section and Table 1                  | 1  |

|----------------------------------------------------------|----|

| Changes to Table 3                                       | 4  |

| Changes to Table 5                                       | 6  |

| Changes to Table 7                                       |    |

| Changes to Table 9                                       | 10 |

| Changes to Table 10, Regulatory Information Section, and |    |

| Table 11                                                 | 11 |

| Changes to Table 13 and Figure 2                         | 12 |

| Changes to Figure 4 to Figure 7                          | 15 |

| Changes to High Speed Channels Section                   | 16 |

| Changes to Power Consumption Section                     | 19 |

| -                                                        |    |

## 7/2014—Revision 0: Initial Version

## **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS—5 V OPERATION**

All typical specifications are at  $T_A = 25^{\circ}\text{C}$  and  $V_{DD1} = V_{DD2} = 5 \text{ V}$ . Minimum and maximum specifications apply over the entire recommended operation range:  $4.5 \text{ V} \le V_{DD1} \le 5.5 \text{ V}$ ,  $4.5 \text{ V} \le V_{DD2} \le 5.5 \text{ V}$ , and  $-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ , unless otherwise noted. Switching specifications are tested with  $C_L = 15 \text{ pF}$  and CMOS signal levels, unless otherwise noted.

**Table 2. Switching Specifications**

|                                                              |                                     |      | A Grad | е   |      | B Grad | е   |      |                                      |

|--------------------------------------------------------------|-------------------------------------|------|--------|-----|------|--------|-----|------|--------------------------------------|

| Parameter                                                    | Symbol                              | Min  | Тур    | Max | Min  | Тур    | Max | Unit | Test Conditions/Comments             |

| MCLK, MO, SO                                                 |                                     |      |        |     |      |        |     |      |                                      |

| SPI Clock Rate                                               | $SPI_{MCLK}$                        |      |        | 10  |      |        | 17  | MHz  |                                      |

| Data Rate Fast (MO, SO)                                      | DR <sub>FAST</sub>                  |      |        | 40  |      |        | 40  | Mbps | Within PWD limit                     |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |      |        | 25  |      | 12     | 14  | ns   | 50% input to 50% output              |

| Pulse Width                                                  | PW                                  | 12.5 |        |     | 12.5 |        |     | ns   | Within PWD limit                     |

| Pulse Width Distortion                                       | PWD                                 |      |        | 2   |      |        | 2   | ns   | t <sub>PLH</sub> — t <sub>PHL</sub>  |

| Codirectional Channel Matching <sup>1</sup>                  | <b>t</b> <sub>PSKCD</sub>           |      |        | 2   |      |        | 2   | ns   |                                      |

| Jitter, High Speed                                           | J <sub>HS</sub>                     |      | 1      |     |      | 1      |     | ns   |                                      |

| MSS                                                          |                                     |      |        |     |      |        |     |      |                                      |

| Data Rate Fast                                               | DR <sub>FAST</sub>                  |      |        | 40  |      |        | 40  | Mbps | Within PWD limit                     |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |      | 21     | 25  |      | 21     | 25  | ns   | 50% input to 50% output              |

| Pulse Width                                                  | PW                                  | 12.5 |        |     | 12.5 |        |     | ns   | Within PWD limit                     |

| Pulse Width Distortion                                       | PWD                                 |      |        | 2   |      |        | 2   | ns   | tplh — tphl                          |

| Setup Time <sup>2</sup>                                      | $\overline{MSS}_{SETUP}$            | 1.5  |        |     | 10   |        |     | ns   |                                      |

| Jitter, High Speed                                           | J <sub>HS</sub>                     |      | 1      |     |      | 1      |     | ns   |                                      |

| DCLK                                                         |                                     |      |        |     |      |        |     |      |                                      |

| Data Rate                                                    |                                     |      |        | 40  |      |        | 40  | MHz  |                                      |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |      |        | 50  |      |        | 35  | ns   | $t_{PMCLK} + t_{PSO} + 3 \text{ ns}$ |

| Pulse Width Distortion                                       | PWD                                 |      |        | 3   |      |        | 3   | ns   | t <sub>PLH</sub> — t <sub>PHL</sub>  |

| Pulse Width                                                  | PW                                  | 12   |        |     | 12   |        |     | ns   | Within PWD limit                     |

| Clock Delay Error                                            | DCLK <sub>ERR</sub>                 | 0    | 4.5    | 12  | 1    | 5.5    | 12  | ns   | $t_{PDCLK} - (t_{PMCLK} + t_{PSO})$  |

| Jitter                                                       | J <sub>DCLK</sub>                   |      | 1      |     |      | 1      |     | ns   |                                      |

| V <sub>IA</sub> , V <sub>IB</sub>                            |                                     |      |        |     |      |        |     |      |                                      |

| Data Rate Slow                                               | DR <sub>SLOW</sub>                  |      |        | 250 |      |        | 250 | kbps | Within PWD limit                     |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> | 0.1  |        | 2.6 | 0.1  |        | 2.6 | μs   | 50% input to 50% output              |

| Pulse Width                                                  | PW                                  | 4    |        |     | 4    |        |     | μs   | Within PWD limit                     |

| Jitter, Low Speed                                            | $\mathbf{J}_{LS}$                   |      |        | 2.5 |      |        | 2.5 | μs   |                                      |

| V <sub>lx</sub> <sup>3</sup> Minimum Input Skew <sup>4</sup> | t <sub>VIx SKEW</sub>               | 10   |        |     | 10   |        |     | ns   |                                      |

<sup>1</sup> Codi<u>recti</u>onal channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same sid<u>e of</u> the isolation barrier.

<sup>&</sup>lt;sup>2</sup> The MSS signal is glitch filtered in both speed grades, whereas the other fast signals are not glitch filtered in the B grade. To guarantee that MSS reaches the output ahead of another fast signal, set up MSS prior to the competing signal by different times depending on speed grade.

$<sup>^{3}</sup>$   $V_{1x} = V_{1A}$  or  $V_{1}$

<sup>&</sup>lt;sup>4</sup> An internal asynchronous clock, not available to users, samples the low speed signals. If edge sequence in codirectional channels is critical to the end application, the leading pulse must be at least 1 type skew time ahead of a later pulse to guarantee the correct order or simultaneous arrival at the output.

Table 3. For All Grades<sup>1, 2, 3</sup>

| Parameter                                                     | Symbol                         | Min                  | Тур   | Max                  | Unit    | Test Conditions/Comments                                                                   |

|---------------------------------------------------------------|--------------------------------|----------------------|-------|----------------------|---------|--------------------------------------------------------------------------------------------|

| SUPPLY CURRENT                                                |                                |                      |       |                      |         |                                                                                            |

| 1 MHz, A Grade and B Grade                                    | I <sub>DD1</sub>               |                      | 5     | 8.5                  | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                     |

|                                                               | I <sub>DD2</sub>               |                      | 6.5   | 11                   | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                     |

| 17 MHz, B Grade                                               | I <sub>DD1</sub>               |                      | 15    | 23                   | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                    |

|                                                               | $I_{DD2}$                      |                      | 13.5  | 21                   | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                    |

| DC SPECIFICATIONS                                             |                                |                      |       |                      |         |                                                                                            |

| $MCLK$ , $\overline{MSS}$ , $MO$ , $SO$ , $V_{IA}$ , $V_{IB}$ |                                |                      |       |                      |         |                                                                                            |

| Input Threshold                                               |                                |                      |       |                      |         |                                                                                            |

| Logic High                                                    | V <sub>IH</sub>                | $0.7 \times V_{DDx}$ |       |                      | V       |                                                                                            |

| Logic Low                                                     | VIL                            |                      |       | $0.3 \times V_{DDx}$ | V       |                                                                                            |

| Input Hysteresis                                              | V <sub>IHYST</sub>             |                      | 500   |                      | mV      |                                                                                            |

| Input Current per Channel                                     | l <sub>1</sub>                 | -1                   | +0.01 | +1                   | μΑ      | $0 \text{ V} \leq V_{\text{INPUT}} \leq V_{\text{DDx}}$                                    |

| SCLK, SSS, MI, SI, V <sub>OA</sub> , V <sub>OB</sub> , DCLK   |                                |                      |       |                      |         |                                                                                            |

| Output Voltages                                               |                                |                      |       |                      |         |                                                                                            |

| Logic High                                                    | V <sub>OH</sub>                | $V_{DDx} - 0.1$      | 5.0   |                      | V       | $I_{OUTPUT} = -20 \mu A$ , $V_{INPUT} = V_{IH}$                                            |

|                                                               |                                | $V_{DDx} - 0.4$      | 4.8   |                      | V       | $I_{OUTPUT} = -4 \text{ mA}, V_{INPUT} = V_{IH}$                                           |

| Logic Low                                                     | V <sub>OL</sub>                |                      | 0.0   | 0.1                  | V       | $I_{OUTPUT} = 20 \mu A, V_{INPUT} = V_{IL}$                                                |

|                                                               |                                |                      | 0.2   | 0.4                  | V       | $I_{OUTPUT} = 4 \text{ mA}, V_{INPUT} = V_{IL}$                                            |

| V <sub>DD1</sub> , V <sub>DD2</sub> Undervoltage Lockout      | UVLO                           |                      | 2.6   |                      | V       |                                                                                            |

| Supply Current for High Speed Channel                         |                                |                      |       |                      |         |                                                                                            |

| Dynamic Input                                                 | I <sub>DDI(D)</sub>            |                      | 0.080 |                      | mA/Mbps |                                                                                            |

| Dynamic Output                                                | I <sub>DDO(D)</sub>            |                      | 0.046 |                      | mA/Mbps |                                                                                            |

| Supply Current for All Low Speed Channels                     |                                |                      |       |                      |         |                                                                                            |

| Quiescent Side 1 Current                                      | I <sub>DD1(Q)</sub>            |                      | 4.4   |                      | mA      |                                                                                            |

| Quiescent Side 2 Current                                      | I <sub>DD2(Q)</sub>            |                      | 6.1   |                      | mA      |                                                                                            |

| AC SPECIFICATIONS                                             |                                |                      |       |                      |         |                                                                                            |

| Output Rise/Fall Time                                         | t <sub>R</sub> /t <sub>F</sub> |                      | 2.5   |                      | ns      | 10% to 90%                                                                                 |

| Common-Mode Transient Immunity <sup>4</sup>                   | CM                             | 25                   | 35    |                      | kV/μs   | $V_{INPUT} = V_{DDx}$ , $V_{CM} = 1000 \text{ V}$<br>Transient magnitude = $800 \text{ V}$ |

$<sup>^{1}</sup>V_{DDx} = V_{DD1} \text{ or } V_{DD2}.$   $^{2}V_{INPUT} \text{ is the input voltage of any of the MCLK, } \overline{MSS}, MO, SO, V_{IA}, \text{ or } V_{IB} \text{ pins.}$   $^{3}I_{OUTPUT} \text{ is the output current of any of the SCLK, } \overline{DCLK, } \overline{SSS}, MI, SI, V_{OA}, \text{ or } V_{OB} \text{ pins.}$   $^{4}|CM| \text{ is the maximum common-mode voltage slew rate that can be sustained while maintaining output voltages within the } V_{OH} \text{ and } V_{OL} \text{ limits. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.}$

## **ELECTRICAL CHARACTERISTICS—3.3 V OPERATION**

All typical specifications are at  $T_A = 25^{\circ}\text{C}$  and  $V_{DD1} = V_{DD2} = 3.3 \text{ V}$ . Minimum and maximum specifications apply over the entire recommended operation range:  $3.0 \text{ V} \le V_{DD1} \le 3.6 \text{ V}$ ,  $3.0 \text{ V} \le V_{DD2} \le 3.6 \text{ V}$ , and  $-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ , unless otherwise noted. Switching specifications are tested with  $C_L = 15 \text{ pF}$  and CMOS signal levels, unless otherwise noted.

**Table 4. Switching Specifications**

| Parameter                                                    |                                     | A Grade |      |     |      | B Grade | e    |      |                                              |

|--------------------------------------------------------------|-------------------------------------|---------|------|-----|------|---------|------|------|----------------------------------------------|

|                                                              | Symbol                              | Min     | Тур  | Max | Min  | Тур     | Max  | Unit | Test Conditions/Comments                     |

| MCLK, MO, SO                                                 |                                     |         |      |     |      |         |      |      |                                              |

| SPI Clock Rate                                               | SPI <sub>MCLK</sub>                 |         |      | 8.3 |      |         | 12.5 | MHz  |                                              |

| Data Rate Fast (MO, SO)                                      | DR <sub>FAST</sub>                  |         |      | 40  |      |         | 40   | Mbps | Within PWD limit                             |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |         |      | 30  |      |         | 20   | ns   | 50% input to 50% output                      |

| Pulse Width                                                  | PW                                  | 12.5    |      |     | 12.5 |         |      | ns   | Within PWD limit                             |

| Pulse Width Distortion                                       | PWD                                 |         |      | 3   |      |         | 3    | ns   | tplh - tphl                                  |

| Codirectional Channel Matching <sup>1</sup>                  | t <sub>PSKCD</sub>                  |         |      | 3   |      |         | 3    | ns   |                                              |

| Jitter, High Speed                                           | J <sub>HS</sub>                     |         | 1    |     |      | 1       |      | ns   |                                              |

| MSS                                                          |                                     |         |      |     |      |         |      |      |                                              |

| Data Rate Fast                                               | DR <sub>FAST</sub>                  |         |      | 40  |      |         | 40   | Mbps | Within PWD limit                             |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |         |      | 30  |      |         | 30   | ns   | 50% input to 50% output                      |

| Pulse Width                                                  | PW                                  | 12.5    |      |     | 12.5 |         |      | ns   | Within PWD limit                             |

| Pulse Width Distortion                                       | PWD                                 |         |      | 3   |      |         | 3    | ns   | tplh — tphl                                  |

| Setup Time <sup>2</sup>                                      | MSS <sub>SETUP</sub>                | 1.5     |      |     | 10   |         |      | ns   |                                              |

| Jitter, High Speed                                           | J <sub>HS</sub>                     |         | 1    |     |      | 1       |      | ns   |                                              |

| DCLK                                                         |                                     |         |      |     |      |         |      |      |                                              |

| Data Rate                                                    |                                     |         |      | 40  |      |         | 40   | MHz  |                                              |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |         |      | 60  |      |         | 40   | ns   | t <sub>PMCLK</sub> + t <sub>PSO</sub> + 3 ns |

| Pulse Width Distortion                                       | PWD                                 |         |      | 3   |      |         | 3    | ns   | tplh — tphl                                  |

| Pulse Width                                                  | PW                                  | 12      |      |     | 12   |         |      | ns   | Within PWD limit                             |

| Clock Delay Error                                            | DCLK <sub>ERR</sub>                 | -4      | +2.4 | +9  | -3   | +2.5    | +8   | ns   | tpdclk - (tpmclk + tpso)                     |

| Jitter                                                       | J <sub>DCLK</sub>                   |         | 1    |     |      | 1       |      | ns   |                                              |

| $V_{IA}$ , $V_{IB}$                                          |                                     |         |      |     |      |         |      |      |                                              |

| Data Rate Slow                                               | DR <sub>SLOW</sub>                  |         |      | 250 |      |         | 250  | kbps | Within PWD limit                             |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> | 0.1     |      | 2.6 | 0.1  |         | 2.6  | μs   | 50% input to 50% output                      |

| Pulse Width                                                  | PW                                  | 4       |      |     | 4    |         |      | μs   | Within PWD limit                             |

| Jitter, Low Speed                                            | J <sub>LS</sub>                     |         |      | 2.5 |      |         | 2.5  | μs   |                                              |

| V <sub>lx</sub> <sup>3</sup> Minimum Input Skew <sup>4</sup> | t <sub>VIx</sub> skew               | 10      |      |     | 10   |         |      | ns   |                                              |

¹ Codirectional channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier.

<sup>&</sup>lt;sup>2</sup> The MSS signal is glitch filtered in both speed grades, whereas the other fast signals are not glitch filtered in the B grade. To guarantee that MSS reaches the output ahead of another fast signal, set up MSS prior to the competing signal by different times depending on speed grade.

$<sup>^3</sup>$   $V_{Ix} = V_{IA}$  or  $V_{II}$

<sup>&</sup>lt;sup>4</sup> An internal asynchronous clock, not available to users, samples the low speed signals. If edge sequence in codirectional channels is critical to the end application, the leading pulse must be at least 1 tvik skew time ahead of a later pulse to guarantee the correct order or simultaneous arrival at the output.

**Table 5. For All Grades**<sup>1, 2, 3</sup>

| Parameter                                                   | Symbol                         | Min                  | Тур   | Max                        | Unit    | Test Conditions/Comments                                                      |

|-------------------------------------------------------------|--------------------------------|----------------------|-------|----------------------------|---------|-------------------------------------------------------------------------------|

| SUPPLY CURRENT                                              | -                              |                      | *     |                            |         |                                                                               |

| 1 MHz, A Grade and B Grade                                  | I <sub>DD1</sub>               |                      | 3.5   | 6                          | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                        |

|                                                             | I <sub>DD2</sub>               |                      | 4.9   | 8                          | mA      | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                        |

| 17 MHz, B Grade                                             | I <sub>DD1</sub>               |                      | 9.5   | 20                         | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                       |

|                                                             | $I_{DD2}$                      |                      | 8     | 16                         | mA      | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                       |

| DC SPECIFICATIONS                                           |                                |                      |       |                            |         |                                                                               |

| MCLK, MSS, MO, SO, VIA, VIB                                 |                                |                      |       |                            |         |                                                                               |

| Input Threshold                                             |                                |                      |       |                            |         |                                                                               |

| Logic High                                                  | $V_{IH}$                       | $0.7 \times V_{DDx}$ |       |                            | V       |                                                                               |

| Logic Low                                                   | V <sub>IL</sub>                |                      |       | $0.3\times V_{\text{DDx}}$ | V       |                                                                               |

| Input Hysteresis                                            | V <sub>IHYST</sub>             |                      | 500   |                            | mV      |                                                                               |

| Input Current per Channel                                   | I <sub>I</sub>                 | -1                   | +0.01 | +1                         | μΑ      | $0 \text{ V} \leq V_{\text{INPUT}} \leq V_{\text{DDx}}$                       |

| SCLK, $\overline{SSS}$ , MI, SI, $V_{OA}$ , $V_{OB}$ , DCLK |                                |                      |       |                            |         |                                                                               |

| Output Voltages                                             |                                |                      |       |                            |         |                                                                               |

| Logic High                                                  | V <sub>OH</sub>                | $V_{DDx} - 0.1$      | 3.3   |                            | V       | $I_{OUTPUT} = -20 \mu A, V_{INPUT} = V_{IH}$                                  |

|                                                             |                                | $V_{DDx} - 0.4$      | 3.1   |                            | V       | $I_{OUTPUT} = -4 \text{ mA}, V_{INPUT} = V_{IH}$                              |

| Logic Low                                                   | Vol                            |                      | 0.0   | 0.1                        | V       | $I_{OUTPUT} = 20 \mu A, V_{INPUT} = V_{IL}$                                   |

|                                                             |                                |                      | 0.2   | 0.4                        | V       | $I_{OUTPUT} = 4 \text{ mA}, V_{INPUT} = V_{IL}$                               |

| V <sub>DD1</sub> , V <sub>DD2</sub> Undervoltage Lockout    | UVLO                           |                      | 2.6   |                            | V       |                                                                               |

| Supply Current for High Speed Channel                       |                                |                      |       |                            |         |                                                                               |

| Dynamic Input                                               | I <sub>DDI(D)</sub>            |                      | 0.086 |                            | mA/Mbps |                                                                               |

| Dynamic Output                                              | I <sub>DDO(D)</sub>            |                      | 0.019 |                            | mA/Mbps |                                                                               |

| Supply Current for All Low Speed Channels                   |                                |                      |       |                            |         |                                                                               |

| Quiescent Side 1 Current                                    | I <sub>DD1(Q)</sub>            |                      | 2.9   |                            | mA      |                                                                               |

| Quiescent Side 2 Current                                    | I <sub>DD2(Q)</sub>            |                      | 4.6   |                            | mA      |                                                                               |

| AC SPECIFICATIONS                                           |                                |                      |       |                            |         |                                                                               |

| Output Rise/Fall Time                                       | t <sub>R</sub> /t <sub>F</sub> |                      | 2.5   |                            | ns      | 10% to 90%                                                                    |

| Common-Mode Transient Immunity <sup>4</sup>                 | CM                             | 25                   | 35    |                            | kV/μs   | $V_{INPUT} = V_{DDx}, V_{CM} = 1000 \text{ V}$<br>Transient magnitude = 800 V |

$<sup>^{1}</sup>V_{DDx} = V_{DD1} \text{ or } V_{DD2}.$   $^{2}V_{INPUT} \text{ is the input voltage of any of the MCLK, } \overline{MSS}, MO, SO, V_{IA}, \text{ or } V_{IB} \text{ pins.}$   $^{3}I_{OUTPUT} \text{ is the output current of any of the SCLK, } \overline{DCLK, } \overline{SSS}, MI, SI, V_{OA}, \text{ or } V_{OB} \text{ pins.}$   $^{4}|CM| \text{ is the maximum common-mode voltage slew rate that can be sustained while maintaining output voltages within the } V_{OH} \text{ and } V_{OL} \text{ limits. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.}$

## **ELECTRICAL CHARACTERISTICS—MIXED 5 V/3.3 V OPERATION**

All typical specifications are at  $T_A = 25^{\circ}\text{C}$  and  $V_{DD1} = 5 \text{ V}$ ,  $V_{DD2} = 3.3 \text{ V}$ . Minimum and maximum specifications apply over the entire recommended operation range:  $4.5 \text{ V} \le V_{DD1} \le 5.5 \text{ V}$ ,  $3.0 \text{ V} \le V_{DD2} \le 3.6 \text{ V}$ , and  $-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ , unless otherwise noted. Switching specifications are tested with  $C_L = 15 \text{ pF}$  and CMOS signal levels, unless otherwise noted.

**Table 6. Switching Specifications**

| Parameter                                                    |                                     |      | A Grade |     |      | B Grade |      |      |                                              |

|--------------------------------------------------------------|-------------------------------------|------|---------|-----|------|---------|------|------|----------------------------------------------|

|                                                              | Symbol                              | Min  | Тур     | Max | Min  | Тур     | Max  | Unit | Test Conditions/Comments                     |

| MCLK, MO, SO                                                 |                                     |      |         |     |      |         |      |      |                                              |

| SPI Clock Rate                                               | SPI <sub>MCLK</sub>                 |      |         | 9.2 |      |         | 15.6 | MHz  |                                              |

| Data Rate Fast (MO, SO)                                      | DR <sub>FAST</sub>                  |      |         | 40  |      |         | 40   | Mbps | Within PWD limit                             |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |      |         | 27  |      |         | 16   | ns   | 50% input to 50% output                      |

| Pulse Width                                                  | PW                                  | 12.5 |         |     | 12.5 |         |      | ns   | Within PWD limit                             |

| Pulse Width Distortion                                       | PWD                                 |      |         | 3   |      |         | 2    | ns   | tplh — tphl                                  |

| Codirectional Channel Matching <sup>1</sup>                  | t <sub>PSKCD</sub>                  |      |         | 2   |      |         | 2    | ns   |                                              |

| Jitter, High Speed                                           | J <sub>HS</sub>                     |      | 1       |     |      | 1       |      | ns   |                                              |

| MSS                                                          |                                     |      |         |     |      |         |      |      |                                              |

| Data Rate Fast                                               | DR <sub>FAST</sub>                  |      |         | 40  |      |         | 40   | Mbps | Within PWD limit                             |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |      |         | 27  |      |         | 26   | ns   | 50% input to 50% output                      |

| Pulse Width                                                  | PW                                  | 12.5 |         |     | 12.5 |         |      | ns   | Within PWD limit                             |

| Pulse Width Distortion                                       | PWD                                 |      |         | 2   |      |         | 2    | ns   | tplh — tphl                                  |

| Setup Time <sup>2</sup>                                      | MSS <sub>SETUP</sub>                | 1.5  |         |     | 10   |         |      | ns   |                                              |

| Jitter, High Speed                                           | J <sub>HS</sub>                     |      | 1       |     |      | 1       |      | ns   |                                              |

| DCLK                                                         |                                     |      |         |     |      |         |      |      |                                              |

| Data Rate                                                    |                                     |      |         | 40  |      |         | 40   | MHz  |                                              |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |      |         | 50  |      |         | 35   | ns   | t <sub>PMCLK</sub> + t <sub>PSO</sub> + 3 ns |

| Pulse Width Distortion                                       | PWD                                 |      |         | 3   |      |         | 3    | ns   | tplh — tphl                                  |

| Pulse Width                                                  | PW                                  | 12   |         |     | 12   |         |      | ns   | Within PWD limit                             |

| Clock Delay Error                                            | DCLK <sub>ERR</sub>                 | -5   | 0       | +7  | -5   | +1.2    | +9   | ns   | tpdclk — (tpmclk + tpso)                     |

| Jitter                                                       | J <sub>DCLK</sub>                   |      | 1       |     |      | 1       |      | ns   |                                              |

| $V_{IA}$ , $V_{IB}$                                          |                                     |      |         |     |      |         |      |      |                                              |

| Data Rate Slow                                               | DR <sub>SLOW</sub>                  |      |         | 250 |      |         | 250  | kbps | Within PWD limit                             |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> | 0.1  |         | 2.6 | 0.1  |         | 2.6  | μs   | 50% input to 50% output                      |

| Pulse Width                                                  | PW                                  | 4    |         |     | 4    |         |      | μs   | Within PWD limit                             |

| Jitter, Low Speed                                            | J <sub>LS</sub>                     |      |         | 2.5 |      |         | 2.5  | μs   |                                              |

| V <sub>lx</sub> <sup>3</sup> Minimum Input Skew <sup>4</sup> | t <sub>VIx</sub> skew               | 10   |         |     | 10   |         |      | ns   |                                              |

<sup>1</sup> Codirectional channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier.

<sup>&</sup>lt;sup>2</sup> The MSS signal is glitch filtered in both speed grades, whereas the other fast signals are not glitch filtered in the B grade. To guarantee that MSS reaches the output ahead of another fast signal, set up MSS prior to the competing signal by different times depending on speed grade.

$<sup>^{3}</sup>$   $V_{Ix} = V_{IA}$  or  $V_{II}$

<sup>&</sup>lt;sup>4</sup> An internal asynchronous clock, not available to users, samples the low speed signals. If edge sequence in codirectional channels is critical to the end application, the leading pulse must be at least 1 tvik skew time ahead of a later pulse to guarantee the correct order or simultaneous arrival at the output.

Table 7. For All Grades<sup>1, 2, 3</sup>

| Parameter                                                                             | Symbol                         | Min                    | Тур                    | Max                  | Unit  | Test Conditions/Comments                                                         |

|---------------------------------------------------------------------------------------|--------------------------------|------------------------|------------------------|----------------------|-------|----------------------------------------------------------------------------------|

| SUPPLY CURRENT                                                                        |                                |                        |                        |                      |       |                                                                                  |

| 1 MHz, A Grade and B Grade                                                            | I <sub>DD1</sub>               |                        | 5.3                    | 8.5                  | mA    | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                           |

|                                                                                       | $I_{DD2}$                      |                        | 4.9                    | 8                    | mA    | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                           |

| 17 MHz, B Grade                                                                       | I <sub>DD1</sub>               |                        | 16                     | 23                   | mA    | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                          |

|                                                                                       | I <sub>DD2</sub>               |                        | 10                     | 16                   | mA    | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                          |

| DC SPECIFICATIONS                                                                     |                                |                        |                        |                      |       |                                                                                  |

| MCLK, MSS, MO, SO, VIA, VIB                                                           |                                |                        |                        |                      |       |                                                                                  |

| Input Threshold                                                                       |                                |                        |                        |                      |       |                                                                                  |

| Logic High                                                                            | V <sub>IH</sub>                | $0.7 \times V_{DDx}$   |                        |                      | V     |                                                                                  |

| Logic Low                                                                             | VIL                            |                        |                        | $0.3 \times V_{DDx}$ | V     |                                                                                  |

| Input Hysteresis                                                                      | V <sub>IHYST</sub>             |                        | 500                    |                      | mV    |                                                                                  |

| Input Current per Channel SCLK, SSS, MI, SI, V <sub>OA</sub> , V <sub>OB</sub> , DCLK | l <sub>1</sub>                 | <b>-1</b>              | +0.01                  | +1                   | μΑ    | $0 \text{ V} \leq V_{\text{INPUT}} \leq V_{\text{DDx}}$                          |

| Output Voltages                                                                       |                                |                        |                        |                      |       |                                                                                  |

| Logic High                                                                            | V <sub>OH</sub>                | V <sub>DDx</sub> - 0.1 | $V_{DDx}$              |                      | V     | $I_{OUTPUT} = -20 \mu A, V_{INPUT} = V_{IH}$                                     |

|                                                                                       |                                | $V_{DDx} - 0.4$        | $V_{\text{DDx}} - 0.2$ |                      | V     | $I_{OUTPUT} = -4 \text{ mA}, V_{INPUT} = V_{IH}$                                 |

| Logic Low                                                                             | VoL                            |                        | 0.0                    | 0.1                  | V     | $I_{OUTPUT} = 20 \mu A, V_{INPUT} = V_{IL}$                                      |

|                                                                                       |                                |                        | 0.2                    | 0.4                  | V     | $I_{OUTPUT} = 4 \text{ mA}, V_{INPUT} = V_{IL}$                                  |

| V <sub>DD1</sub> , V <sub>DD2</sub> Undervoltage Lockout                              | UVLO                           |                        | 2.6                    |                      | V     |                                                                                  |

| Supply Current for All Low Speed Channels                                             |                                |                        |                        |                      |       |                                                                                  |

| Quiescent Side 1 Current                                                              | I <sub>DD1(Q)</sub>            |                        | 4.4                    |                      | mA    |                                                                                  |

| Quiescent Side 2 Current                                                              | I <sub>DD2(Q)</sub>            |                        | 4.6                    |                      | mA    |                                                                                  |

| AC SPECIFICATIONS                                                                     |                                |                        |                        |                      |       |                                                                                  |

| Output Rise/Fall Time                                                                 | t <sub>R</sub> /t <sub>F</sub> |                        | 2.5                    |                      | ns    | 10% to 90%                                                                       |

| Common-Mode Transient Immunity <sup>4</sup>                                           | CM                             | 25                     | 35                     |                      | kV/μs | $V_{INPUT} = V_{DDx}$ , $V_{CM} = 1000 \text{ V}$<br>Transient magnitude = 800 V |

$<sup>^{1}</sup>V_{DDx} = V_{DD1} \text{ or } V_{DD2}.$   $^{2}V_{INPUT} \text{ is the input voltage of any of the MCLK, } \overline{MSS}, MO, SO, V_{IA}, \text{ or } V_{IB} \text{ pins.}$   $^{3}I_{OUTPUT} \text{ is the output current of any of the SCLK, DCLK, } \overline{SSS}, MI, SI, V_{OA}, \text{ or } V_{OB} \text{ pins.}$   $^{4}|CM| \text{ is the maximum common-mode voltage slew rate that can be sustained while maintaining output voltages within the } V_{OH} \text{ and } V_{OL} \text{ limits. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.}$

## **ELECTRICAL CHARACTERISTICS—MIXED 3.3 V/5 V OPERATION**

All typical specifications are at  $T_A = 25^{\circ}\text{C}$ ,  $V_{DD1} = 3.3 \text{ V}$  and  $V_{DD2} = 5 \text{ V}$ . Minimum and maximum specifications apply over the entire recommended operation range:  $3.0 \text{ V} \le V_{DD1} \le 3.6 \text{ V}$ ,  $4.5 \text{ V} \le V_{DD2} \le 5.5 \text{ V}$ , and  $-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ , unless otherwise noted. Switching specifications are tested with  $C_L = 15 \text{ pF}$  and CMOS signal levels, unless otherwise noted.

**Table 8. Switching Specifications**

|                                                              | A                                   |      | A Grad | e   | B Grade |     |      |      |                                              |

|--------------------------------------------------------------|-------------------------------------|------|--------|-----|---------|-----|------|------|----------------------------------------------|

| Parameter                                                    | Symbol                              | Min  | Тур    | Max | Min     | Тур | Max  | Unit | Test Conditions/Comments                     |

| MCLK, MO, SO                                                 |                                     |      |        |     |         |     |      |      |                                              |

| SPI Clock Rate                                               | SPI <sub>MCLK</sub>                 |      |        | 9.2 |         |     | 15.6 | MHz  |                                              |

| Data Rate Fast (MO, SO)                                      | DR <sub>FAST</sub>                  |      |        | 40  |         |     | 40   | Mbps | Within PWD limit                             |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |      |        | 27  |         |     | 16   | ns   | 50% input to 50% output                      |

| Pulse Width                                                  | PW                                  | 12.5 |        |     | 12.5    |     |      | ns   | Within PWD limit                             |

| Pulse Width Distortion                                       | PWD                                 |      |        | 2   |         |     | 2    | ns   | tplh — tphl                                  |

| Codirectional Channel Matching <sup>1</sup>                  | t <sub>PSKCD</sub>                  |      |        | 3   |         |     | 3    | ns   |                                              |

| Jitter, High Speed                                           | J <sub>HS</sub>                     |      | 1      |     |         | 1   |      | ns   |                                              |

| MSS                                                          |                                     |      |        |     |         |     |      |      |                                              |

| Data Rate Fast                                               | DR <sub>FAST</sub>                  |      |        | 40  |         |     | 40   | Mbps | Within PWD limit                             |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |      |        | 26  |         |     | 26   | ns   | 50% input to 50% output                      |

| Pulse Width                                                  | PW                                  | 12.5 |        |     | 12.5    |     |      | ns   | Within PWD limit                             |

| Pulse Width Distortion                                       | PWD                                 |      |        | 3   |         |     | 3    | ns   | tplh - tphl                                  |

| Setup Time <sup>2</sup>                                      | MSS <sub>SETUP</sub>                | 1.5  |        |     | 10      |     |      | ns   |                                              |

| Jitter, High Speed                                           | J <sub>HS</sub>                     |      | 1      |     |         | 1   |      | ns   |                                              |

| DCLK                                                         |                                     |      |        |     |         |     |      |      |                                              |

| Data Rate                                                    |                                     |      |        | 40  |         |     | 40   | MHz  |                                              |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> |      |        | 60  |         |     | 40   | ns   | t <sub>PMCLK</sub> + t <sub>PSO</sub> + 3 ns |

| Pulse Width Distortion                                       | PWD                                 |      |        | 3   |         |     | 3    | ns   | t <sub>PLH</sub> — t <sub>PHL</sub>          |

| Pulse Width                                                  | PW                                  | 12   |        |     | 12      |     |      | ns   | Within PWD limit                             |

| Clock Delay Error                                            | DCLK <sub>ERR</sub>                 | 2    | 7      | 13  | 2       | 6.8 | 11   | ns   | tpdclk — (tpmclk + tpso)                     |

| Jitter                                                       | <b>J</b> <sub>DCLK</sub>            |      | 1      |     |         | 1   |      | ns   |                                              |

| V <sub>IA</sub> , V <sub>IB</sub>                            |                                     |      |        |     |         |     |      |      |                                              |

| Data Rate Slow                                               | DR <sub>SLOW</sub>                  |      |        | 250 |         |     | 250  | kbps | Within PWD limit                             |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> | 0.1  |        | 2.6 | 0.1     |     | 2.6  | μs   | 50% input to 50% output                      |

| Pulse Width                                                  | PW                                  | 4    |        |     | 4       |     |      | μs   | Within PWD limit                             |

| Jitter, Low Speed                                            | <b>J</b> LS                         |      |        | 2.5 |         |     | 2.5  | μs   |                                              |

| V <sub>lx</sub> <sup>3</sup> Minimum Input Skew <sup>4</sup> | t <sub>VIx</sub> skew               | 10   |        |     | 10      |     |      | ns   |                                              |

¹ Codirectional channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier.

<sup>&</sup>lt;sup>2</sup> The  $\overline{\text{MSS}}$  signal is glitch filtered in both speed grades, whereas the other fast signals are not glitch filtered in the B grade. To guarantee that  $\overline{\text{MSS}}$  reaches the output ahead of another fast signal, set up  $\overline{\text{MSS}}$  prior to the competing signal by different times depending on speed grade.

$<sup>^{3}</sup>$   $V_{Ix} = V_{IA}$  or  $V_{I}$

<sup>&</sup>lt;sup>4</sup> An internal asynchronous clock, not available to users, samples the low speed signals. If edge sequence in codirectional channels is critical to the end application, the leading pulse must be at least 1 tvik skew time ahead of a later pulse to guarantee the correct order or simultaneous arrival at the output.

Table 9. For All Grades<sup>1, 2, 3</sup>

| Parameter                                                                             | Symbol                         | Min                  | Тур                    | Max                  | Unit  | Test Conditions/Comments                                                                   |

|---------------------------------------------------------------------------------------|--------------------------------|----------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------|

| SUPPLY CURRENT                                                                        |                                |                      |                        |                      |       |                                                                                            |

| 1 MHz, A Grade and B Grade                                                            | I <sub>DD1</sub>               |                      | 3.5                    | 6                    | mA    | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz, $DR_{SLOW} = 0$ MHz                                     |

|                                                                                       | $I_{DD2}$                      |                      | 6.8                    | 11                   | mA    | $C_L = 0$ pF, $DR_{FAST} = 1$ MHz,<br>$DR_{SLOW} = 0$ MHz                                  |

| 17 MHz, B Grade                                                                       | I <sub>DD1</sub>               |                      | 12.5                   | 20                   | mA    | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                    |

|                                                                                       | I <sub>DD2</sub>               |                      | 14                     | 21                   | mA    | $C_L = 0$ pF, $DR_{FAST} = 17$ MHz, $DR_{SLOW} = 0$ MHz                                    |

| DC SPECIFICATIONS                                                                     |                                |                      |                        |                      |       |                                                                                            |

| MCLK, $\overline{\text{MSS}}$ , MO, SO, V <sub>IA</sub> , V <sub>IB</sub>             |                                |                      |                        |                      |       |                                                                                            |

| Input Threshold                                                                       |                                |                      |                        |                      |       |                                                                                            |

| Logic High                                                                            | V <sub>IH</sub>                | $0.7 \times V_{DDx}$ |                        |                      | V     |                                                                                            |

| Logic Low                                                                             | VIL                            |                      |                        | $0.3 \times V_{DDx}$ | V     |                                                                                            |

| Input Hysteresis                                                                      | V <sub>IHYST</sub>             |                      | 500                    |                      | mV    |                                                                                            |

| Input Current per Channel SCLK, SSS, MI, SI, V <sub>OA</sub> , V <sub>OB</sub> , DCLK | l <sub>1</sub>                 | -1                   | +0.01                  | +1                   | μΑ    | $0 \text{ V} \leq V_{\text{INPUT}} \leq V_{\text{DDx}}$                                    |

| Output Voltages                                                                       |                                |                      |                        |                      |       |                                                                                            |

| Logic High                                                                            | V <sub>OH</sub>                | $V_{DDx} - 0.1$      | $V_{\text{DDx}}$       |                      | V     | $I_{OUTPUT} = -20 \mu A, V_{INPUT} = V_{IH}$                                               |

| -                                                                                     |                                | $V_{DDx} - 0.4$      | $V_{\text{DDx}} - 0.2$ |                      | V     | $I_{OUTPUT} = -4 \text{ mA}, V_{INPUT} = V_{IH}$                                           |

| Logic Low                                                                             | VoL                            |                      | 0.0                    | 0.1                  | V     | $I_{OUTPUT} = 20 \mu A, V_{INPUT} = V_{IL}$                                                |

|                                                                                       |                                |                      | 0.2                    | 0.4                  | V     | $I_{OUTPUT} = 4 \text{ mA}, V_{INPUT} = V_{IL}$                                            |

| V <sub>DD1</sub> , V <sub>DD2</sub> Undervoltage Lockout                              | UVLO                           |                      | 2.6                    |                      | V     |                                                                                            |

| Supply Current for All Low Speed Channels                                             |                                |                      |                        |                      |       |                                                                                            |

| Quiescent Side 1 Current                                                              | I <sub>DD1(Q)</sub>            |                      | 2.9                    |                      | mA    |                                                                                            |

| Quiescent Side 2 Current                                                              | I <sub>DD2(Q)</sub>            |                      | 6.1                    |                      | mA    |                                                                                            |

| AC SPECIFICATIONS                                                                     |                                |                      |                        |                      |       |                                                                                            |

| Output Rise/Fall Time                                                                 | t <sub>R</sub> /t <sub>F</sub> |                      | 2.5                    |                      | ns    | 10% to 90%                                                                                 |

| Common-Mode Transient Immunity <sup>4</sup>                                           | CM                             | 25                   | 35                     |                      | kV/μs | $V_{INPUT} = V_{DDx}$ , $V_{CM} = 1000 \text{ V}$<br>Transient magnitude = $800 \text{ V}$ |

$<sup>^{1}</sup>V_{DDx} = V_{DD1} \text{ or } V_{DD2}.$   $^{2}V_{INPUT} \text{ is the input voltage of any of the MCLK, } \overline{MSS}, MO, SO, V_{IA}, \text{ or } V_{IB} \text{ pins.}$   $^{3}I_{OUTPUT} \text{ is the output current of any of the SCLK, DCLK, } \overline{SSS}, MI, SI, V_{OA}, \text{ or } V_{OB} \text{ pins.}$   $^{4}|CM| \text{ is the maximum common-mode voltage slew rate that can be sustained while maintaining output voltages within the } V_{OH} \text{ and } V_{OL} \text{ limits. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.}$

## **PACKAGE CHARACTERISTICS**

## Table 10.

| Parameter                                  | Symbol           | Min | Тур              | Max | Unit | Test Conditions/Comments                          |

|--------------------------------------------|------------------|-----|------------------|-----|------|---------------------------------------------------|

| Resistance (Input-to-Output) <sup>1</sup>  | R <sub>I-O</sub> |     | 10 <sup>12</sup> |     | Ω    |                                                   |

| Capacitance (Input-to-Output) <sup>1</sup> | C <sub>I-O</sub> |     | 1.0              |     | pF   | f = 1 MHz                                         |

| Input Capacitance <sup>2</sup>             | Cı               |     | 4.0              |     | pF   |                                                   |

| IC Junction-to-Case Thermal Resistance     | $\theta_{JC}$    |     | 68.5             |     | °C/W | 4-layer JEDEC test board, JESD 51-7 specification |

<sup>&</sup>lt;sup>1</sup> The device is considered a 2-terminal device: Pin 1 through Pin 10 are shorted together, and Pin 11 through Pin 20 are shorted together.

## **REGULATORY INFORMATION**

The ADuM3150 is approved by the organizations listed in Table 11. See Table 16 and the Insulation Lifetime section for recommended maximum working voltages for specific cross-isolation waveforms and insulation levels.

Table 11.

| UL                                                                  | CSA                                                                                                                                              | VDE                                                                             |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Recognized under 1577 Component<br>Recognition Program <sup>1</sup> | Approved under CSA Component Acceptance Notice 5A                                                                                                | Certified according to DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 <sup>2</sup> |

| 3750 V rms Single Protection                                        | Basic insulation per CSA 60950-1-07+A1+A2 and IEC 60950-1 2 <sup>nd</sup> Ed.+A1+A2, 510 V rms (721 V peak) maximum working voltage <sup>3</sup> | Reinforced insulation, 565 V peak                                               |

| File E214100                                                        | File 205078                                                                                                                                      | File 2471900-4880-0001                                                          |

¹ In accordance with UL 1577, the ADuM3150 is proof tested by applying an insulation test voltage ≥ 4500 V rms for 1 second (current leakage detection limit = 10 µA).

## **INSULATION AND SAFETY RELATED SPECIFICATIONS**

Table 12.

| Parameter                                        | Symbol | Value | Unit   | Conditions                                                                           |

|--------------------------------------------------|--------|-------|--------|--------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage              |        | 3750  | V rms  | 1-minute duration                                                                    |

| Minimum External Air Gap (Clearance)             | L(I01) | 5.1   | mm min | Measured from input terminals to output terminals, shortest distance through air     |

| Minimum External Tracking (Creepage)             | L(102) | 5.1   | mm min | Measured from input terminals to output terminals, shortest distance path along body |

| Minimum Internal Gap (Internal Clearance)        |        | 0.017 | mm min | Insulation distance through insulation                                               |

| Tracking Resistance (Comparative Tracking Index) | CTI    | >400  | V      | DIN IEC 112/VDE 0303 Part 1                                                          |

| Material Group                                   |        | II    |        | Material Group (DIN VDE 0110, 1/89, Table 1)                                         |

<sup>&</sup>lt;sup>2</sup> Input capacitance is from any input data pin to ground.

<sup>&</sup>lt;sup>2</sup> In accordance with DIN V VDE V 0884-10, the ADuM3150 is proof tested by applying an insulation test voltage ≥ 525 V peak for 1 second (partial discharge detection limit = 5 pC). The asterisk (\*) marked on the component designates DIN V VDE V 0884-10 approval.

<sup>&</sup>lt;sup>3</sup> See Table 16 for recommended maximum working voltages under various operating conditions.

## DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 INSULATION CHARACTERISTICS

This isolator is suitable for reinforced electrical isolation only within the safety limit data. Maintenance of the safety data is ensured by protective circuits. The asterisk (\*) marked on packages denotes DIN V VDE V 0884-10 approval.

Table 13.

| Description                                              | Test Conditions/Comments                                                                                         | Symbol            | Characteristic | Unit   |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------|

| Installation Classification per DIN VDE 0110             |                                                                                                                  |                   |                |        |

| For Rated Mains Voltage ≤ 150 V rms                      |                                                                                                                  |                   | I to IV        |        |

| For Rated Mains Voltage ≤ 300 V rms                      |                                                                                                                  |                   | l to III       |        |

| For Rated Mains Voltage ≤ 400 V rms                      |                                                                                                                  |                   | l to II        |        |

| Climatic Classification                                  |                                                                                                                  |                   | 40/105/21      |        |

| Pollution Degree per DIN VDE 0110, Table 1               |                                                                                                                  |                   | 2              |        |

| Maximum Working Insulation Voltage                       |                                                                                                                  | VIORM             | 565            | V peak |

| Input-to-Output Test Voltage, Method b1                  | $V_{IORM} \times 1.875 = V_{pd(m)}$ , 100% production test,<br>$t_{ini} = t_m = 1$ sec, partial discharge < 5 pC | $V_{pd(m)}$       | 1059           | V peak |

| Input-to-Output Test Voltage, Method a                   |                                                                                                                  |                   |                |        |

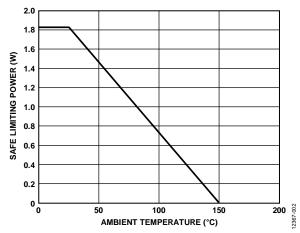

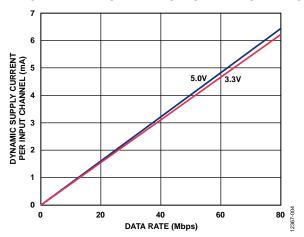

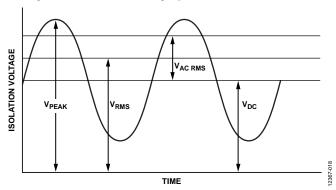

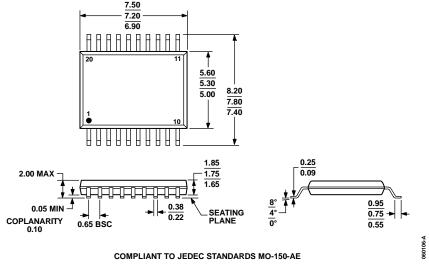

| After Environmental Tests Subgroup 1                     | $V_{IORM} \times 1.5 = V_{pd(m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5$ pC               | $V_{pd(m)}$       | 848            | V peak |