**TC850**

# 15-Bit, Fast Integrating CMOS A/D Converter

#### Features:

- 15-bit Resolution Plus Sign Bit

- Up to 40 Conversions per Second

- Integrating ADC Technique:

- Monotonic

- High Noise Immunity

- Auto-Zeroed Amplifiers Eliminate Offset Trimming

- Wide Dynamic Range: 96 dB

- Low Input Bias Current: 30 pA

- Low Input Noise: 30 μV<sub>P-P</sub>

- Sensitivity: 100 μV

- · Flexible Operational Control

- · Continuous or On Demand Conversions

- · Data Valid Output

- Bus Compatible, 3-State Data Outputs:

- 8-Bit Data Bus

- Simple μP Interface

- Two Chip Enables

- Read ADC Result Like Memory

- $\pm$  5V Power Supply Operation: 20 m $\Omega$

- 40-Pin Dual-in-Line or 44-Pin PLCC Packages

# **Applications:**

- · Precision Analog Signal Processor

- Precision Sensor Interface

- · High Accuracy DC Measurements

#### **Device Selection Table**

| Part Number | Package       | Temperature<br>Range |

|-------------|---------------|----------------------|

| TC850CPL    | 40-Pin PDIP   | 0°C to +70°C         |

| TC850IJL    | 40-Pin CERDIP | -25°C to +85°C       |

| TC850CLW    | 44-Pin PLCC   | 0°C to +70°C         |

| TC850ILW    | 44-Pin PLCC   | -25°C to +85°C       |

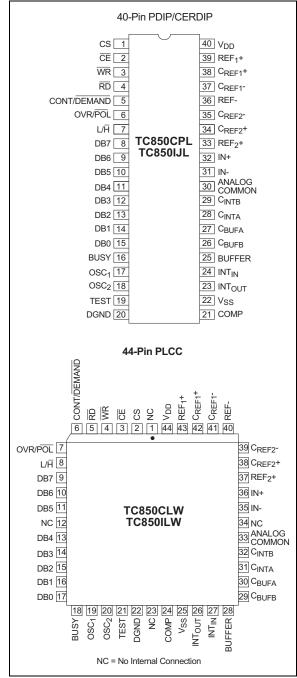

# Package Types

# **General Description:**

The TC850 is a monolithic CMOS A/D converter (ADC) with resolution of 15-bits plus sign. It combines a chopper-stabilized buffer and integrator with a unique multiple-slope integration technique that increases conversion speed. The result is 16 times improvement in speed over previous 15-bit, monolithic integrating ADCs (from 2.5 conversions per second up to 40 per second). Faster conversion speed is especially welcome in systems with human interface, such as digital scales.

The TC850 incorporates an ADC and a  $\mu P$ -compatible digital interface. Only a voltage reference and a few, noncritical, passive components are required to form a complete 15-bit plus sign ADC. CMOS processing provides the TC850 with high-impedance, differential inputs. Input bias current is typically only 30 pA, permitting direct interface to sensors. Input sensitivity of 100  $\mu V$  per Least Significant bit (LSb) eliminates the need

for precision external amplifiers. The internal amplifiers are auto-zeroed, ensuring a zero digital output, with 0V analog input. Zero adjustment potentiometers or calibrations are not required.

The TC850 outputs data on an 8-bit, 3-state bus. Digital inputs are CMOS compatible while outputs are TTL/CMOS compatible. Chip-enable and byte-select inputs, combined with an end-of-conversion output, ensures easy interfacing to a wide variety of microprocessors. Conversions can be performed continuously or on command. In Continuous mode, data is read as three consecutive bytes and manipulation of address lines is not required.

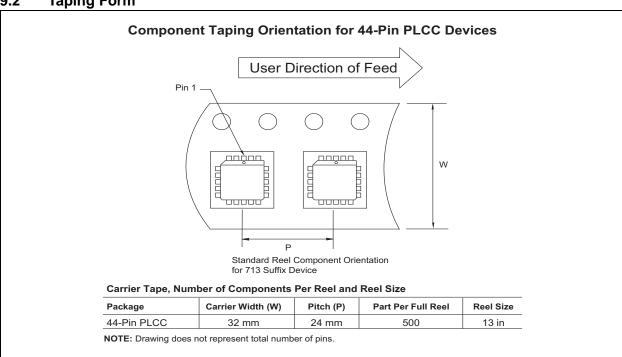

Operating from  $\pm 5\text{V}$  supplies, the TC850 dissipates only 20 m $\Omega$ . The TC850 is packaged in a 40-pin plastic or ceramic dual-in-line package (DIPs) and in a 44-pin plastic leaded chip carrier (PLCC), surface-mount package.

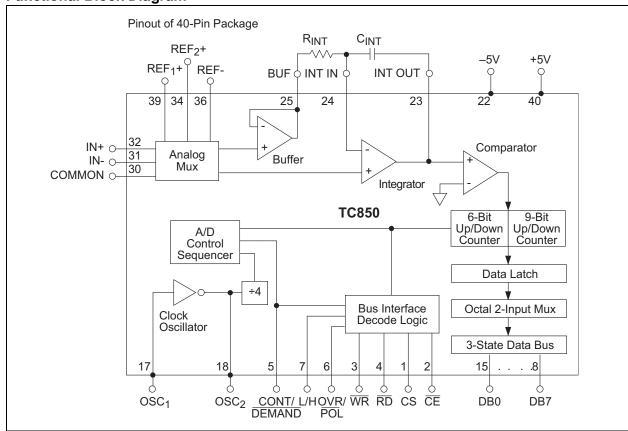

# **Functional Block Diagram**

# 1.0 ELECTRICAL SPECIFICATIONS

# **Absolute Maximum Ratings\***

| Positive Supply Voltage  Negative Supply Voltage  Analog Input Voltage (IN+ pr IN-)  Voltage Reference Input: | 9V                   |

|---------------------------------------------------------------------------------------------------------------|----------------------|

| (REF <sub>1</sub> +, REF <sub>1</sub> -, REF <sub>2</sub> +)                                                  | $V_{DD}$ to $V_{SS}$ |

| Logic Input VoltageV <sub>DD</sub> + 0.3\                                                                     | √ to GND – 0.3V      |

| Current Into Any Pin                                                                                          | 10 mA                |

| While Operating                                                                                               | 100 μΑ               |

| Ambient Operating Temperature Rang                                                                            | je                   |

| C Device                                                                                                      | 0°C to +70°C         |

| I Device                                                                                                      | 25°C to +85°C        |

| Package Power Dissipation (T <sub>A</sub> ≤ 70°C                                                              | C)                   |

| CerDIP                                                                                                        | 2.29Ω                |

| Plastic DIP                                                                                                   | 1.23Ω                |

| Plastic PLCC                                                                                                  | 1.23Ω                |

|                                                                                                               |                      |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

## TABLE 1-1: TC850 ELECTRICAL SPECIFICATIONS

| Symbol           | Parameter                                   | Min                   | Тур   | Max                   | Unit           | Test Conditions                                                                                                                |

|------------------|---------------------------------------------|-----------------------|-------|-----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|

| Cymbol           | Zero Scale Error                            |                       | ±0.25 | ±0.5                  | LSB            | V <sub>IN</sub> = 0V                                                                                                           |

|                  |                                             |                       |       |                       |                | 114                                                                                                                            |

|                  | End Point Linearity Error                   |                       | ±1    | ±2                    | LSB            | $-V_{FS} \le V_{IN} \le +V_{FS}$                                                                                               |

|                  | Differential Nonlinearity                   | _                     | ±0.1  | ±0.5                  | LSB            |                                                                                                                                |

| I <sub>IN</sub>  | Input Leakage Current                       | _                     | 30    | 75                    | pA             | V <sub>IN</sub> = 0V, T <sub>A</sub> = 25°C                                                                                    |

|                  |                                             | _                     | 1.1   | 3                     | nA             | -25° ≤ T <sub>A</sub> ≤ +85°C                                                                                                  |

| $V_{CMR}$        | Common Mode Voltage Range                   | V <sub>SS</sub> + 1.5 | _     | V <sub>SS</sub> - 1.5 | V              | Over Operating Temperature Range                                                                                               |

| CMRR             | Common Mode Rejection Ratio                 | _                     | 80    | -                     | dB             | $V_{IN} = 0V$ , $V_{CM} = \pm 1V$                                                                                              |

|                  | Full Scale Gain Temperature<br>Coefficient  |                       | 2     | 5                     | ppm/°C         | External Ref. Temperature<br>Coefficient = 0 ppm/ $^{\circ}$ C<br>0 $^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ +70 $^{\circ}$ C |

|                  | Zero Scale Error<br>Temperature Coefficient |                       | 0.3   | 2                     | μV/°C          | $V_{IN} = 0V$<br>$0^{\circ}C \le T_{A} \le +70^{\circ}C$                                                                       |

|                  | Full Scale Magnitude<br>Symmetry Error      |                       | 0.5   | 2                     | LSB            | $V_{IN} = \pm 3.275 V$                                                                                                         |

| e <sub>N</sub>   | Input Noise                                 | _                     | 30    | _                     | $\mu V_{P-P}$  | Not Exceeded 95% of Time                                                                                                       |

| l <sub>S</sub> + | Positive Supply Current                     | _                     | 2     | 3.5                   | mA             |                                                                                                                                |

| I <sub>S</sub> - | Negative Supply Current                     | _                     | 2     | 3.5                   | mA             |                                                                                                                                |

| V <sub>OH</sub>  | Output High Voltage                         | 3.5                   | 4.9   | _                     | V              | I <sub>O</sub> = 500 μA                                                                                                        |

| V <sub>OL</sub>  | Output Low Voltage                          | _                     | 0.15  | 0.4                   | V              | I <sub>O</sub> = 1.6 mA                                                                                                        |

| I <sub>OP</sub>  | Output Leakage Current                      | _                     | 0.1   | 1                     | μΑ             | Pins 8 -15, High-impedance State                                                                                               |

| V <sub>IH</sub>  | Input High Voltage                          | 3.5                   | 2.3   |                       | V              | Note 3                                                                                                                         |

| V <sub>IL</sub>  | Input Low Voltage                           | _                     | 2.1   | 1                     | V              | Note 3                                                                                                                         |

| I <sub>PU</sub>  | Input Pull-Up Current                       | _                     | 4     | _                     | μΑ             | Pins 2, 3, 4, 6, 7; V <sub>IN</sub> = 0V                                                                                       |

| I <sub>PD</sub>  | Input Pull-Down Current                     | _                     | 14    | _                     | μΑ             | Pins 1, 5; V <sub>IN</sub> = 5V                                                                                                |

| losc             | Oscillator Output Current                   | _                     | 140   | _                     | <u>.</u><br>μΑ | Pin 18, V <sub>OUT</sub> = 2.5V                                                                                                |

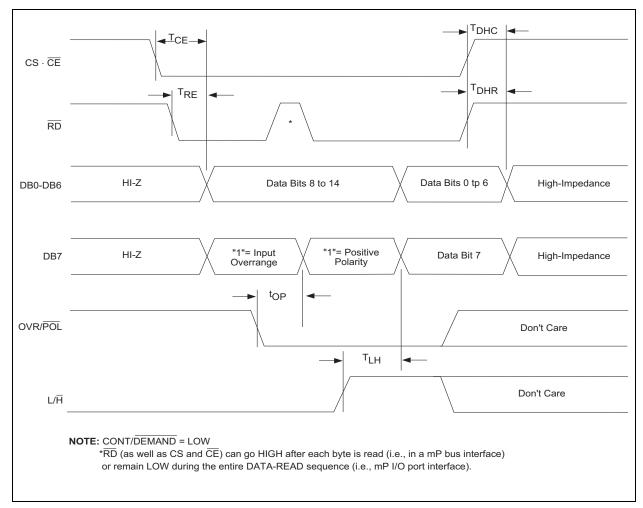

**Note 1:** Demand mode, CONT/ $\overline{DEMAND}$  = LOW. Figure 8-2 timing diagram.  $C_L$  = 100 pF.

- 2: Continuous mode, CONT/DEMAND = HIGH. Figure 8-4 timing diagram.

- 3: Digital inputs have CMOS logic levels and internal pull-up/pull-down resistors. For TTL compatibility, external pull-up resistors to V<sub>DD</sub> are recommended.

**TC850 ELECTRICAL SPECIFICATIONS (CONTINUED) TABLE 1-1:**

| <b>Electrical Characteristics:</b> $V_S = \pm 5V$ ; $F_{CLK} = 61.44$ kHz, $V_{FS} = 3.2768$ V, $T_A = 25$ °C, Figure 1-1, unless otherwise specified. |                           |     |     |     |      |                                                                                |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|-----|-----|------|--------------------------------------------------------------------------------|--|

| Symbol                                                                                                                                                 | Parameter                 | Min | Тур | Max | Unit | Test Conditions                                                                |  |

| C <sub>IN</sub>                                                                                                                                        | Input Capacitance         | _   | 1   |     | pF   | Pins 1 - 7, 17                                                                 |  |

| C <sub>OUT</sub>                                                                                                                                       | Output Capacitance        | _   | 15  | -   | pF   | Pins 8 -15, High-impedance State                                               |  |

| T <sub>CE</sub>                                                                                                                                        | Chip-Enable Access Time   | _   | 230 | 450 | nsec | CS or $\overline{CE}$ , $\overline{RD}$ = LOW (Note 1)                         |  |

| $T_RE$                                                                                                                                                 | Read-Enable Access Time   | _   | 190 | 450 | nsec | $CS = HIGH, \overline{CE} = LOW, $ (Note 1)                                    |  |

| T <sub>DHC</sub>                                                                                                                                       | Data Hold From CS or CE   | _   | 250 | 450 | nsec | RD = LOW, (Note 1)                                                             |  |

| $T_DHR$                                                                                                                                                | Data Hold From RD         | _   | 210 | 450 | nsec | $CS = HIGH, \overline{CE} = LOW, $ (Note 1)                                    |  |

| T <sub>OP</sub>                                                                                                                                        | OVR/POL Data Access Time  | _   | 140 | 300 | nsec | $\frac{CS}{RD}$ = HIGH, $\overline{CE}$ = LOW, $\overline{RD}$ = LOW, (Note 1) |  |

| T <sub>LH</sub>                                                                                                                                        | Low/High Byte Access Time | _   | 140 | 300 | nsec | $CS = HIGH, \overline{CE} = LOW,$<br>RD = LOW, (Note 1)                        |  |

|                                                                                                                                                        | Clock Setup Time          | 100 | _   | _   | nsec | Positive or Negative Pulse Width                                               |  |

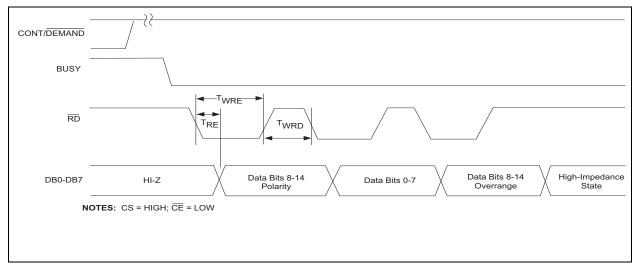

| T <sub>WRE</sub>                                                                                                                                       | RD Minimum Pulse Width    | 450 | 230 | _   | nsec | CS = HIGH, CE = LOW, (Note 2)                                                  |  |

| T <sub>WRD</sub>                                                                                                                                       | RD Minimum Delay Time     | 150 | 50  | _   | nsec | CS = HIGH, CE = LOW, (Note 2)                                                  |  |

| T <sub>WWD</sub>                                                                                                                                       | WR Minimum Pulse Width    | 75  | 25  | _   | nsec | CS = HIGH, CE = LOW, (Note 1)                                                  |  |

Note 1: Demand mode, CONT/DEMAND = LOW. Figure 8-2 timing diagram. C<sub>L</sub> = 100 pF.

2: Continuous mode, CONT/DEMAND = HIGH. Figure 8-4 timing diagram.

<sup>3:</sup> Digital inputs have CMOS logic levels and internal pull-up/pull-down resistors. For TTL compatibility, external pull-up resistors to  $V_{\mbox{\scriptsize DD}}$  are recommended.

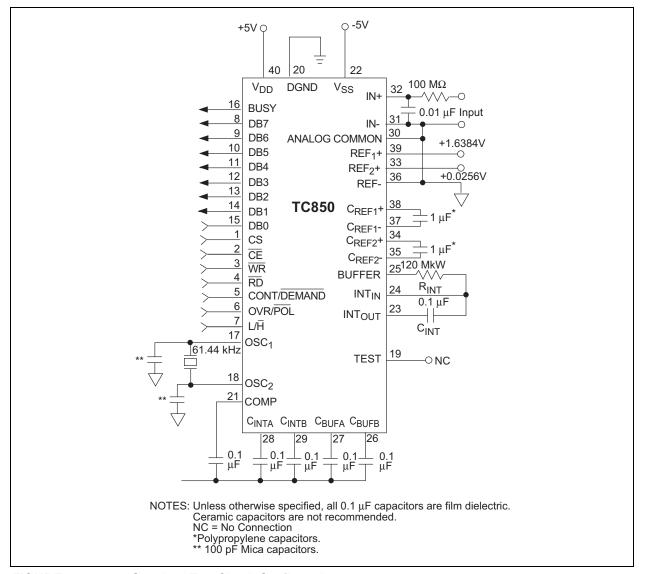

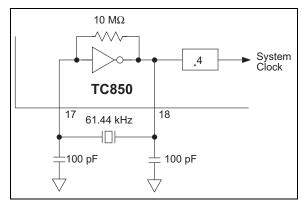

FIGURE 1-1: Standard Test Circuit Configuration

#### 2.0 **PIN DESCRIPTIONS**

The descriptions of the pins are listed in Table 2-1.

**TABLE 2-1: PIN FUNCTION TABLE**

| Pin Number<br>(40-Pin<br>PDIP/CERDIP) | Pin Number<br>(44-Pin PLCC) | Symbol             | Description                                                                                                                                                                                                     |

|---------------------------------------|-----------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                     | 2                           | CS                 | Chip Select, active HIGH. Logically ANDed, with $\overline{\text{CE}}$ to enable read and write inputs (Note 1).                                                                                                |

| 2                                     | 3                           | CE                 | Chip enable, active LOW (Note 2).                                                                                                                                                                               |

| 3                                     | 4                           | WR                 | Write input, active LOW. When chip is selected (CS = HIGH and $\overline{CE}$ = LOW) and in Demand mode (CONT/ $\overline{DEMAND}$ = LOW), a logic LOW on $\overline{WR}$ starts a conversion (Note 1).         |

| 4                                     | 5                           | RD                 | Read input, active LOW. When CS = HIGH and $\overline{CE}$ = LOW, a logic LOW on $\overline{RD}$ enables the 3-state data outputs (Note 2).                                                                     |

| 5                                     | 6                           | CONT/<br>DEMAND    | Conversion control input. When CONT/ $\overline{DEMAND}$ = LOW, conversions are initiated by the $\overline{WR}$ input. When CONT/ $\overline{DEMAND}$ = HIGH, conversions are performed continuously (Note 1). |

| 6                                     | 7                           | OVR/POL            | Overrange/polarity data-select input. When making conversions in the Demand mode (CONT/DEMAND = LOW), OVR/POL controls the data output on DB7 when the high-order byte is active (Note 2).                      |

| 7                                     | 8                           | L/H                | Low/high byte-select input. When CONT/DEMAND = LOW, this input controls whether low-byte or high-byte data is enabled on DB0 through DB7 (Note 2).                                                              |

| 8                                     | 9                           | DB7                | Most Significant data bit output. When reading the A/D conversion result, the polarity, overrange and DB7 data are output on this pin.                                                                          |

| 9-15                                  | 10-17                       | DB6-DB0            | Data outputs DB6-DB0. 3-state, bus compatible.                                                                                                                                                                  |

| 16                                    | 18                          | BUSY               | A/D conversion status output. BUSY goes to a logic HIGH at the beginning of the de-integrate phase, then goes LOW when conversion is complete. The falling edge of BUSY can be used to generate a µP interrupt. |

| 17                                    | 19                          | OSC <sub>1</sub>   | Crystal oscillator connection or external oscillator input.                                                                                                                                                     |

| 18                                    | 20                          | OSC <sub>2</sub>   | Crystal oscillator connection.                                                                                                                                                                                  |

| 19                                    | 21                          | TEST               | For factory testing purposes only. Do not make external connection to this pin.                                                                                                                                 |

| 20                                    | 22                          | DGND               | Digital ground connection.                                                                                                                                                                                      |

| 21                                    | 24                          | COMP               | Connection for comparator auto-zero capacitor. Bypass to $V_{\mbox{SS}}$ with 0.1 $\mu\mbox{F}$ .                                                                                                               |

| 22                                    | 25                          | V <sub>SS</sub>    | Negative power supply connection, typically -5V.                                                                                                                                                                |

| 23                                    | 26                          | INT <sub>OUT</sub> | Output of the integrator amplifier. Connect to C <sub>INT</sub> .                                                                                                                                               |

| 24                                    | 27                          | INT <sub>IN</sub>  | Input to the integrator amplifier. Connect to summing node of $R_{\text{INT}}$ and $C_{\text{INT}}$ .                                                                                                           |

| 25                                    | 28                          | BUFFER             | Output of the input buffer. Connect to R <sub>INT</sub> .                                                                                                                                                       |

| 26                                    | 29                          | C <sub>BUFB</sub>  | Connection for buffer auto-zero capacitor. Bypass to V <sub>SS</sub> with 0.1 μF.                                                                                                                               |

| 27                                    | 30                          | C <sub>BUFA</sub>  | Connection to buffer auto-zero capacitor. Bypass to $V_{\mbox{SS}}$ with 0.1 $\mu\mbox{F}$ .                                                                                                                    |

| 28                                    | 31                          | C <sub>INTA</sub>  | Connection for integrator auto-zero capacitor. Bypass to $V_{\mbox{SS}}$ with 0.1 $\mu\mbox{F}$ .                                                                                                               |

| 29                                    | 32                          | C <sub>INTB</sub>  | Connection for integrator auto-zero capacitor. Bypass to $V_{\mbox{SS}}$ with 0.1 $\mu\mbox{F}$ .                                                                                                               |

| 30                                    | 33                          | ANALOG<br>COMMON   | Analog common.                                                                                                                                                                                                  |

| 31                                    | 35                          | IN-                | Negative differential analog input.                                                                                                                                                                             |

| 32                                    | 36                          | IN+                | Positive differential analog input.                                                                                                                                                                             |

**Note 1:** This pin incorporates a pull-down resistor to DGND.

2: This pin incorporates a pull-up resistor to V<sub>DD</sub>.

3: Pins 1, 23 and 34 (44-PLCC) package are NC "No Internal connection".

PIN FUNCTION TABLE (CONTINUED) **TABLE 2-1:**

| Pin Number<br>(40-Pin<br>PDIP/CERDIP) | Pin Number<br>(44-Pin PLCC) | Symbol              | Description                                                                                          |

|---------------------------------------|-----------------------------|---------------------|------------------------------------------------------------------------------------------------------|

| 33                                    | 37                          | REF <sub>2</sub> +  | Positive input for reference voltage V <sub>REF2</sub> . (V <sub>REF2</sub> = V <sub>REF1</sub> /64) |

| 34                                    | 38                          | C <sub>REF2</sub> + | Positive connection for V <sub>REF2</sub> reference capacitor.                                       |

| 35                                    | 39                          | C <sub>REF2</sub> - | Negative connection for V <sub>REF2</sub> reference capacitor.                                       |

| 36                                    | 40                          | REF-                | Negative input for reference voltages.                                                               |

| 37                                    | 41                          | C <sub>REF1</sub> - | Negative connection for V <sub>REF1</sub> reference capacitor.                                       |

| 38                                    | 42                          | C <sub>REF1</sub> + | Positive connection for V <sub>REF1</sub> reference capacitor.                                       |

| 39                                    | 43                          | REF <sub>1</sub> +  | Positive input for V <sub>REF1</sub> .                                                               |

| 40                                    | 44                          | $V_{DD}$            | Positive power supply connection, typically +5V.                                                     |

Note 1: This pin incorporates a pull-down resistor to DGND.

2: This pin incorporates a pull-up resistor to V<sub>DD</sub>.

3: Pins 1, 23 and 34 (44-PLCC) package are NC "No Internal connection".

#### 3.0 DETAILED DESCRIPTION

The TC850 is a multiple-slope, integrating A/D converter (ADC). The multiple-slope conversion process, combined with chopper-stabilized amplifiers, results in a significant increase in ADC speed, while maintaining very high resolution and accuracy.

# 3.1 Dual-Slope Conversion Principles

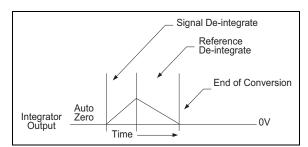

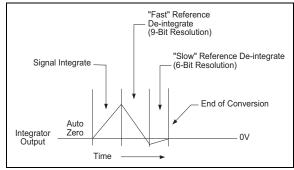

The conventional dual-slope converter measurement cycle (shown in Figure 3-1) has two distinct phases:

- 1. Input signal integration

- 2. Reference voltage integration (de-integration).

FIGURE 3-1: Dual-Slope ADC Cycle

The input signal being converted is integrated for a fixed time period, measured by counting clock pulses. An opposite polarity constant reference voltage is then de-integrated until the integrator output voltage returns to zero. The reference integration time is directly proportional to the input signal.

In a simple dual-slope converter, complete conversion requires the integrator output to "ramp-up" and "ramp-down." Most dual-slope converters add a third phase, auto-zero. During auto-zero, offset voltages of the input buffer, integrator and comparator are nulled, thereby eliminating the need for zero offset adjustments.

Dual-slope converter accuracy is unrelated to the integrating resistor and capacitor values, as long as they are stable during a measurement cycle. By converting the unknown analog input voltage into an easily measured function of time, the dual-slope converter reduces the need for expensive, precision passive components.

Noise immunity is an inherent benefit of the integrating conversion method. Noise spikes are integrated, or averaged, to zero during the integration period. Integrating ADCs are immune to the large conversion errors that plague successive approximation converters in high-noise environments.

A simple mathematical equation relates the input signal, reference voltage and integration time:

#### **EQUATION 3-1:**

$$\frac{1}{R_{INT}C_{INT}}\!\!\int_{0}^{T_{INT}}\!\!V_{IN}\!(T)DT = \frac{V_{REF}\,T_{DEINT}}{R_{INT}C_{INT}}$$

where:

V<sub>REF</sub> = Reference voltage

T<sub>INT</sub> = Signal integration time (fixed)

$T_{DEINT}$  = Reference voltage integration time

(variable).

# 3.2 Multiple-Slope Conversion Principles

One limitation of the dual-slope measurement technique is conversion speed. In a typical dual-slope method, the auto-zero and integrate times are each one-half of the de-integrate time. For a 15-bit conversion,  $2^{14} + 2^{14} + 2^{15}$  (65,536) clock pulses are required for auto-zero, integrate and de-integrate phases, respectively. The large number of clock cycles effectively limits the conversion rate to about 2.5 conversions per second, when a typical analog CMOS fabrication process is used.

The TC850 uses a multiple-slope conversion technique to increase conversion speed (Figure 3-2). This technique makes use of a two-slope de-integration phase and permits 15-bit resolution up to 40 conversions per second.

During the TC850's de-integration phase, the integration capacitor is rapidly discharged to yield a resolution of 9 bits. At this point, some charge will remain on the capacitor. This remaining charge is then slowly de-integrated, producing an additional 6 bits of resolution. The result is 15 bits of resolution achieved with only  $2^9 + 2^6$  (512 + 64, or 576) clock pulses for de-integration. A complete conversion cycle occupies only 1280 clock pulses.

In order to generate "fast-slow" de-integration phases, two voltage references are required. The primary reference ( $V_{REF1}$ ) is set to one-half of the full scale voltage (typically  $V_{REF1}=1.6384V$ , and  $V_{FS}=3.2768V$ ). The secondary voltage reference ( $V_{REF2}$ ) is set to  $V_{REF1}/64$  (typically 25.6 mV). To maintain 15-bit linearity, a tolerance of 0.5% for  $V_{REF2}$  is recommended.

FIGURE 3-2: Integration Cycle

"Fast Slow" Reference De-

# 4.0 ANALOG SECTION DESCRIPTION

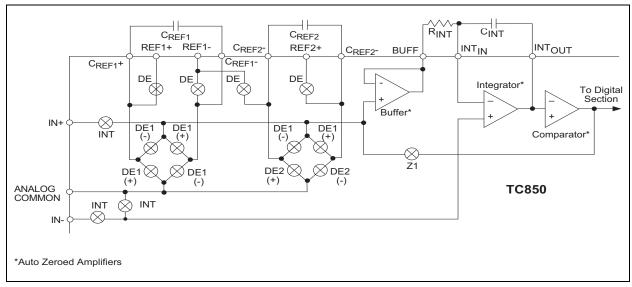

The TC850 analog section consists of an input buffer amplifier, integrator amplifier, comparator and analog switches. A simplified block diagram is shown in Figure 4-1.

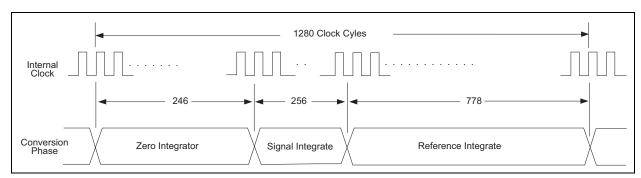

# 4.1 Conversion Timing

Each conversion consists of three phases:

- Zero Integrator

- 2. Signal Integrate

- 3. Reference Integrate (or De-integrate)

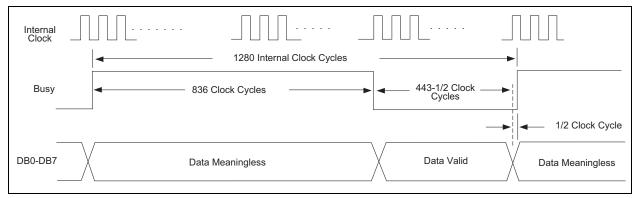

Each conversion cycle requires 1280 internal clock cycles (Figure 4-2).

FIGURE 4-1: Analog Section Simplified Schematic

FIGURE 4-2: Conversion Timing

# 4.2 Zero Integrator Phase

During the zero integrator phase, the differential input signal is disconnected from the circuit by opening internal analog gates. The internal nodes are shorted to analog common (ground) to establish a zero input condition. At the same time, a feedback loop is closed around the input buffer, integrator and comparator. The feedback loop ensures the integrator output is near 0V before the signal integrate phase begins.

During this phase, a chopper-stabilization technique is used to cancel offset errors in the input buffer, integrator and comparator. Error voltages are stored on the  $C_{BUFF}$ ,  $C_{INT}$  and COMP capacitors. The zero integrate phase requires 246 clock cycles.

# 4.3 Signal Integrate Phase

The zero integrator loop is opened and the internal differential inputs are connected to IN+ and IN-. The differential input signal is integrated for a fixed time period. The TC850 signal integrate period is 256 clock periods, or counts. The crystal oscillator frequency is ÷4 before clocking the internal counters.

The integration time period is:

#### **EQUATION 4-1:**

$$T_{INT} = \frac{4 \times 256}{F_{OSC}}$$

### 4.4 Reference Integrate Phase

During reference integrate phase, the charge stored on the integrator capacitor is discharged. The time required to discharge the capacitor is proportional to the analog input voltage.

The reference integrate phase is divided into three subphases:

- 1. Fast

- 2. Slow

- 3. Overrange de-integrate

During fast de-integrate,  $V_{IN}$ - is internally connected to analog common and  $V_{IN}$ + is connected across the previously-charged reference capacitor ( $C_{REF1}$ ). The integrator capacitor is rapidly discharged for a maximum of 512 internal clock pulses, yielding 9 bits of resolution.

During the slow de-integrate phase, the internal  $V_{\rm IN}$ + node is now connected to the  $C_{\rm REF2}$  capacitor and the residual charge on the integrator capacitor is further discharged a maximum of 64 clock pulses. At this point, the analog input voltage has been converted with 15 bits of resolution.

If the analog input is greater than full scale, the TC850 performs up to three overrange de-integrate subphases. Each subphase occupies a maximum of 64 clock pulses. The overrange feature permits analog inputs up to 192 LSBs greater than full scale to be correctly converted. This feature permits the user to digitally null up to 192 counts of input offset, while retaining full 15-bit resolution.

In addition to 512 counts of fast, 64 counts of slow and 192 counts of overrange de-integrate, the reference integrate phase uses 10 clock pulses to permit internal nodes to settle. Therefore, the reference integrate cycle occupies 778 clock pulses.

# 5.0 PIN DESCRIPTION (ANALOG)

## 5.1 Differential Inputs (IN+ and IN-)

The analog signal to be measured is applied at the IN+ and IN– inputs. The differential input voltage must be within the Common mode range of the converter. The input Common mode range extends from  $V_{DD}$  - 1.5V to  $V_{SS}$  +1.5V. Within this Common mode voltage range, an 80 dB CMRR is typical.

The integrator output also follows the Common mode voltage. The integrator output must not be allowed to saturate. A worst-case condition exists, for example, when a large, positive Common mode voltage, with a near full scale negative differential input voltage, is applied. The negative input signal drives the integrator positive when most of its available swing has been used up by the positive Common mode voltage. For applications where maximum Common mode range is critical, integrator swing can be reduced. The integrator output can swing within 0.4V of either supply without loss of linearity.

# 5.2 Differential Reference (V<sub>RFF</sub>)

The TC850 requires two reference voltage sources in order to generate the "fast-slow" de-integrate phases. The main voltage reference ( $V_{REF1}$ ) is applied between the REF<sub>1</sub>+ and REF- pins. The secondary reference ( $V_{REF2}$ ) is applied between the REF<sub>2</sub>+ and REF- pins.

The reference voltage inputs are fully differential and the reference voltage can be generated anywhere within the power supply voltage of the converter. However, to minimize rollover error, especially at high conversion rates, keep the reference Common mode voltage (i.e., REF-) near or at the analog common potential. All voltage reference inputs are high-impedance. Average reference input current is typically only 30 pA.

# 5.3 Analog Common (ANALOG COMMON)

Analog common is used as the IN- return during the zero integrator and de-integrate phases of each conversion. If IN- is at a different potential than analog common, a Common mode voltage exists in the system. This signal is rejected by the 80dB CMRR of the converter. However, in most applications, IN- will be set at a fixed, known voltage (power supply common, for instance). In this case, analog common should be tied to the same point so that the Common mode voltage is eliminated.

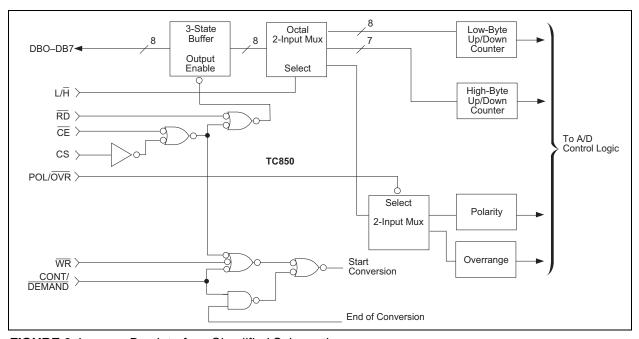

# 6.0 DIGITAL SECTION DESCRIPTION

The TC850 digital section consists of two sets of conversion counters, control and sequencing logic, clock oscillator and divider, data latches and an 8-bit, 3-state interface bus. A simplified schematic of the bus interface logic is shown in Figure 6-1

#### 6.1 Clock Oscillator

The TC850 includes a crystal oscillator on-chip. All that is required is to connect a crystal across OSC<sub>1</sub> and OSC<sub>2</sub> pins and to add two inexpensive capacitors

(Figure 1-1). The oscillator output is ÷ 4 prior to clocking the A/D internal counters. For example, a 100 kHz crystal produces a system clock frequency of 25 kHz. Since each conversion requires 1280 clock periods, in this case the conversion rate will be 25,000/1280, or 19.5 conversions per second.

In most applications, however, an external clock is divided down from the microprocessor clock. In this case, the  ${\sf OSC_1}$  pin is used as the external oscillator input and  ${\sf OSC_2}$  is left unconnected. The external clock driver should swing from digital ground to  ${\sf V_{DD}}.$  The  $\div$  4 function is active for both external clock and crystal oscillator operations.

FIGURE 6-1: Bus Interface Simplified Schematic

# 6.2 Digital Operating Modes

Two modes of operation are available with the TC850, continuous conversions and on-demand. The Operating mode is controlled by the CONT/DEMAND input. The bus interface method is different for Continuous and Demand modes of operation.

#### 6.2.1 DEMAND MODE OPERATION

When CONT/DEMAND is low, the TC850 performs one conversion each time the chip is selected and the WR input is pulsed low. Data is valid on the falling edge of the BUSY output and can be accessed using the interface truth table (Table 6-1).

## 6.2.2 CONTINUOUS MODE OPERATION

When CONT/DEMAND is high, the TC850 continuously performs conversions. Data will be valid on the falling edge of the BUSY output and remains valid for 443-1/2 clock cycles.

The low/high (L/H) byte-select and overrange/polarity (OVR/POL) inputs are disabled during Continuous mode operation. Data must be read in three consecutive bytes, as shown in Table 6-1.

Note:

In Continuous mode, the conversion result must be read within 443-1/2 clock cycles of the BUSY output falling edge. After this time (i.e.,1/2 clock cycle before BUSY goes high) the internal counters are reset and the data is lost.

TABLE 6-1: BUS INTERFACE TRUTH TABLE

| CE • CS<br>Pins 1 and 2 | RD<br>Pin 4 | CONT/DEMAND<br>Pin 5 | L/H<br>Pin 7 | OVR/POL<br>Pin 6 | DB7<br>Pin 8                      | DB6-DB0<br>Pin 9-Pin 15 (Note 1) |

|-------------------------|-------------|----------------------|--------------|------------------|-----------------------------------|----------------------------------|

| 0                       | 0           | 0                    | 0            | 0                | "1" = Input Positive              | Data Bits 14 - 8                 |

| 0                       | 0           | 0                    | 0            | 1                | "1" = Input Overrange<br>(Note 2) | Data Bits 14 - 8                 |

| 0                       | 0           | 0                    | 1            | Х                | Data Bit 7                        | Data Bits 6 - 0                  |

| 0                       | 0           | 1                    | Х            | Х                | Note 3                            |                                  |

| 0                       | 1           | Х                    | Х            | Х                | High-Impedance State              |                                  |

| 1                       | Х           | Х                    | Х            | Х                | High-Impedance State              |                                  |

Note 1: Pin numbers refer to 40-pin PDIP.

2: Extended overrange operation: Although rated at 15 bits (±32,767 counts) of resolution, the TC850 provides an additional 191 counts above full scale. For example, with a full-scale input of 3.2768V, the maximum analog input voltage which will be properly converted is 3.2958V. The extended resolution is signified by the overrange bit being high and the low-order byte contents being between 0 and 190. For example, with a full-scale voltage of 3.2768V:

| <u>V<sub>IN</sub></u> | Overrange Bit | Low Byte          | <u>Data Bits 14–8</u> |

|-----------------------|---------------|-------------------|-----------------------|

| 3.2767V               | Low           | 255 <sub>10</sub> | 127 <sub>10</sub>     |

| 3.2768V               | High          | 000 <sub>10</sub> | 0 <sub>10</sub>       |

| 3.2769V               | High          | 001 <sub>10</sub> | 0 <sub>10</sub>       |

| 3.2867V               | High          | 09910             | 010                   |

- 3: Continuous mode data transfer:

- a. In Continuous mode, data MUST be read in three sequential bytes after the BUSY output goes low:

- (1) The first byte read will be the high-order byte, with DB7 = polarity.

- (2) The second byte read will contain the low-order byte.

- (3) The third byte read will again be the high-order byte, but with DB7 = overrange.

- b. All three data bytes must be read within 443-1/2 clock cycles after the falling edge of BUSY.

- c. The  $\overline{c}$  input must go high after each byte is read, so that the internal byte counter will be incremented. However, the CS and  $\overline{CE}$ inputs can remain enabled through the entire data transfer sequence.

# 6.3 Pin Description (Digital)

# 6.3.1 CHIP SELECT AND CHIP ENABLE (CS AND CE)

The CS and CE inputs permit easy interfacing to a variety of digital bus systems.  $\overline{\text{CE}}$  is active LOW while CS is active HIGH. These inputs are logically ANDed internally and are used to enable the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  inputs.

# 6.3.2 WRITE ENABLE INPUT (WR)

The write input is used to initiate a conversion when the TC850 is in Demand mode. CS and  $\overline{\text{CE}}$  must be active for the  $\overline{\text{WR}}$  input to be recognized. The status of the data bus is meaningless during the  $\overline{\text{WR}}$  pulse, because no data is actually written into the TC850.

# 6.3.3 READ ENABLE INPUT (RD)

The read input, combined with CS and  $\overline{\text{CE}}$ , enable the 3-state data bus outputs. Also, in Continuous mode, the rising edge of the  $\overline{\text{RD}}$  input activates an internal byte counter to sequentially read the three data bytes.

# 6.3.4 LOW/HIGH BYTE SELECT ( $L/\overline{H}$ )

The  $L/\overline{H}$  input determines whether the low (Least Significant) Byte or high (Most Significant) Byte of data is placed on the 3-state data bus. This input is meaningful only when the TC850 is in the Demand mode. In the Continuous mode, data must be read in three predetermined bytes, so the  $L/\overline{H}$  input is ignored.

# 6.3.5 OVERRANGE/POLARITY BIT SELECT (OVR/POL)

The TC850 provides 15 bits of resolution, plus polarity and overrange bits. Thus, 17 bits of information must be transferred on an 8-bit data bus. To accomplish this, the overrange and polarity bits are multiplexed onto data bit DB7 of the Most Significant Byte. When OVR/ $\overline{POL}$  is HIGH, DB7 of the high byte contains the overrange status (HIGH = analog input overrange, LOW = input within full scale). When OVR/ $\overline{POL}$  is LOW, DB7 is HIGH for positive analog input polarity and LOW for negative polarity. The  $\overline{OVR/POL}$  input is meaningful only when CS,  $\overline{CE}$  and  $\overline{RD}$  are active, and  $\overline{L/H}$  is  $\overline{LOW}$  (i.e., the Most Significant Byte is selected).  $\overline{OVR/POL}$  is ignored when the TC850 is in Continuous mode.

# 6.3.6 CONTINUOUS/DEMAND MODE INPUT (CONT/DEMAND)

This input controls the TC850 Operating mode. When CONT/DEMAND is HIGH, the TC850 performs conversions continuously. In Continuous mode, data must be read in the prescribed sequence shown in Table 6-1. Also, all three data bytes must be read within 443-1/2 internal clock cycles after the BUSY output goes low. After 443-1/2 clock cycles data will be lost.

When CONT/DEMAND is LOW, the TC850 begins a conversion each time CS and  $\overline{\text{CE}}$  are active and  $\overline{\text{WR}}$  is being pulsed LOW. The conversion is complete and data can be read after the falling edge of the BUSY output. In Demand mode, data can be read in any sequence and remains valid until  $\overline{\text{WR}}$  is again pulsed LOW.

## 6.3.7 BUSY OUTPUT (BUSY)

The BUSY output is used to convey an end-of-conversion to external logic. BUSY goes HIGH at the beginning of the de-integrate phase and goes LOW at the end of the conversion cycle. Data is valid on the falling edge of BUSY. The output-high period is fixed at 836 clock periods, regardless of the analog input value. BUSY is active during Continuous and Demand mode operation.

This output can also be used to generate an end-of-conversion interrupt in  $\mu P$ -based systems. Noninterrupt-driven systems can poll BUSY to determine when data is valid.

# 7.0 ANALOG SECTION TYPICAL APPLICATIONS

# 7.1 Component Selection

#### 7.1.1 REFERENCE VOLTAGE

The typical value for reference voltage  $V_{REF1}$  is 1.6384V. This value yields a full scale voltage of 3.2768V and resolution of 100  $\mu$ V per step. The  $V_{REF2}$  value is derived by dividing  $V_{REF1}$  by 64. Thus, typical  $V_{REF2}$  value is 1.6384V/64, or 25.6 mV. The  $V_{REF2}$  value should be adjusted within ±1% to maintain 15-bit accuracy for the total conversion process;

# EQUATION 7-1: :

$$V_{REF} = \frac{V_{REF1} \pm 1\%}{64}$$

The reference voltage is not limited to exactly 1.6384V, however, because the TC850 performs a ratiometric conversion. Therefore, the conversion result will be:

#### **EQUATION 7-2:**

Digital Counts =

$$\frac{V_{IN}}{V_{REF1}}$$

16384

The full scale voltage can range from 3.2V to 3.5V. Full scale voltages of less than 3.2V will result in increased noise in the Least Significant bits, while a full scale above 3.5V will exceed the input common-mode range.

#### 7.1.2 INTEGRATION RESISTOR

The TC850 buffer supplies 25  $\mu$ A of integrator charging current with minimal linearity error.  $R_{INT}$  is easily calculated:

# **EQUATION 7-3:**

$$R_{INT} = \frac{V_{FULLSCALE}}{25 \,\mu A}$$

For a full scale voltage of 3.2768V, values of R  $_{INT}$  between 120  $k\Omega$  and 150  $k\Omega$  are acceptable.

#### 7.1.3 INTEGRATION CAPACITOR

The integration capacitor should be selected to produce an integrator swing of  $\approx$  4V at full scale. The capacitor value is easily calculated:

## **EQUATION 7-4:**

$$C = \frac{V_{FS}}{R_{INT}} \bullet \frac{4 \bullet 256}{4V F_{CLOCK}}$$

where:

$F_{CLOCK}$  is the crystal or external oscillator frequency and  $V_{FS}$  is the maximum input voltage.

The integration capacitor should be selected for low dielectric absorption to prevent rollover errors. A polypropylene, polyester or polycarbonate dielectric capacitor is recommended.

#### 7.1.4 REFERENCE CAPACITORS

The reference capacitors require a low-leakage dielectric, such as polypropylene, polyester or polycarbonate. A value of 1  $\mu\text{F}$  is recommended for operation over the temperature range. If high-temperature operation is not required, the  $C_{REF}$  values can be reduced.

#### 7.1.5 AUTO-ZERO CAPACITORS

Five capacitors are required to auto-zero the input buffer, integrator amplifier and comparator. Recommended capacitors are 0.1  $\mu F$  film dielectric (such as polyester or polypropylene). Ceramic capacitors are not recommended.

# 8.0 DIGITAL SECTION TYPICAL APPLICATIONS

# 8.1 Oscillator

The TC850 may operate with a crystal oscillator. The crystal selected should be designed for a Pierce oscillator, such as an AT-cut quartz crystal. The crystal oscillator schematic is shown in Figure 8-1.

Since low-frequency crystals are very large and ceramic resonators are too lossy, the TC850 clock should be derived from an external source, such as a microprocessor clock. The clock should be input on the  ${\sf OSC}_1$  pin and no connection should be made to the  ${\sf OSC}_2$  pin. The external clock should swing between DGND and  ${\sf V}_{\sf DD}$ .

Since oscillator frequency is  $\div$  4 internally and each conversion requires 1280 internal clock cycles, the conversion time will be:

#### **EQUATION 8-1:**

Conversion Time =

$$\frac{4 \times 1280}{F_{CLOCK}}$$

An important advantage of the integrating ADC is the ability to reject periodic noise. This feature is most often used to reject line frequency (50 Hz or 60 Hz) noise. Noise rejection is accomplished by selecting the integration period equal to one or more line frequency cycles. The desired clock frequency is selected as follows:

#### **EQUATION 8-2:**

$F_{CLOCK} = F_{NOISE} \times 4 \times 256$

where:

$F_{\mbox{NOISE}}$  is the noise frequency to be rejected,

4 represents the clock divider,

256 is the number of integrate cycles.

For example, 60 Hz noise will be rejected with a clock frequency of 61.44 kHz, giving a conversion rate of 12 conversions/sec. Integer submultiples of 61.44 kHz (such as 30.72 kHz, etc.) will also reject 60 Hz noise. For 50 Hz noise rejection, a 51.2 kHz frequency is recommended.

If noise rejection is not important, other clock frequencies can be used. The TC850 will typically operate at conversion rates ranging from 3 to 40 conversions/sec, corresponding to oscillator frequencies from 15.36 kHz to 204.8 kHz.

FIGURE 8-1: Crystal Oscillator Schematic

# 8.2 Data Bus Interfacing

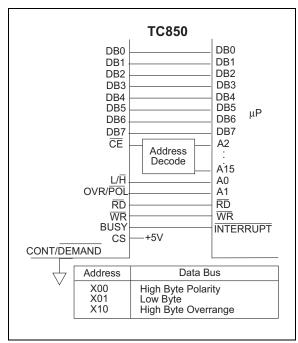

The TC850 provides an easy and flexible digital interface. A 3-state data bus and six control inputs permit the TC850 to be treated as a memory device, in most applications. The conversion result can be accessed over an 8-bit bus or via a  $\mu P$  I/O port.

A typical  $\mu P$  bus interface for the TC850 is shown in Figure 8-2. In this example, the TC850 operates in the Demand mode and conversion begins when a write operation is performed to any decoded address space. The BUSY output interrupts the  $\mu P$  at the end-of-conversion.

The A/D conversion result is read as three memory bytes. The two LSBs of the address bus select high/low byte and overrange/polarity bit data, while high-order address lines enable the  $\overline{\text{CE}}$  input.

**FIGURE 8-2:** Interface to Typical  $\mu$ P Data Bus

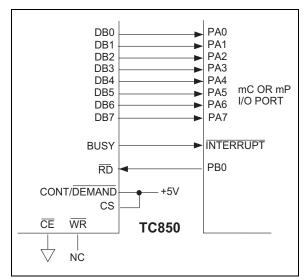

Figure 8-3 shows a typical interface to a  $\mu P$  I/O port or single-chip  $\mu C$ . The TC850 operates in the Continuous mode and can either interrupt the  $\mu C/\mu P$  or be polled with an input pin.

**FIGURE 8-3:** Interface to Typical  $\mu$ P I/O Port or Single Chip  $\mu$ C

Since the PA0-PA7 inputs are dedicated to reading A/D data, the A/D CS/ $\overline{\text{CE}}$  inputs can be enabled continuously. In Continuous mode, data must be read in 3 bytes, as shown in Table 6-1. The required  $\overline{\text{RD}}$  pulses are provided by a  $\mu\text{C}/\mu\text{P}$  output pin.

The circuit of Figure 8-3 can also operate in the Demand mode, with the start-up conversion strobe generated by a  $\mu C/\mu P$  output pin. In this case, the L/H and CONT/DEMAND inputs can be controlled by I/O pins and the  $\overline{RD}$  input connected to digital ground.

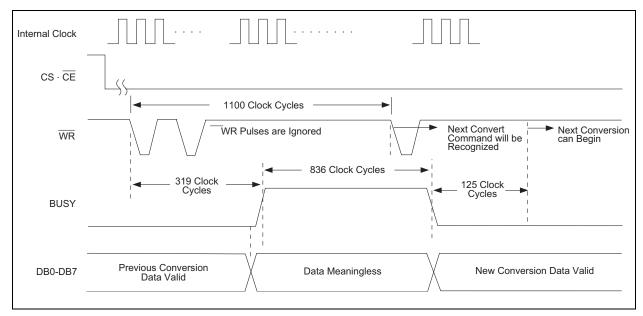

# 8.3 Demand Mode Interface Timing

When CONT/DEMAND input is LOW, the TC850 performs a conversion each time CE and CS are active and WR is strobed LOW.

The Demand mode conversion timing is shown in Figure 8-1. BUSY goes LOW and data is valid 1155 clock pulses after WR goes LOW. After BUSY goes low, 125 additional clock cycles are required before the next conversion cycle will begin.

Once conversion is started,  $\overline{WR}$  is ignored for 1100 internal clock cycles. After 1100 clock cycles, another  $\overline{WR}$  pulse is recognized and initiates a new conversion when the present conversion is complete. A negative edge on  $\overline{WR}$  is required to begin conversion. If  $\overline{WR}$  is held LOW, conversions will not occur continuously.

The A/D conversion data is valid on the falling edge of BUSY and remains valid until one-half internal clock cycle before BUSY goes HIGH on the succeeding conversion. BUSY can be monitored with an I/O pin to determine end of conversion or to generate a  $\mu P$  interrupt.

In Demand mode, the three data bytes can be read in any desired order. The TC850 is simply regarded as three bytes of memory and accessed accordingly. The bus output timing is shown in Figure 8-2.

# 8.4 Continuous Mode Interface Timing

When the CONT/DEMAND input is HIGH, the TC850 performs conversions continuously. Data will be valid on the falling edge of BUSY and all three bytes must be read within 443-1/2 internal clock cycles of BUSY going LOW. The timing diagram is shown in Figure 8-3.

In Continuous mode,  $OVR/\overline{POL}$  and  $L/\overline{H}$  byte-select inputs are ignored. The TC850 automatically cycles through three data bytes, as shown in Table 6-1. Bus output timing in the Continuous mode is shown in Figure 8-4.

FIGURE 8-4: Conversion Timing, Demand Mode

FIGURE 8-5: Bus Output Timing, Demand Mode

FIGURE 8-6: Conversion Timing, Continuous Mode

FIGURE 8-7: Bus Output Timing, Continuous Mode

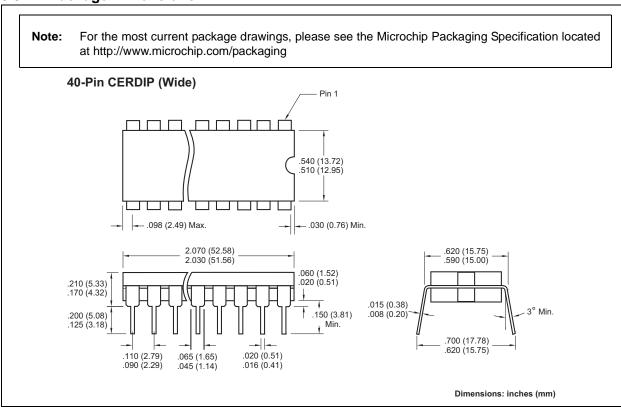

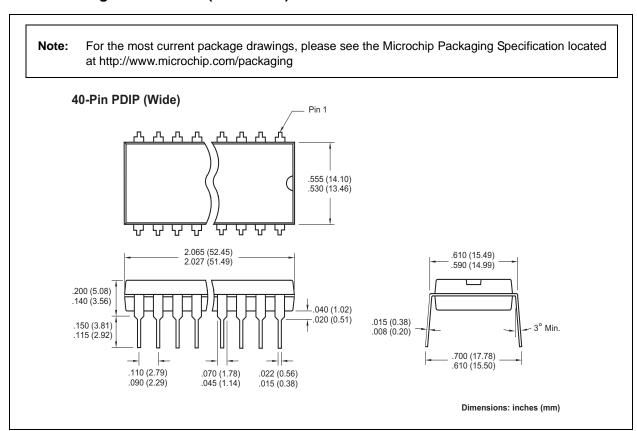

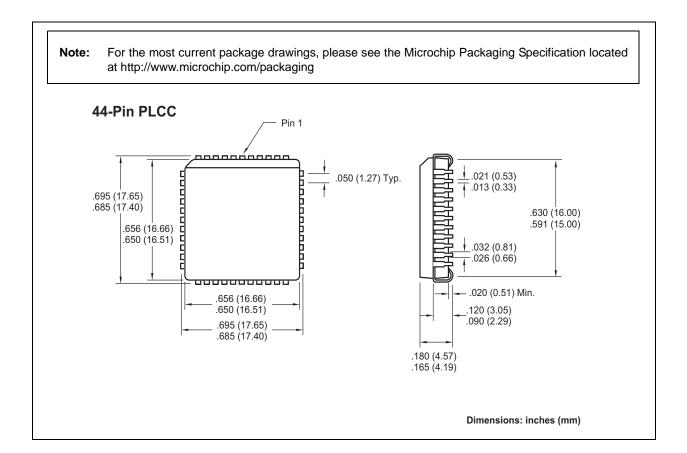

#### 9.0 **PACKAGING INFORMATION**

#### 9.1 **Package Marking Information**

Package marking data not available at this time

#### 9.2 **Taping Form**

# 9.3 Package Dimensions

# 9.3 Package Dimensions (Continued)

# 10.0 REVISION HISTORY

Revision D (December 2012)

Added a note to each package outline drawing.

| _   | -             |   | _ |

|-----|---------------|---|---|

| - 1 | / <b>~</b> () |   |   |

|     |               | _ |   |

|     |               |   |   |

NOTES:

# **SALES AND SUPPORT**

## **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- Your local Microchip sales office

- 1. 2. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

| _   | -             |   | _ |

|-----|---------------|---|---|

| - 1 | / <b>~</b> () |   |   |

|     |               | _ |   |

|     |               |   |   |

NOTES:

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager Reader Response       | Total Pages Sent                         |

|------------|------------------------------------------------------|------------------------------------------|

| From       | : Name                                               |                                          |

|            | Company                                              |                                          |

|            | Address                                              |                                          |

|            | City / State / ZIP / Country                         |                                          |

|            | Telephone: ()                                        | FAX: (                                   |

| Appli      | cation (optional):                                   |                                          |

| Woul       | d you like a reply?YN                                |                                          |

| Devic      | e: TC850                                             | Literature Number: DS21479D              |

| Ques       | tions:                                               |                                          |

| 1. V       | Vhat are the best features of this document?         |                                          |

| _          |                                                      |                                          |

| 2. H       | low does this document meet your hardware and so     | oftware development needs?               |

| _          |                                                      |                                          |

| 3. [       | o you find the organization of this document easy t  | o follow? If not, why?                   |

| _          |                                                      |                                          |

| 4. V       | What additions to the document do you think would    | enhance the structure and subject?       |

| _          |                                                      |                                          |

| 5. V       | What deletions from the document could be made w     | ithout affecting the overall usefulness? |

| _          |                                                      |                                          |

| _          |                                                      |                                          |

| 6. Is      | s there any incorrect or misleading information (wha | at and where)?                           |

| _          |                                                      |                                          |

| 7. H       | low would you improve this document?                 |                                          |

| _          |                                                      |                                          |

| _          |                                                      |                                          |

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2001-2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620768433

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **Worldwide Sales and Service**

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario, Canada

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 **China - Nanjing**

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan Tel: 86-27-5980-5300

Fax: 86-27-5980-5118 China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-6-6152-7160

Fax: 81-6-6152-9310 Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859 **Malaysia - Penang**

Tel: 60-4-227-8870 Fax: 60-4-227-4068 Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

## **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

## Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А