# **Enhanced, High-Efficiency Power Factor Controller**

The NCP1612 is designed to drive PFC boost stages based on an innovative Current Controlled Frequency Fold-back (CCFF) method. In this mode, the circuit classically operates in Critical conduction Mode (CrM) when the inductor current exceeds a programmable value. When the current is below this preset level, the NCP1612 linearly decays the frequency down to about 20 kHz when the current is null. CCFF maximizes the efficiency at both nominal and light load. In particular, the stand-by losses are reduced to a minimum.

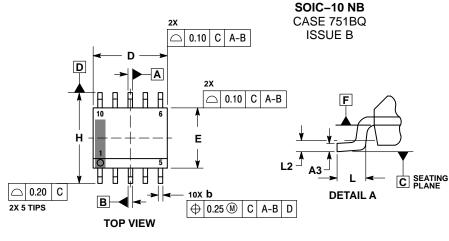

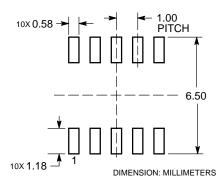

Like in *FCCrM* controllers, an internal circuitry allows near-unity power factor even when the switching frequency is reduced. Housed in a SO–10 package, the circuit also incorporates the features necessary for robust and compact PFC stages, with few external components.

### **General Features**

- Near-unity Power Factor

- Critical Conduction Mode (CrM)

- Current Controlled Frequency Fold-back (CCFF): Low Frequency Operation is Forced at Low Current Levels

- On-time Modulation to Maintain a Proper Current Shaping in CCFF Mode

- Skip Mode Near the Line Zero Crossing

- Fast Line/Load Transient Compensation (Dynamic Response Enhancer)

- Valley Turn On

- High Drive Capability: -500 mA/+800 mA

- V<sub>CC</sub> Range: from 9.5 V to 35 V

- Low Start-up Consumption

- Six Versions: NCP1612A, B, A1, A2, A3 and B2 (see Table 1)

- Line Range Detection

- pfcOK Signal

- This is a Pb-Free Device

### **Safety Features**

- Separate Pin for Fast Over-voltage Protection (FOVP) for Redundancy

- Soft Over-voltage Protection

- Brown-out Detection

- Soft-start for Smooth Start-up Operation (A, A1, A2 and A3 Versions)

- Over Current Limitation

- Disable Protection if the Feedback is Not Connected

- Thermal Shutdown

- Latched Off Capability

### ON Semiconductor®

www.onsemi.com

SOIC-10 CASE 751BQ

### **MARKING DIAGRAM**

1612x = Specific Device Code

x = A, A1, A2, A3, B or B2 = Assembly Location

A = Assembly Loc L = Wafer Lot

Y = Year

W = Work Week

Pb-Free Package

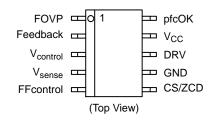

### PIN CONNECTIONS

### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 30 of this data sheet.

- Low Duty-cycle Operation if the Bypass Diode is shorted

- Open Ground Pin Fault Monitoring

- Saturated Inductor Protection

- Detailed Safety Testing Analysis (Refer to Application Note <u>AND9079/D</u>)

### **Typical Applications**

- PC Power Supplies

- All Off Line Appliances Requiring Power Factor Correction

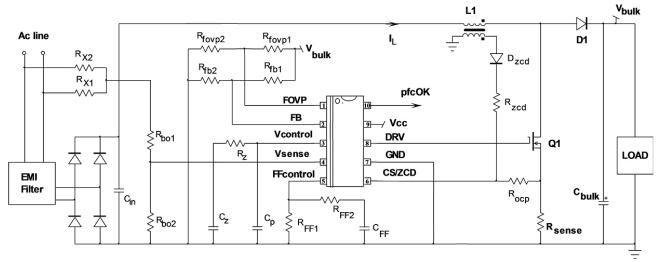

Figure 1. Typical Application Schematic

**Table 1. FIVE NCP1612 VERSIONS**

| Part Number | Typical UVLO<br>Hysteresis | Condition for<br>BUV Tripping<br>(typical threshold) | Maximum<br>Dead-time<br>(typical value) | Condition for<br>Latching-off<br>(typical threshold) | UVP2 if V <sub>FOVP</sub> <v<sub>UVP2</v<sub> | Dynamic Re-<br>sponse<br>Enhancer (DRE)                                           |

|-------------|----------------------------|------------------------------------------------------|-----------------------------------------|------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------|

| NCP1612A    | 1.5 V                      | V <sub>FOVP</sub> < 76%.V <sub>REF</sub>             | 48.5 μs                                 | V <sub>pfcOK</sub> > 7.5 V                           | YES                                           | Disabled until pfcOK turns high                                                   |

| NCP1612A1   | 1.5 V                      | V <sub>FOVP</sub> < 40%.V <sub>REF</sub>             | 48.5 μs                                 | V <sub>pfcOK</sub> > 7.5 V                           | YES                                           | Disabled until pfcOK turns high                                                   |

| NCP1612A2   | 1.5 V                      | V <sub>FB</sub> < 76%.V <sub>REF</sub>               | 48.5 μs                                 | V <sub>FOVP</sub> > 107%.V <sub>REF</sub>            | NO                                            | Disabled until pfcOK turns high                                                   |

| NCP1612A3   | 1.5 V                      | V <sub>FOVP</sub> < 40%.V <sub>REF</sub>             | 41.5 μs                                 | V <sub>pfcOK</sub> > 7.5 V                           | YES                                           | Disabled until pfcOK turns high                                                   |

| NCP1612B    | 8.0 V                      | V <sub>FOVP</sub> < 76%.V <sub>REF</sub>             | 48.5 μs                                 | V <sub>pfcOK</sub> > 7.5 V                           | YES                                           | Enabled as soon<br>as the circuit<br>turns on to<br>speed-up the<br>startup phase |

| NCP1612B2*  | 8.0 V                      | V <sub>FB</sub> < 76%.V <sub>REF</sub>               | 48.5 μs                                 | V <sub>FOVP</sub> > 107%.V <sub>REF</sub>            | NO                                            | Enabled as soon<br>as the circuit<br>turns on to<br>speed-up the<br>startup phase |

<sup>\*</sup>Please contact local sales representative for availability

### **Recommended Applications:**

- The NCP1612B and NCP1612B2 large UVLO hysteresis (6 V minimum) avoids the need for large V<sub>CC</sub> capacitors and help shorten the start-up time without the need for too dissipative start-up elements in self-powered PFC applications (where high-impedance start-up resistors are generally implemented to pre-charge the V<sub>CC</sub> capacitor).

- The A, A1, A2 and A3 versions are preferred in applications where the circuit is fed by an external power source (from an auxiliary power supply or from a downstream converter). Its maximum start-up level (11.25 V) is set low enough so that the circuit can be powered from a 12-V voltage rail.

- A2 and B2 versions are to be preferred when a signal other than a portion of the output voltage is applied to the FOVP pin (e.g., a voltage representative of the output voltage provided by an auxiliary winding) and/or if the pfcOK pin voltage must be able to rise up to the V<sub>CC</sub> level without latching the part. Note that with the A2 and B2 versions, the fast OVP protection latches-off the circuit when triggered.

Table 2. MAXIMUM RATINGS (Note 1)

| Symbol                             | Pin | Rating                                                                                                                             | Value                                | Unit       |

|------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------|

| V <sub>CC</sub>                    | 9   | Power Supply Input                                                                                                                 | -0.3, +35                            | V          |

| FOVP                               | 1   | FOVP Pin                                                                                                                           | -0.3, +10                            | V          |

| Feedback                           | 2   | Feedback Pin                                                                                                                       | -0.3, +10                            | V          |

| V <sub>CONTROL</sub>               | 3   | V <sub>CONTROL</sub> Pin (Note 2)                                                                                                  | −0.3, V <sub>CONTROL</sub> MAX       | V          |

| V <sub>sense</sub>                 | 4   | V <sub>sense</sub> Pin (Note 3)                                                                                                    | -0.3, +10                            | V          |

| FFcontrol                          | 5   | FFcontrol Pin                                                                                                                      | -0.3, +10                            | V          |

| CS/ZCD                             | 6   | Input Voltage (Note 4)<br>Current Injected to Pin 4 (Note 5)                                                                       | -0.3, +35<br>+5                      | V<br>mA    |

| DRV                                | 8   | Driver Voltage (Note 2)<br>Driver Current                                                                                          | -0.3, V <sub>DRV</sub><br>-500, +800 | V<br>mA    |

| pfcOK                              | 10  | pfcOK Pin                                                                                                                          | -0.3, V <sub>CC</sub>                | V          |

| P <sub>D</sub><br>R <sub>θJA</sub> |     | Power Dissipation and Thermal Characteristics Maximum Power Dissipation @ T <sub>A</sub> = 70°C Thermal Resistance Junction-to-Air | 550<br>145                           | mW<br>°C/W |

| TJ                                 |     | Operating Junction Temperature Range                                                                                               | -40 to +125                          | °C         |

| T <sub>Jmax</sub>                  |     | Maximum Junction Temperature                                                                                                       | 150                                  | °C         |

| T <sub>Smax</sub>                  |     | Storage Temperature Range                                                                                                          | -65 to 150                           | °C         |

| T <sub>Lmax</sub>                  |     | Lead Temperature (Soldering, 10s)                                                                                                  | 300                                  | °C         |

| MSL                                |     | Moisture Sensitivity Level                                                                                                         | 1                                    | _          |

|                                    |     | ESD Capability, Human Body Model (Note 6)                                                                                          | > 2000                               | V          |

|                                    |     | ESD Capability, Machine Model (Note 6)                                                                                             | > 200                                | V          |

|                                    |     | ESD Capability, Charged Device Model (Note 6)                                                                                      | 1000                                 | V          |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

- "V<sub>CONTROL</sub>MAX" is the pin3 clamp voltage and "V<sub>DRV</sub>" is the DRV clamp voltage (V<sub>DRVhigh</sub>). If V<sub>CC</sub> is below V<sub>DRVhigh</sub>, "V<sub>DRV</sub>" is V<sub>CC</sub>.

- 3. Recommended maximum  $V_{sense}$  voltage for optimal operation is 4.5 V.

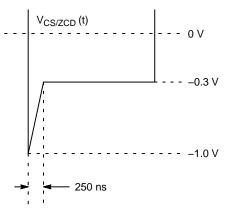

- 4. The recommended maximum voltage not to exceed remains -0.3 V but Figure 2 short negative spike on the CS/ZCD pin is typically acceptable. However, it implies the full characterization of the circuit embedding the NCP1612, including at maximum temperature conditions, during which no erratic operation is observed. If otherwise noted, we recommend to clamp the negative voltage on the CS/ZCD pin to avoid carrier injection within the die.

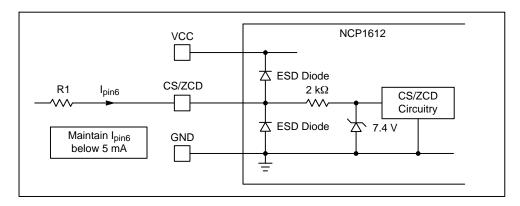

Maximum CS/ZCD current that can be injected into pin6 (see Figure 3).

- 6. This device(s) contains ESD protection and exceeds the following tests: Human Body Model 2000 V per JEDEC Standard JESD22-A114E Machine Model Method 200 V per JEDEC Standard JESD22-A115-A Charged Device Model Method 1000 V per JEDEC Standard JESD22-C101E

Figure 2.

Figure 3.

## **Table 3. TYPICAL ELECTRICAL CHARACTERISTICS**

(Conditions: V<sub>CC</sub> = 15 V, T<sub>J</sub> from -40°C to +125°C, unless otherwise specified)

| Symbol                 | Rating                                                                                                                | Min           | Тур            | Max            | Unit |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------|----------------|----------------|------|

| TART-UP AND            | SUPPLY CIRCUIT                                                                                                        |               |                |                | •    |

| V <sub>CC(on)</sub>    | Start-up Threshold, V <sub>CC</sub> increasing: A, A1, A2 and A3 versions B and B2 versions                           | 9.75<br>15.80 | 10.50<br>17.00 | 11.25<br>18.20 | V    |

| V <sub>CC(off)</sub>   | Minimum Operating Voltage, V <sub>CC</sub> falling                                                                    | 8.5           | 9.0            | 9.5            | V    |

| V <sub>CC(HYST)</sub>  | Hysteresis ( $V_{CC(on)} - V_{CC(off)}$ ) A, A1, A2 and A3 versions B and B2 versions                                 |               | 1.50<br>8.00   | -<br>-         | V    |

| V <sub>CC(reset)</sub> | V <sub>CC</sub> level below which the circuit resets                                                                  | 2.5           | 4.0            | 6.0            | V    |

| I <sub>CC(start)</sub> | Start-up Current, V <sub>CC</sub> = 9.4 V                                                                             | -             | 20             | 50             | μΑ   |

| I <sub>CC(op)1</sub>   | Operating Consumption, no switching (V <sub>SENSE</sub> pin being grounded)                                           | -             | 0.5            | 1.0            | mA   |

| I <sub>CC(op)2</sub>   | Operating Consumption, 50 kHz switching, no load on DRV pin                                                           | -             | 2.0            | 3.0            | mA   |

| CURRENT CON            | ITROLLED FREQUENCY FOLD-BACK                                                                                          |               |                |                |      |

| T <sub>DT1</sub>       | Dead-time, V <sub>FFcontrol</sub> = 2.60 V (Note 7)                                                                   | _             | _              | 0              | μS   |

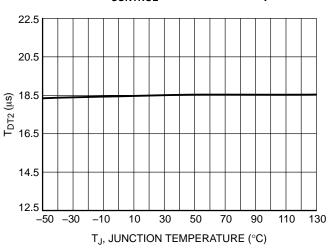

| T <sub>DT2</sub>       | Dead-time, V <sub>FFcontrol</sub> = 1.75 V                                                                            | 14            | 18             | 22             | μS   |

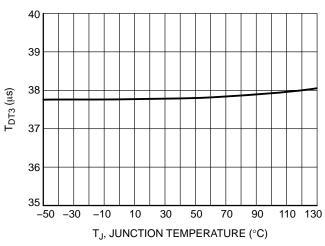

| T <sub>DT3</sub>       | Dead-time, V <sub>FFcontrol</sub> = 1.00 V                                                                            | 32            | 38             | 44             | μs   |

| T <sub>DT4</sub>       | Dead-time, V <sub>FFcontrol</sub> = V <sub>SKIP_L</sub> + 30 mV (NCP1612A3 Only) @ 25°C<br>Over the Temperature Range | 34.0<br>32.0  | 41.5<br>41.5   | 45.0<br>47.0   | μs   |

| I <sub>DT1</sub>       | FFcontrol Pin current, $V_{sense} = 1.4 \text{ V}$ and $V_{control}$ maximum                                          | 180           | 200            | 220            | μΑ   |

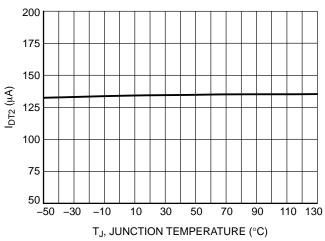

| $I_{\mathrm{DT2}}$     | FFcontrol Pin current, $V_{sense} = 2.8 \text{ V}$ and $V_{control}$ maximum                                          | 110           | 135            | 160            | μΑ   |

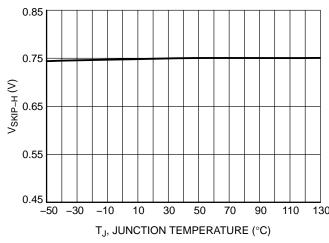

| V <sub>SKIP-H</sub>    | FFcontrol pin Skip Level, V <sub>FFcontrol</sub> rising All Versions Except NCP1612A3 NCP1612A3                       | 1 1           | 0.75<br>1.00   | 0.85<br>1.05   | V    |

| V <sub>SKIP-L</sub>    | FFcontrol pin Skip Level, V <sub>FFcontrol</sub> falling All Versions Except NCP1612A3 NCP1612A3                      | 0.55<br>0.85  | 0.65<br>0.90   | _<br>_         | V    |

| H <sub>SKIP-L</sub>    | FFcontrol pin Skip Hysteresis                                                                                         | 50            | -              | _              | mV   |

| SATE DRIVE (N          | lote 8)                                                                                                               |               |                |                |      |

| T <sub>R</sub>         | Output voltage rise-time @ $C_L$ = 1 nF, 10–90% of output signal                                                      | _             | 30             | _              | ns   |

| T <sub>F</sub>         | Output voltage fall-time @ $C_L$ = 1 nF, 10–90% of output signal                                                      | -             | 20             | _              | ns   |

| R <sub>OH</sub>        | Source resistance                                                                                                     | -             | 10             | _              | Ω    |

| R <sub>OL</sub>        | Sink resistance                                                                                                       | -             | 7.0            | _              | Ω    |

| I <sub>SOURCE</sub>    | Peak source current, V <sub>DRV</sub> = 0 V (guaranteed by design)                                                    | -             | 500            | _              | mA   |

| I <sub>SINK</sub>      | Peak sink current, $V_{DRV} = 12 \text{ V (guaranteed by design)}$                                                    |               | 800            | _              | mA   |

| $V_{DRVlow}$           | DRV pin level at $V_{CC}$ close to $V_{CC(off)}$ with a 10 k $\Omega$ resistor to GND                                 |               | _              | _              | V    |

| $V_{DRVhigh}$          | DRV pin level at $V_{CC}$ = 35 V ( $R_L$ = 33 k $\Omega$ , $C_L$ = 220 pF)                                            |               | 12             | 14             | V    |

# Table 3. TYPICAL ELECTRICAL CHARACTERISTICS (continued)

(Conditions:  $V_{CC}$  = 15 V,  $T_J$  from  $-40^{\circ}C$  to +125 $^{\circ}C$ , unless otherwise specified)

| Symbol                                                                         | Rating                                                                                                                  |              | Тур          | Max          | Unit     |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|----------|

| REGULATION BL                                                                  | оск                                                                                                                     |              | •            | •            |          |

| V <sub>REF</sub>                                                               | Feedback Voltage Reference:                                                                                             |              |              |              | V        |

|                                                                                | @ 25°C Over the temperature range                                                                                       | 2.44<br>2.42 | 2.50<br>2.50 | 2.54<br>2.54 |          |

| I                                                                              | Error Amplifier Current Capability                                                                                      |              | ±20          | 2.04         | ^        |

| I <sub>EA</sub><br>G <sub>EA</sub>                                             | Error Amplifier Gain                                                                                                    | 110          | 220          | 290          | μA<br>μS |

|                                                                                | V <sub>CONTROL</sub> Pin Voltage:                                                                                       | 110          | 220          | 290          | γ        |

| V <sub>CONTROL</sub><br>-V <sub>CONTROL</sub> MAX<br>-V <sub>CONTROL</sub> MIN | - @ V <sub>FB</sub> = 2 V<br>- @ V <sub>FB</sub> = 3 V                                                                  | -            | 4.5<br>0.5   | -<br>-       | V        |

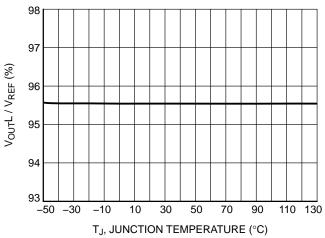

| V <sub>OUT</sub> L/V <sub>REF</sub>                                            | Ratio (V <sub>OUT</sub> Low Detect Threshold/V <sub>REF</sub> ) (guaranteed by design)                                  | 95.0         | 95.5         | 96.0         | %        |

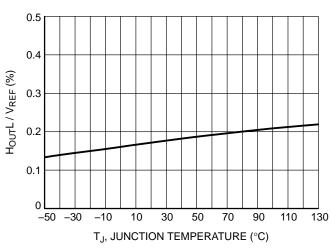

| H <sub>OUT</sub> L/V <sub>REF</sub>                                            | Ratio (V <sub>OUT</sub> Low Detect Hysteresis/V <sub>REF</sub> ) (guaranteed by design)                                 | -            | -            | 0.5          | %        |

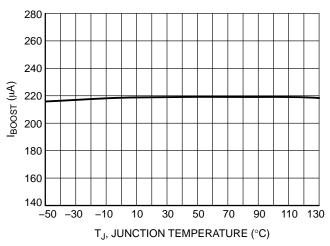

| I <sub>BOOST</sub>                                                             | $V_{CONTROL}$ Pin Source Current when ( $V_{OUT}$ Low Detect) is activated                                              | 180          | 220          | 250          | μΑ       |

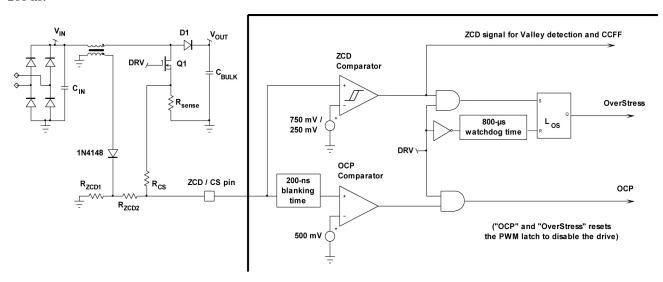

| CURRENT SENS                                                                   | E AND ZERO CURRENT DETECTION BLOCKS                                                                                     |              | •            | •            | •        |

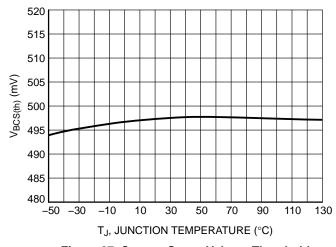

| V <sub>CS(th)</sub>                                                            | Current Sense Voltage Reference                                                                                         | 450          | 500          | 550          | mV       |

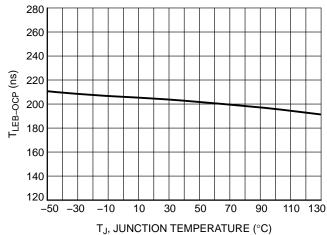

| T <sub>LEB,OCP</sub>                                                           | Over-current Protection Leading Edge Blanking Time (guaranteed by design)                                               | 100          | 200          | 350          | ns       |

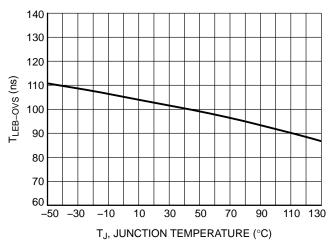

| T <sub>LEB,OVS</sub>                                                           | "OverStress" Leading Edge Blanking Time (guaranteed by design)                                                          | 50           | 100          | 170          | ns       |

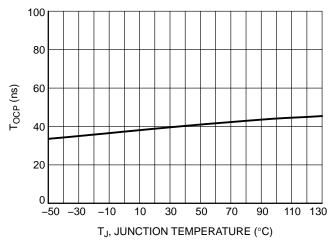

| T <sub>OCP</sub>                                                               | Over-current Protection Delay from $V_{CS/ZCD} > V_{CS(th)}$ to DRV low $(dV_{CS/ZCD} / dt = 10 \text{ V/}\mu\text{s})$ | -            | 40           | 200          | ns       |

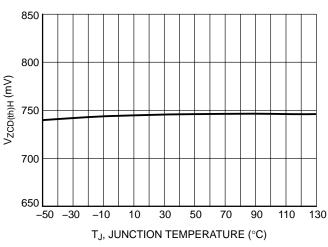

| V <sub>ZCD(th)H</sub>                                                          | Zero Current Detection, V <sub>CS/ZCD</sub> rising                                                                      | 675          | 750          | 825          | mV       |

| V <sub>ZCD(th)L</sub>                                                          | Zero Current Detection, V <sub>CS/ZCD</sub> falling                                                                     | 200          | 250          | 300          | mV       |

| V <sub>ZCD(hyst)</sub>                                                         | Hysteresis of the Zero Current Detection Comparator                                                                     | 375          | 500          | -            | mV       |

| R <sub>ZCD/CS</sub>                                                            | V <sub>ZCD(th)H</sub> over V <sub>CS(th)</sub> Ratio                                                                    | 1.4          | 1.5          | 1.6          | -        |

| V <sub>CL(pos)</sub>                                                           | CS/ZCD Positive Clamp @ I <sub>CS/ZCD</sub> = 5 mA                                                                      | _            | 15.6         | -            | V        |

| I <sub>ZCD(bias)</sub>                                                         | Current Sourced by the CS/ZCD Pin, $V_{\text{CS/ZCD}} = V_{\text{ZCD(th)H}}$                                            | 0.5          | -            | 2.0          | μΑ       |

| I <sub>ZCD(bias)</sub>                                                         | Current Sourced by the CS/ZCD Pin, $V_{\text{CS/ZCD}} = V_{\text{ZCD}(th)L}$                                            | 0.5          | -            | 2.0          | μΑ       |

| T <sub>ZCD</sub>                                                               | $(V_{CS/ZCD} < V_{ZCD(th)L})$ to (DRV high)                                                                             | -            | 60           | 200          | ns       |

| T <sub>SYNC</sub>                                                              | Minimum ZCD Pulse Width                                                                                                 | _            | 110          | 200          | ns       |

| T <sub>WDG</sub>                                                               | Watch Dog Timer                                                                                                         | 80           | 200          | 320          | μs       |

| T <sub>WDG(OS)</sub>                                                           | Watch Dog Timer in "Overstress" Situation                                                                               | 400          | 800          | 1200         | μS       |

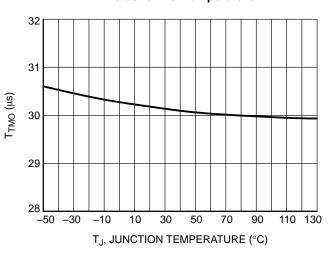

| T <sub>TMO</sub>                                                               | Time-out Timer                                                                                                          | 20           | 30           | 50           | μS       |

| I <sub>ZCD(gnd)</sub>                                                          | Source Current for CS/ZCD pin impedance Testing                                                                         | -            | 250          | _            | μΑ       |

| STATIC OVP                                                                     |                                                                                                                         |              |              |              |          |

| D <sub>MIN</sub>                                                               | Duty Cycle, $V_{FB} = 3 \text{ V}$ , $V_{control}$ pin open                                                             | _            | -            | 0            | %        |

| ON-TIME CONTR                                                                  | OL                                                                                                                      |              | •            | •            | •        |

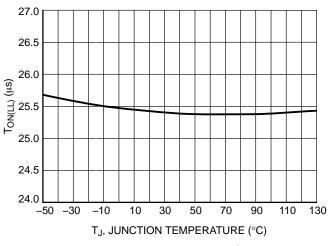

| T <sub>ON(LL)</sub>                                                            | Maximum On Time, $V_{sense} = 1.4 \text{ V}$ and $V_{control}$ maximum (CrM)                                            | 22.0         | 25.0         | 29.0         | μs       |

| T <sub>ON(LL)2</sub>                                                           | On Time, $V_{sense} = 1.4 \text{ V}$ and $V_{control} = 2.5 \text{ V}$ (CrM)                                            | 10.5         | 12.5         | 14.0         | μs       |

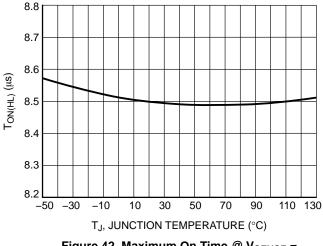

| T <sub>ON(HL)</sub>                                                            | Maximum On Time, $V_{sense} = 2.8 \text{ V}$ and $V_{control}$ maximum (CrM)                                            | 7.3          | 8.5          | 9.6          | μs       |

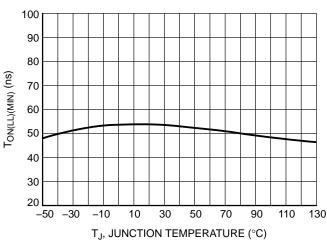

| T <sub>ON(LL)(MIN)</sub>                                                       | Minimum On Time, $V_{sense} = 1.4 \text{ V}$ (not tested, guaranteed by characterization)                               | -            | -            | 200          | ns       |

| T <sub>ON(HL)(MIN)</sub>                                                       | Minimum On Time, $V_{sense}$ = 2.8 V (not tested, guaranteed by characterization)                                       | _            | -            | 100          | ns       |

| FEED-BACK OVI                                                                  | ER AND UNDER-VOLTAGE PROTECTION (SOFT OVP AND UVP)                                                                      |              |              |              |          |

| R <sub>softOVP</sub>                                                           | Ratio (soft OVP Threshold, $V_{FB}$ rising) over $V_{REF}$ ( $V_{softOVP}/V_{REF}$ ) (guaranteed by design)             | 104          | 105          | 106          | %        |

| R <sub>softOVP(HYST)</sub>                                                     | Ratio (Soft OVP Hysteresis) over V <sub>REF</sub> (guaranteed by design)                                                | 1.5          | 2.0          | 2.5          | %        |

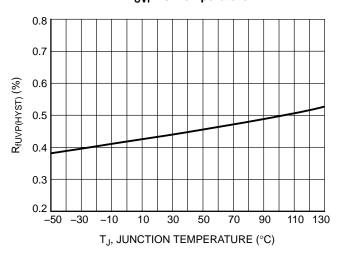

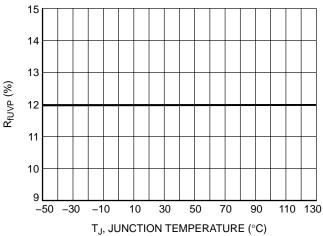

| R <sub>UVP</sub>                                                               | Ratio (UVP Threshold, $V_{FB}$ rising) over $V_{REF}$ ( $V_{UVP}/V_{REF}$ ) (guaranteed by design)                      | 8            | 12           | 16           | %        |

| R <sub>UVP(HYST)</sub>                                                         | Ratio (UVP Hysteresis) over V <sub>REF</sub> (guaranteed by design)                                                     | -            | -            | 1            | %        |

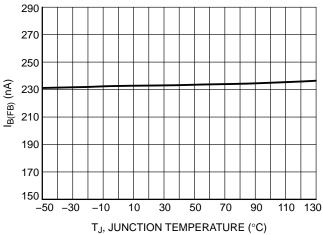

| (I <sub>B</sub> ) <sub>FB</sub>                                                | FB Pin Bias Current @ $V_{FB} = V_{SoftOVP}$ and $V_{FB} = V_{UVP}$                                                     | 50           | 200          | 450          | nA       |

|                                                                                |                                                                                                                         |              |              |              | ·        |

### Table 3. TYPICAL ELECTRICAL CHARACTERISTICS (continued)

(Conditions:  $V_{CC} = 15 \text{ V}$ ,  $T_J$  from  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , unless otherwise specified)

| Symbol                                | Rating                                                                                                                                                                                                                           | Min                  | Тур                  | Max                  | Unit |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

| FAST OVER VO                          | LTAGE PROTECTION AND BULK UNDER-VOLTAGE PROTECTION (FAST C                                                                                                                                                                       | VP AND B             | UV)                  | •                    | I    |

| $V_{fastOVP}$                         | Fast OVP Threshold, V <sub>FOVP</sub> rising                                                                                                                                                                                     |                      | 2.675                | 2.750                | V    |

| R <sub>fastOVP1</sub>                 | Ratio (Fast OVP Threshold, $V_{FOVP}$ rising) over (soft OVP Threshold, $V_{FB}$ rising) ( $V_{fastOVP}/V_{softOVP}$ ) (guaranteed by design)                                                                                    | 101.5                | 102.0                | 102.5                | %    |

| R <sub>fastOVP2</sub>                 | Ratio (Fast OVP Threshold, V <sub>FOVP</sub> rising) over V <sub>REF</sub> (V <sub>fastOVP</sub> /V <sub>REF</sub> ) (guaranteed by design)                                                                                      | 106                  | 107                  | 108                  | %    |

| V <sub>BUV</sub>                      | BUV Threshold: NCP1612A, NCP1612B, V <sub>FOVP</sub> falling NCP1612A1, NCP1612A3, V <sub>FOVP</sub> falling NCP1612A2 and NCP1612B2, V <sub>FB</sub> falling                                                                    | 1.80<br>0.90<br>1.80 | 1.90<br>1.00<br>1.90 | 2.00<br>1.10<br>2.00 | V    |

| R <sub>BUV</sub>                      | Ratio (BUV Threshold) over V <sub>REF</sub> (V <sub>BUV</sub> /V <sub>REF</sub> ) NCP1612A, NCP1612B, V <sub>FOVP</sub> falling NCP1612A1, NCP1612A3, V <sub>FOVP</sub> falling NCP1612A2 and NCP1612B2, V <sub>FB</sub> falling |                      | 76<br>40<br>76       | 78<br>43<br>78       | %    |

| (I <sub>B</sub> ) <sub>FOVP/BUV</sub> | Pin1 Bias Current  @ V <sub>pin1</sub> = V <sub>fastOVP</sub> (all versions)  @ V <sub>pin1</sub> = V <sub>BUV</sub> (NCP1612A, NCP1612A1, NCP1612B, NCP1612A3 only)                                                             | 50<br>50             | 200<br>200           | 450<br>450           | nA   |

| V <sub>UVP2</sub>                     | UVP2 Threshold for Floating Pin Detection (NCP1612A, NCP1612A1, NCP1612A3 and NCP1612B only)                                                                                                                                     | 0.2                  | 0.3                  | 0.4                  | V    |

| ROWN-OUT PR                           | ROTECTION AND FEED-FORWARD                                                                                                                                                                                                       | •                    | •                    | •                    |      |

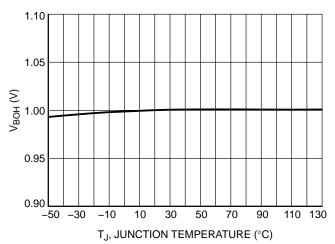

| V <sub>BOH</sub>                      | Brown-out Threshold, V <sub>sense</sub> rising                                                                                                                                                                                   | 0.96                 | 1.00                 | 1.04                 | V    |

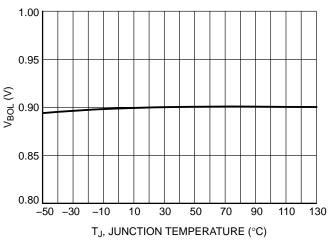

| V <sub>BOL</sub>                      | Brown-out Threshold, V <sub>sense</sub> falling                                                                                                                                                                                  | 0.86                 | 0.90                 | 0.94                 | V    |

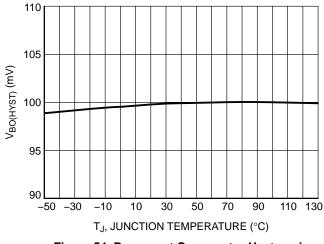

| V <sub>BO(HYST)</sub>                 | Brown-out Comparator Hysteresis                                                                                                                                                                                                  | 60                   | 100                  | _                    | mV   |

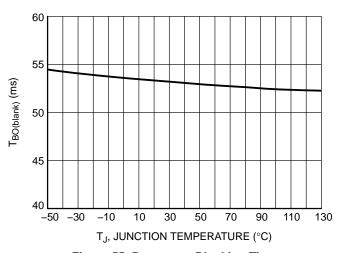

| T <sub>BO(blank)</sub>                | Brown-out Blanking Time                                                                                                                                                                                                          | 35                   | 50                   | 65                   | ms   |

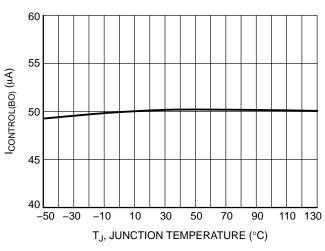

| I <sub>CONTROL(BO)</sub>              | V <sub>CONTROL</sub> Pin Sink Current, V <sub>sense</sub> < V <sub>BOL</sub>                                                                                                                                                     | 40                   | 50                   | 60                   | μΑ   |

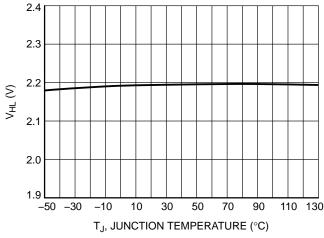

| $V_{HL}$                              | High-line Detection Comparator Threshold, V <sub>sense</sub> rising                                                                                                                                                              | 2.1                  | 2.2                  | 2.3                  | V    |

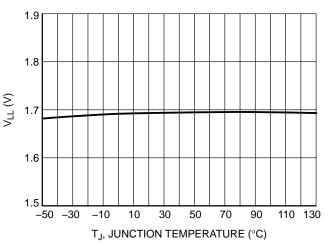

| V <sub>LL</sub>                       | High-line Detection Comparator Threshold, V <sub>sense</sub> falling                                                                                                                                                             | 1.6                  | 1.7                  | 1.8                  | V    |

| V <sub>HL(hyst)</sub>                 | High-line Detection Comparator Hysteresis                                                                                                                                                                                        | 400                  | 500                  | 600                  | mV   |

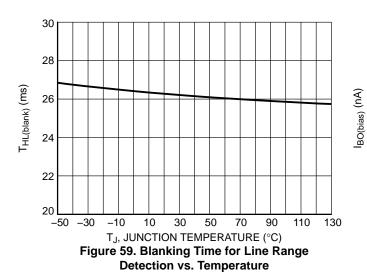

| T <sub>HL(blank)</sub>                | Blanking Time for Line Range Detection                                                                                                                                                                                           | 15                   | 25                   | 35                   | ms   |

| I <sub>BO(bias)</sub>                 | Brown-out Pin Bias Current, V <sub>sense</sub> = V <sub>BO</sub>                                                                                                                                                                 | -250                 | _                    | 250                  | nA   |

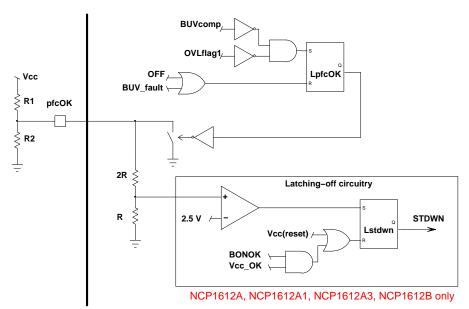

| fcOK SIGNAL                           |                                                                                                                                                                                                                                  | *                    |                      |                      |      |

| (V <sub>pfcOK</sub> ) <sub>L</sub>    | pfcOK low state voltage @ IpfcOK = 5 mA                                                                                                                                                                                          | _                    | _                    | 250                  | mV   |

| V <sub>STDWN</sub>                    | Shutdown Threshold Voltage (NCP1612A, NCP1612A1, NCP1612A3 and NCP1612B only)                                                                                                                                                    |                      | 7.5                  | 8.0                  | V    |

| R <sub>pfcOK</sub>                    | Impedance of the pfcOK pin in high state (all versions)                                                                                                                                                                          | 150                  | 300                  | _                    | kΩ   |

| HERMAL SHUT                           | TDOWN                                                                                                                                                                                                                            | •                    | •                    | •                    | •    |

| T <sub>LIMIT</sub>                    | Thermal Shutdown Threshold                                                                                                                                                                                                       | _                    | 150                  | _                    | °C   |

| H <sub>TEMP</sub>                     | Thermal Shutdown Hysteresis                                                                                                                                                                                                      | _                    | 50                   | _                    | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>7.</sup> There is actually a minimum dead-time that is the delay between the core reset detection and the DRV turning on (T<sub>ZCD</sub> parameter of the "Current Sense and Zero Current Detection Blocks" section).

<sup>8.</sup> Guaranteed by design, the VCC pin can handle the double of the DRV peak source current, that is, 1 A typically.

**Table 4. DETAILED PIN DESCRIPTION**

| Pin Number | Name                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

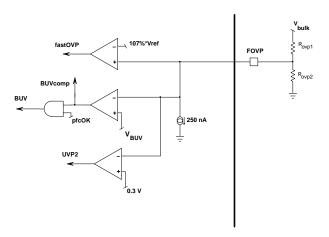

| 1          | FOVP                  | V <sub>pin1</sub> is the input signal for the Fast Over-voltage (FOVP). The circuit disables the driver if V <sub>pin1</sub> exceeds the FOVP threshold which is set 2% higher than the reference for the soft OVP comparator (that monitors the feedback pin) so that pins 1 and 2 can receive the same portion of the output voltage.  With the NCP1612A, NCP1612A1, NCP1612A3 and NCP1612B, V <sub>pin1</sub> is also used for under-voltage detection (UVP2) and Bulk Under Voltage (BUV) detection. The BUV comparator disables the driver and grounds the pfcOK pin when V <sub>pin1</sub> drops below 76% of the 2.5 V reference voltage in the A and B versions and below 40% of the 2.5 V reference voltage in the A1/A3 version. The BUV function has no action whenever the pfcOK pin is in low state. A 250 nA sink current is built-in to ground the pin if the pin is accidentally open.                                     |

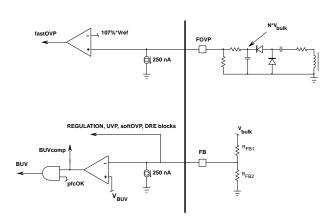

| 2          | Feedback              | This pin receives a portion of the PFC output voltage for the regulation and the Dynamic Response Enhancer (DRE) that drastically speeds-up the loop response when the output voltage drops below 95.5% of the desired output level. $V_{pin2} \   \text{is also the input signal for the Over-voltage (OVP) and Under-voltage (UVP)} \   \text{comparators}. The UVP comparator prevents operation as long as $V_{pin2}$ is lower than 12% of the reference voltage (V_{REF}). A soft OVP comparator gradually reduces the duty-ratio to zero when $V_{pin2}$ exceeds 105% of $V_{REF}$ (soft OVP). With the NCP1612A2 and the NCP1612B2, $V_{pin2}$ is used for Bulk Under Voltage (BUV) detection. A 250 nA sink current is built-in to trigger the UVP protection and disable the part if the feedback pin is accidentally open.$                                                                                                      |

| 3          | V <sub>CONTROL</sub>  | The error amplifier output is available on this pin. The network connected between this pin and ground adjusts the regulation loop bandwidth that is typically set below 20 Hz to achieve high Power Factor ratios.  Pin3 is grounded when the circuit is off so that when it starts operation, V <sub>CONTROL</sub> slowly charges up to provide a soft-start function with the A, A1, A2 and A3 versions which disables the dynamic response enhancer (DRE) until the startup phase is completed. With the versions optimized for self-powered PFC stages (NCP1612B and NCP1612B2), DRE speeds-up the V <sub>CONTROL</sub> charge for a shortened startup phase.                                                                                                                                                                                                                                                                         |

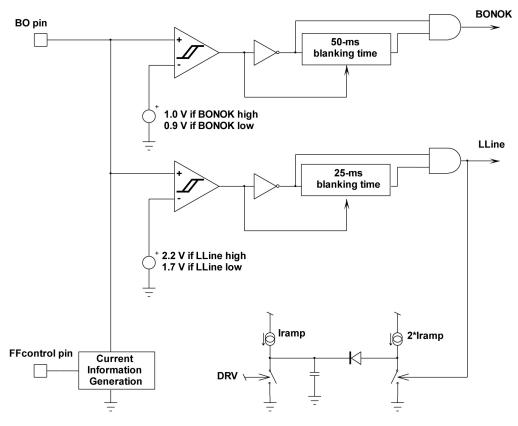

| 4          | V <sub>SENSE</sub>    | A portion of the instantaneous input voltage is to be applied to pin4 in order to detect brown-out conditions. If $V_{pin4}$ is lower than 0.9 V for more than 50 ms, the circuit stops pulsing until the pin voltage rises again and exceeds 1 V.  This pin also detects the line range. By default, the circuit operates the "low-line gain" mode. If $V_{pin4}$ exceeds 2.2 V, the circuit detects a high-line condition and reduces the loop gain by 3. Conversely, if the pin voltage remains lower than 1.7 V for more than 25 ms, the low-line gain is set.  Connecting the pin 4 to ground disables the part once the 50-ms blanking time has elapsed.                                                                                                                                                                                                                                                                             |

| 5          | FF <sub>CONTROL</sub> | This pin sources a current representative to the line current. Connect a resistor between pin5 and ground to generate a voltage representative of the line current. When this voltage exceeds the internal 2.5 V reference (V <sub>REF</sub> ), the circuit operates in critical conduction mode. If the pin voltage is below 2.5 V, a dead-time is generated that approximately equates [66 $\mu s \bullet (1 - (V_{pin5}/V_{REF}))]$ . By this means, the circuit forces a longer dead-time when the current is small and a shorter one as the current increases. The circuit skips cycles whenever $V_{pin5}$ is below 0.65 V to prevent the PFC stage from operating near the line zero crossing where the power transfer is particularly inefficient. This does result in a slightly increased distortion of the current. If superior power factor is required, offset pin 5 by more than 0.75 V offset to inhibit the skip function. |

| 6          | CS/ZCD                | This pin monitors the MOSFET current to limit its maximum current.  This pin is also connected to an internal comparator for Zero Current Detection (ZCD). This comparator is designed to monitor a signal from an auxiliary winding and to detect the core reset when this voltage drops to zero. The auxiliary winding voltage is to be applied through a diode to avoid altering the current sense information for the on-time (see application schematic).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7          | Ground                | Connect this pin to the PFC stage ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8          | Drive                 | The high-current capability of the totem pole gate drive (-0.5/+0.8 A) makes it suitable to effectively drive high gate charge power MOSFETs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9          | V <sub>CC</sub>       | This pin is the positive supply of the IC. The circuit starts to operate when V <sub>CC</sub> exceeds 10.5 V (A, A1, A2 and A3 versions, 17.0 V for the B and B2 versions) and turns off when V <sub>CC</sub> goes below 9.0 V (typical values). After start-up, the operating range is 9.5 V up to 35 V. The A, A1, A2 and A3 versions are preferred in applications where the circuit is fed by an external power source (from an auxiliary power supply or the downstream converter). Its maximum start-up level (11.25 V) is set low enough so that the circuit can be powered from a 12 V rail. The B and B2 versions are optimized for applications where the PFC stage is self-powered.                                                                                                                                                                                                                                             |

| 10         | pfcOK                 | This pin is grounded until the PFC output has reached its nominal level. It is also grounded if the NCP1612 detects a fault. For the rest of the time, i.e., when the PFC stage outputs the nominal bulk voltage, pin10 is in high-impedance state.  The NCP1612A, NCP1612A1, NCP1612A3 and NCP1612B latch off if V <sub>pin10</sub> exceeds 7.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

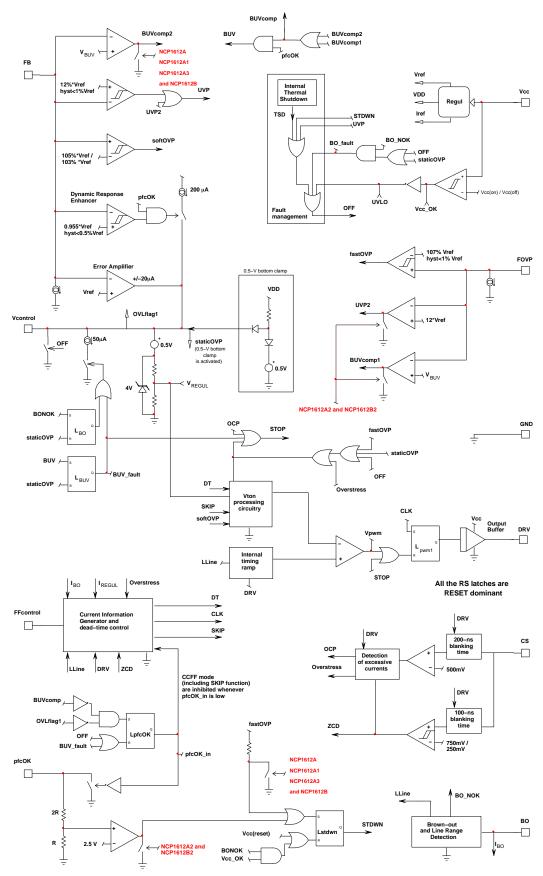

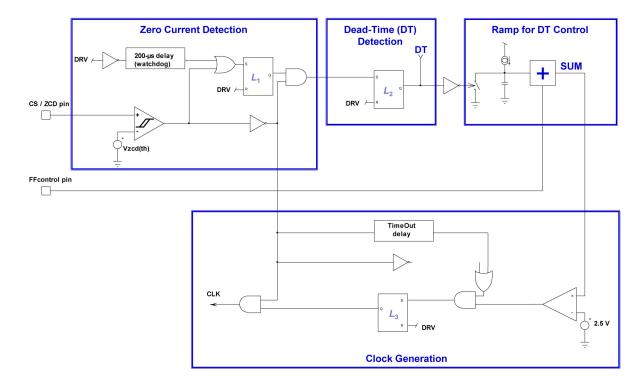

Figure 4. Block Diagram

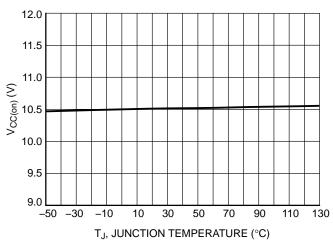

Figure 5. Start-up Threshold, V<sub>CC</sub> Increasing (V<sub>CC(on)</sub>) vs. Temperature (A, A1, A2 and A3 Versions)

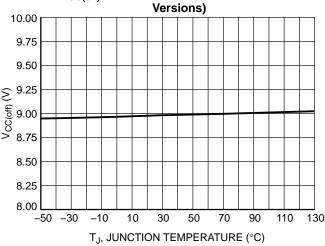

Figure 7.  $V_{CC}$  Minimum Operating Voltage,  $V_{CC}$  Falling ( $V_{CC(off)}$ ) vs. Temperature

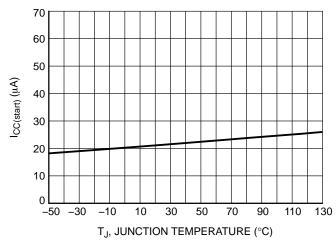

Figure 9. Start-up Current @ V<sub>CC</sub> = 9.4 V vs. Temperature

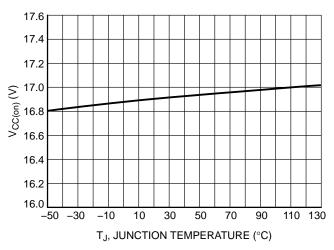

Figure 6. Start-up Threshold, V<sub>CC</sub> Increasing (V<sub>CC(on)</sub>) vs. Temperature (B and B2 Versions)

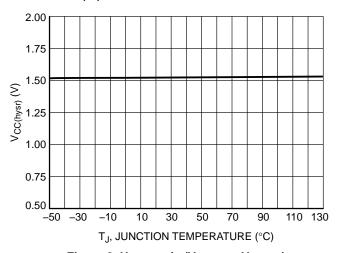

Figure 8. Hysteresis ( $V_{CC(on)} - V_{CC(off)}$ ) vs. Temperature (A, A1, A2 and A3 Versions)

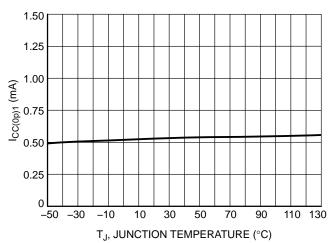

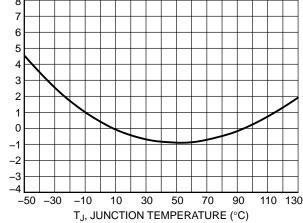

Figure 10. Operating Current, No Switching (V<sub>SENSE</sub> Grounded) vs. Temperature

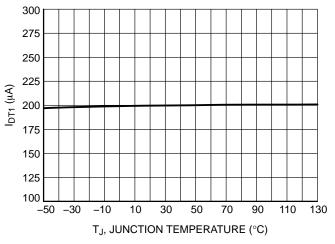

Figure 11. FFcontrol Pin Current, V<sub>SENSE</sub> = 1.4 V and V<sub>CONTROL</sub> Maximum vs. Temperature

Figure 13. Dead-time, V<sub>FFcontrol</sub> = 1.75 V vs. Temperature

Figure 15. FFcontrol Pin Skip Level (V<sub>FFcontrol</sub> Rising) vs. Temperature

Figure 12. FFcontrol Pin Current, V<sub>SENSE</sub> = 2.8 V and V<sub>CONTROL</sub> Maximum vs. Temperature

Figure 14. Dead-time, V<sub>FFcontrol</sub> = 1.00 V vs. Temperature

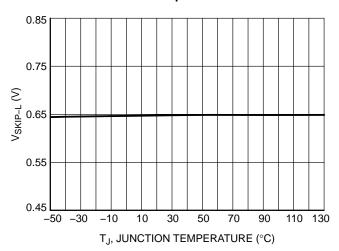

Figure 16. FFcontrol Pin Skip Level (V<sub>FFcontrol</sub> Falling) vs. Temperature

### **TYPICAL CHARACTERISTICS**

70

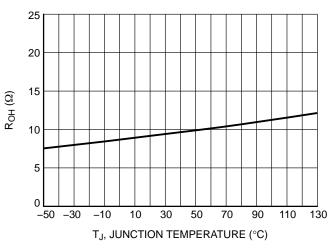

Figure 17. DRV Source Resistance vs. Temperature

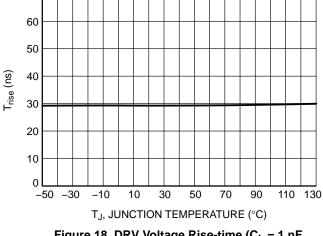

Figure 18. DRV Voltage Rise-time ( $C_L = 1 \text{ nF}$ , 10-90% of Output Signal) vs. Temperature

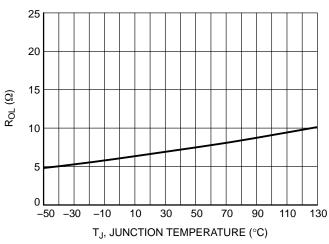

Figure 19. DRV Sink Resistance vs. Temperature

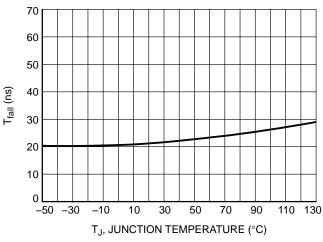

Figure 20. DRV Voltage Fall-time ( $C_L = 1 \text{ nF}$ , 10–90% of Output Signal) vs. Temperature

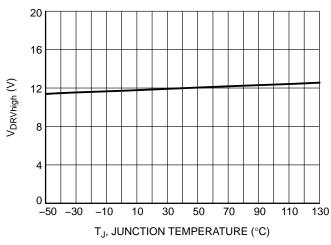

Figure 21. DRV Pin Level @  $V_{CC}$  = 35 V (R<sub>L</sub> = 33 k $\Omega$ , C<sub>L</sub> = 1 nF) vs. Temperature

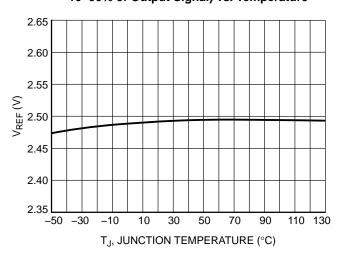

Figure 22. Feedback Reference Voltage vs. Temperature

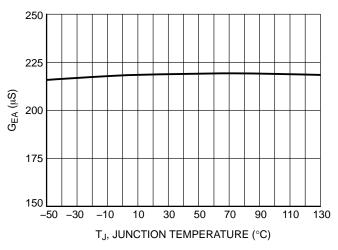

Figure 23. Error Amplifier Transconductance

Gain vs. Temperature

Figure 25. Ratio (V<sub>OUT</sub> Low Detect Hysteresis / V<sub>REF</sub>) vs. Temperature

Figure 27. Current Sense Voltage Threshold vs. Temperature

Figure 24. Ratio (V<sub>OUT</sub> Low Detect Threshold / V<sub>RFF</sub>) vs. Temperature

Figure 26. V<sub>CONTROL</sub> Source Current when (V<sub>OUT</sub> Low Detect) is Activated for Dynamic Response Enhancer (DRE) vs. Temperature

Figure 28. Over-current Protection Leading Edge Blanking vs. Temperature

Figure 29. "Overstress" Protection Leading Edge Blanking vs. Temperature

Figure 30. Over-current Protection Delay from  $V_{CS/ZCD} > V_{CS(th)}$  to DRV Low ( $dV_{CS/ZCD}$  /  $dt = 10 \text{ V/}\mu\text{s}$ ) vs. Temperature

Figure 31. Zero Current Detection, V<sub>CS/ZCD</sub> Rising vs. Temperature

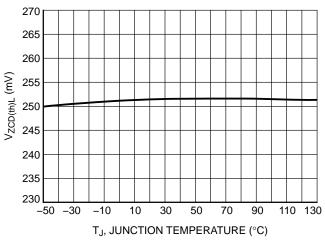

Figure 32. Zero Current Detection, V<sub>CS/ZCD</sub> Falling vs. Temperature

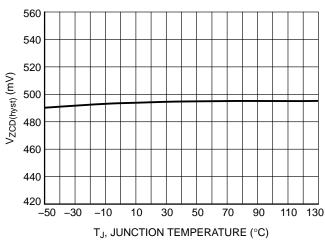

Figure 33. Hysteresis of the Zero Current Detection Comparator vs. Temperature

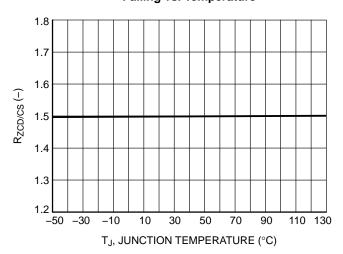

Figure 34. V<sub>ZCD(th)</sub> over V<sub>CS(th)</sub> Ratio vs. Temperature

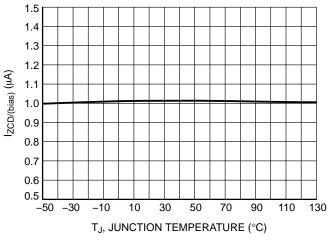

Figure 35. CS/ZCD Pin Bias Current @ V<sub>CS/ZCD</sub> = 0.75 V vs. Temperature

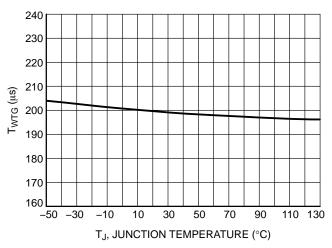

Figure 36. Watchdog Timer vs. Temperature

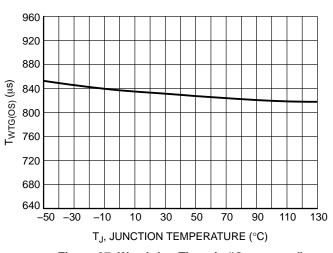

Figure 37. Watchdog Timer in "Overstress" Situation vs. Temperature

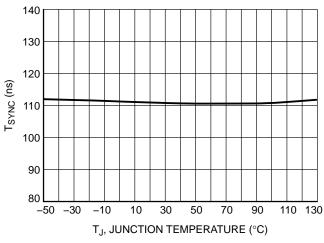

Figure 38. Minimum ZCD Pulse Width for ZCD Detection vs. Temperature

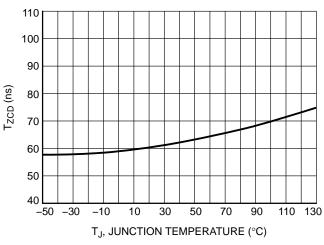

Figure 39. ((V<sub>CS/ZCD</sub> < V<sub>ZCD(th)</sub>) to DRV High) Delay vs. Temperature

Figure 40. Timeout Timer vs. Temperature

Figure 41. Maximum On Time @ V<sub>SENSE</sub> = 1.4 V vs. Temperature

Figure 42. Maximum On Time @ V<sub>SENSE</sub> = 2.8 V vs. Temperature

Figure 43. Minimum On Time @ V<sub>SENSE</sub> = 1.4 V vs. Temperature

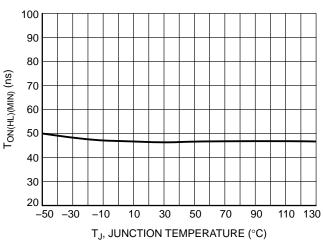

Figure 44. Minimum On Time @ V<sub>SENSE</sub> = 2.8 V vs. Temperature

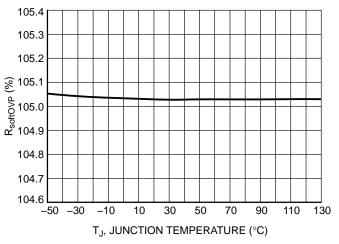

Figure 45. Ratio (Soft OVP Threshold, V<sub>FB</sub> Rising) over V<sub>REF</sub> vs. Temperature

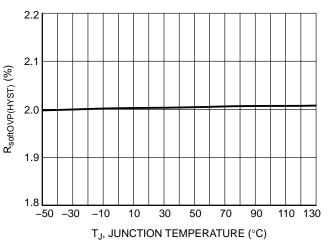

Figure 46. Ratio (Soft OVP Hysteresis) over V<sub>REF</sub> vs. Temperature

### **TYPICAL CHARACTERISTICS**

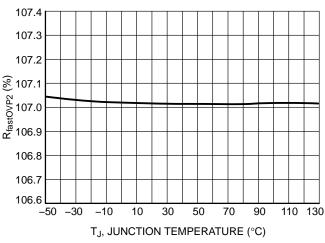

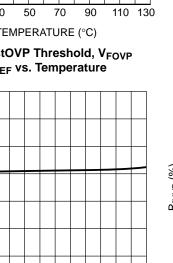

Figure 47. Ratio (fastOVP Threshold, V<sub>FOVP</sub> Rising) over V<sub>REF</sub> vs. Temperature

290

270

250

230

210

190

170 150

-50 -30

T<sub>J</sub>, JUNCTION TEMPERATURE (°C) Figure 49. Feedback Pin Bias Current @ VFB = **V<sub>UVP</sub> vs. Temperature**

50

70

90

110

130

30

Figure 51. Ratio (UVP Hysteresis) over V<sub>REF</sub> vs. Temperature

Figure 48. Feedback Pin Bias Current @ VFB = V<sub>OVP</sub> vs. Temperature

Figure 50. Ratio (UVP Threshold, VFB Rising) over V<sub>REF</sub> vs. Temperature

Figure 52. Brown-out Threshold, V<sub>SENSE</sub> Rising vs. Temperature

Figure 53. Brown-out Threshold, V<sub>SENSE</sub> Falling vs. Temperature

Figure 54. Brown-out Comparator Hysteresis vs. Temperature

Figure 55. Brown-out Blanking Time vs. Temperature

Figure 56. V<sub>CONTROL</sub> Pin Sink Current when a Brown-out Situation is Detected vs.

Temperature

Figure 57. Comparator Threshold for Line Range Detection, V<sub>SENSE</sub> Rising vs. Temperature

Figure 58. Comparator Threshold for Line Range Detection, V<sub>SENSE</sub> Falling vs.

Temperature

### TYPICAL CHARACTERISTICS

Figure 60. Brown-out Pin Bias Current, (V<sub>SENSE</sub> = V<sub>BOH</sub>) vs. Temperature

### **DETAILED OPERATING DESCRIPTION**

### Introduction

The NCP1612 is designed to optimize the efficiency of your PFC stage throughout the load range. In addition, it incorporates protection features for rugged operation. More generally, the NCP1612 is ideal in systems where cost-effectiveness, reliability, low stand-by power and high efficiency are the key requirements:

- Current Controlled Frequency Fold-back: the NCP1612 is designed to drive PFC boost stages in so-called Current Controlled Frequency Fold-back (CCFF). In this mode, the circuit classically operates in Critical conduction Mode (CrM) when the inductor current exceeds a programmable value. When the current is below this preset level, the NCP1612 linearly reduces the frequency down to about 20 kHz when the current is zero. CCFF maximizes the efficiency at both nominal and light load. In particular, stand-by losses are reduced to a minimum. Similarly to FCCrM controllers, an internal circuitry allows near-unity power factor even when the switching frequency is reduced.

- Skip Mode: to further optimize the efficiency, the circuit skips cycles near the line zero crossing when the current is very low. This is to avoid circuit operation when the power transfer is particularly inefficient at the cost of current distortion. When superior power factor is required, this function can be inhibited by offsetting the "FFcontrol" pin by 0.75 V.

- Low Start-up Current and large V<sub>CC</sub> range (B and B2 versions): The consumption of the circuit is minimized to allow the use of high-impedance start-up resistors to pre-charge the V<sub>CC</sub> capacitor. Also, the minimum value of the UVLO hysteresis is 6 V to avoid the need for large V<sub>CC</sub> capacitors and help shorten the start-up time without the need for too dissipative start-up elements. The A, A1, A2 and A3 versions are preferred in applications where the circuit is fed by an external power source (from an

- auxiliary power supply or from the downstream converter). Their maximum start-up level (11.25 V) is set low enough so that the circuit can be powered from a 12 V rail. After start-up, the high  $V_{CC}$  maximum rating allows a large operating range from 9.5 V up to 35 V.

- pfcOK signal: the pfcOK pin is to disable/enable the downstream converter. Grounded until the PFC output has reached its nominal level and whenever the NCP1612 detects a fault, it is in high-impedance when the PFC stage outputs the nominal bulk voltage. In addition, with the A, A1, A3 and B versions, the circuit latches off if a voltage exceeding 7.5 V is applied to pin 10.

- Fast Line/Load Transient Compensation (Dynamic Response Enhancer): since PFC stages exhibit low loop bandwidth, abrupt changes in the load or input voltage (e.g., at start-up) may cause excessive over- or under-shoot. This circuit limits possible deviations from the regulation level as follows:

- The Soft Over-Voltage Protection contains the output voltage when it tends to become excessive.

- The NCP1612 dramatically speeds-up the regulation loop when the output voltage goes below 95.5 % of its regulation level. In the versions targeting applications where V<sub>CC</sub> is supplied by an external power supply or the downstream converter (A, A1, A2 and A3), this function is disabled until the PFC stage having started-up, pfcOK is in high state. This is to take benefit from the soft-start effect offered by the V<sub>CONTROL</sub> pin gradual charge.

- Safety Protections: the NCP1612 permanently monitors

the input and output voltages, the MOSFET current and

the die temperature to protect the system from possible

over-stress making the PFC stage extremely robust and

reliable. In addition to the OVP protection, these methods

of protection are provided:

- Maximum Current Limit: the circuit senses the MOSFET current and turns off the power switch if the set current limit is exceeded. In addition, the circuit enters a low duty-cycle operation mode when the current reaches 150% of the current limit as a result of the inductor saturation or a short of the bypass diode.

- Under-Voltage Protection: this circuit turns off when it detects that the output voltage is below 12% of the voltage reference (typically). This feature protects the PFC stage if the ac line is too low or if there is a failure in the feedback network (e.g., bad connection).

- Fast Over-Voltage Detection (Fast OVP): the FOVP pin provides a redundant protection in the case of an excessive output voltage level. Note that with the NCP1612A2 and NCP1612B2 versions, the fast OVP latches off the circuit.

- Bulk Under-Voltage Detection (BUV): The BUV function is implemented to prevent the downstream converter from operating when the buck voltage is too low. Practically, the BUV comparator monitors the FOVP pin (NCP1612A, NCP1612A1, NCP1612A3 and NCP1612B) or the FB pin (NCP1612A2, NCP1612B2) to disable the driver, gradually discharge the control pin and ground the

- pfcOK pin when the sensed voltage drops below the BUV threshold (40% of the 2.5 V reference voltage with the A1/A3 version, 76% with the other versions). The BUV function has no action whenever the pfcOK pin is in low state.

- Brown-Out Detection: the circuit detects low ac line conditions and stops operation thus protecting the PFC stage from excessive stress.

- Thermal Shutdown: an internal thermal circuitry disables the gate drive when the junction temperature exceeds 150°C (typically). The circuit resumes operation once the temperature drops below approximately 100°C (50°C hysteresis).

- Output Stage Totem Pole: the NCP1612 incorporates a -0.5 A/+0.8 A gate driver to efficiently drive most TO220 or TO247 power MOSFETs.

### **NCP1612 Operation Modes**

As mentioned, the NCP1612 PFC controller implements a *Current Controlled Frequency Fold-back (CCFF)* where:

- The circuit operates in classical *Cr*itical conduction *M*ode (*CrM*) when the inductor current exceeds a programmable value.

- When the current is below this preset level, the NCP1612 linearly reduces the operating frequency down to about 20 kHz when the current is zero.

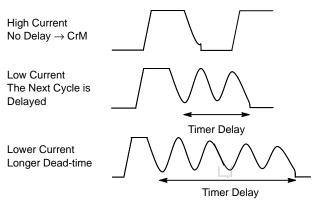

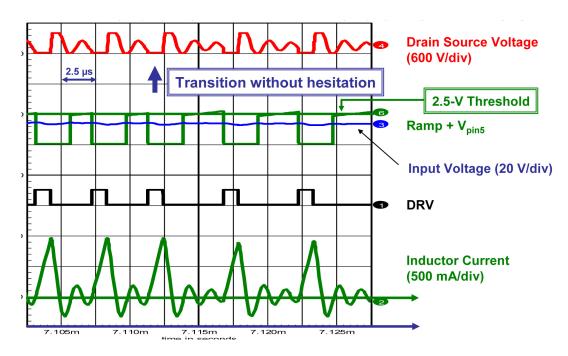

Figure 61. CCFF Operation

As illustrated in Figure 61, under high load conditions, the boost stage is operating in CrM but as the load is reduced, the controller enters controlled frequency discontinuous operation.

Figure 62 details the operation. A voltage representative of the input current ("current information") is generated. If this signal is higher than a 2.5 V internal reference (named "Dead-time Ramp Threshold" in Figure 62), there is no dead-time and the circuit operates in CrM. If the current information is lower than the 2.5 V threshold, a dead-time is inserted that lasts for the time necessary for the internal ramp to reach 2.5 V from the current information floor. Hence, the lower the current information is, the longer the dead-time. For all versions except NCP1612A3, the maximum dead-time is

approximately 48.5  $\mu$ s when the current information is 0.65 V typically. The NCP1612A3 limits the maximum dead-time to 41.5  $\mu$ s typically when the current information is 0.90 V typically. In both cases, if the current information further decreases, the circuit enters skip mode (see next section).

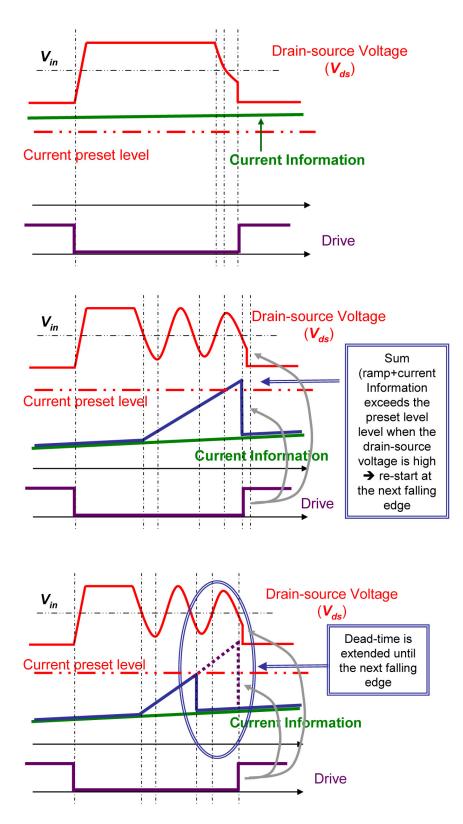

To further reduce the losses, the MOSFET turns on is stretched until its drain-source voltage is at its valley. As illustrated in Figure 62, the ramp is synchronized to the drain-source ringing. If the ramp exceeds the 2.5 V threshold while the drain-source voltage is below  $V_{in}$ , the ramp is extended until it oscillates above  $V_{in}$  so that the drive will turn on at the next valley.

<u>Top:</u> CrM operation when the current information exceeds the preset level during the demagnetization phase <u>Middle:</u> the circuit re-starts at the next valley if the sum (ramp + current information) exceeds the preset level during the dead-time, while the drain-source voltage is high

<u>Bottom:</u> the sum (ramp + current information) exceeds the preset level while during the dead-time, the drain-source voltage is low. The circuit skips the current valley and re-starts at the following one.

Figure 62. Dead-Time generation

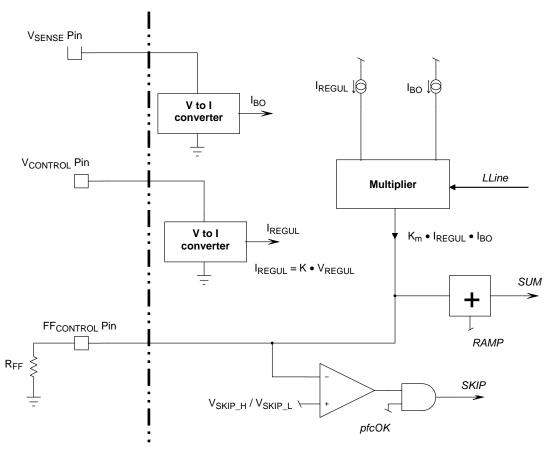

### **Current Information Generation**

The "FFcontrol" pin sources a current that is representative of the input current. In practice,  $I_{pin5}$  is built by multiplying the internal control signal ( $V_{REGUL}$ , i.e., the internal signal that controls the on-time) by the sense voltage (pin 4) that is proportional to the input voltage. The

multiplier gain ( $K_m$  of Figure 63) is three times less in high-line conditions (that is when the "LLine" signal from the brown-out block is in low state) so that  $I_{pin5}$  provides a voltage representative of the input current across resistor  $R_{FF}$  placed between pin 5 and ground. Pin 5 voltage is the current information.

Figure 63. Generation of the Current Information

### Skip Mode

As illustrated in Figure 63, the circuit also skips cycles near the line zero crossing where the current is very low. A comparator monitors the pin 5 voltage ("FFcontrol" voltage) and inhibits the switching operation when *Vpin5* is lower than V<sub>SKIP\_L</sub> (0.90 V typically for the NCP1612A3, 0.65 V for the other versions). Switching resumes when *Vpin5* exceeds V<sub>SKIP\_H</sub> (1 V typically for the NCP1612A3, 0.75 V for the other versions). This function prevents circuit operation when the power transfer is particularly inefficient at the expense of slightly increased current distortion. When superior power factor is needed, this function can be

inhibited offsetting the "FFcontrol" pin by a voltage higher than  $V_{SKIP\_H}$ . The skip mode capability is disabled whenever the PFC stage is not in nominal operation (as dictated by the "pfcOK" signal – see block diagram and "pfcOK Internal Signal" Section).

The circuit does not abruptly interrupt the switching when *Vpin5* goes below V<sub>SKIP\_L</sub>. Instead, the signal *VTON* that controls the on-time is gradually decreased by grounding the *VREGUL* signal applied to the *VTON* processing block (see Figure 68). Doing so, the on-time smoothly decays to zero in 3 to 4 switching periods typically. Figure 64 shows the practical implementation.

Figure 64. CCFF Practical Implementation

CCFF maximizes the efficiency at both nominal and light load. In particular, the stand-by losses are reduced to a minimum. Also, this method avoids that the system stalls between valleys. Instead, the circuit acts so that the PFC

stage transitions from the n valley to (n + 1) valley or vice versa from the n valley to (n - 1) cleanly as illustrated by Figure 65.

Figure 65. Clean Transition Without Hesitation Between Valleys

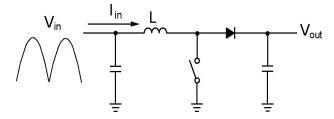

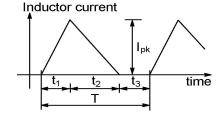

### NCP1612 On-time Modulation

Let's analyze the ac line current absorbed by the PFC boost stage. The initial inductor current at the beginning of each switching cycle is always zero. The coil current ramps up when the MOSFET is on. The slope is  $(V_{IN}/L)$  where L is the coil inductance. At the end of the on-time  $(t_1)$ , the inductor starts to demagnetize. The inductor current ramps down until it reaches zero. The duration of this phase is  $(t_2)$ . In some cases, the system enters then the dead-time  $(t_3)$  that

lasts until the next clock is generated.

One can show that the ac line current is given by:

$$I_{in} = V_{in} \left[ \frac{t_1(t_1 + t_2)}{2TL} \right]$$

(eq. 1)

Where  $T = (t_1 + t_2 + t_3)$  is the switching period and  $V_{in}$  is the ac line rectified voltage.

In light of this equation, we immediately note that  $I_{in}$  is proportional to  $V_{in}$  if  $[t_1(t_1 + t_2) / T]$  is a constant.

Figure 66. PFC Boost Converter (left) and Inductor Current in DCM (right)

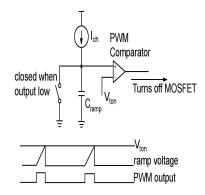

The NCP1612 operates in voltage mode. As portrayed by Figure 67, the MOSFET on-time  $t_1$  is controlled by the signal V<sub>ton</sub> generated by the regulation block and an internal ramp as follows:

$$t_1 = \frac{C_{ramp} \cdot V_{ton}}{I_{ch}}$$

(eq. 2)

The charge current is constant at a given input voltage (as mentioned, it is three times higher at high line compared to its value at low line).  $C_{ramp}$  is an internal capacitor.

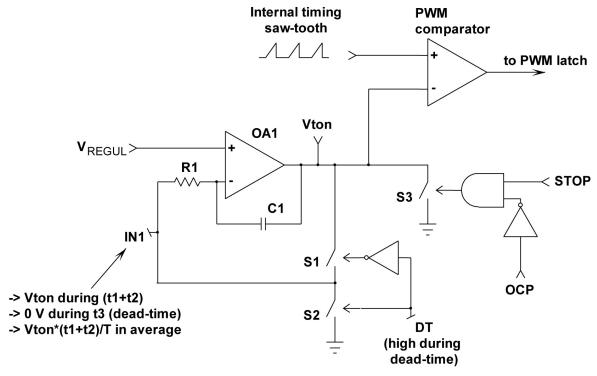

The output of the regulation block  $(V_{CONTROL})$  is linearly transformed into a signal (V<sub>REGUL</sub>) varying between 0 and 1 V.  $(V_{REGUL})$  is the voltage that is injected into the PWM section to modulate the MOSFET duty-cycle. The NCP1612 includes some circuitry that processes ( $V_{REGUL}$ ) to form the signal (Vton) that is used in the PWM section (see Figure 68). (V<sub>ton</sub>) is modulated in response to the dead-time sensed during the precedent current cycles, that is, for a proper shaping of the ac line current. This modulation leads to:

$$V_{ton} = \frac{T \cdot V_{REGUL}}{t_1 + t_2}$$

(eq. 3)

or

$$V_{ton} \cdot \frac{t_1 + t_2}{T} = V_{REGUL}$$

Given the low regulation bandwidth of the PFC systems,  $(V_{CONTROL})$  and then  $(V_{REGUL})$  are slow varying signals. Hence, the  $(V_{ton} \times (t_1 + t_2)/T)$  term is substantially constant. Provided that in addition,  $(t_1)$  is proportional to  $(V_{ton})$ , Equation 1 leads to: , where k is a constant. More exactly:

$$I_{in} = k \cdot V_{in}$$

where:

$$k = constant = \left[ \frac{1}{2L} \cdot \frac{V_{REGUL}}{(V_{REGUL})_{max}} \cdot t_{on,max} \right]$$

Where  $t_{on,max}$  is the maximum on-time obtained when  $V_{REGUL}$  is at its  $(V_{REGUL})_{max}$  maximum level. The parametric table shows that  $t_{on,max}$  is equal to 25 µs  $(T_{ON(LL)})$  at low line and to 8.5  $\mu s$   $(T_{ON(HL)})$  at high line (when pin4 happens to exceeds 1.8 V with a pace higher than 40 Hz - see BO 25 ms blanking time).

Hence, we can re-write the above equation as follows:

$$I_{in} = \frac{V_{in} \cdot T_{ON(LL)}}{2 \cdot L} \cdot \frac{V_{REGUL}}{(V_{REGUL}) \max}$$

at low line.

$$I_{in} = \frac{V_{in} \cdot T_{ON(HL)}}{2 \cdot L} \cdot \frac{V_{REGUL}}{(V_{REGUL}) max}$$

at high line.

From these equations, we can deduce the expression of the average input power:

$$P_{in,avg} = \frac{\left(V_{in,rms}\right)^2 \cdot V_{REGUL} \cdot T_{ON(LL)}}{2 \cdot L \cdot \left(V_{REGUL}\right)}$$

at low line.

$$P_{in,avg} = \frac{\left(V_{in,rms}\right)^2 \cdot V_{REGUL} \cdot T_{ON(HL)}}{2 \cdot L \cdot \left(V_{REGUL}\right)_{max}}$$

at high line.

Where  $(V_{REGUL})_{max}$  is the  $V_{REGUL}$  maximum value.

Hence, the maximum power that can be delivered by the PFC stage is:

$$(P_{in,avg})_{max} = \frac{(V_{in,rms})^2 \cdot T_{ON(LL)}}{2 \cdot L}$$

at low line.

$$(P_{in,avg})_{max} = \frac{(V_{in,ms})^2 \cdot T_{ON(HL)}}{2 \cdot I}$$

at high line.

The input current is then proportional to the input voltage. Hence, the ac line current is properly shaped.

One can note that this analysis is also valid in the CrM case. This condition is just a particular case of this functioning where  $(t_3 = 0)$ , which leads to  $(t_1 + t_2 = T)$  and  $(V_{TON} = V_{REGUL})$ . That is why the NCP1612 automatically

adapts to the conditions and transitions from DCM and CrM (and vice versa) without power factor degradation and without discontinuity in the power delivery.

Figure 67. PWM circuit and timing diagram.

Figure 68.  $V_{TON}$  Processing Circuit. The integrator OA1 amplifies the error between  $V_{REGUL}$  and IN1 so that on average,  $(V_{TON}^* (t_1+t_2)/T)$  equates  $V_{REGUL}$ .

### Remark:

The " $V_{ton}$  processing circuit" is "informed" when a condition possibly leading to a long interruption of the drive activity (functions generating the STOP signal that disables the drive – see block diagram – except OCP, i.e., BUV\_fault, OVP, OverStress, SKIP, staticOVP and OFF). Otherwise, such situations would be viewed as a normal dead-time phase and  $V_{ton}$  would inappropriately over-dimension  $V_{ton}$  to compensate it. Instead, as illustrated in Figure 68, the  $V_{ton}$  signal is grounded leading to a short soft-start when the circuit recovers.

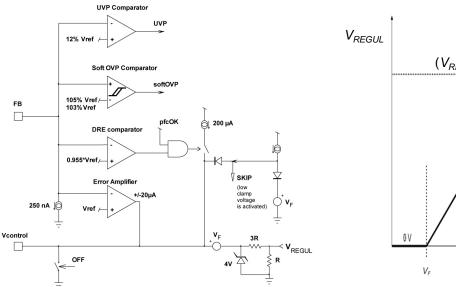

### **Regulation Block and Low Output Voltage Detection**

A trans-conductance error amplifier (OTA) with access to the inverting input and output is provided. It features a typical trans-conductance gain of 200  $\mu S$  and a maximum capability of  $\pm 20~\mu A$ . The output voltage of the PFC stage is typically scaled down by a resistors divider and monitored by the inverting input (pin 2). Bias current is minimized (less than 500 nA) to allow the use of a high impedance feed-back network. However, it is high enough so that the pin remains in low state if the pin is not connected.

The output of the error amplifier is brought to pin 3 for external loop compensation. Typically a type–2 network is applied between pin 3 and ground, to set the regulation bandwidth below about 20 Hz and to provide a decent phase boost.

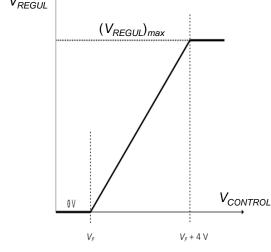

The swing of the error amplifier output is limited within an accurate range:

- It is forced above a voltage drop  $(V_F)$  by some circuitry.

- It is clamped not to exceed 4.0 V + the same *V<sub>F</sub>* voltage drop.

Hence,  $V_{pin3}$  features a 4 V voltage swing.  $V_{pin3}$  is then offset down by  $(V_F)$  and scaled down by a resistors divider before it connects to the " $V_{TON}$  processing block" and the PWM section. Finally, the output of the regulation block is a signal (" $V_{REGUL}$ " of the block diagram) that varies between 0 and a top value corresponding to the maximum on-time.

The  $V_F$  value is 0.5 V typically.

Figure 69. a) Regulation Block Figure (left), b) Correspondence between V<sub>CONTROL</sub> and V<sub>REGUL</sub> (right)

Given the low bandwidth of the regulation loop, abrupt variations of the load, may result in excessive over or under-shoots. Over-shoot is limited by the soft Over-voltage Protection (OVP) connected to the feedback pin or the fast OVP of pin1.

The NCP1612 embeds a "dynamic response enhancer" circuitry (DRE) that contains under-shoots. An internal comparator monitors the feed-back ( $V_{pin1}$ ) and when  $V_{pin2}$  is lower than 95.5% of its nominal value, it connects a 200  $\mu$ A current source to speed-up the charge of the compensation network. Effectively this appears as a 10x increase in the loop gain.

In the A, A1, A2 and A3 versions, DRE is disabled during the start-up sequence until the PFC stage has stabilized (that is when the "pfcOK" signal of the block diagram, is high). The resulting slow and gradual charge of the pin 3 voltage ( $V_{CONTROL}$ ) softens the soft start-up sequence. In the B and B2 versions, DRE is enabled during start-up to speed-up this phase and allow for the use of smaller  $V_{CC}$  capacitors.

The circuit also detects overshoot and immediately reduces the power delivery when the output voltage exceeds 105% of its desired level. The NCP1612 does not abruptly interrupt the switching. Instead, the signal  $V_{TON}$  that

controls the on-time is gradually decreased by grounding the  $V_{REGUL}$  signal applied to the  $V_{TON}$  processing block (see Figure 68). Doing so, the on-time smoothly decays to zero in 4 to 5 switching periods typically. If the output voltage still increases, the fast OVP comparator immediately disables the driver if the output voltage exceeds 108.5% of its desired level.

The error amplifier OTA and the soft OVP, UVP and DRE comparators share the same input information. Based on the typical value of their parameters and if (V<sub>out,nom</sub>) is the output voltage nominal value (e.g., 390 V), we can deduce:

- Output Regulation Level: V<sub>out,nom</sub>

- Output Soft OVP Level:  $V_{out,sovp} = 105\% \times V_{out,nom}$

- Output UVP Level:  $V_{out,uvp} = 12\% \times V_{out,nom}$

- Output DRE Level:  $V_{out,dre} = 95.5\% \times V_{out,nom}$

### Fast OVP and Bulk Under-Voltage (BUV)

These functions check that the output voltage is within the proper window:

The fast Over-Voltage Protection trips if the bulk voltage reaches abnormal levels. When the feedback network is properly designed and correctly connected,

the bulk voltage cannot exceed the level set by the soft OVP function ( $V_{out,sovp} = 105\% \times V_{out,nom}$ , see precedent section). This second protection offers some redundancy for a higher safety level. The FOVP threshold is set 2% higher than the soft OVP comparator reference so that the same portion of the output voltage can be applied to both the FOVP/BUV and feedback input pins (pins 1 and 2). Note that the versions A, A1, A3 and B only interrupt the DRV activity until the FOVP pin voltage drops below the fast OVP threshold (1% hysteresis). Versions A2 and B2 latch off the circuit when the fast OVP trips.