#### **FEATURES**

- Standard MityDSP-Pro SO-DIMM-200 Interface

- RS-232 Serial Interface

- USB Interface

- 1.2/2.0 Compatible

- 6 MBit Link Speed

- Windows Drivers Available

- Two 10/100 MBit Ethernet Interfaces

- One FPGA core based

- One DSP EMAC based

- 5 High Speed LVDS Pairs

- Supports Quarter VGA Interface

- Camera Link Interface

- 16/20-bit per pixel support

- 8 On-Board Digital to Analog Converters

- 12 Bit resolution

- 1 µs settling time

- 8 On-Board Analog to Digital Converters

- 12 Bit resolution

- 200 Ksps sample rate

- On-board Real Time Clock

- Four MDK-4 Daughter Card Expansion Slots

- Four MDK-8 Daughter Card Expansion Slots

#### **APPLICATIONS**

- MityDSP-Pro Evaluation

- Embedded Instrumentation

- Rapid Prototyping

- Control Processing

- Remote Sensing

- Embedded Signal Processing

#### DESCRIPTION

The MityDSP-Pro Development Kit Motherboard (MDK-Pro-MB) provides a low-cost target platform for integration and development using the MityDSP-Pro based family of Processor Cards. The MDK-Pro-MB includes on board RS-232, 10/100 MBit Ethernet and Universal Serial Bus (USB) communications interfaces. For basic data acquisition and control, an 8 channel 12-bit DAC and an 8 channel 12-bit ADC is included. For display, an LVDS link connection to an off-board quarter VGA (QGVA) display controller with backlight driver is provided. A Camera Link interface is also provided.

In addition to the on-board I/O interfaces, the MDK-Pro-MB provides interfaces for four MDK-8 and four MDK-4 form factor daughter card sites for system expansion. The daughter card sites are laid out to also allow the use of MDK-12, MDK-16, and MDK-24 size daughter cards by combining card slots as described in the Daughter Card Configuration section, below. The MDK daughter cards allow customization of the system card based on the application. Users may select from several off-the-shelf cards available from Critical Link or design their own based on their specific requirements.

The MDK-Pro-MB includes on board voltage regulation for providing power digital and analog circuits. The card requires a power supply capable of providing a nominal +9 to +18 Volts DC. Input power can be supplied via the 2-pin 0.156" Molex header, or a standard barrel-style power jack.

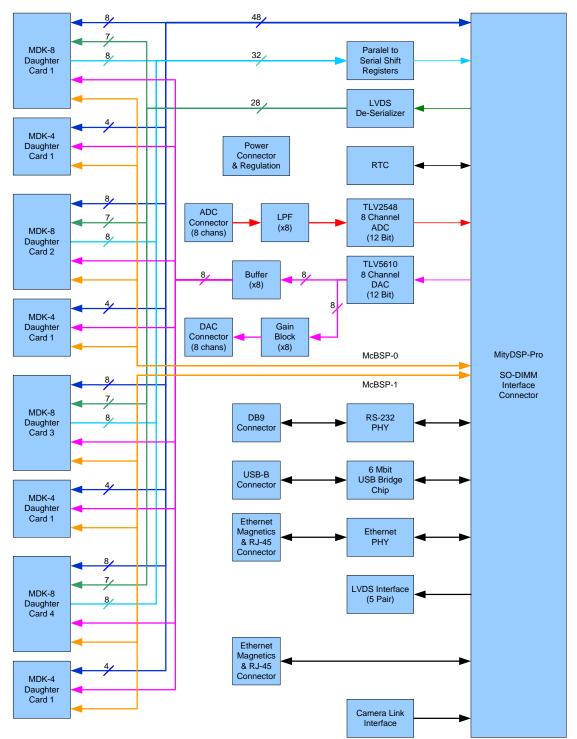

A block diagram of the MDK-Pro-MB is illustrated in Figure 1. All available FPGA I/O lines and the two C645x McBSP ports are either used directly by the MDK-Pro-MB or are routed to the MDK daughter card sites. Control of the on-board interface hardware and connected daughter cards require proper configuration of the MityDSP-Pro FPGA and DSP. While not required, it is strongly recommended that the MityDSP software and firmware development kit and supplied API be used to manage these interfaces.

Figure 1: MityDSP-Pro Development Kit Block Diagram

### **RS-232 Interface Description**

The on-board RS-232 level driver and DB-9 connector provides standard serial interface at data rates up to 115,200 baud. The serial interface is routed to the primary MityDSP-Pro serial bootloading port in order to allow remote code download and FLASH upgrades on an attached MityDSP-Pro from this connector.

### **USB Interface Description**

The on-board USB interface leverages a serial UART to USB 2.0 compliant bridge chip that supports data rates up to 6 Mbits per second. Drivers for the USB interface are provided with the MityDSP software development kit and are compatible with Windows XP, 2000, and Vista. The USB serial interface is routed to the alternate MityDSP-Pro serial bootloading port in order to allow remote code download and FLASH upgrades on an attached MityDSP-Pro from this connector.

## **Ethernet Interfaces Description**

The on-board Ethernet interface features a network PHY capable of running at 10/100 Mbit including link auto-negotiation and MII/MDIO capability. An industry standard RJ-45 connector is provided for an external connection. Use of the Ethernet interface requires an Ethernet Media Access Controller (MAC) implementation in the MityDSP-Pro FPGA. The MityDSP hardware and software development kit includes a fully tested Ethernet MAC as well as an implementation of the LwIP TCP/IP stack, providing a full Ethernet capable platform ready for integration. This Ethernet interface may be used to perform remote code download and FLASH upgrades on an attached MityDSP-Pro.

Also included on-board is a second Ethernet interface connector that is wired directly to the MityDSP-Pro's Ethernet PHY device. This PHY device is connected to the DSP's on-chip Ethernet MAC, and is capable of 10/100 Mbit operation. Support for this interface is included starting with MDK 2.7.0. Remote code download via this interface is supported by the bootloader, though it is only activated if an Ethernet MAC core is not found in the bootloader FPGA.

The DSP's on-chip MAC is actually capable of Gigabit operation, but this functionality requires a PHY device external to the MityDSP-Pro module (connectivity provided by its auxiliary interface connector), nor is such a PHY device included on the MityDSP-Pro motherboard.

### **LVDS Interface Description**

The MDK-Pro-MB provides a flat-ribbon cable low profile interface for five Low Voltage Differential Signaling (LVDS) pairs. The interface design is intended to support high speed off board interconnects. In addition to custom user interfacing, the pairs may be used to interface to a Quarter VGA LCD screen using the MityDSP hardware and software development kit LCD interface libraries and an appropriate daughterboard interface. Off-the-shelf display solutions for QVGA interfaces are provided by Critical Link.

### **Camera Link Interface Description**

The MDK-Pro-MB provides an interface port for connection to industry standard Camera Link compatible video sources. This feature enables the MDK-Pro-MB system to implement a Camera Link compatible frame grabber, and video processing engine. The interface carries 3-bits of sync signals plus 16-bits per pixel in any color mode, or black & white. The interface also supports Camera Link's bi-directional asynchronous serial control channel, and 4-bit uni-directional Camera Control lines.

### **DAC Description**

The MDK-Pro-MB provides an on-board 8-channel 12-bit digital to analog converter to the MityDSP-Pro's TI C645x DSP via McBSP port-1. The DAC component is the TLV5610 from Texas Instruments $^{\text{@}}$  / Burr Brown $^{\text{@}}$  and is capable of output settling times of 1  $\mu$ s.

The eight channels are routed to the external DAC connector J200, a standard dual-row, 14-pin, 0.1" pitch shrouded header. All channels provide a voltage output range of 0 to 10 Volts with respect to AGND, and are buffered to provide an output impedance of less than 300 ohms.

The eight channels are also independently buffered and routed (1 each) to the four MDK-8 and the four MDK-4 daughter card slots, and provide an output range of 0 to 4.096 Volts. Note: Use of a daughter card that requires the use an associated DAC line implies that the corresponding pin on the external DAC connector should not be used. Please refer to the data sheet for a specific daughter card in order to determine if the DAC channel is required.

For details regarding the signal interface to the MityDSP-Pro McBSP port, please refer to the MDK-Pro-MB reference schematic. The MityDSP software development kit includes an API for interfacing to the TLV5610.

## **ADC Description**

The MDK-Pro-MB provides an on-board 8-channel 12-bit analog to digital converter to the MityDSP-Pro's TI C645x DSP via McBSP port-0. The ADC component is the TLV2548 from Texas Instruments<sup>®</sup> / Burr Brown<sup>®</sup> and is capable of sampling at rates up to 200 Ksps, aggregate.

The eight input channels enter the board via a standard dual-row, 10-pin, 0.1" pitch shrouded header, J301. All input channels have an input range of 0 to 10 Volts with respect to AGND, and have an input impedance of 10k ohms. The signals are unity-gain buffered, and then low-pass filtered using a simple R/C network having a –3dB corner frequency of 48 kHz.

For details regarding the signal interface to the MityDSP-Pro McBSP port, please refer to the MDK-Pro-MB reference schematic. The MityDSP software development kit includes an API for interfacing to the TLV2548.

# **Real Time Clock Description**

The MDK-Pro-MB provides a real-time clock using an I2C device with part number M41T81SM6F. Use of the RTC requires an implementation of an I2C driver interface within the FPGA of the MityDSP-Pro. The MityDSP software development kit includes an API for interfacing to the M41T81SM6F.

For details regarding the signal interface to the MityDSP-Pro I/O pins, please refer to the MDK-Pro-MB reference schematic.

## **ABSOLUTE MAXIMUM RATINGS**

#### **OPERATING CONDITIONS**

If Military/Aerospace specified cards are required, please contact the Critical Link Sales Office or unit Distributors for availability and specifications.

Maximum Supply Voltage 19 V

Storage Temperature Range -65 to 80C

Shock, Z-Axis ±10 g

Shock, X/Y-Axis ±10 g

Ambient Temperature 0 to 55C

Range

Humidity 0 to 95%

Non-

condensing

Vibration, Z-Axis TBS Vibration, X/Y-Axis TBS

## **ELECTRICAL CHARACTERISTICS**

| Symbol                                           | Parameter                                                                                     | Conditions           | Typical           | Limit     | Units<br>(Limits)      |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------|-------------------|-----------|------------------------|

| Power Dissip                                     | <br>ation                                                                                     |                      |                   |           |                        |

| Vs                                               | Supply Voltage.                                                                               |                      | 12                | 9 / 18    | Volts<br>(Min/Max)     |

| Is                                               | Supply Current.                                                                               |                      | 0.33 <sup>1</sup> | 1.0       | Amps<br>(Max)          |

| On Board An                                      | alog To Digital Compartor                                                                     |                      |                   |           |                        |

| BW <sub>ADC</sub>                                | alog To Digital Converter  3 DB Bandwidth Analog to Digital Converter                         | R/C filtering        | 48                | _         | KHz                    |

|                                                  |                                                                                               | N/C fillefillig      |                   | TBD       | Volts                  |

| V <sub>Min,ADC</sub>                             | Minimum Analog Input Voltage  Maximum Analog Input Voltage                                    |                      | 10                | TBD       | Volts                  |

| FS <sub>ADC</sub>                                | Maximum Sample Rate. ADC                                                                      |                      | 10                | TBD       | KHz                    |

| R <sub>IN, ADC-Ex</sub> t                        | Input Impedance                                                                               |                      | 10                | 8         | KOhms<br>(Min)         |

|                                                  |                                                                                               |                      |                   |           | ,                      |

|                                                  | ital To Analog Converter                                                                      |                      |                   |           |                        |

| V <sub>Min,DAC-Ext</sub>                         | Minimum Analog Input Voltage, External DAC connection.                                        |                      | 0                 | -0.2      | Volts                  |

| V <sub>Max,DAC-Ext</sub>                         | Maximum Analog Input voltage External DAC connection.                                         |                      | 10                | 10.2      | Volts                  |

| V <sub>Min,DAC-DBC</sub>                         | Minimum Analog Input Voltage, MDK-4/8 Daughter Board DAC Interface.                           |                      | 0                 | -0.2      | Volts                  |

| V <sub>Max,DAC-DBC</sub>                         | Maximum Analog Input Voltage, MDK-4/8 Daughter Board DAC Interface.                           |                      | 4.096             | 4.3       | Volts                  |

| FSDAC                                            | Maximum Output Sample Rate, DAC                                                               |                      | 2                 | 200       | KHz                    |

| Rout DAC-Ext                                     | Output Impedance                                                                              |                      | 200               | 300       | Ohms<br>(Max)          |

| MDK 9 Digital                                    | 110                                                                                           |                      |                   |           |                        |

| MDK-8 Digital                                    |                                                                                               | 1                    | 25                | 25        | MHz                    |

| F <sub>clk,din</sub>                             | Clock Frequency, Digital Inputs                                                               |                      | 1680              | 1680      |                        |

| T <sub>update,din</sub><br>F <sub>clk,dout</sub> | Update Period, Digital Inputs  Clock Frequency, Digital Output LVDS clk entering deserializer |                      | 50                | 20 / 68   | ns<br>MHz<br>(Min/Max) |

| T <sub>update,dout</sub>                         | Update Period, Digital Outputs                                                                |                      | 20                | 14.7 / 50 | ns<br>(Min/Max)        |

| Notes:                                           | Power Supply load is dependent on Daug                                                        | hter Card configurat | ion and utiliza   | ation     |                        |

#### DAUGHTER CARD CONFIGURATION

The MDK-Pro-MB and daughter card system provides a high level of flexibility in configuration in order to maximize the use of the available MityDSP-Pro expansion pins. The daughter cards used in the MDK system are sized according to their complexity and number of required I/O pins to the MityDSP-Pro. There are several possible form factors: MDK-4, MDK-8, MDK-12, MDK-16, MDK-24, and MDK-48. The primary form factors, however, are the MDK-4 and MDK-8 configurations. All of the other factors listed are simply a combination of these card sizes.

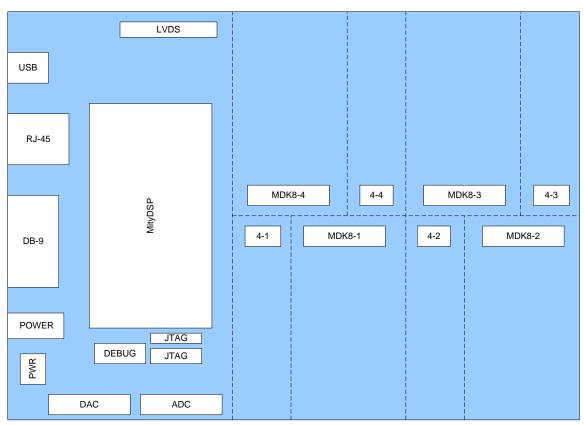

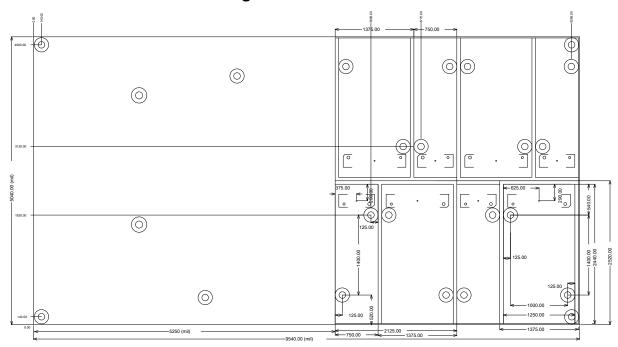

Figure 2 provides a top view of the MDK-Pro-MB circuit card and its corresponding interface connectors. In the figure, the daughter card sites are located on the right hand side of the board. The basic MDK-4 and MDK-8 card connectors are divided evenly into the top half of the card and the bottom half of the card. While this section illustrates configurations for the bottom half of the card, please note that the top half provides similar connectivity.

Figure 2: MDK-Pro-MB Connector Locations, Top View

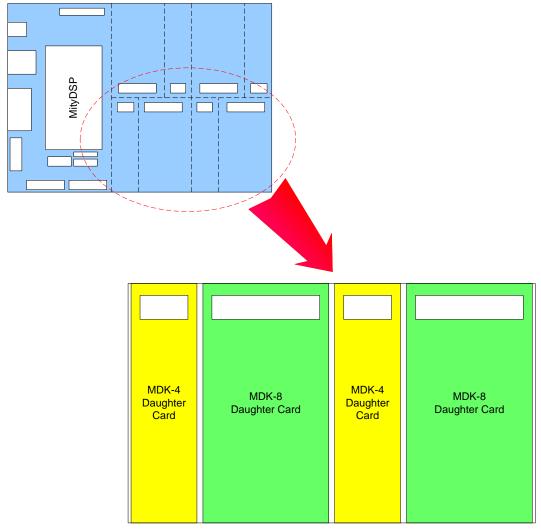

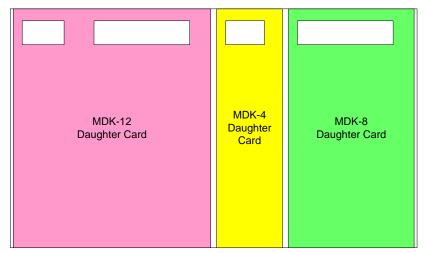

Figure 3 illustrates the bottom half of the MDK-Pro-MB daughter card expansion area using two each of the MDK-4 and MDK-8 form factor daughter cards. In this configuration, the cards are simply plugged into their corresponding connectors on the board.

Figure 3: Daughter Card Configuration, 2 MDK-4 and 2 MDK-8 Cards (Top View)

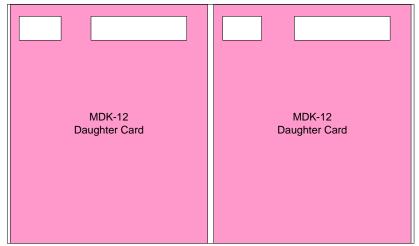

Figure 4 illustrates the use of MDK-12 form factor daughter cards, which occupy one each of the MDK-4 and MDK-8 slot connectors. As is shown in Figure 5, the MDK-12 cards may be mixed and matched with MDK-4 or MDK-8 cards in an MDK-Pro-MB configuration. Card slots may be left empty.

Figure 4: Daughter Card Configuration, 2 MDK-12 Cards (Top View)

Figure 5: Daughter Card Configuration, 1 each MDK-12, MDK-4, and MDK-8 (Top View)

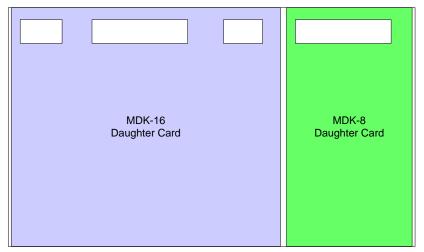

Use of an MDK-16 Daughter Card requires two MDK-4 slots and an MDK-8 slot as shown in Figure 6.

Figure 6: Daughter Card Configuration, MDK-16 and MDK-8 (Top View)

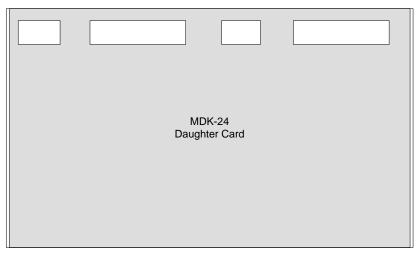

The MD-24 uses two each of the MDK-4 and MDK-8 slots as shown in Figure 7. Similarly (and not shown), an MDK-48 card would use all available slots on the MDK-Pro-MB. MDK-48 cards are typically full custom designs.

Figure 7: Daughter Card Configuration MDK-24 (Top View)

#### **ELECTRICAL INTERFACE DESCRIPTION**

#### MityDSP-Pro JTAG Interface

The DSP/FPGA JTAG connection is made directly on the MityDSP-Pro module. See the MityDSP-Pro datasheet for details.

## **Input Power**

The MDK-Pro-MB power interface, J800 or J801, requires a single +9 to +18 Volt power supply. J800 is a 2.1mm-ID, 5.5mm-OD barrel-style power jack, center-positive. J801 is a standard 2-pin, 0.156" pitch Molex locking header. The Pin-out for the power interfaces is included in Table 1.

**Table 1: Input Power Interface Pin Description**

| Signal          | J800 Position | J801 Position |

|-----------------|---------------|---------------|

| +9 to +18 Volts | Center-pin    | 1             |

| GND             | Outer-ring    | 2             |

### **Analog I/O Connectors**

The MDK-Pro-MB provides two double-row shrouded connectors for the on-board DAC circuit outputs and the on board ADC connectors. Table 2 defines the DAC external interface connectors. A cable using AMP® connector 1658621-2 (or equivalent) should be used. All channels provide a voltage output range of 0 to 10 Volts with respect to AGND, and are buffered to provide an output impedance of less than 300 ohms. Note that all DAC outputs are also shared with the MDK daughter card slots. MDK cards that require use of the DACs preclude the use of the external interface DAC channel.

Table 2: J200 On-Board DAC External Interface Connector

| Pin | Signal | Shared Slot |

|-----|--------|-------------|

| 1   | AGND   | N/A         |

| 2   | AGND   | N/A         |

| 3   | AGND   | N/A         |

| 4   | DAC_1  | MDK8-1      |

| 5   | DAC_2  | MDK8-2      |

| 6   | DAC_3  | MDK8-3      |

| 7   | DAC_4  | MDK8-4      |

| 8   | DAC_5  | MDK4-1      |

| 9   | DAC_6  | MDK4-2      |

| 10  | DAC_7  | MDK4-3      |

| 11  | DAC_8  | MDK4-4      |

| 12  | AGND   | N/A         |

| 13  | AGND   | N/A         |

| 14  | AGND   | N/A         |

Table 3 defines the ADC external interface connectors. A cable using AMP® connector 1658621-1 (or equivalent) should be used. All input channels have an input range of 0 to 10 Volts with respect to AGND, and have an input impedance of 10k ohms.

Table 3: J301 On-Board ADC External Interface Connector

| Doura ADC External mit |        |  |  |  |

|------------------------|--------|--|--|--|

| Pin                    | Signal |  |  |  |

| 1                      | AGND   |  |  |  |

| 2                      | ADC_1  |  |  |  |

| 3                      | ADC_2  |  |  |  |

| 4                      | ADC_3  |  |  |  |

| 5                      | ADC_4  |  |  |  |

| 6                      | ADC_5  |  |  |  |

| 7                      | ADC_6  |  |  |  |

| 8                      | ADC_7  |  |  |  |

| 9                      | ADC_8  |  |  |  |

| 10                     | AGND   |  |  |  |

#### **LVDS** Interface

The LVDS interface connector provides up to 5 pairs of LVDS signals connected to the Spartan 3 device on a connected MityDSP-Pro. The interface uses a standard 2 mm 24 position male header.

Table 4 defines the LVDS connector pinout. A cable using Molex® 87568-2493 connector (or equivalent) should be used. Use of the LVDS pairs as outputs will require addition of termination resistors (100 Ohm) on externally designed circuit assemblies. Use of the LVDS pairs as inputs will require population of 0603 sized termination resistors on the MDK-Pro-MB on the provided solder pads. Refer to the detailed schematic and assembly drawing for further information.

Table 4: J600 LVDS Interface Pin Description

| Pin | Signal       | Type   | Standard | Notes                                 |

|-----|--------------|--------|----------|---------------------------------------|

| 1   | +5 V         | -      | -        | 500 mA Max.                           |

| 2   | +5 V         | -      | -        | 500 mA Max.                           |

| 3   | GND          | -      | -        |                                       |

| 4   | GND          | -      | -        |                                       |

| 5   | DISP_A0_P    | I/O    | LVDS     | Display/LVDS Data channel 0           |

| 6   | DISP_A0_N    | I/O    | LVDS     | Display/LVDS Data channel 0           |

| 7   | DISP_A1_P    | I/O    | LVDS     | Display/LVDS Data channel 1           |

| 8   | DISP_A1_N    | I/O    | LVDS     | Display/LVDS Data channel 1           |

| 9   | DISP_A2_P    | I/O    | LVDS     | Display/LVDS Data channel 2           |

| 10  | DISP_A2_N    | I/O    | LVDS     | Display/LVDS Data channel 2           |

| 11  | DISP_A3_P    | I/O    | LVDS     | Display/LVDS Data channel 3           |

| 12  | DISP_A3_N    | I/O    | LVDS     | Display/LVDS Data channel 3           |

| 13  | GND          | -      | =        |                                       |

| 14  | GND          | -      | =        |                                       |

| 15  | DISP_CLKIN_P | I/O    | LVDS     | Display/LVDS Clock (or Data)          |

| 16  | DISP_CLKIN_N | I/O    | LVDS     | Display/LVDS Clock (or Data)          |

| 17  | GND          | -      | =        |                                       |

| 18  | P_SW         | I/O/PU | CMOS     | Display Aux. I/O (push-button switch) |

| 19  | DISP_I2      | I      | CMOS     | Display Touch-screen Input 2          |

| 20  | DISP_I1      | I      | CMOS     | Display Touch-screen Input 1          |

| 21  | DISP_I0      | I      | CMOS     | Display Touch-screen Input 0          |

| 22  | DISP_O2      | О      | CMOS     | Display Touch-screen Output 2         |

| 23  | DISP_O1      | О      | CMOS     | Display Touch-screen Output 1         |

| 24  | DISP_O0      | О      | CMOS     | Display Touch-screen Output 0         |

#### **Camera Link Interface**

The Camera Link interface connector provides connection to industry standard Camera Link compatible cameras or other video sources. The Camera Link standard defines this connector to be an MDR-26 connector from 3M<sup>®</sup>. As specified in the standard, Table 5 defines the pinout of this connector. The high speed LVDS lines are connected to a National Semiconductor<sup>®</sup> Channel Link<sup>®</sup> SERDES receiver chip, which translates the high speed interface to a more manageable speed, though wider, LVCMOS bus connected to the MityDSP-Pro interface pins. For more information on Camera Link, please refer to the Camera Link Standard specification. For more information on Channel Link, please refer to National Semiconductor's website.

Table 5: J1 Camera Link Interface connector (MDR-26)

| Table 5: J1 Camera Link Interface connector (MDR-26) |              |      |          |                             |  |  |  |

|------------------------------------------------------|--------------|------|----------|-----------------------------|--|--|--|

| Pin                                                  | Signal       | Type | Standard | Notes                       |  |  |  |

| 1                                                    | Inner shield | -    | -        | Tied to Digital GND         |  |  |  |

| 14                                                   | Inner shield | -    | -        | Tied to Digital GND         |  |  |  |

| 2                                                    | CC4-         | 0    | LVDS     | Camera Control channel 4    |  |  |  |

| 15                                                   | CC4+         | 0    | LVDS     | Camera Control channel 4    |  |  |  |

| 3                                                    | CC3+         | 0    | LVDS     | Camera Control channel 3    |  |  |  |

| 16                                                   | CC3-         | 0    | LVDS     | Camera Control channel 3    |  |  |  |

| 4                                                    | CC2-         | 0    | LVDS     | Camera Control channel 2    |  |  |  |

| 17                                                   | CC2+         | 0    | LVDS     | Camera Control channel 2    |  |  |  |

| 5                                                    | CC1+         | 0    | LVDS     | Camera Control channel 1    |  |  |  |

| 18                                                   | CC1-         | 0    | LVDS     | Camera Control channel 1    |  |  |  |

| 6                                                    | SerTFG+      | I    | LVDS     | Serial to Frame Grabber     |  |  |  |

| 19                                                   | SerTFG-      | I    | LVDS     | Serial to Frame Grabber     |  |  |  |

| 7                                                    | SerTC-       | 0    | LVDS     | Serial to Camera            |  |  |  |

| 20                                                   | SerTC+       | 0    | LVDS     | Serial to Camera            |  |  |  |

| 8                                                    | X3+          | I    | LVDS     | Video SERDES Link channel 3 |  |  |  |

| 21                                                   | Х3-          | I    | LVDS     | Video SERDES Link channel 3 |  |  |  |

| 9                                                    | Xclk+        | I    | LVDS     | Video SERDES Link clock     |  |  |  |

| 22                                                   | Xclk-        | I    | LVDS     | Video SERDES Link clock     |  |  |  |

| 10                                                   | X2+          | I    | LVDS     | Video SERDES Link channel 2 |  |  |  |

| 23                                                   | X2-          | I    | LVDS     | Video SERDES Link channel 2 |  |  |  |

| 11                                                   | X1+          | I    | LVDS     | Video SERDES Link channel 1 |  |  |  |

| 24                                                   | X1-          | I    | LVDS     | Video SERDES Link channel 1 |  |  |  |

| 12                                                   | X0+          | I    | LVDS     | Video SERDES Link channel 0 |  |  |  |

| 25                                                   | Х0-          | I    | LVDS     | Video SERDES Link channel 0 |  |  |  |

| 13                                                   | Inner shield | -    | -        | Tied to Digital GND         |  |  |  |

| 26                                                   | Inner shield | -    | -        | Tied to Digital GND         |  |  |  |

# **MDK-8 Daughter Card Interface**

The MDK-Pro-MB provides four MDK-8 Daughter Card interface positions. position includes one 50 position dual row socket. Mating connectors for these sockets FX6-50P-0.8SV are the Hirose plugs. defines cards. Table signals pin for 6 the on each the Table 8 provides the electrical standards for the various nets.

Table 6: Daughter Card – MDK-8 Connector Pin Assignments

| Table 6: Daughter Card – MDK-8 Connector Pin Assignments |        |     |        |  |  |  |

|----------------------------------------------------------|--------|-----|--------|--|--|--|

| Pin                                                      | Signal | Pin | Signal |  |  |  |

| A1                                                       | IO_0   | B1  | +5 V   |  |  |  |

| A2                                                       | IO_1   | B2  | +5 V   |  |  |  |

| A3                                                       | IO_2   | В3  | +3.3 V |  |  |  |

| A4                                                       | IO_3   | B4  | +3.3 V |  |  |  |

| A5                                                       | IO_4   | B5  | +12 VA |  |  |  |

| A6                                                       | IO_5   | B6  | GND    |  |  |  |

| A7                                                       | IO_6   | В7  | GND    |  |  |  |

| A8                                                       | IO_7   | B8  | GND    |  |  |  |

| A9                                                       | DO_0   | В9  | -12 VA |  |  |  |

| A10                                                      | DO_1   | B10 | +15 V  |  |  |  |

| A11                                                      | DO_2   | B11 | +15 V  |  |  |  |

| A12                                                      | DO_3   | B12 | -15 V  |  |  |  |

| A13                                                      | DO_4   | B13 | -15 V  |  |  |  |

| A14                                                      | DO_5   | B14 | AGND   |  |  |  |

| A15                                                      | DO_6   | B15 | AGND   |  |  |  |

| A16                                                      | DI_0   | B16 | DO_CLK |  |  |  |

| A17                                                      | DI_1   | B17 | RSV    |  |  |  |

| A18                                                      | DI_2   | B18 | RSV    |  |  |  |

| A19                                                      | DI_3   | B19 | RSV    |  |  |  |

| A20                                                      | DI_4   | B20 | RSV    |  |  |  |

| A21                                                      | DI_5   | B21 | RSV    |  |  |  |

| A22                                                      | DI_6   | B22 | RSV    |  |  |  |

| A23                                                      | DI_7   | B23 | RSV    |  |  |  |

| A24                                                      | ADC    | B24 | RSV    |  |  |  |

| A25                                                      | DAC    | B25 | RSV    |  |  |  |

## **MDK-4 Daughter Card Interface**

The MDK-Pro-MB provides 4 MDK-4 Daughter Card interface positions. Each position includes one 20 position dual row socket. Mating connectors for these sockets are the Hirose FX6-20P-0.8SV plugs. Table 7 defines the signals on each pin for the cards. Table 8 provides the electrical standards for the various nets.

**Table 7: Daughter Card MDK-4 Connector Assignments**

| Pin | Signal | Pin | Signal |

|-----|--------|-----|--------|

| A1  | IO_0   | B1  | +5V    |

| A2  | IO_1   | B2  | +5V    |

| A3  | IO_2   | В3  | +3.3V  |

| A4  | IO_3   | B4  | +3.3V  |

| A5  | +15 V  | B5  | GND    |

| A6  | +15 V  | В6  | GND    |

| A7  | DAC    | В7  | RSV    |

| A8  | AGND   | B8  | RSV    |

| A9  | RSV    | В9  | RSV    |

| A10 | RSV    | B10 | RSV    |

## **Daughter Card Signal Description**

**Table 8: Daughter Card Signal Description**

| Table 6. Daughter Card Signal Description |      |           |                                          |  |  |  |

|-------------------------------------------|------|-----------|------------------------------------------|--|--|--|

| Signal                                    | Type | Standard  | Notes                                    |  |  |  |

| IO_##                                     | I/O  | 3.3V CMOS | Direct Interface to MityDSP-Pro Spartan3 |  |  |  |

|                                           |      |           | FPGA.                                    |  |  |  |

| DO_##                                     | О    | 3.3V CMOS | Digital Output. Update Rate of 20 nsec.  |  |  |  |

|                                           |      |           | DO_CLK provides sampling clock – outputs |  |  |  |

|                                           |      |           | should be sampled on rising edge.        |  |  |  |

| DI_##                                     | I    | 3.3V CMOS | Digital Input. Sampling interval < 2 μs. |  |  |  |

| DAC_1                                     | О    | 0-4.096 V | 12 Bit.                                  |  |  |  |

| DAC_2                                     |      |           |                                          |  |  |  |

| DAC_3                                     |      |           |                                          |  |  |  |

| DAC_4                                     |      |           |                                          |  |  |  |

| ADC_1                                     | I    | 0-2 V     | 12 Bit. 10 Khz R/C filtering.            |  |  |  |

| ADC_2                                     |      |           |                                          |  |  |  |

| ADC_3                                     |      |           |                                          |  |  |  |

| ADC_4                                     |      |           |                                          |  |  |  |

# **MECHANICAL INTERFACE DESCRIPTION**

# **Main Board Interface / Mounting**

Figure 8: MDK-Pro-MB PCB Outline and Mounting Hole Locations (Top View, mils)

## **Daughter Card Interface / Mounting**

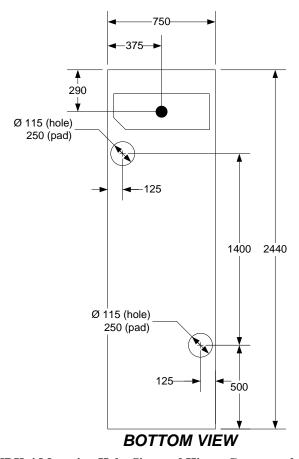

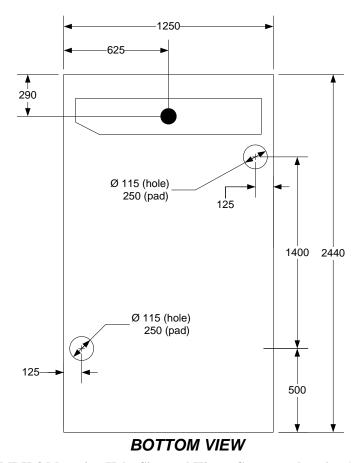

Mechanical outlines for each of the MDK-4 and MDK-8 form factors are shown in Figure 9 and Figure 10, respectively. For larger MDK-12, MDK-16, and MDK-24 form factors, a 1/8th inch gap (125 mils) is required between each of the board outlines. Figure 12 illustrates and MDK-16 form factor board with the necessary spacing.

Figure 9: MDK-4 Mounting Hole, Size, and Hirose Connector location (units in mils)

Figure 10: MDK-8 Mounting Hole, Size, and Hirose Connector location (units in mils)

**BOTTOM VIEW**

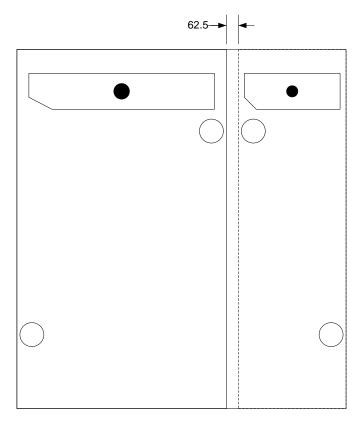

Figure 11: MDK-12 Alignment (MDK-4 and MDK-8 footprints separated by 62.5 mils)

#### **BOTTOM VIEW**

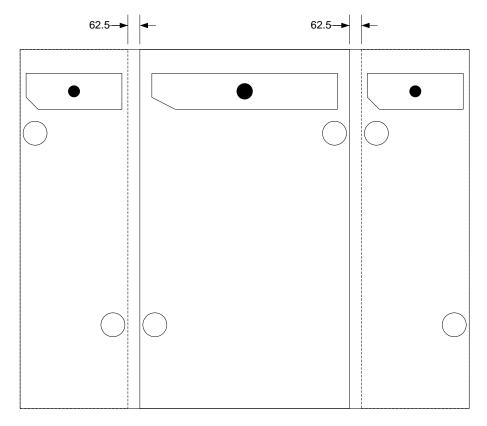

Figure 12: MDK-16 Alignment (MDK-4 and MDK-8 footprints separated by 62.5 mils)

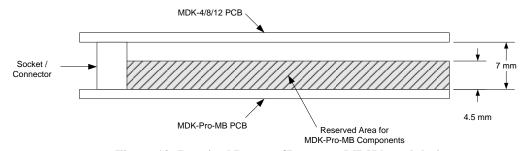

In the vertical dimension, the base board to board spacing is 7 mm. The MDK-Pro-MB includes components underneath the area used by the MDK daughter boards. 4.5 mm has been reserved for use by these components. Therefore, MDK daughter boards must be designed requiring no more than 2.5 mm of clearance for bottom side mounted components. This is illustrated in Figure 13.

Figure 13: Required Bottom Clearance, MDK board designs

# MityDSP-Pro Interface

Table 9: MityDSP-Pro/SO-DIMM Connector Assignments

| Pin | I/O | Table 9: MityDSP-Pro/SC<br>Signal | Pin | I/O | Signal        |

|-----|-----|-----------------------------------|-----|-----|---------------|

| 1   | -   | 3.3 V                             | 2   | -   | 3.3 V         |

| 3   | -   | 3.3 V                             | 4   | -   | 3.3 V         |

| 5   | -   | 3.3 V                             | 6   | -   | 3.3 V         |

| 7   | _   | GND                               | 8   | -   | GND           |

| 9   | _   | GND                               | 10  | -   | GND           |

| 11  | I   | MRESET#                           | 12  | I   | BOOT MODE     |

| 13  | 0   | ETH_TD_P                          | 14  | O   | RS232_TXD     |

| 15  | 0   | ETH_TD_N                          | 16  | I   | RS232_RXD     |

| 17  | I   | ETH_TD_N ETH_RD_P                 | 18  | O   | RS232_RTS     |

| 19  | I   | ETH_RD_N                          | 20  | I   | RS232_CTS     |

| 21  | -   | FPGA RSV1                         | 22  | 0   | SCL           |

| 23  | -   | FPGA_RSV2                         | 24  | I/O | SDA           |

| 25  | I/O | CLKR0                             | 26  | I/O | CLKR1         |

| 27  | I/O | CLKX0                             | 28  | I/O | CLKX1         |

| 29  | I   | DR0                               | 30  | I   | DR1           |

| 31  | 0   | DX0                               | 32  | 0   | DX1           |

| 33  | I/O | FSR0                              | 34  | I/O | FSR1          |

| 35  | I/O | FSX0                              | 36  | I/O | FSX1          |

| 37  | -   | VCCO_2                            | 38  | -   | VCCO_1        |

| 39  | -   | VCCO 0                            | 40  | -   | VCCO 7        |

| 41  | -   | GND                               | 42  | -   | GND           |

| 43  | I/O | DC1_IO8                           | 44  | 0   | USB TXD       |

| 45  | I/O | DC1_IO9                           | 46  | I   | USB_RXD       |

| 47  | I/O | DC1_IO10                          | 48  | O   | USB_RTS       |

| 49  | I/O | DC1_IO10                          | 50  | I   | USB_CTS       |

| 51  | I/O | DC1_IO0                           | 52  | 0   | DI_CLK        |

| 53  | I/O | DC1_IO1                           | 54  | 0   | DI_LOAD       |

| 55  | I/O | DC1 IO2                           | 56  | 0   | ADC_CS        |

| 57  | I/O | DC1_IO3                           | 58  | I   | DI_DAT        |

| 59  | I/O | DC1_IO4                           | 60  | 0   | RTC_SCL       |

| 61  | I/O | DC1_IO5                           | 62  | I/O | RTC_SDA       |

| 63  | -   | GND                               | 64  | -   | GND           |

| 65  | I/O | DC1_IO6                           | 66  | I/O | ETH_MDIO      |

| 67  | I/O | DC1_IO7                           | 68  | 0   | ETH_MDC       |

| 69  | I/O | DC2 IO8                           | 70  | 0   | 25MHZ REF CLK |

| 71  | I/O | DC2_IO9                           | 72  | 0   | ETH_RESET#    |

| 73  | I/O | DC2 IO10                          | 74  | I   | ETH_RX_CLK    |

| 75  | I/O | DC2_IO11                          | 76  | Ī   | ETH_RX_DV     |

| 77  | I/O | DC2_IO2                           | 78  | I   | ETH_CRS       |

| 79  | I/O | DC2_IO1                           | 80  | I   | ETH_RX_ER     |

| 81  | I/O | DC2 IO3                           | 82  | I   | ETH COL       |

| 83  | I/O | DC2_IO4                           | 84  | I   | ETH RXD0      |

| 85  | -   | GND                               | 86  | -   | GND           |

| 87  | I/O | DC2_IO5                           | 88  | I   | ETH RXD1      |

| 89  | I/O | DC2_IO6                           | 90  | I   | ETH_RXD2      |

| 91  | I/O | DC2_IO7                           | 92  | I   | ETH_RXD3      |

| 93  | I/O | DC2_IO0                           | 94  | I   | ETH_TX_CLK    |

| 95  | I/O | DC4_IO0                           | 96  | 0   | ETH_TX_EN     |

| 97  | I/O | DC4_IO1                           | 98  | 0   | ETH TXD0      |

|     |     |                                   |     | _   |               |

| Pin        | I/O        | Signal             | Pin        | I/O    | Signal       |

|------------|------------|--------------------|------------|--------|--------------|

| 99         | I/O        | DC4_IO2            | 100        | 0      | ETH_TXD1     |

| 101        | I/O        | DC4_IO3            | 100        | 0      | ETH TXD2     |

| 103        | I/O        | DC4_IO4            | 102        | 0      | ETH_TXD3     |

| 105        | I/O        | DC4_IO5            | 104        | 0      | SerTC        |

| 107        | -          | GND                | 108        | -      | GND          |

| 107        | I/O        | DC4_IO6            | 110        | I      | SerTFG       |

| 111        | I/O        | DC4_IO7            | 110        | O      | CC_ENABLE    |

| 113        | I/O        | DC4_IO8            | 114        | I      | X_0          |

| 115        | I/O        | DC4_IO9            | 116        | I      | X_CLK        |

| 117        | I/O        | DC4_IO10           | 118        | I      | X_1          |

| 117        | I/O        | DC4_IO10           | 120        | I      | X_1<br>X_2   |

| 121        | I/O        | DC3_IO0            | 120        | I      | X_3          |

| 123        | I/O        | DC3_IO1            | 124        | I      | X_3<br>  X_4 |

| 125        | I/O        | DC3_IO2            | 124        |        | X_4<br>X_5   |

| 123        | I/O        | DC3_IO2<br>DC3_IO3 |            | I      |              |

| 127        | 1/O<br>-   | GND                | 128<br>130 | - I    | X_6<br>GND   |

| 131        | I/O        | DC3_IO4            | 130        | -<br>I | X 7          |

|            |            |                    |            |        | _            |

| 133<br>135 | I/O<br>I/O | DC3_IO5<br>DC3_IO6 | 134<br>136 | I      | X_8<br>X_9   |

|            |            |                    |            |        |              |

| 137        | I/O        | DC3_IO7            | 138        | I      | X_10         |

| 139        | I/O        | DC3_IO8            | 140        | I      | X_11         |

| 141        | I/O        | DC3_IO9            | 142        | I      | X_12         |

| 143        | I/O        | DC3_IO10           | 144        | I      | X_13         |

| 145        | I/O        | DC3_IO11           | 146        | I      | X_14         |

| 147        | 0          | CC1                | 148        | I      | X_27         |

| 149        | O          | CC2                | 150        | I      | X_26         |

| 151        | -          | GND                | 152        | -      | GND          |

| 153        | 0          | CC3                | 154        | I      | X_25         |

| 155        | O          | CC4                | 156        | I      | X_24         |

| 157        | -          | Unused             | 158        | I      | X3_P         |

| 159        | -          | Unused             | 160        | I      | X3_N         |

| 161        | -          | Unused             | 162        | I      | XClk_P       |

| 163        | -          | Unused             | 164        | I      | XClk_N       |

| 165        | -          | Unused             | 166        | I      | X2_P         |

| 167        | -          | Unused             | 168        | I      | X2_N         |

| 169        | I          | X0_P               | 170        | I      | X1_P         |

| 171        | I          | X0_N               | 172        | I      | X1_N         |

| 173        | -          | GND                | 174        | -      | GND          |

| 175        | O          | DO_A3_P            | 176        | O      | DISP_A0_P    |

| 177        | O          | DO_A3_N            | 178        | O      | DISP_A0_N    |

| 179        | O          | DO_CLKIN_P         | 180        | O      | DISP_A1_P    |

| 181        | O          | DO_CLKIN_N         | 182        | O      | DISP_A1_N    |

| 183        | O          | DO_A2_P            | 184        | O      | DISP_A2_P    |

| 185        | O          | DO_A2_N            | 186        | O      | DISP_A2_N    |

| 187        | O          | DO_A1_P            | 188        | O      | DISP_A3_P    |

| 189        | O          | DO_A1_N            | 190        | O      | DISP_A3_N    |

| 191        | 0          | DO_A0_P            | 192        | 0      | DISP_CLKIN_P |

| 193        | O          | DO_A0_N            | 194        | O      | DISP_CLKIN_N |

| 195        | -          | GND                | 196        | -      | GND          |

| 197        | -          | 3.3V               | 198        | ı      | 3.3V         |

| 199        | -          | 3.3V               | 200        | -      | 3.3V         |

# **MDK Interface Cards**

Table 10: MDK Off-The-Shelf Interface Cards (see www.mitydsp.com for latest list)

| Card Number   | DK Off-The-Shelf Interface Cards (see www.mit                                                                                    | <br>  |       |        |        | ,      |       |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------|--------|--------|-------|

| Card Number   | Description / Features                                                                                                           | MDK-4 | MDK-8 | MDK-12 | MDK-16 | MDK-24 | Other |

| MDK4-RS232    | Single RS-232 Interface Card with hardware flow control lines (no modem control)  OR  Dual RS-232 Interface without flow control | X     |       |        |        |        |       |

| MDK4-RS485    | RS-485 Interface Card supporting 2 output and 2 input signaling lines.                                                           | X     |       |        |        |        |       |

| MDK4-SD       | SD-FLASH interface card controller, SPIO mode.                                                                                   | X     |       |        |        |        |       |

| MDK4-TSA      | Touch Screen Adaptor                                                                                                             | X     |       |        |        |        |       |

| MDK8-ADS8239  | 1 Msps 16 bit Analog to Digital Converter utilizing ADS8239.                                                                     |       | X     |        |        |        |       |

| MDK8-ADS8344  | 8 channel 16 bit 100 Msps Analog to Digital<br>Converter utilizing ADS8344.                                                      |       | X     |        |        |        |       |

| MDK8-DIGIOISO | TTL Discrete Input/Output Interface Card, isolated inputs/outputs.                                                               |       | X     |        |        |        |       |

| MDK8-A3967    | Independent dual axis stepper motor controller, micro-stepping down to 1/8 step size.                                            |       | X     |        |        |        |       |

| MDK12-TTLIO   | TTL Discrete Input/Output Interface Card                                                                                         |       |       | X      |        |        |       |

| MDK16-AWG     | Analog Waveform Generator, dual summed 14 bit DACs, 100 Msps.                                                                    |       |       |        | X      |        |       |

| MDK-QVGA-LCD  | Quarter VGA LCD Display Adaptor, LVDS interface.                                                                                 |       |       |        |        | ·      | X     |

# **REVISION HISTORY**

| Date        | Change Description                                      |

|-------------|---------------------------------------------------------|

| 29-SEP-2009 | Initial release of current spec.                        |

| 27-MAR-2013 | Revision history table added and header/footer updated. |

|             |                                                         |

|             |                                                         |

|             |                                                         |

|             |                                                         |

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А