Data Sheet: Advance Information

### Document Number: MC22XS4200 Rev. 5.0, 6/2018

# Dual 24 V, 22 mOhm high-side switch

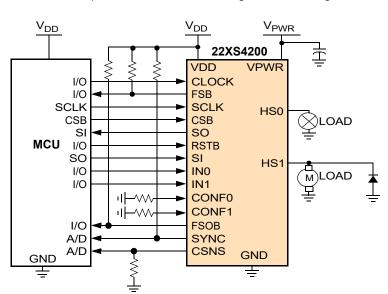

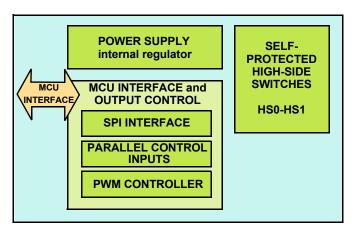

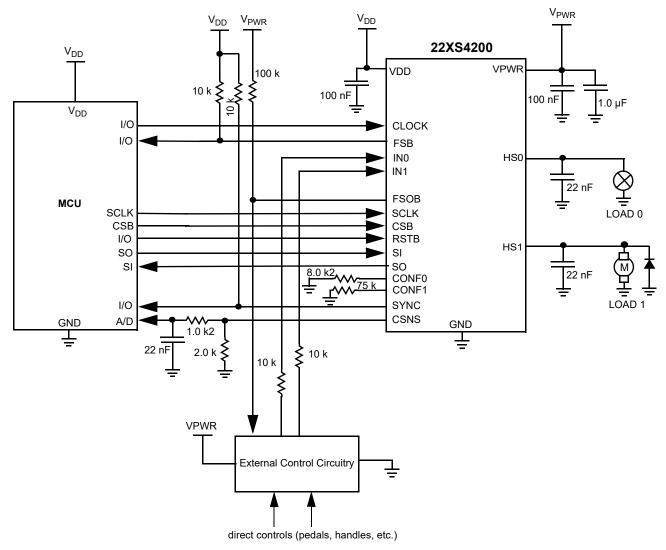

The 22XS4200 device is part of a 24 V dual high-side switch product family with integrated control, and a high number of protective and diagnostic functions. It is designed for truck and bus applications. The low  $R_{\mbox{\scriptsize DS(on)}}$  channels (<22 m $\Omega$ ) can control different load types; bulbs, solenoids, or DC motors. Control, device configuration, and diagnostics are performed through a 16-bit serial peripheral interface (SPI), allowing easy integration into existing applications. This device is powered by SMARTMOS technology.

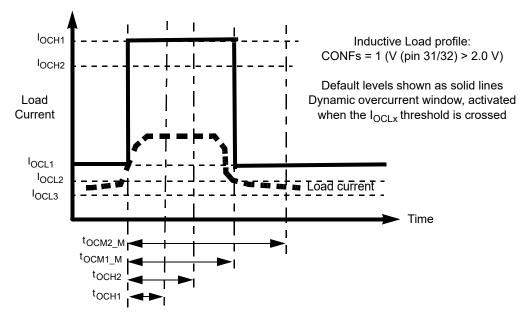

Both channels can be controlled individually by external/internal clock signals, or by direct inputs. Using the internal clock allows fully autonomous device operation. Programmable output voltage slew rates (individually programmable) helps improve electromagnetic compatibility (EMC) performance. To avoid shutting off the device upon inrush current, while still being able to closely track the load current, a dynamic overcurrent threshold profile is featured. Switching current of each channel can be sensed with a programmable sensing ratio. Whenever communication with the external microcontroller is lost, the device enters a Fail-safe operation mode, but remains operational, controllable, and protected.

#### **Features**

- Two fully-protected 22 mΩ (at 25 °C) high-side switches

- Up to 4.2 A steady state current per channel

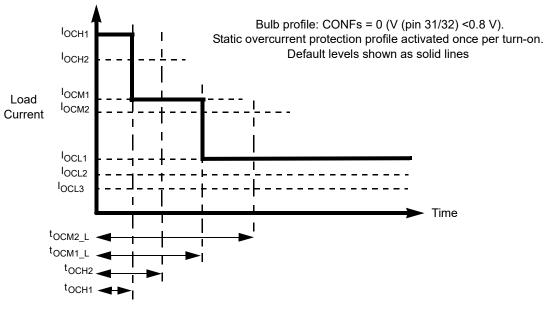

- Separate bulb and DC motor latched overcurrent handling

- · Individually programmable internal/external PWM clock signals

- Overcurrent, short-circuit, and overtemperature protection with programmable autoretry functions

- · Accurate temperature and current sensing

- Open load detection (channel in OFF and ON state), also for LED applications (7.0 mA typ.)

- Normal operating range: 8.0 V to 36 V, extended range: 6.0 V to 58 V

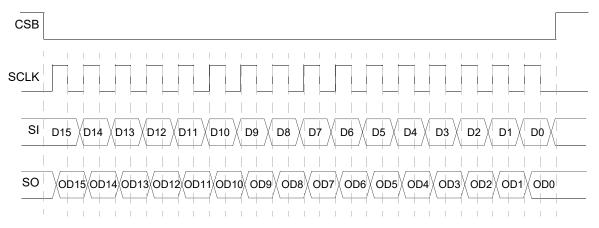

- 3.3 V and 5.0 V compatible 16-bit SPI port for device control, configuration and diagnostics at rates up to 8.0 MHz

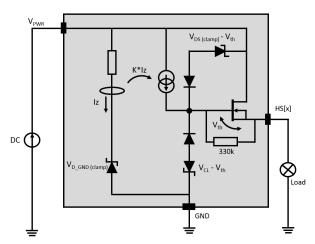

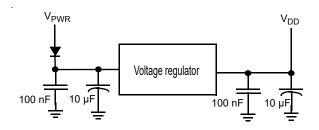

Figure 1. Simplified application diagram

## 22XS4200

#### **HIGH-SIDE SWITCH**

#### **Applications**

- Truck, bus and 24 V transportation systems

- Resistive, capacitive, and inductive loads

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

# **Table of Contents**

| 1 | Orderable parts                           | . 3 |

|---|-------------------------------------------|-----|

|   | Internal block diagram                    |     |

|   | Pin assignment                            |     |

| 4 | Electrical characteristics                | . 7 |

|   | 4.1 Maximum ratings                       | . 7 |

|   | 4.2 Static electrical characteristics     | . 9 |

|   | 4.3 Dynamic electrical characteristics    | 15  |

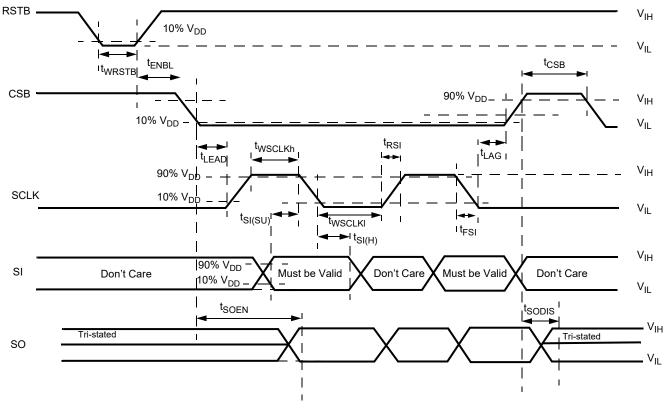

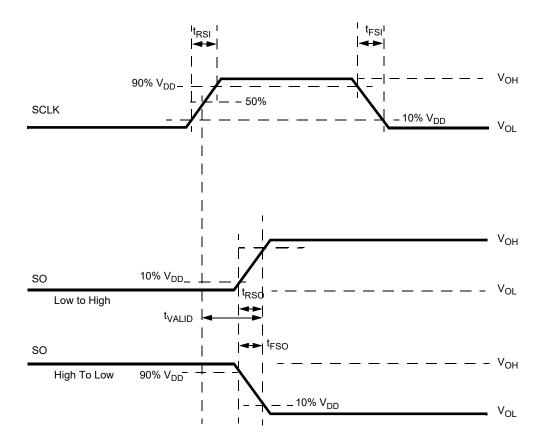

|   | 4.4 Timing diagrams                       | 20  |

| 5 | Functional description                    |     |

|   | 5.1 Introduction                          |     |

|   | 5.2 Pin assignment and functions          | 23  |

|   | 5.3 Functional internal block description | 26  |

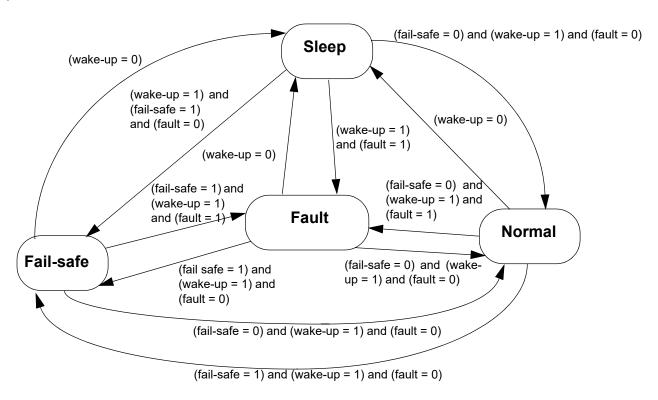

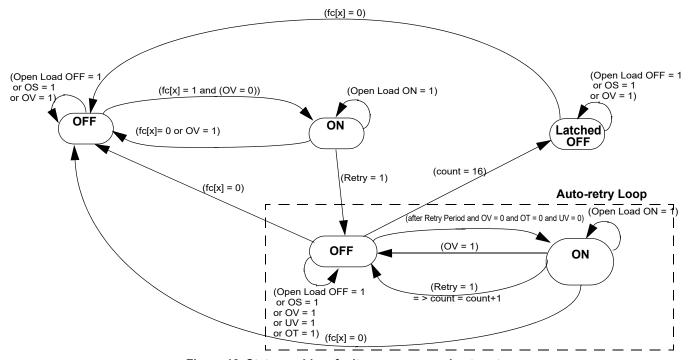

| 6 | Functional device operation               | 27  |

|   | 6.1 Operation and operating modes         | 27  |

|   | 6.3 Logic commands and SPI registers      | 46  |

| 7 | Typical applications                      |     |

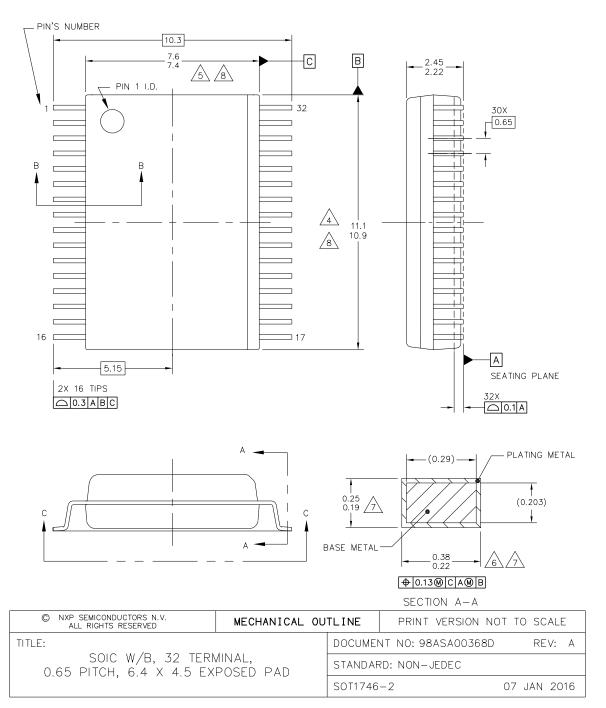

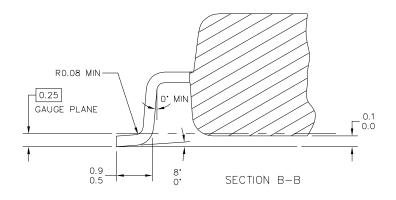

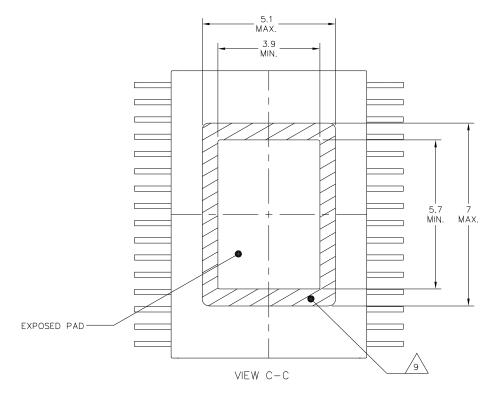

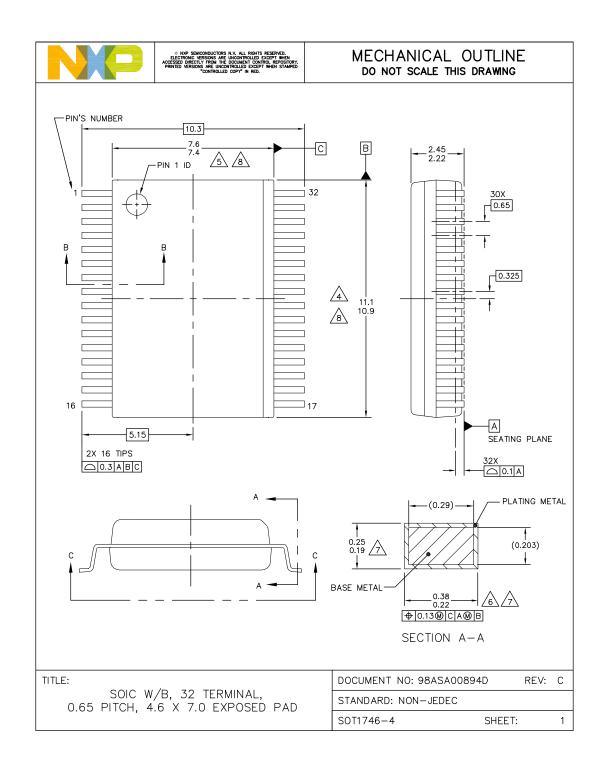

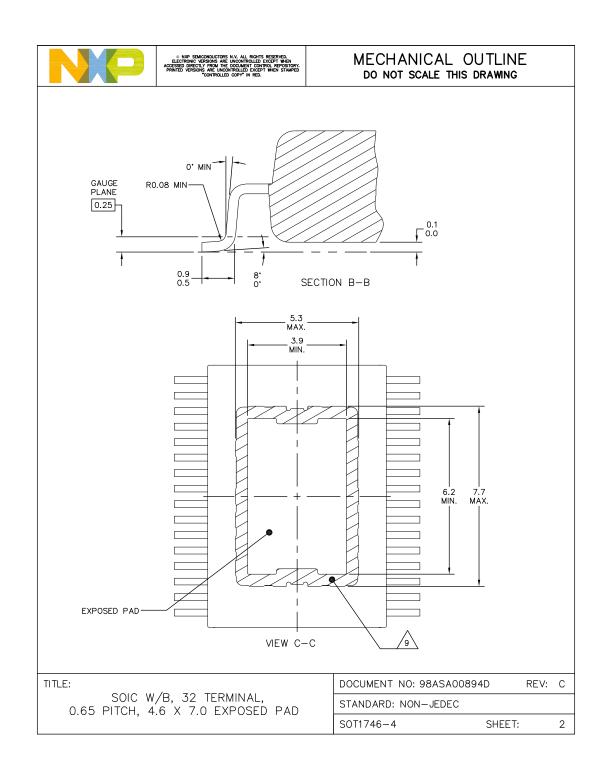

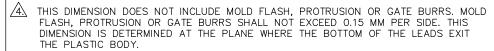

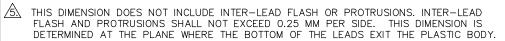

| 8 | Packaging                                 | 56  |

|   | 8.1 Package mechanical dimensions         | 56  |

| 9 | Revision history                          | 63  |

# 1 Orderable parts

### Table 1. Orderable part variations

| Part number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package    |

|----------------------------|-------------------------------|------------|

| MC22XS4200BEK              | -40 °C to 125 °C              | 32 SOIC-EP |

| MC22XS4200CEK              | 40 0 10 120 0                 | 32 3010-LF |

### Notes

1. To order parts in tape and reel, add the R2 suffix to the part number.

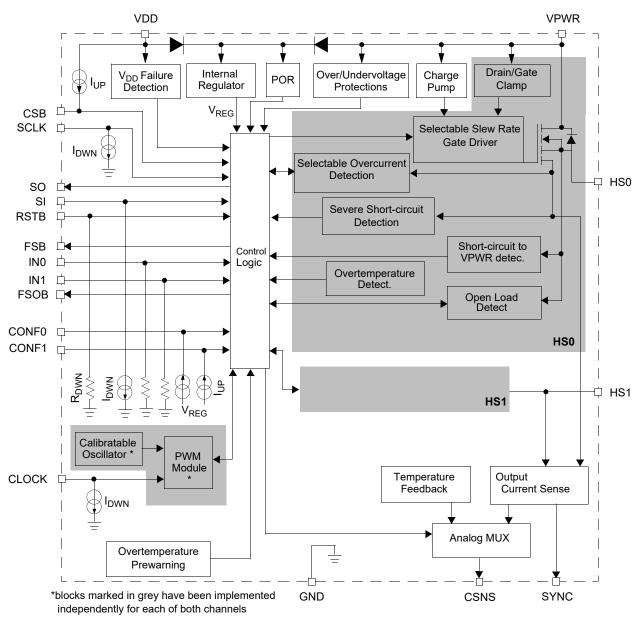

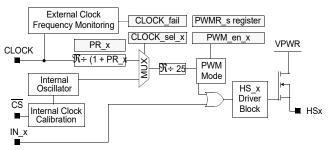

# 2 Internal block diagram

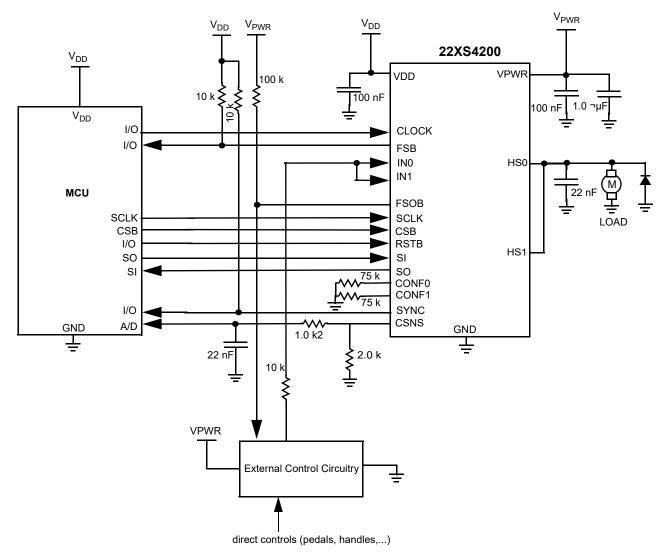

Figure 2. Internal block diagram

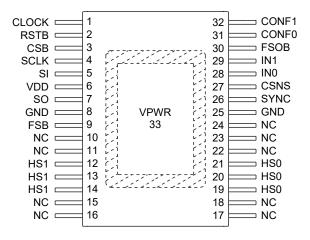

# 3 Pin assignment

### **Transparent Top View**

Figure 3. Device pin assignments

The function of each pin is described in the section Functional description

Table 2. 22XS4200 pin description

| Pin<br>number                            | Pin name   | Function | Formal name                  | Definition                                                                                                                                                                                                                                                                                                           |

|------------------------------------------|------------|----------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                        | CLOCK      | Input    | PWM Clock                    | The clock input gives the time-base when the device is operated in external clock/internal PWM mode. This pin has an internal pull-down current source.                                                                                                                                                              |

| 2                                        | RSTB       | Input    | Reset                        | This input pin is used to initialize the device's configuration - and fault registers. Reset puts the device in Sleep mode (low current consumption) provided it is not stimulated by direct input signals. This pin is connected to GND by an internal pull-down resistor.                                          |

| 3                                        | CSB        | Input    | Chip Select (Active Low)     | This input pin is connected to the SPI chip-select output of an external microcontroller. CSB is internally pulled up to $V_{DD}$ by a current source $I_{UP}$ .                                                                                                                                                     |

| 4                                        | SCLK       | Input    | Serial Clock                 | This input pin is to be connected to an external SPI Clock signal. The SCLK pin is internally connected to a pull-down current source I <sub>DWN</sub> .                                                                                                                                                             |

| 5                                        | SI         | Input    | Serial Input                 | This input pin receives the SPI input data from an external device (microcontroller or another extreme switch device in case of daisy-chaining). The SI pin is internally connected to a pull-down current source I <sub>DWN</sub> .                                                                                 |

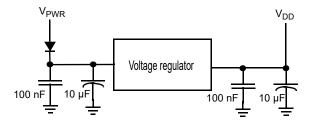

| 6                                        | VDD        | Power    | Digital Drain Voltage        | This is the positive supply pin of the SPI interface.                                                                                                                                                                                                                                                                |

| 7                                        | SO         | Output   | Serial Output                | This output pin transmits SPI data to an external device (external microcontroller or the SI pin of the next SPI device in case of daisy-chaining). The pin doesn't require external pull-up or pull-down resistors, but a series resistor is recommended to limit current consumption in case of GND disconnection. |

| 8, 25                                    | GND        | Ground   | Ground                       | These pins are the ground for the logic and analog circuitries of the device. For ESD and electrical parameter accuracy purpose, the ground pins must be shorted in the board.                                                                                                                                       |

| 9                                        | FSB        | Output   | Fault Status<br>(Active Low) | This open drain output pin (external pull-up resistor to $V_{DD}$ required) is set when the device enters Fault mode (see Fault mode).                                                                                                                                                                               |

| 10, 11, 15,<br>16, 17, 18,<br>22, 23, 24 | NC         | N/A      | Not connected                | These pins may not be connected.                                                                                                                                                                                                                                                                                     |

| 12, 13, 14,<br>19, 20, 21                | HS1<br>HS0 | Output   | Power Switch Outputs         | Output pins of the switches, to be connected to the load.                                                                                                                                                                                                                                                            |

Table 2. 22XS4200 pin description (continued)

| Pin<br>number                                                                                                                                                  | Pin name       | Function                                                                                                                                                                                                                                                                                                                                                                   | Formal name                                     | Definition                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26                                                                                                                                                             | SYNC           | Output                                                                                                                                                                                                                                                                                                                                                                     | Output Current<br>Monitoring<br>Synchronization | This output pin is asserted (active low) when the Current Sense (CS) output signal is within the specified accuracy range. Reading the SYNC pin allows the external microprocessor to synchronize to the device when operating in autonomous operating mode. SYNC is open drain and requires a pull-up resistor to V <sub>DD</sub> . |

| Output Current/ proportional to the temperature of the GND pin (pin 14). Selection bet temperature sensing, as well as setting the current sensing sensitivity |                | This pin either outputs a current proportional to the channel's output current or a voltage proportional to the temperature of the GND pin (pin 14). Selection between current and temperature sensing, as well as setting the current sensing sensitivity are performed through the SPI interface. An external pull-down resistor must be connected between CSNS and GND. |                                                 |                                                                                                                                                                                                                                                                                                                                      |

| 28, 29                                                                                                                                                         | IN0<br>IN1     | Input                                                                                                                                                                                                                                                                                                                                                                      | Direct Inputs                                   | The IN[0: 1] input pins are used to directly control the switching state of both switches and consequently the voltage on the HS0: HS1 output pins. The pins are connected to GND by internal pull-down resistors.                                                                                                                   |

| 30                                                                                                                                                             | FSOB           | Output                                                                                                                                                                                                                                                                                                                                                                     | Fail-safe Output<br>(Active Low)                | FSOB is asserted (active-low) upon entering Fail-safe mode (see Functional description) This open drain output requires an external pull-up resistor to $V_{\text{PWR}}$ .                                                                                                                                                           |

| 31, 32                                                                                                                                                         | CONF0<br>CONF1 | Input                                                                                                                                                                                                                                                                                                                                                                      | Configuration Input                             | The CONF[0: 1] input pins are used to select the appropriate overcurrent detection profile (bulb/DC motor) for each of both channels. CONF requires a pull-down resistor to GND.                                                                                                                                                     |

| 33                                                                                                                                                             | VPWR           | Power                                                                                                                                                                                                                                                                                                                                                                      | Positive Power Supply                           | This exposed pad connects to the positive power supply and is the drain of both internal MOSFET switches.                                                                                                                                                                                                                            |

# 4 Electrical characteristics

# 4.1 Maximum ratings

Table 3. Maximum ratings

All voltages are relative to ground unless mentioned otherwise. Exceeding these ratings may cause permanent damage.

| Symbol                                                                  | Parameter                                                                                                                                                                            | Maximum ratings                | Unit | Notes   |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|---------|

| Electrical rating                                                       | gs                                                                                                                                                                                   |                                |      |         |

| $V_{PWR}$                                                               | VPWR supply voltage range  • Load dump at 25 °C (350 ms)  • Reverse battery at 25 °C  • Fast negative transient pulses (ISO 7637-2 pulse #1, V <sub>PWR</sub> =28 V & Ri=10 Ω)       | 58<br>-32<br>-60               | V    |         |

| $V_{DD}$                                                                | VDD supply voltage range                                                                                                                                                             | -0.3 to 5.5                    | V    |         |

| V <sub>MAX,LOGIC</sub>                                                  | Voltage on input pins (except IN[0:1]) and Output pins) (except HS[0:1])                                                                                                             | -0.3 to 5.5                    | V    | (2) (3) |

| V <sub>FSO</sub>                                                        | Voltage on fail-safe output (FSOB)                                                                                                                                                   | -0.3 to 58                     | V    |         |

| V <sub>SO</sub>                                                         | Voltage on SO pin                                                                                                                                                                    | -0.3 to V <sub>DD</sub> +0.3   | V    |         |

| $V_{IN,MAX}$                                                            | Voltage (continuous, max. allowable) on IN[0:1] inputs                                                                                                                               | 58                             | V    |         |

| V <sub>HS[0:1]</sub>                                                    | Voltage (continuous, max. allowable) on output pins (HS [0:1]),                                                                                                                      | -32 to 58                      | V    |         |

| I <sub>HS[0:1]</sub>                                                    | Rated continuous output current per channel                                                                                                                                          | 4.2                            | Α    | (4)     |

| E <sub>CL[0:1]_SING</sub>                                               | Maximum allowable energy dissipation per channel and two parallel channels, single-pulse method                                                                                      | 36                             | mJ   | (5)     |

| V <sub>ESD1</sub> V <sub>ESD2</sub> V <sub>ESD3</sub> V <sub>ESD4</sub> | ESD voltage  Human body model (HBM) for HS[0:1], VPWR and GND  Human body model (HBM) for other pins  Charge device model (CDM)  Package corner pins (1, 13, 19, 20)  All other pins | ±8000<br>±2000<br>±750<br>±500 | V    | (6)     |

#### Notes:

- 2. Concerned input pins are: CONF[0:1], RSTB, SI, SCLK, Clock, and CSB.

- 3. Concerned output pins are: CSNS, SYNC, and FSB.

- 4. Output current rating valid as long as maximum junction temperature is not exceeded. For computation of the maximum allowable output current, the thermal resistance of the package and the underlying heatsink must be taken into account.

- 5. Single pulse energy dissipation, single-pulse short-circuit method ( $L_L$  = 0.5 mH, R = 48 m $\Omega$  V<sub>PWR</sub> = 28 V, T<sub>J</sub> = 150 °C initial).

- 6. ESD testing is performed in accordance with the Human body model (HBM) ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ), and the charge device model (CDM), robotic ( $C_{ZAP} = 4.0 \text{ pF}$ ).

### Table 3. Maximum ratings (continued)

All voltages are relative to ground unless mentioned otherwise. Exceeding these ratings may cause permanent damage.

| Symbol            | Parameter                                         | Maximum ratings          | Unit | Notes   |

|-------------------|---------------------------------------------------|--------------------------|------|---------|

| Thermal ratings   |                                                   |                          |      |         |

| T <sub>A</sub>    | Operating temperature                             | -40 to 125<br>-40 to 150 | °C   |         |

| T <sub>STG</sub>  | Storage temperature                               | -55 to 150               | °C   |         |

| $R_{	heta JC}$    | Thermal resistance junction to case (exposed pad) | 1.4                      | °C/W |         |

| $R_{\theta JA}$   | Thermal resistance junction to ambient            | 22                       | °C/W | (7)     |

| T <sub>PPRT</sub> | Peak package reflow temperature during reflow     | Note 9                   | °C   | (8),(9) |

#### Notes:

- 7. Four layer board (2s2p), per JEDEC JESD51-6 with the board (JESD51-7) horizontal

- 8. Pin soldering temperature limit is for 40 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 9. NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), go to www.nxp.com, search by part number (remove prefixes/suffixes), enter the core ID to view all orderable parts, and review parametrics.

### 4.2 Static electrical characteristics

#### Table 4. Static electrical characteristics

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V and V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                  | Parameter                                                                                                                                                                                | Min.        | Тур.                 | Max.         | Unit | Notes |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|--------------|------|-------|

| Supply electrica        | I characteristics                                                                                                                                                                        |             |                      | 1            | I    | 1     |

| $V_{PWR}$               | Supply voltage range:     Full specification compliant     Extended mode                                                                                                                 | 8.0<br>6.0  | 24<br>-              | 36<br>58     | V    | (10)  |

| I <sub>PWR(ON)</sub>    | V <sub>PWR</sub> supply current, device in Wake-up mode, channel On, open load outputs in ON-state, HS[0:1] open, IN[0:1] > V <sub>IH</sub>                                              | -           | 6.5                  | 8.5          | mA   |       |

| I <sub>PWR(SBY)</sub>   | $V_{PWR}$ supply current, device in Wake-up mode (Standby), channel Off open load in OFF-state detection disabled, HS[0:1] shorted to ground with $V_{DD}$ = 5.5 V and RSTB > $V_{WAKE}$ | -           | 6.5                  | 8.5          | mA   |       |

| I <sub>PWR(SLEEP)</sub> | Sleep state supply current  V <sub>PWR</sub> = 24 V, RSTB = IN[0:1] < V <sub>WAKE</sub> , HS[0:1] connected to ground  • T <sub>A</sub> = 25 °C  • T <sub>A</sub> = 125 °C               | -<br>-      | 3.0                  | 10.0<br>60.0 | μА   |       |

| V <sub>DD(ON)</sub>     | V <sub>DD</sub> supply voltage                                                                                                                                                           | 3.0         | _                    | 5.5          | V    |       |

| I <sub>DD(ON)</sub>     | V <sub>DD</sub> supply current at V <sub>DD</sub> = 5.5 V  • No SPI communication  • 8.0 MHz SPI communication                                                                           | -<br>-      | _<br>5.0             | 2.2          | mA   | (11)  |

| I <sub>DD(SLEEP)</sub>  | $V_{DD}$ sleep state current at $V_{DD} = 5.5 \text{ V}$ with or without $V_{PWR}$                                                                                                       | -           | _                    | 5.0          | μΑ   |       |

| V <sub>PWR(OV)</sub>    | Overvoltage shutdown threshold                                                                                                                                                           | 39          | 42                   | 45.5         | V    |       |

| V <sub>PWR(OVHYS)</sub> | Overvoltage shutdown hysteresis                                                                                                                                                          | 0.2         | 0.8                  | 1.5          | V    |       |

| V <sub>PWR(UV)</sub>    | Undervoltage shutdown threshold                                                                                                                                                          | 5.0         | _                    | 6.0          | V    | (12)  |

| V <sub>PWR(POR)</sub>   | V <sub>PWR</sub> Power-on reset (POR) voltage threshold                                                                                                                                  | 2.2         | 2.6                  | 4.0          | V    | (12)  |

| V <sub>DD(POR)</sub>    | V <sub>DD</sub> Power-on reset (POR) voltage threshold                                                                                                                                   | 1.5         | 2.0                  | 2.5          | V    | (12)  |

| V <sub>DD(FAIL)</sub>   | $V_{DD}$ supply failure voltage threshold (assumed $V_{PWR} > V_{PWR(UV)}$ )                                                                                                             | 2.2         | 2.5                  | 2.8          | V    |       |

| R <sub>DS(on)25</sub>   | ON-Resistance, Drain-to-Source (I <sub>HS</sub> = 1.0 A, T <sub>J</sub> = 25 °C) CSNS_ratio = 0  • V <sub>PWR</sub> = 8.0 V  • V <sub>PWR</sub> = 28 V  • V <sub>PWR</sub> = 36 V        | -<br>-<br>- | 18.7<br>18.7<br>18.7 | -<br>-<br>-  | mΩ   |       |

#### Notes

<sup>10.</sup> In Extended mode, availability of several device functions (channel control, value of R<sub>DS(on)</sub>, overtemperature protection) is guaranteed, but compliance with the specified values in this document is not. Below 6.0 V, the device is only protected from overheating (thermal shutdown). Above V<sub>PWR(OV)</sub>, the channels can only be turned ON when the overvoltage detection function has been disabled.

<sup>11.</sup> Typical value guaranteed per design.

<sup>12.</sup> When the device recovers from undervoltage and returns to Normal mode (6.0 V < V<sub>PWR</sub> < 58 V) before the end of the auto-retry period (see Auto-retry), the device performs normally. When V<sub>PWR</sub> drops below V<sub>PWR(UV)</sub>, undervoltage is detected (see Undervoltage fault (Latchable fault) and EMC performances).

Unless specified otherwise:  $8.0 \text{ V} \le \text{V}_{PWR} \le 36 \text{ V}$ ,  $3.0 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$ ,  $-40 \text{ °C} \le \text{T}_{A} \le 125 \text{ °C}$ , GND = 0 V. Typical values are average values evaluated under nominal conditions  $\text{T}_{A}$  = 25 °C,  $\text{V}_{PWR}$  = 28 V and  $\text{V}_{DD}$  = 5.0 V, unless specified otherwise.

| Symbol                                                                           | Parameter                                                                                                                                                                                                                                                                                                                                      | Min.                                             | Тур.                                             | Max.                                             | Unit | Notes |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------|-------|

| lectrical charac                                                                 | teristics of the output stage (HS0 and HS1)                                                                                                                                                                                                                                                                                                    |                                                  | 1                                                | ı                                                | 1    | 1     |

| R <sub>DS(on)150</sub>                                                           | ON-Resistance, Drain-to-Source (I <sub>HS</sub> = 1.0 A,T <sub>J</sub> = 150 °C) CSNS_ratio = 0  • V <sub>PWR</sub> = 8.0 V  • V <sub>PWR</sub> = 28 V  • V <sub>PWR</sub> = 36 V                                                                                                                                                              | -<br>-<br>-                                      | -<br>-<br>-                                      | 43<br>43<br>43                                   | mΩ   |       |

| $\Delta R_{DS(on)150}$                                                           | ON-Resistance, Drain-to-Source difference from one channel to the other in Parallel mode (I <sub>HS</sub> = 1.0 A,T <sub>J</sub> = 150 °C) CSNS_ratio = X                                                                                                                                                                                      | -0.9                                             | _                                                | 0.9                                              | mΩ   |       |

| R <sub>SD(on)150</sub>                                                           | ON-Resistance, Source-Drain (I <sub>HS</sub> = -1.0 A, T <sub>J</sub> = 150 °C, V <sub>PWR</sub> = -24 V)                                                                                                                                                                                                                                      | _                                                | _                                                | 43                                               | mΩ   |       |

| L <sub>SHORT</sub>                                                               | Max. detectable wiring length (2.5 mm²) for severe short-circuit detection (see Severe short-circuit fault (Latchable fault)):  • High slew rate selected  • Medium slew rate selected  • Low slew rate selected                                                                                                                               | 30<br>55<br>110                                  | 100<br>175<br>365                                | 180<br>300<br>620                                | cm   |       |

| I_OCH1_0<br>I_OCH2_0<br>I_OCM1_0<br>I_OCM2_0<br>I_OCL1_0<br>I_OCL2_0<br>I_OCL3_0 | Overcurrent detection thresholds with CSNS_ratio bit = 0 (CSR0)                                                                                                                                                                                                                                                                                | 26.4<br>16.3<br>10.4<br>6.4<br>4.3<br>2.9<br>1.4 | 32<br>20.1<br>12.6<br>7.7<br>5.3<br>3.6<br>1.8   | 38.5<br>24.5<br>15.2<br>9.3<br>6.3<br>4.3<br>2.2 | А    |       |

| I_OCH1_1 I_OCH2_1 I_OCM1_1 I_OCM2_1 I_OCL1_1 I_OCL2_1 I_OCL3_1                   | Overcurrent detection thresholds with CSNS_ratio bit = 1(CSR1)                                                                                                                                                                                                                                                                                 | 8.9<br>5.6<br>3.5<br>2.2<br>1.45<br>0.98<br>0.48 | 10.7<br>6.8<br>4.25<br>2.7<br>1.75<br>1.2<br>0.6 | 12.8<br>8.2<br>5.1<br>3.2<br>2.1<br>1.45<br>0.72 | A    |       |

| I <sub>OUT_LEAK</sub>                                                            | Output (HS[x]) leakage current in sleep state (positive value = outgoing)  • V <sub>HS,OFF</sub> = 0 V (V <sub>HS,OFF</sub> = output voltage in OFF state)  V <sub>HS,OFF</sub> = V <sub>PWR</sub> , device in sleep state (V <sub>PWR</sub> = 24 V)  V <sub>HS,OFF</sub> = V <sub>PWR</sub> , device in sleep state (V <sub>PWR</sub> = 36 V) | -<br>-120<br>-1400                               | _<br>_<br>_                                      | +5.0<br>+5.0<br>+5.0                             | μА   |       |

| I <sub>OUT_OFF</sub>                                                             | Output biasing current in off-state (positive value = outgoing) with OL_OFF disabled (worst case for V <sub>PWR</sub> = 36 V, V <sub>HS,OFF</sub> = 34 V) • Fast slew rate selected • Medium slew rate selected • Slow slew rate selected • With OL_OFF disabled and ECU ground disconnected (V <sub>PWR</sub> = 32 V)                         | -620<br>-440<br>-330                             | -495<br>-360<br>-280                             | -380<br>-280<br>-230<br>1000                     | μА   |       |

| V <sub>D_GND(CLAMP)</sub>                                                        | Switch turn-on threshold for supply overvoltage (V <sub>PWR</sub> -GND)                                                                                                                                                                                                                                                                        | 58                                               | _                                                | 67                                               | V    |       |

| V <sub>DS(CLAMP)</sub>                                                           | Switch turn-on threshold for Drain-Source overvoltage (measured at I <sub>OUT</sub> = 500 mA                                                                                                                                                                                                                                                   | 58                                               | _                                                | 66                                               | V    |       |

| $\Delta V_{DS(CLAMP)}$                                                           | Switch turn-on threshold for Drain-Source overvoltage difference from one channel to the other in Parallel mode (at $I_{HS} = 500$ mA)                                                                                                                                                                                                         | -2.0                                             | _                                                | +2.0                                             | V    |       |

22XS4200

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V and V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                               | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Min.                                                                              | Тур.                       | Max.                                          | Unit | Notes |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------|-----------------------------------------------|------|-------|

| Electrical charact                   | teristics of the output stage (HS0 and HS1) (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |                            |                                               | I    |       |

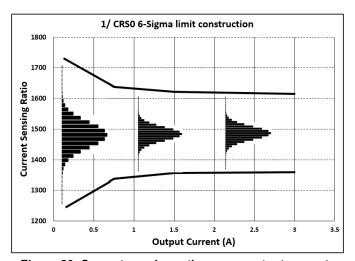

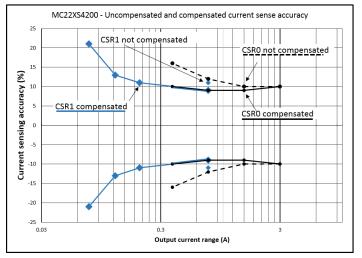

| C <sub>SR0</sub><br>C <sub>SR1</sub> | Current Sensing Ratio  CSNS_ratio bit = 0 (high current mode)  CSNS_ratio bit = 1 (low current mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -<br>-                                                                            | 1/1500<br>1/500            | _<br>_                                        | -    | (13)  |

| I_LOAD_MIN                           | Minimum measurable load current with compensated error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                 | _                          | 50                                            | mA   | (14)  |

| I <sub>CSR_LEAK</sub>                | CSNS leakage current in OFF state (CSNSx_en = 0, CSNS_ratio bit_x = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -4.0                                                                              | _                          | +4.0                                          | μΑ   |       |

| I_LOAD_ERR_SYS                       | Systematic offset error (see Current sense errors)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                 | -4.0                       | _                                             | mA   |       |

| I_LOAD_ERR_RAND                      | Random offset error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -125                                                                              | _                          | 125                                           | mA   |       |

| I <sub>CSNS,MAX</sub>                | CSNS pin current sourcing capability, absolute upper limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.15                                                                              | -                          | _                                             | mA   |       |

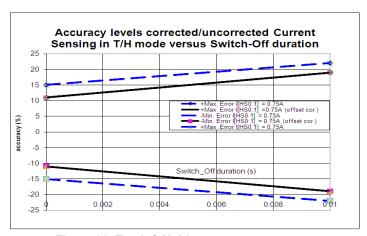

| E <sub>SR0_ERR</sub>                 | $\begin{split} &E_{SR0} \text{ output current sensing error (\%), uncompensated at output current level} \\ &(sense \text{ ratio } C_{SR0} \text{ selected}) \text{:} \\ &T_J = -40 ^\circC \\ & \cdot 3.0 A \\ & \cdot 1.5 A \\ & \cdot 0.75 A \\ & \cdot 0.375 A \\ & T_J = 125 ^\circC \\ & \cdot 3.0 A \\ & \cdot 1.5 A \\ & \cdot 0.75 A \\ & \cdot 0.375 A \\ & T_J = 25 ^\circC \text{ to } 125 ^\circC \\ & \cdot 3.0 A \\ & \cdot 1.5 A \\ & \cdot 0.75 A \\ & \cdot 0.375 A \end{split}$ | -13<br>-12<br>-17<br>-26<br>-10<br>-9.0<br>-12<br>-15<br>-10<br>-10<br>-12<br>-16 | -<br>-<br>-<br>-<br>-<br>- | 13<br>12<br>17<br>26<br>10<br>9.0<br>12<br>15 | %    | (15)  |

#### Notes:

- 13. Current sense ratio  $C_{SRx} = I_{CSNS} / (I_{HS[x]} + I_{LOAD\_ERR\_SYS})$

- 14. See note (15), but with I<sub>CSNS\_MEAS</sub> obtained after compensation of I<sub>LOAD\_ERR\_RAND</sub> (see Activation and use of offset compensation). Further accuracy improvements can be obtained by performing a 1 or 2 point calibration (see Application Note).

- 15. E<sub>SRx\_ERR</sub>=(I<sub>CSNS\_MEAS</sub> / I<sub>CSNS\_MODEL</sub>) -1, with I<sub>CSNS\_MODEL</sub> = (I(HS[x])+ I<sub>LOAD\_ERR\_SYS</sub>) \* C<sub>SRx\_</sub>, (I<sub>LOAD\_ERR\_SYS</sub> defined above, see section Current sense error model). With this model, load current becomes: I(HS[x]) = I<sub>CSNS</sub> / C<sub>SRx\_</sub> I<sub>LOAD\_ERR\_SYS</sub>

Unless specified otherwise:  $8.0 \text{ V} \le \text{V}_{PWR} \le 36 \text{ V}$ ,  $3.0 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$ ,  $-40 \,^{\circ}\text{C} \le \text{T}_{A} \le 125 \,^{\circ}\text{C}$ , GND = 0 V. Typical values are average values evaluated under nominal conditions  $\text{T}_{A}$  = 25  $^{\circ}\text{C}$ ,  $\text{V}_{PWR}$  = 28 V and  $\text{V}_{DD}$  = 5.0 V, unless specified otherwise.

| Symbol                      | Parameter                                                                                                                                    | Min.       | Тур. | Max. | Unit | Notes |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|------|-------|

| Electrical charact          | teristics of the output stage (HS0 and HS1) (continued)                                                                                      |            | l    | l    | ı    |       |

|                             | E <sub>SR0</sub> output current sensing error (%) after offset compensation at output current level (sense ratio C <sub>SR0</sub> selected): |            |      |      |      |       |

|                             | $T_J = -40$ °C                                                                                                                               | -11        | _    | 11   |      |       |

|                             | • 3.0 A                                                                                                                                      | -11        | _    | 11   |      |       |

|                             | • 1.5 A                                                                                                                                      | -11        |      | 11   |      |       |

|                             | • 0.75 A                                                                                                                                     | -11<br>-11 |      | 11   |      |       |

|                             | • 0.375 A                                                                                                                                    | -11        | _    | ''   |      |       |

|                             | T <sub>J</sub> = 125 °C                                                                                                                      | 0.0        |      | 0.0  |      | (16)  |

| $E_{SR0\_ERR}(Comp)$        | • 3.0 A                                                                                                                                      | -9.0       | _    | 9.0  | %    | (10)  |

|                             | • 1.5 A                                                                                                                                      | -9.0       | _    | 9.0  |      |       |

|                             | • 0.75 A                                                                                                                                     | -9.0       | _    | 9.0  |      |       |

|                             | • 0.375 A                                                                                                                                    | -10        | _    | 10   |      |       |

|                             | $T_J = 25 ^{\circ}\text{C}$ to 125 $^{\circ}\text{C}$                                                                                        |            |      |      |      |       |

|                             | • 3.0 A                                                                                                                                      | -10        | _    | 10   |      |       |

|                             | • 1.5 A                                                                                                                                      | -9.0       | _    | 9.0  |      |       |

|                             | • 0.75 A                                                                                                                                     | -9.0       | _    | 9.0  |      |       |

|                             | • 0.375 A                                                                                                                                    | -10        | _    | 10   |      |       |

|                             | $E_{SR1}$ output current sensing error (%), uncompensated at output current level (sense ratio $C_{SR1}$ selected):                          |            |      |      |      |       |

| Е                           | T <sub>J</sub> = -40 °C<br>• 0.75 A                                                                                                          | -16        | _    | 16   | 0/.  | (16)  |

| E <sub>SR1_ERR</sub>        | T <sub>J</sub> = 125 °C<br>• 0.75 A                                                                                                          | 40         |      | 40   | 70   | ( -7  |

|                             | T <sub>J</sub> = 25 °C to 125 °C                                                                                                             | -10        | _    | 10   |      |       |

|                             | • 0.75 A                                                                                                                                     | -12        | _    | 12   |      |       |

|                             | E <sub>SR1</sub> output current sensing error (%) after offset compensation at output                                                        |            |      |      | %    |       |

|                             | current level (sense ratio C <sub>SR1</sub> selected):<br>T <sub>.I</sub> = -40 °C                                                           |            |      |      |      |       |

|                             | · ·                                                                                                                                          | -11        | _    | 11   |      |       |

|                             | • 0.75 A                                                                                                                                     | -14        | _    | 14   |      |       |

|                             | • 0.25 A                                                                                                                                     | -19        | _    | 19   |      |       |

|                             | • 0.125 A                                                                                                                                    | -29        |      | 29   |      |       |

|                             | • 0.075 A                                                                                                                                    | -29        | _    | 29   |      |       |

|                             | T <sub>J</sub> = 125 °C                                                                                                                      | 0.0        |      | 0.0  |      | (17)  |

| E <sub>SR1_ERR</sub> (Comp) | • 0.75 A                                                                                                                                     | -9.0       | _    | 9.0  | %    | (17)  |

|                             | • 0.25 A                                                                                                                                     | -10        | _    | 10   |      |       |

|                             | • 0.125 A                                                                                                                                    | -12        | _    | 12   |      |       |

|                             | • 0.075 A                                                                                                                                    | -16        | _    | 16   |      |       |

|                             | $T_J = 25$ °C to 125 °C                                                                                                                      |            |      |      |      |       |

|                             | • 0.75 A                                                                                                                                     | -9.0       | _    | 9.0  |      |       |

|                             | • 0.25 A                                                                                                                                     | -11        | _    | 11   |      |       |

|                             | • 0.125 A                                                                                                                                    | -13        | _    | 13   |      |       |

|                             | • 0.075 A                                                                                                                                    | -21        | _    | 21   |      |       |

|                             |                                                                                                                                              |            |      |      |      |       |

#### Notes:

22XS4200

<sup>16.</sup> E<sub>SRx\_ERR</sub>=(I<sub>CSNS\_MEAS</sub> / I<sub>CSNS\_MODEL</sub>) -1, with I<sub>CSNS\_MODEL</sub> = (I(HS[x])+ I<sub>LOAD\_ERR\_SYS</sub>) \* C<sub>SRx\_</sub> (I<sub>LOAD\_ERR\_SYS</sub> defined above, see section Current sense error model). With this model, load current becomes: I(HS[x]) = I<sub>CSNS</sub> / C<sub>SRx</sub> - I<sub>LOAD\_ERR\_SYS</sub>

<sup>17.</sup> See note (18), but with I<sub>CSNS\_MEAS</sub> obtained after compensation of I<sub>LOAD\_ERR\_RAND</sub> (see Activation and use of offset compensation). Further accuracy improvements can be obtained by performing a 1 or 2 point calibration.

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V and V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                   | Parameter                                                                                                                                                                                              | Min.                  | Тур.                  | Max.                  | Unit | Notes |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|------|-------|

| Electrical charac        | teristics of the output stage (HS0 and HS1) (continued)                                                                                                                                                | I.                    |                       |                       |      | II.   |

|                          | E <sub>SR0</sub> output current sensing error in parallel mode (%), uncompensated) at outputs current level (sense ratio C <sub>SR0</sub> selected):                                                   |                       |                       |                       |      |       |

|                          | T <sub>J</sub> = -40 °C<br>• 6.0 A                                                                                                                                                                     | -10                   | _                     | 10                    |      |       |

|                          | • 3.0 A                                                                                                                                                                                                | -11                   | _                     | 11                    |      |       |

| E <sub>SR0_ERR_PAR</sub> | T <sub>.1</sub> = 125 °C                                                                                                                                                                               |                       |                       |                       | %    | (18)  |

| -SRU_ERR_PAR             | • 6.0 A                                                                                                                                                                                                | -8.0                  | _                     | 8.0                   | 70   |       |

|                          | • 3.0 A                                                                                                                                                                                                | -8.0                  | _                     | 8.0                   |      |       |

|                          | $T_J = 25$ °C to 125 °C                                                                                                                                                                                |                       |                       |                       |      |       |

|                          | • 6.0 A                                                                                                                                                                                                | -9.0                  | _                     | 9.0                   |      |       |

|                          | • 3.0 A                                                                                                                                                                                                | -9.0                  | _                     | 9.0                   |      |       |

| V <sub>CL(CSNS)</sub>    | Current sense clamping voltage (condition: R(CSNS) > 10 k $\Omega$ )                                                                                                                                   | 5.5                   | _                     | 7.5                   | V    |       |

| I <sub>OLD(OFF)</sub>    | Open load detection current threshold in OFF state                                                                                                                                                     | 30                    | -                     | 100                   | μΑ   |       |

| V <sub>OLD(THRES)</sub>  | Open load fault detection voltage threshold                                                                                                                                                            | 4.0                   | -                     | 5.5                   | V    |       |

| I <sub>OLD(ON)</sub>     | Open load detection current threshold in ON state (see Open load detection in On state (OL_ON)):  • CSNS_ratio bit = 0  • CSNS_ratio bit = 1 (fast slew rate SR[1:0] = 10 mandatory for this function) | 40<br>4.0             | 150<br>7.0            | 300<br>10             | mA   |       |

| tolled                   | Time period of the periodically activated open load in ON state detection for CSNS_ratio bit = 1                                                                                                       | 105                   | 150                   | 195                   | ms   |       |

| V <sub>OSD(THRES)</sub>  | Output shorted-to-V <sub>PWR</sub> detection voltage threshold (channel in OFF state)                                                                                                                  | V <sub>PWR</sub> -1.2 | V <sub>PWR</sub> -0.8 | V <sub>PWR</sub> -0.4 | V    |       |

| V <sub>CL</sub>          | Switch turn-on threshold for negative output voltages (protects against negative transients) - (measured at I <sub>OUT</sub> = 100mA, channel in OFF state)                                            | -38                   | -                     | -32                   | V    |       |

| $\Delta V_{CL}$          | Switch turn-on threshold for negative output voltages difference from one channel to the other in parallel mode - (measured at I <sub>OUT</sub> = 100 mA, channel in OFF state)                        | -2.0                  | -                     | +2.0                  | V    |       |

| V <sub>HS_TH</sub>       | Switching State (On/Off) discrimination thresholds                                                                                                                                                     | 0.45*V <sub>PWR</sub> | 0.5*V <sub>PWR</sub>  | 0.55*V <sub>PWR</sub> | V    |       |

| T <sub>SD</sub>          | Shutdown temperature (power MOSFET junction; 6.0 V < V <sub>PWR</sub> < 58 V)                                                                                                                          | 160                   | 175                   | 190                   | °C   |       |

#### Notes:

<sup>18.</sup> Minimum required value of open load impedance for detection of open load in OFF-state: 200 k $\Omega$ .( $V_{OLD(THRES)} = V_{HS}$  at  $I_{OLD(OFF)}$ )

Unless specified otherwise:  $8.0 \text{ V} \le \text{V}_{PWR} \le 36 \text{ V}$ ,  $3.0 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$ ,  $-40 \text{ °C} \le \text{T}_{A} \le 125 \text{ °C}$ , GND = 0 V. Typical values are average values evaluated under nominal conditions  $\text{T}_{A}$  = 25 °C,  $\text{V}_{PWR}$  = 28 V and  $\text{V}_{DD}$  = 5.0 V, unless specified otherwise.

| Symbol                | Parameter                                                                                                                                                     | Min.                 | Тур.   | Max.           | Unit | Notes |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|----------------|------|-------|

| Electrical chara      | cteristics of the control interface pins                                                                                                                      |                      | I      |                |      | ı     |

| V <sub>IH</sub>       | Logic input voltage, high                                                                                                                                     | 2.0                  | _      | 5.5            | V    | (19)  |

| V <sub>IL</sub>       | Logic input voltage, low                                                                                                                                      | -0.3                 | _      | 0.8            | V    | (19)  |

| $V_{WAKE}$            | Wake-up threshold voltage (IN[0:1] and RSTB)                                                                                                                  | 1.0                  | _      | 2.2            | V    | (20)  |

| I <sub>DWN</sub>      | Internal pull-down current source (on inputs: CLOCK, SCLK and SI)                                                                                             | 5.0                  | _      | 20             | μА   | (21)  |

| I <sub>UP_CSB</sub>   | Internal pull-up current source (input CSB)                                                                                                                   | 5.0                  | _      | 20             | μА   | (22)  |

| I <sub>UP_CONF</sub>  | Internal pull-up current source (input CONF[0:1])                                                                                                             | 25                   | -      | 100            | μА   | (23)  |

| C <sub>SO</sub>       | Capacitance of SO, FSB and FSOB pins in tri-state                                                                                                             | -                    | -      | 20             | pF   |       |

| R <sub>DWN</sub>      | Internal pull-down resistance (RSTB and IN[0:1])                                                                                                              | 125                  | 250    | 500            | kΩ   |       |

| C <sub>IN</sub>       | Input capacitance                                                                                                                                             | -                    | 4.0    | 12             | pF   | (24)  |

| $V_{SOH}$             | SO high-state output voltage • (I <sub>OH</sub> = 1.0 mA)                                                                                                     | V <sub>DD</sub> -0.4 | _      | _              | V    |       |

| $V_{SOL}$             | SYNC, SO, FSOB and FSB low-state output voltage • (I <sub>OL</sub> = -1.0 mA)                                                                                 | _                    | _      | 0.4            | V    |       |

| I <sub>SO(LEAK)</sub> | SYNC, SO, CSNS, FSOB and FSB tri-state leakage current:  • 0.0 V < V(SO) < V <sub>DD</sub> , or V(FS) or V(SYNC) = 5.5 V, or V(FSO) = 36 V or V(CSNS) = 0.0 V | -2.0                 | 0.0    | 2.0            | μА   |       |

| R <sub>CONF</sub>     | CONF[0:1]: Required values of the external pull-down resistor                                                                                                 | 1.0<br>50            | _<br>_ | 10<br>Infinite | kΩ   |       |

#### Notes

- 19. High and low voltage ranges apply to SI, CSB, SCLK, RSTB, IN[0:1] and CLOCK input signals. The IN[0:1] signals may be derived from V<sub>PWR</sub> and can tolerate voltages up to 58 V.

- 20. Voltage above which the device wakes up

- 21. Valid for  $V_{SI} \ge 0.8$  V and  $V_{SCLK} \ge 0.8$  V and  $V_{CLOCK} \ge 0.8$  V

- 22. Valid for  $V_{CSB} \le 2.0 \text{ V}$ . CSB has an internal pull-up current source derived from  $V_{DD}$

- 23. Pins CONF[0:1] are connected to an internal current source, derived from an internal voltage regulator (V<sub>REG</sub> ~ 3.0 V).

- 24. Input capacitance of SI, CSB, SCLK, RSTB, IN[0:1], CONF[0:1], and CLOCK pins. This parameter is guaranteed by the manufacturing process but is not tested in production.

# 4.3 Dynamic electrical characteristics

#### Table 5. Dynamic electrical characteristics

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V and V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                                   | Parameter                                                                                                                                                                                                          | Min.                    | Тур.              | Max.                 | Unit | Note       |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------|----------------------|------|------------|

| tput voltage                             | switching characteristics                                                                                                                                                                                          |                         | l                 |                      |      | _ <b>I</b> |

| SR <sub>R_00</sub><br>SR <sub>F_00</sub> | Rising and falling edges medium slew rate (SR[1:0] = 00)  • V <sub>PWR</sub> = 16 V  • V <sub>PWR</sub> = 28 V  • V <sub>PWR</sub> = 36 V                                                                          | 0.4<br>0.6<br>0.7       | -<br>-<br>-       | 1.2<br>1.8<br>2.1    | V/µs | (25)       |

| SR <sub>R_01</sub><br>SR <sub>F_01</sub> | Rising and falling edges low slew rate (SR[1:0] = 01)  • V <sub>PWR</sub> = 16 V  • V <sub>PWR</sub> = 28 V  • V <sub>PWR</sub> = 36 V                                                                             | 0.2<br>0.3<br>0.35      | -<br>-<br>-       | 0.6<br>0.9<br>1.05   | V/µs | (25)       |

| SR <sub>R_10</sub><br>SR <sub>F_10</sub> | Rising and falling edges high slew rate / SR[1:0] = 10)  • V <sub>PWR</sub> = 16 V  • V <sub>PWR</sub> = 28 V  • V <sub>PWR</sub> = 36 V                                                                           | 0.8<br>1.2<br>1.4       | -<br>-<br>-       | 2.5<br>3.6<br>4.2    | V/µs | (25)       |

| ΔSR                                      | Rising/falling edge slew rate matching (SR <sub>R</sub> /SR <sub>F</sub> ) • 16 V < V <sub>PWR</sub> < 36 V                                                                                                        | 0.75                    | _                 | 1.25                 |      |            |

| ΔSR                                      | Edge slew rate difference from one channel to the other in Parallel mode  16 V < V <sub>PWR</sub> < 36 V  SR[1:0] = 00  SR[1:0] = 01  SR[1:0] = 10                                                                 | -0.16<br>-0.08<br>-0.32 | 0.0<br>0.0<br>0.0 | 0.16<br>0.08<br>0.32 | V/µs | (25)       |

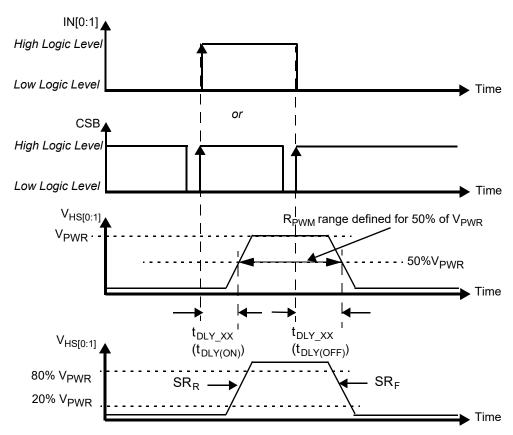

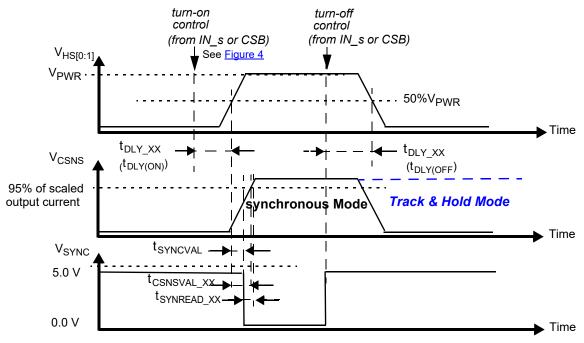

| t <sub>DLY_00</sub>                      | Output Turn-ON and Turn-OFF Delays (medium slew rate: SR[1:0] = 00) • 16 V < V <sub>PWR</sub> < 36 V                                                                                                               | 6.0                     | _                 | 60                   | μs   | (26)       |

| t <sub>DLY_01</sub>                      | Output Turn-ON and Turn-OFF delays (low slew rate / SR[1:0] = 01) • 16 V < V <sub>PWR</sub> < 36 V                                                                                                                 | 10                      | -                 | 120                  | μѕ   | (26)       |

| t <sub>DLY_10</sub>                      | Output Turn-ON and Turn-OFF delays (high slew rate / SR[1:0] = 10) • 16 V < V <sub>PWR</sub> < 36 V                                                                                                                | 4.0                     | _                 | 35                   | μs   | (26        |

| $\Delta t_{RF\_00}$                      | Turn-ON and Turn-OFF delay time matching $(t_{DLY(ON)} - t_{DLY(OFF)})$<br>• $f_{PWM} = 400$ Hz, 16 V < $V_{PWR} < 36$ V, duty cycle on $IN[x] = 50$ %, SR[1:0] = 00                                               | -25                     | _                 | 25                   | μs   |            |

| Δt <sub>RF_01</sub>                      | Turn-ON and Turn-OFF delay time matching $(t_{DLY(ON)} - t_{DLY(OFF)})$<br>• $f_{PWM} = 200$ Hz, 16 V < $V_{PWR}$ < 36 V, duty cycle on $IN[x] = 50$ %, SR[1:0] = 01                                               | -50                     | _                 | 50                   | μs   |            |

| Δt <sub>RF_10</sub>                      | Turn-ON and Turn-OFF Delay time matching $(t_{DLY(ON)} - t_{DLY(OFF)})$<br>• $f_{PWM} = 1.0 \text{ kHz}$ , $16 \text{ V} < \text{V}_{PWR} < 36 \text{ V}$ , duty cycle on $IN[x] = 50 \text{ \%}$ , $SR[1:0] = 10$ | -13                     | _                 | 13                   | μs   |            |

#### Notes

<sup>25.</sup> Rising and falling edge slew rates specified for a 20% to 80% voltage variation on a 10.0 Ω resistive load (see Output voltage slew rate and delay).

<sup>26.</sup> Turn-ON delay time measured as delay between a rising edge of the channel control signal (IN[0:1] = 1) and the associated rising edge of the output voltage up to:  $V_{HS[0:1]} = V_{PWR} / 2$  (where  $R_L = 25 \Omega$ ). Turn-OFF delay time is measured as time between a falling edge of the channel control signal (IN[0:1] = 0) and the associated falling edge of the output voltage up to the instant at which:  $V_{HS[0:1]} = V_{PWR} / 2$  ( $R_L = 25 \Omega$ )

Unless specified otherwise:  $8.0 \text{ V} \le \text{V}_{\text{PWR}} \le 36 \text{ V}$ ,  $3.0 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ ,  $-40 \,^{\circ}\text{C} \le \text{T}_{\text{A}} \le 125 \,^{\circ}\text{C}$ , GND = 0 V. Typical values are average values evaluated under nominal conditions  $\text{T}_{\text{A}} = 25 \,^{\circ}\text{C}$ ,  $\text{V}_{\text{PWR}} = 28 \text{ V}$  and  $\text{V}_{\text{DD}} = 5.0 \text{ V}$ , unless specified otherwise.

| Symbol                                     | Parameter                                                                                               | Min.        | Тур.        | Max.         | Unit | Notes |  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------|-------------|--------------|------|-------|--|

| utput voltage s                            | witching characteristics (continued)                                                                    |             | 1           |              | I    | I     |  |

| $\Delta t_{(DLY)}$                         | SR[1:0] = 01                                                                                            |             |             | 25<br>50     | μs   | (27)  |  |

|                                            | SR[1:0] = 10                                                                                            | -12         | 0.0         | 12           |      |       |  |