## 28-CHANNEL SONET/SDH VT MAPPER REGISTER DESCRIPTION WITH M13

JUNE 2010 REV. 2.0.0

#### GENERAL DESCRIPTION

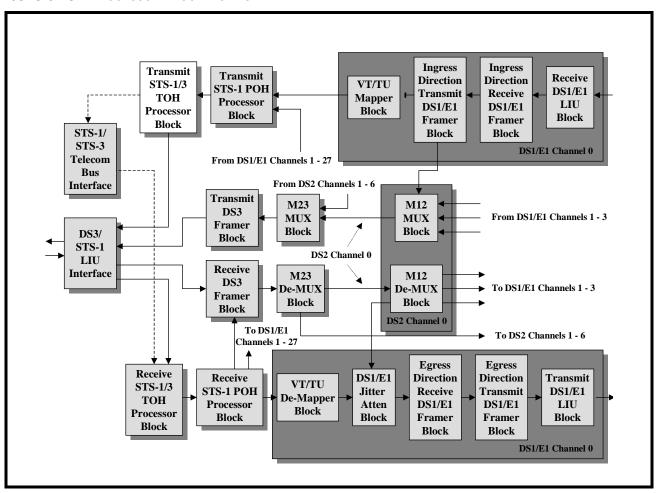

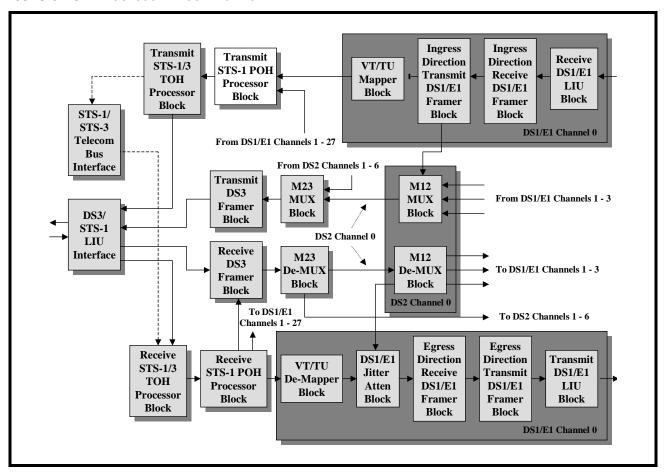

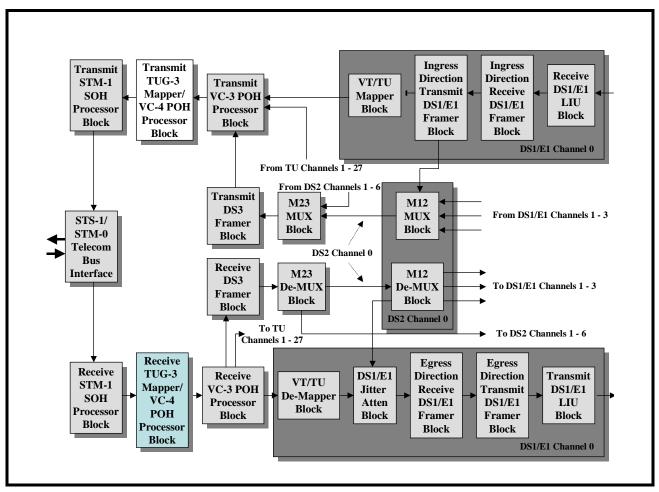

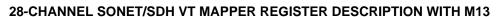

The XRT86SH328 is an integrated VT/TU Mapper with 28 port T1 or 21 port E1 Line Interface Units. The XRT86SH328 contains integrated DS1/E1/J1 Framers for performance monitoring.

The XRT86SH328 processes the Section, Line and Path overhead in the SONET/SDH data-stream. The processing of path overhead bytes within the STS-1s or TUG-3s include 64 bytes (of buffer) for storing the (Section Trace and Path Trace) messages. Path Overhead bytes can be accessed either by on-chip registers or a Serial Output Port.

Each of the T1 or E1 Channels use an internal De-Synchronizer circuit with an internal pointer leak algorithm. This removes the jitter due to mapping and pointer adjustments from the T1 or E1 signals that are de-mapped from the incoming SONET/SDH datastream. These De-Synchronizer circuits do not need any external clock references for its operation.

The Transmit Blocks permit flexible insertion of TOH and POH bytes via both Hardware and Software control.

The Receive Blocks receive a SONET STS-1 signals or an SDH STM-1 signal and performs the necessary Transport and Path Overhead Processing.

A PRBS Pattern Generator and Receiver is implemented within each of the T1/E1 channels in order to implement and measure Bit-Error performance.

A general purpose Microprocessor Interface is included for control, configuration and monitoring.

#### **FEATURES**

- Provides mapping of up to 28 T1 streams as Asynchronous VT1.5 into an STS-1 SPE or TU-11 tributary unit into an STM-1/VC-3 or TUG-3 from STM-1/ VC-4

- Supports 28 T1 streams M13 multiplexed into a serial DS3

- Supports 21 E1 streams M13 multiplexed into a serial DS3 (compliant with ITU-T G.747)

- 28 T1 Streams M13 Multiplexed into a DS3 and DS3 is asynchronously mapped into STS-1.

- 21 E1 Streams M13 Multiplexed into a DS3 (ITU-T G.747) and DS3 is asynchronously mapped into STS-1.

- Supports 21 E1 mapped as Asynchronous VT2 into an STS-1 SPE or TU-12 tributary units into STM-1/VC-3 or TUG-3 from a STM-1/VC-4.

- Supports TU cross-mapping function TU-12/VC-11/T1.

- Supports mixed mapping of VT-G/VT1.5 and VT-G/VT2.

- Supports mixed mapping of TUG-2/TU-11 and TUG-2/ TU-12

- 28 VT1.5/TU-11 or 21 VT-2/TU-12 tributaries can be passed as transparent between SONET/SDH Telecom Bus on the line side and Clock and Data on the system side.

- Supports Unframed T1/E1 signals

- Supports DS1/E1 Performance Monitoring in both Egress and Ingress direction

- VC-11/VC-12 Tandem Connection Monitoring support

- Complies with the Category I Intrinsic Jitter Requirements for DS1 signals being de-mapped from SONET, per Telcordia GR-253-CORE

- Complies with the "Mapping Jitter Generation Specification" for DS1 and E1 signals being de-mapped from SDH, per ITU-T G.783

- Complies with the "Combined Jitter Generation Specification" for DS1 and E1 signals being de-mapped from SDH, per ITU-T G.783

- Line and Facility Loop-backs

- Each of the 28 T1/E1 Channels includes a PRBS Generator and Receiver.

- Each of the 28 VT-Mapper blocks are capable of generating BIP-2 and REI errors upon software command (for diagnostic purposes).

- The Transmit and Receive DS3 Framer blocks support both the M13(M23) and the C-bit Parity Framing formats.

- Integrated 28 T1/E1/J1 Short-Haul Line Interface Units

- IEEE 1149.1 Standard Boundary Scan

- Low Power: 1.8V Power Supply for Core Logic; 3.3V Power Supply for I/O

- General Purpose Microprocessor Interface

#### **APPLICATIONS**

- Channelized and Unchannelized DS3 applications

- T1/E1 Terminals

- SONET/SDH ADM

REV. 2.0.0

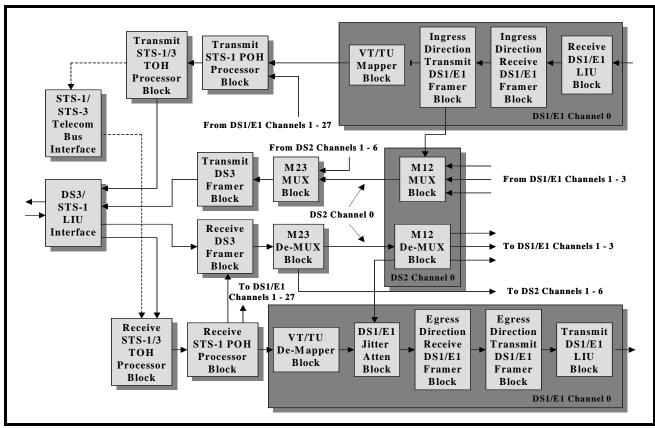

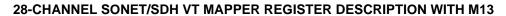

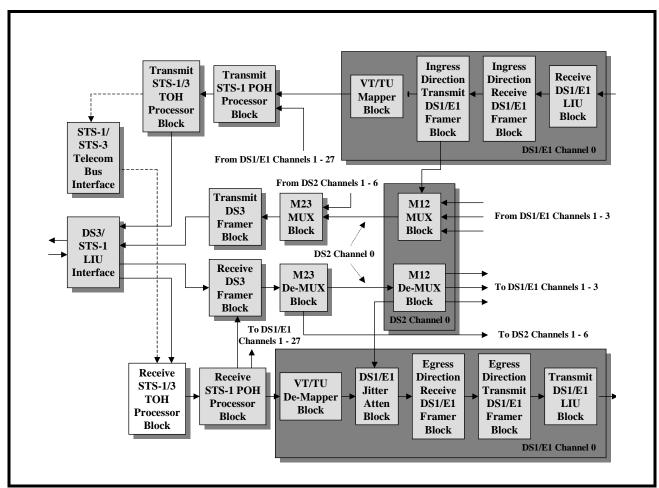

FIGURE 1. BLOCK DIAGRAM OF THE XRT86SH328

**TABLE 1: ORDERING INFORMATION**

| PRODUCT NUMBER | PACKAGE TYPE | OPERATING TEMPERATURE RANGE |  |  |

|----------------|--------------|-----------------------------|--|--|

| XRT86SH328IB   | 568 Ball BGA | -40°C to +85°C              |  |  |

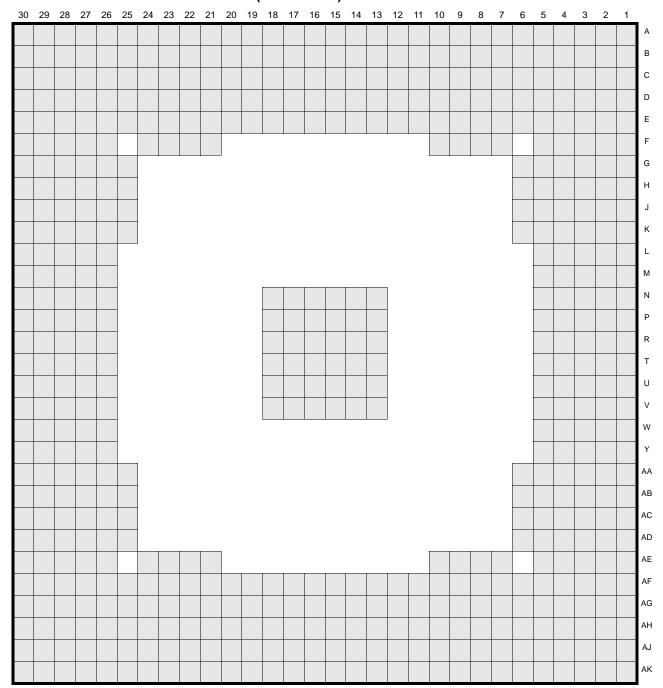

## FIGURE 2. PIN OUT OF THE XRT86SH328 (BOTTOM VIEW)

## **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                                                                                                                                                                          | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FEATURES                                                                                                                                                                                                                     | 1  |

| APPLICATIONS                                                                                                                                                                                                                 |    |

| Figure 1. Block Diagram of the XRT86SH328                                                                                                                                                                                    |    |

| TABLE 1: ORDERING INFORMATION                                                                                                                                                                                                |    |

| FIGURE 2. PIN OUT OF THE XRT86SH328 (BOTTOM VIEW)                                                                                                                                                                            |    |

| TABLE OF CONTENTS                                                                                                                                                                                                            |    |

| 1.0 REGISTER MAP & DESCRIPTION FOR THE XRT86SH328 SONET/SDH WITH DS3 MUX AND VT-                                                                                                                                             |    |

|                                                                                                                                                                                                                              |    |

| PER IC - SONET APPLICATIONS                                                                                                                                                                                                  |    |

| 1.1 REGISTER MAP OF THE XRT86SH328                                                                                                                                                                                           |    |

| TABLE 2: OPERATION CONTROL REGISTERS                                                                                                                                                                                         |    |

| TABLE 3: RECEIVE STS-1/STS-3 TOH PROCESSOR BLOCK REGISTERS                                                                                                                                                                   | _  |

| TABLE 4: RECEIVE STS-1/STS-3 PUH PROCESSOR BLOCK REGISTERS                                                                                                                                                                   |    |

| TABLE 5. RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SECTION TRACE MESSAGE BUFFER                                                                                                                                                |    |

| TABLE 0. RECEIVE STS-1/STS-S FATH - RECEIVE FATH TRACE WIESSAGE BUFFER                                                                                                                                                       |    |

| TABLE 7: RECEIVE TU-3 FOTT FROCESSOR BLOCK REGISTERS (SDT/TOG-3 APPLICATIONS ONLY)                                                                                                                                           |    |

| TABLE 9: TRANSMIT STS-1/STS-3 TOH PROCESSOR BLOCK REGISTERS                                                                                                                                                                  |    |

| TABLE 10: TRANSMIT STS-1/STS-3 POH PROCESSOR BLOCK REGISTERS                                                                                                                                                                 |    |

| TABLE 11: TRANSMIT STS-1/STS-3 TOH PROCESSOR BLOCK - TRANSMIT SECTION TRACE MESSAGE BUFFER                                                                                                                                   |    |

| TABLE 12: TRANSMIT STS-1/STS-3 POH PROCESSOR BLOCK - TRANSMIT PATH TRACE MESSAGE BUFFER                                                                                                                                      |    |

| TABLE 13: TRANSMIT TU-3 POH PROCESSOR BLOCK REGISTERS (SDH/TUG-3 APPLICATIONS ONLY)                                                                                                                                          | 18 |

| TABLE 14: TRANSMIT TU-3 POH PROCESSOR BLOCK - TRANSMIT PATH TRACE MESSAGE BUFFER                                                                                                                                             | 20 |

| TABLE 15: VT MAPPER CONTROL REGISTERS                                                                                                                                                                                        |    |

| TABLE 16: DS3 MAPPER CONTROL REGISTERS                                                                                                                                                                                       |    |

| TABLE 17: DS3 FRAMER AND M13 MUX BLOCK REGISTERS                                                                                                                                                                             |    |

| TABLE 18: VT MAPPER REGISTER (WHERE N RANGES IN VALUE FROM 0x01 TO 0x1C)                                                                                                                                                     |    |

| 2.0 REGISTER DESCRIPTIONS                                                                                                                                                                                                    |    |

| TABLE 19: OPERATION CONTROL REGISTER - BYTE 3 (ADDRESS = 0x0000)                                                                                                                                                             |    |

| 2.1 OPERATION CONTROL REGISTERS                                                                                                                                                                                              |    |

| TABLE 20: OPERATION CONTROL REGISTER - BYTE 3 (ADDRESS = 0x0000)                                                                                                                                                             |    |

| TABLE 21: OPERATION CONTROL REGISTER - BYTE 2 (ADDRESS = 0x0001)                                                                                                                                                             |    |

| TABLE 22: OPERATION CONTROL REGISTER - BYTE 0 (ADDRESS = 0x0003)                                                                                                                                                             |    |

| TABLE 23: DEVICE ID VALUE REGISTER - BYTE 3 (ADDRESS = 0x0004)                                                                                                                                                               |    |

| TABLE 24: REVISION NUMBER VALUE REGISTER - BYTE 2 (ADDRESS = 0x0005)                                                                                                                                                         |    |

| TABLE 26: OPERATION INTERRUPT STATUS REGISTER - BYTE 0 (ADDRESS = 0X000F)                                                                                                                                                    |    |

| TABLE 27: OPERATION INTERRUPT ENABLE REGISTER - BYTE 1 (ADDRESS = 0X0001)                                                                                                                                                    |    |

| TABLE 28: OPERATION BLOCK INTERRUPT STATUS REGISTER - BYTE 1 (ADDRESS = 0x0012)                                                                                                                                              |    |

| TABLE 29: OPERATION BLOCK INTERRUPT ENABLE REGISTER - BYTE 1 (ADDRESS = 0x0016)                                                                                                                                              |    |

| TABLE 30: OPERATION BLOCK INTERRUPT ENABLE REGISTER - BYTE 0 (ADDRESS = 0x0017)                                                                                                                                              |    |

| TABLE 31: MODE CONTROL REGISTER - BYTE 0 (ADDRESS = 0x001B)                                                                                                                                                                  |    |

| TABLE 32: LOOP-BACK CONTROL REGISTER - BYTE 0 (ADDRESS = 0X001F)                                                                                                                                                             |    |

| TABLE 33: STS-1/STS-3 TELECOM BUS CONTROL REGISTER - BYTE 3 (ADDRESS = 0x0034)                                                                                                                                               | 38 |

| TABLE 34: STS-1/STS-3 TELECOM BUS CONTROL REGISTER - BYTE 2 (ADDRESS = 0x0035)                                                                                                                                               |    |

| TABLE 35: STS-3/STS-1/STS-3 TELECOM BUS CONTROL REGISTER - BYTE 1 (ADDRESS = 0x0036)                                                                                                                                         |    |

| TABLE 36: STS-3/STS-1/STS-3 TELECOM BUS CONTROL REGISTER - BYTE 0 (ADDRESS = 0x0037)                                                                                                                                         |    |

| TABLE 37: OPERATION BLOCK - INTERFACE CONTROL REGISTER (ADDRESS = 0x003C)                                                                                                                                                    |    |

| TABLE 38: OPERATION GENERAL PURPOSE INPUT/OUTPUT REGISTER - BYTE 0 (ADDRESS = 0x0047)                                                                                                                                        |    |

| TABLE 39: OPERATION GENERAL PURPOSE INPUT/OUTPUT DIRECTION REGISTER 0 (ADDRESS = 0X004B)                                                                                                                                     |    |

| TABLE 40: OPERATION I/O CONTROL REGISTER 1 (ADDRESS = 0X004E)                                                                                                                                                                |    |

| TABLE 41: OPERATION I/O CONTROL REGISTER 0 (ADDRESS = 0x004F)                                                                                                                                                                |    |

| TABLE 42: BIT FIELD CONTENTS FOR RECOVERED LINE CLOCK SELECT                                                                                                                                                                 |    |

| TABLE 44: CHANNEL INTERRUPT INDICATION REGISTER - DS 1/E 1 FRAMER (VT SIDE) BLOCK - BYTE 3 (ADDRESS = 0x0030)  TABLE 44: CHANNEL INTERRUPT INDICATION REGISTER - DS 1/E 1 FRAMER (VT SIDE) BLOCK - BYTE 2 (ADDRESS = 0x0051) |    |

| TABLE 45: CHANNEL INTERRUPT INDICATION REGISTER - DS 1/E 1 FRAMER (VT SIDE) BLOCK - BYTE 2 (ADDRESS = 0X0051)  TABLE 45: CHANNEL INTERRUPT INDICATION REGISTER - DS 1/E 1 FRAMER (VT SIDE) BLOCK - BYTE 1 (ADDRESS = 0X0052) |    |

| TABLE 46: CHANNEL INTERRUPT INDICATION REGISTER - DS 1/E1 FRAMER (VT SIDE) BLOCK - BYTE 1 (ADDRESS = 0x0052)  TABLE 46: CHANNEL INTERRUPT INDICATION REGISTER - DS 1/E1 FRAMER (VT SIDE) BLOCK - BYTE 0 (ADDRESS = 0x0053)   |    |

| TABLE 47: CHANNEL INTERRUPT INDICATION REGISTER - DS1/E1 FRAMER (M13 SIDE) BLOCK - BYTE 3 (ADDRESS = 0x0054)                                                                                                                 |    |

| Table 48: Channel Interrupt Indication Register - DS1/E1 Framer (M13 Side) Block - Byte 2 (Address = 0x0055)                                                                                                                 |    |

| TABLE 49: CHANNEL INTERRUPT INDICATION REGISTER - DS1/E1 FRAMER (M13 SIDE) BLOCK - BYTE 1 (ADDRESS = 0x0056)                                                                                                                 |    |

| TABLE 50: CHANNEL INTERRUPT INDICATION REGISTER - DS1/E1 FRAMER (M13 SIDE) BLOCK - BYTE 0 (ADDRESS = 0x0057)                                                                                                                 |    |

| TABLE 51: CHANNEL INTERRUPT INDICATION REGISTER - DS1/E1 LIU BLOCK - BYTE 3 (ADDRESS = 0x0058)                                                                                                                               | 49 |

|                                                                                                                                                                                                                              |    |

#### REV. 2.0.0

## 28-CHANNEL SONET/SDH VT MAPPER REGISTER DESCRIPTION WITH M13

|   | TABLE 52: | CHANNEL INTERRUPT INDICATION REGISTER - DS1/E1 LIU BLOCK - BYTE 2 (ADDRESS = 0x0059)                    | 49    |

|---|-----------|---------------------------------------------------------------------------------------------------------|-------|

|   | TABLE 53: | CHANNEL INTERRUPT INDICATION REGISTER - DS1/E1 LIU BLOCK - BYTE 1 (ADDRESS = 0x005A)                    | 50    |

|   | TABLE 54: | CHANNEL INTERRUPT INDICATION REGISTER - DS1/E1 LIU BLOCK - BYTE 0 (ADDRESS = 0x005B)                    | 50    |

|   | TABLE 55: | CHANNEL INTERRUPT INDICATION REGISTER - VT-MAPPER BLOCK - BYTE 3 (ADDRESS = 0x005C)                     | 50    |

|   | TABLE 56: | CHANNEL INTERRUPT INDICATION REGISTER - VT-MAPPER BLOCK - BYTE 2 (ADDRESS = 0x005D)                     | 51    |

|   |           | CHANNEL INTERRUPT INDICATION REGISTER - VT-MAPPER BLOCK - BYTE 1 (ADDRESS = 0x005E)                     |       |

|   |           | CHANNEL INTERRUPT INDICATION REGISTER - VT-MAPPER BLOCK - BYTE 0 (ADDRESS = 0x005F)                     |       |

|   |           | CHANNEL DE-JITTER FIFO DEPTH REGISTER - VT-MAPPER BLOCK - BYTE 3 (ADDRESS = 0x0080)                     |       |

|   |           | CHANNEL DE-JITTER FIFO DEPTH REGISTER - VT-MAPPER BLOCK - BYTE 2 (ADDRESS = 0x0081)                     |       |

|   |           | CHANNEL DE-JITTER FIFO DEPTH REGISTER - VT-MAPPER BLOCK - BYTE 1 (ADDRESS = 0x0082)                     |       |

|   |           | CHANNEL DE-JITTER FIFO DEPTH REGISTER - VT-MAPPER BLOCK - BYTE 0 (ADDRESS = 0x0083)                     |       |

|   |           | CHANNEL DE-JITTER FIFO STATUS REGISTER - VT-MAPPER BLOCK - BYTE 3 (ADDRESS = 0x0084)                    |       |

|   |           | CHANNEL DE-JITTER FIFO STATUS REGISTER - VT-MAPPER BLOCK - BYTE 2 (ADDRESS = 0x0085)                    |       |

|   |           | CHANNEL DE-JITTER FIFO STATUS REGISTER - VT-MAPPER BLOCK - BYTE 1 (ADDRESS = 0x0086)                    |       |

|   |           | CHANNEL DE-JITTER FIFO STATUS REGISTER - VT-MAPPER BLOCK - BYTE 0 (ADDRESS = 0x0087)                    |       |

| 2 |           | VE STS-1/STS-3 TOH PROCESSOR BLOCK REGISTERS                                                            |       |

| _ |           | ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328, WITH THE RECEIVE STS-1/STS-3 TOH PROCES |       |

|   |           |                                                                                                         |       |

|   |           | BLOCK HIGHLIGHTED                                                                                       |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT CONTROL REGISTER - BYTE 1 (ADDRESS LOCATION = 0x0202)                     |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT CONTROL REGISTER - BYTE 0 (ADDRESS LOCATION = 0x0203)                     |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT STATUS REGISTER - BYTE 1 (ADDRESS LOCATION= 0x0206)                       |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT STATUS REGISTER - BYTE 0 (ADDRESS LOCATION = 0x0207)                      |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT INTERRUPT STATUS REGISTER - BYTE 2 (ADDRESS LOCATION= 0x0209)             |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT INTERRUPT STATUS REGISTER - BYTE 1 (ADDRESS LOCATION= 0x020A)             |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT INTERRUPT STATUS REGISTER - BYTE 0 (ADDRESS LOCATION= 0x020B)             |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT INTERRUPT ENABLE REGISTER - BYTE 2 (ADDRESS LOCATION= 0x020D)             |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT INTERRUPT ENABLE REGISTER - BYTE 1 (ADDRESS LOCATION= 0x020E)             |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT INTERRUPT STATUS REGISTER - BYTE 0 (ADDRESS LOCATION= 0x020F)             |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - B1 BYTE ERROR COUNT REGISTER - BYTE 3 (ADDRESS LOCATION= 0x0210)        |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - B1 BYTE ERROR COUNT REGISTER - BYTE 2 (ADDRESS LOCATION= 0x0211)        |       |

|   | TABLE 79: | RECEIVE STS-1/STS-3 TRANSPORT - B1 BYTE ERROR COUNT REGISTER - BYTE 1 (ADDRESS LOCATION= 0x0212)        | 69    |

|   | TABLE 80: | RECEIVE STS-1/STS-3 TRANSPORT - B1 BYTE ERROR COUNT REGISTER - BYTE 0 (ADDRESS LOCATION= 0x0213)        | 69    |

|   | TABLE 81: | RECEIVE STS-1/STS-3 TRANSPORT - B2 BYTE ERROR COUNT REGISTER - BYTE 3 (ADDRESS LOCATION= 0x0214)        | 70    |

|   | TABLE 82: | RECEIVE STS-1/STS-3 TRANSPORT - B2 BYTE ERROR COUNT REGISTER - BYTE 2 (ADDRESS LOCATION= 0x0215)        | 70    |

|   | TABLE 83: | RECEIVE STS-1/STS-3 TRANSPORT - B2 BYTE ERROR COUNT REGISTER - BYTE 1 (ADDRESS LOCATION= 0x0216)        | 70    |

|   | TABLE 84: | RECEIVE STS-1/STS-3 TRANSPORT - B2 BYTE ERROR COUNT REGISTER - BYTE 0 (ADDRESS LOCATION= 0X0217)        | 71    |

|   | TABLE 85: | RECEIVE STS-1/STS-3 TRANSPORT - REI-L EVENT COUNT REGISTER - BYTE 3 (ADDRESS LOCATION = 0x0218)         | 71    |

|   | TABLE 86: | RECEIVE STS-1/STS-3 TRANSPORT - REI-L EVENT COUNT REGISTER - BYTE 2 (ADDRESS LOCATION= 0X0219)          | 72    |

|   | TABLE 87: | RECEIVE STS-1/STS-3 TRANSPORT - REI-L EVENT COUNT REGISTER - BYTE 1 (ADDRESS LOCATION= 0X021A)          | 72    |

|   | TABLE 88: | RECEIVE STS-1/STS-3 TRANSPORT - REI-L EVENT COUNT REGISTER - BYTE 0 (ADDRESS LOCATION= 0x021B)          | 72    |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVED K1 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x021F)              |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVED K2 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x0223)              |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVED S1 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x0227)              |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE IN-SYNC THRESHOLD REGISTER (ADDRESS = 0x022B)                   |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - LOS THRESHOLD VALUE - MSB (ADDRESS LOCATION= 0x022E)                    |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - LOS THRESHOLD VALUE - LSB (ADDRESS LOCATION= 0x022F)                    |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SF SET MONITOR INTERVAL - BYTE 2 (ADDRESS LOCATION= 0x0231)     |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SF SET MONITOR INTERVAL - BYTE 1 (ADDRESS LOCATION= 0x0232)     |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SF SET MONITOR INTERVAL - BYTE 0 (ADDRESS LOCATION= 0x0233)     |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SF SET THRESHOLD - BYTE 1 (ADDRESS LOCATION= 0x0236)            |       |

|   |           | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SF SET THRESHOLD - BYTE 1 (ADDRESS ECCATION= 0x0230)            |       |

|   |           | D: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SF CLEAR THRESHOLD - BYTE 1 (ADDRESS LOCATION= 0x023A)       |       |

|   |           | : RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SF CLEAR THRESHOLD - BYTE 0 (ADDRESS LOCATION= 0x023A)        |       |

|   |           |                                                                                                         |       |

|   |           | 2: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SD SET MONITOR INTERVAL - BYTE 2 (ADDRESS LOCATION= 0X023D)  |       |

|   |           | 3: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SD SET MONITOR INTERVAL - BYTE 1 (ADDRESS LOCATION= 0X023E)  |       |

|   |           | 1: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SD SET MONITOR INTERVAL - BYTE 0 (ADDRESS LOCATION= 0x023F)  |       |

|   |           | 5: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SD SET THRESHOLD - BYTE 1 (ADDRESS LOCATION= 0X0242)         |       |

|   |           | 6: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SD SET THRESHOLD - BYTE 0 (ADDRESS LOCATION= 0X0243)         |       |

|   |           | 7: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SD CLEAR THRESHOLD - BYTE 1 (ADDRESS LOCATION= 0X0246)       |       |

|   |           | 3: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SD CLEAR THRESHOLD - BYTE 1 (ADDRESS LOCATION= 0x0247)       |       |

|   |           | 2: RECEIVE STS-1/STS-3 TRANSPORT - FORCE SEF DEFECT CONDITION REGISTER (ADDRESS LOCATION= 0x024B)       |       |

|   |           | ): RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SECTION TRACE MESSAGE BUFFER CONTROL REGISTER (ADDRESS LOCAT |       |

|   |           | 0x024F)                                                                                                 |       |

|   |           | I: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SD BURST ERROR TOLERANCE - BYTE 1 (ADDRESS LOCATION= 0x0252  |       |

|   |           | 2: RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SD BURST ERROR TOLERANCE - BYTE 0 (ADDRESS LOCATION= 0x0253  |       |

|   | TABLE 113 | RECEIVE STS-1/STS-3 TRANSPORT - RECEIVE SE BURST ERROR TOLERANCE - RYTE 1 (ADDRESS LOCATION— 0Y0256     | 1) 83 |

## 28-CHANNEL SONET/SDH VT MAPPER REGISTER DESCRIPTION WITH M13

REV. 2.0.0

|          |        |          |       |         | TRANSPORT    |              |          |             |             |           |                    |            |          |                   |

|----------|--------|----------|-------|---------|--------------|--------------|----------|-------------|-------------|-----------|--------------------|------------|----------|-------------------|

|          |        |          |       |         | TRANSPORT    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | TRANSPORT    |              |          |             |             |           |                    |            |          |                   |

| TABLE    | 117:   | RECEIVE  | STS-1 | /STS-3  | TRANSPORT    | - RECEIVE SI | O CLEAR  | MONITOR IN  | ITERVAL - E | BYTE 0 (  | ADDRESS            | LOCATION=  | = 0x025E | B) 84             |

| TABLE    | 118:   | RECEIVE  | STS-1 | /STS-3  | TRANSPORT    | - RECEIVE SF | CLEAR I  | MONITOR IN  | ITERVAL - E | 3YTE 2 (A | ADDRESS            | LOCATION=  | = 0x025L | D) 85             |

| TABLE    | 119:   | RECEIVE  | STS-1 | /STS-3  | TRANSPORT    | - RECEIVE SF | CLEAR I  | MONITOR IN  | ITERVAL - E | 3YTE 1 () | ADDRESS            | LOCATION=  | : 0x025E | ≣) 85             |

| TABLE    | 120:   | RECEIVE  | STS-1 | /STS-3  | TRANSPORT    | - RECEIVE SF | CLEAR I  | MONITOR IN  | ITERVAL - E | 3YTE 0 (A | ADDRESS            | LOCATION=  | : 0x025F | <del>-</del> ) 86 |

| TABLE    | 121:   | RECEIVE  | STS-1 | /STS-3  | TRANSPORT    | - Auto AIS C | CONTROL  | REGISTER (  | ADDRESS     | LOCATIO   | $N = 0 \times 026$ | 53)        |          | . 86              |

| TABLE    | 122:   | RECEIVE  | STS-1 | /STS-3  | TRANSPORT    | - SERIAL POP | RT CONTR | ROL REGISTE | ER (ADDRE   | ss Loca   | TION= 0x           | 0267)      |          | . 88              |

| TABLE    | 123:   | RECEIVE  | STS-1 | /STS-3  | TRANSPORT    | - AUTO AIS ( | IN DOWN  | STREAM T1/  | E1s) Con    | TROL RE   | GISTER (A          | ADDRESS LO | OCATION: | =                 |

|          | 0      | х026B).  |       |         |              |              |          |             |             |           |                    |            |          | . 88              |

| TABLE    | 124:   | RECEIVE  | STS-1 | /STS-3  | TRANSPORT    | - A1, A2 BYT | E ERROR  | COUNT RE    | GISTER - B  | BYTE 1 (A | ADDRESS I          | LOCATION=  | 0x026E   | 90 (              |

|          |        |          |       |         | TRANSPORT    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | TRANSPORT -  |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         |              |              |          |             |             |           |                    | •          |          |                   |

| TABLE    |        |          |       |         | TRANSPORT -  |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         |              |              |          |             |             |           |                    |            |          |                   |

| TABLE    |        |          |       |         | TRANSPORT    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         |              |              |          |             |             |           |                    |            |          |                   |

| 2.3 RE   |        |          |       |         | CESSOR E     |              |          |             |             |           |                    |            |          |                   |

| FIGURE   | = 4 li | LUSTRATI | ONOF  | THE FUN | ICTIONAL BLO | CK DIAGRAM   | OF THE X | RT86SH32    | 8 WITH THI  | E RECEIN  | /F.STS-1           | POH Proc   | ESSOR F  | BLOCK             |

| 7 700712 |        |          |       |         |              |              |          |             |             |           |                    |            |          |                   |

| TARIF    |        |          |       |         | RECEIVE CO.  |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | CONTROL RE   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | SONET REC    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | SONET REC    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | SONET REC    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | SONET REC    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | SONET REC    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | SONET REC    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | SONET REC    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | SONET REC    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVED P   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | EXPECTED P   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | - B3 BYTE ER |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | - B3 BYTE ER |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | - B3 BYTE ER |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | - B3 BYTE ER |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | REI-P EVEN   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | REI-P EVEN   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | REI-P EVEN   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | REI-P EVEN   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE PA   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | POINTER VAL  |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | POINTER VAL  |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | Loss of Po   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | · AIS CONCAT |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE AU   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE AU   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | AUTO AIS (   |              |          |             | •           |           | ,                  |            |          |                   |

|          |        |          |       |         | SERIAL PORT  |              | •        |             |             | ,         |                    |            |          |                   |

|          |        |          |       |         | SONET REC    |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE NE   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE NE   |              |          |             |             |           | ,                  |            | ,        |                   |

|          |        |          |       |         | RECEIVE PO   |              |          |             |             |           | •                  |            | ,        |                   |

|          |        |          |       |         | RECEIVE PO   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         |              |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE J1   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE B3   |              |          | •           |             |           | ,                  |            |          |                   |

|          |        |          |       |         | RECEIVE C2   |              |          | ,           |             |           | ,                  |            |          |                   |

|          |        |          |       |         | RECEIVE G1   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE F2   |              |          | •           |             |           | ,                  |            |          |                   |

|          |        |          |       |         | RECEIVE H4   |              |          | ,           |             |           | ,                  |            |          |                   |

|          |        |          |       |         | RECEIVE Z3   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE Z4   |              |          |             |             |           |                    |            |          |                   |

|          |        |          |       |         | RECEIVE Z5   |              |          |             |             |           |                    |            |          |                   |

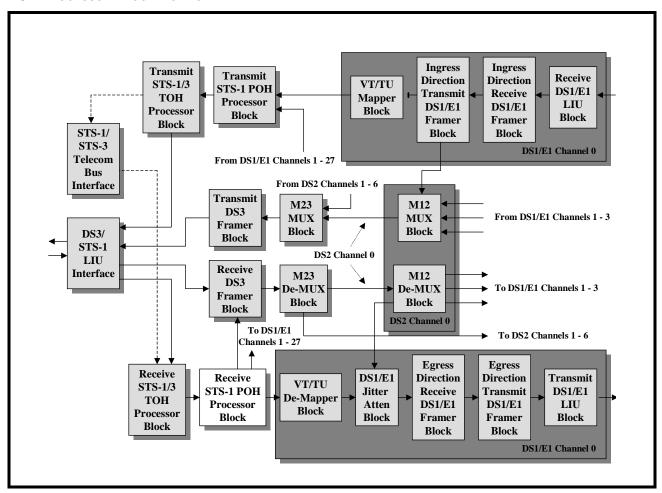

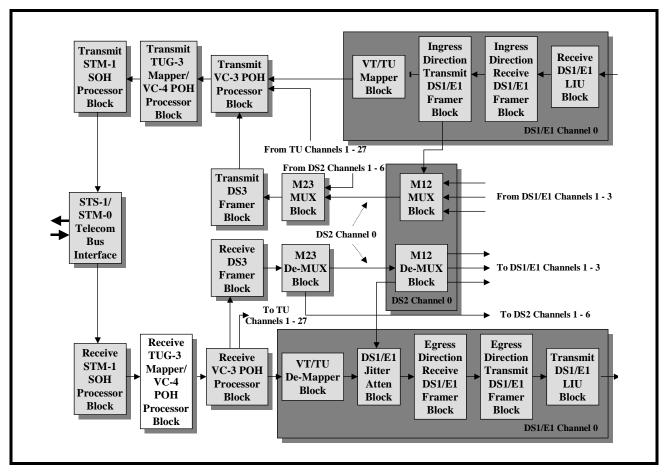

| 2.4 RE(  | ۱۷عر   | '⊏ IUG-  | 3 WAI | PER/    | VC-4 POH I   | -KUCESS(     | OK BLC   | JCK REGI    | SIERS (     | SDH/T     | UG-3 AF            | PLICATI    | UNS O    | NLY               |

120

| FIGURE 5. ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328 DEVICE, WITH THE RECEIVE TUG-3 MAPPER                                                                                                                   |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| POH Processor block "Highlighted"                                                                                                                                                                                                |            |

| 2.5 TRANSMIT STS-1/STS-3 TOH PROCESSOR BLOCK REGISTERS                                                                                                                                                                           | 120        |

| FIGURE 6. ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328, WITH THE TRANSMIT STS-1/STS-3 TOH PL                                                                                                                   | ROCES      |

| SOR BLOCK HIGHLIGHTED                                                                                                                                                                                                            |            |

| TABLE 172: TRANSMIT STS-1/STS-3 TRANSPORT- TRANSMIT CONTROL REGISTER - BYTE 3 (ADDRESS LOCATION = 0x0700)  TABLE 173: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT CONTROL REGISTER - BYTE 2 (ADDRESS LOCATION = 0x0701)            |            |

| TABLE 173. TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT CONTROL REGISTER - BYTE 2 (ADDRESS LOCATION = 0X0701)  TABLE 174: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT CONTROL REGISTER - BYTE 1 (ADDRESS LOCATION= 0X0702)            |            |

| TABLE 174: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSPORT - TRANSMIT CONTROL REGISTER - BYTE 1 (ADDRESS LOCATION= 0x0702)  TABLE 175: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT CONTROL REGISTER - BYTE 0 (ADDRESS LOCATION= 0x0703) |            |

| TABLE 176: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSPORT - TRANSMIT CONTROL REGISTER - BYTE O (ADDRESS LOCATION = 0X0713)  TABLE 176: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT A1 BYTE ERROR REGISTER (ADDRESS LOCATION = 0X0717)  |            |

| TABLE 170: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT AT BITE ERROR REGISTER (ADDRESS LOCATION = 0x0717)  TABLE 177: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT A2 BYTE ERROR REGISTER (ADDRESS LOCATION = 0x071F)                 |            |

| TABLE 178: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT B1 BYTE ERROR MASK REGISTER (ADDRESS LOCATION = 0x0723)                                                                                                                     |            |

| TABLE 179: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT BY BYTE ERROR MASK REGISTER (ADDRESS LOCATION = 0x0727)                                                                                                                     |            |

| TABLE 180: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMIT B2 BIT ERROR MASK REGISTER (ADDRESS LOCATION= 0x072B)                                                                                                                       |            |

| TABLE 181: TRANSMIT STS-1/STS-3 TRANSPORT - K2 BYTE VALUE REGISTER - BYTE 1 (ADDRESS LOCATION= 0x072E)                                                                                                                           |            |

| TABLE 182: TRANSMIT STS-1/STS-3 TRANSPORT - K1 BYTE VALUE REGISTER - BYTE 1 (ADDRESS LOCATION= 0x072F)                                                                                                                           |            |

| TABLE 183: TRANSMIT STS-1/STS-3 TRANSPORT - RDI-L CONTROL REGISTER (ADDRESS LOCATION= 0x0733)                                                                                                                                    |            |

| TABLE 184: TRANSMIT STS-1/STS-3 TRANSPORT - MOM1 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x0737)                                                                                                                                  |            |

| TABLE 185: TRANSMIT STS-1/STS-3 TRANSPORT - S1 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x073B)                                                                                                                                    |            |

| TABLE 186: TRANSMIT STS-1/STS-3 TRANSPORT - F1 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x073F)                                                                                                                                    |            |

| TABLE 187: TRANSMIT STS-1/STS-3 TRANSPORT - E1 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x0743)                                                                                                                                    |            |

| TABLE 188: TRANSMIT STS-1/STS-3 TRANSPORT - E2 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x0747)                                                                                                                                    |            |

| TABLE 189: TRANSMIT STS-1/STS-3 TRANSPORT - JO BYTE VALUE REGISTER (ADDRESS LOCATION= 0x074B)                                                                                                                                    |            |

| TABLE 190: TRANSMIT STS-1/STS-3 TRANSPORT - TRANSMITTER JO BYTE CONTROL REGISTER (ADDRESS LOCATION= 0x074F).                                                                                                                     |            |

| 2.6 TRANSMIT STS-1/STS-3 POH PROCESSOR BLOCK REGISTERS                                                                                                                                                                           | 132        |

| FIGURE 7. ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328, WITH THE TRANSMIT STS-1/STS-3 POH PI                                                                                                                   | ROCES      |

| SOR BLOCK HIGHLIGHTED                                                                                                                                                                                                            |            |

| TABLE 191: TRANSMIT STS-1/STS-3 PATH - TRANSMIT CONTROL REGISTER - BYTE 1 (ADDRESS LOCATION = 0x0782)                                                                                                                            | 132        |

| TABLE 192: TRANSMIT STS-1/STS-3 PATH - TRANSMIT CONTROL REGISTER - BYTE 0 (ADDRESS LOCATION= 0x0783)                                                                                                                             | 133        |

| Table 193: Transmit STS-1/STS-3 Path - Transmitter J1 Byte Value Register (Address Location= 0x0793)                                                                                                                             | 135        |

| TABLE 194: TRANSMIT STS-1/STS-3 PATH - TRANSMIT B3 BYTE ERROR MASK REGISTER (ADDRESS LOCATION= 0x0797)                                                                                                                           | 135        |

| TABLE 195: TRANSMIT STS-1/STS-3 PATH - TRANSMIT C2 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x079B)                                                                                                                                |            |

| Table 196: Transmit STS-1/STS-3 Path - Transmit G1 Byte Value Register (Address Location= 0x079F)                                                                                                                                |            |

| TABLE 197: TRANSMIT STS-1/STS-3 PATH - TRANSMIT F2 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x07A3)                                                                                                                                |            |

| TABLE 198: TRANSMIT STS-1/STS-3 PATH - TRANSMIT H4 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x07A7)                                                                                                                                |            |

| TABLE 199: TRANSMIT STS-1/STS-3 PATH - TRANSMIT Z3 BYTE VALUE REGISTER (ADDRESS LOCATION= 0x07AB)                                                                                                                                |            |

| TABLE 200: TRANSMIT STS-1/STS-3 PATH - TRANSMIT Z4 BYTE VALUE REGISTER (ADDRESS LOCATION= 0xN9AF)                                                                                                                                |            |

| TABLE 201: TRANSMIT STS-1/STS-3 PATH - TRANSMIT Z5 BYTE VALUE REGISTER (ADDRESS LOCATION= 0X07B3)                                                                                                                                |            |

| TABLE 202: TRANSMIT STS-1/STS-3 PATH - TRANSMIT PATH CONTROL REGISTER (ADDRESS LOCATION= 0x07B7)                                                                                                                                 |            |

| TABLE 203: TRANSMIT STS-1/STS-3 PATH - SONET PATH J1 CONTROL REGISTER (ADDRESS LOCATION= 0x07BB)                                                                                                                                 |            |

| TABLE 204: TRANSMIT STS-1/STS-3 PATH - TRANSMIT ARBITRARY H1 POINTER REGISTER (ADDRESS LOCATION= 0x07BF)                                                                                                                         |            |

| TABLE 205: TRANSMIT STS-1/STS-3 PATH - TRANSMIT ARBITRARY H2 POINTER REGISTER (ADDRESS LOCATION= 0x07C3)                                                                                                                         |            |

| TABLE 206: TRANSMIT STS-1/STS-3 PATH - TRANSMIT CURRENT POINTER BYTE REGISTER - BYTE 1 (ADDRESS LOCATION= 0x07                                                                                                                   | C6)        |

| 141 TABLE 207: TRANSMIT STS-1/STS-3 PATH - TRANSMIT CURRENT POINTER BYTE REGISTER - BYTE 0 (ADDRESS LOCATION= 0x07                                                                                                               | (CZ)       |

| 141                                                                                                                                                                                                                              | <i>(1)</i> |

| TABLE 208: TRANSMIT STS-1/STS-3 PATH - RDI-P CONTROL REGISTER - BYTE 2 (ADDRESS LOCATION= 0x07C9)                                                                                                                                | 1/12       |

| TABLE 200: TRANSMIT STS-1/STS-3 PATH - RDI-P CONTROL REGISTER - BYTE 1 (ADDRESS LOCATION= 0x07CA)                                                                                                                                |            |

| TABLE 210: TRANSMIT STS-1/STS-3 PATH - RDI-P CONTROL REGISTER - BYTE 0 (ADDRESS LOCATION= 0X07CB)                                                                                                                                |            |

| TABLE 211: TRANSMIT STS-1/STS-3 PATH - SERIAL PORT CONTROL REGISTER (ADDRESS LOCATION= 0x07CF)                                                                                                                                   |            |

| TABLE 212: TRANSMIT STS-1/STS-3 PATH - TRANSMIT NEGATIVE POINTER ADJUSTMENT COUNT REGISTER - BYTE 1 (ADDRESS L                                                                                                                   |            |

| TION= 0x07D0)                                                                                                                                                                                                                    |            |

| TABLE 213: TRANSMIT STS-1/STS-3 PATH - TRANSMIT NEGATIVE POINTER ADJUSTMENT COUNT REGISTER - BYTE 0 (ADDRESS L                                                                                                                   | OCA-       |

| TION= 0x07D1)                                                                                                                                                                                                                    |            |

| TABLE 214: TRANSMIT STS-1/STS-3 PATH - TRANSMIT POSITIVE POINTER ADJUSTMENT COUNT REGISTER - BYTE 1 (ADDRESS LOCA                                                                                                                |            |

| 0x07D2)                                                                                                                                                                                                                          |            |

| TABLE 215: TRANSMIT STS-1/STS-3 PATH - TRANSMIT POSITIVE POINTER ADJUSTMENT COUNT REGISTER - BYTE 1 (ADDRESS LOCA                                                                                                                |            |

| 0x07D3)                                                                                                                                                                                                                          | 145        |

| 2.7 TRANSMIT TUG-3 MAPPER/VC-4 POH PROCESSOR BLOCK REGISTERS (SDH/TUG-3 APPLICATION                                                                                                                                              |            |

| ONLY)                                                                                                                                                                                                                            |            |

| FIGURE 8. ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328 DEVICE, WITH THE TRANSMIT TUG-3 MAPPE                                                                                                                   |            |

| 4 POH Processor block "Highlighted"                                                                                                                                                                                              |            |

| 2.8 GLOBAL VT MAPPER BLOCK CONTROL REGISTERS                                                                                                                                                                                     | 146        |

| TABLE 216: GLOBAL CONTROL - VT-MAPPER BLOCK - VT MAPPER BLOCK CONTROL REGISTER (ADDRESS = 0x0C03)                                                                                                                                |            |

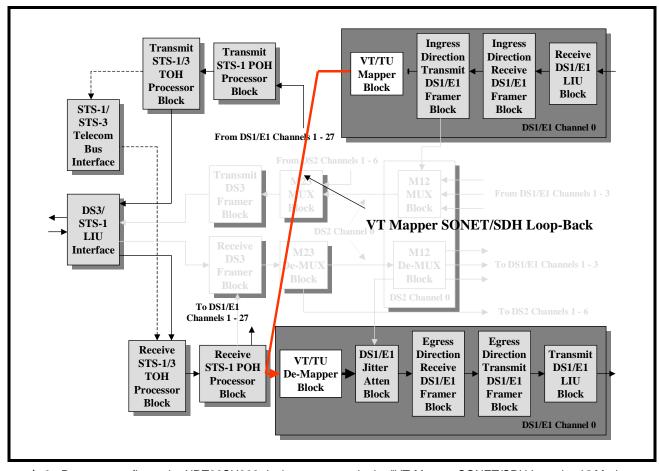

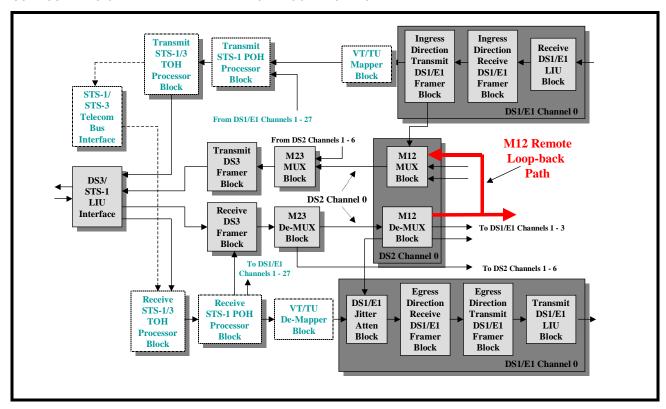

| FIGURE 9. ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328 WITH THE VT-MAPPER SONET/SDH LOOP                                                                                                                       |            |

## EXAR Powering Connectivity

## 28-CHANNEL SONET/SDH VT MAPPER REGISTER DESCRIPTION WITH M13

| RFV 2.0 | n |

|---------|---|

| PATH DEPICTED                                                                                                                |                       |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| TABLE 217: GLOBAL CONTROL - VT-MAPPER BLOCK - TEST PATTERN CONTROL REGISTER - BYTE 1 (ADDRESS = 0x0C0E                       | ) 1 <i>4</i> 8        |

| TABLE 218: GLOBAL VT-MAPPER BLOCK - TEST PATTERN CONTROL REGISTER - BYTE 0 (ADDRESS = 0x0C0F)                                | 149                   |

| Table 219: Global Control - VT-Mapper Block - Test Pattern Drop Register - Byte 1 (Address = 0x0C12)                         | 150                   |

| Table 220: Global Control - VT-Mapper Block - Test Pattern Drop Register - Byte 0 (Address = 0x0C13)                         | 152                   |

| Table 221: Global Control - VT-Mapper - Test Pattern Detector Error Count Register - Upper Byte (Addre                       | SS = 0x0C16)          |

| 153                                                                                                                          |                       |

| TABLE 222: GLOBAL CONTROL - VT-MAPPER - TEST PATTERN DETECTOR ERROR COUNT REGISTER - LOWER BYTE (ADDRE                       | $SS = 0 \times 0C17)$ |

| 154                                                                                                                          |                       |

| Table 223: Global Control - VT-Mapper - Transmit Tributary Size Select Register (Address = 0x0C1A)                           |                       |

| Table 224: Global Control - VT-Mapper - Transmit Tributary Size Select Register (Address = 0x0C1B)                           |                       |

| TABLE 225: GLOBAL CONTROL - VT-MAPPER - RECEIVE TRIBUTARY SIZE SELECT REGISTER (ADDRESS = 0x0C1E)                            |                       |

| TABLE 226: GLOBAL CONTROL - VT-MAPPER - RECEIVE TRIBUTARY SIZE SELECT REGISTER (ADDRESS = 0x0C1F)                            |                       |

| 2.9 DS3 MAPPER CONTROL REGISTERS                                                                                             |                       |

| Table 227: DS3 Mapper Block - Control Register - Byte 1 (Address Location = 0x0D02)                                          |                       |

| Table 228: DS3 Mapper Block - Control Register - Byte 0 (Address Location = 0x0D03)                                          |                       |

| Table 229: DS3 Mapper Block - Receive Status Register - Byte 1 (Address Location = 0x0D06)                                   |                       |

| Table 230: DS3 Mapper Block - Receive Status Register - Byte 0 (Address Location = 0x0D07)                                   |                       |

| TABLE 231: DS3 MAPPER BLOCK - RECEIVE MAPPER INTERRUPT STATUS REGISTER - BYTE 0 (ADDRESS = 0x0D0B)                           |                       |

| TABLE 232: DS3 MAPPER BLOCK - RECEIVE MAPPER INTERRUPT ENABLE REGISTER - BYTE 0 (ADDRESS = 0x0D0E)                           |                       |

| TABLE 233: DS3 MAPPER BLOCK - POINTER JUSTIFICATION STATUS REGISTER - BYTE 2 (ADDRESS = 0x0D21)                              |                       |

| TABLE 234: DS3 MAPPER BLOCK - POINTER JUSTIFICATION STATUS REGISTER - BYTE 1 (ADDRESS = 0x0D22)                              |                       |

| TABLE 235: DS3 MAPPER BLOCK - POINTER JUSTIFICATION STATUS REGISTER - BYTE 0 (ADDRESS = 0x0D23)                              |                       |

| TABLE 236: DS3 MAPPER BLOCK - POINTER JUSTIFICATION JITTER CONTROL REGISTER - BYTE 0 (ADDRESS = 0x0D27)                      |                       |

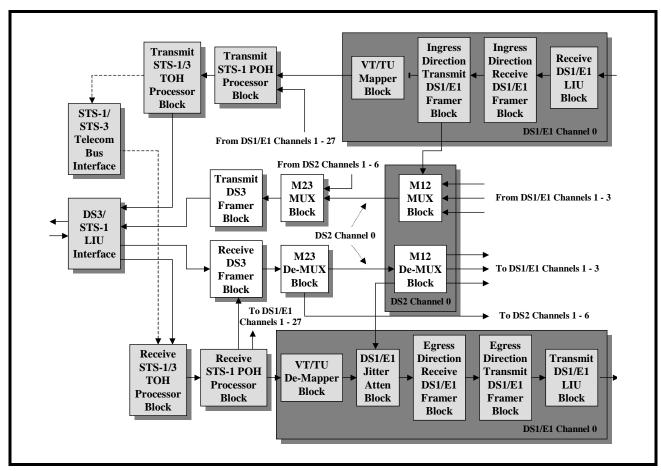

| 2.10 DS3 FRAMER AND M13 MUX BLOCK REGISTERS                                                                                  |                       |

| FIGURE 10. ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328, WITH THE FUNCTIONAL BLOCKS (W                     |                       |

| TROLLED/MONITORED VIA THE DS3 FRAMER AND M13 MUX BLOCK REGISTERS) HIGHLIGHTED                                                |                       |

| TABLE 237: DS3 FRAMER BLOCK OPERATING MODE REGISTER (ADDRESS = 0x0E00)                                                       |                       |

| TABLE 238: DS3 FRAMER BLOCK - I/O CONTROL REGISTER (ADDRESS = 0x0E01)                                                        |                       |

| TABLE 239: DS3 FRAMER BLOCK - BLOCK INTERRUPT ENABLE REGISTER (ADDRESS = 0x0E04)                                             |                       |

| TABLE 240: DS3 FRAMER BLOCK - BLOCK INTERRUPT STATUS REGISTER (ADDRESS = 0x0E05)                                             |                       |

| Table 241: DS3 Framer Block - M23 Configuration Register (Address = 0x0E07)                                                  | 169                   |

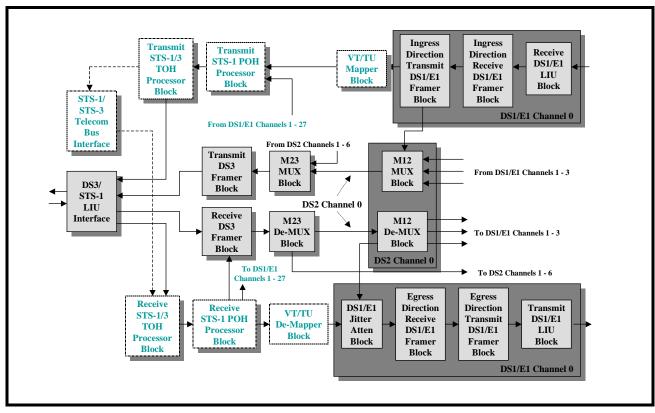

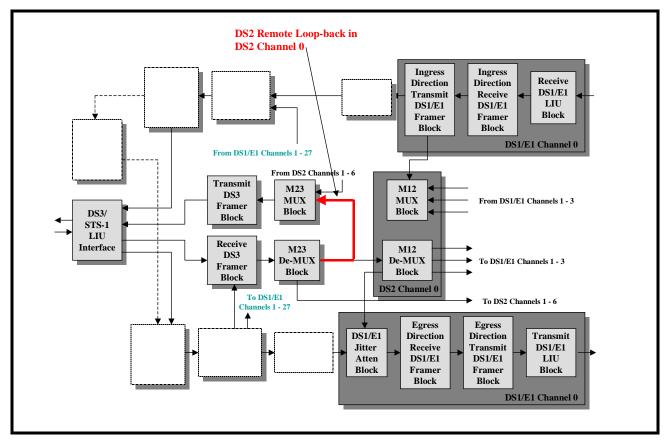

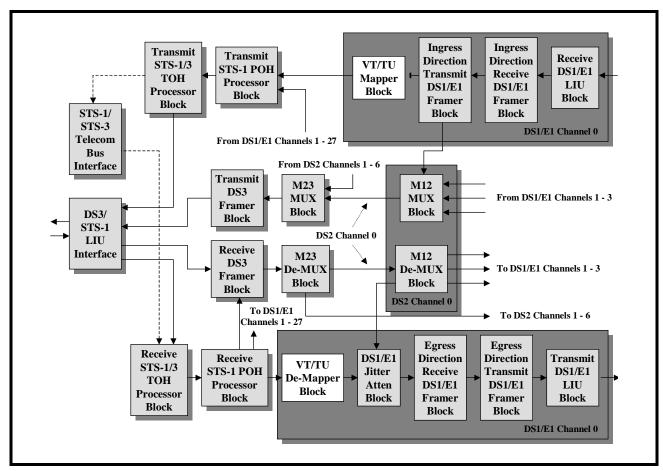

| FIGURE 11. AN ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328, WHENEVER IT HAS BEEN CONF                      |                       |

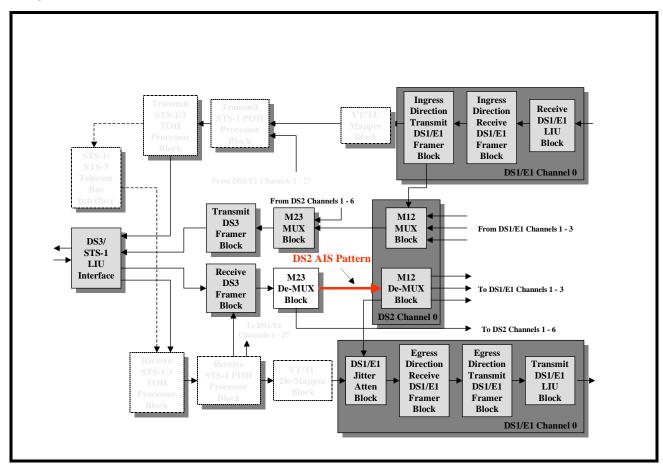

| ERATE IN THE M13 LOCAL LOOP- BACK MODETABLE 242: DS3 FRAMER BLOCK - M23 TRANSMIT DS2 AIS COMMAND REGISTER (ADDRESS = 0x0E08) |                       |

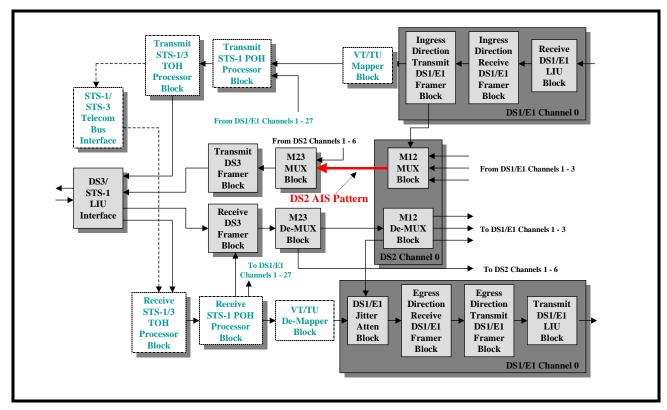

| FIGURE 12. AN ILLUSTRATION OF THE XRT86SH328, WHENEVER THE M12 MUX HAS BEEN CONFIGURED TO TRANSMIT THE                       |                       |

| CATOR TOWARDS BOTH THE M23 MUX AND THE TRANSMIT DS3 FRAMER BLOCK                                                             |                       |

| TABLE 243: DS3 FRAMER BLOCK - M23 - DS2 LOOP-BACK REQUEST REGISTER (ADDRESS = 0x0E09)                                        |                       |

| TABLE 244: DS3 FRAMER BLOCK - M23 LOOP-BACK REQUEST REGISTER (ADDRESS = 0x0E0A)                                              |                       |

| FIGURE 13. AN ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328, WHENEVER A GIVEN DS2 CHAN                      |                       |

| CONFIGURED TO OPERATE IN THE REMOTE DS2 LOOP-BACK MODE                                                                       |                       |

| Table 245: DS3 Framer Block - M23 MUX Force Receive DS2 AIS Command Registers (Address = 0x0E0B)                             |                       |

| FIGURE 14. AN ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328, WHENEVER THE M23 DE-MUX                        |                       |

| FIGURED TO TRANSMIT THE DS2 AIS INDICATOR IN THE EGRESS DIRECTION OF DS2 CHANNEL 0                                           |                       |

| TABLE 246: DS3 FRAMER AND M13 MUX BLOCK - DS3 TEST REGISTER (ADDRESS = 0x0E0C)                                               |                       |

| TABLE 247: DS3 FRAMER AND M13 MUX BLOCK - DS3 TEST REGISTER #2 (ADDRESS = 0x0E0E)                                            |                       |

| Table 248: DS3 Framer Block - Receive DS3 Configuration & Status Register (Address = 0x0E10)                                 |                       |

| Table 249: DS3 Framer Block - Receive DS3 Status Register (Address = 0x0E11)                                                 | 178                   |

| TABLE 250: DS3 FRAMER BLOCK - RECEIVE DS3 INTERRUPT ENABLE REGISTER (ADDRESS = 0X0E12)                                       |                       |

| Table 251: DS3 Framer Block - Receive DS3 Interrupt Status                                                                   | x0E13) 181            |

| Table 252: DS3 Framer Block - Receive DS3 Sync Detect Register (Address = 0x0E14)                                            | 182                   |

| Table 253: DS3 Framer Block - Receive DS3 FEAC Register (Address = 0x0E16)                                                   | 182                   |

| TABLE 254: DS3 FRAMER BLOCK - RECEIVE DS3 FEAC INTERRUPT ENABLE/STATUS REGISTER (ADDRESS = 0x0E17)                           | 183                   |

| Table 255: DS3 Framer Block - Receive LAPD Control Register (Address = 0x0E18)                                               | 184                   |

| Table 256: DS3 Framer Block - Receive DS3 LAPD Status Register (Address = 0x0E19)                                            |                       |

| Table 257: DS3 Framer Block - M12 Configuration Register - DS2 Channel # 1 (Address = 0x0E1A)                                | 186                   |

| Table 258: DS3 Framer Block - M12 Configuration Register - DS2 Channel #2 (Address = 0x0E1B)                                 |                       |

| Table 259: DS3 Framer Block - M12 Configuration Register - DS2 Channel #3 (Address = 0x0E1C)                                 |                       |

| Table 260: DS3 Framer Block - M12 Configuration Register - DS2 Channel # 4 (Address = 0x0E1D)                                |                       |

| Table 261: DS3 Framer Block - M12 Configuration Register - DS2 Channel # 5 (Address = 0x0E1E)                                |                       |

| Table 262: DS3 Framer Block - M12 Configuration Register - DS2 Channel # 6 (Address = 0x0E1F)                                |                       |

| Table 263: DS3 Framer Block - M12 Configuration Register - DS2 Channel #7 (Address = 0x0E20)                                 |                       |

| TABLE 264: DS3 FRAMER BLOCK - M12 DE-MUX FORCE DS1/E1 AIS REGISTER - DS2 CHANNEL # 1 (ADDRESS = 0x0E2                        |                       |

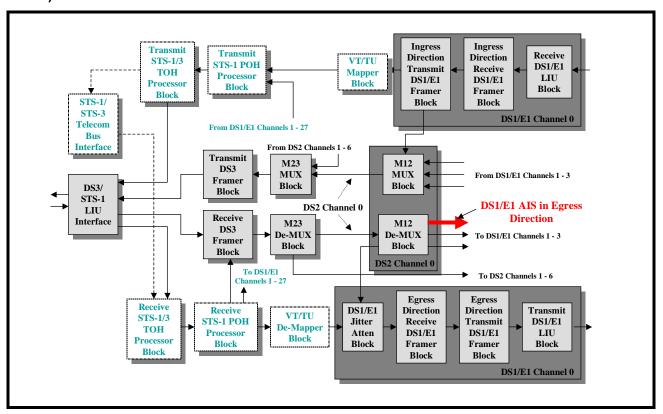

| FIGURE 15. AN ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE XRT86SH328, WHENEVER A GIVEN M12 DE-M                      |                       |

| BEEN CONFIGURED TO TRANSMIT THE DS1/E1 AIS INDICATOR (WITHIN A GIVEN DS1/E1 SIGNAL) IN THE EGRESS                            | DIRECTION             |

| 189                                                                                                                          |                       |

## REV. 2.0.0 28-CHANNEL SONET/SDH VT MAPPER REGISTER DESCRIPTION WITH M13

| T 007 D00 F D 140 40 D D00 D 144 44 D D00 D00 D00 D00 D00 D00 D00 D00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Table 265: DS3 Framer Block - M12 AIS Register - DS2 Channel # 1 (Address = 0x0E22)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 190                                                                                                     |

| Table 266: DS3 Framer Block - M12 AIS Register - DS2 Channel # 2 (ADDRESS = 0x0E23)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |