## **SHARC Processors**

# ADSP-21367/ADSP-21368/ADSP-21369

#### **SUMMARY**

High performance 32-bit/40-bit floating-point processor optimized for high performance audio processing Single-instruction, multiple-data (SIMD) computational architecture

On-chip memory—2M bits of on-chip SRAM and 6M bits of on-chip mask programmable ROM

Code compatible with all other members of the SHARC family The ADSP-21367/ADSP-21368/ADSP-21369 are available with a 400 MHz core instruction rate with unique audiocentric peripherals such as the digital applications interface, S/PDIF transceiver, serial ports, 8-channel asynchronous sample rate converter, precision clock generators, and more. For complete ordering information, see Ordering Guide on Page 58.

### **DEDICATED AUDIO COMPONENTS**

S/PDIF-compatible digital audio receiver/transmitter 4 independent asynchronous sample rate converters (SRC) 16 PWM outputs configured as four groups of four outputs ROM-based security features include

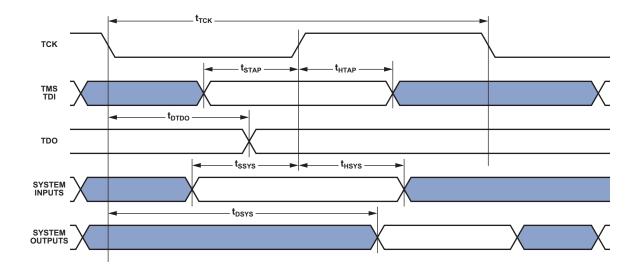

JTAG access to memory permitted with a 64-bit key

Protected memory regions that can be assigned to limit

access under program control to sensitive code

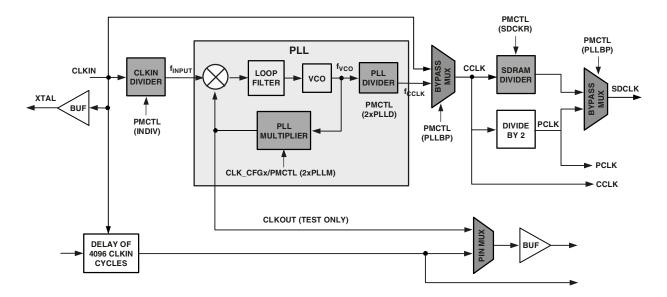

PLL has a wide variety of software and hardware multiplier/divider ratios

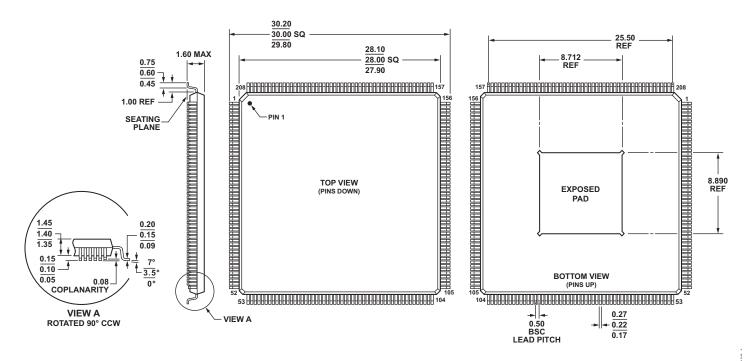

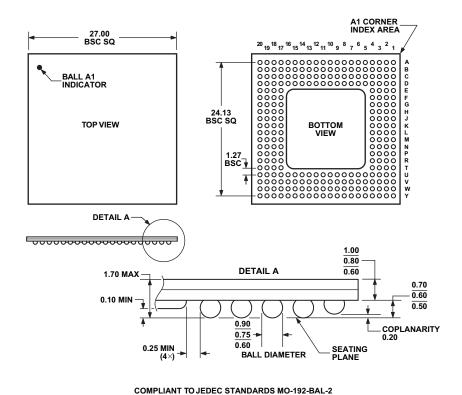

Available in 256-ball BGA\_ED and 208-lead LQFP\_EP packages

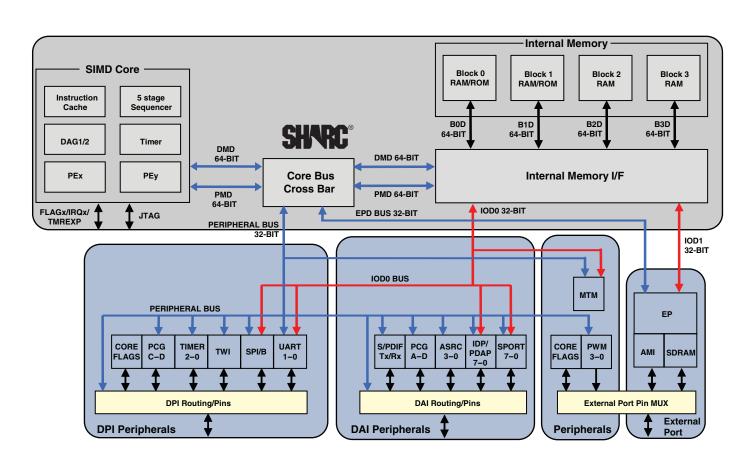

Figure 1. Functional Block Diagram

SHARC and the SHARC logo are registered trademarks of Analog Devices, Inc.

### Rev. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

Added 366 MHz LQFP EPAD models for the ADSP-21367 and ADSP-21369. For additional specifications for these models,

Specifications16Clock Input21SDRAM Interface Timing (166 MHz SDCLK)28Serial Ports34Ordering Guide58

refer to the following:

## **TABLE OF CONTENTS**

| Dedicated Audio Components         1         Maximum Power Dissipation         18           General Description         3         Absolute Maximum Ratings         18           SHARC Family Core Architecture         4         Timing Specifications         18           Family Peripheral Architecture         7         Output Drive Currents         48           I/O Processor Features         10         Test Conditions         48           System Design         10         Capacitive Loading         48           Development Tools         11         Thermal Characteristics         50           Additional Information         12         256-Ball BGA_ED Pinout         51           Pin Function Descriptions         13         208-Lead LQFP_EP Pinout         54           Specifications         16         Package Dimensions         56           Operating Conditions         16         Surface-Mount Design         57           Electrical Characteristics         17         Automotive Products         58           Package Information         18         Ordering Guide         58           REVISION HISTORY         7/09—Rev. D to Rev. E         E         Corrected all outstanding document errata. Also replaced core clock references (PCLK).         5           Revised Func | IADLE OF CONTENTS                                                                                                                                           |                           |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----|

| Semily   Core Architecture   4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Summary 1                                                                                                                                                   | ESD Caution               | 18 |

| SHARC Family Core Architecture       4       Timing Specifications       18         Family Peripheral Architecture       7       Output Drive Currents       48         I/O Processor Features       10       Test Conditions       48         System Design       10       Capacitive Loading       48         Development Tools       11       Thermal Characteristics       50         Additional Information       12       256-Ball BGA_ED Pinout       51         Pin Function Descriptions       13       208-Lead LQFP_EP Pinout       54         Specifications       16       Package Dimensions       56         Operating Conditions       16       Surface-Mount Design       57         Electrical Characteristics       17       Automotive Products       58         Package Information       18       Ordering Guide       58         REVISION HISTORY         7/09—Rev. D to Rev. E       E       Corrected all outstanding document errata. Also replaced core clock references (PCLK).       5         Revised Functional Block Diagram       1       Added Context Switch       5         Added Universal Registers       .5       5         Clarified VCO operations. See       5         Voltage Controlled Oscillator                                                                           | Dedicated Audio Components                                                                                                                                  | Maximum Power Dissipation | 18 |

| Family Peripheral Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | General Description                                                                                                                                         | Absolute Maximum Ratings  | 18 |

| I/O Processor Features 10 Test Conditions 48 System Design 10 Capacitive Loading 48 Development Tools 11 Thermal Characteristics 50 Additional Information 12 256-Ball BGA_ED Pinout 51 Pin Function Descriptions 13 208-Lead LQFP_EP Pinout 54 Specifications 16 Package Dimensions 56 Operating Conditions 16 Surface-Mount Design 57 Electrical Characteristics 17 Automotive Products 58 Package Information 18 Ordering Guide 58  REVISION HISTORY 7/09—Rev. D to Rev. E Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK). Revised Functional Block Diagram 1 Added Context Switch 5 Added Universal Registers 5 Clarified VCO operations. See Voltage Controlled Oscillator 18 Corrected the pins names for the DAI and DPI in 256-Ball BGA_ED Pinout 51                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SHARC Family Core Architecture 4                                                                                                                            | Timing Specifications     | 18 |

| System Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Family Peripheral Architecture                                                                                                                              | Output Drive Currents     | 48 |

| Development Tools 11 Thermal Characteristics 50 Additional Information 12 256-Ball BGA_ED Pinout 51 Pin Function Descriptions 13 208-Lead LQFP_EP Pinout 54 Specifications 16 Package Dimensions 56 Operating Conditions 16 Surface-Mount Design 57 Electrical Characteristics 17 Automotive Products 58 Package Information 18 Ordering Guide 58  REVISION HISTORY 7/09—Rev. D to Rev. E Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK). Revised Functional Block Diagram 1 Added Context Switch 5 Added Universal Registers 5 Clarified VCO operations. See Voltage Controlled Oscillator 18 Corrected the pins names for the DAI and DPI in 256-Ball BGA_ED Pinout 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O Processor Features                                                                                                                                      | Test Conditions           | 48 |

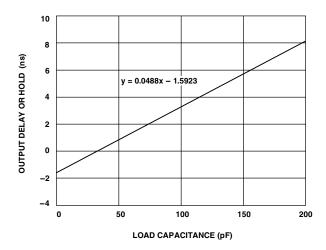

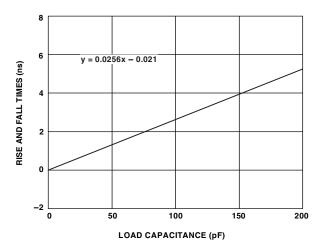

| Additional Information 12 256-Ball BGA_ED Pinout 51  Pin Function Descriptions 13 208-Lead LQFP_EP Pinout 54  Specifications 16 Package Dimensions 56  Operating Conditions 16 Surface-Mount Design 57  Electrical Characteristics 17 Automotive Products 58  Package Information 18 Ordering Guide 58  REVISION HISTORY  7/09—Rev. D to Rev. E  Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK).  Revised Functional Block Diagram 1  Added Context Switch 5  Added Universal Registers 5  Clarified VCO operations. See  Voltage Controlled Oscillator 18  Corrected the pins names for the DAI and DPI in 256-Ball BGA_ED Pinout 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | System Design                                                                                                                                               | Capacitive Loading        | 48 |

| Pin Function Descriptions 13 208-Lead LQFP_EP Pinout 54 Specifications 16 Package Dimensions 56 Operating Conditions 16 Surface-Mount Design 57 Electrical Characteristics 17 Automotive Products 58 Package Information 18 Ordering Guide 58  REVISION HISTORY 7/09—Rev. D to Rev. E Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK). Revised Functional Block Diagram 1 Added Context Switch 5 Added Universal Registers 5 Clarified VCO operations. See Voltage Controlled Oscillator 18 Corrected the pins names for the DAI and DPI in 256-Ball BGA_ED Pinout 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Development Tools                                                                                                                                           | Thermal Characteristics   | 50 |

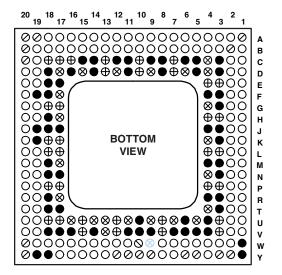

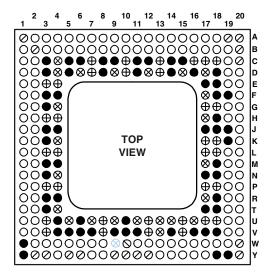

| Specifications 16 Package Dimensions 56 Operating Conditions 16 Surface-Mount Design 57 Electrical Characteristics 17 Automotive Products 58 Package Information 18 Ordering Guide 58  REVISION HISTORY 7/09—Rev. D to Rev. E Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK). Revised Functional Block Diagram 1 Added Context Switch 5 Added Universal Registers 5 Clarified VCO operations. See Voltage Controlled Oscillator 18 Corrected the pins names for the DAI and DPI in 256-Ball BGA_ED Pinout 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Additional Information                                                                                                                                      | 256-Ball BGA_ED Pinout    | 51 |

| Operating Conditions 16 Surface-Mount Design 57 Electrical Characteristics 17 Automotive Products 58 Package Information 18 Ordering Guide 58  REVISION HISTORY 7/09—Rev. D to Rev. E Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK). Revised Functional Block Diagram 1 Added Context Switch 5 Added Universal Registers 5 Clarified VCO operations. See Voltage Controlled Oscillator 18 Corrected the pins names for the DAI and DPI in 256-Ball BGA_ED Pinout 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin Function Descriptions                                                                                                                                   | 208-Lead LQFP_EP Pinout   | 54 |

| Electrical Characteristics 17 Automotive Products 58 Package Information 18 Ordering Guide 58  REVISION HISTORY 7/09—Rev. D to Rev. E Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK). Revised Functional Block Diagram 1 Added Context Switch 5 Added Universal Registers 5 Clarified VCO operations. See Voltage Controlled Oscillator 18 Corrected the pins names for the DAI and DPI in 256-Ball BGA_ED Pinout 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Specifications                                                                                                                                              | Package Dimensions        | 56 |

| Package Information 18 Ordering Guide 58  REVISION HISTORY  7/09—Rev. D to Rev. E  Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK).  Revised Functional Block Diagram 1  Added Context Switch 5  Added Universal Registers 5  Clarified VCO operations. See  Voltage Controlled Oscillator 18  Corrected the pins names for the DAI and DPI in 256-Ball BGA_ED Pinout 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Operating Conditions                                                                                                                                        | Surface-Mount Design      | 57 |

| REVISION HISTORY  7/09—Rev. D to Rev. E  Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK).  Revised Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Electrical Characteristics                                                                                                                                  | Automotive Products       | 58 |

| 7/09—Rev. D to Rev. E  Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK).  Revised Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Package Information                                                                                                                                         | Ordering Guide            | 58 |

| Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK).  Revised Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REVISION HISTORY                                                                                                                                            |                           |    |

| clock references (CCLK) in the timing specifications with peripheral clock references (PCLK).  Revised Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7/09—Rev. D to Rev. E                                                                                                                                       |                           |    |

| Added Context Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Corrected all outstanding document errata. Also replaced core clock references (CCLK) in the timing specifications with peripheral clock references (PCLK). |                           |    |

| Added Universal Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Revised Functional Block Diagram1                                                                                                                           |                           |    |

| Clarified VCO operations. See Voltage Controlled Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Added Context Switch5                                                                                                                                       |                           |    |

| Voltage Controlled Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Added Universal Registers5                                                                                                                                  |                           |    |

| 256-Ball BGA_ED Pinout51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Clarified VCO operations. See Voltage Controlled Oscillator                                                                                                 |                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                             |                           |    |

### **GENERAL DESCRIPTION**

The ADSP-21367/ADSP-21368/ADSP-21369 SHARC® processors are members of the SIMD SHARC family of DSPs that feature Analog Devices' Super Harvard Architecture. These processors are source code-compatible with the ADSP-2126x and ADSP-2116x DSPs as well as with first generation ADSP-2106x SHARC processors in SISD (single-instruction, single-data) mode. The processors are 32-bit/40-bit floating-point processors optimized for high performance automotive audio applications with its large on-chip SRAM, mask programmable ROM, multiple internal buses to eliminate I/O bottlenecks, and an innovative digital applications interface (DAI).

As shown in the functional block diagram on Page 1, the processors use two computational units to deliver a significant performance increase over the previous SHARC processors on a range of DSP algorithms. Fabricated in a state-of-the-art, high speed, CMOS process, the ADSP-21367/ADSP-21368/ADSP-21369 processors achieve an instruction cycle time of up to 2.5 ns at 400 MHz. With its SIMD computational hardware, the processors can perform 2.4 GFLOPS running at 400 MHz.

Table 1 shows performance benchmarks for these devices.

Table 1. Processor Benchmarks (at 400 MHz)

| Benchmark Algorithm                             | Speed<br>(at 400 MHz) |

|-------------------------------------------------|-----------------------|

| 1024 Point Complex FFT (Radix 4, with reversal) | 23.2 μs               |

| FIR Filter (per tap) <sup>1</sup>               | 1.25 ns               |

| IIR Filter (per biquad) <sup>1</sup>            | 5.0 ns                |

| Matrix Multiply (pipelined)                     |                       |

| $[3\times3]\times[3\times1]$                    | 11.25 ns              |

| $[4\times4]\times[4\times1]$                    | 20.0 ns               |

| Divide (y/x)                                    | 8.75 ns               |

| Inverse Square Root                             | 13.5 ns               |

<sup>&</sup>lt;sup>1</sup> Assumes two files in multichannel SIMD mode.

Table 2. ADSP-2136x Family Features<sup>1</sup>

| Feature                | ADSP-21367 | ADSP-21368 | ADSP-21369/<br>ADSP-21369W |

|------------------------|------------|------------|----------------------------|

| Frequency              |            | 400 MHz    |                            |

| RAM                    |            | 2M bits    |                            |

| ROM <sup>2</sup>       |            | 6M bits    |                            |

| Audio Decoders in ROM  |            | Yes        |                            |

| Pulse-Width Modulation |            | Yes        |                            |

| S/PDIF                 |            | Yes        |                            |

| SDRAM Memory Bus Width |            | 32/16 bits |                            |

Table 2. ADSP-2136x Family Features<sup>1</sup> (Continued)

| Feature                 | ADSP-21367                               | ADSP-21368       | ADSP-21369/<br>ADSP-21369W               |

|-------------------------|------------------------------------------|------------------|------------------------------------------|

| Serial Ports            |                                          | 8                |                                          |

| IDP                     |                                          | Yes              |                                          |

| DAI                     |                                          | Yes              |                                          |

| UART                    |                                          | 2                |                                          |

| DAI and DPI             | Yes                                      |                  |                                          |

| S/PDIF Transceiver      | 1                                        |                  |                                          |

| AMI Interface Bus Width | 32/16/8 bits                             |                  |                                          |

| SPI                     | 2                                        |                  |                                          |

| TWI                     | Yes                                      |                  |                                          |

| SRC Performance         | 128 dB                                   |                  |                                          |

| Package                 | 256 Ball-<br>BGA,<br>208-Lead<br>LQFP_EP | 256 Ball-<br>BGA | 256 Ball-<br>BGA,<br>208-Lead<br>LQFP_EP |

<sup>&</sup>lt;sup>1</sup> W = Automotive grade product. See Automotive Products on Page 58 for more information.

The diagram on Page 1 shows the two clock domains that make up the ADSP-21367/ADSP-21368/ADSP-21369 processors. The core clock domain contains the following features.

- Two processing elements (PEx, PEy), each of which comprises an ALU, multiplier, shifter, and data register file

- Data address generators (DAG1, DAG2)

- Program sequencer with instruction cache

- PM and DM buses capable of supporting 2x64-bit data transfers between memory and the core at every core processor cycle

- One periodic interval timer with pinout

- On-chip SRAM (2M bit)

- On-chip mask-programmable ROM (6M bit)

- JTAG test access port for emulation and boundary scan.

The JTAG provides software debug through user breakpoints which allows flexible exception handling.

<sup>&</sup>lt;sup>2</sup> Audio decoding algorithms include PCM, Dolby Digital EX, Dolby Prologic IIx, DTS 96/24, Neo:6, DTS ES, MPEG-2 AAC, MP3, and functions like bass management, delay, speaker equalization, graphic equalization, and more. Decoder/post-processor algorithm combination support varies depending upon the chip version and the system configurations. Please visit www.analog.com for complete information.

The block diagram of the ADSP-21368 on Page 1 also shows the peripheral clock domain (also known as the I/O processor) and contains the following features:

- IOD0 (peripheral DMA) and IOD1 (external port DMA) buses for 32-bit data transfers

- Peripheral and external port buses for core connection

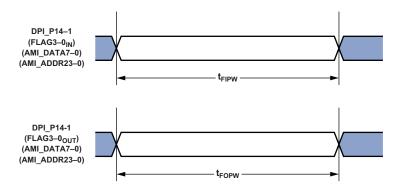

- · External port with an AMI and SDRAM controller

- 4 units for PWM control

- 1 MTM unit for internal-to-internal memory transfers

- Digital applications interface that includes four precision clock generators (PCG), a input data port (IDP) for serial and parallel interconnect, an S/PDIF receiver/transmitter, four asynchronous sample rate converters, eight serial ports, a flexible signal routing unit (DAI SRU).

• Digital peripheral interface that includes three timers, a 2-wire interface, two UARTs, two serial peripheral interfaces (SPI), 2 precision clock generators (PCG) and a flexible signal routing unit (DPI SRU).

### **SHARC FAMILY CORE ARCHITECTURE**

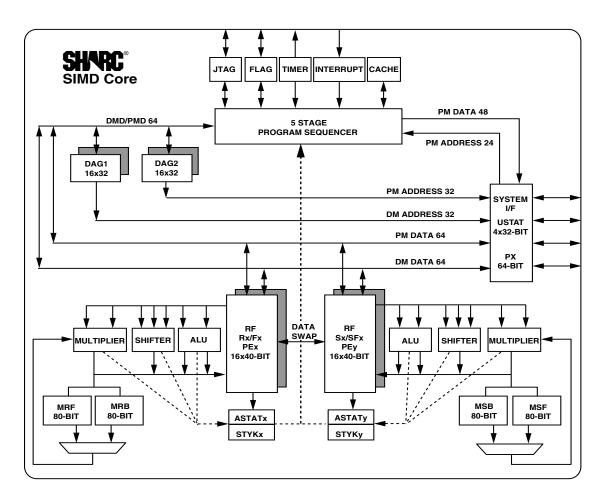

The ADSP-21367/ADSP-21368/ADSP-21369 are code compatible at the assembly level with the ADSP-2126x, ADSP-21160, and ADSP-21161, and with the first generation ADSP-2106x SHARC processors. The ADSP-21367/ADSP-21368/ADSP-21369 processors share architectural features with the ADSP-2126x and ADSP-2116x SIMD SHARC processors, as shown in Figure 2 and detailed in the following sections.

Figure 2. SHARC Core Block Diadram

### **SIMD Computational Engine**

The processors contain two computational processing elements that operate as a single-instruction, multiple-data (SIMD) engine. The processing elements are referred to as PEX and PEY and each contains an ALU, multiplier, shifter, and register file. PEX is always active, and PEY may be enabled by setting the PEYEN mode bit in the MODE1 register. When this mode is enabled, the same instruction is executed in both processing elements, but each processing element operates on different data. This architecture is efficient at executing math intensive DSP algorithms.

Entering SIMD mode also has an effect on the way data is transferred between memory and the processing elements. When in SIMD mode, twice the data bandwidth is required to sustain computational operation in the processing elements. Because of this requirement, entering SIMD mode also doubles the bandwidth between memory and the processing elements. When using the DAGs to transfer data in SIMD mode, two data values are transferred with each access of memory or the register file.

### **Independent, Parallel Computation Units**

Within each processing element is a set of computational units. The computational units consist of an arithmetic/logic unit (ALU), multiplier, and shifter. These units perform all operations in a single cycle. The three units within each processing element are arranged in parallel, maximizing computational throughput. Single multifunction instructions execute parallel ALU and multiplier operations. In SIMD mode, the parallel ALU and multiplier operations occur in both processing elements. These computation units support IEEE 32-bit single-precision floating-point, 40-bit extended precision floating-point, and 32-bit fixed-point data formats.

### **Data Register File**

A general-purpose data register file is contained in each processing element. The register files transfer data between the computation units and the data buses, and store intermediate results. These 10-port, 32-register (16 primary, 16 secondary) register files, combined with the ADSP-2136x enhanced Harvard architecture, allow unconstrained data flow between computation units and internal memory. The registers in PEX are referred to as R0–R15 and in PEY as S0–S15.

### **Context Switch**

Many of the processor's registers have secondary registers that can be activated during interrupt servicing for a fast context switch. The data registers in the register file, the DAG registers, and the multiplier result registers all have secondary registers. The primary registers are active at reset, while the secondary registers are activated by control bits in a mode control register.

### **Universal Registers**

These registers can be used for general-purpose tasks. The USTAT (4) registers allow easy bit manipulations (Set, Clear, Toggle, Test, XOR) for all system registers (control/status) of the core.

The data bus exchange register (PX) permits data to be passed between the 64-bit PM data bus and the 64-bit DM data bus, or between the 40-bit register file and the PM data bus. These registers contain hardware to handle the data width difference.

#### Timer

A core timer that can generate periodic software Interrupts. The core timer can be configured to use FLAG3 as a timer expired signal

### Single-Cycle Fetch of Instruction and Four Operands

The ADSP-21367/ADSP-21368/ADSP-21369 feature an enhanced Harvard architecture in which the data memory (DM) bus transfers data and the program memory (PM) bus transfers both instructions and data (see Figure 2 on Page 4). With separate program and data memory buses and on-chip instruction cache, the processors can simultaneously fetch four operands (two over each data bus) and one instruction (from the cache), all in a single cycle.

### **Instruction Cache**

The processors include an on-chip instruction cache that enables three-bus operation for fetching an instruction and four data values. The cache is selective—only the instructions whose fetches conflict with PM bus data accesses are cached. This cache allows full-speed execution of core, looped operations such as digital filter multiply-accumulates, and FFT butterfly processing.

# Data Address Generators with Zero-Overhead Hardware Circular Buffer Support

The ADSP-21367/ADSP-21368/ADSP-21369 have two data address generators (DAGs). The DAGs are used for indirect addressing and implementing circular data buffers in hardware. Circular buffers allow efficient programming of delay lines and other data structures required in digital signal processing, and are commonly used in digital filters and Fourier transforms. The two DAGs contain sufficient registers to allow the creation of up to 32 circular buffers (16 primary register sets, 16 secondary). The DAGs automatically handle address pointer wraparound, reduce overhead, increase performance, and simplify implementation. Circular buffers can start and end at any memory location.

### Flexible Instruction Set

The 48-bit instruction word accommodates a variety of parallel operations for concise programming. For example, the ADSP-21367/ADSP-21368/ADSP-21369 can conditionally execute a multiply, an add, and a subtract in both processing elements while branching and fetching up to four 32-bit values from memory—all in a single instruction.

### **On-Chip Memory**

The processors contain two megabits of internal RAM and six megabits of internal mask-programmable ROM. Each block can be configured for different combinations of code and data storage (see Table 3 on Page 6). Each memory block supports single-cycle, independent accesses by the core processor and I/O

processor. The memory architecture, in combination with its separate on-chip buses, allows two data transfers from the core and one from the I/O processor, in a single cycle.

Table 3. Internal Memory Space <sup>1</sup>

| IOP Registers 0x0000 0000-0x0003 FFFF |                                                                                                                                                          |                                     |                                     |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|--|

| Long Word (64 Bits)                   | Extended Precision Normal or<br>Instruction Word (48 Bits)                                                                                               | Normal Word (32 Bits)               | Short Word (16 Bits)                |  |

| Block 0 ROM (Reserved)                | Block 0 ROM (Reserved)                                                                                                                                   | Block 0 ROM (Reserved)              | Block 0 ROM (Reserved)              |  |

| 0x0004 0000–0x0004 BFFF               | 0x0008 0000–0x0008 FFFF                                                                                                                                  | 0x0008 0000–0x0009 7FFF             | 0x0010 0000–0x0012 FFFF             |  |

| Reserved<br>0x0004 F000–0x0004 FFFF   | Reserved 0x0009 4000–0x0009 FFFF                                                                                                                         | Reserved<br>0x0009 E000–0x0009 FFFF | Reserved 0x0013 C000–0x0013 FFFF    |  |

| Block 0 SRAM                          | Block 0 SRAM                                                                                                                                             | Block 0 SRAM                        | Block 0 SRAM                        |  |

| 0x0004 C000–0x0004 EFFF               | 0x0009 0000–0x0009 3FFF                                                                                                                                  | 0x0009 8000–0x0009 DFFF             | 0x0013 0000–0x0013 BFFF             |  |

| Block 1 ROM (Reserved)                | Block 1 ROM (Reserved)                                                                                                                                   | Block 1 ROM (Reserved)              | Block 1 ROM (Reserved)              |  |

| 0x0005 0000-0x0005 BFFF               | 0x000A 0000–0x000A FFFF                                                                                                                                  | 0x000A 0000–0x000B 7FFF             | 0x0014 0000–0x0016 FFFF             |  |

| Reserved                              | Reserved                                                                                                                                                 | Reserved 0x000B E000–0x000B FFFF    | Reserved                            |  |

| 0x0005 F000–0x0005 FFFF               | 0x000B 4000–0x000B FFFF                                                                                                                                  |                                     | 0x0017 C000–0x0017 FFFF             |  |

| Block 1 SRAM                          | Block 1 SRAM                                                                                                                                             | Block 1 SRAM                        | Block 1 SRAM                        |  |

| 0x0005 C000–0x0005 EFFF               | 0x000B 0000–0x000B 3FFF                                                                                                                                  | 0x000B 8000–0x000B DFFF             | 0x0017 0000–0x0017 BFFF             |  |

| Block 2 SRAM                          | Block 2 SRAM                                                                                                                                             | Block 2 SRAM                        | Block 2 SRAM                        |  |

| 0x0006 0000–0x0006 0FFF               | 0x000C 0000-0x000C 1554                                                                                                                                  | 0x000C 0000–0x000C 1FFF             | 0x0018 0000–0x0018 3FFF             |  |

| Reserved                              | Reserved                                                                                                                                                 | Reserved                            | Reserved 0x0018 4000–0x001B FFFF    |  |

| 0x0006 1000– 0x0006 FFFF              | 0x000C 1555–0x000C 3FFF                                                                                                                                  | 0x000C 2000–0x000D FFFF             |                                     |  |

| Block 3 SRAM                          | Block 3 SRAM                                                                                                                                             | Block 3 SRAM                        | Block 3 SRAM                        |  |

| 0x0007 0000–0x0007 0FFF               | 0x000E 0000-0x000E 1554                                                                                                                                  | 0x000E 0000–0x000E 1FFF             | 0x001C 0000-0x001C 3FFF             |  |

| Reserved<br>0x0007 1000–0x0007 FFFF   | Reserved         Reserved         Reserved         Reserved           0x000E 1555-0x000F FFFF         0x000E 2000-0x000F FFFF         0x001C 4000-0x001F |                                     | Reserved<br>0x001C 4000–0x001F FFFF |  |

<sup>&</sup>lt;sup>1</sup>The ADSP-21368 and ADSP-21369 processors include a customer-definable ROM block. Please contact your Analog Devices sales representative for additional details.

The SRAM can be configured as a maximum of 64k words of 32-bit data, 128k words of 16-bit data, 42k words of 48-bit instructions (or 40-bit data), or combinations of different word sizes up to two megabits. All of the memory can be accessed as 16-bit, 32-bit, 48-bit, or 64-bit words. A 16-bit floating-point storage format is supported that effectively doubles the amount of data that can be stored on-chip. Conversion between the 32-bit floating-point and 16-bit floating-point formats is performed in a single instruction. While each memory block can store combinations of code and data, accesses are most efficient when one block stores data using the DM bus for transfers, and the other block stores instructions and data using the PM bus for transfers.

Using the DM bus and PM buses, with one bus dedicated to each memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available in the cache.

### **On-Chip Memory Bandwidth**

The internal memory architecture allows programs to have four accesses at the same time to any of the four blocks (assuming there are no block conflicts). The total bandwidth is realized using the DMD and PMD buses (2x64-bits, core CLK) and the IOD0/1 buses (2x32-bit, PCLK).

### **ROM-Based Security**

The ADSP-21367/ADSP-21368/ADSP-21369 have a ROM security feature that provides hardware support for securing user software code by preventing unauthorized reading from the internal code when enabled. When using this feature, the processor does not boot-load any external code, executing exclusively from internal ROM. Additionally, the processor is not freely accessible via the JTAG port. Instead, a unique 64-bit key, which must be scanned in through the JTAG or test access port will be assigned to each customer. The device will ignore a wrong key. Emulation features and external boot modes are only available after the correct key is scanned.

### FAMILY PERIPHERAL ARCHITECTURE

The ADSP-21367/ADSP-21368/ADSP-21369 family contains a rich set of peripherals that support a wide variety of applications including high quality audio, medical imaging, communications, military, test equipment, 3D graphics, speech recognition, motor control, imaging, and other applications.

### **External Port**

The external port interface supports access to the external memory through core and DMA accesses. The external memory address space is divided into four banks. Any bank can be programmed as either asynchronous or synchronous memory. The external ports of the ADSP-21367/8/9 processors are comprised of the following modules.

- An Asynchronous Memory Interface which communicates with SRAM, FLASH, and other devices that meet the standard asynchronous SRAM access protocol. The AMI supports 14M words of external memory in bank 0 and 16M words of external memory in bank 1, bank 2, and bank 3.

- An SDRAM controller that supports a glueless interface with any of the standard SDRAMs. The SDC supports 62M words of external memory in bank 0, and 64M words of external memory in bank 1, bank 2, and bank 3.

- Arbitration Logic to coordinate core and DMA transfers between internal and external memory over the external port.

- A Shared Memory Interface that allows the connection of up to four ADSP-21368 processors to create shared external bus systems (ADSP-21368 only).

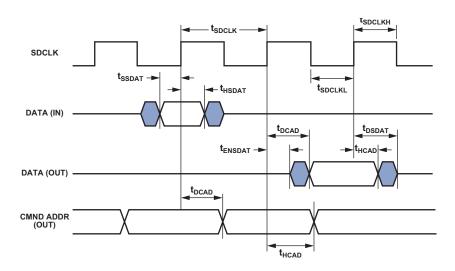

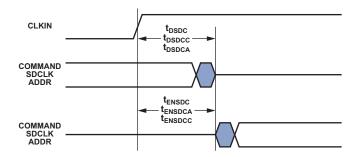

### **SDRAM Controller**

The SDRAM controller provides an interface of up to four separate banks of industry-standard SDRAM devices or DIMMs, at speeds up to  $f_{\text{\tiny SCLK}}$ . Fully compliant with the SDRAM standard, each bank has its own memory select line ( $\overline{\text{MSO}}$ – $\overline{\text{MS3}}$ ), and can be configured to contain between 16M bytes and 128M bytes of memory. SDRAM external memory address space is shown in Table 4.

A set of programmable timing parameters is available to configure the SDRAM banks to support slower memory devices. The memory banks can be configured as either 32 bits wide for maximum performance and bandwidth or 16 bits wide for minimum device count and lower system cost.

The SDRAM controller address, data, clock, and control pins can drive loads up to distributed 30 pF loads. For larger memory systems, the SDRAM controller external buffer timing should be selected and external buffering should be provided so that the load on the SDRAM controller pins does not exceed 30 pF.

### **External Memory**

The external port provides a high performance, glueless interface to a wide variety of industry-standard memory devices. The 32-bit wide bus can be used to interface to synchronous and/or asynchronous memory devices through the use of its separate internal memory controllers. The first is an SDRAM controller

Table 4. External Memory for SDRAM Addresses

| Bank   | Size in<br>Words | Address Range           |

|--------|------------------|-------------------------|

| Bank 0 | 62M              | 0x0020 0000-0x03FF FFFF |

| Bank 1 | 64M              | 0x0400 0000-0x07FF FFFF |

| Bank 2 | 64M              | 0x0800 0000-0x0BFF FFFF |

| Bank 3 | 64M              | 0x0C00 0000-0x0FFF FFFF |

for connection of industry-standard synchronous DRAM devices and DIMMs (dual inline memory module), while the second is an asynchronous memory controller intended to interface to a variety of memory devices. Four memory select pins enable up to four separate devices to coexist, supporting any desired combination of synchronous and asynchronous device types. Non-SDRAM external memory address space is shown in Table 5.

Table 5. External Memory for Non-SDRAM Addresses

| Bank   | Size in<br>Words | Address Range           |

|--------|------------------|-------------------------|

| Bank 0 | 14M              | 0x0020 0000-0x00FF FFFF |

| Bank 1 | 16M              | 0x0400 0000-0x04FF FFFF |

| Bank 2 | 16M              | 0x0800 0000-0x08FF FFFF |

| Bank 3 | 16M              | 0x0C00 0000-0x0CFF FFFF |

### **Shared External Memory**

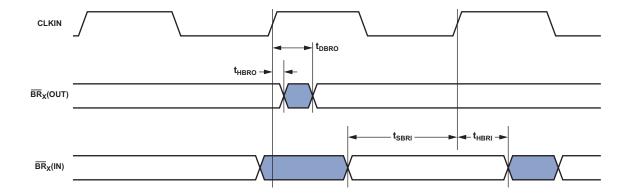

The ADSP-21368 processor supports connecting to common shared external memory with other ADSP-21368 processors to create shared external bus processor systems. This support includes:

- Distributed, on-chip arbitration for the shared external bus

- Fixed and rotating priority bus arbitration

- Bus time-out logic

- Bus lock

Multiple processors can share the external bus with no additional arbitration logic. Arbitration logic is included on-chip to allow the connection of up to four processors.

Bus arbitration is accomplished through the  $\overline{BR1-4}$  signals and the priority scheme for bus arbitration is determined by the setting of the RPBA pin. Table 8 on Page 13 provides descriptions of the pins used in multiprocessor systems.

### **External Port Throughput**

The throughput for the external port, based on 166 MHz clock and 32-bit data bus, is 221M bytes/s for the AMI and 664M bytes/s for SDRAM.

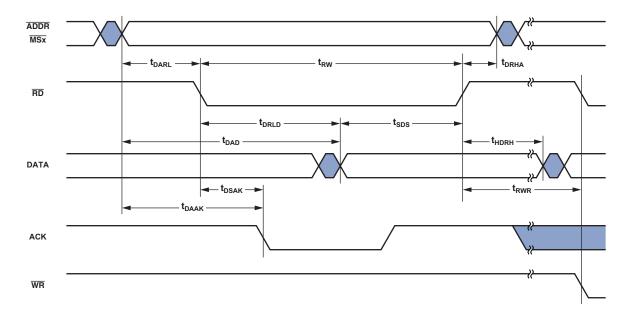

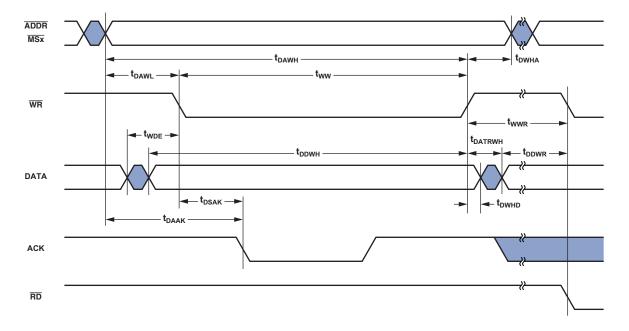

### **Asynchronous Memory Controller**

The asynchronous memory controller provides a configurable interface for up to four separate banks of memory or I/O devices. Each bank can be independently programmed with different timing parameters, enabling connection to a wide variety of memory devices including SRAM, ROM, flash, and EPROM, as well as I/O devices that interface with standard memory control lines. Bank 0 occupies a 14M word window and Banks 1, 2, and 3 occupy a 16M word window in the processor's address space but, if not fully populated, these windows are not made contiguous by the memory controller logic. The banks can also be configured as 8-bit, 16-bit, or 32-bit wide buses for ease of interfacing to a range of memories and I/O devices tailored either to high performance or to low cost and power.

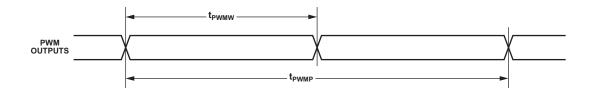

### **Pulse-Width Modulation**

The PWM module is a flexible, programmable, PWM waveform generator that can be programmed to generate the required switching patterns for various applications related to motor and engine control or audio power control. The PWM generator can generate either center-aligned or edge-aligned PWM waveforms. In addition, it can generate complementary signals on two outputs in paired mode or independent signals in non-paired mode (applicable to a single group of four PWM waveforms).

The entire PWM module has four groups of four PWM outputs each. Therefore, this module generates 16 PWM outputs in total. Each PWM group produces two pairs of PWM signals on the four PWM outputs.

The PWM generator is capable of operating in two distinct modes while generating center-aligned PWM waveforms: single update mode or double update mode. In single update mode, the duty cycle values are programmable only once per PWM period. This results in PWM patterns that are symmetrical about the midpoint of the PWM period. In double update mode, a second updating of the PWM registers is implemented at the midpoint of the PWM period. In this mode, it is possible to produce asymmetrical PWM patterns that produce lower harmonic distortion in 2-phase PWM inverters.

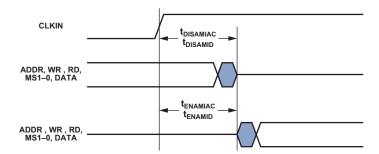

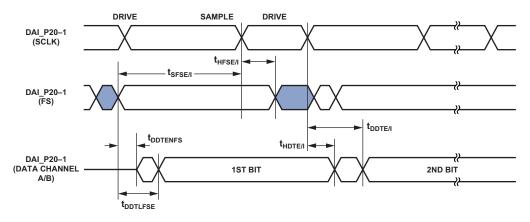

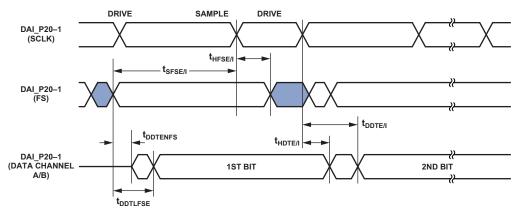

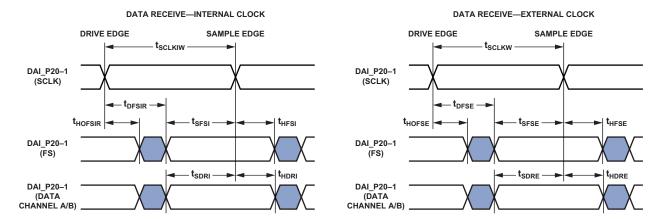

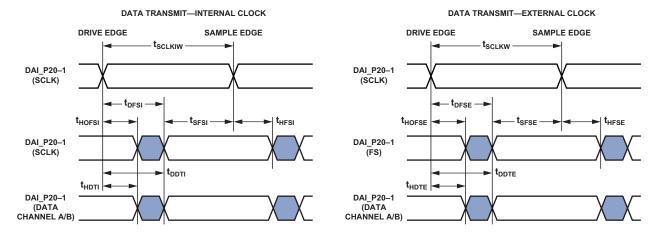

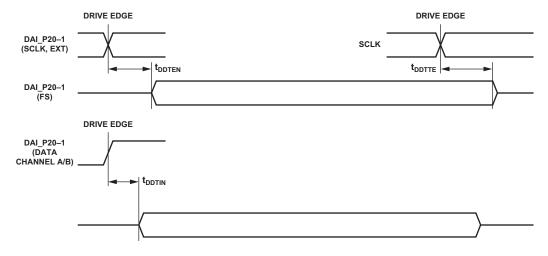

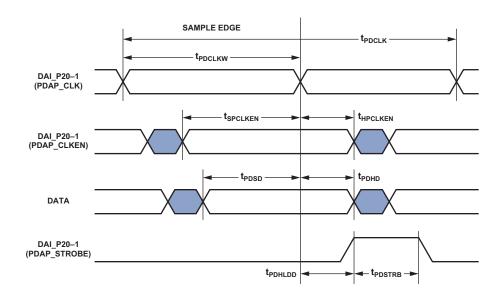

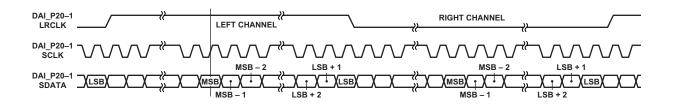

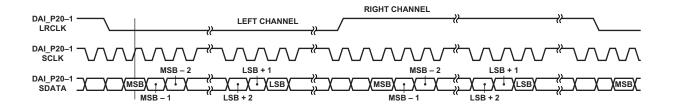

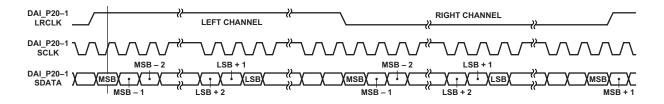

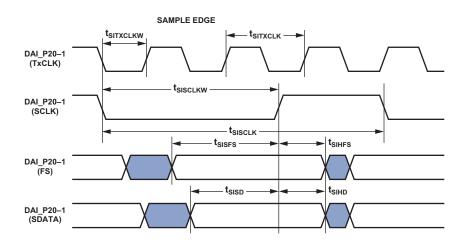

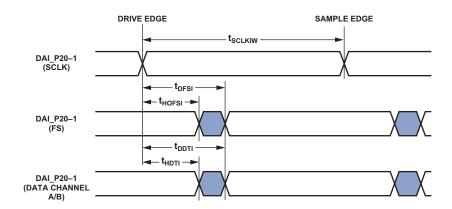

### **Digital Applications Interface (DAI)**

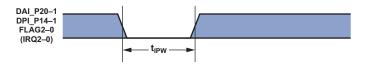

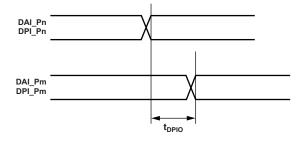

The digital applications interface (DAI) provide the ability to connect various peripherals to any of the DSP's DAI pins (DAI\_P20-1). Programs make these connections using the signal routing unit (SRU1), shown in Figure 1.

The SRU is amatrix routing unit (or group of multiplexers) that enable the peripherals provided by the DAI to be interconnected under software control. This allows easy use of the associated peripherals for a much wider variety of applications by using a larger set of algorithms than is possible with nonconfigurable signal paths.

The DAI include eight serial ports, an S/PDIF receiver/transmitter, four precision clock generators (PCG), eight channels of synchronous sample rate converters, and an input data port (IDP). The IDP provides an additional input path to the

processor core, configurable as either eight channels of I<sup>2</sup>S serial data or as seven channels plus a single 20-bit wide synchronous parallel data acquisition port. Each data channel has its own DMA channel that is independent from the processor's serial ports.

For complete information on using the DAI, see the ADSP-21368 SHARC Processor Hardware Reference.

### **Serial Ports**

The processors feature eight synchronous serial ports (SPORTs) that provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as Analog Devices' AD183x family of audio codecs, ADCs, and DACs. The serial ports are made up of two data lines, a clock, and frame sync. The data lines can be programmed to either transmit or receive and each data line has a dedicated DMA channel.

Serial ports are enabled via 16 programmable and simultaneous receive or transmit pins that support up to 32 transmit or 32 receive channels of audio data when all eight SPORTs are enabled, or eight full duplex TDM streams of 128 channels per frame.

The serial ports operate at a maximum data rate of 50 Mbps. Serial port data can be automatically transferred to and from on-chip memory via dedicated DMA channels. Each of the serial ports can work in conjunction with another serial port to provide TDM support. One SPORT provides two transmit signals while the other SPORT provides the two receive signals. The frame sync and clock are shared.

Serial ports operate in five modes:

- Standard DSP serial mode

- Multichannel (TDM) mode with support for packed I<sup>2</sup>S mode

- I<sup>2</sup>S mode

- Packed I<sup>2</sup>S mode

- · Left-justified sample pair mode

Left-justified sample pair mode is a mode where in each frame sync cycle two samples of data are transmitted/received—one sample on the high segment of the frame sync, the other on the low segment of the frame sync. Programs have control over various attributes of this mode.

Each of the serial ports supports the left-justified sample pair and  $I^2S$  protocols ( $I^2S$  is an industry-standard interface commonly used by audio codecs, ADCs, and DACs such as the Analog Devices AD183x family), with two data pins, allowing four left-justified sample pair or  $I^2S$  channels (using two stereo devices) per serial port, with a maximum of up to 32  $I^2S$  channels. The serial ports permit little-endian or big-endian transmission formats and word lengths selectable from 3 bits to 32 bits. For the left-justified sample pair and  $I^2S$  modes, dataword lengths are selectable between 8 bits and 32 bits. Serial ports offer selectable synchronization and transmit modes as well as optional  $\mu$ -law or A-law companding selection on a per channel basis. Serial port clocks and frame syncs can be internally or externally generated.

The serial ports also contain frame sync error detection logic where the serial ports detect frame syncs that arrive early (for example, frame syncs that arrive while the transmission/reception of the previous word is occurring). All the serial ports also share one dedicated error interrupt.

### S/PDIF-Compatible Digital Audio Receiver/Transmitter

The S/PDIF receiver/transmitter has no separate DMA channels. It receives audio data in serial format and converts it into a biphase encoded signal. The serial data input to the receiver/transmitter can be formatted as left-justified, I²S, or right-justified with word widths of 16, 18, 20, or 24 bits.

The serial data, clock, and frame sync inputs to the S/PDIF receiver/transmitter are routed through the signal routing unit (SRU). They can come from a variety of sources such as the SPORTs, external pins, the precision clock generators (PCGs), or the sample rate converters (SRC) and are controlled by the SRU control registers.

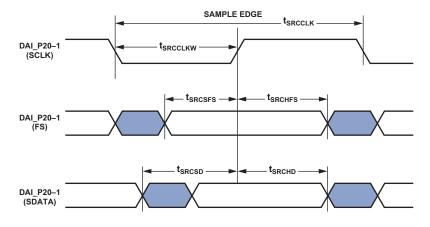

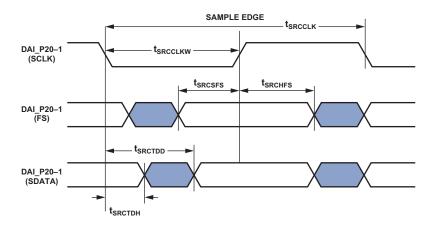

### Synchronous/Asynchronous Sample Rate Converter

The sample rate converter (SRC) contains four SRC blocks and is the same core as that used in the AD1896 192 kHz stereo asynchronous sample rate converter and provides up to 128 dB SNR. The SRC block is used to perform synchronous or asynchronous sample rate conversion across independent stereo channels, without using internal processor resources. The four SRC blocks can also be configured to operate together to convert multichannel audio data without phase mismatches. Finally, the SRC can be used to clean up audio data from jittery clock sources such as the S/PDIF receiver.

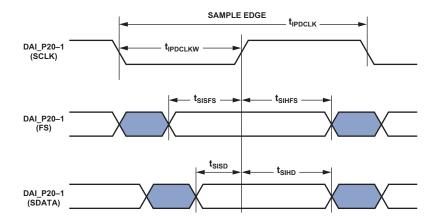

### **Input Data Port**

The IDP provides up to eight serial input channels—each with its own clock, frame sync, and data inputs. The eight channels are automatically multiplexed into a single 32-bit by eight-deep FIFO. Data is always formatted as a 64-bit frame and divided into two 32-bit words. The serial protocol is designed to receive audio channels in I2S, left-justified sample pair, or right-justified mode. One frame sync cycle indicates one 64-bit left/right pair, but data is sent to the FIFO as 32-bit words (that is, one-half of a frame at a time). The processor supports 24- and 32-bit I<sup>2</sup>S, 24- and 32-bit left-justified, and 24-, 20-, 18- and 16-bit right-justified formats.

### **Precision Clock Generators**

The precision clock generators (PCG) consist of four units, each of which generates a pair of signals (clock and frame sync) derived from a clock input signal. The units, A B, C, and D, are identical in functionality and operate independently of each other. The two signals generated by each unit are normally used as a serial bit clock/frame sync pair.

### Digital Peripheral Interface (DPI)

The digital peripheral interface provides connections to two serial peripheral interface ports (SPI), two universal asynchronous receiver-transmitters (UARTs), a 2-wire interface (TWI), 12 flags, and three general-purpose timers.

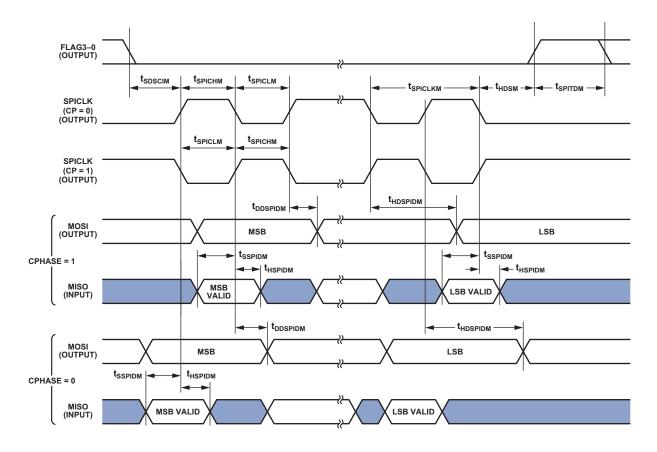

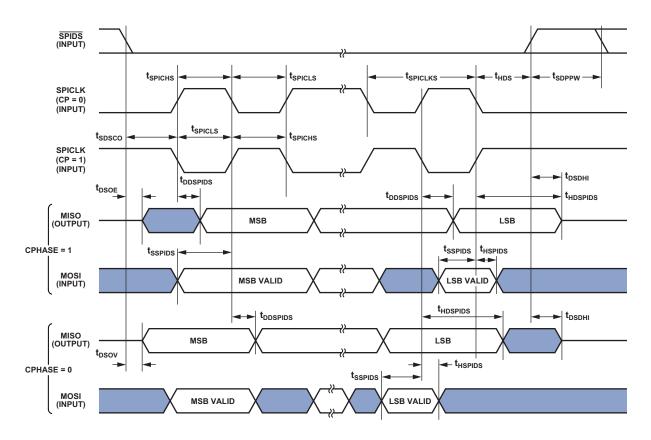

### Serial Peripheral (Compatible) Interface

The processors contain two serial peripheral interface ports (SPIs). The SPI is an industry-standard synchronous serial link, enabling the SPI-compatible port to communicate with other SPI-compatible devices. The SPI consists of two data pins, one device select pin, and one clock pin. It is a full-duplex synchronous serial interface, supporting both master and slave modes. The SPI port can operate in a multimaster environment by interfacing with up to four other SPI-compatible devices, either acting as a master or slave device. The ADSP-21367/ADSP-21368/ADSP-21369 SPI-compatible peripheral implementation also features programmable baud rate and clock phase and polarities. The SPI-compatible port uses open-drain drivers to support a multimaster configuration and to avoid data contention.

### **UART Port**

The processors provide a full-duplex universal asynchronous receiver/transmitter (UART) port, which is fully compatible with PC-standard UARTs. The UART port provides a simplified UART interface to other peripherals or hosts, supporting full-duplex, DMA-supported, asynchronous transfers of serial data. The UART also has multiprocessor communication capability using 9-bit address detection. This allows it to be used in multidrop networks through the RS-485 data interface standard. The UART port also includes support for five data bits to eight data bits, one stop bit or two stop bits, and none, even, or odd parity. The UART port supports two modes of operation:

- PIO (programmed I/O) The processor sends or receives data by writing or reading I/O-mapped UART registers.

The data is double-buffered on both transmit and receive.

- DMA (direct memory access) The DMA controller transfers both transmit and receive data. This reduces the number and frequency of interrupts required to transfer data to and from memory. The UART has two dedicated DMA channels, one for transmit and one for receive. These DMA channels have lower default priority than most DMA channels because of their relatively low service rates.

The UART port's baud rate, serial data format, error code generation and status, and interrupts are programmable:

- Supporting bit rates ranging from ( $f_{\text{SCLK}}/1,048,576$ ) to ( $f_{\text{SCLK}}/16$ ) bits per second.

- Supporting data formats from 7 bits to 12 bits per frame.

- Both transmit and receive operations can be configured to generate maskable interrupts to the processor.

Where the 16-bit UART\_Divisor comes from the DLH register (most significant eight bits) and DLL register (least significant eight bits).

In conjunction with the general-purpose timer functions, autobaud detection is supported.

### **Peripheral Timers**

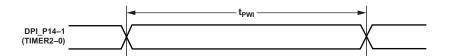

Three general-purpose timers can generate periodic interrupts and be independently set to operate in one of three modes:

- · Pulse waveform generation mode

- Pulse width count/capture mode

- External event watchdog mode

Each general-purpose timer has one bidirectional pin and four registers that implement its mode of operation: a 6-bit configuration register, a 32-bit count register, a 32-bit period register, and a 32-bit pulse width register. A single control and status register enables or disables all three general-purpose timers independently.

### 2-Wire Interface Port (TWI)

The TWI is a bidirectional 2-wire serial bus used to move 8-bit data while maintaining compliance with the I<sup>2</sup>C bus protocol. The TWI master incorporates the following features:

- Simultaneous master and slave operation on multiple device systems with support for multimaster data arbitration

- Digital filtering and timed event processing

- 7-bit and 10-bit addressing

- 100 kbps and 400 kbps data rates

- Low interrupt rate

### I/O PROCESSOR FEATURES

The I/O processor provides many channels of DMA, and controls the extensive set of peripherals described in the previous sections.

### **DMA Controller**

The processor's on-chip DMA controller allows data transfers without processor intervention. The DMA controller operates independently and invisibly to the processor core, allowing DMA operations to occur while the core is simultaneously executing its program instructions. DMA transfers can occur between the processor's internal memory and its serial ports, the SPI-compatible (serial peripheral interface) ports, the IDP (input data port), the parallel data acquisition port (PDAP), or the UART.

Thirty four channels of DMA are available on the ADSP-2136x processors as shown in Table 6.

Table 6. DMA Channels

| Peripheral       | DMA Channels |

|------------------|--------------|

| SPORTs           | 16           |

| PDAP             | 8            |

| SPI              | 2            |

| UART             | 4            |

| External Port    | 2            |

| Memory-to-Memory | 2            |

### **Delay Line DMA**

The ADSP-21367/ADSP-21368/ADSP-21369 processors provide delay line DMA functionality. This allows processor reads and writes to external delay line buffers (in external memory, SRAM, or SDRAM) with limited core interaction.

#### SYSTEM DESIGN

The following sections provide an introduction to system design options and power supply issues.

### **Program Booting**

The internal memory of the processors can be booted up at system power-up from an 8-bit EPROM via the external port, an SPI master or slave, or an internal boot. Booting is determined by the boot configuration (BOOT\_CFG1-0) pins (see Table 7 and the processor hardware reference). Selection of the boot source is controlled via the SPI as either a master or slave device, or it can immediately begin executing from ROM.

Table 7. Boot Mode Selection

| BOOT_CFG1-0 | Booting Mode     |

|-------------|------------------|

| 00          | SPI Slave Boot   |

| 01          | SPI Master Boot  |

| 10          | EPROM/FLASH Boot |

| 11          | Reserved         |

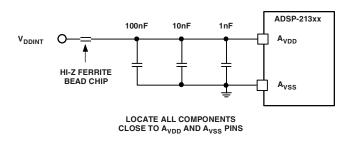

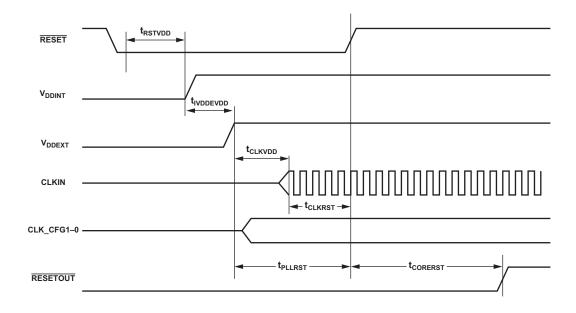

### **Power Supplies**