# **Compact Flash Card**

Oct. 19, 2010

#### FEATURES:

• Compliant with Compact Flash specification version 4.1

#### • PC card ATA and True IDE Interface

- 512 bytes sector

- ATA command set compatible

- Support Data Transfer up to PIO Mode-6 /Multi-Word DMA 4/ Ultra DMA 5/ Ultra DMA 6

- Capacities:

- 2GB 32GB

- RoHS Compliant

- Performance

- Max. performance up to 20MB/s for Read, 5MB/s for Write

#### • Power Management Unit

- Auto Stand-by and Sleep Mode.

#### • Temperature Ranges

- 0°C to +70°C for operating

- -20°C to 85°C for storage

- Support Voltage Read and Write Operation

3.3 V

- 5.0 V

- Support wear leveling function

- Support ECC function

- 4KB / 8KB data per page

#### • Physical Dimensions

- 36.4mm x 42.8mm x 3.3mm

## TABLE OF CONTENTS

| PRODUCT DESCRIPTION             | 4  |

|---------------------------------|----|

| 1.0 GENERAL DESCRIPTION         | 5  |

| 2.0 ELECTRICAL INTERFACE        | 6  |

| 2.1 Pin Assignment and Pin Type | 6  |

| 2.2 Signal Description          | 8  |

| 3.0 ELECTRICAL SPECIFICATION    | 15 |

| 4.0 PHYSICAL DIMENSIONS         | 16 |

| REVISION HISTORY                | 17 |

## **PRODUCT DESCRIPTION**

Apacer Photo Steno CompactFlash card is a high performance, removable flash memory data storage system. This product is well suited for solid-state mass storage portable applications offering new and expanded functionality while enabling smaller and lighter designs.

Apacer Photo Steno IV technology is widely used in a variety of consumer products such as portable computers, digital cameras, handheld data collection scanners, Personal Digital Assistants (PDAs), handy terminals, audio players, monitoring devices and set-top boxes. Also, it is special for high-end professional photographers who require the highest possible performance and the largest capacities for their SLR cameras.

Photo Steno IV CF card provides completes PCMCIA – ATA functionality and compatibility, besides, it supports Ultra DMA technology. This is achieved because the 50-pin CF card can be easily slipped into a passive 68-pin Type II adapter card that fully meets PCMCIA electrical and mechanical interface specifications.

## **1.0 GENERAL DESCRIPTION**

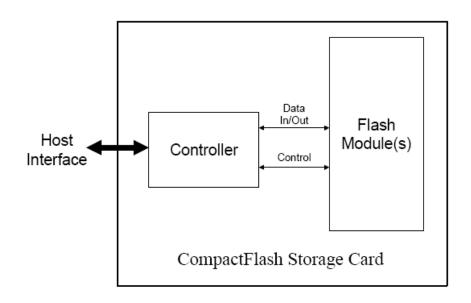

The Compact Flash Storage Card contains a single chip controller and flash memory module(s) in a matchbook-sized package with a 50-pin connector consisting of two rows of 25 female contacts each on 50 mil (1.27 mm) centers.

CompactFlash Storage Card Block Diagram

## 2.0 ELECTRICAL INTERFACE

### 2.1 Pin Assignment and Pin Type

The signal/pin assignments are listed in Table A Low active signals have a "-" prefix. Pin types are Input, Output or Input/ Output.

| PC Card Memory Mode |                  | PC Card I | /O Mode |                         | True IDE Mode <sup>4</sup> |    |                       |     |

|---------------------|------------------|-----------|---------|-------------------------|----------------------------|----|-----------------------|-----|

| Pin Num             | Signal<br>Name   | Pin Type  | Pin Num | Pin Num Signal Pin Type |                            |    | Pin Num Signal Name F |     |

| 1                   | GND              |           | 1       | GND                     |                            | 1  | GND                   |     |

| 2                   | D03              | I/O       | 2       | D03                     | I/O                        | 2  | D03                   | I/O |

| 3                   | D04              | I/O       | 3       | D04                     | I/O                        | 3  | D04                   | I/O |

| 4                   | D05              | I/O       | 4       | D05                     | I/O                        | 4  | D05                   | I/O |

| 5                   | D06              | I/O       | 5       | D06                     | I/O                        | 5  | D06                   | I/O |

| 6                   | D07              | I/O       | 6       | D07                     | I/O                        | 6  | D07                   | I/O |

| 7                   | -CE1             | I         | 7       | -CE1                    | 1                          | 7  | -CS0                  | I   |

| 8                   | A10              | I         | 8       | A10                     | I                          | 8  | A10 <sup>2</sup>      | I   |

| 9                   | -OE              | I         | 9       | -OE                     | I                          | 9  | -ATA<br>SEL           | I   |

| 10                  | A09              | I         | 10      | A09                     | I                          | 10 | A09 <sup>2</sup>      | I   |

| 11                  | A08              | I         | 11      | A08                     | I                          | 11 | A08 <sup>2</sup>      | I   |

| 12                  | A07              | I         | 12      | A07                     | I                          | 12 | A07 <sup>2</sup>      | I   |

| 13                  | VCC              |           | 13      | VCC                     |                            | 13 | VCC                   |     |

| 14                  | A06              | I         | 14      | A06                     | I                          | 14 | A06 <sup>2</sup>      | I   |

| 15                  | A05              | I         | 15      | A05                     | I                          | 15 | A05 <sup>2</sup>      | I   |

| 16                  | A04              | I         | 16      | A04                     | I                          | 16 | A04 <sup>2</sup>      | I   |

| 17                  | A03              | I         | 17      | A03                     | I                          | 17 | A03 <sup>2</sup>      | I   |

| 18                  | A02              | I         | 18      | A02                     | 1                          | 18 | A02                   | I   |

| 19                  | A01              | I         | 19      | A01                     | I                          | 19 | A01                   | I   |

| 20                  | A00              | I         | 20      | A00                     | I                          | 20 | A00                   | I   |

| 21                  | D00              | I/O       | 21      | D00                     | I/O                        | 21 | D00                   | I/O |

| 22                  | D01              | I/O       | 22      | D01                     | I/O                        | 22 | D01                   | I/O |

| 23                  | D02              | I/O       | 23      | D02                     | I/O                        | 23 | D02                   | I/O |

| 24                  | WP               | 0         | 24      | -IOIS16                 | 0                          | 24 | -IOCS16               | 0   |

| 25                  | -CD2             | 0         | 25      | -CD2                    | 0                          | 25 | -CD2                  | 0   |

| 26                  | -CD1             | 0         | 26      | -CD1                    | 0                          | 26 | -CD1                  | 0   |

| 27                  | D11 <sup>1</sup> | I/O       | 27      | D11 <sup>1</sup>        | I/O                        | 27 | D11 <sup>1</sup>      | I/O |

#### TABLE A: CARD PIN ASSIGNMENT

| 28 | D12 <sup>1</sup>        | I/O | 28 | D12 <sup>1</sup>        | I/O | 28 | D12 <sup>1</sup>        | I/O |

|----|-------------------------|-----|----|-------------------------|-----|----|-------------------------|-----|

| 29 | D13 <sup>1</sup>        | I/O | 29 | D13 <sup>1</sup>        | I/O | 29 | D13 <sup>1</sup>        | I/O |

| 30 | D14 <sup>1</sup>        | I/O | 30 | D14 <sup>1</sup>        | I/O | 30 | D14 <sup>1</sup>        | I/O |

| 31 | D15 <sup>1</sup>        | I/O | 31 | D15 <sup>1</sup>        | I/O | 31 | D15 <sup>1</sup>        | I/O |

| 32 | -CE2 <sup>1</sup>       | I   | 32 | -CE2 <sup>1</sup>       | I   | 32 | -CS1 <sup>1</sup>       | I   |

| 33 | -VS1                    | 0   | 33 | -VS1                    | 0   | 33 | -VS1                    | 0   |

|    | -IORD                   |     |    | -IORD                   |     |    | -IORD                   |     |

| 34 | HSTROBE                 |     | 34 | HSTROBE                 |     | 34 | HSTROBE                 | 1   |

|    | -<br>HDMARDY            |     |    | -<br>HDMARDY            | -   |    | -<br>HDMARDY            |     |

| 35 | -IOWR                   |     | 35 | -IOWR                   | 1   | 35 | -IOWR                   |     |

| 30 | STOP                    | 1   | 30 | STOP                    |     | 30 | STOP                    |     |

| 36 | -WE                     | I   | 36 | -WE                     | I   | 36 | -WE <sup>3</sup>        | I   |

| 37 | READY                   | 0   | 37 | -IREQ                   | 0   | 37 | INTRQ                   | 0   |

| 38 | VCC                     |     | 38 | VCC                     |     | 38 | VCC                     |     |

| 39 | -CSEL <sup>5</sup>      | I   | 39 | -CSEL <sup>5</sup>      | 1   | 39 | -CSEL                   | I   |

| 40 | -VS2                    | 0   | 40 | -VS2                    | 0   | 40 | -VS2                    | 0   |

| 41 | RESET                   | I   | 41 | RESET                   | I   | 41 | -RESET                  | I   |

|    | -WAIT                   |     |    | -WAIT                   |     |    | IORDY                   |     |

| 42 | -<br>DOMARDY<br>DSTROBE | 0   | 42 | -<br>DOMARDY<br>DSTROBE | 0   | 42 | -<br>DOMARDY<br>DSTROBE | 0   |

|    | -INPACK                 |     |    | -INPACK                 |     |    |                         |     |

| 43 | -DMARQ                  | 0   | 43 | -DMARQ                  | 0   | 43 | DMARQ                   | 0   |

|    | -REG                    |     |    | -REG                    |     |    | DIALOK                  |     |

| 44 | DMACK                   | 1   | 44 | DMACK                   | -1  | 44 | -DMACK                  | I   |

| 45 | BVD2                    | 0   | 45 | -SPKR                   | 0   | 45 | -DASP                   | I/O |

| 46 | BVD1                    | 0   | 46 | -<br>STSCHG             | 0   | 46 | -PDIAG                  | I/O |

| 47 | D08 <sup>1</sup>        | I/O | 47 | D08 <sup>1</sup>        | I/O | 47 | D08 <sup>1</sup>        | I/O |

| 48 | D09 <sup>1</sup>        | I/O | 48 | D09 <sup>1</sup>        | I/O | 48 | D09 <sup>1</sup>        | I/O |

| 49 | D10 <sup>1</sup>        | I/O | 49 | D10 <sup>1</sup>        | I/O | 49 | D10 <sup>1</sup>        | I/O |

| 50 | GND                     |     | 50 | GND                     |     | 50 | GND                     |     |

## 2.2 Signal Description

| Signal Name                        | Туре | Pin                                     | Description                                                                                                                                                                                                                                                                                                                             |

|------------------------------------|------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10 – A0<br>(PC Card Memory mode)  | Î    | 8,10,11,12,<br>14,15,16,17<br>,18,19,20 | These address lines along with the -REG signal are<br>used to select the following: The I/O port address<br>registers within the Compact-Flash card, the<br>memory mapped port address registers within the<br>Compact Flash card, a byte in the card's information<br>structure and its configuration control and status<br>registers. |

| A10 – A0<br>(PC Card I/O mode)     |      |                                         | This signal is the same as the PC Card Memory<br>Mode signal                                                                                                                                                                                                                                                                            |

| A10 – A0<br>(True IDE mode)        |      | 18,19,20                                | In True IDE Mode only A[2:0] are used to select the one of eight (True IDE Mode) registers in the Task File, the remaining address lines should be grounded by the host.                                                                                                                                                                |

| BVD1<br>(PC Card Memory mode)      | I/O  | 46                                      | This signal is asserted high, as BVD1 is not supported.                                                                                                                                                                                                                                                                                 |

| -STSCHG<br>(PC Card I/O mode)      |      |                                         | This signal is asserted low to alert the host to changes<br>in the RDY/- BSY and Write Protect states, while the<br>I/O interface is configured. Its use is controlled by the<br>Card Config and Status Register                                                                                                                        |

| -PDIAG<br>(True IDE mode)          |      |                                         | In the True IDE Mode, this input/output is the Pass<br>Diagnostic signal in the Master/Slave handshake<br>protocol.                                                                                                                                                                                                                     |

| BVD2<br>(PC Card Memory mode)      | I/O  | 45                                      | This signal is asserted high, as BVD2 is not supported.                                                                                                                                                                                                                                                                                 |

| -SPKR<br>(PC Card I/O mode)        |      |                                         | This line is the Binary Audio output from the card. If<br>the Card does not support the Binary Audio<br>function, this line should be held negated.                                                                                                                                                                                     |

| -DASP<br>(True IDE mode)           |      |                                         | In the True IDE Mode, this input/output is the Disk<br>Active/Slave Present signal in the Master/Slave<br>handshake protocol.                                                                                                                                                                                                           |

| -CD1,-CD2<br>(PC Card Memory mode) | 0    | 26,25                                   | These Card Detect pins are connected to ground on<br>the Compact Flash Storage Card. They are used by<br>the host to determine that the Compact Flash<br>Storage Card is fully inserted into its socket.                                                                                                                                |

| -CD1,-CD2<br>(PC Card I/O mode)    |      |                                         | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                  |

| -CD1,-CD2<br>(True IDE mode)       |      |                                         | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                  |

| Signal Name                                       | Туре | Pin                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------|------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -CE1,-CE2<br>(PC Card Memory mode)<br>Card Enable | 1    | 7,32                                 | These input signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performedCE2 always accesses the odd byte of the wordCE1 accesses the even byte or the Odd byte of the word depending on A0 and -CE2.<br>A multiplexing scheme based on A0,-CE1, -CE2 allows 8 bit hosts to access all data on D0-D7. See Table 30, Table 33, Table 35, Table 39, Table 41 and Table 42.<br>While (-) DMACK is asserted, -CE1 and -CE2 shall be held negated and the width of the transfers shall be 16 bits. |

| -CE1,-CE2<br>(PC Card I/O mode)<br>Card Enable    |      |                                      | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| - CE1,- CE2<br>(True IDE mode)                    |      |                                      | In the True IDE Mode, -CS0 is the address range select<br>for the task file registers while -CS1 is used to select the<br>Alternate Status Register and the Device Control<br>Register.<br>While –DMACK is asserted, -CS0 and –CS1 shall be held<br>negated and the width of the transfers shall be 16 bits.                                                                                                                                                                                                                                               |

| -CSEL<br>(PC Card Memory mode)                    | I    | 39                                   | This signal is not used for this mode, but should be connected by the host to PC Card A25 or grounded by the host.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -CSEL<br>(PC Card I/O mode)                       |      |                                      | This signal is not used for this mode, but should be<br>connected by the host to PC Card A25 or grounded by<br>the host.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -CSEL<br>(True IDE mode)                          |      |                                      | This internally pulled up signal is used to configure this<br>device as a Master or a Slave when configured in the True<br>IDE Mode. When this pin is grounded, this device is<br>configured as a Master. When the pin is open, this device is<br>configured as a Slave                                                                                                                                                                                                                                                                                    |

| D15 – D0<br>(PC Card Memory mode)                 | I/O  | 31,30,29,<br>28,27,49,<br>48,47,6,5, | These lines carry the Data, Commands and Status information<br>between the host and the controller. D00 is the LSB of the Even<br>Byte of the Word. D08 is the LSB of the Odd Byte of the Word.                                                                                                                                                                                                                                                                                                                                                            |

| D15 – D0<br>(PC Card I/O mode)                    |      | 4,3,2,23<br>,22,21                   | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D15 – D0<br>(True IDE mode)                       |      |                                      | In True IDE Mode, all Task File operations occur in Byte-Mode<br>on the low order bus D00-D07 while all data transfers are 16 bit<br>using D00- D15.                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND<br>(PC Card Memory mode)                      | -    | 1,50                                 | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND<br>(PC Card I/O mode)                         |      |                                      | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GND<br>(True IDE mode)                            |      |                                      | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   |      |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Signal Name                                                                                                                                                    | Туре | Pin | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -INPACK<br>((PC Card Memory Mode<br>except Ultra DMA<br>Protocol Active)                                                                                       | 0    | 43  | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -INPACK<br>(PC Card I/O Mode<br>except Ultra DMA<br>Protocol Active)<br>Input Acknowledge                                                                      |      |     | The Input Acknowledge signal is asserted by the Compact Flash<br>Card when the card is selected and responding to an I/O read<br>cycle at the address that is on the address bus. This signal is<br>used by the host to control the enable of any input data buffers<br>between the Compact Flash card and the CPU.<br>Hosts that support a single socket per interface logic,<br>such as for Advanced Timing Modes and Ultra DMA<br>operation may ignore the –INPACK signal from the<br>device and manage their input buffers based solely on<br>Card Enable signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DMARQ<br>(PC Card Memory Mode -<br>Ultra DMA Protocol<br>Active)<br>-DMARQ<br>(PC Card I/O Mode -<br>Ultra DMA Protocol<br>Active)<br>DMARQ<br>(True IDE Mode) |      |     | Card Enable signals.<br>This signal is a DMA Request that is used for DMA data<br>transfers between host and device. It shall be asserted by<br>the device when it is ready to transfer data to or from the<br>host. For Multiword DMA transfers, the direction of data<br>transfer is controlled by -IORD and -IOWR. This signal is<br>used in a handshake manner with (-) DMACK, i.e., the<br>device shall wait until the host asserts (-) DMACK before<br>negating (-) DMARQ, and re-asserting (-) DMARQ if there<br>is more data to transfer.<br>In PCMCIA I/O Mode, the -DMARQ shall be ignored by<br>the host while the host is performing an I/O Read cycle to<br>the device. The host shall not initiate an I/O Read cycle to<br>the device. The host shall not initiate an I/O Read cycle to<br>the device is not selected in the Drive-Head register.<br>While a DMA operation is in progress, -CS0 (-CE1) and -<br>CS1 (-CE2) shall be held negated and the width of the<br>transfers shall be 16 bits.<br>If there is no hardware support for True IDE DMA mode<br>in the host, this output signal is not used and should not<br>be connected at the host. In this case, the BIOS must<br>report that DMA mode is not supported by the host so<br>that device drivers will not attempt DMA mode operation.<br>A host that does not support DMA mode and implements<br>both PC Card and True IDE modes of operation need not<br>alter the PC Card mode connections while in True IDE<br>mode as long as this does not prevent proper operation in<br>any mode. |

| Signal Name                                                             | Туре | Pin | Description                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IORD<br>(PC Card Memory Mode<br>except Ultra DMA<br>Protocol Active)   |      | 34  | This signal is not used in this mode.                                                                                                                                                                                                                                                                                  |

| -IORD<br>(PC Card I/O Mode<br>except Ultra DMA<br>Protocol Active)      |      |     | This is an I/O Read strobe generated by the host. This signal gates I/ O data onto the bus from the Compact Flash Card when the card is configured to use the I/O interface.                                                                                                                                           |

| -IORD<br>(True IDE Mode – Except<br>Ultra DMA Protocol<br>Active)       |      |     | In True IDE Mode, this signal has the same function as in PC<br>Card I/ O Mode.                                                                                                                                                                                                                                        |

| -HDMARDY<br>(All Modes - Ultra DMA<br>Protocol DMA Read)                |      |     | In all modes when Ultra DMA mode DMA Read is active,<br>this signal is asserted by the host to indicate that the host<br>is ready to receive Ultra DMA data-in bursts. The host<br>may negate –HDMARDY to pause an Ultra DMA transfer.                                                                                 |

| HSTROBE<br>(All Modes - Ultra DMA<br>Protocol DMA Write)                |      |     | In all modes when Ultra DMA mode DMA Write is active,<br>this signal is the data out strobe generated by the host.<br>Both the rising and falling edge of HSTROBE cause data<br>to be latched by the device. The host may stop<br>generating HSTROBE edges to pause an Ultra DMA<br>data-out burst.                    |

| -IOWR<br>(PC Card Memory Mode<br>– Except Ultra DMA<br>Protocol Active) | I    | 35  | This signal is not used in this mode.                                                                                                                                                                                                                                                                                  |

| -IOWR<br>(PC Card I/O Mode –<br>Except Ultra DMA<br>Protocol Active)    |      |     | The I/O Write strobe pulse is used to clock I/O data on<br>the Card Data bus into the Compact Flash Storage Card<br>controller registers when the Compact Flash Storage<br>Card is configured to use the I/O interface.<br>The clocking shall occur on the negative to positive edge<br>of the signal (trailing edge). |

| -IOWR<br>(True IDE Mode – Except<br>Ultra DMA Protocol<br>Active)       | •    |     | In True IDE Mode, while Ultra DMA mode protocol is not<br>active, this signal has the same function as in PC Card<br>I/O Mode. When Ultra DMA mode protocol is supported,<br>this signal must be negated before entering Ultra DMA<br>mode protocol.                                                                   |

| STOP<br>(All Modes – Ultra DMA<br>Protocol Active)                      |      |     | In All Modes, while Ultra DMA mode protocol is active,<br>the assertion of this signal causes the termination of the<br>Ultra DMA data burst.                                                                                                                                                                          |

| -OE<br>(PC Card Memory mode)                                            | I    | 9   | This is an Output Enable strobe generated by the host<br>interface. It is used to read data from the Compact Flash<br>Storage Card in Memory Mode and to read the CIS and<br>configuration registers.                                                                                                                  |

| -OE<br>(PC Card I/O mode)<br>-ATA SEL                                   |      |     | In PC Card I/O Mode, this signal is used to read the CIS<br>and configuration registers.<br>To enable True IDE Mode this input should be grounded by                                                                                                                                                                   |

| (True IDE mode)                                                         |      |     | the host.                                                                                                                                                                                                                                                                                                              |

|                                                                         |      |     |                                                                                                                                                                                                                                                                                                                        |

|                                                                         |      |     |                                                                                                                                                                                                                                                                                                                        |

| Signal Name                                                                                       | Туре | Pin | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDY/-BSY<br>(PC Card Memory mode)                                                                 | 0    | 37  | In Memory Mode, this signal is set high when the<br>Compact Flash Storage Card is ready to accept a new<br>data transfer operation and is held low when the card is<br>busy.<br>At power up and at Reset, the READY signal is held low<br>(busy) until the Compact Flash Storage Card has<br>completed its power up or reset function. No access of<br>any type should be made to the Compact Flash Storage<br>Card during this time.<br>Note, however, that when a card is powered up and used<br>with RESET continuously disconnected or asserted, the<br>Reset function of the RESET pin is disabled.<br>Consequently, the continuous assertion of RESET from<br>the application of power shall not cause the READY<br>signal to remain continuously in the busy state.<br>I/O Operation - After the Compact Flash card has been |

| (PC Card I/O mode)                                                                                |      |     | configured for I/O operation, this signal is used as -Interrupt<br>Request. This line is strobe low to generate a pulse mode<br>interrupt or held low for a level mode interrupt.<br>In True IDE Mode signal is the active high Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTRQ<br>(True IDE mode)                                                                          |      |     | to the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -REG<br>(PC Card Memory Mode<br>– Except Ultra DMA<br>Protocol Active)<br>Attribute Memory Select | -    | 44  | This signal is used during Memory Cycles to distinguish<br>between Common Memory and Register (Attribute)<br>Memory accesses. High for Common Memory, Low for<br>Attribute Memory.<br>In PC Card Memory Mode, when Ultra DMA Protocol is<br>supported by the host and the host has enabled Ultra<br>DMA protocol on the card the, host shall keep the -REG<br>signal negated during the execution of any DMA<br>Command by the device.<br>The signal shall also be active (low) during I/O Cycles<br>when the I/O address is on the Bus.                                                                                                                                                                                                                                                                                            |

| Except Ultra DMA<br>Protocol Active)<br>-DMACK<br>(PC Card Memory Mode<br>when Ultra DMA Protocol | -    |     | In PC Card I/O Mode, when Ultra DMA Protocol is<br>supported by the host and the host has enabled Ultra<br>DMA protocol on the card the, host shall keep the -REG<br>signal asserted during the execution of any DMA<br>Command by the device.<br>This is a DMA Acknowledge signal that is asserted by the<br>host in response to (-) DMARQ to initiate DMA transfers.<br>In True IDE Mode, while DMA operations are not active,                                                                                                                                                                                                                                                                                                                                                                                                    |

| Active)<br>DMACK<br>(PC Card I/O Mode when<br>Ultra DMA Protocol<br>Active)                       | _    |     | <ul> <li>the card shall ignore the (-) DMACK signal, including a floating condition.</li> <li>If DMA operation is not supported by a True IDE Mode only host, this signal should be driven high or connected to VCC by the host.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -DMACK<br>(True IDE Mode)                                                                         |      |     | A host that does not support DMA mode and implements<br>both PC Card and True-IDE modes of operation need not<br>alter the PC Card mode connections while in True-IDE<br>mode as long as this does not prevent proper operation<br>all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Signal Name                                                             | Туре | Pin      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET<br>(PC Card Memory mode)<br>RESET                                 |      | 41       | The Compact Flash Storage Card is Reset when the<br>RESET pin is high with the following important exception:<br>The host may leave the RESET pin open or keep it<br>continually high from the application of power without<br>causing a continuous Reset of the card. Under either of<br>these conditions, the card shall emerge from power-up<br>having completed an initial Reset.<br>The Compact Flash Storage Card s also Reset when the<br>Soft Reset bit in the Card Configuration Option Register<br>is set.<br>This signal is the same as the PC Card Memory Mode |

| (PC Card I/O mode)<br>RESET<br>(True IDE mode)                          |      |          | signal.<br>In the True IDE Mode this input pin is the active low<br>hardware reset from the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VCC<br>(PC Card Memory mode)                                            | I-   | 13,38    | +5.0V, +3.3V power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VCC<br>(PC Card I/O mode)                                               |      |          | This signal is the same for all modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCC<br>(True IDE mode)                                                  |      |          | This signal is the same for all modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -VS1<br>-VS2<br>(PC Card Memory mode)                                   | 0    | 33<br>40 | Voltage Sense SignalsVS1 is grounded on the Card<br>and sensed by the Host so that the Compact Flash<br>Storage Card CIS can be read at 3.3 volts and -VS2 is<br>reserved by PCMCIA for a secondary voltage and is not<br>connected on the Card.                                                                                                                                                                                                                                                                                                                           |

| -VS1<br>-VS2<br>(PC Card I/O mode)                                      |      |          | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -VS1<br>-VS2<br>(True IDE Mode)                                         |      |          | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -WAIT<br>(PC Card Memory Mode<br>– Except Ultra DMA<br>Protocol Active) | 0    | 42       | The -WAIT signal is driven low by the Compact Flash<br>Storage Card to signal the host to delay completion of a<br>memory or I/O cycle that is in progress.                                                                                                                                                                                                                                                                                                                                                                                                                |

| -WAIT<br>(PC Card I/O Mode –<br>Except Ultra DMA<br>Protocol Active)    |      |          | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IORDY<br>(True IDE Mode – Except<br>Ultra DMA Protocol<br>Active)       |      |          | In True IDE Mode, except in Ultra DMA modes, this output signal may be used as IORDY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -DDMARDY<br>(All Modes – Ultra DMA<br>Write Protocol Active)            |      |          | In all modes, when Ultra DMA mode DMA Write is active,<br>this signal is asserted by the device during a data burst to<br>indicate that the device is ready to receive Ultra DMA<br>data out bursts. The device may negate -DDMARDY to<br>pause an Ultra DMA transfer.                                                                                                                                                                                                                                                                                                     |

| DSTROBE<br>(All Modes – Ultra DMA<br>Read Protocol Active)              |      |          | In all modes, when Ultra DMA mode DMA Read is active,<br>this signal is the data in strobe generated by the device.<br>Both the rising and falling edge of DSTROBE cause data<br>to be latched by the host. The device may stop<br>generating DSTROBE edges to pause an Ultra DMA data<br>in burst.                                                                                                                                                                                                                                                                        |

| Signal Name                                  | Туре | Pin | Description                                                                                                                                                                                                                                                             |

|----------------------------------------------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -WE<br>(PC Card Memory mode)                 | I    | 36  | This is a signal driven by the host and used for storing<br>memory write data to the registers of the Compact Flash<br>card when the card is configured in the memory interface<br>mode. It is also used for writing the configuration registers.                       |

| -WE<br>(PC Card I/O mode)                    |      |     | In PC Card I/O Mode, this signal is used for writing the<br>configuration registers.                                                                                                                                                                                    |

| -WE<br>(True IDE mode)                       |      |     | In True IDE Mode this input signal is not used and should be connected to VCC by the host                                                                                                                                                                               |

|                                              |      |     |                                                                                                                                                                                                                                                                         |

| WP<br>(PC Card Memory Mode)<br>Write Protect | I    | 24  | Memory Mode - The Compact Flash card does not have<br>a write protect switch. This signal is held low after the<br>completion of the reset initialization sequence.                                                                                                     |

| -IOCS16<br>(PC Card I/O mode)                |      |     | I/O Operation - When the Compact Flash card is configured<br>for I/O Operation Pin 24 is used for the -I/O Selected is 16 Bit<br>Port (-IOCS16) function. A Low signal indicates that a 16 bit<br>or Odd Byte only operation can be performed at the<br>addressed port. |

| -IOCS16<br>(True IDE mode)                   |      |     | In True IDE Mode this output signal is asserted low when this device is expecting a word data transfer cycle.                                                                                                                                                           |

## **3.0 ELECTRICAL SPECIFICATION**

#### Absolute Maximum Conditions

| Parameter                                          | Symbol | Conditions                    |

|----------------------------------------------------|--------|-------------------------------|

| Input Power                                        | Vcc    | -0.3V min. to 6.5V max.       |

| Voltage on any pin except Vcc with respect to GND. | V      | -0.5V min. to Vcc + 0.5V max. |

#### Input Power

| Voltage    | Maximum Average Current | Measurement Method |

|------------|-------------------------|--------------------|

| 3.3V ± 5%  | 75 mA                   | 3.3V at 25°C       |

| 5.0V ± 10% | 100 mA                  | 5.0V at 25°C       |

#### Compact Flash interface I/O at 5.0V

| Parameter                 | Symbol | Min.    | Max. | Unit | Remark              |

|---------------------------|--------|---------|------|------|---------------------|

| Supply Voltage            | VCC    | 4.5     | 5.5  | V    |                     |

| High level output voltage | VOH    | VCC-0.8 |      | V    |                     |

| Low level output voltage  | VOL    |         | 0.8  | V    |                     |

| High level input voltage  | VIH    | 4       |      | V    | Non-schmitt trigger |

|                           |        | 2.92    |      | V    | Schmitt trigge      |

| Low level input voltage   | VIL    |         | 0.8  | V    | Non-schmitt trigger |

|                           |        |         | 1.70 | V    | Schmitt trigge      |

#### Compact Flash interface I/O at 3.3V

| Parameter                 | Symbol | Min.    | Max. | Unit | Remark              |

|---------------------------|--------|---------|------|------|---------------------|

| Supply Voltage            | VCC    | 2.97    | 3.63 | V    |                     |

| High level output voltage | VOH    | VCC-0.8 |      | V    |                     |

| Low level output voltage  | VOL    |         | 0.8  | V    |                     |

| High level input voltage  | VIH    | 2.4     |      | V    | Non-schmitt trigger |

|                           |        | 2.05    |      | V    | Schmitt trigge      |

| Low level input voltage   | VIL    |         | 0.6  | V    | Non-schmitt trigger |

|                           |        |         | 1.25 | V    | Schmitt trigge      |

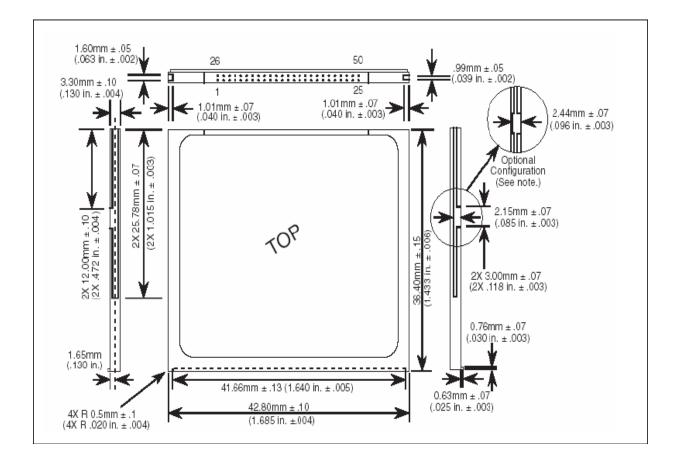

## **4.0 PHYSICAL DIMENSIONS**

PHYSICAL MECHANICAL OUTLINE:

| Length:                | 36.40 +/- 0.15mm (1.433+/- 0.06 in.) |  |  |  |  |

|------------------------|--------------------------------------|--|--|--|--|

| Width:                 | 42.80 +/- 0.10mm (1.685+/- 0.04 in.) |  |  |  |  |

| Thickness:             | 2.0 mm $(0.400 + 0.04$ mm            |  |  |  |  |

| (Including Label Area) | 3.3mm+/-0.10mm (0.130+/-0.04in.)     |  |  |  |  |

## **REVISION HISTORY**

| Revision | Date       | History         | Remark |

|----------|------------|-----------------|--------|

| 1.0      | 08/07/2007 | Fist release    |        |

| 1.1      | 05/11/2009 | Capacity update |        |

| 1.2      | 10/19/2010 | Format revised  |        |

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

«JONHON» (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«FORSTAR» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный) Факс: 8 (812) 320-03-32 Электронная почта: ocean@oceanchips.ru Web: http://oceanchips.ru/ Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А