## Automotive door actuator driver with embedded LIN

#### Datasheet - production data

#### **Features**

- AEC-Q100 qualified

- 1 half bridge for 7.5 A load (R<sub>ON</sub> = 100 mΩ)

- 1 half bridge for 7.5 A load (R<sub>ON</sub> = 150 mΩ)

- 2 half bridges for 3 A load (R<sub>ON</sub> = 300 mΩ)

- 1 configurable high-side driver for up to 1.5 A (R<sub>ON</sub> = 500 mΩ) or 0.35 A (R<sub>ON</sub> = 1600 mΩ) load

- 1 configurable high-side driver for 0.8 A (R<sub>ON</sub> = 800 mΩ) or 0.35 A (R<sub>ON</sub> = 1600 mΩ) load

- 3 configurable high-side drivers for 0.15 A/0.35 A (R<sub>ON</sub> =2 Ω)

- 1 configurable high-side driver for 0.25 A/0.5 A (R<sub>ON</sub> = 2 Ω)

- 4 configurable high-side drivers for 0.15 A/0.25 A (R<sub>ON</sub> = 5 Ω)

- Internal 10bit PWM timer for each stand-alone high-side driver

- Buffered supply for voltage regulators and 2 high-side drivers (OUT15 & OUT\_HS / both P-channel) to supply e.g. external contacts

- Programmable soft-start function to drive loads with higher inrush currents as current limitation value (for OUT1-6, OUT7, OUT8 and OUT\_HS) with thermal expiration feature

- All the embedded outputs come with protection and supervision features:

- Current Monitor (high-side only)

- Open-load

- Overcurrent

- Thermal warning

- Thermal shutdown

- Fully protected driver for external MOSFETs in H-bridge configuration

- Two 5 V voltage regulators for microcontroller and peripheral supply

- Programmable reset generator for power-on and undervoltage

- Configurable window watchdog

- LIN 2.2a compliant (SAEJ2602 compatible) transceiver

- Separated (Isolated) fail-safe block with 2 LS (R<sub>ON</sub> = 1 Ω) to pull down the gates of the external HS MOSFETs

- Thermal clusters

- A/D conversion of supply voltages and internal temperature sensors

- Embedded and programmable VS duty cycle adjustment for LED driver outputs

# **Applications**

Door zone applications.

Contents L99DZ120

# **Contents**

| 1 | Desc | ription   |                                                         | 12 |

|---|------|-----------|---------------------------------------------------------|----|

| 2 | Bloc | k diagra  | am and pin descriptions                                 | 13 |

| 3 | Elec | trical sp | pecifications                                           | 18 |

|   | 3.1  | Absolu    | ute maximum ratings                                     | 18 |

|   | 3.2  | ESD p     | rotection                                               | 20 |

|   | 3.3  | Therm     | al data                                                 | 20 |

|   |      | 3.3.1     | LQFP64 thermal data                                     |    |

|   | 3.4  | Electric  | cal characteristics                                     | 25 |

|   |      | 3.4.1     | Supply and supply monitoring                            |    |

|   |      | 3.4.2     | Oscillator                                              |    |

|   |      | 3.4.3     | Power-on reset (VSREG)                                  | 26 |

|   |      | 3.4.4     | Voltage regulator V1                                    | 27 |

|   |      | 3.4.5     | Voltage regulator V2                                    | 29 |

|   |      | 3.4.6     | Reset output                                            | 29 |

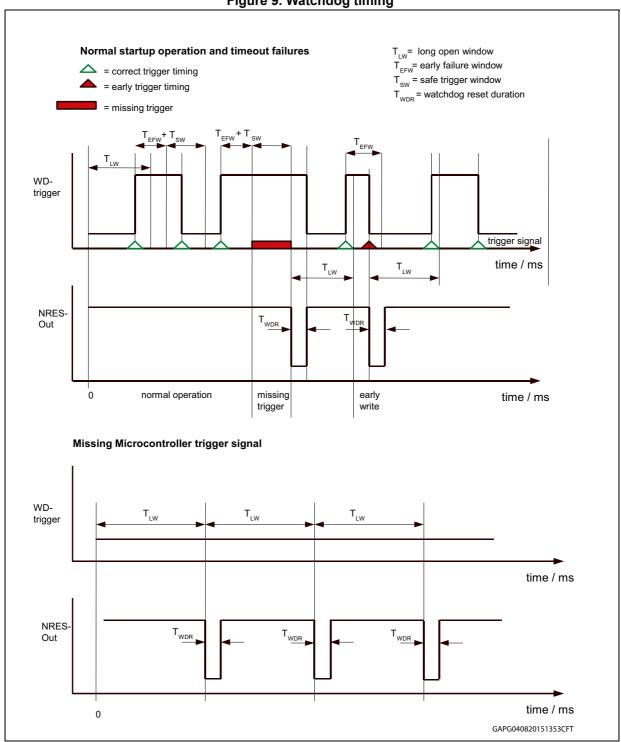

|   |      | 3.4.7     | Watchdog timing                                         | 31 |

|   |      | 3.4.8     | Current monitor output (CM)                             | 33 |

|   |      | 3.4.9     | Charge pump                                             | 34 |

|   |      | 3.4.10    | Outputs OUT1 - OUT15, OUT_HS                            | 35 |

|   |      | 3.4.11    | Power outputs switching times                           | 37 |

|   |      | 3.4.12    | Over Current Recovery settings                          | 38 |

|   |      | 3.4.13    | Current monitoring                                      | 39 |

|   |      | 3.4.14    | H-bridge driver                                         | 41 |

|   |      | 3.4.15    | Gate drivers for the external Power-MOS switching times | 42 |

|   |      | 3.4.16    | Drain source monitoring external H-bridge               | 45 |

|   |      | 3.4.17    | Open-load monitoring external H-bridge                  | 45 |

|   |      | 3.4.18    | Fail safe low-side switch                               | 46 |

|   |      | 3.4.19    | Wake up input WU                                        |    |

|   |      | 3.4.20    | LIN transceiver                                         | 47 |

|   |      | 3.4.21    | SPI                                                     |    |

|   |      | 3.4.22    | Input LIN_FLASH for Flash mode                          |    |

|   |      | 3.4.23    | Inputs DIR, DIRH, PWMH                                  |    |

|   |      | 3.4.24    | Debug input                                             | 53 |

|   |       | 3.4.25   | ADC characteristics                                 | 53 |

|---|-------|----------|-----------------------------------------------------|----|

|   |       | 3.4.26   | Temperature diode characteristics                   | 54 |

|   |       | 3.4.27   | Interrupt outputs                                   | 54 |

|   |       | 3.4.28   | Timer1 and Timer2                                   | 55 |

|   |       | 3.4.29   | SGND loss comparator                                | 58 |

| 4 | Appli | ication  | information                                         | 59 |

|   | 4.1   | Supply   | V <sub>S</sub> , V <sub>SREG</sub>                  | 59 |

|   | 4.2   |          | e regulators                                        |    |

|   |       | 4.2.1    | Voltage regulator: V1                               | 59 |

|   |       | 4.2.2    | Voltage regulator: V2                               | 59 |

|   |       | 4.2.3    | Voltage regulator failure                           | 60 |

|   |       | 4.2.4    | Short to ground detection                           | 60 |

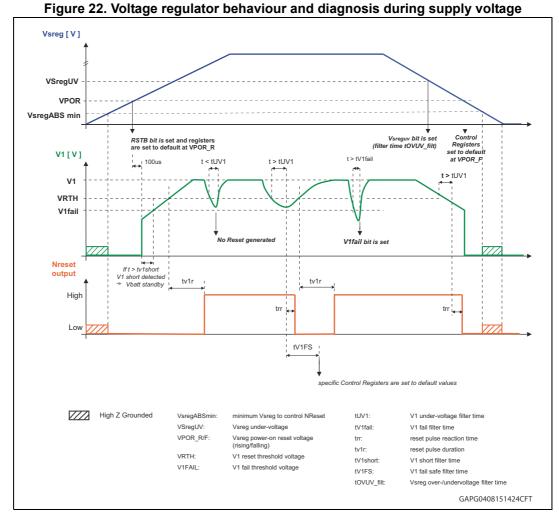

|   |       | 4.2.5    | Voltage regulator behavior                          | 61 |

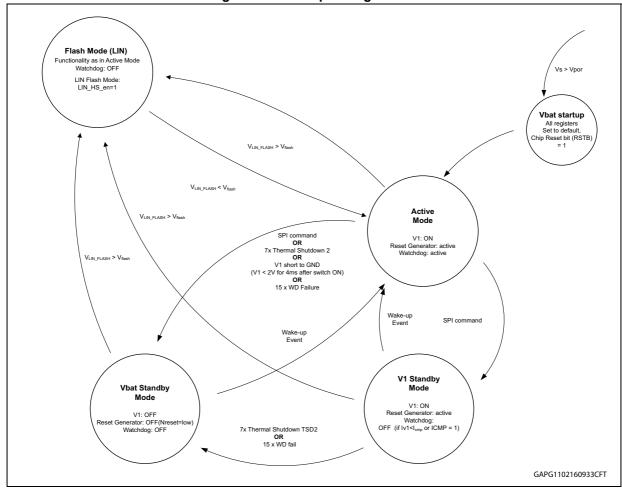

|   | 4.3   | Operat   | ing modes                                           | 61 |

|   |       | 4.3.1    | Active mode                                         | 61 |

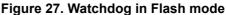

|   |       | 4.3.2    | Flash mode                                          | 62 |

|   |       | 4.3.3    | SW-debug mode                                       | 62 |

|   |       | 4.3.4    | V1_standby mode                                     | 62 |

|   |       | 4.3.5    | Interrupt                                           | 63 |

|   |       | 4.3.6    | VBAT_standby mode                                   | 63 |

|   | 4.4   | Wake-ı   | up from Standby modes                               | 63 |

|   |       | 4.4.1    | Wake up input                                       | 64 |

|   | 4.5   | Functio  | onal overview (truth table)                         | 64 |

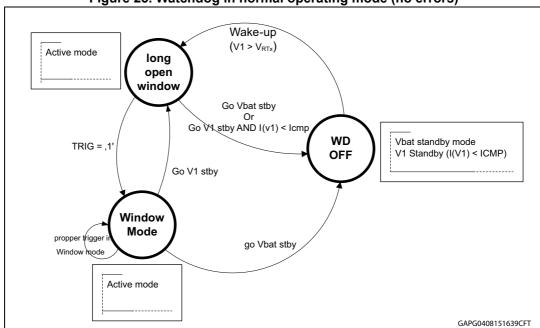

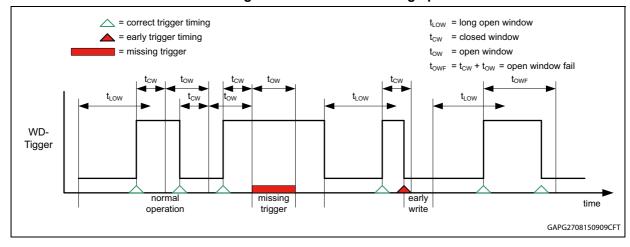

|   | 4.6   | Configu  | urable window watchdog                              | 66 |

|   |       | 4.6.1    | Change watchdog timing                              | 69 |

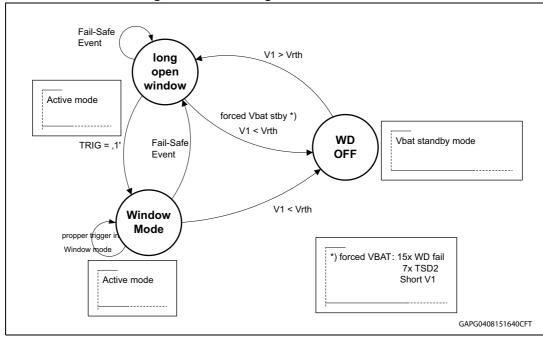

|   | 4.7   |          | fe mode                                             |    |

|   |       | 4.7.1    | Temporary failures                                  |    |

|   |       | 4.7.2    | Non-recoverable failures – forced Vbat_standby mode |    |

|   | 4.8   |          | output (NReset)                                     |    |

|   | 4.9   |          | s Interface                                         |    |

|   | 4.5   | 4.9.1    | Features                                            |    |

|   |       | 4.9.2    | Error handling                                      |    |

|   |       | 4.9.3    | Wake up from Standby modes                          |    |

|   |       | 4.9.4    | Receive-only mode                                   |    |

|   | 4.10  |          | Peripheral Interface (ST SPI Standard)              |    |

|   | 4.10  | ociiai f | enpheral interiace (31 3F1 Standard)                | /4 |

|   | 4.11        | Power supply failure                                                       | 75 |

|---|-------------|----------------------------------------------------------------------------|----|

|   |             | 4.11.1 V <sub>S</sub> supply failure                                       | 75 |

|   |             | 4.11.2 V <sub>SREG</sub> supply failure                                    | 76 |

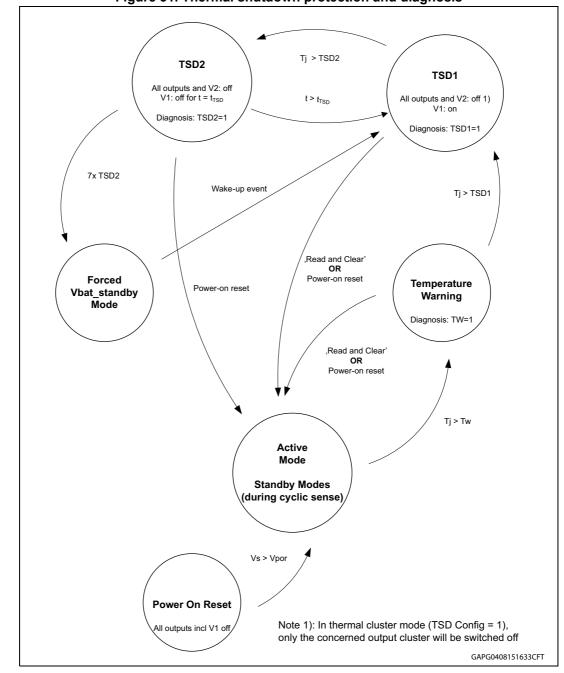

|   | 4.12        | Temperature warning and thermal shutdown                                   | 77 |

|   | 4.13        | Power outputs OUT115 and OUT_HS                                            | 78 |

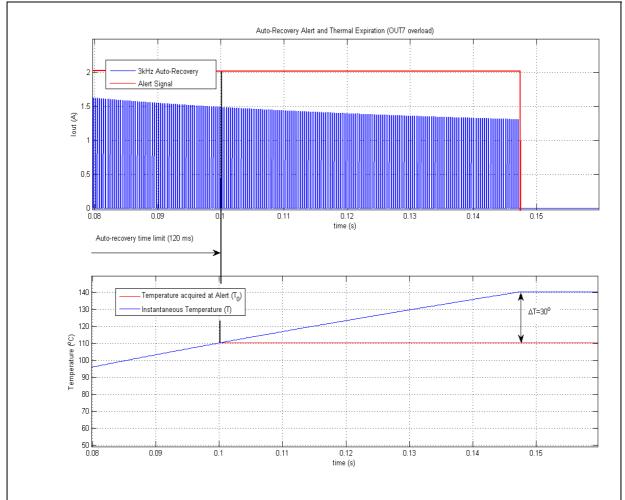

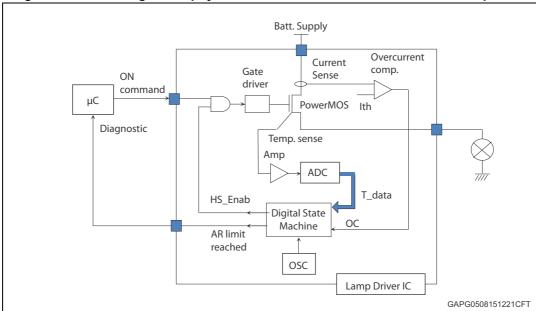

|   | 4.14        | Auto-recovery alert and thermal expiration                                 | 79 |

|   | 4.15        | Charge pump                                                                | 81 |

|   | 4.16        | Inductive loads                                                            | 81 |

|   | 4.17        | Open-load detection                                                        | 82 |

|   | 4.18        | Overcurrent detection                                                      | 82 |

|   | 4.19        | Current monitor                                                            | 82 |

|   | 4.20        | PWM mode of the power outputs                                              | 82 |

|   | 4.21        | Cross-current protection                                                   | 82 |

|   | 4.22        | Programmable soft-start function to drive loads with higher inrush current |    |

|   |             |                                                                            |    |

|   | 4.23        | H-bridge control                                                           |    |

|   | 4.24        | H-bridge driver slew-rate control                                          |    |

|   | 4.25        | Resistive low                                                              |    |

|   | 4.26        | Short circuit detection / drain source monitoring                          |    |

|   | 4.27        | H-bridge monitoring in off-mode                                            |    |

|   | 4.28        | Programmable cross current protection                                      |    |

|   | 4.29        | Power window H-bridge safety switch off block                              |    |

|   | 4.30        | Temperature warning and shutdown                                           |    |

|   | 4.31        | Thermal clusters                                                           |    |

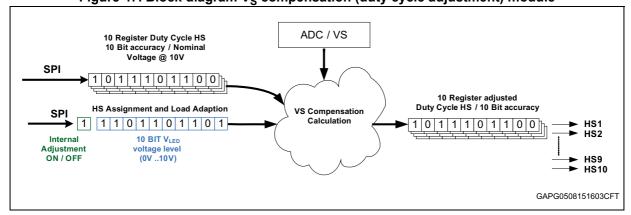

|   | 4.32        | V <sub>S</sub> compensation (duty cycle adjustment) module                 | 95 |

|   | 4.33        | Analog digital converter                                                   | 96 |

| 5 | Sorial      | I Peripheral Interface (SPI)                                               | 97 |

| • | 5.1         | ST SPI 4.0                                                                 |    |

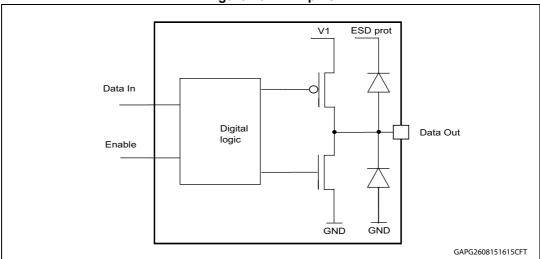

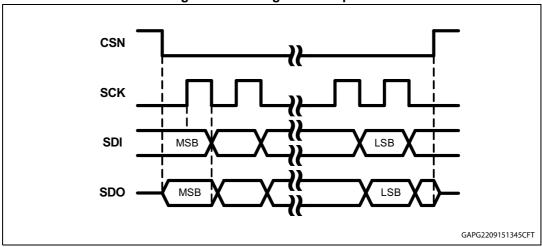

|   | J. 1        | 5.1.1 Physical layer                                                       |    |

|   | 5.2         | Signal description                                                         |    |

|   | ~· <b>-</b> | 5.2.1 Clock and Data Characteristics                                       |    |

|   |             | 5.2.2 Communication protocol                                               |    |

|   |             | 5.2.3 Address definition                                                   | 03 |

|   |             |                                                                            |    |

|   |      | 5.2.4     | Protocol failure detection                  | 09 |

|---|------|-----------|---------------------------------------------|----|

| 6 | Appl | lication  |                                             | 11 |

| 7 | SPII | Register  | rs                                          | 12 |

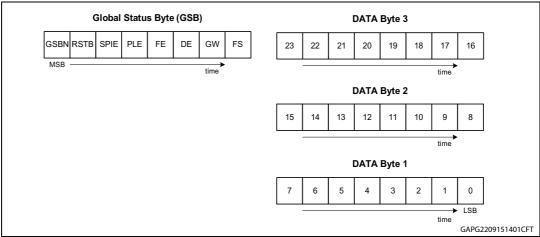

|   | 7.1  | Global    | Status Byte GSB1                            | 12 |

|   | 7.2  | Contro    | l register overview1                        | 15 |

|   | 7.3  | Status    | register overview                           | 19 |

|   | 7.4  | Contro    | I registers                                 | 21 |

|   |      | 7.4.1     | Control Register CR1 (0x01)                 |    |

|   |      | 7.4.2     | Control Register CR2 (0x02)                 |    |

|   |      | 7.4.3     | Control Register CR3 (0x03)                 |    |

|   |      | 7.4.4     | Control Register CR4 (0x04)                 | 28 |

|   |      | 7.4.5     | Control Register CR5 (0x05)                 | 29 |

|   |      | 7.4.6     | Control Register CR6 (0x06)                 | 31 |

|   |      | 7.4.7     | Control Register CR7 (0x07)                 | 32 |

|   |      | 7.4.8     | Control Register CR8 (0x08)                 | 34 |

|   |      | 7.4.9     | Control Register CR9 (0x09)                 | 35 |

|   |      | 7.4.10    | Control Register CR10 (0x0A)                | 36 |

|   |      | 7.4.11    | Control Register CR11 (0x0B)                | 37 |

|   |      | 7.4.12    | Control Register CR12 (0x0C)                | 37 |

|   |      | 7.4.13    | Control Register CR13 (0x0D) to CR17 (0x11) | 39 |

|   |      | 7.4.14    | Control Register CR18 (0x12) to CR22 (0x16) | 40 |

|   |      | 7.4.15    | Control Register CR34 (0x22)                | 42 |

|   |      | 7.4.16    | Configuration Register (0x3F)               | 42 |

|   | 7.5  | Status    | Registers                                   | 45 |

|   |      | 7.5.1     | Status Register SR1 (0x31)                  | 45 |

|   |      | 7.5.2     | Status Register SR2 (0x32)                  | 47 |

|   |      | 7.5.3     | Status Register SR3 (0x33)                  | 49 |

|   |      | 7.5.4     | Status Register SR4 (0x34)                  | 50 |

|   |      | 7.5.5     | Status Register SR5 (0x35)                  | 51 |

|   |      | 7.5.6     | Status Register SR6 (0x36)                  | 52 |

|   |      | 7.5.7     | Status Register SR7 (0x37) to SR9 (0x39)    | 53 |

|   |      | 7.5.8     | Status Register SR10 (0x3A)                 | 54 |

|   |      | 7.5.9     | Status Register SR11 (0x3B)                 | 55 |

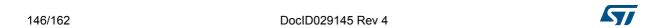

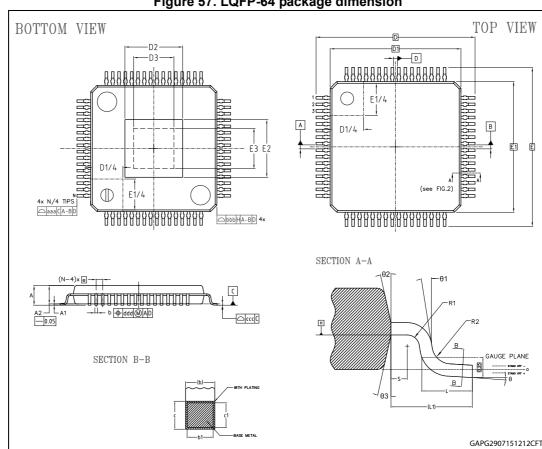

| 8 | Pack | cage info | ormation                                    | 57 |

| Contents | L99DZ1 |                             |     |

|----------|--------|-----------------------------|-----|

|          | 8.1    | LQFP-64 package information | 157 |

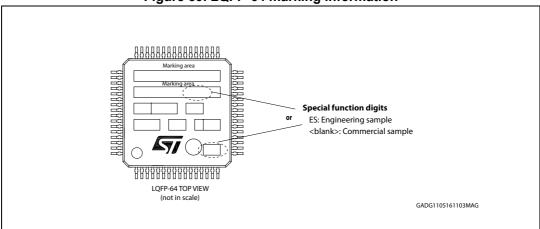

|          | 8.2    | LQFP-64 marking information | 159 |

| 9        | Orde   | er code                     | 160 |

| 10       | Revi   | ision history               | 161 |

L99DZ120 List of tables

# List of tables

| Table 1.   | Pin definitions and functions                                  | 13 |

|------------|----------------------------------------------------------------|----|

| Table 2.   | Absolute maximum ratings                                       | 18 |

| Table 3.   | ESD protection                                                 | 20 |

| Table 4.   | Operating junction temperature                                 | 20 |

| Table 5.   | Temperature warning and thermal shutdown                       | 21 |

| Table 6.   | Supply and supply monitoring                                   |    |

| Table 7.   | Oscillator                                                     |    |

| Table 8.   | Power-on reset (V <sub>SREG</sub> )                            |    |

| Table 9.   | Voltage regulator V1                                           |    |

| Table 10.  | Voltage regulator V2                                           |    |

| Table 11.  | Reset output                                                   |    |

| Table 12.  | Watchdog timing                                                |    |

| Table 13.  | Current monitor output (CM)                                    |    |

| Table 14.  | Charge pump electrical characteristics                         |    |

| Table 15.  | Outputs OUT1 - OUT15, OUT_HS                                   |    |

| Table 16.  | Power outputs switching times                                  |    |

| Table 10.  | Half bridges (OUT1, OUT4, OUT5 and OUT6) OCR timing parameters |    |

| Table 17.  |                                                                |    |

| Table 16.  | High-side (OUT7, OUT8 and OUT_HS) OCR timing parameters        |    |

|            | Current monitoring                                             |    |

| Table 20.  | H-bridge driver                                                |    |

| Table 21.  | Gate drivers for the external Power-MOS switching times        |    |

| Table 22.  | Drain source monitoring external H-bridge                      |    |

| Table 23.  | Open-load monitoring external H-bridge                         |    |

| Table 24.  | Fail safe low-side switch                                      |    |

| Table 25.  | Wake-up inputs                                                 |    |

| Table 26.  | LIN transmit data input: pin TxD                               |    |

| Table 27.  | LIN receive data output: pin RxD                               |    |

| Table 28.  | LIN transmitter and receiver: pin LIN                          |    |

| Table 29.  | LIN transceiver timing                                         |    |

| Table 30.  | Input: CSN                                                     |    |

| Table 31.  | Inputs: CLK, DI                                                | 50 |

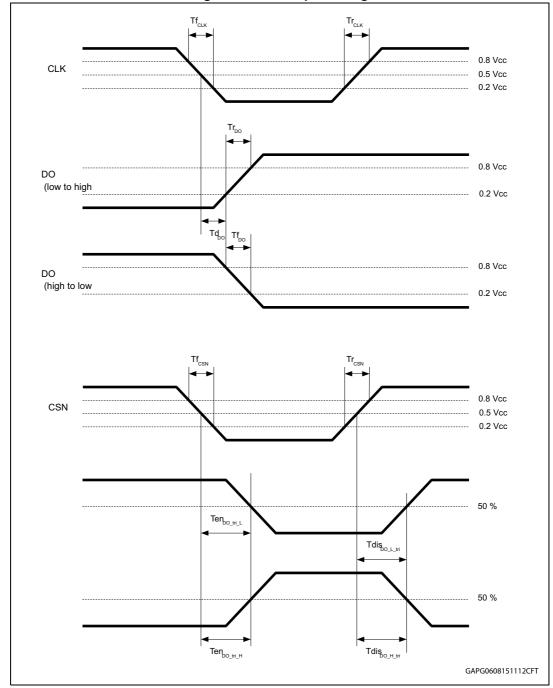

| Table 32.  | DI, CLK and CSN timing                                         | 51 |

| Table 33.  | Output: DO                                                     | 51 |

| Table 34.  | DO timing                                                      | 52 |

| Table 35.  | CSN timing                                                     | 52 |

| Table 36.  | Inputs LIN_FLASH for Flash mode                                | 52 |

| Table 37.  | Inputs DIR, DIRH, PWMH                                         | 53 |

| Table 38.  | Debug input                                                    | 53 |

| Table 39.  | ADC characteristics                                            | 53 |

| Table 40.  | Temperature diode characteristics                              | 54 |

| Table 41.  | Interrupt outputs                                              |    |

| Table 42.  | Timer1 and Timer2                                              |    |

| Table 43.  | SGND loss comparator                                           |    |

| Table 44.  | Wake-up events description                                     |    |

| Table 45.  | Status of different functions/features vs operating modes      |    |

| Table 46.  | Temporary failures description                                 |    |

| Table 47.  | Non-recoverable failure                                        |    |

| Table 48.  | Power output settings                                          |    |

| . 22.5 10. |                                                                |    |

| Table 49.              | H-bridge control truth table        |     |

|------------------------|-------------------------------------|-----|

| Table 50.              | H-bridge monitoring in off-mode     |     |

| Table 51.              | Thermal cluster definition          |     |

| Table 52.              | Operation codes                     |     |

| Table 53.              | Global Status Byte                  |     |

| Table 54.              | Device application access           |     |

| Table 55.              | Device information read access      |     |

| Table 56.              | RAM address range                   |     |

| Table 57.              | ROM address range                   |     |

| Table 58.              | Information Registers Map           |     |

| Table 59.              | SPI Mode Register                   |     |

| Table 60.              | Burst Read Bit.                     |     |

| Table 61.              | SPI Data Length                     |     |

| Table 62.              | Data Consistency Check              |     |

| Table 63.              | WD Type/Timing                      |     |

| Table 64.              | WD bit position                     |     |

| Table 65.              | Global Status Byte (GSB)            |     |

| Table 66.              | GSB signals description             |     |

| Table 67.              | Control register overview           |     |

| Table 68.              | Status register overview            |     |

| Table 69.              | Control Register CR1                |     |

| Table 70.              | CR1 signals description             |     |

| Table 71.              | Wake-up input1 filter configuration |     |

| Table 72.              | Voltage regulator V2 configuration  |     |

| Table 73.              | Standby transition configuration    |     |

| Table 74.              | Control Register CR2                |     |

| Table 75.              | CR2 signals description             |     |

| Table 76.              | Configuration of Timer x on-time    |     |

| Table 77.              | Control Register CR3                |     |

| Table 78.              | CR3 signals description             |     |

| Table 79.              | Control Register CR4                |     |

| Table 80.              | CR4 signals description             |     |

| Table 81.              | Control Register CR5                |     |

| Table 82.              | CR5 signals description             |     |

| Table 83.              | OUTx Configuration bits             |     |

| Table 84.              | Control Register CR6                |     |

| Table 85.              | CR6 signals description             |     |

| Table 86.              | Control Register CR7                |     |

| Table 87.              | CR7 signals description             |     |

| Table 88.              | Control Register CR8                |     |

| Table 89.              | CR8 signals description             |     |

| Table 90.              | Control Register CR9                |     |

| Table 91.              | CR9 signals description             |     |

| Table 92.              | Control Register CR10               |     |

| Table 93.              | CR10 signals description            |     |

| Table 94.<br>Table 95. | Control Register CR11               |     |

| Table 95.              | CR11 signals description            |     |

| Table 96.              | Control Register CR12               |     |

| Table 97.              | CR12 signals description            |     |

| Table 98.              | Control Register CR13 to CR17       |     |

| Table 99.              | Control Register CR18               |     |

| TADIC IUU.             | Outilial Dedigici OI/10             | 140 |

L99DZ120 List of tables

| Table 101. | CR18 to CR22 signals description         | 141 |

|------------|------------------------------------------|-----|

| Table 102. | Control Register CR34                    | 142 |

| Table 103. | CR34 signals description                 | 142 |

| Table 104. | Configuration Register                   | 142 |

| Table 105. | CR signals description                   | 143 |

| Table 106. | Status Register SR1 (0x31)               | 145 |

| Table 107. | SR1 signals description                  | 145 |

| Table 108. | Status Register SR2 (0x32)               | 147 |

| Table 109. | SR2 signals description                  | 147 |

| Table 110. | Status Register SR3 (0x33)               | 149 |

| Table 111. | SR3 signals description                  | 149 |

| Table 112. | Status Register SR4 (0x34)               | 150 |

| Table 113. | SR4 signals description                  | 151 |

| Table 114. | Status Register SR5 (0x35)               | 151 |

| Table 115. | SR5 signals description                  | 151 |

| Table 116. | Status Register SR6 (0x36)               | 152 |

| Table 117. | SR6 signals description                  | 152 |

| Table 118. | Status Register SR7 (0x37) to SR9 (0x39) | 153 |

| Table 119. | SR7 to SR9 signals description           | 153 |

| Table 120. | Status Register SR10 (0x3A)              | 154 |

| Table 121. | SR10 signals description                 | 154 |

| Table 122. | Status Register SR11 (0x3B)              | 155 |

| Table 123. | SR11 signals description                 | 155 |

| Table 124. | LQFP-64 mechanical data                  | 157 |

| Table 125. | Device summary                           | 160 |

| Table 126  | Document revision history                | 161 |

List of figures L99DZ120

# **List of figures**

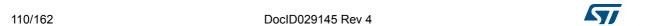

| Figure 1.                | Block diagram                                                                                     | 13 |

|--------------------------|---------------------------------------------------------------------------------------------------|----|

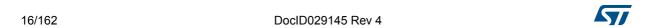

| Figure 2.                | Pin connection (top view)                                                                         | 17 |

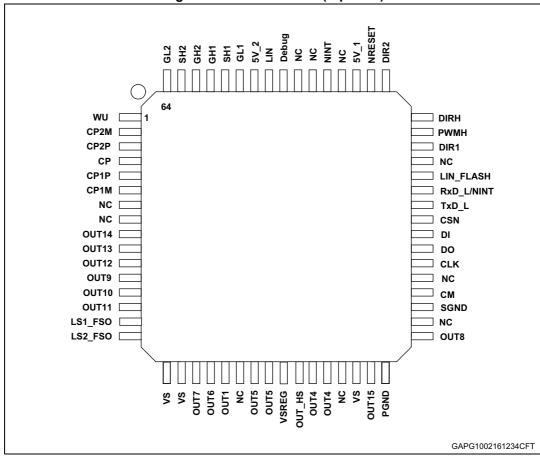

| Figure 3.                | Activation profile 1                                                                              |    |

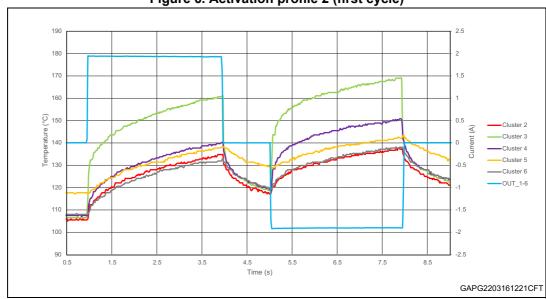

| Figure 4.                | Activation profile 1 (first cycle)                                                                |    |

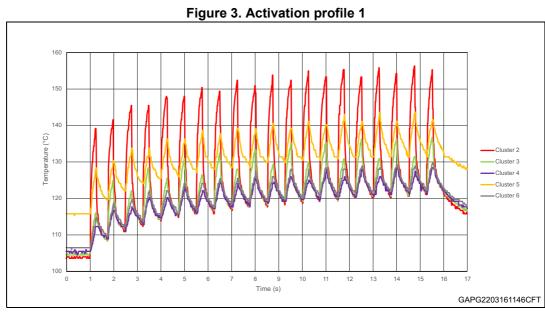

| Figure 5.                | Activation profile 2                                                                              | 23 |

| Figure 6.                | Activation profile 2 (first cycle)                                                                | 24 |

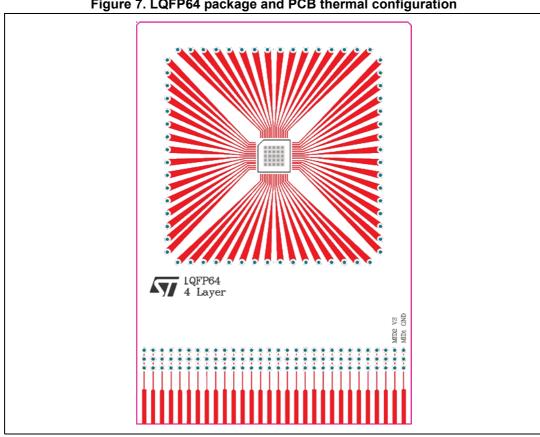

| Figure 7.                | LQFP64 package and PCB thermal configuration                                                      |    |

| Figure 8.                | Voltage regulator V1 characteristics (quiescent current and accuracy)                             | 28 |

| Figure 9.                | Watchdog timing                                                                                   | 32 |

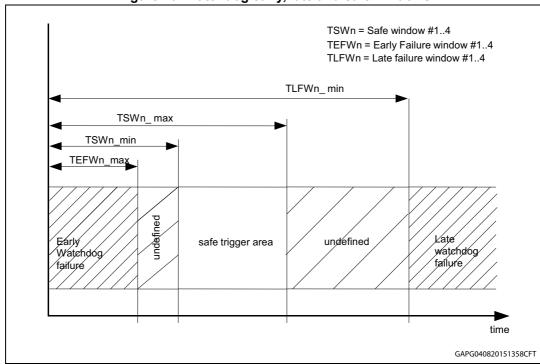

| Figure 10.               | Watchdog early, late and safe windows                                                             | 33 |

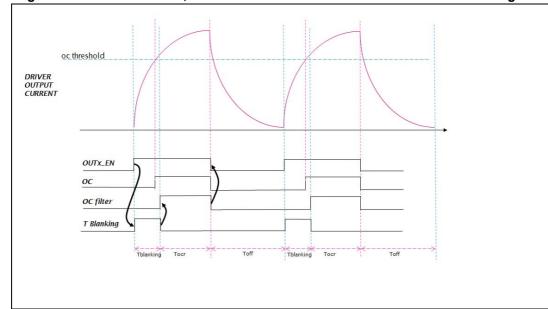

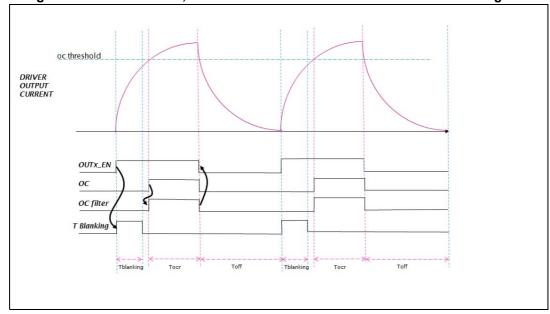

| Figure 11.               | Hard Short case, the OC threshold is reached before end of blanking time                          | 39 |

| Figure 12.               | Overload case, the OC threshold is reached after end of blanking time                             | 39 |

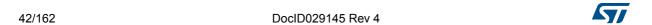

| Figure 13.               | H-driver delay times                                                                              |    |

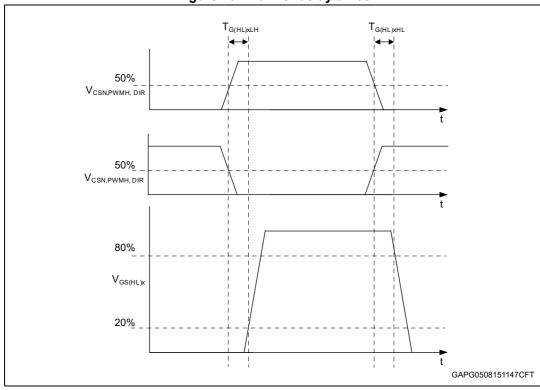

| Figure 14.               | IGHxr ranges                                                                                      |    |

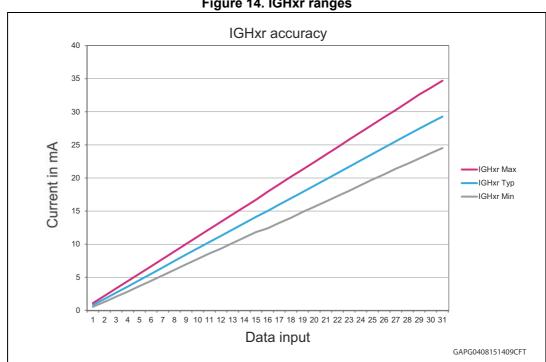

| Figure 15.               | IGHxf ranges                                                                                      |    |

| Figure 16.               | LIN transmit, receive timing                                                                      |    |

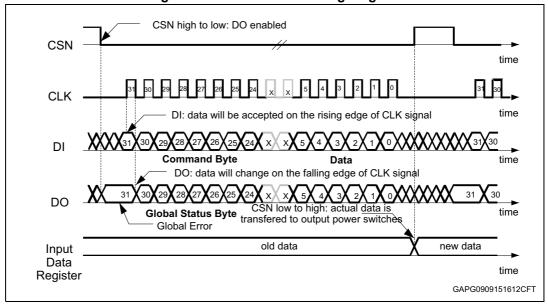

| Figure 17.               | SPI – transfer timing diagram                                                                     |    |

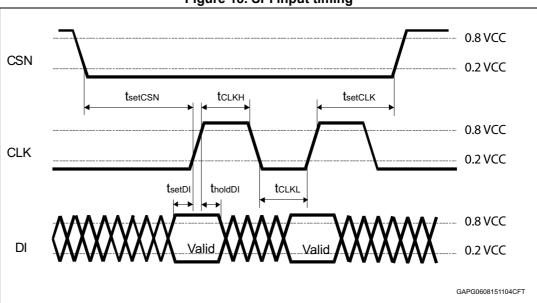

| Figure 18.               | SPI input timing                                                                                  |    |

| Figure 19.               | SPI output timing                                                                                 |    |

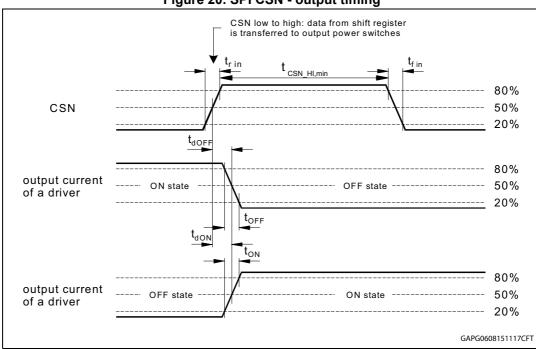

| Figure 20.               | SPI CSN - output timing                                                                           |    |

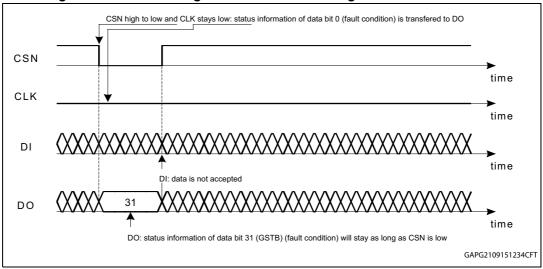

| Figure 21.               | SPI – CSN high to low transition and global status bit access                                     |    |

| Figure 22.               | Voltage regulator behaviour and diagnosis during supply voltage                                   |    |

| Figure 23.               | NINT pins                                                                                         |    |

| Figure 24.               | Main operating modes                                                                              |    |

| Figure 25.               | Watchdog in normal operating mode (no errors)                                                     |    |

| Figure 26.               | Watchdog with error conditions                                                                    |    |

| Figure 27.               | Watchdog in Flash mode                                                                            |    |

| Figure 28.               | NReset pin                                                                                        |    |

| Figure 29.               | RxDL pin                                                                                          |    |

| Figure 30.               | Wake-up behavior according to LIN 2.2a                                                            |    |

| Figure 31.               | Thermal shutdown protection and diagnosis                                                         |    |

| Figure 32.               | Example of long auto-recovery on OUT7. Temperature acquisition starts after t <sub>AR</sub> , the |    |

| riguic 52.               | expiration occurs after a $\Delta T = 30^{\circ}$                                                 |    |

| Figure 33.               | Block diagram of physical realization of AR alert and thermal expiration                          |    |

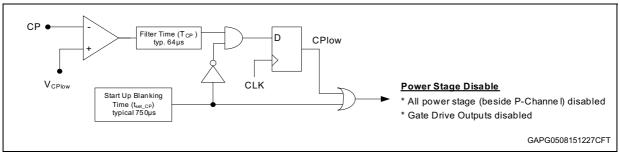

| Figure 34.               | Charge pump low filtering and start up implementation                                             |    |

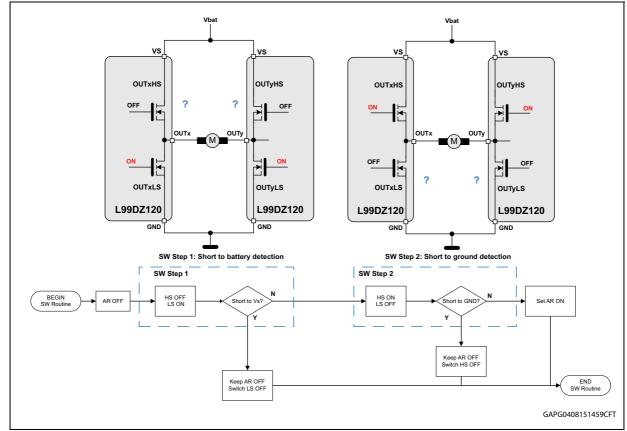

| Figure 35.               | Software strategy for half bridges before applying auto-recovery mode                             |    |

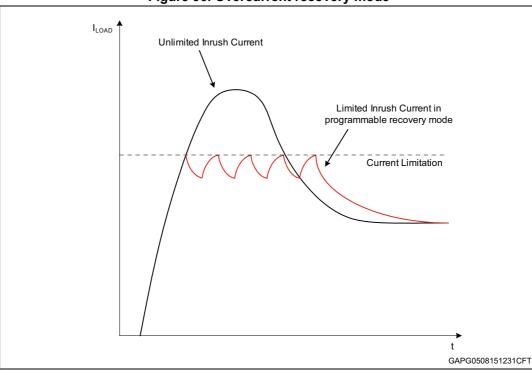

| Figure 36.               | Overcurrent recovery mode                                                                         |    |

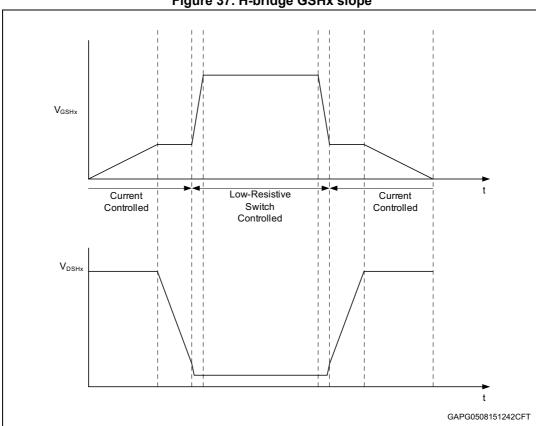

|                          | H-bridge GSHx slope                                                                               |    |

| Figure 37.<br>Figure 38. | H-bridge diagnosis                                                                                |    |

| Figure 30.               | H-bridge open-load-detection (no open-load detected)                                              |    |

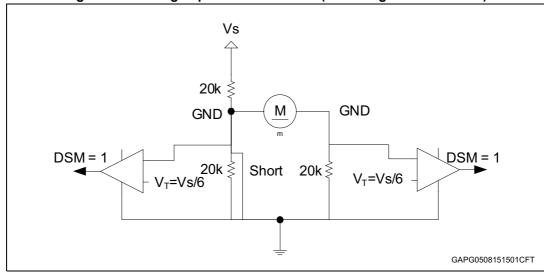

| •                        | H-bridge open-load-detection (open-load detected)                                                 |    |

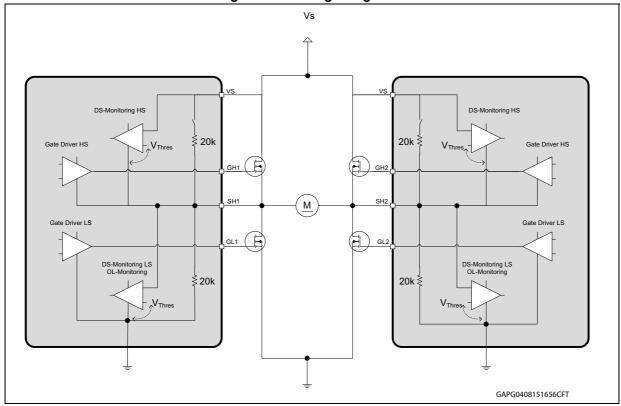

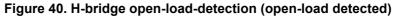

| Figure 40.               |                                                                                                   |    |

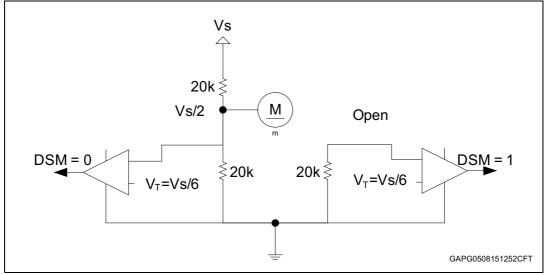

| Figure 41.<br>Figure 42. | H-bridge open-load-detection (short to ground detected)                                           |    |

| •                        | H-bridge open-load detection (short to V <sub>S</sub> detected)                                   |    |

| Figure 43.               | PWMH cross current protection time implementation.                                                |    |

| Figure 44.               | LSx_FSO: low-side driver "passively" turned on, taking supply from output pin (if main            |    |

| Figure 45                | fails), can guarantee V <sub>LSx_FSO</sub> < V <sub>OUT_max</sub>                                 |    |

| Figure 45.               | Safety concept                                                                                    |    |

| Figure 46.               | Thermal clusters identification                                                                   | 94 |

L99DZ120 List of figures

| Figure 47. | Block diagram V <sub>S</sub> compensation (duty cycle adjustment) module           | 05    |

|------------|------------------------------------------------------------------------------------|-------|

|            |                                                                                    |       |

| Figure 48. | Sequential ADC Read Out for V <sub>SREG</sub> , V <sub>S</sub> , WU and THCL1THCL6 | 96    |

| Figure 49. | SPI pin description                                                                | 98    |

| Figure 50. | SDO pin                                                                            | 99    |

| Figure 51. | SPI signal description                                                             | 99    |

|            | SDI Frame                                                                          |       |

| Figure 53. | SDO frame                                                                          | . 102 |

| Figure 54. | Window watchdog operation                                                          | . 108 |

| Figure 55. | Typical application diagram                                                        |       |

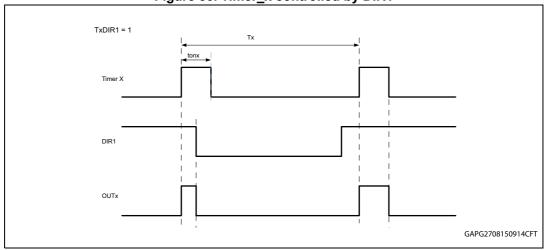

|            | Timer_x controlled by DIR1                                                         |       |

|            | LQFP-64 package dimension                                                          |       |

|            | LQFP-64 footprint                                                                  |       |

|            | LQFP-64 marking information                                                        |       |

Description L99DZ120

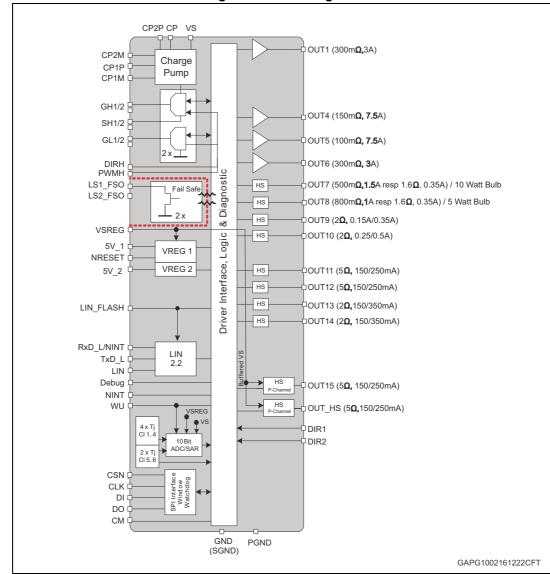

# 1 Description

The L99DZ120 is a door zone systems IC providing electronic control modules with enhanced power management power supply functionality, including various standby modes, as well as LIN physical communication layers.

The two low-drop voltage regulators of the devices supply the system microcontroller and external peripheral loads such as sensors and provide enhanced system standby functionality with programmable local and remote wake-up capability. In addition 8 high-side drivers to supply LEDs, 2 high-side drivers to supply bulbs increase the system integration level.

Up to 3 DC motors and 4 external MOS transistors in H-bridge configuration can be driven. All outputs are SC protected and implement an open-load diagnosis.

The ST standard SPI interface (4.0) allows control and diagnosis of the device and enables generic software development.

# 2 Block diagram and pin descriptions

Figure 1. Block diagram

Table 1. Pin definitions and functions

| Pin | Symbol | Function                                                                      |

|-----|--------|-------------------------------------------------------------------------------|

| 1   | WU     | Wake-up Input: Input pin for static or cyclic monitoring of external contacts |

| 2   | CP2M   | Charge pump pin for capacitor 2, negative side                                |

| 3   | CP2P   | Charge pump pin for capacitor 2, positive side                                |

| 4   | СР     | Charge pump output                                                            |

| 5   | CP1P   | Charge pump pin for capacitor 1, positive side                                |

| 6   | CP1M   | Charge pump pin for capacitor 1, negative side                                |

Table 1. Pin definitions and functions (continued)

| Pin | Symbol        | Function                                                                                                                                                                                                                                                                                                                             |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | NC            | Not connected                                                                                                                                                                                                                                                                                                                        |

| 8   | NC            | Not connected                                                                                                                                                                                                                                                                                                                        |

| 9   | OUT14         | High-side-driver output to drive LEDs                                                                                                                                                                                                                                                                                                |

| 10  | OUT13         | High-side-driver output to drive LEDs                                                                                                                                                                                                                                                                                                |

| 11  | OUT12         | High-side-driver output to drive LEDs                                                                                                                                                                                                                                                                                                |

| 12  | OUT9          | High-side-driver output to drive LEDs                                                                                                                                                                                                                                                                                                |

| 13  | OUT10         | High-side-driver-output                                                                                                                                                                                                                                                                                                              |

| 14  | OUT11         | High-side-driver output to drive LEDs                                                                                                                                                                                                                                                                                                |

| 15  | LS1_FSO       | Fail Safe low-side switch (Active low)                                                                                                                                                                                                                                                                                               |

| 16  | LS2_FSO       | Fail Safe low-side switch (Active low)                                                                                                                                                                                                                                                                                               |

| 17  | VS            | Power supply voltage for power stage outputs (external reverse battery protection required), for this input a ceramic capacitor as close as possible to GND is recommended. Important: For the capability of driving, the full current at the outputs all pins of VS must be connected externally!                                   |

| 18  | VS; 2nd pin   | Current capability (pin description see above)                                                                                                                                                                                                                                                                                       |

| 19  | OUT7          | High-side-driver output to drive LEDs or a 10 Watt bulb (programmable R <sub>dson</sub> )                                                                                                                                                                                                                                            |

| 20  | OUT6          | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to VS, low-side driver from GND to output)           |

| 21  | OUT1          | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to VS, low-side driver from GND to output)           |

| 22  | NC            | Not connected                                                                                                                                                                                                                                                                                                                        |

| 23  | OUT5          | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to $V_{\rm S}$ , low-side driver from GND to output) |

| 24  | OUT5; 2nd pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                       |

| 25  | $V_{SREG}$    | Power supply voltage to supply the internal voltage regulators, OUT15 and the OUT_HS (external reverse battery protection required / Diode) for this input a ceramic capacitor as close as possible to GND and an electrolytic back up capacitor is recommended.                                                                     |

| 26  | OUT_HS        | High-side-driver output to drive LEDs or to supply contacts                                                                                                                                                                                                                                                                          |

Table 1. Pin definitions and functions (continued)

| Pin | Symbol                    | Function                                                                                                                                                                                                                                                                                                                                |

|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                           |                                                                                                                                                                                                                                                                                                                                         |

| 27  | OUT4                      | Half-bridge outputs: the output is built by a high-side and a low-side switch which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: high-side driver from output to V <sub>S</sub> , low-side driver from GND to output) |

| 28  | OUT4; 2 <sup>nd</sup> pin | Current capability (pin description see above)                                                                                                                                                                                                                                                                                          |

| 29  | NC                        | Not connected                                                                                                                                                                                                                                                                                                                           |

| 30  | VS; 3rd pin               | Current capability (for the pin description see above)                                                                                                                                                                                                                                                                                  |

| 31  | OUT15                     | High-side-driver output to drive LEDs                                                                                                                                                                                                                                                                                                   |

| 32  | PGND                      | Power GND                                                                                                                                                                                                                                                                                                                               |

| 33  | OUT8                      | High-side-driver output to drive LEDs or a 5 Watt bulb (programmable $R_{dson}$ )                                                                                                                                                                                                                                                       |

| 34  | NC                        | Not connected                                                                                                                                                                                                                                                                                                                           |

| 35  | SGND                      | Signal Ground                                                                                                                                                                                                                                                                                                                           |

| 36  | СМ                        | Current monitor output: depending on the selected multiplexer bits $CM\_SEL\_x$ ( $CR$ 7) of the; Control Register this output sources an image of the instant current; through the corresponding high-side driver with a fixed ratio                                                                                                   |

| 37  | NC                        | Not connected                                                                                                                                                                                                                                                                                                                           |

| 38  | CLK                       | SPI: serial clock input                                                                                                                                                                                                                                                                                                                 |

| 39  | DO                        | SPI: serial data output (push pull output stage)                                                                                                                                                                                                                                                                                        |

| 40  | DI                        | SPI: serial data input                                                                                                                                                                                                                                                                                                                  |

| 41  | CSN                       | SPI: chip select not input                                                                                                                                                                                                                                                                                                              |

| 42  | TxD_L                     | LIN Transmit data input                                                                                                                                                                                                                                                                                                                 |

| 43  | RxD_L/NINT                | RxDL -> LIN receive data output; NINT -> indicates local/remote wake-up events (push pull output stage)                                                                                                                                                                                                                                 |

| 44  | LIN_FLASH                 | LIN Flash Mode enable (former TxD_C pin, to guarantee family compatibility)                                                                                                                                                                                                                                                             |

| 45  | NC                        | Not connected                                                                                                                                                                                                                                                                                                                           |

| 46  | DIR1                      | Direct Drive Input 1                                                                                                                                                                                                                                                                                                                    |

| 47  | PWMH                      | PWMH input: this input signal can be used to control the H-bridge Gate Drivers.                                                                                                                                                                                                                                                         |

| 48  | DIRH                      | Direction Input: this input controls the H-bridge Drivers for the external MOSFETs                                                                                                                                                                                                                                                      |

| 49  | DIR2                      | Direct Drive Input 2                                                                                                                                                                                                                                                                                                                    |

| 50  | NRESET                    | NReset output to micro controller; (reset state = LOW) (low-side switch with drain connected to the output pin and internal pull up resistance to 5V_1)                                                                                                                                                                                 |

| 51  | 5V_1                      | Voltage regulator 1 output: 5 V supply e.g. micro controller                                                                                                                                                                                                                                                                            |

| 52  | NC                        | Not connected                                                                                                                                                                                                                                                                                                                           |

Table 1. Pin definitions and functions (continued)

| Pin | Symbol | Function                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53  | NINT   | Interrupt output (low active; push-pull output stage) to indicate V <sub>SREG</sub> early warning (Active mode); indicates wake-up events from V1_standby mode |

| 54  | NC     | Not connected                                                                                                                                                  |

| 55  | NC     | Not connected                                                                                                                                                  |

| 56  | Debug  | Debug input to deactivate the window watchdog (high active)                                                                                                    |

| 57  | LIN    | LIN bus line                                                                                                                                                   |

| 58  | 5V_2   | Voltage regulator 2 output: 5 V supply for external loads (potentiometer, sensors). V2 is protected against reverse supply                                     |

| 59  | GL1    | Gate driver for PowerMOS low-side switch in half-bridge 1                                                                                                      |

| 60  | SH1    | Source of high-side switch in half-bridge 1                                                                                                                    |

| 61  | GH1    | Gate driver for PowerMOS high-side switch in half-bridge 1                                                                                                     |

| 62  | GH2    | Gate driver for PowerMOS high-side switch in half-bridge 2                                                                                                     |

| 63  | SH2    | Source of high-side switch in half-bridge 2                                                                                                                    |

| 64  | GL2    | Gate driver for PowerMOS low-side switch in half-bridge 2                                                                                                      |

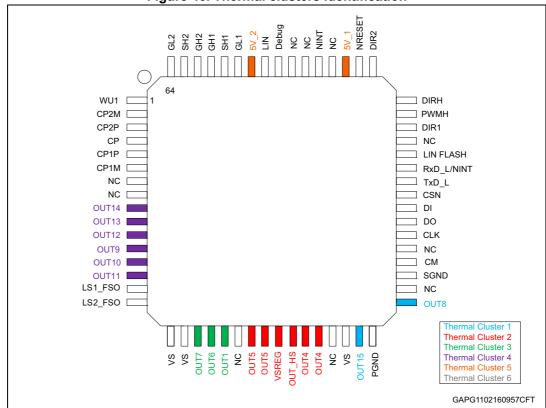

Figure 2. Pin connection (top view)

# 3 Electrical specifications

# 3.1 Absolute maximum ratings

Stressing the device above the rating listed in *Table 2* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability

Table 2. Absolute maximum ratings

| Symbol                                                                                                                                                                                                                                 | Parameter / test condition                                           | Value [DC voltage]                                                                           | Unit     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------|

| \/ \/                                                                                                                                                                                                                                  | DC supply voltage / "jump start"                                     | -0.3 to +28                                                                                  | V        |

| V <sub>S,</sub> V <sub>SREG</sub>                                                                                                                                                                                                      | Load dump                                                            | -0.3 to +40                                                                                  | V        |

| 5V_1                                                                                                                                                                                                                                   | Stabilized supply voltage, logic supply                              | -0.3 to 6.5<br>V1 < V <sub>SREG</sub>                                                        | V        |

| 5V_2 <sup>(1)</sup>                                                                                                                                                                                                                    | Stabilized supply voltage                                            | -0.3 to +28 <sup>(2)</sup>                                                                   | V        |

| V <sub>DI</sub> , V <sub>CLK</sub> V <sub>CSN</sub> V <sub>DO</sub> , V <sub>RXDL/NINT</sub> , V <sub>NRESET</sub> , V <sub>CM</sub> , V <sub>DIR</sub> , V <sub>DIR2</sub> , V <sub>PWMH</sub> , V <sub>DIRH</sub> , V <sub>INT</sub> | Logic input / output voltage range                                   | -0.3 to V1+0.3                                                                               | ٧        |

| V <sub>LIN_FLASH</sub> , V <sub>TXDL</sub>                                                                                                                                                                                             | Multi Level Inputs                                                   | -0.3 to 40                                                                                   | V        |

| V <sub>Debug</sub>                                                                                                                                                                                                                     | Debug input pin voltage range                                        | -0.3 to 40                                                                                   | ٧        |

| V <sub>LS1_FSO</sub> ,<br>V <sub>LS2_FSO</sub>                                                                                                                                                                                         | Output voltage range of Fail-Safe low-side Switches                  | -0.3 to 35                                                                                   | V        |

| V                                                                                                                                                                                                                                      | DC Wake up input voltage / "jump start"                              | -0.3 to +28                                                                                  | ٧        |

| V <sub>WU</sub>                                                                                                                                                                                                                        | Load dump                                                            | -0.3 to +40                                                                                  | V        |

| V <sub>LIN</sub>                                                                                                                                                                                                                       | LIN bus I/O voltage range                                            | -20 to +40                                                                                   | ٧        |

| I <sub>Input</sub> <sup>(3)</sup>                                                                                                                                                                                                      | Current injection into V <sub>S</sub> related input pins             | 20                                                                                           | mA       |

| I <sub>OUT_INJ</sub> (3)                                                                                                                                                                                                               | Current injection into V <sub>S</sub> related outputs                | 20                                                                                           | mA       |

| V <sub>OUTn</sub> , V <sub>out_HS</sub>                                                                                                                                                                                                | Output voltage (n = 1 to 15)                                         | -0.3 to V <sub>S</sub> +0.3                                                                  | V        |

| V <sub>GH1</sub> , V <sub>GH2</sub> (V <sub>Gxy</sub> )                                                                                                                                                                                | High Voltage Signal Pins                                             | $V_{Sxy}$ -0.3 to $V_{Sxy}$ +13; $V_{CP}$ +0.3                                               | <b>V</b> |

| V <sub>GL1,</sub> V <sub>GL2</sub> , (V <sub>Gxy</sub> )                                                                                                                                                                               | High Voltage Signal Pins                                             | V <sub>Sxy</sub> -0.3 to<br>V <sub>Sxy</sub> +13; V <sub>CP</sub> -0.3V<br>to +12V; Vcp+0.3V | ٧        |

|                                                                                                                                                                                                                                        | High Voltage Signal Pins                                             | -1 to 40                                                                                     | V        |

| $V_{SH1}, V_{SH2} (V_{Sxy})$                                                                                                                                                                                                           | High Voltage Signal Pins; single pulse with t <sub>max</sub> = 200ns | -5 to 40                                                                                     | V        |

| V <sub>CP1P</sub>                                                                                                                                                                                                                      | High Voltage Signal Pins                                             | V <sub>S</sub> -0.3 to V <sub>S</sub> +14                                                    | V        |

| V <sub>CP2P</sub>                                                                                                                                                                                                                      | High Voltage Signal Pins                                             | V <sub>S</sub> -0.6 to V <sub>S</sub> +14                                                    | V        |

18/162 DocID029145 Rev 4

Table 2. Absolute maximum ratings (continued)

| Symbol                                                                  | Parameter / test condition                                                                          | Value [DC voltage]                        | Unit |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------|------|

| V <sub>CP1M</sub> , V <sub>CP2M</sub>                                   | High Voltage Signal Pins                                                                            | -0.3 to V <sub>S</sub> +0.3               | V    |

| V                                                                       | High Voltage Signal Pin V <sub>S</sub> ≤ 26 V                                                       | V <sub>S</sub> -0.3 to V <sub>S</sub> +14 | V    |

| V <sub>CP</sub>                                                         | High Voltage Signal Pin V <sub>S</sub> > 26 V                                                       | V <sub>S</sub> -0.3 to +40                | V    |

| lout9, lout10,<br>lout11, lout12,<br>lout13, lout14,<br>lout15, lout_нs |                                                                                                     | ±1.25                                     | A    |

| I <sub>OUT8</sub>                                                       | Output current <sup>(2)</sup>                                                                       | ±2.5                                      | Α    |

| I <sub>OUT7</sub>                                                       |                                                                                                     | ±5                                        | Α    |

| I <sub>OUT1,6</sub>                                                     |                                                                                                     | ±5                                        | Α    |

| I <sub>OUT4,5</sub>                                                     |                                                                                                     | ±10                                       | Α    |

|                                                                         | Maximum cumulated current at V <sub>S</sub> drawn by OUT1 <sup>(2)</sup>                            | ±7.5                                      | Α    |

|                                                                         | Maximum cumulated current at V <sub>S</sub> drawn by OUT8 & OUT10 <sup>(2)</sup>                    | ±2.5                                      | Α    |

|                                                                         | Maximum cumulated current at V <sub>S</sub> drawn by OUT4 <sup>(2)</sup>                            | ±10                                       | Α    |

| I <sub>VScum</sub>                                                      | Maximum cumulated current at V <sub>S</sub> drawn by OUT5 <sup>(2)</sup>                            | ±10                                       | Α    |

|                                                                         | Maximum cumulated current at V <sub>S</sub> drawn by OUT6 & OUT7 <sup>(2)</sup>                     | ±7.5                                      | Α    |

| I <sub>VScum</sub>                                                      | Maximum cumulated current at V <sub>S</sub> drawn by OUT9, OUT11, OUT12, OUT13, OUT14, OUT15 and CP | ±2.5                                      | А    |

| I <sub>VSREG</sub>                                                      | Maximum current at V <sub>SREG</sub> pin <sup>(2)</sup> (5V_1. 5V_2 and OUT_HS)                     | ±2.5                                      | Α    |

|                                                                         | Maximum cumulated current at PGND drawn by OUT1 & OUT6 <sup>(2)</sup>                               | ±7.5                                      | Α    |

| I <sub>PGNDcum</sub>                                                    | Maximum cumulated current at PGND drawn by OUT5 <sup>(2)</sup>                                      | ±12.5                                     | Α    |

|                                                                         | Maximum cumulated current at PGND drawn by OUT4 <sup>(2)</sup>                                      | ±12.5                                     | Α    |

| I <sub>SGND</sub>                                                       | Maximum current at SGND <sup>(2)</sup>                                                              | ±1.25                                     | Α    |

| GND pins                                                                | PGND versus SGND                                                                                    | -0.3 to 0.3                               | V    |

<sup>1.</sup>  $5V_2$  is robust against SC to 28 V only in case  $V_{\mbox{SREG}}$  is supplied.

Note:

All maximum ratings are absolute ratings. Leaving the limitation of any of these values may cause an irreversible damage of the integrated circuit!

<sup>2.</sup> Values for the absolute maximum DC current through the bond wires. This value does not consider maximum power dissipation or other limits.

<sup>3.</sup> Guaranteed by design.

Note:

Loss of ground or ground shift with externally grounded loads: ESD structures are configured for nominal currents only. If external loads are connected to different grounds, the current load must be limited to this nominal current.

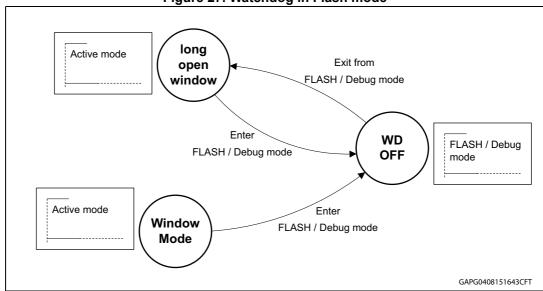

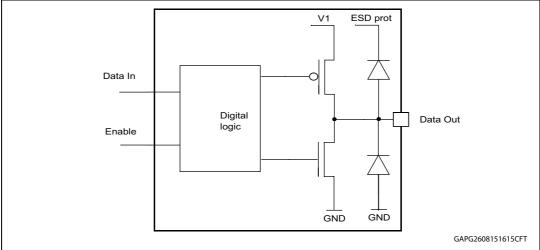

# 3.2 ESD protection

Table 3. ESD protection

| Parameter                                                   | Value                                                              | Unit |

|-------------------------------------------------------------|--------------------------------------------------------------------|------|

| All pins <sup>(1)</sup>                                     | +/-2                                                               | kV   |

| All power output pins <sup>(2)</sup> : OUT1 – OUT15, OUT_HS | +/-4                                                               | kV   |

| LIN                                                         | +/-8 <sup>(2)</sup><br>+/-10 <sup>(3)</sup><br>+/-6 <sup>(4)</sup> | kV   |

| All pins <sup>(5)</sup>                                     | +/-500                                                             | V    |

| Corner pins <sup>(5)</sup>                                  | +/-750 <sup>(6)</sup>                                              | V    |

| All pins <sup>(7)</sup>                                     | +/- 200                                                            | V    |

- 1. HBM (human body model, 100 pF, 1.5 kΩ) according to MIL 883C, Method 3015.7 or EIA/JESD22A114-A.

- 2. HBM with all none zapped pins grounded.

- 3. Indirect ESD Test according to IEC 61000-4-2 (150 pF, 330 Ω) and 'Hardware Requirements for LIN, CAN and Flexray Interfaces in Automotive Applications' (version 1.3, 2012-05-04).

- Direct ESD Test according to IEC 61000-4-2 (150 pF, 330 Ω) and 'Hardware Requirements for LIN, CAN and Flexray Interfaces in Automotive Applications' (version 1.3, 2012-05-04).

- 5. Charged device model.

- $6. \quad \text{For WU, these limits are referred to one-zap stress; in case of three-zap stress, the limits are +750 V/-400 V.}\\$

- 7. Machine model; C = 220 pF, R = 0  $\Omega$ .

### 3.3 Thermal data

Table 4. Operating junction temperature

| Symbol         | Parameter                      | Value      | Unit |

|----------------|--------------------------------|------------|------|

| T <sub>j</sub> | Operating junction temperature | -40 to 175 | °C   |

All parameters are guaranteed in the junction temperature range -40 to 150°C (unless otherwise specified); the device is still operative and functional at higher temperatures (up to 175°C).

Note: Parameters limits at higher junction temperatures than 150°C may change respect to what is specified as per the standard temperature range.

Note: Device functionality at high junction temperature is guaranteed by characterization.

5//

| Symbol               | Parameter                                 |                                                             | Min.       | Тур.       | Max.       | Unit |

|----------------------|-------------------------------------------|-------------------------------------------------------------|------------|------------|------------|------|

| $T_W$                | Thermal overtemperature warning threshold | $T_j^{(1)}$                                                 | 140        | 150        | 160        | °C   |

| T <sub>SD1</sub>     | Thermal shutdown junction temperature 1   | T <sub>j</sub> <sup>(1)</sup><br>Cluster 1-4<br>Cluster 5-6 | 165<br>165 | 175<br>175 | 185<br>190 | °C   |

| T <sub>SD2</sub>     | Thermal shutdown junction temperature 2   | T <sub>j</sub> <sup>(1)</sup>                               | 175        | 185        | 195        | °C   |

| T <sub>SD12hys</sub> | memai shataown janetion temperature 2     | Hysteresis                                                  |            | 5          |            | °C   |

| T <sub>jtft</sub>    | Thermal warning / shutdown filter time    |                                                             |            | 32         |            | μs   |

Table 5. Temperature warning and thermal shutdown

#### 3.3.1 LQFP64 thermal data

Devices belonging to L99DZxxx family embed a multitude of junctions (i.e. Outputs based on a PowerMOSFET stage) housed in a relatively small piece of silicon. The most complex device contains, among all the described features, 6 half-bridges (12 N-Channel PowerMOS), 10 high-sides and two voltage regulators; all the other derivatives, even if smaller than the family super set device, still contain a significant number of junctions.

For this reason, using the Thermal Impedance of a single junction (i.e. voltage regulator or major power dissipation contributor) does not allow to predict thermal behavior of the whole device and therefore it is not possible to assess if a device is thermally suitable for a given activation profile and loads characteristics.

Thermal information is provided as temperature reading by different clusters placed close to the most dissipative junctions.

Some representative and realistic worst-case thermal profiles are described in the below paragraph.

Following measurement methods can be easily implemented, by final user, for a specific activation profile.

#### L99DZ120 thermal profiles

#### **Profile 1**

Battery Voltage: 16V, Ambient temperature start: 85°C

DC activation

- V1 charged with 70 mA (DC activation)

- V2 charged with 30 mA (DC activation)

- OUT7: 1 x10W bulb (DC activation)

- OUT8: 1 x 5W bulb (DC activation)

- OUT11: 300 Ω resistor (DC activation)

- OUT12: 300 Ω resistor (DC activation)

- OUT13: 300 Ω resistor (DC activation)

- OUT14: 300 Ω resistor (DC activation)

<sup>1.</sup> Non-overlapping.

#### Cyclic activation

- OUT4 OUT5: 3,3  $\Omega$  resistor placed across those outputs

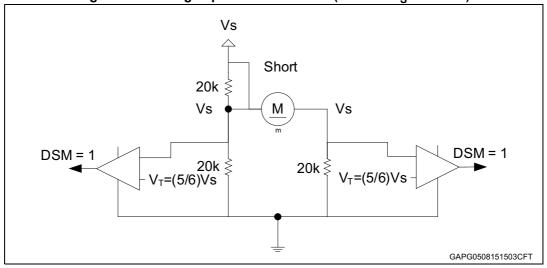

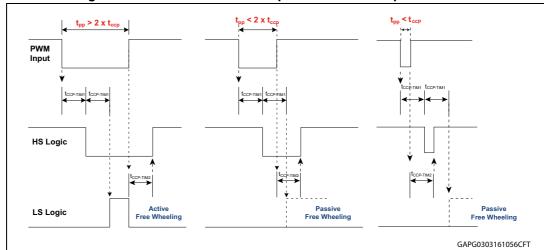

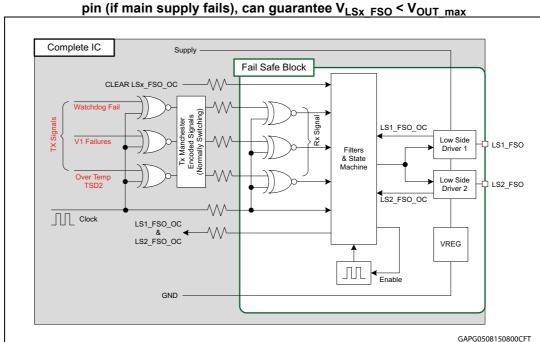

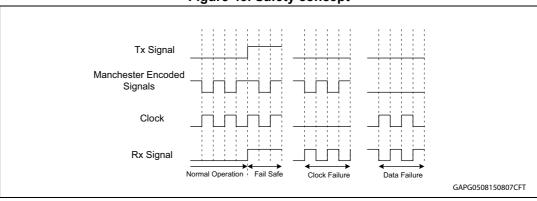

- 10 activations of Lock/Un-lock (250 ms ON Lock; 500 ms wait; 250 ms ON Un-lock unlock; 500 ms wait)