# High-Voltage Switcher for Low Power Offline SMPS

The NCP106X products integrate a fixed frequency current mode controller with a 700 V MOSFET. Available in a PDIP-7, SOIC-10 or SOIC-16 package, the NCP106X offer a high level of integration, including soft-start, frequency-jittering, short-circuit protection, skip-cycle, adjustable peak current set point, ramp compensation, and a Dynamic Self-Supply (eliminating the need for an auxiliary winding).

Unlike other monolithic solutions, the NCP106X is quiet by nature: during nominal load operation, the part switches at one of the available frequencies (60 kHz or 100 kHz). When the output power demand diminishes, the IC automatically enters frequency foldback mode and provides excellent efficiency at light loads. When the power demand reduces further, it enters into a skip mode to reduce the standby consumption down to a no load condition.

Protection features include: a timer to detect an overload or a short–circuit event, Overvoltage Protection with auto–recovery and AC input line voltage detection (A version).

The ON proprietary integrated Over Power Protection (OPP) lets you harness the maximum delivered power without affecting your standby performance simply via external resistors.

For improved standby performance, the connection of an auxiliary winding stops the DSS operation and helps to reduce input power consumption below 50 mW at high line.

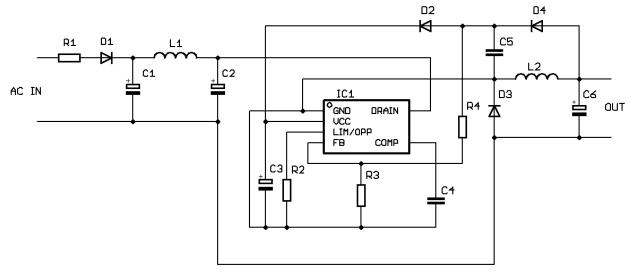

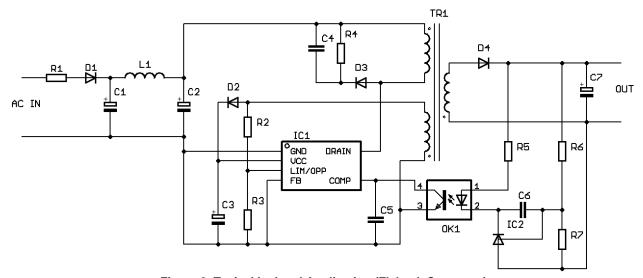

NCP106x can be seamlessly used both in non-isolated and in isolated topologies.

#### **Features**

- Built–in 700 V MOSFET with  $R_{DS(on)}$  of 34  $\Omega$  (NCP1060) and 11.4  $\Omega$  (NCP1063)

- Large Creepage Distance Between High-voltage Pins

- Current–Mode Fixed Frequency Operation 60 kHz or 100 kHz (130 kHz on demand)

- Adjustable Peak Current: see below table

- Fixed Ramp Compensation

- Direct Feedback Connection for Non-isolated Converter

- Internal and Adjustable Over Power Protection (OPP) Circuit

- Skip-Cycle Operation at Low Peak Currents Only

- Dynamic Self–Supply: No Need for an Auxiliary Winding

- Internal 4 ms Soft–Start

- Auto–Recovery Output Short Circuit Protection with Timer–Based Detection

- Auto–Recovery Overvoltage Protection with Auxiliary Winding Operation

- Frequency Jittering for Better EMI Signature

- No Load Input Consumption < 50 mW

## ON Semiconductor™

www.onsemi.com

#### MARKING DIAGRAMS

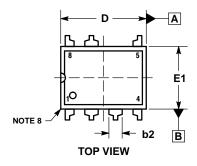

PDIP-7 CASE 626A AP SUFFIX

SOIC-10 CASE 751BQ AD or BD SUFFIX

x = Power Switch Circuit On–state Resistance

$(0 = 34 \Omega, 3 = 11.4 \Omega)$

f = Brown In (A = Yes, B = No)

yyy = Oscillator Frequency

(060 = 60 kHz, 100 = 100 kHz)

A = Assembly Location L. WL = Wafer Lot

Y. YY = Year

W, WW = Work Week

G or ■ = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 26 of this data sheet.

- Frequency Foldback to Improve Efficiency at Light Load

- These are Pb-Free Devices

# **Typical Applications**

- Auxiliary / Standby Isolated and Non-isolated Power Supplies

- Power Meter SMPS

- Wide Vin Low Power Industrial SMPS

## PRODUCT INFORMATION & INDICATIVE MAXIMUM OUTPUT POWER

|                 |                     |                     | 230 Vac ± 15% |            | 85 –    | 265 Vac    |

|-----------------|---------------------|---------------------|---------------|------------|---------|------------|

| Product         | R <sub>DS(on)</sub> | I <sub>IPK(0)</sub> | Adapter       | Open Frame | Adapter | Open Frame |

| NCP1060 60 kHz  | 34 Ω                | 300 mA              | 3.3 W         | 8.3 W      | 1.9 W   | 4.7 W      |

| NCP1063 100 kHz | 11.4 Ω              | 780 mA              | 6.2 W         | 15.5 W     | 3.3 W   | 7.8 W      |

NOTE: Informative values only, with  $T_{amb} = 25^{\circ}C$ ,  $T_{case} = 100^{\circ}C$ , PDIP-7 package, Self supply via Auxiliary winding and circuit mounted on minimum copper area as recommended.

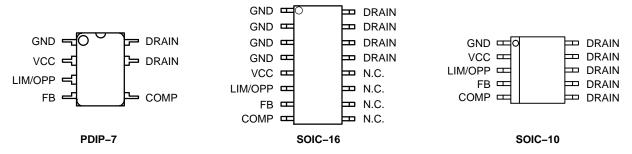

Figure 1. Pin Connections

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin No PDIP 7   SOIC 10   SOIC 16 |      |          |                 |                                   |                                                                                                                                                                                                                                                                               |

|-----------------------------------|------|----------|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |      | Pin Name | Function        | Pin Description                   |                                                                                                                                                                                                                                                                               |

| 1                                 | 1    | 1–4      | GND             | The IC Ground                     |                                                                                                                                                                                                                                                                               |

| 2                                 | 2    | 5        | V <sub>CC</sub> | Powers the internal circuitry     | This pin is connected to an external capacitor. The V <sub>DD</sub> includes an auto–recovery over voltage protection.                                                                                                                                                        |

| 3                                 | 3    | 6        | LIM/OPP         | Ipeak set / Over power limitation | The current drown from the pin decreases Ipeak of the primary winding. If resistive divider from the auxiliary winding is connected to this pin it sets the OPP compensation level (it diminishes the peak current.)                                                          |

| 4                                 | 4    | 7        | FB              | Feedback signal<br>input          | This is the inverting input of the trans conductance error amplifier. It is normally connected to the switching power supply output through a resistor divider.                                                                                                               |

| 5                                 | 5    | 8        | Comp            | Compensation                      | The error amplifier output is available on this pin. The network connected between this pin and ground adjusts the regulation loop bandwidth. Also, by connecting an opto-coupler to this pin, the peak current set point is adjusted accordingly to the output power demand. |

| 6                                 |      | 9–12     |                 |                                   | This un–connected pin ensures adequate creepage distance                                                                                                                                                                                                                      |

| 7,8                               | 6–10 | 13–16    | Drain           | Drain connection                  | The internal drain MOSFET connection                                                                                                                                                                                                                                          |

Figure 2. Typical Non-isolated Application (Buck Converter)

Figure 3. Typical Isolated Application (Flyback Converter)

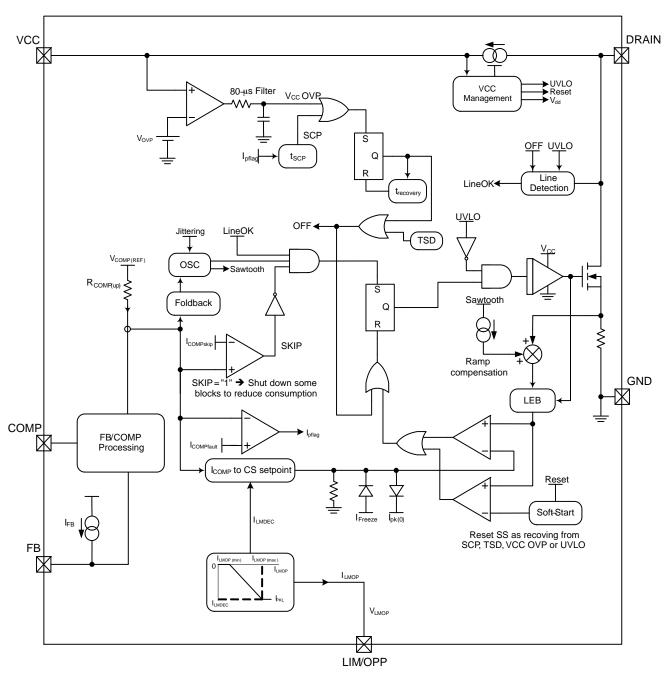

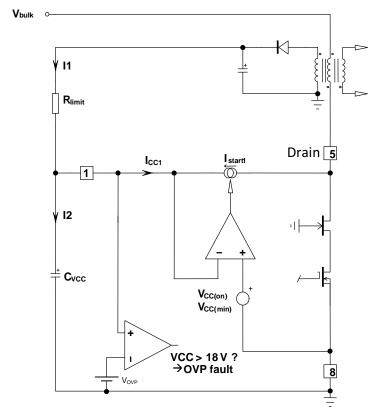

**Figure 4. Simplified Internal Circuit Architecture**

Table 2. MAXIMUM RATING TABLE (All voltages related to GND terminal)

| Rating                                                                                                                                                                                                                                                          | Symbol              | Value                                   | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|------|

| Power supply voltage, V <sub>CC</sub> pin, continuous voltage                                                                                                                                                                                                   | V <sub>CC</sub>     | -0.3 to 20                              | V    |

| Voltage on all pins, except Drain and V <sub>CC</sub> pin                                                                                                                                                                                                       | Vinmax              | -0.3 to 10                              | V    |

| Drain voltage                                                                                                                                                                                                                                                   | BVdss               | -0.3 to 700                             | V    |

| Maximum Current into V <sub>CC</sub> pin                                                                                                                                                                                                                        | I <sub>CC</sub>     | 10                                      | mA   |

| Drain Current Peak during Transformer Saturation ( $T_J$ = 150°C): NCP1060 NCP1063 Drain Current Peak during Transformer Saturation ( $T_J$ = 125°C): NCP1060 NCP1063 Drain Current Peak during Transformer Saturation ( $T_J$ = 25°C): NCP1060 NCP1060 NCP1063 | I <sub>DS(PK)</sub> | 300<br>850<br>335<br>950<br>520<br>1500 | mA   |

| Thermal Resistance Junction-to-Air - PDIP7 with 200 mm² of 35-μ copper area                                                                                                                                                                                     | $R_{\theta J-A}$    | 115                                     | °C/W |

| Thermal Resistance Junction-to-Air - SOIC10 with 200 mm² of 35-µ copper area                                                                                                                                                                                    | $R_{\theta J-A}$    | 132                                     | °C/W |

| Thermal Resistance Junction–to–Air – SOIC16 with 200 mm² of 35–μ copper area                                                                                                                                                                                    | $R_{\theta J-A}$    | 104                                     | °C/W |

| Maximum Junction Temperature                                                                                                                                                                                                                                    | $T_{JMAX}$          | 150                                     | °C   |

| Storage Temperature Range                                                                                                                                                                                                                                       |                     | -60 to +150                             | °C   |

| Human Body Model ESD Capability (All pins except HV pin) per JEDEC JESD22-A114F                                                                                                                                                                                 | HBM                 | 2                                       | kV   |

| Charged–Device Model ESD Capability per JEDEC JESD22–C101E                                                                                                                                                                                                      | CDM                 | 1                                       | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>1.</sup> This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

## **Table 3. ELECTRICAL CHARACTERISTICS**

(For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 14$  V unless otherwise noted)

| Symbol                           | Rating                                                                                                                                                                                                                                                                            | Pin                       | Min         | Тур                          | Max                          | Unit |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------|------------------------------|------------------------------|------|

| SUPPLY SEC                       | CTION AND V <sub>CC</sub> MANAGEMENT                                                                                                                                                                                                                                              |                           |             |                              |                              |      |

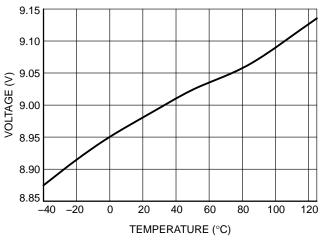

| V <sub>CC(on)</sub>              | V <sub>CC</sub> increasing level at which the switcher starts operation                                                                                                                                                                                                           | 2 (5)                     | 8.4         | 9.0                          | 9.5                          | V    |

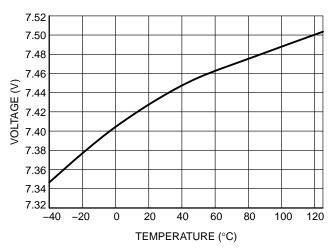

| V <sub>CC(min)</sub>             | V <sub>CC</sub> decreasing level at which the HV current source restarts                                                                                                                                                                                                          | 2 (5)                     | 7.0         | 7.5                          | 7.8                          | V    |

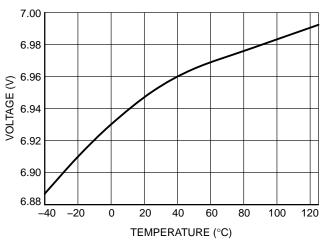

| V <sub>CC(off)</sub>             | V <sub>CC</sub> decreasing level at which the switcher stops operation (UVLO)                                                                                                                                                                                                     | 2 (5)                     | 6.7         | 7.0                          | 7.2                          | V    |

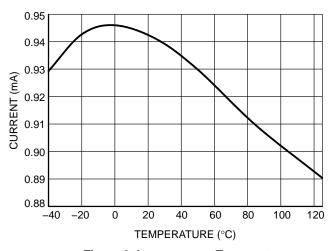

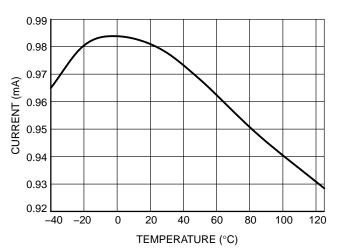

| I <sub>CC1</sub>                 | Internal IC consumption, NCP1060 switching at 60 kHz, LIM/OPP = 0 A Internal IC consumption, NCP1060 switching at 100 kHz, LIM/OPP = 0 A Internal IC consumption, NCP1063 switching at 60 kHz, LIM/OPP = 0 A Internal IC consumption, NCP1063 switching at 100 kHz, LIM/OPP = 0 A | 2 (5)                     | -<br>-<br>- | 0.92<br>0.97<br>0.99<br>1.07 | 1.05<br>1.10<br>1.12<br>1.22 | mA   |

| I <sub>CCskip</sub>              | Internal IC consumption, COMP is 0 V (No switching on MOSFET)                                                                                                                                                                                                                     | 2 (5)                     | _           | 340                          | _                            | μΑ   |

|                                  | ITCH CIRCUIT                                                                                                                                                                                                                                                                      |                           |             |                              |                              |      |

| R <sub>DS(on)</sub>              | Power Switch Circuit on–state resistance  NCP1060 (Id = 50 mA)  Tj = 25°C  Tj = 125°C  NCP1063 (Id = 50 mA)  Tj = 25°C  Tj = 125°C                                                                                                                                                | 7, 8<br>(6–10)<br>(13–16) | -<br>-<br>- | 34<br>65<br>11.4<br>22       | 41<br>72<br>14.0<br>24       | Ω    |

| BV <sub>DSS</sub>                | Power Switch Circuit & Startup breakdown voltage (ID $_{(off)}$ = 120 $\mu$ A, Tj = 25°C)                                                                                                                                                                                         | 7, 8<br>(6–10)<br>(13–16) | 700         | -                            | -                            | V    |

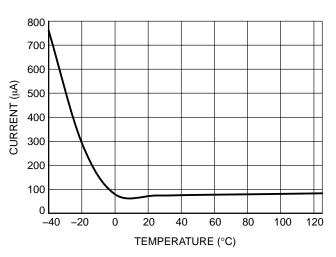

| I <sub>DSS(off)</sub>            | Power Switch & Startup breakdown voltage off–state leakage current Tj = 125°C (Vds = 700 V)                                                                                                                                                                                       | 7, 8<br>(6–10)<br>(13–16) | -           | 84                           | -                            | μΑ   |

| t <sub>r</sub><br>t <sub>f</sub> | Switching characteristics (R <sub>L</sub> = $50~\Omega$ , V <sub>DS</sub> set for I <sub>drain</sub> = $0.7~x$ Ilim) Turn–on time ( $90\% - 10\%$ ) Turn–off time ( $10\% - 90\%$ )                                                                                               | 7, 8<br>(6–10)<br>(13–16) | -<br>-      | 20<br>10                     | -<br>-                       | ns   |

| t <sub>on(min)</sub>             | Minimum on time<br>NCP1060<br>NCP1063                                                                                                                                                                                                                                             | 7, 8<br>(6–10)<br>(13–16) | -<br>-      | 200<br>230                   | -<br>-                       | ns   |

| NTERNAL S                        | TART-UP CURRENT SOURCE                                                                                                                                                                                                                                                            |                           |             | •                            | •                            |      |

| I <sub>start1</sub>              | High–voltage current source, $V_{CC} = V_{CC(on)} - 200 \text{ mV}$                                                                                                                                                                                                               | 7, 8<br>(6–10)<br>(13–16) | 5           | 8                            | 12                           | mA   |

| I <sub>start2</sub>              | High–voltage current source, V <sub>CC</sub> = 0 V                                                                                                                                                                                                                                | 7, 8<br>(6–10)<br>(13–16) | -           | 0.5                          | -                            | mA   |

| V <sub>CCTH</sub>                | V <sub>CC</sub> Transient level for I <sub>start1</sub> to I <sub>start2</sub> toggling point                                                                                                                                                                                     | 2 (5)                     | -           | 1.4                          | _                            | V    |

| V <sub>start(min)</sub>          | Minimum startup voltage, V <sub>CC</sub> = 0 V                                                                                                                                                                                                                                    | 7, 8<br>(6–10)<br>(13–16) |             |                              | 21                           | V    |

| URRENT C                         | OMPARATOR                                                                                                                                                                                                                                                                         |                           |             |                              |                              |      |

| I <sub>IPK</sub>                 | Maximum internal current setpoint at 50% duty cycle FB = 2 V, LIM/OPP = 0 μA, Tj = 25°C NCP1060 NCP1063                                                                                                                                                                           |                           | -<br>-      | 250<br>650                   | -<br>-                       | mA   |

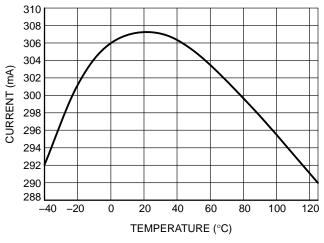

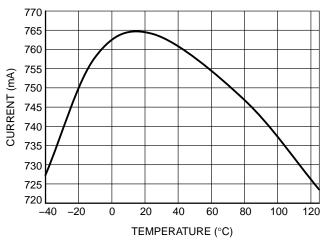

| I <sub>IPK(0)</sub>              | Maximum internal current setpoint at beginning of switching cycle FB = 2 V, LIM/OPP pin open Tj = 25°C NCP1060 NCP1063                                                                                                                                                            | -<br>-                    | 268<br>702  | 300<br>780                   | 332<br>858                   | mA   |

The final switch current is: I<sub>IPK(0)</sub> / (V<sub>in</sub>/L<sub>P</sub> + S<sub>a</sub>) x V<sub>in</sub>/L<sub>P</sub> + V<sub>in</sub>/L<sub>P</sub> x t<sub>prop</sub>, with S<sub>a</sub> the built–in slope compensation, Vin the input voltage, L<sub>P</sub> the primary inductor in a flyback, and t<sub>prop</sub> the propagation delay.

Oscillator frequency is measured with disabled jittering.

# **Table 3. ELECTRICAL CHARACTERISTICS**

(For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 14$  V unless otherwise noted)

| Symbol                              | Rating                                                                                                                       | Pin    | Min          | Тур          | Max          | Unit |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------|--------------|--------------|--------------|------|

| CURRENT C                           | OMPARATOR                                                                                                                    |        |              |              |              |      |

| I <sub>IPKSW</sub>                  | Final switch current with a primary slope of 200 mA/μs, F <sub>SW</sub> = 60 kHz (Note 2), LIM/OPP pin open NCP1060 NCP1063  | _<br>_ | _<br>_       | 330<br>740   | -<br>-       | mA   |

| I <sub>IPKSW</sub>                  | Final switch current with a primary slope of 200 mA/μs, F <sub>SW</sub> = 100 kHz (Note 2), LIM/OPP pin open NCP1060 NCP1063 |        | _<br>_<br>_  | 320<br>710   | -<br>-       | mA   |

| I <sub>LMDEC</sub>                  | Maximum internal current setpoint at beginning of switching cycle FB = 2 V, LIM/OPP = -285 μA, Tj = 25°C NCP1060 NCP1063     |        | -<br>-       | 128<br>312   | -<br>-       | mA   |

| t <sub>SS</sub>                     | Soft-start duration (guaranteed by design)                                                                                   | _      | _            | 4            | _            | ms   |

| t <sub>prop</sub>                   | Propagation delay from current detection to drain OFF state                                                                  | -      | _            | 70           | _            | ns   |

| t <sub>LEB</sub>                    | Leading Edge Blanking Duration<br>NCP1060<br>NCP1063                                                                         | -<br>- | _<br>_       | 130<br>160   | _<br>_       | ns   |

| INTERNAL O                          | SCILLATOR                                                                                                                    |        |              |              |              |      |

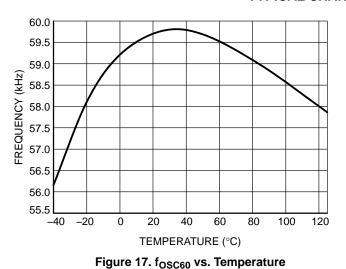

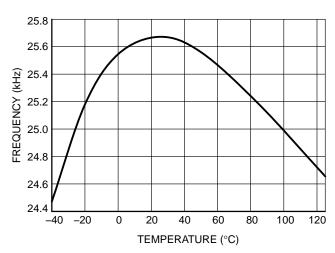

| fosc                                | Oscillation frequency, 60 kHz version, Tj = 25°C (Note 3)                                                                    | _      | 54           | 60           | 66           | kHz  |

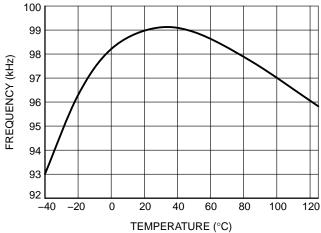

| f <sub>OSC</sub>                    | Oscillation frequency, 100 kHz version, Tj = 25°C (Note 3)                                                                   | _      | 90           | 100          | 110          | kHz  |

| f <sub>jitter</sub>                 | Frequency jittering in percentage of fOSC                                                                                    | _      | _            | ±6           | _            | %    |

| f <sub>swing</sub>                  | Jittering swing frequency                                                                                                    | -      | _            | 300          | _            | Hz   |

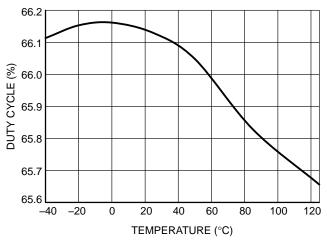

| D <sub>max</sub> Maximum duty-cycle |                                                                                                                              | _      | 62           | 66           | 72           | %    |

| ERROR AMP                           | PLIFIER SECTION                                                                                                              | -      |              |              |              |      |

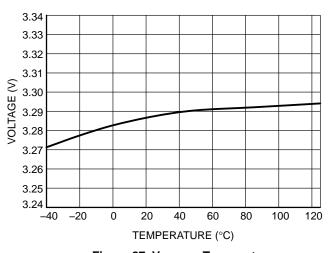

| $V_{REF}$                           | Voltage Feedback Input (V <sub>COMP</sub> = 2.5 V)                                                                           | 4 (7)  | 3.2          | 3.3          | 3.4          | V    |

| I <sub>FB</sub>                     | Input Bias Current (V <sub>FB</sub> = 3.3 V)                                                                                 | 4 (7)  | _            | 1            | _            | μΑ   |

| $G_M$                               | Transconductance                                                                                                             | 5 (8)  |              | 2            |              | mS   |

| I <sub>OTAlim</sub>                 | OTA maximum current capability (V <sub>FB</sub> > V <sub>OTAen</sub> )                                                       | 5 (8)  |              | ±150         |              | μΑ   |

| V <sub>OTAen</sub>                  | FB voltage to disable OTA                                                                                                    | 4 (7)  | 0.7          | 1.3          | 1.7          | V    |

| COMPENSA                            | TION SECTION                                                                                                                 |        |              |              |              |      |

| I <sub>COMPfault</sub>              | COMP current for which Fault is detected                                                                                     | 5 (8)  | -            | -40          | _            | μΑ   |

| I <sub>COMP100%</sub>               | COMP current for which internal current set-point is 100% (I <sub>IPK(0)</sub> )                                             | 5 (8)  | _            | -44          | _            | μΑ   |

| I <sub>COMPfreeze</sub>             | COMP current for which internal current setpoint is: I <sub>Freeze1 or 2</sub> (NCP1060/3)                                   | 5 (8)  | _            | -80          | _            | μΑ   |

| V <sub>COMP(REF)</sub>              | Equivalent pull-up voltage in linear regulation range (Guaranteed by design)                                                 | 5 (8)  | _            | 2.7          | -            | V    |

| R <sub>COMP(up)</sub>               | Equivalent feedback resistor in linear regulation range (Guaranteed by design)                                               | 5 (8)  | _            | 17.7         | -            | kΩ   |

| $V_{LMOP}$                          | Voltage on LIM/OPP pin @ $I_{LMOP}$ = -35 $\mu A$ Voltage on LIM/OPP pin @ $I_{LMOP}$ = -250 $\mu A$ , Tj = 25°C             | 3 (6)  | 1.40<br>1.28 | 1.50<br>1.35 | 1.60<br>1.42 | V    |

| I <sub>LMOP</sub>                   | Maximum current from LIM/OPP pin                                                                                             | 3 (6)  |              | -330         | -420         | μΑ   |

| I <sub>LMOP(min)</sub>              | Current at which LIM/OPP starts to decrease I <sub>PEAK</sub>                                                                | 3 (6)  | -20          | -26          | -32          | μΑ   |

| I <sub>LMOP(max)</sub>              | Current at which LIM/OPP stops to decrease I <sub>PEAK</sub>                                                                 | 3 (6)  |              | -285         |              | μΑ   |

| I <sub>LMOP(neg)</sub>              | Negative Active Clamp Voltage (I <sub>LMOP</sub> = -2.5 mA)                                                                  | 3 (6)  |              | -0.7         |              | V    |

The final switch current is: I<sub>IPK(0)</sub> / (V<sub>in</sub>/L<sub>P</sub> + S<sub>a</sub>) x V<sub>in</sub>/L<sub>P</sub> + V<sub>in</sub>/L<sub>P</sub> x t<sub>prop</sub>, with S<sub>a</sub> the built–in slope compensation, Vin the input voltage, L<sub>P</sub> the primary inductor in a flyback, and t<sub>prop</sub> the propagation delay.

Oscillator frequency is measured with disabled jittering.

## **Table 3. ELECTRICAL CHARACTERISTICS**

(For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 14$  V unless otherwise noted)

| Symbol                     | Rating                                                                                                                                  | Pin                      | Min    | Тур         | Max    | Unit  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------|-------------|--------|-------|

| COMPENSAT                  | TION SECTION                                                                                                                            |                          |        |             |        |       |

| I <sub>LMOP(pos)</sub>     | Positive Active Clamp (Guaranteed by design)                                                                                            | 3 (6)                    |        | 2.5         |        | mA    |

| FREQUENCY                  | FOLDBACK & SKIP                                                                                                                         |                          |        |             |        |       |

| I <sub>COMPfold</sub>      | Start of frequency foldback COMP pin current level                                                                                      | 5 (8)                    | -      | -68         | -      | μΑ    |

| I <sub>COMPfold(end)</sub> | End of frequency foldback COMP pin current level, f <sub>sw</sub> = f <sub>min</sub>                                                    | 5 (8)                    | -      | -100        | -      | μΑ    |

| f <sub>min</sub>           | The frequency below which skip-cycle occurs                                                                                             | _                        | 21     | 25          | 29     | kHz   |

| I <sub>COMPskip</sub>      | The COMP pin current level to enter skip mode                                                                                           | 5 (8)                    | -      | -120        | -      | μΑ    |

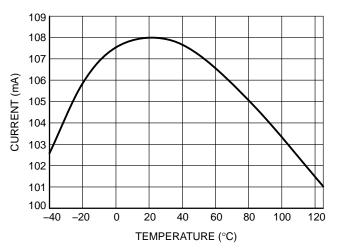

| I <sub>Freeze1</sub>       | Internal minimum current setpoint (I <sub>COMP</sub> = I <sub>COMPFreeze</sub> ) in NCP1060                                             |                          | -      | 110         | -      | mA    |

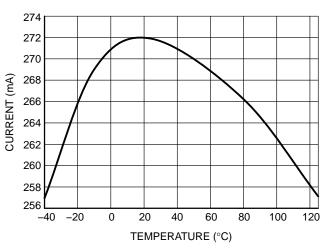

| I <sub>Freeze2</sub>       | Internal minimum current setpoint (I <sub>COMP</sub> = I <sub>COMPFreeze</sub> ) in NCP1063                                             |                          | -      | 270         | -      | mA    |

| RAMP COMP                  | ENSATION                                                                                                                                |                          |        |             |        |       |

| S <sub>a(60)</sub>         | The internal ramp compensation @ 60 kHz: NCP1060 NCP1063                                                                                |                          | -<br>- | 8.4<br>15.6 | _<br>_ | mA/μs |

| S <sub>a(100)</sub>        | The internal ramp compensation @ 100 kHz: NCP1060 NCP1063                                                                               |                          | _<br>_ | 14<br>26    | _<br>_ | mA/μs |

| PROTECTION                 | NS                                                                                                                                      |                          |        | •           | •      |       |

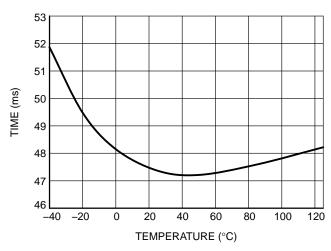

| t <sub>SCP</sub>           | Fault validation further to error flag assertion                                                                                        | -                        | 35     | 48          | _      | ms    |

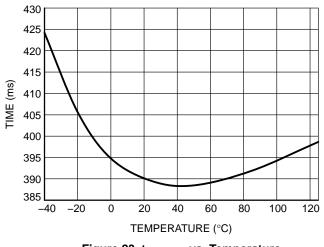

| t <sub>recovery</sub>      | OFF phase in fault mode                                                                                                                 | -                        | _      | 400         | _      | ms    |

| V <sub>OVP</sub>           | V <sub>CC</sub> voltage at which the switcher stops pulsing                                                                             | 1 (5)                    | 17.0   | 18.0        | 18.8   | V     |

| t <sub>OVP</sub>           | The filter of V <sub>CC</sub> OVP comparator                                                                                            | _                        | _      | 80          | _      | μs    |

| V <sub>HV(EN)</sub>        | The drain pin voltage above which allows MOSFET operate, which is detected after TSD, UVLO, SCP, or $V_{CC}$ OVP mode. (A version only) | 7,8<br>(6–10)<br>(13–16) | 67     | 87          | 110    | V     |

| TEMPERATU                  | RE MANAGEMENT                                                                                                                           | •                        |        |             |        |       |

| TSD                        | Temperature shutdown (Guaranteed by design)                                                                                             | -                        | 150    | 163         | _      | °C    |

| TSD <sub>hyst</sub>        | Hysteresis in shutdown (Guaranteed by design)                                                                                           | -                        | -      | 20          | _      | °C    |

The final switch current is: I<sub>IPK(0)</sub> / (V<sub>in</sub>/L<sub>P</sub> + S<sub>a</sub>) x V<sub>in</sub>/L<sub>P</sub> + V<sub>in</sub>/L<sub>P</sub> x t<sub>prop</sub>, with S<sub>a</sub> the built–in slope compensation, Vin the input voltage, L<sub>P</sub> the primary inductor in a flyback, and t<sub>prop</sub> the propagation delay.

Oscillator frequency is measured with disabled jittering.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

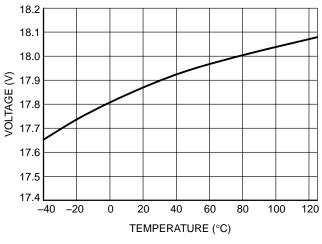

Figure 5. V<sub>CC(on)</sub> vs. Temperature

Figure 6. V<sub>CC(min)</sub> vs. Temperature

Figure 7. V<sub>CC(off)</sub> vs. Temperature

Figure 8. I<sub>DSS(off)</sub> vs. Temperature

Figure 9.  $I_{CC1\ 60\ kHz}$  vs. Temperature

Figure 10.  $I_{CC1\ 100\ kHz}$  vs. Temperature

Figure 11. I<sub>IPK(0)1060</sub> vs. Temperature

Figure 12. I<sub>IPK(0)1063</sub> vs. Temperature

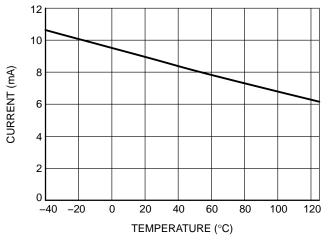

Figure 13. I<sub>start1</sub> vs. Temperature

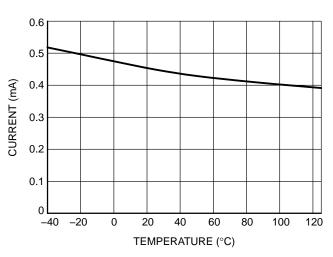

Figure 14. I<sub>start2</sub> vs. Temperature

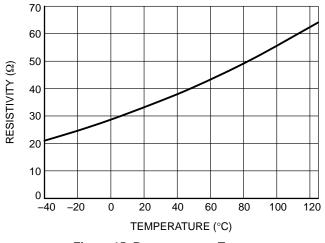

Figure 15.  $R_{DS(on)1060}$  vs. Temperature

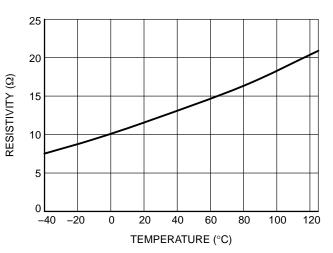

Figure 16. R<sub>DS(on)1063</sub> vs. Temperature

Figure 18. f<sub>OSC100</sub> vs. Temperature

Figure 19. I<sub>freeze1060</sub> vs. Temperature

Figure 20.  $I_{freeze1063}$  vs. Temperature

Figure 21. D<sub>(max)</sub> vs. Temperature

Figure 22. f<sub>min</sub> vs. Temperature

Figure 23. t<sub>recovery</sub> vs. Temperature

Figure 24. t<sub>SCP</sub> vs. Temperature

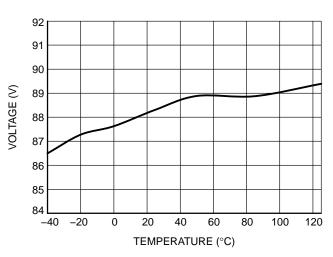

Figure 25. V<sub>OVP</sub> vs. Temperature

Figure 26.  $V_{HV(EN)}$  vs. Temperature

Figure 27.  $V_{REF}$  vs. Temperature

Figure 28. V<sub>OTAen</sub> vs. Temperature

#### **Application Information**

#### Introduction

The NCP106X offers a complete current—mode control solution. The component integrates everything needed to build a rugged and cost effective Switch—Mode Power Supply (SMPS) featuring low standby power. The Quick Selection Table, Table 4, details the differences between references, mainly peak current setpoints,  $R_{DS(on)}$  value and operating frequency.

- Current-mode operation: the controller uses current-mode control architecture.

- 700 V Power MOSFET: Due to ON Semiconductor Very High Voltage Integrated Circuit technology, the circuit hosts a high–voltage power MOSFET featuring a 34  $\Omega$  or 11.4  $\Omega$  R<sub>DS(on)</sub> Tj = 25°C. This value lets the designer build a power supply up to 7.8 W or 15.5 W operated on universal mains. An internal current source delivers the startup current, necessary to crank the power supply.

- Dynamic Self-Supply: Due to the internal high voltage current source, this device could be used in the application without the auxiliary winding to provide supply voltage.

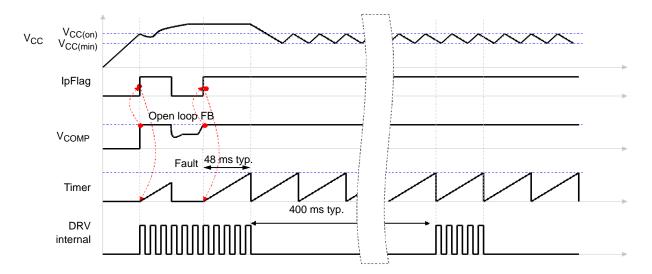

- Short circuit protection: by permanently monitoring the COMP line activity, the IC is able to detect the presence of a short–circuit, immediately reducing the output power for a total system protection. A t<sub>SCP</sub> timer is started as soon as the COMP current is below threshold, I<sub>COMPfault</sub>, which indicates the maximum peak current. If at the end of this timer the fault is still present, then the device enters a safe, auto–recovery burst mode, affected by a fixed timer recurrence, t<sub>recovery</sub>. Once the short has disappeared, the controller resumes and goes back to normal operation.

- Built-in VCC Over Voltage Protection: when the auxiliary winding is used to bias the V<sub>CC</sub> pin (no DSS), an internal comparator is connected to V<sub>CC</sub> pin. In case the voltage on the pin exceeds a level of V<sub>OVP</sub> (18 V typically), the controller immediately stops switching and waits a full timer period (t<sub>recovery</sub>) before attempting to restart. If the fault is gone, the controller resumes operation. If the fault is still there, e.g. a broken opto-coupler, the controller protects the load through a safe burst mode.

- Line detection: An internal comparator monitors the drain voltage as recovering from one of the following situations:

- Short Circuit Protection,

- V<sub>CC</sub> OVP is confirmed,

- UVLO.

- TSD

- If the drain voltage is lower than the internal threshold (V<sub>HV(EN)</sub>), the internal power switch is inhibited. This avoids operating at too low ac input. This is also called brown—in function in some fields. For applications not using standard AC mains (24 Vdc industrial bus for instance), the B version doesn't incorporate this line detection and let the device start as soon as voltage supply reaches V<sub>start(min)</sub>.

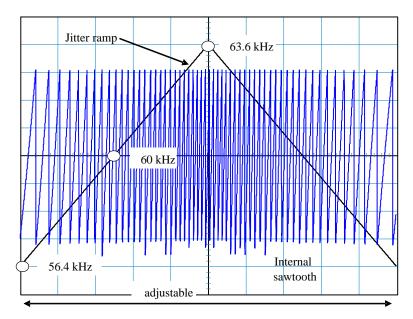

- Frequency jittering: an internal low-frequency modulation signal varies the pace at which the oscillator frequency is modulated. This helps spreading out energy in conducted noise analysis. To improve the EMI signature at low power levels, the jittering remains active in frequency foldback mode.

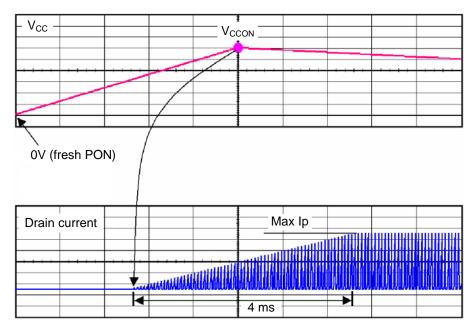

- **Soft–Start:** a 4 ms soft–start ensures a smooth startup sequence, reducing output overshoots.

- Frequency foldback capability: a continuous flow of pulses is not compatible with no-load/light-load standby power requirements. To excel in this domain, the controller observes the COMP pin current information and when it reaches a level of I<sub>COMPfold</sub>, the oscillator then starts to reduce its switching frequency as the feedback current continues to increase (the power demand continues to reduce). It can go down to 25 kHz (typical) reached for a feedback level of I<sub>COMPfold(end)</sub> (100 μA roughly). At this point, if the power continues to drop, the controller enters classical skip-cycle mode.

- Skip: if SMPS naturally exhibits a good efficiency at nominal load, it begins to be less efficient when the output power demand diminishes. By skipping un–needed switching cycles, the NCP106X drastically reduces the power wasted during light load conditions.

- **Ipeak set:** If current in range 26 μA and 285 μA is drawn from the pin, the peak current is proportionally reduced down to 40% of its original value. This feature enables to designer to set up the peak current to the value which is ideal for the application.

By routing a portion of the negative voltage present during the on-time on the auxiliary winding to the LIM/OPP pin, the user has a simple and non-dissipative means to alter the maximum peak current setpoint as the bulk voltage increases.

#### **Application Information**

#### **Startup Sequence**

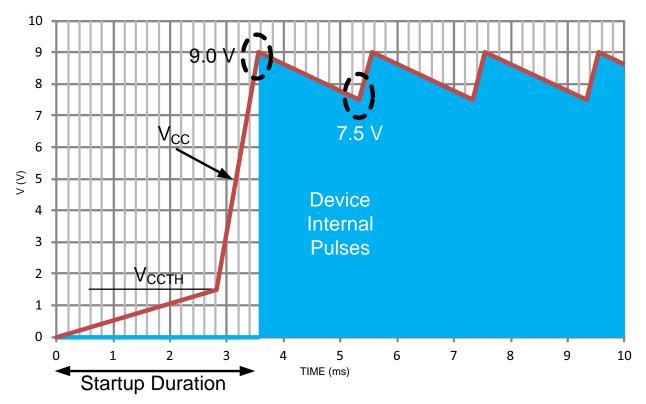

When the power supply is first powered from the mains outlet, the internal current source (typically 8.0 mA) is biased and charges up the  $V_{CC}$  capacitor from the drain pin. Once the voltage on this  $V_{CC}$  capacitor reaches the  $V_{CC(on)}$  level (typically 9.0 V), the current source turns off and

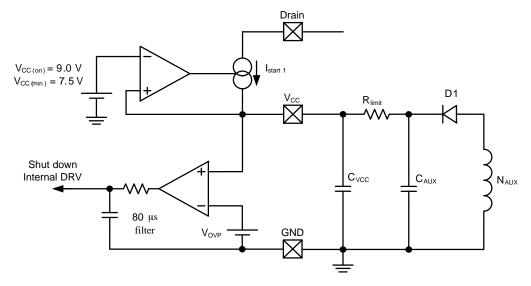

pulses are delivered by the output stage: the circuit is awake and activates the power MOSFET if the bulk voltage is above  $V_{HV(EN)}$  level (87 V typically) for A version and if bulk voltage is above  $V_{start(min)}$  (21 V dc) for B version. Figure 29 details the simplified internal circuitry.

Figure 29. The Internal Arrangement of the Start-up Circuitry

Being loaded by the circuit consumption, the voltage on the  $V_{CC}$  capacitor goes down. When  $V_{CC}$  is below  $V_{CC(min)}$  level (7.5 V typically), it activates the internal current source to bring  $V_{CC}$  toward  $V_{CC(on)}$  level and stops again: a cycle takes place whose low frequency depends on the  $V_{CC}$

capacitor and the IC consumption. A 1.5 V ripple takes place on the  $V_{CC}$  pin whose average value equals ( $V_{CC(on)} + V_{CC(min)}$ )/2. Figure 30 portrays a typical operation of the DSS

Figure 30. The Charge/Discharge Cycle Over a 1  $\mu F$  V<sub>CC</sub> Capacitor

As one can see, even if there is auxiliary winding to provide energy for  $V_{CC}$ , it happens that the device is still biased by DSS during start—up time or some fault mode when the voltage on auxiliary winding is not ready yet. The  $V_{CC}$  capacitor shall be dimensioned to avoid  $V_{CC}$  crosses  $V_{CC(off)}$  level, which stops operation. The  $\Delta V$  between  $V_{CC(min)}$  and  $V_{CC(off)}$  is 0.5 V. There is no current source to charge  $V_{CC}$  capacitor when driver is on, i.e. drain voltage is close to zero. Hence the  $V_{CC}$  capacitor can be calculated using

$$C_{VCC} \ge \frac{I_{CC1} \cdot D_{max}}{f_{OSC} \cdot \Delta V}$$

(eq. 1)

Take the  $60\ \text{kHz}$  device as an example.  $C_{VCC}$  should be above

$$\frac{0.8 \text{ m} \cdot 72\%}{54 \text{ kHz} \cdot 0.5} = 21 \text{ nF}.$$

A margin that covers the temperature drift and the voltage drop due to switching inside FET should be considered, and thus a capacitor above  $0.1~\mu F$  is appropriate.

The  $V_{CC}$  capacitor has only a supply role and its value does not impact other parameters such as fault duration or the frequency sweep period for instance. As one can see on Figure 29, an internal OVP comparator, protects the switcher against lethal  $V_{CC}$  runaways. This situation can occur if the feedback loop optocoupler fails, for instance, and you would like to protect the converter against an over voltage event. In that case, the over voltage protection (OVP) circuit and immediately stops the output pulses for

$t_{recovery}$  duration (400 ms typically). Then a new start-up attempt takes place to check whether the fault has disappeared or not. The OVP paragraph gives more design details on this particular section.

# Fault Condition - Short-circuit on V<sub>CC</sub>

In some fault situations, a short–circuit can purposely occur between  $V_{CC}$  and GND. In high line conditions ( $V_{HV} = 370~V_{DC}$ ) the current delivered by the startup device will seriously increase the junction temperature. For instance, since  $I_{start1}$  equals 5 mA (the min corresponds to the highest  $T_j$ ), the device would dissipate 370 x 5 m = 1.85 W. To avoid this situation, the controller includes a novel circuitry made of two startup levels,  $I_{start1}$  and  $I_{start2}$ . At power–up, as long as  $V_{CC}$  is below a 1.4 V level, the source delivers  $I_{start2}$  (around 500  $\mu$ A typical), then, when  $V_{CC}$  reaches 1.4 V, the source smoothly transitions to  $I_{start1}$  and delivers its nominal value. As a result, in case of short–circuit between  $V_{CC}$  and GND, the power dissipation will drop to 370 x 500  $\mu$  = 185 mW. Figure 30 portrays this particular behavior.

The first startup period is calculated by the formula C x V = I x t, which implies a 1  $\mu$  x 1.4 / 500  $\mu$  = 2.8 ms startup time for the first sequence. The second sequence is obtained by toggling the source to 8 mA with a delta V of  $V_{CC(on)}-V_{CCTH}=9.0-1.4=7.6$  V, which finally leads to a second startup time of 1  $\mu$  x 7.6 / 8 m = 0.95 ms. The total startup time becomes 2.8 m + 0.95 m = 3.75 ms. Please note that this calculation is approximated by the presence of the knee in the vicinity of the transition.

#### Fault Condition - Output Short-circuit

As soon as  $V_{CC}$  reaches  $V_{CC(on)}$ , drive pulses are internally enabled. If everything is correct, the auxiliary winding increases the voltage on the  $V_{CC}$  pin as the output voltage rises. During the start–sequence, the controller smoothly ramps up the peak drain current to maximum setting, i.e.  $I_{IPK}$ , which is reached after a typical period of 4 ms. When the output voltage is not regulated, the current coming through COMP pin is below  $I_{COMPfault}$  level (40  $\mu$ A typically), which is not only during the startup period but also anytime an overload occurs, an internal error flag is

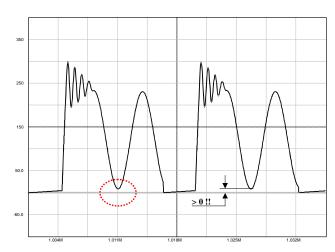

asserted, Ipflag, indicating that the system has reached its maximum current limit set point. The assertion of this flag triggers a fault counter t<sub>SCP</sub> (48 ms typically). If at counter completion, I<sub>pflag</sub> remains asserted, all driving pulses are stopped and the part stays off in t<sub>recovery</sub> duration (about 400 ms). A new attempt to re–start occurs and will last 48 ms providing the fault is still present. If the fault still affects the output, a safe burst mode is entered, affected by a low duty–cycle operation (11%). When the fault disappears, the power supply quickly resumes operation. Figure 31 depicts this particular mode:

Figure 31. In case of short-circuit or overload, the NCP106X protects itself and the power supply via a low frequency burst mode. The V<sub>CC</sub> is maintained by the current source and self-supplies the controller.

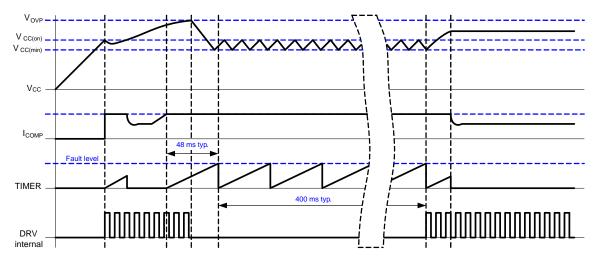

#### **Auto-recovery Over Voltage Protection**

The particular NCP106X arrangement offers a simple way to prevent output voltage runaway when the optocoupler fails. As Figure 32 shows, a comparator monitors the  $V_{CC}$  pin. If the auxiliary pushes too much voltage into the  $C_{VCC}$  capacitor, then the controller considers an OVP situation and stops the internal drivers. When an OVP occurs, all switching pulses are permanently disabled. After  $t_{recovery}$  delay, it resumes the internal drivers. If the failure symptom still exists, e.g. feedback opto—coupler fails, the device keeps the auto—recovery OVP mode. It is recommended insertion of a resistor ( $R_{limit}$ ) between the auxiliary dc level and the  $V_{CC}$  pin to protect the

IC against high voltage spikes, which can damage the IC, and to filter out the Vcc line to avoid undesired OVP activation.  $R_{limit}$  should be carefully selected to avoid triggering the OVP as we discussed, but also to avoid disturbing the  $V_{CC}$  in low / light load conditions.

Self–supplying controllers in extremely low standby applications often puzzles the designer. Actually, if a SMPS operated at nominal load can deliver an auxiliary voltage of an arbitrary 16 V ( $V_{nom}$ ), this voltage can drop below 10 V ( $V_{stby}$ ) when entering standby. This is because the recurrence of the switching pulses expands so much that the low frequency re–fueling rate of the  $V_{CC}$  capacitor is not enough to keep a proper auxiliary voltage.

Figure 32. A more detailed view of the NCP106X offers better insight on how to properly wire an auxiliary winding

Figure 33. describes the main signal variations when the part operates in auto-recovery OVP:

Figure 33: If the VCC current exceeds a certain threshold, an auto-recovery protection is activated.

#### Soft-start

The NCP106X features a 4 ms soft–start which reduces the power–on stress but also contributes to lower the output overshoot. Figure 34 shows a typical operating waveform. The NCP106X features a novel patented structure which offers a better soft–start ramp, almost ignoring the start–up pedestal inherent to traditional current–mode supplies.

Figure 34. The 4 ms Soft-start Sequence

#### **Jittering**

Frequency jittering is a method used to soften the EMI signature by spreading the energy in the vicinity of the main switching component. The NCP106X offers a  $\pm 6\%$  deviation of the nominal switching frequency. The sweep

sawtooth is internally generated and modulates the clock up and down with a fixed frequency of 300 Hz. Figure 35 shows the relationship between the jitter ramp and the frequency deviation. It is not possible to externally disable the jitter.

Figure 35. Modulation Effects on the Clock Signal by the Jittering Sawtooth

# Line Detection (for A version only)

An internal comparator monitors the drain voltage as recovering from one of the following situations:

- Short Circuit Protection,

- V<sub>CC</sub> OVP is confirmed,

- UVLO

- TSD

If the drain voltage is lower than the internal threshold  $V_{HV(EN)}$  (87 Vdc typically), the internal power switch is inhibited. This avoids operating at too low ac input.

#### Frequency Foldback

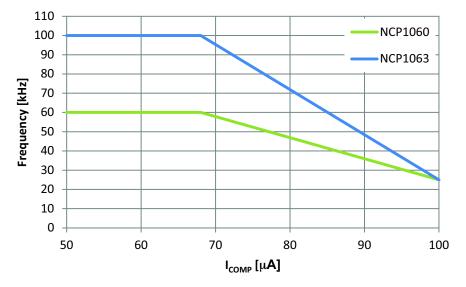

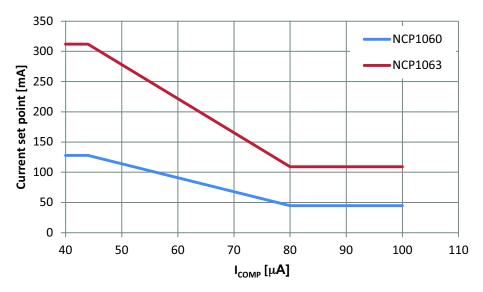

The reduction of no–load standby power associated with the need for improving the efficiency, requires to change the traditional fixed–frequency type of operation. This device implements a switching frequency foldback when the COMP current passes above a certain level,  $I_{COMPfold}$ , set around 68  $\mu A$ . At this point, the oscillator enters frequency foldback and reduces its switching frequency.

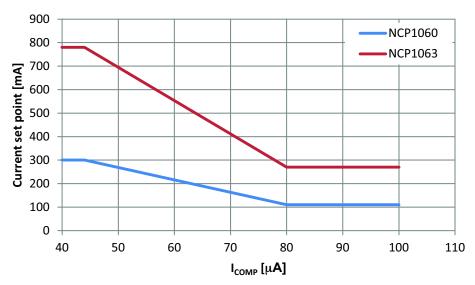

The internal peak current set-point is following the COMP current information until its level reaches  $I_{Freeze}$ .

Below this value, the peak current setpoint is frozen to 30% of the  $I_{PK(0)}.$  The only way to further reduce the transmitted power is to diminish the operating frequency down to  $F_{min}$  (25 kHz typically). This value is reached at a COMP current level of  $I_{COMPfold(end)}$  (100  $\mu A$  typically). Below this point, if the output power continues to decrease, the part enters skip cycle for the best noise–free performance in no–load conditions. Figure 36 and Figure 37 depict the adopted scheme for the part.

Figure 36. By observing the current on the COMP pin, the controller reduces its switching frequency for an improved performance at light load.

Figure 37. lpk set-point is frozen at lower power demand.

Figure 38. lpk set-point is frozen at lower power demand ( $I_{LMOP} \ge 285 \mu A$ )

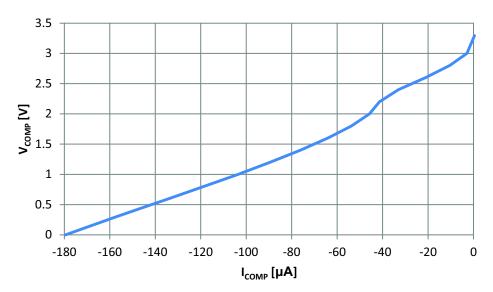

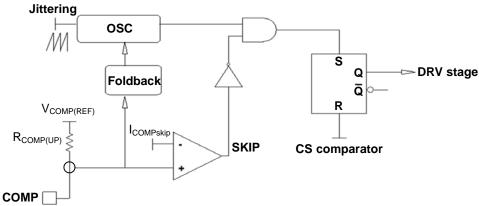

#### Feedback and Skip

Figure 39 depicts the relationship between COMP pin voltage and current. The COMP pin operates linearly as the absolute value of COMP current ( $I_{COMP}$ ) is above 40  $\mu A$ . In

this linear operating range, the dynamic resistance is 17.7 k $\Omega$  typically ( $R_{COMP(up)}$ ) and the effective pull up voltage is 2.7 V typically ( $V_{COMP(REF)}$ ). When  $I_{COMP}$  is decreases, the COMP voltage will increase to 3.2 V.

Figure 39. COMP Pin Voltage vs. Current

Figure 40 depicts the skip mode block diagram. When the COMP current information reaches I<sub>COMPskip</sub>, the internal clock setting the flip–flop is blanked and the internal consumption of the controller is decreased. The hysteresis of

internal skip comparator is minimized to lower the ripple of the auxiliary voltage for  $V_{CC}$  pin and  $V_{OUT}$  of power supply during skip mode. It easies the design of  $V_{CC}$  over load range.

Figure 40. Skip Cycle Schematic

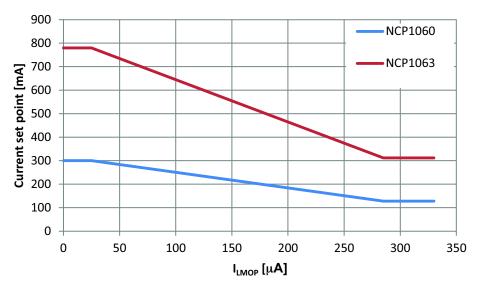

#### **Ilimit and OPP Function**

The function makes the integrated circuit more flexible. The current drawn out of LIM/OPP pin defines the current set point.

Figure 41. lpk set-point dependence on I<sub>LMOP</sub> current

There are several known ways to implement Over Power Protection (OPP), all suffering from particular problems. These problems range from the added consumption burden on the converter or the skip—cycle disturbance brought by the current—sense offset. A way to reduce the power capability at high line is to capitalize on the negative voltage swing present on the auxiliary diode anode. During the power switch on—time, this point dips to —NV<sub>in</sub>, N being the turns ratio between the primary winding and the auxiliary winding. The negative plateau on auxiliary winding will have an amplitude dependant on the input voltage. Resistors

R<sub>OPPU</sub> and R<sub>OPPL</sub> (Figure 42) define current drawn from LIM/OPP and the negative voltage on auxiliary winding. The negative voltage is tied up with bulk voltage, so the higher the bulk voltage is, the deeper is the negative voltage on auxiliary winding, the higher current is drawn from LIM/OPP pin and the lower the peak current is. During the internal MOSFET off period, voltage on auxiliary winding is positive, but the IC ignores the LIM/OPP current. The positive LIM/OPP current has no influence on proper IC function.

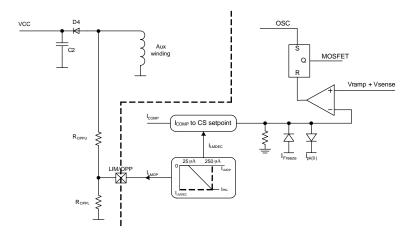

Figure 42. The OPP Circuitry Affects the Maximum Peak Current Set Point

#### Ramp Compensation and Ipk Set-point

In order to allow the NCP106X to operate in CCM with a duty cycle above 50%, a fixed slope compensation is internally applied to the current-mode control.

Here we got a table of the ramp compensation, the initial current set point, and the final current set—point of different versions of switcher.

|                               | NCP <sup>-</sup> | 1060     | NCP1063    |          |  |

|-------------------------------|------------------|----------|------------|----------|--|

| $f_{sw}$                      | 60 kHz           | 100 kHz  | 60 kHz     | 100 kHz  |  |

| Sa                            | 8.4 mA/μs        | 14 mA/μs | 15.6 mA/μs | 26 mA/μs |  |

| I <sub>pk(Duty</sub><br>=50%) | 250              | mA       | 650        | mA       |  |

| $I_{pk(0)}$                   | 300              | mA       | 780        | mA       |  |

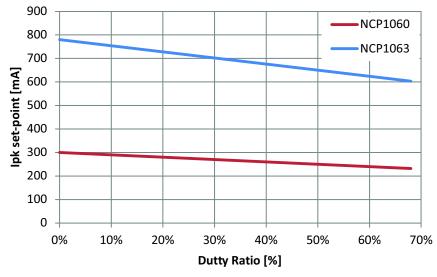

Figure 43 depicts the variation of I<sub>PK</sub> set–point vs. the power switcher duty ratio, which is caused by the internal ramp compensation.

Figure 43. IPK set-point varies with power switch on time, which is caused by the ramp compensation.

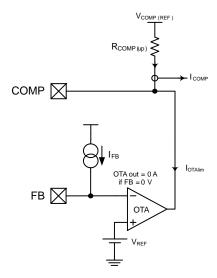

#### **FB Pin Function**

The FB pin is used in non isolated SMPS application only. Portion of the output voltage is connected into the pin. The voltage is compared with internal  $V_{REF}$  (3.3 V) using Operation Transconductance Amplifier (Figure 44). The OTAs output is connected to COMP pin. The OTA output is accessible through the COMP pin and is used for the loop compensation, usually an RC network. The current capability of OTA is limited to  $-150~\mu A$  typically. The

positive current is defined by internal  $R_{COMP(up)}$  resistor and  $V_{COMP(ref)}$  voltage. If FB path loop is broken (i.e. the FB pin is disconnected), an internal current  $I_{FB}$  (1  $\mu A$  typ.) will pull up the FB pin and the IC stops switching to avoid uncontrolled output voltage increasing.

In isolated topology, the FB pin should be connected to GND pin. In this configuration no current flows from OTA to COMP pin (OTA is disabled) so the OTA has no influence on regulation at all.

Figure 44. FB Pin Connection

#### **Design Procedure**

The design of an SMPS around a monolithic device does not differ from that of a standard circuit using a controller and a MOSFET. However, one needs to be aware of certain characteristics specific of monolithic devices. Let us follow the steps:

$V_{in} \min = 90 \text{ Vac or } 127 \text{ Vdc once rectified, assuming a low bulk ripple}$

$V_{in}$  max = 265 Vac or 375 Vdc

$V_{out} = 12 \text{ V}$

$P_{out} = 5 W$

Operating mode is CCM

$$\eta = 0.8$$

1. The lateral MOSFET body—diode shall never be forward biased, either during start—up (because of a large leakage inductance) or in normal operation as shown in Figure 45. This condition sets the maximum voltage that can be reflected during toff. As a result, the Flyback voltage which is reflected on the drain at the switch opening cannot be larger than the input voltage. When selecting components, you thus must adopt a turn ratio which adheres to the following equation:

$$N \cdot (V_{out} + V_f) < V_{in,min}$$

(eq. 2)

2. In our case, since we operate from a 127 V DC rail while delivering 12 V, we can select a reflected voltage of 120 V dc maximum. Therefore, the turn ratio Np:Ns must be smaller than

$$\frac{V_{reflect}}{V_{out} + V_f} = \frac{120}{12 + 0.5} = 9.6 \text{ or Np}: Ns < 9.6.$$

Here we choose N = 8 in this case. We will see later on how it affects the calculation.

Figure 45. The Drain-Source Wave Shall Always be Positive

Figure 46. Primary Inductance Current Evolution in CCM

3. Lateral MOSFETs have a poorly doped body-diode which naturally limits their ability to sustain the avalanche. A traditional RCD clamping network shall thus be installed to protect the MOSFET. In some low power applications, a simple capacitor can also be used since

$$V_{drain,max} = V_{in} + N \cdot \left(V_{out} + V_{f}\right) + I_{peak} \cdot \sqrt{\frac{L_{f}}{C_{tot}}} \text{ (eq. 3)}$$

where  $L_f$  is the leakage inductance,  $C_{tot}$  the total capacitance at the drain node (which is increased by the capacitor you will wire between drain and source), N the  $N_P:N_S$  turn ratio,  $V_{out}$  the output voltage,  $V_f$  the secondary diode forward drop and finally,  $I_{peak}$  the maximum peak current. Worse case occurs when the SMPS is very close to regulation, e.g. the  $V_{out}$  target is almost reached and  $I_{peak}$  is still pushed to the maximum. For this design, we have selected our maximum voltage around 650 V (at  $V_{in}$  = 375 Vdc). This voltage is given by the RCD clamp installed from the drain to the bulk voltage. We will see how to calculate it later on.

4. Calculate the maximum operating duty-cycle for this flyback converter operated in CCM:

$$\begin{split} d_{max} &= \frac{N \cdot \left(V_{out} \cdot V_{f}\right)}{N \cdot \left(V_{out} \cdot V_{f}\right) + V_{in,min}} \\ &= \frac{1}{1 + \frac{V_{in,min}}{N \cdot \left(V_{out} \cdot V_{f}\right)}} = 0.44 \end{split} \tag{eq. 4}$$

5. To obtain the primary inductance, we have the choice between two equations:

$$L = \frac{\left(V_{\text{in}} \cdot d\right)^2}{f_{\text{SW}} \cdot K \cdot P_{\text{in}}}$$

(eq. 5)

where

$$K = \frac{\Delta I_L}{I_{Lavg}}$$

and defines the amount of ripple we want in CCM (see Figure 46).

- Small K: deep CCM, implying a large primary inductance, a low bandwidth and a large leakage inductance.

- Large K: approaching DCM where the RMS losses are worse, but smaller inductance, leading to a better leakage inductance.

From Equation 6, a *K* factor of 1 (50% ripple), gives an inductance of:

$$L = \frac{(127 \cdot 0.44)^2}{60k \cdot 1 \cdot 5} = 10.04 \text{ mH}$$

$$\Delta I_L = \frac{V_{\text{in}} \cdot d}{L \cdot f_{\text{SW}}} = \frac{127 \cdot 0.44}{10.04 \text{m} \cdot 60k} = 92.8 \text{ mA peak to peak}$$

The peak current can be evaluated to be:

$$I_{peak} = \frac{I_{avg}}{d} + \frac{\Delta I_L}{2} = \frac{49.2 \text{ m}}{0.44} + \frac{92.8 \text{ m}}{2} = 158 \text{ mA}$$

On I<sub>L</sub>, I<sub>Lavg</sub> can also be calculated:

$$I_{Lavg} = I_{peak} - \frac{\Delta I_{L}}{2} = 158m - \frac{92.8m}{2} = 111.6 \text{ mA}$$

6. Based on the above numbers, we can now evaluate the conduction losses:

$$I_{d,rms} = \sqrt{d \cdot \left(I_{peak}^{2} - I_{peak} \cdot \Delta I_{L} + \frac{\Delta I_{L}^{2}}{3}\right)}$$

$$= \sqrt{0.44 \cdot \left(0.158^{2} - 0.158 \cdot 0.0928 + \frac{0.0928^{2}}{3}\right)}$$

$$= 57 \text{ mA}$$

If we take the maximum  $R_{DS(on)}$  for a 125°C junction temperature, i.e. 34  $\Omega$ , then conduction losses worse case are:

$$P_{cond} = I_{d,rms}^{2} \cdot R_{DS(on)} = 110 \text{ mW}$$

7. Off-time and on-time switching losses can be estimated based on the following calculations:

$$P_{off} = \frac{I_{peak} \cdot \left(V_{bulk} + V_{clamp}\right) \cdot t_{off}}{2T_{SW}}$$

$$= \frac{0.158 \cdot (127 + 100 \cdot 2) \cdot 10n}{2 \cdot 16.7 \,\mu}$$

$$= 15.5 \,\text{mW}$$

(eq. 6)

Where, assume the  $V_{clamp}$  is equal to 2 times of reflected voltage.

$$\begin{split} P_{on} &= \frac{I_{valley} \cdot \left(V_{bulk} + N \cdot (V_{out} + V_{f})\right) \cdot t_{on}}{6 \cdot T_{SW}} \\ &= \frac{0.0464 \cdot (127 + 100) \cdot 10 \text{ n}}{6 \cdot 16.7 \text{ }\mu} \\ &= 2.1 \text{ mW} \end{split}$$

It is noted that the overlap of voltage and current seen on MOSFET during turning on and off duration is dependent on the snubber and parasitic capacitance seen from drain pin. Therefore the t<sub>off</sub> and t<sub>on</sub> in Equation 7 and Equation 8 have to be modified after measuring on the bench.

8. The theoretical total power is then

$$117 + 15.5 + 2.1 = 127.6 \text{ mW}$$

If the NCP106X operates at DSS mode, then the losses caused by DSS mode should be counted as losses of this device on the following calculation:

$$P_{DSS} = I_{CC1} \cdot V_{in,max} = 0.8 \text{m} \cdot 375 = 300 \text{ mW (eq. 8)}$$

#### **MOSFET Protection**

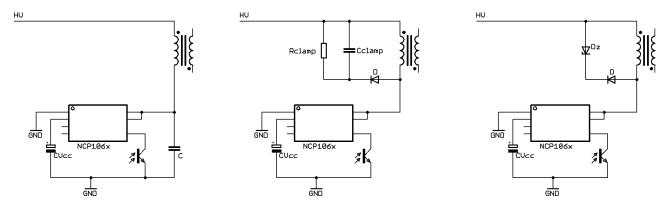

As in any Flyback design, it is important to limit the drain excursion to a safe value, e.g. below the MOSFET BVdss which is 700 V. Figure 47 **a–b–c** present possible implementations:

Figure 47. a, b, c : Different Options to Clamp the Leakage Spike

Figure 47a: the simple capacitor limits the voltage according to the lateral MOSFET body–diode shall never be forward biased, either during start–up (because of a large leakage inductance) or in normal operation as shown by Figure 45. This condition sets the maximum voltage that can be reflected during t<sub>off</sub>. As a result, the flyback voltage which is reflected on the drain at the switch opening cannot be larger than the input voltage. When selecting components, you must adopt a turn ratio which adheres to the following Equation 3. This option is only valid for low power applications, e.g. below 5 W, otherwise chances exist to destroy the MOSFET. After evaluating the leakage inductance, you can compute C with (Equation 4). Typical values are between 100 pF and up to 470 pF. Large capacitors increase capacitive losses...

Figure 47b: the most standard circuitry is called the RCD network. You calculate  $R_{clamp}$  and  $C_{clamp}$  using the following formulae:

$$\begin{split} R_{clamp} &= \frac{2 \cdot V_{clamp} \cdot \left(V_{clamp} + N \cdot (V_{out} + V_{f})\right)}{L_{leak} \cdot I_{leak}^{2} \cdot f_{sw}} \text{ (eq. 9)} \\ C_{clamp} &= \frac{V_{clamp}}{V_{ripple} \cdot f_{sw} \cdot R_{clamp}} \end{split}$$

$V_{clamp}$  is usually selected 50–80 V above the reflected value N x (V\_{out}+V\_f). The diode needs to be a fast one and

a MUR160 represents a good choice. One major drawback of the RCD network lies in its dependency upon the peak current. Worse case occurs when  $I_{peak}$  and  $V_{in}$  are maximum and  $V_{out}$  is close to reach the steady–state value.

Figure 47c: this option is probably the most expensive of all three but it offers the best protection degree. If you need a very precise clamping level, you must implement a zener diode or a TVS. There are little technology differences behind a standard zener diode and a TVS. However, the die area is far bigger for a transient suppressor than that of zener. A 5 W zener diode like the 1N5388B will accept 180 W peak power if it lasts less than 8.3 ms. If the peak current in the worse case (e.g. when the PWM circuit maximum current limit works) multiplied by the nominal zener voltage exceeds these 180 W, then the diode will be destroyed when the supply experiences overloads. A transient suppressor like the P6KE200 still dissipates 5 W of continuous power but is able to accept surges up to 600 W @ 1 ms. Select the zener or TVS clamping level between 40 to 80 volts above the reflected output voltage when the supply is heavily loaded.

As a good design practice, it is recommended to implement one of this protection to make sure Drain pin voltage doesn't go above 650 V (to have some margin between Drain pin voltage and BVdss) during most stringent operating conditions (high Vin and peak power).

#### **Power Dissipation and Heatsinking**

The NCP106X welcomes two dissipating terms, the DSS current–source (when active) and the MOSFET. Thus,  $P_{tot} = P_{DSS} + P_{MOSFET}$ . It is mandatory to properly manage the heat generated by losses. If no precaution is taken, risks exist to trigger the internal thermal shutdown (TSD). To help dissipating the heat, the PCB designer must foresee large copper areas around the package. Take the PDIP–7 package as an example, when surrounded by a surface approximately  $200~\text{mm}^2$  of  $35~\mu\text{m}$  copper, the maximum power the device can thus evacuate is:

$$P_{\text{max}} = \frac{T_{\text{Jmax}} - T_{\text{ambmax}}}{R_{\text{ftJA}}}$$

(eq. 10)

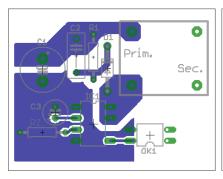

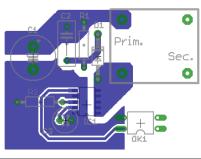

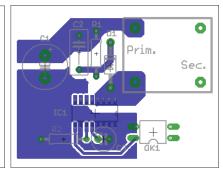

which gives around 870 mW for an ambient of  $50^{\circ}$ C and a maximum junction of  $150^{\circ}$ C. If the surface is not large enough, the  $R_{\theta JA}$  is growing and the maximum power the device can evacuate decreases. Figure 48 gives a possible layout to help drop the thermal resistance.

Figure 48. A Possible PCB Arrangement to Reduce the Thermal Resistance Junction-to-Ambient

#### Bill of material:

C1 Bulk capacitor, input DC voltage is connected to the capacitor

C2, R1, D1 Clamping elements

C3 Vcc capacitor

OK1 Optocoupler

R2 Resistor to setting I<sub>PEAK</sub> current

**Table 4. ORDERING INFORMATION**

| Device          | Frequency | R <sub>DS(on)</sub> | Brown In | Package Type | Shipping           |

|-----------------|-----------|---------------------|----------|--------------|--------------------|

| NCP1060AP060G   | 60 kHz    | 34                  | Yes      | PDIP-7       | 50 Units / Rail    |

| NCP1060AP100G   | 100 kHz   | 34                  | Yes      | (Pb-Free)    | 50 Units / Rail    |

| NCP1060AD060R2G | 60 kHz    | 34                  | Yes      |              | 2500 / Tape & Reel |

| NCP1060AD100R2G | 100 kHz   | 34                  | Yes      | SOIC-10      | 2500 / Tape & Reel |

| NCP1060BD060R2G | 60 kHz    | 34                  | No       | (Pb-Free)    | 2500 / Tape & Reel |

| NCP1060BD100R2G | 100 kHz   | 34                  | No       |              | 2500 / Tape & Reel |

| NCP1063AP060G   | 60 kHz    | 11.4                | Yes      | PDIP-7       | 50 Units / Rail    |

| NCP1063AP100G   | 100 kHz   | 11.4                | Yes      | (Pb-Free)    | 50 Units / Rail    |

| NCP1063AD060R2G | 60 kHz    | 11.4                | Yes      | SOIC-16      | 2500 / Tape & Reel |

| NCP1063AD100R2G | 100 kHz   | 11.4                | Yes      | (Pb-Free)    | 2500 / Tape & Reel |

#### PACKAGE DIMENSIONS

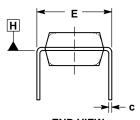

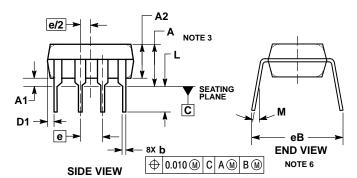

# PDIP-7 (PDIP-8 LESS PIN 6)

CASE 626A **ISSUE B**

END VIEW WITH LEADS CONSTRAINED NOTE 5

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: INCHES.

3. DIMENSIONS A, A1 AND L ARE MEASURED WITH THE PACKAGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3.

4. DIMENSIONS D, D1 AND E1 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS ARE NOT TO EXCEED 0.10 INCH.

5. DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR TO DATUM C. TO DATUM C.

6. DIMENSION E3 IS MEASURED AT THE LEAD TIPS WITH THE

- 6. DIMENSION E3 IS MEASURED AT THE LEAD TIFS WITH THE LEADS UNCONSTRAINED.

7. DATUM PLANE H IS COINCIDENT WITH THE BOTTOM OF THE LEADS, WHERE THE LEADS EXIT THE BODY.

8. PACKAGE CONTOUR IS OPTIONAL (ROUNDED OR SQUARE CONTOUR TO THE PROPERTY OF THE PROPE

|     | INC         | HES   | MILLIM | ETERS |

|-----|-------------|-------|--------|-------|

| DIM | MIN         | MAX   | MIN    | MAX   |

| Α   |             | 0.210 |        | 5.33  |

| A1  | 0.015       |       | 0.38   |       |

| A2  | 0.115       | 0.195 | 2.92   | 4.95  |

| b   | 0.014       | 0.022 | 0.35   | 0.56  |

| b2  | 0.060 TYP 1 |       | 1.52   | TYP   |

| С   | 0.008       | 0.014 | 0.20   | 0.36  |

| D   | 0.355       | 0.400 | 9.02   | 10.16 |

| D1  | 0.005       |       | 0.13   | -     |

| E   | 0.300       | 0.325 | 7.62   | 8.26  |

| E1  | 0.240       | 0.280 | 6.10   | 7.11  |

| е   | 0.100       | BSC   | 2.54   | BSC   |

| eВ  |             | 0.430 |        | 10.92 |

| L   | 0.115       | 0.150 | 2.92   | 3.81  |

| М   |             | 10°   |        | 10°   |

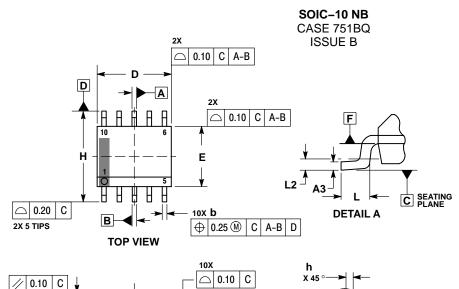

## PACKAGE DIMENSIONS

Ċ

SIDE VIEW

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- ASJME 114-SW, 1894.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.10mm TOTAL IN EXCESS OF 'b' AT MAXIMUM MATERIAL CONDITION.

DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15mm PER SIDE. DIMENSIONS D AND E ARE DETERMINED AT DATUM F.

DIMENSIONS A AND B ARE TO BE DETERMINED AT DATUM F.

A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 1.25        | 1.75  |  |  |

| A1  | 0.10        | 0.25  |  |  |

| A3  | 0.17        | 0.25  |  |  |

| b   | 0.31        | 0.51  |  |  |

| D   | 4.80        | 5.00  |  |  |

| E   | 3.80        | 4.00  |  |  |

| е   | 1.00        | BSC   |  |  |

| Н   | 5.80        | 6.20  |  |  |

| h   | 0.37        | 7 REF |  |  |

| L   | 0.40        | 0.80  |  |  |

| L2  | 0.25        | BSC   |  |  |

| D.A | n°          | ο °   |  |  |

# SEATING PLANE **END VIEW RECOMMENDED**

DETAIL A

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

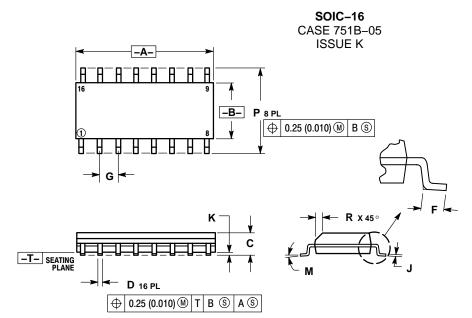

#### PACKAGE DIMENSIONS

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INC       | HES   |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 9.80   | 10.00  | 0.386     | 0.393 |  |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |  |

| С   | 1.35   | 1.75   | 0.054     | 0.068 |  |

| D   | 0.35   | 0.49   | 0.014     | 0.019 |  |

| F   | 0.40   | 1.25   | 0.016     | 0.049 |  |

| G   | 1.27   | BSC    | 0.050 BSC |       |  |

| J   | 0.19   | 0.25   | 0.008     | 0.009 |  |

| K   | 0.10   | 0.25   | 0.004     | 0.009 |  |

| M   | 0°     | 7°     | 0°        | 7°    |  |

| Р   | 5.80   | 6.20   | 0.229     | 0.244 |  |

| R   | 0.25   | 0.50   | 0.010     | 0.019 |  |

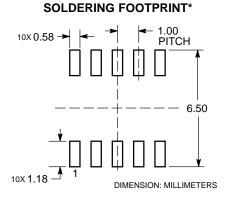

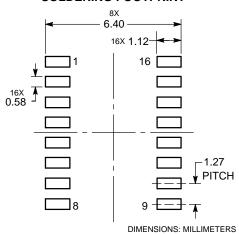

#### **SOLDERING FOOTPRINT**

ON Semiconductor and the (III) are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC date seets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim

alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

## Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;