# High Speed, Video Difference Amplifier

# AD830

#### FEATURES

**Differential amplification** Wide common-mode voltage range: +12.8 V to -12 V Differential voltage: ±2 V High CMRR: 60 dB at 4 MHz Built-in differential clipping level: ±2.3 V Fast dynamic performance 85 MHz unity gain bandwidth 35 ns settling time to 0.1% 360 V/µs slew rate Symmetrical dynamic response **Excellent video specifications** Differential gain error: 0.06% Differential phase error: 0.08° 15 MHz (0.1 dB) bandwidth **Flexible operation** High output drive of ±50 mA min Specified with both ±5 V and ±15 V supplies Low distortion: THD = -72 dB @ 4 MHz Excellent DC performance: 3 mV max input **Offset voltage**

#### APPLICATIONS

Differential line receiver High speed level shifter High speed in-amp Differential to single-ended conversion Resistorless summation and subtraction High speed analog-to-digital converter

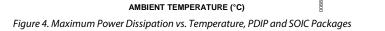

#### **GENERAL DESCRIPTION**

The AD830 is a wideband, differencing amplifier designed for use at video frequencies but also useful in many other applications. It accurately amplifies a fully differential signal at the input and produces an output voltage referred to a user-chosen level. The undesired common-mode signal is rejected, even at high frequencies. High impedance inputs ease interfacing to finite source impedances and, thus, preserve the excellent commonmode rejection. In many respects, it offers significant improvements over discrete difference amplifier approaches, in particular in high frequency common-mode rejection.

The wide common-mode and differential voltage range of the AD830 make it particularly useful and flexible in level shifting applications but at lower power dissipation than discrete solutions. Low distortion is preserved over the many possible differential and common-mode voltages at the input and output.

#### Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

Figure 1. 8-Lead Plastic PDIP (N), CERDIP (Q), and SOIC (RN) Packages

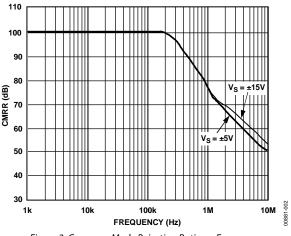

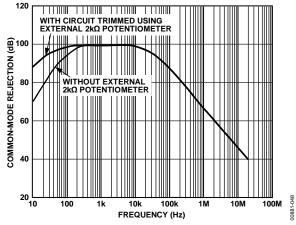

Figure 2. Common-Mode Rejection Ratio vs. Frequency

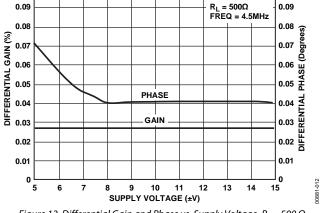

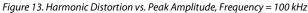

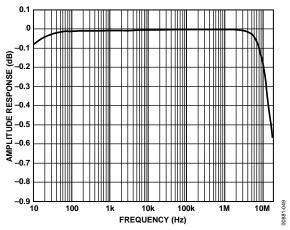

Good gain flatness and excellent differential gain of 0.06% and phase of 0.08° make the AD830 suitable for many video system applications. Furthermore, the AD830 is suited for general-purpose signal processing from dc to 10 MHz.

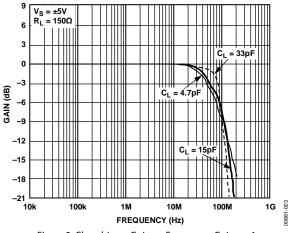

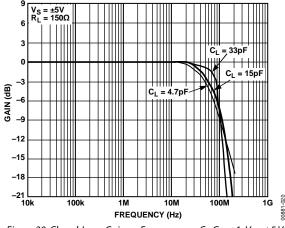

Figure 3. Closed-Loop Gain vs. Frequency, Gain = +1

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2005-2010 Analog Devices, Inc. All rights reserved.

## TABLE OF CONTENTS

| Features                            | 1 |

|-------------------------------------|---|

| Applications                        | 1 |

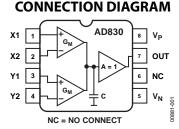

| Connection Diagram                  | 1 |

| General Description                 | 1 |

| Revision History                    | 2 |

| Specifications                      | 3 |

| Absolute Maximum Ratings            | 7 |

| Maximum Power Dissipation           | 7 |

| Thermal Resistance                  | 7 |

| ESD Caution                         | 7 |

| Typical Performance Characteristics | 8 |

#### **REVISION HISTORY**

#### 3/10-Rev. B to Rev. C

| Updated Format             | Universal |

|----------------------------|-----------|

| Changes to Ordering Guide  |           |

| 1/03—Rev. A to Rev. B.     |           |

| Updated Ordering Guide     |           |

| Change to Figure 30        |           |

| Updated Outline Dimensions | 15        |

| Theory of Operation 11                           |

|--------------------------------------------------|

| Traditional Differential Amplification11         |

| Problems With the Op Amp Based Approach11        |

| AD830 for Differential Amplification11           |

| Advantageous Properties of the AD83011           |

| Understanding the AD830 Topology11               |

| Interfacing the Input 12                         |

| Supplies, Bypassing, and Grounding (Figure 34)14 |

| AC-Coupled Line Receiver17                       |

| Outline Dimensions                               |

| Ordering Guide                                   |

### **SPECIFICATIONS**

$V_{\text{S}}=\pm15$  V,  $R_{\text{LOAD}}=150~\Omega,$   $C_{\text{LOAD}}=5$  pF,  $T_{\text{A}}=25^{\circ}C$  , unless otherwise noted.

#### Table 1.

|                                          |                                                   | AD830J/AD830A                         |             |       |       | AD830S <sup>1</sup> |       |         |

|------------------------------------------|---------------------------------------------------|---------------------------------------|-------------|-------|-------|---------------------|-------|---------|

| Parameter                                | Conditions                                        | Min                                   | Тур         | Max   | Min   | Тур                 | Max   | Unit    |

| DYNAMIC CHARACTERISTICS                  |                                                   |                                       |             |       |       |                     |       |         |

| 3 dB Small Signal Bandwidth              | $Gain = +1$ , $V_{OUT} = 100 \text{ mV rms}$      | 75                                    | 85          |       | 75    | 85                  |       | MHz     |

| 0.1 dB Gain Flatness<br>Frequency        | $Gain = +1, V_{OUT} = 100 \text{ mV rms}$         | 11                                    | 15          |       | 11    | 15                  |       | MHz     |

| Differential Gain Error                  | 0 V to 0.7 V, frequency =<br>4.5 MHz              |                                       | 0.06        | 0.09  |       | 0.06                | 0.09  | %       |

| Differential Phase Error                 | 0 V to 0.7 V, frequency =<br>4.5 MHz              |                                       | 0.08        | 0.12  |       | 0.08                | 0.12  | Degrees |

| Slew Rate                                | 2 V step, $R_L = 500 \Omega$                      |                                       | 360         |       |       | 360                 |       | V/µs    |

|                                          | 4 V step, $R_L = 500 \Omega$                      |                                       | 350         |       |       | 350                 |       | V/µs    |

| 3 dB Large Signal Bandwidth              | $Gain = +1, V_{OUT} = 1 V rms$                    | 38                                    | 45          |       | 38    | 45                  |       | MHz     |

| Settling Time, Gain = +1                 | $V_{OUT} = 2 V$ step, to 0.1%                     |                                       | 25          |       |       | 25                  |       | ns      |

|                                          | $V_{OUT} = 4 V$ step, to 0.1%                     |                                       | 35          |       |       | 35                  |       | ns      |

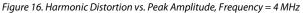

| Harmonic Distortion                      | 2 V p-p, frequency = 1 MHz                        |                                       | -82         |       |       | -82                 |       | dBc     |

|                                          | 2 V p-p, frequency = 4 MHz                        |                                       | -72         |       |       | -72                 |       | dBc     |

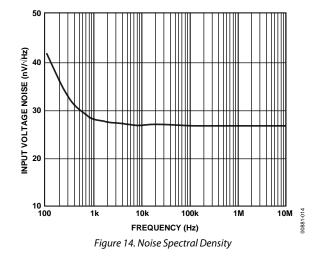

| Input Voltage Noise                      | frequency = 10 kHz                                |                                       | 27          |       |       | 27                  |       | nV/√Hz  |

| Input Current Noise                      |                                                   |                                       | 1.4         |       |       | 1.4                 |       | pA/√Hz  |

| DC PERFORMANCE                           |                                                   |                                       |             |       |       |                     |       | -       |

| Offset Voltage                           | Gain = +1                                         |                                       | ±1.5        | ±3    |       | ±1.5                | ±3    | mV      |

| 5                                        | $Gain = +1, T_{MIN} - T_{MAX}$                    |                                       |             | ±5    |       |                     | ±7    | mV      |

| Open-Loop Gain                           | DC                                                | 64                                    | 69          | -     | 64    | 69                  |       | dB      |

| Gain Error                               | $R_L = 1 k\Omega, G = \pm 1$                      |                                       | ±0.1        | ±0.6  |       | ±0.1                | ±0.6  | %       |

| Peak Nonlinearity, $R_L = 1 \ k\Omega$ , | $-1 V \le X \le +1 V$                             |                                       | 0.01        | 0.03  |       | 0.01                | 0.03  | % FS    |

| Gain = +1                                | $-1.5 V \le X \le +1.5 V$                         |                                       | 0.035       | 0.07  |       | 0.035               | 0.07  | % FS    |

|                                          | $-2 V \le X \le +2 V$                             |                                       | 0.15        | 0.4   |       | 0.15                | 0.4   | % FS    |

| Input Bias Current                       | $V_{IN} = 0 V$ , 25°C to $T_{MAX}$                |                                       | 5           | 10    |       | 5                   | 10    | μA      |

|                                          | $V_{IN} = 0 V, T_{MIN}$                           |                                       | 7           | 13    |       | 8                   | 17    | μA      |

| Input Offset Current                     | $V_{IN} = 0 V$ , $T_{MIN} - T_{MAX}$              |                                       | 0.1         | 1     |       | 0.1                 | 1     | μA      |

| INPUT CHARACTERISTICS                    |                                                   |                                       |             |       |       |                     |       |         |

| Differential Voltage Range               | V <sub>CM</sub> = 0                               |                                       | ±2.0        |       |       | ±2.0                |       | v       |

| Differential Clipping Level <sup>2</sup> | Pin 1 and Pin 2 inputs only                       | ±2.1                                  | ±2.3        |       | ±2.1  | ±2.3                |       | v       |

| Common-Mode Voltage<br>Range             | $V_{DM} = \pm 1 V$                                | -12.0                                 |             | +12.8 | -12.0 |                     | +12.8 | v       |

| CMRR                                     | DC, Pin 1/Pin 2, ±10 V<br>DC, Pin 1/Pin 2, ±10 V, | 90                                    | 100         |       | 90    | 100                 |       | dB      |

|                                          | $T_{MIN} - T_{MAX}$                               | 88                                    |             |       | 86    |                     |       | dB      |

|                                          | Frequency = 4 MHz                                 | 55                                    | 60          |       | 55    | 60                  |       | dB      |

| Input Resistance                         |                                                   |                                       | 370         |       |       | 370                 |       | kΩ      |

| Input Capacitance                        |                                                   |                                       | 2           |       |       | 2                   |       | pF      |

| OUTPUT CHARACTERISTICS                   |                                                   |                                       |             |       |       |                     |       | P.      |

| Output Voltage Swing                     | $R_L \ge 1 k\Omega$                               | ±12                                   | +13.8/-13.8 |       | ±12   | +13.8/-13.8         |       | v       |

| e apartonage offing                      | $R_L \ge 1 \ k\Omega, \pm 16.5 \ V_S$             | ±12                                   | +15.3/-14.7 |       | ±13   | +15.3/-14.7         |       | v       |

|                                          | Short to ground                                   | , , , , , , , , , , , , , , , , , , , | ±80         |       | - 1 J | ±80                 |       | mA      |

| Short-Circuit Current                    | Short to dround                                   |                                       |             |       |       |                     |       |         |

|                            |                                                |     | AD830J/AD830A |       |     | AD83051 |       |      |

|----------------------------|------------------------------------------------|-----|---------------|-------|-----|---------|-------|------|

| Parameter                  | Conditions                                     | Min | Тур           | Мах   | Min | Тур     | Max   | Unit |

| POWER SUPPLIES             |                                                |     |               |       |     |         |       |      |

| Operating Range            |                                                | ±4  |               | ±16.5 | ± 4 |         | ±16.5 | V    |

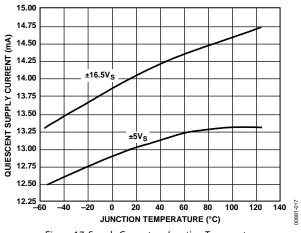

| Quiescent Current          | $T_{MIN} - T_{MAX}$                            |     | 14.5          | 17    |     | 14.5    | 17    | mA   |

| +PSRR (to V <sub>P</sub> ) | DC, G = +1                                     |     | 86            |       |     | 86      |       | dB   |

| -PSRR (to V <sub>N</sub> ) | DC, G = +1                                     |     | 68            |       |     | 68      |       | dB   |

| PSRR                       | DC, G = $+1$ , $\pm 5$ to $\pm 15$ Vs          | 66  | 71            |       | 66  | 71      |       | dB   |

| PSRR                       | DC, G = +1, $\pm 5$ to $\pm 15$ V <sub>s</sub> |     |               |       |     |         |       |      |

|                            | T <sub>MIN</sub> – T <sub>MAX</sub>            | 62  | 68            |       | 60  | 68      |       | dB   |

<sup>1</sup> See the Standard Military Drawing 5962-9313001MPA for specifications.

<sup>2</sup> Clipping level function on X channel only.

$V_{\text{S}}=\pm5$  V,  $R_{\text{LOAD}}=150~\Omega,$   $C_{\text{LOAD}}=5$  pF,  $T_{\text{A}}=+25^{\circ}C$  , unless otherwise noted.

#### Table 2.

|                                          |                                              | A    | D830J/AD83 | BOA  | AD83051 |           |      |         |

|------------------------------------------|----------------------------------------------|------|------------|------|---------|-----------|------|---------|

| Parameter                                | Conditions                                   | Min  | Тур        | Max  | Min     | Тур       | Max  | Units   |

| DYNAMIC CHARACTERISTICS                  |                                              |      |            |      |         |           |      |         |

| 3 dB Small Signal Bandwidth              | $Gain = +1$ , $V_{OUT} = 100 \text{ mV rms}$ | 35   | 40         |      | 35      | 40        |      | MHz     |

| 0.1 dB Gain Flatness Frequency           | $Gain = +1$ , $V_{OUT} = 100 \text{ mV rms}$ | 5    | 6.5        |      | 5       | 6.5       |      | MHz     |

| Differential Gain Error                  | 0 V to 0.7 V, frequency = 4.5 MHz,           |      |            |      |         |           |      |         |

|                                          | Gain = +2                                    |      | 0.14       | 0.18 |         | 0.14      | 0.18 | %       |

| Differential Phase Error                 | 0 V to 0.7 V, frequency = 4.5 MHz,           |      |            |      |         |           |      |         |

|                                          | Gain = +2                                    |      | 0.32       | 0.4  |         | 0.32      | 0.4  | Degrees |

| Slew Rate, Gain $= +1$                   | 2 V step, $R_L = 500 \Omega$                 |      | 210        |      |         | 210       |      | V/µs    |

|                                          | 4 V step, $R_L = 500 \Omega$                 |      | 240        |      |         | 240       |      | V/µs    |

| 3 dB Large Signal Bandwidth              | Gain = $+1$ , V <sub>OUT</sub> = 1 V rms     | 30   | 36         |      | 30      | 36        |      | MHz     |

| Settling Time                            | $V_{OUT} = 2 V$ step, to 0.1%                |      | 35         |      |         | 35        |      | ns      |

|                                          | $V_{OUT} = 4 V$ step, to 0.1%                |      | 48         |      |         | 48        |      | ns      |

| Harmonic Distortion                      | 2 V p-p, frequency = 1 MHz                   |      | -69        |      |         | -69       |      | dBc     |

|                                          | 2 V p-p, frequency = 4 MHz                   |      | -56        |      |         | -56       |      | dBc     |

| Input Voltage Noise                      | Frequency = 10 kHz                           |      | 27         |      |         | 27        |      | nV/√Hz  |

| Input Current Noise                      |                                              |      | 1.4        |      |         | 1.4       |      | pA/√Hz  |

| DC PERFORMANCE                           |                                              |      |            |      |         |           |      |         |

| Offset Voltage                           | Gain = +1                                    |      | ±1.5       | ±3   |         | ±1.5      | ±3   | mV      |

|                                          | $Gain = +1, T_{MIN} - T_{MAX}$               |      |            | ±4   |         |           | ±5   | mV      |

| Open-Loop Gain                           | DC                                           | 60   | 65         |      | 60      | 65        |      | dB      |

| Unity Gain Accuracy                      | $R_L = 1 \ k\Omega$                          |      | ±0.1       | ±0.6 |         | ±0.1      | ±0.6 | %       |

| Peak Nonlinearity, R∟= 1 kΩ              | $-1 V \le X \le +1 V$                        |      | 0.01       | 0.03 |         | 0.01      | 0.03 | % FS    |

|                                          | $-1.5 V \le X \le +1.5 V$                    |      | 0.045      | 0.07 |         | 0.045     | 0.07 | % FS    |

|                                          | $-2 V \le X \le +2 V$                        |      | 0.23       | 0.4  |         | 0.23      | 0.4  | % FS    |

| Input Bias Current                       | $V_{IN} = 0 V$ , 25°C to $T_{MAX}$           |      | 5          | 10   |         | 5         | 10   | μΑ      |

|                                          | $V_{IN} = 0 V, T_{MIN}$                      |      | 7          | 13   |         | 8         | 17   | μΑ      |

| Input Offset Current                     | $V_{IN} = 0 \text{ V}, T_{MIN} - T_{MAX}$    |      | 0.1        | 1    |         | 0.1       | 1    | μA      |

| INPUT CHARACTERISTICS                    |                                              |      |            |      |         |           |      |         |

| Differential Voltage Range               | $V_{CM} = 0$                                 |      | ±2.0       |      |         | ±2.0      |      | V       |

| Differential Clipping Level <sup>2</sup> | Pin 1 and Pin 2 inputs only                  | ±2.0 | ±2.2       |      | ±2.0    | ±2.2      |      | V       |

| Common-Mode Voltage Range                | $V_{DM} = \pm 1 V$                           | -2.0 |            | +2.9 | -2.0    |           | +2.9 | V       |

| CMRR                                     | DC, Pin 1/Pin 2, +4 V to -2 V                | 90   | 100        |      | 90      | 100       |      | dB      |

|                                          | DC, Pin 1/Pin 2, +4 V to –2 V,               |      |            |      |         |           |      |         |

|                                          | T <sub>MIN</sub> - T <sub>MAX</sub>          | 88   |            |      | 86      |           |      | dB      |

|                                          | Frequency = 4 MHz                            | 55   | 60         |      | 55      | 60        |      | dB      |

| Input Resistance                         |                                              |      | 370        |      |         | 370       |      | kΩ      |

| Input Capacitance                        |                                              |      | 2          |      |         | 2         |      | pF      |

| OUTPUT CHARACTERISTICS                   |                                              |      |            |      |         |           |      |         |

| Output Voltage Swing                     | $R_L \geq 150 \; \Omega$                     | ±3.2 | ±3.5       |      | ±3.2    | ±3.5      |      | V       |

|                                          | $R_L \ge 150 \ \Omega, \pm 4 \ V_S$          | ±2.2 | -2.4/+2.7  |      | ±2.2    | -2.4/+2.7 |      | V       |

| Short-Circuit Current                    | Short to ground                              |      | -55/+70    |      |         | -55/+70   |      | mA      |

| Output Current                           |                                              | ±40  |            |      | ±40     |           |      | mA      |

|                            |                                       | A   | AD830J/AD830A |       |     | AD830S1 |       |       |

|----------------------------|---------------------------------------|-----|---------------|-------|-----|---------|-------|-------|

| Parameter                  | Conditions                            | Min | Тур           | Мах   | Min | Тур     | Max   | Units |

| POWER SUPPLIES             |                                       |     |               |       |     |         |       |       |

| Operating Range            |                                       | ±4  |               | ±16.5 | ±4  |         | ±16.5 | V     |

| Quiescent Current          | T <sub>MIN</sub> - T <sub>MAX</sub>   |     | 13.5          | 16    |     | 13.5    | 16    | mA    |

| +PSRR (to V <sub>P</sub> ) | DC, $G = +1$ , offset                 |     | 86            |       |     | 86      |       | dB    |

| –PSRR (to V <sub>N</sub> ) | DC, $G = +1$ , Offset                 |     | 68            |       |     | 68      |       | dB    |

| PSRR (Dual Supply)         | DC, G = $+1$ , $\pm 5$ to $\pm 15$ Vs | 66  | 71            |       | 66  | 71      |       | dB    |

| PSRR (Dual Supply)         | DC, G = $+1$ , $\pm 5$ to $\pm 15$ Vs |     |               |       |     |         |       |       |

|                            | $T_{MIN} - T_{MAX}$                   | 62  | 68            |       | 60  | 68      |       | dB    |

<sup>1</sup> See Standard Military Drawing 5962-9313001MPA for specifications. <sup>2</sup> Clipping level function on X channel only.

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

2.5

€2.0

0 ⊾ \_50

-30

-10

| Parameter                                 | Rating                     |

|-------------------------------------------|----------------------------|

| Supply Voltage                            | ±18 V                      |

| Internal Power Dissipation                | Observe derating<br>curves |

| Output Short-Circuit Duration             | Observe derating<br>curves |

| Common-Mode Input Voltage                 | ±Vs                        |

| Differential Input Voltage                | ±Vs                        |

| Storage Temperature Range (Q)             | –65°C to +150°C            |

| Storage Temperature Range (N)             | −65°C to +125°C            |

| Storage Temperature Range (RN)            | –65°C to +125°C            |

| Operating Temperature Range               |                            |

| AD830J                                    | 0°C to +70°C               |

| AD830A                                    | -40°C to +85°C             |

| AD830S                                    | −55°C to +125°C            |

| Lead Temperature Range (Soldering 60 sec) | 300°C                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

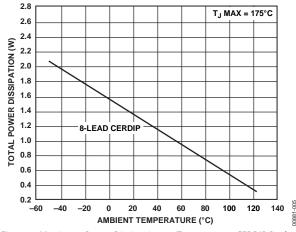

The maximum power that can be safely dissipated by the AD830 is limited by the associated rise in junction temperature. For the plastic packages, the maximum safe junction temperature is 145°C. For the CERDIP, the maximum junction temperature is 175°C. If these maximums are exceeded momentarily, proper circuit operation will be restored as soon as the die temperature is reduced. Leaving the AD830 in the overheated condition for an extended period can result in permanent damage to the device. To ensure proper operation, it is important to observe the recommended derating curves.

While the AD830 output is internally short-circuit protected, this may not be sufficient to guarantee that the maximum junction temperature is not exceeded under all conditions. If the output is shorted to a supply rail for an extended period, then the amplifier may be permanently destroyed.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 4. Thermal Resistance

| Package Type          | θ <sub>JA</sub> | Unit |

|-----------------------|-----------------|------|

| 28-Lead PDIP Package  | 90              | °C/W |

| 8-Lead SOIC Package   | 155             | °C/W |

| 8-Lead CERDIP Package | 11              | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

10

8-LEAD SOIC

30

50

70

90

8-LEAD PDIP

T. MAX = 145°C

Figure 5. Maximum Power Dissipation vs. Temperature, CERDIP Package

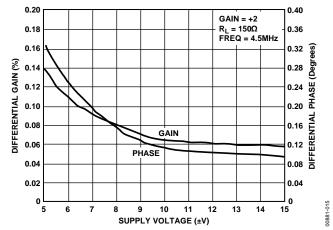

Figure 15. Differential Gain and Phase vs. Supply Voltage,  $R_L = 150 \Omega$

0.10

GAIN = +2

0.10

Figure 12. Differential Gain and Phase vs. Supply Voltage,  $R_L = 500 \Omega$

Figure 17. Supply Current vs. Junction Temperature

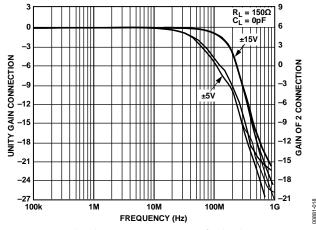

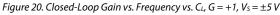

Figure 18. Closed-Loop Gain vs. Frequency for the Three Common Connections of Figure 16

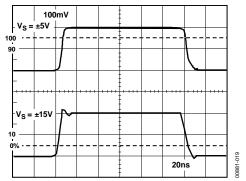

Figure 19. Small Signal Pulse Response,  $R_L = 150 \Omega$ ,  $C_L = 4.7 pF$ , G = +1

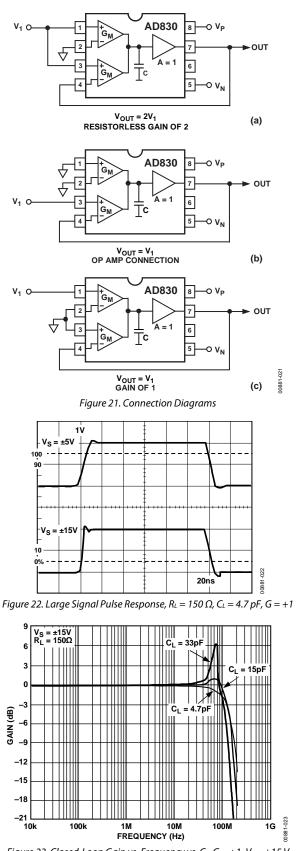

Figure 23. Closed-Loop Gain vs. Frequency vs.  $C_L$ , G = +1,  $V_S = \pm 15 V$

### THEORY OF OPERATION TRADITIONAL DIFFERENTIAL AMPLIFICATION

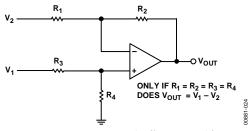

In the past, when differential amplification was needed to reject common-mode signals superimposed with a desired signal, most often the solution used was the classic op amp based difference amplifier shown in Figure 24. The basic function  $V_0 = V_1 - V_2$  is simply achieved, but the overall performance is poor and the circuit possesses many serious problems that make it difficult to realize a robust design with moderate to high levels of performance.

Figure 24. Op Amp Based Difference Amplifier

#### PROBLEMS WITH THE OP AMP BASED APPROACH

- Low common-mode rejection ratio (CMRR)

- Low impedance inputs

- CMRR highly sensitive to the value of source R

- Different input impedance for the + and input

- Poor high frequency CMRR

- Requires very highly matched resistors, R<sub>1</sub> to R<sub>4</sub>, to achieve high CMRR

- Halves the bandwidth of the op amp

- High power dissipation in the resistors for large commonmode voltage

#### AD830 FOR DIFFERENTIAL AMPLIFICATION

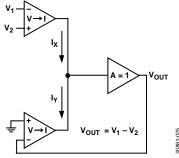

The AD830 amplifier was specifically developed to solve the listed problems with the discrete difference amplifier approach. Its topology, discussed in detail in the Understanding the AD830 Topology section, by design acts as a difference amplifier. The circuit of Figure 25 shows how simply the AD830 is configured to produce the difference of the two signals,  $V_1$  and  $V_2$ , in which the applied differential signal is exactly reproduced at the output relative to a separate output common. Any common-mode voltage present at the input is removed by the AD830.

Figure 25. AD830 as a Difference Amplifier

#### **ADVANTAGEOUS PROPERTIES OF THE AD830**

- High common-mode rejection ratio (CMRR)

- High impedance inputs

- Symmetrical dynamic response for +1 and -1 Gain

- Low sensitivity to the value of source R

- Equal input impedance for the + and input

- Excellent high frequency CMRR

- No halving of the bandwidth

- Constant power distortion versus common-mode voltage

- Highly matched resistors not needed

#### **UNDERSTANDING THE AD830 TOPOLOGY**

The AD830 represents Analog Devices first amplifier product to embody a powerful alternative amplifier topology. Referred to as active feedback, the topology used in the AD830 provides inherent advantages in the handling of differential signals, differing system commons, level shifting, and low distortion, high frequency amplification. In addition, it makes possible the implementation of many functions not realizable with single op amp circuits or superior to op amp based equivalent circuits. With this in mind, it is important to understand the internal structure of the AD830.

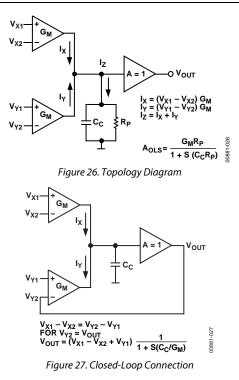

The topology, reduced to its elemental form, is shown in Figure 26. Nonideal effects, such as nonlinearity, bias currents, and limited full scale, are omitted from this model for simplicity but are discussed later. The key feature of this topology is the use of two, identical voltage-to-current converters, G<sub>M</sub>, that make up input and feedback signal interfaces. They are labeled with inputs V<sub>X</sub> and V<sub>Y</sub>, respectively. These voltage-to-current converters possess fully differential inputs, high linearity, high input impedance, and wide voltage range operation. This enables the part to handle large amplitude differential signals; it also provides high common-mode rejection, low distortion, and negligible loading on the source. The label, G<sub>M</sub>, is meant to convey that the transconductance is a large signal quantity, unlike in the front end of most op amps. The two GM stage current outputs, I<sub>x</sub> and I<sub>y</sub>, sum together at a high impedance node, which is characterized by an equivalent resistance and capacitance connected to an ac common. A unity voltage gain stage follows the high impedance node to provide buffering from loads. Relative to either input, the open-loop gain, AoL, is set by the transconductance, G<sub>M</sub>, working into the resistance,  $R_P$ ;  $A_{OL} = G_M \times R_P$ . The unity gain frequency,  $\omega_{0 dB}$ , for the openloop gain is established by the transconductance, G<sub>M</sub>, working into the capacitance,  $C_C$ ;  $\omega_0 _{dB} = G_M/C_C$ . The open-loop description of the AD830 is shown below for completeness.

Precise amplification is accomplished through closed-loop operation of this topology. Voltage feedback is implemented via the Y G<sub>M</sub> stage where the output is connected to the -Y input for negative feedback, as shown in Figure 27. An input signal is applied across the X G<sub>M</sub> stage, either fully differential or singleended referred to common. It produces a current signal that is summed at the high impedance node with the output current from the Y G<sub>M</sub> stage. Negative feedback nulls this sum to a small error current necessary to develop the output voltage at the high impedance node. The error current is usually negligible, so the null condition essentially forces the Y GM output stage current to equal the exact X G<sub>M</sub> output current. Because the two transconductances are identical, the differential voltage across the Y inputs equals the negative of the differential voltage across the X input;  $V_Y = -V_X$  or, more precisely,  $V_{Y2} - V_{Y1} = V_{X1} - V_{X2}$ . This simple relation provides the basis to easily analyze any function possible to synthesize with the AD830, including any feedback situation.

The bandwidth of the circuit is defined by the  $G_M$  and the capacitor,  $C_C$ . The highly linear  $G_M$  stages give the amplifier a single-pole response, excluding the output amplifier and loading effects. It is important to note that the bandwidth and general dynamic behavior is symmetrical (identical) for the noninverting and the inverting connections of the AD830. In addition, the input impedance and CMRR are the same for either connection. This is very advantageous and unlike in a voltage or current feedback amplifier where there is a distinct difference in performance between the inverting and noninverting gain. The practical importance of this cannot be overemphasized and is a key feature offered by the AD830 amplifier topology.

#### **INTERFACING THE INPUT**

#### Common-Mode Voltage Range

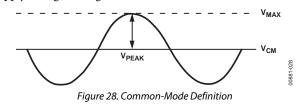

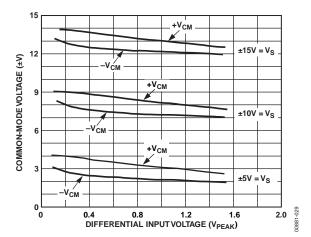

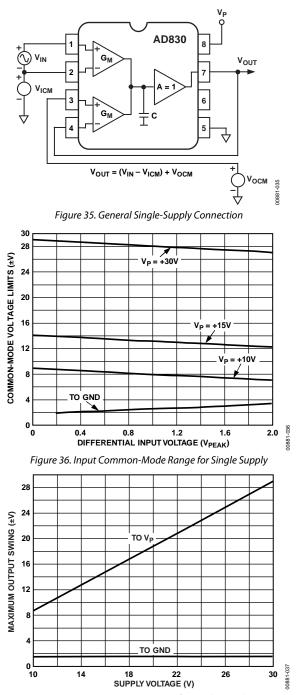

The common-mode range of the AD830 is defined by the amplitude of the differential input signal and the supply voltage. The general definition of common-mode voltage,  $V_{CM}$ , is usually applied to a symmetrical differential signal centered around a particular voltage, as illustrated in Figure 28. This is the meaning implied here for common-mode voltage. The internal circuitry establishes the maximum allowable voltage on the input or feedback pins for a given supply voltage. This constraint and the differential input voltage sets the common-mode voltage limit. Figure 29 shows a curve of the common-mode voltage range versus the differential voltage for three supply voltage settings.

Figure 29. Input Common-Mode Voltage Range vs. Differential Input Voltage

#### Differential Voltage Range

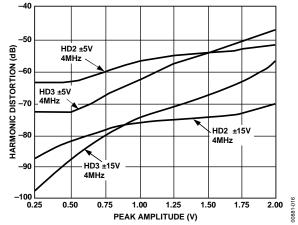

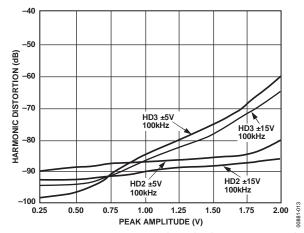

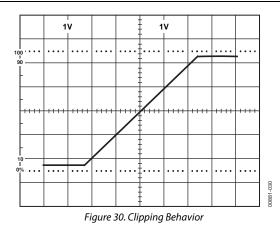

The maximum applied differential voltage is limited by the clipping range of the input stages. This is nominally set at a 2.4 V magnitude and depicted in the cross plot (X-Y) in Figure 30. The useful linear range of the input stages is set at 2 V but is actually a function of the distortion required for a particular application. The distortion increases for larger differential input voltages. A plot of relative distortion versus the input differential voltage is shown in Figure 13 and Figure 16. The distortion characteristics impose a secondary limit to the differential input voltage for high accuracy applications.

#### **Choice of Polarity**

The sign of the gain is easily selected by choosing the polarity of the connections to the + and - inputs of the X G<sub>M</sub> stage. Swapping between inverting and noninverting gain is possible simply by reversing the input connections. The response of the amplifier is identical in either connection, except for the sign change.

The bandwidth, high impedance, and transient behavior of the AD830 is symmetrical for both polarities of gain. This is very advantageous and unlike an op amp.

#### Input Impedance

The relatively high input impedance of the AD830, for a differential receiver amplifier, permits connections to modest impedance sources without much loading or loss of commonmode rejection. The nominal input resistance is 300 k $\Omega$ . The real limit to the upper value of the source resistance is in its effect on common-mode rejection and bandwidth. If the source resistance is in only one input, then the low frequency common-mode rejection is lowered to  $\approx R_{IN}/R_s$ . The source resistance/input capacitance pole limits the bandwidth. Refer to the following equation:

$$\left(f = \frac{1}{2\pi} \times R_S \times C_{IN}\right)$$

Furthermore, the high frequency common-mode rejection is additionally lowered by the difference in the frequency response caused by the  $R_S \times C_{IN}$  pole. Therefore, to maintain good low and high frequency common-mode rejection, it is recommended that the source resistances of the + and – inputs be matched and of modest value ( $\leq 10 \text{ k}\Omega$ ).

#### Handling Bias Currents

The bias currents are typically 4  $\mu$ A flowing into each pin of the G<sub>M</sub> stages of the AD830. Because all applications possess some finite source resistance, the bias current through this resistor creates a voltage drop ( $I_{BLAS} \times R_S$ ). The relatively high input impedance of the AD830 permits modest values of  $R_S$ , typically  $\leq 10 \text{ k}\Omega$ . If the source resistance is in only one terminal, then an objectionable offset voltage may result, for example, 4  $\mu$ A × 5  $k\Omega = 20$  mV. Placement of an equal value resistor in series with the other input cancels the offset to first order. However, due to

mismatches in the resistances, a residual offset remains and is likely to be greater than the bias current (offset current) mismatches.

#### Applying Feedback

The AD830 is intended for use with gains from 1 to 100. Gains greater than one are simply set by a pair of resistors connected as shown in the difference amplifier (Figure 40) with gain >1. The value of the bottom resistor,  $R_2$ , should be kept less than 1 k $\Omega$  to ensure that the pole formed by  $C_{IN}$  and the parallel connection of  $R_1$  and  $R_2$  is sufficiently high in frequency so that it does not introduce excessive phase shift around the loop and destabilize the amplifier. A compensating resistor, equal to the parallel combination of  $R_1$  and  $R_2$ , should be placed in series with the other Y  $G_M$  stage input to preserve the high frequency common-mode rejection and to lower the offset voltage induced by the input bias current.

#### **Output Common Mode**

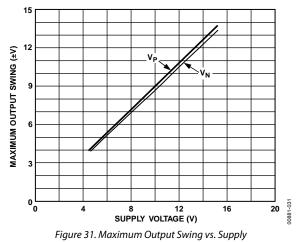

The output swing of the AD830 is defined by the differential input voltage, the gain, and the output common. Depending on the anticipated signal span, the output common (or ground) may be set anywhere between the allowable peak output voltage in a manner similar to that described for input voltage common mode. A plot of the peak output voltage versus the supply is shown in Figure 31. A prediction of the common-mode range versus the peak output differential voltage can be easily derived from the maximum output swing as  $V_{OCM} = V_{MAX} - V_{PEAK}$ .

#### **Output Current**

The absolute peak output current is set by the short-circuit current limiting, typically greater than 60 mA. The maximum drive capability is rated at 50 mA but without a guarantee of distortion performance. Best distortion performance is obtained by keeping the output current  $\leq 20$  mA. Attempting to drive large voltages into low valued resistances, for example, 10 V into 150  $\Omega$  causes an apparent lowering of the limit for output signal swing but is just the current limiting behavior.

#### **Driving Cap Loads**

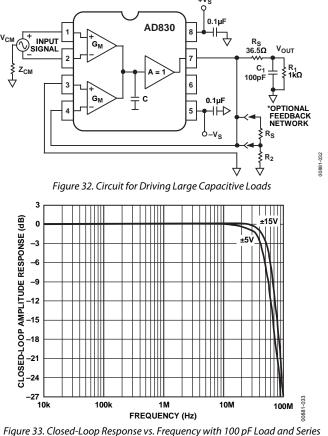

The AD830 is capable of driving modest sized capacitive loads while maintaining its rated performance. Several curves of bandwidth versus capacitive load are given in Figure 34 and Figure 37. The AD830 was designed primarily as a low distortion video speed amplifier but with a trade-off, for example, giving up very large capacitive load driving capability. If very large capacitive loads must be driven, the network shown in Figure 32 should be used to ensure stable operation. If the loss of gain caused by the resistor, R<sub>s</sub>, in series with the load is objectionable, the optional feedback network shown may be added to restore the lost gain.

Resistor Compensation

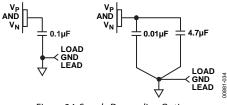

# SUPPLIES, BYPASSING, AND GROUNDING (FIGURE 34)

The AD830 is capable of operating over a wide range of supply voltages, both single and dual supplies. The coupling may be dc or ac, provided the input and output voltages stay within the specified common-mode voltage limits. For dual supplies, the device works from  $\pm 4$  V to  $\pm 16.5$  V. Single-supply operation is possible over 8 V to 33 V. It is also possible to operate the part with split-supply voltages, for example,  $\pm 24$  V or  $\pm 5$  V for special applications such as level shifting. The primary constraint is that the total potential between the two supplies does not exceed 33 V.

Inclusion of power supply bypassing capacitors is necessary to achieve stable behavior and the specified performance. It is especially important when driving low resistance loads. At minimum, connect a 0.1  $\mu$ F ceramic capacitor at the supply lead of the AD830 package. In addition, for the best bypassing, it is best to connect a 0.01  $\mu$ F ceramic capacitor and 4.7  $\mu$ F tantalum capacitor to the supply lead going to the AD830.

The AD830 is designed to be capable of rejecting noise and dissimilar potentials in the ground lines. Therefore, proper care is necessary to realize the benefits of the differential amplification of the part. Separation of the input and output grounds is crucial in rejection of the common-mode noise at the inputs and eliminating any ground drops on the input signal line. For example, connecting the ground of a coaxial cable to the AD830 output common (board ground) could degrade the CMR and also introduce power-down loading on cable grounds.

However, it is also necessary as in any electronic system to provide a return path for bias currents back to their original power supply. This is accomplished by providing a connection between the differing grounds through a modest impedance labeled  $Z_{CM}$ , for example, 100  $\Omega$ .

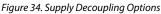

#### Single-Supply Operation

The AD830 is capable of operating in single power supply applications down to a voltage of 8 V, with the generalized connection shown in Figure 35. There is a constraint on the common-mode voltage at the input and output that establishes the range for these voltages. Direct coupling may be used for input and output voltages that lie in these ranges. Any gain network applied needs to be referred to the output common connection or have an appropriate offset voltage. In situations where the signal lies at a common voltage outside the commonmode range of the AD830, direct coupling does not work, so ac coupling should be used. Figure 47 shows how to easily accomplish coupling to the AD830. For single-supply operation where direct coupling is desired, the input and output commonmode curves (Figure 36 and Figure 37) should be used.

#### Figure 37. Output Swing Limit for Single Supply

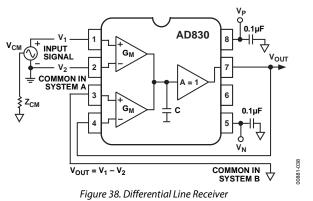

#### **Differential Line Receiver**

The AD830 is specifically designed to perform as a differential line receiver. The circuit in Figure 38 shows how simple it is to configure the AD830 for this function. The signal from System A is received differentially relative to the common of System A, and that voltage is exactly reproduced relative to the common in System B. The common-mode rejection versus frequency, shown in Figure 6, is excellent, typically 100 dB at low frequencies. The high input impedance permits the AD830 to operate as a bridging amplifier across low impedance terminations with negligible loading. The differential gain and phase specifications are very good, as shown in Figure 12 for 500  $\Omega$  and Figure 15 for 150  $\Omega$ . The input and output common should be separated to achieve the full CMR performance of the AD830 as a differential amplifier. However, a common return path is necessary between System A and System B.

#### Wide Range Level Shifter

The wide common-mode range and accuracy of the AD830 allows easy level shifting of differential signals referred to an input common-mode voltage to any new voltage defined at the output. The inputs may be referenced to levels as high as 10 V at the inputs with a  $\pm 2$  V swing around 10 V. In the circuit in Figure 39, the output voltage, V<sub>OUT</sub>, is defined by the simple equation shown below. The excellent linearity and low distortion are preserved over the full input and output common-mode range. The voltage sources need not be of low impedance, since the high input resistance and modest input bias current of the AD830 V-to-I converters permit the use of resistive voltage dividers as reference voltages.

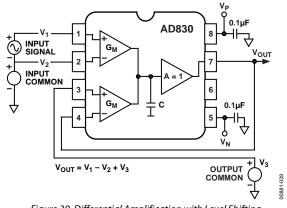

Figure 39. Differential Amplification with Level Shifting

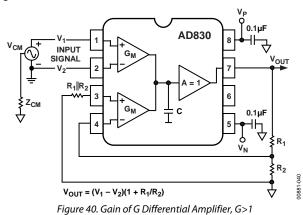

#### Difference Amplifier with Gain > 1

The AD830 can provide instrumentation amplifier style and differential amplification at gains greater than 1. The input signal is connected differentially and the gain is set via feedback resistors, as shown in Figure 40. The gain is  $G = (R_2 + R_1)/R_2$ . The AD830 can provide either inverting or noninverting differential amplification. The polarity of the gain is established by the polarity of the connection at the input. Feedback resistor,  $R_2$ , should generally be  $R_2 \leq 1 \text{ k}\Omega$  to maintain closed-loop

stability and also keep bias current induced offsets low. Highest CMRR and lowest dc offsets are preserved by including a compensating resistor in series with Pin 3. The gain may be as high as 100.

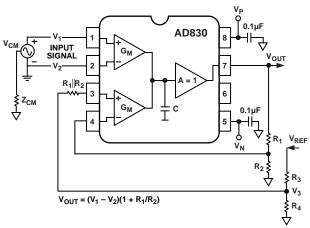

#### Offsetting the Output With Gain

Some applications, such as ADCs, require that the signal be amplified and also offset, typically to accommodate the input range of the device. The AD830 can offset the output signal very simply through Pin 3 even with gain > 1. The voltage applied to Pin 3 must be attenuated by an appropriate factor so that  $V_3 \times G$  = desired offset. In Figure 41, a resistive divider from a voltage reference is used to produce the attenuated offset voltage.

Figure 41. Offsetting the Output with Differential Gain >1

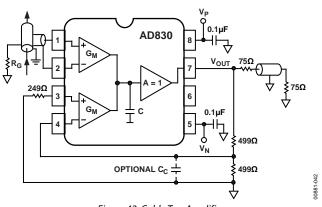

#### Loop Through or Line Bridging Amplifier (Figure 42)

The AD830 is ideally suited for use as a video line bridging amplifier. The video signal is tapped from the conductor of the cable relative to its shield. The high input impedance of the AD830 provides negligible loading on the cable. More significantly, the benign loading is maintained while the AD830 is powered down. Coupled with its good video load driving performance, the AD830 is well suited for video cable monitoring applications.

Figure 42. Cable Tap Amplifier

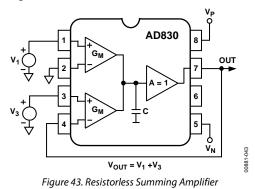

#### **Resistorless Summing**

Direct, two input, resistorless summing is easily realized from the general unity gain mode. By grounding  $V_{X2}$  and applying the two inputs to  $V_{X1}$  and  $V_{Y1}$ , the output is the exact sum of the applied voltages,  $V_1$  and  $V_3$ , relative to common;  $V_{OUT} = V_1 + V_3$ . A diagram of this simple but potent application is shown below in Figure 43. The AD830 summing circuit possesses several virtues not present in the classic op amp based summing circuits.

It has high impedance inputs, no resistors, very precise summing, high reverse isolation, and noninverting gain. Achieving this function and performance with op amps requires significantly more components.

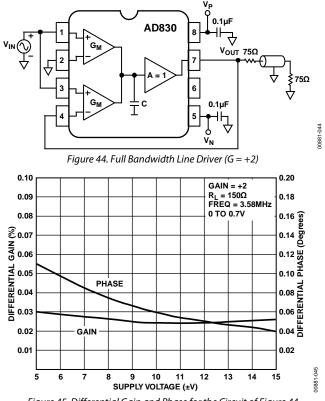

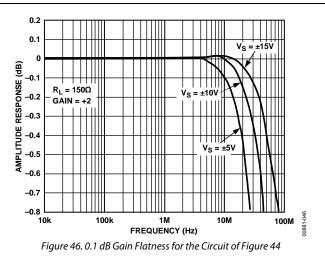

#### 2× Gain Bandwidth Line Driver

A gain of two, without the use of resistors, is possible with the AD830. This is accomplished by grounding  $V_{X2}$ , tying the  $V_{X1}$  and  $V_{Y1}$  inputs together, and applying the input,  $V_{IN}$ , to this wired connection. The output is exactly twice the applied voltage,  $V_{IN}$ ;  $V_{OUT} = 2 \times V_{IN}$ . Figure 44 shows the connections for this highly useful application. The most notable characteristic of this alternative gain of +2 is that there is no loss of bandwidth as in a voltage feedback op amp based gain of +2 where the bandwidth is halved; therefore, the gain bandwidth is doubled. In addition, this circuit is accurate without the need for any precise valued resistors, as in the op amp equivalents, and it possesses excellent differential gain and phase performance, as shown in Figure 45 and Figure 46.

00881-041

Figure 45. Differential Gain and Phase for the Circuit of Figure 44

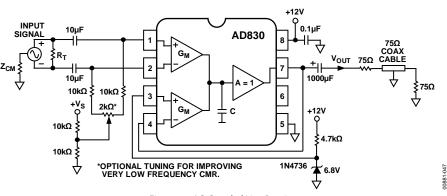

#### **AC-COUPLED LINE RECEIVER**

The AD830 is configurable as an ac-coupled differential amplifier on a single- or bipolar-supply voltage. All that is needed is inclusion of a few noncritical passive components, as illustrated in Figure 47. A simple resistive network at the X  $G_M$ input establishes a common-mode bias. Here, the common mode is centered at 6 V, but in principle can be any voltage within the common-mode limits of the AD830. The 10  $k\Omega$ resistors to each input bias the X G<sub>M</sub> stage with sufficiently high impedance to keep the input coupling corner frequency low, but not too large so that residual bias current induced offset voltage becomes troublesome. For dual-supply operation, the 10 k $\Omega$ resistors may go directly to ground. The output common is conveniently set by a Zener diode for a low impedance reference to preserve the high frequency CMR. However, a simple resistive divider works fine, and good high frequency CMR can be maintained by placing a compensating resistor in series with the +Y input. The excellent CMRR response of the circuit is shown in Figure 48. A plot of the 0.1 dB flatness from 10 Hz is also shown. With the use of 10  $\mu$ F capacitors, the CMR is >90 dB down to a few tens of hertz. This level of performance is almost impossible to achieve with discrete solutions.

Figure 47. AC-Coupled Line Receiver

Figure 48. Common-Mode Rejection vs. Frequency for Line Receiver

Figure 49. Amplitude Response vs. Frequency for Line Receiver

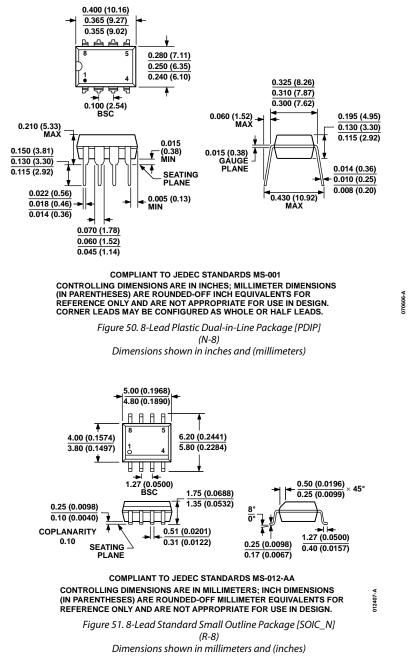

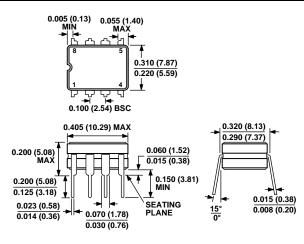

### **OUTLINE DIMENSIONS**

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 52. 8-Lead Ceramic Dual In-Line Package [CERDIP]

(Q-8)

Dimensions shown in inches and (millimeters)

#### **ORDERING GUIDE**

| Model <sup>1</sup>           | Temperature Range | Package Description | Package Option |

|------------------------------|-------------------|---------------------|----------------|

| AD830AN                      | -40°C to +85°C    | 8-Lead PDIP         | N-8            |

| AD830ANZ                     | -40°C to +85°C    | 8-Lead PDIP         | N-8            |

| AD830AR                      | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD830ARZ                     | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD830ARZ-REEL                | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD830ARZ-REEL7               | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD830JR                      | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD830JR-REEL                 | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD830JR-REEL7                | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD830JRZ                     | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD830JRZ-RL                  | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD830JRZ-R7                  | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| 5962-9313001MPA <sup>2</sup> | –55°C to +125°C   | 8-Lead CERDIP       | Q-8            |

$^{1}$  Z = RoHS Compliant Part.

<sup>2</sup> See Standard Military Drawing 5962-9313001 MPA for specifications.

©2005–2010 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D00881-0-3/10(C)

www.analog.com

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

«JONHON» (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«FORSTAR» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный) Факс: 8 (812) 320-03-32 Электронная почта: ocean@oceanchips.ru Web: http://oceanchips.ru/ Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А