# Integrated IEEE 802.3af PoE-PD Interface Controller

#### Description

The NCP1093 and NCP1094 are members of ON Semiconductor's high power HIPO $^{™}$  Power over Ethernet Powered Device (PoE-PD) product family and integrate an IEEE 802.3at PoE-PD interface controller.

Both variants incorporate the required functions such as detection, classification, under voltage lockout, inrush and operational current limit. A power good and NCLASS\_AT signal have been added to guarantee proper enabling/disabling of the DC-DC controller for both type-I and type-II operation. In addition, the NCP1093 offers a programmable under-voltage while the NCP1094 provides an auxiliary pin for applications supporting auxiliary supplies.

The NCP1093 and NCP1094 are fabricated in a robust high voltage process and integrate a rugged vertical N-channel DMOS suitable for the most demanding environments and capable of withstanding harsh environments such as hot swap and cable ESD events.

The NCP1093 and NCP1094 complement ON Semiconductor's ASSP portfolio in industrial devices and can be combined with stepper motor drivers, CAN bus drivers and other high-voltage interfacing devices to offer complete solutions to the industrial and security market.

#### **Features**

- Fully Supports IEEE 802.3af/at Specifications

- Programmable Classification Current

- Support Two Event Classification-Signature

- Adjustable Under Voltage Lock Out (NCP1094 Only)

- Open-Drain Power Good Indicator

- 130 mA Inrush Current Limit

- 500 mA Operational Current Limit

- Pass Switch Disabling Input for Rear Auxiliary Supply Operation (NCP1094 Only)

- Over-temperature Protection

- Industrial Temperature Range –40°C to 85°C with Full Operation up to 125°C Junction Temperature

- 0.6 Ω Hot–swap Pass–switch

- Vertical N-channel DMOS Pass-switch Offers the Robustness of Discrete MOSFETs

# ON Semiconductor®

http://onsemi.com

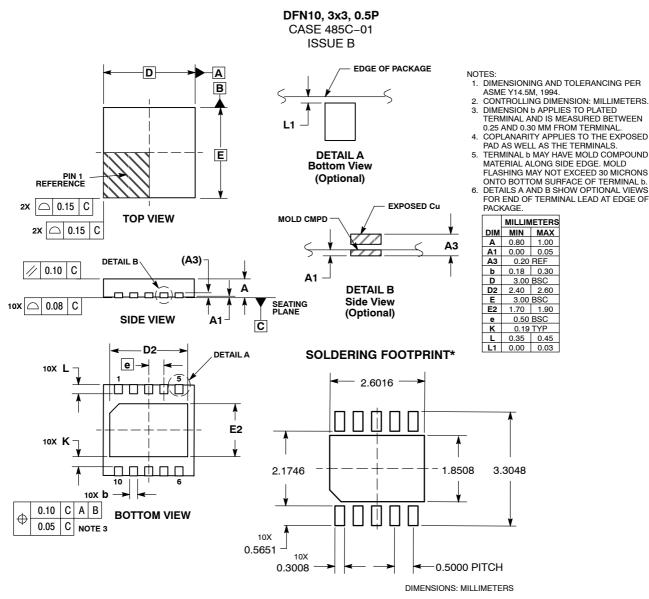

DFN10 MN SUFFIX CASE 485C

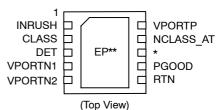

#### **PIN CONFIGURATION**

\*NCP1093 = UVLO NCP1094 = AUX

\*\* Exposed pad should be connected to VPORTN

#### **MARKING DIAGRAMS**

NCP10 93MN ALYW NCP10 94MN ALYW

NCP109xMN = Specific Device Code

A = Assembly Location

L = Wafer Lot Y = Year

W = Work Week

■ Pb-Free Package

(Note: Microdot may be in either location)

#### ORDERING INFORMATION

| Device      | Package            | Shipping <sup>†</sup> |

|-------------|--------------------|-----------------------|

| NCP1093MNG  | DFN10<br>(Pb-Free) | 120 Units / Tube      |

| NCP1093MNRG | DFN10<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP1094MNG  | DFN10<br>(Pb-Free) | 120 Units / Tube      |

| NCP1094MNRG | DFN10<br>(Pb-Free) | 3000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

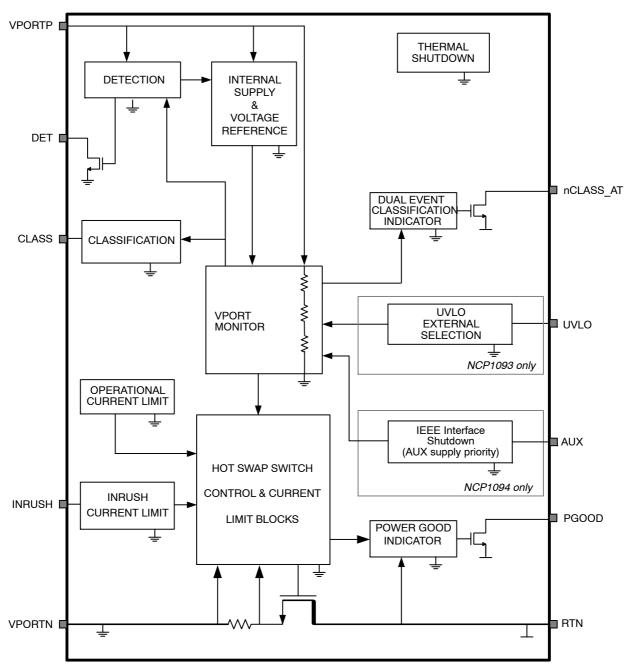

Figure 1. NCP1093/94 Functional Block Diagram

# **Simplified Application Diagrams**

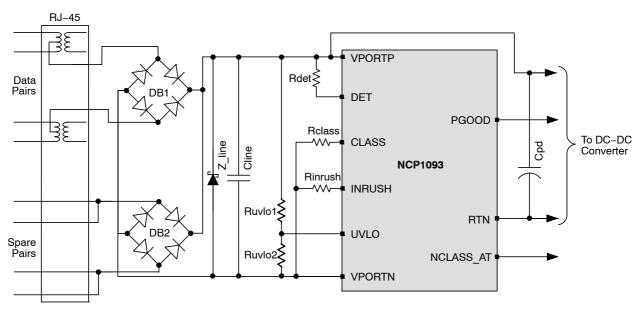

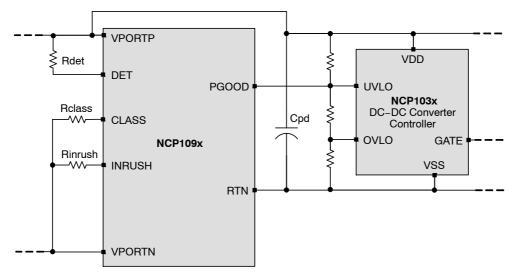

Figure 2. Typical Application Circuit using the NCP1093 with External UVLO Setting

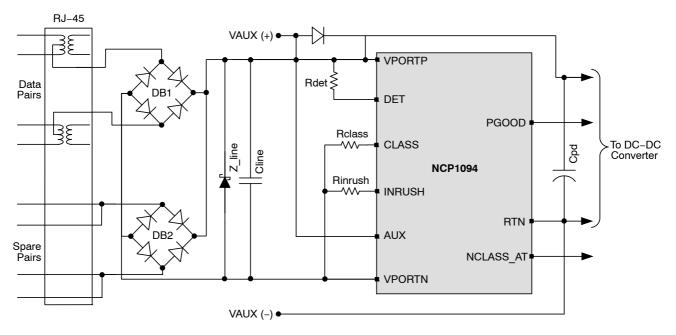

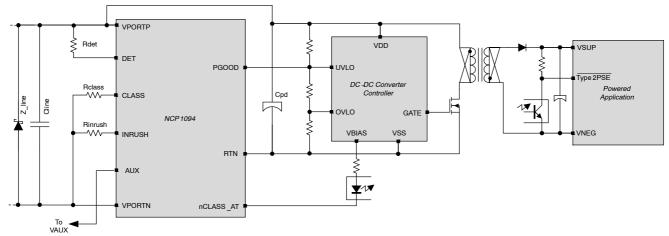

Figure 3. Typical Application Circuit using the NCP1094

**Table 1. PIN DESCRIPTION**

|             | Pin No. |         |                       |                                                                                                                                                                               |  |  |  |  |  |

|-------------|---------|---------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name        | NCP1093 | NCP1094 | Туре                  | Description                                                                                                                                                                   |  |  |  |  |  |

| INRUSH      | 1       | 1       | Output                | Current limit programming pin. Connect a resistor between INRUSH and VPORTN.                                                                                                  |  |  |  |  |  |

| CLASS       | 2       | 2       | Output                | Classification current programming pin. Connect a resistor between CLASS and VPORTN.                                                                                          |  |  |  |  |  |

| DET         | 3       | 3       | Output,<br>Open Drain | Detection pin. Connect a 24.9 $\mbox{k}\Omega$ resistor between DET and VPORTP for a valid PD detection signature.                                                            |  |  |  |  |  |

| VPORTN1     | 4       | 4       | Ground                | Negative input power. Connected to the source of the internal pass-switch                                                                                                     |  |  |  |  |  |

| VPORTN2     | 5       | 5       | Ground                | Negative input power. Connected to the source of the internal pass-switch                                                                                                     |  |  |  |  |  |

| RTN         | 6       | 6       | Ground                | DC-DC controller power return. Connected to the drain of the internal pass-switch                                                                                             |  |  |  |  |  |

| PGOOD       | 7       | 7       | Output,<br>Open Drain | Open Drain Power Good Indicator. Pin is in HZ mode when the power good signal is active.                                                                                      |  |  |  |  |  |

| UVLO        | 8       | -       | Input                 | Undervoltage lockout input. Voltage with respect to VPORTN. Connect a resist-or-divider from VPORTP to UVLO to VPORTNx to set an external UVLO threshold.                     |  |  |  |  |  |

| AUX         | -       | 8       | Input                 | Auxiliary Pin. When this pin is pulled up, the Pass Switch is disabled and allows a supply transition from PSE to the rear auxiliary supply connected between VPORTP and RTN. |  |  |  |  |  |

| NCLASS_AT   | 9       | 9       | Output                | Active low enable signal used to verify high power operation                                                                                                                  |  |  |  |  |  |

| VPORTP      | 10      | 10      | Input                 | Positive input power. Voltage with respect to VPORTN.                                                                                                                         |  |  |  |  |  |

| Exposed Pad | EP      | EP      | Ground                | Exposed pad should be connected to VPORTN.                                                                                                                                    |  |  |  |  |  |

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                       | Min  | Max | Units | Conditions                                                |

|------------------|-------------------------------------------------|------|-----|-------|-----------------------------------------------------------|

| VPORTP           | Input power supply                              | -0.3 | 72  | V     | Voltage with respect to VPORTN                            |

| RTN              | Analog ground supply 2                          | -0.3 | 72  | V     | Pass-switch in off-state (voltage with respect to VPORTN) |

| CLASS            | Analog output                                   | -0.3 | 72  | V     | Voltage with respect to VPORTN                            |

| INRUSH           | Analog output                                   | -0.3 | 3.6 | V     | Voltage with respect to VPORTN                            |

| AUX              | Analog input                                    | -0.3 | 72  | V     | Voltage with respect to VPORTN                            |

| UVLO             | Analog input                                    | -0.3 | 3.6 | V     | Voltage with respect to VPORTN                            |

| PGOOD            | Analog output                                   | -0.3 | 72  | V     | Voltage with respect to RTN                               |

| Ta               | Ambient temperature                             | -40  | 85  | °C    |                                                           |

| Tj               | Junction temperature                            | -    | 125 | °C    |                                                           |

| Tj-TSD           | Junction temperature<br>(Note 1)                | -    | 175 | °C    | Thermal shutdown condition                                |

| T <sub>stg</sub> | Storage Temperature                             | -55  | 150 | °C    |                                                           |

| ТөЈА             | Thermal Resistance,<br>Junction to Air (Note 2) | 50   |     | °C/W  | DFN-10                                                    |

| ESD-HBM          | Human Body Model                                | 2    |     | kV    | per EIA-JESD22-A114 standard                              |

| ESD-CDM          | Charged Device Model                            | 500  |     | V     | per ESD-STM5.3.1 standard                                 |

| ESD-MM           | Machine Model                                   | 200  |     | V     | per EIA-JESD22-A115-A standard                            |

| LU               | Latch-up                                        | ±100 |     | mA    | per JEDEC Standard JESD78                                 |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

<sup>1.</sup> Tj-TSD allowed during error conditions only. It is assumed that this maximum temperature condition does not occur more than 1 hour cumulative during the useful life for reliability reasons.

<sup>2.</sup> Low θJA is obtained with 2S2P test board (2 signal – 2 plane). High θJA is obtained with double sideboard with minimum pad area and natural convection. Refer to Jedec JESD51 for details. The exposed pad must be connected to the VPORTN ground pin.

## **Recommended Operating Conditions**

Operating conditions define the limits for functional operation and parametric characteristics of the device. Note that the functionality of the device outside the operating conditions described in this section is not warranted. Operating outside the recommended operating conditions for extended periods of time may affect device reliability.

Table 3. OPERATING CONDITIONS (All values are with respect to VPORTN unless otherwise noted.)

| Symbol        | Parameter                                                           | Min  | Тур  | Max | Units    | Conditions                                     |

|---------------|---------------------------------------------------------------------|------|------|-----|----------|------------------------------------------------|

| INPUT SUPPLY  |                                                                     |      |      | •   | •        |                                                |

| VPORT         | Input supply voltage                                                | 0    | -    | 57  | V        | VPORT = VPORTP –<br>VPORTN                     |

| SIGNATURE DE  | TECTION                                                             |      |      |     |          |                                                |

| Offset_det1   | I <sub>(VPORTP)</sub> + I <sub>(RTN)</sub>                          | _    | 2    | 5   | μΑ       | VPORTP = RTN = 1.9 V<br>Rdet = 24.9 K $\Omega$ |

| Sleep_det1    | I <sub>(VPORTP)</sub> + I <sub>(RTN)</sub>                          | -    | 15   | 21  | μΑ       | VPORTP = RTN = 9.8 V<br>Rdet = 24.9 KΩ         |

| Offset_det2   | I <sub>(VPORTP)</sub> + I <sub>(RTN)</sub> + I <sub>(DET)</sub>     | 73   | 77   | 81  | μΑ       | VPORTP = RTN = 1.9 V<br>Rdet = 24.9 KΩ         |

| Sleep_det2    | I <sub>(VPORTP)</sub> + I <sub>(RTN)</sub> + I <sub>(DET)</sub>     | 390  | 400  | 412 | μΑ       | VPORTP = RTN = 9.8 V<br>Rdet = 24.9 KΩ         |

| CLASSIFICATIO | N                                                                   |      |      |     | <u> </u> |                                                |

| Vcl_on        | Classification current turn-on lower threshold                      | 9.8  | 11.3 | 13  | V        | VPORTP rising                                  |

| Vcl_off       | Classification current turn-off upper threshold                     | 21   | -    | 24  | V        | VPORTP rising                                  |

| Vclass_reg    | Classification buffer output voltage                                | _    | 9.8  | -   | V        | 13 V < VPORTP < 21 V                           |

| lcl_bias      | I(vportp) quiescent current during classification                   | -    | 600  | _   | μΑ       | I(class) excluded<br>13 V < VPORTP < 21 V      |

| Iclass0       | Class 0: Rclass 4420 Ω (Note 3)                                     | 0    | -    | 4   | mA       | 13 V < VPORTP < 21 V                           |

| Iclass1       | Class 1: Rclass 953 Ω (Note 3)                                      | 9    | -    | 12  | mA       | 13 V < VPORTP < 21 V                           |

| lclass2       | Class 2: Rclass 549 Ω (Note 3)                                      | 17   | -    | 20  | mA       | 13 V < VPORTP < 21 V                           |

| lclass3       | Class 3: Rclass 357 Ω (Note 3)                                      | 26   | -    | 30  | mA       | 13 V < VPORTP < 21 V                           |

| Iclass4       | Class 4: Rclass 255 Ω (Note 3)                                      | 36   | -    | 44  | mA       | 13 V < VPORTP < 21 V                           |

| V_mark        | Mark event voltage range                                            | 5.4  |      | 9.7 | V        | VPORTP falling                                 |

| I_mark        | I <sub>(VPORTP)</sub> + I <sub>(Rdet)</sub> during mark event range | 0.5  | -    | 2   | mA       | 5.4 V ≤ VPORTP ≤ 9.7 V                         |

| dR_mark       | Input signature during mark event (Note 4)                          | _    | -    | 12  | kΩ       |                                                |

| Vreset        | Classification Reset range                                          | 4.3  | 4.9  | 5.4 | V        | VPORTP falling                                 |

| NCLASS_AT 2 E | EVENT CLASSIFICATION INDICATOR                                      |      |      | •   | •        |                                                |

| Inclass       | I <sub>(NCLASS_AT)</sub> sinking current                            | _    | -    | 5   | mA       |                                                |

| Nclass_low    | NCLASS_AT voltage output low                                        | _    | 0.2  | 0.5 | V        | I <sub>(NCLASS_AT)</sub> = 2 mA                |

| UVLO - INTERN | AL SETTING - NCP1093/94                                             |      |      |     |          |                                                |

| Vuvlo_on      | Default turn on voltage                                             | _    | 37   | 40  | V        | VPORTP rising                                  |

| Vuvlo_off     | Default turn off voltage                                            | 29.6 | 31   | -   | V        | VPORTP falling                                 |

| Vhyst_int     | UVLO internal hysteresis                                            | -    | 6    | -   | V        |                                                |

| Uvlo_filter   | UVLO On / Off filter time                                           | -    | 100  | -   | μs       | For information only                           |

<sup>3.</sup> A tolerance of 1% on the Rclass resistor is included in the min/max values.

<sup>4.</sup> Measured with the 2 Point Measurement defined in the IEEE 802.3af standard with 5.4 V and 9.7 V the extreme values for V2 & V1.

Table 3. OPERATING CONDITIONS (All values are with respect to VPORTN unless otherwise noted.)

| Symbol         | Parameter                                                    | Min  | Тур | Max  | Units | Conditions                                                 |

|----------------|--------------------------------------------------------------|------|-----|------|-------|------------------------------------------------------------|

| UVLO – EXTERN  | AL SETTING – NCP1093 ONLY                                    |      | •   | -    | •     |                                                            |

| Vuvlo_pr       | UVLO external programming range                              | 25   | -   | 50   | V     | VPORTP rising                                              |

| Vuvlo_on2      | External UVLO turn on voltage                                | 1.14 | 1.2 | 1.26 | V     |                                                            |

| Vhyst_off2     | External UVLO turn off voltage                               | 0.95 | 1   | 1.05 | V     |                                                            |

| Uvlo_ipd       | UVLO internal pull down current                              | -    | 2.5 | -    | μΑ    |                                                            |

| AUXILIARY SUPI | PLY SETTING – NCP1094 ONLY                                   |      | •   | -    |       |                                                            |

| Aux_h          | AUX input high level voltage                                 | 3.1  | -   |      | V     |                                                            |

| Aux_I          | AUX input low level voltage                                  | -    | -   | 0.6  | V     |                                                            |

| Aux_pd         | AUX internal pull down resistor                              | 100  | -   | _    | ΚΩ    | For information only                                       |

| PASS-SWITCH A  | AND CURRENT LIMITING                                         | •    | •   | •    | •     |                                                            |

| Ron            | Pass-switch Rds-on                                           | -    | 0.6 | 1    | Ω     | Measured with I(RTN) = 200 mA                              |

| I_inrush       | Inrush current with Rinrush = 169 kΩ                         | 75   | 120 | 170  | mA    | Measured at<br>RTN-VPORTN = 3 V                            |

| l_ilim         | Operating current limit with Rinrush = $169 \text{ k}\Omega$ | 610  | 680 | 800  | mA    | Current limit threshold                                    |

| POWER GOOD II  | NDICATOR                                                     |      | •   | -    |       |                                                            |

| Vds_pgood_on   | RTN-VPORTN threshold voltage required for power good status  | 0.8  | 1   | 1.2  | V     | RTN-VPORTN falling                                         |

| Vds_pgood_off  | RTN-VPORTN latchoff threshold voltage                        | 9    | 10  | 11   | V     | RTN-VPORTN rising                                          |

| Pgood_filter   | PGOOD filter time                                            |      | 100 |      | μs    | Rising and falling / for information only                  |

| Ipgood         | I <sub>(PGOOD)</sub> sinking current                         | -    | -   | 5    | mA    |                                                            |

| Vpgood_low     | PGOOD voltage output low                                     | -    | 0.2 | 0.5  | V     | I <sub>(PGOOD)</sub> = 2 mA<br>Voltage with respect to RTN |

| CURRENT CONS   | GUMPTION                                                     |      | •   | -    |       |                                                            |

| IvportP        | I <sub>(VPORTP)</sub> internal current consumption           | -    | 600 | 900  | μΑ    | VPORTP = 48 V                                              |

| THERMAL SHUT   | DOWN                                                         |      |     |      |       |                                                            |

| TSD            | Thermal shutdown threshold                                   | 150  | _   | _    | °C Tj | Tj = junction temperature                                  |

| Thyst          | Thermal hysteresis                                           | -    | 15  | -    | °C Tj | Tj = junction temperature                                  |

| THERMAL RATIN  | IGS                                                          |      |     |      |       |                                                            |

| Ta             | Ambient temperature                                          | -40  | _   | 85   | °C    |                                                            |

| Tj             | Junction temperature                                         | -    | -   | 125  | °C    |                                                            |

|                | •                                                            |      |     |      |       | •                                                          |

A tolerance of 1% on the Rclass resistor is included in the min/max values.

Measured with the 2 Point Measurement defined in the IEEE 802.3af standard with 5.4 V and 9.7 V the extreme values for V2 & V1.

#### **Description of Operation**

#### **Powered Device Interface**

The integrated PD interface supports the IEEE 802.3af defined operating modes: detection signature, current source classification, undervoltage lockout, inrush and operating current limits. The following sections give an overview of these previous processes.

#### **Detection**

During the detection phase, the incremental equivalent resistance seen by the PSE through the cable must be in the IEEE 802.3af standard specification range (23.70 k $\Omega$  to 26.30 k $\Omega$ ) for a PSE voltage from 2.7 V to 10.1 V. In order to compensate for the non–linear effect of the diode bridge and satisfy the specification at low PSE voltage, the NCP1093/94 present a suitable impedance in parallel with the 24.9 k $\Omega$  Rdet external resistor. For some types of diodes (especially Schottky diodes), it may be necessary to adjust this external resistor.

The Rdet resistor has to be inserted between VPORTP and DET pins. During the detection phase, the DET pin is pulled to ground and goes in high impedance mode (open-drain) once the device exit this mode, reducing thus the current consumption on the cable.

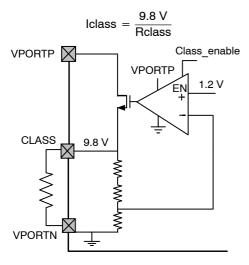

#### Classification

Once the PSE device has detected the PD device, the classification process begins. In classification, the PD regulates a constant current source that is set by the external resistor RCLASS value on the CLASS pin. Figure 4 shows the schematic overview of the classification block. The current source is defined as:

Figure 4. Classification Block Diagram

The NCP1093/94 is able to detect a dual event classification generated by a type 2 PSE, and flag it using its nCLASS AT open drain indicator.

#### **Power Mode**

When the classification hand-shake is completed, the PSE and PD devices move into the operating mode.

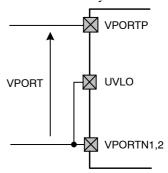

#### **Under Voltage Lock Out (UVLO)**

The NCP1093/94 incorporate a fixed under voltage lock out (UVLO) circuit which monitors the input voltage and determines when to turn on the pass switch and charge the dc–dc converter input capacitor before the power up of the application.

The NCP1093 offers a fixed or adjustable Vuvlo\_on threshold depending if the UVLO pin is used or not. In Figure 5, the UVLO pin is strapped to ground and the Vuvlo on threshold is defined by the internal level.

Figure 5. Default Internal UVLO Configuration (NCP1093 only)

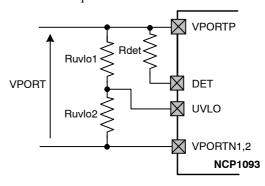

To define the UVLO threshold externally, the ULVO pin must be connected to the center of an external resistor divider between VPORTP and VPORTN as shown in Figure 6.

In order to guarantee the detection signature, the equivalent input resistor made of the Ruvlo1, Ruvlo2 and Rdet should be equal to  $24.9 \text{ k}\Omega$ .

Figure 6. Default Internal UVLO Configuration (NCP1093 only)

For a Vuvlo\_on desired turn-on voltage threshold, Ruvlo1 and Ruvlo2 can be calculated using the following equations:

$$Ruvlo = \frac{24.9 \text{ k} \cdot \text{Rdet}}{\text{Rdet} - 24.9 \text{ k}}$$

with

$$Ruvlo1 + Ruvlo2 = Ruvlo$$

and

$$Ruvlo2 = \frac{1.2}{\text{Vuvlo\_on}} \cdot \text{Ruvlo}$$

With

Vuvlo\_on: Desired Turn-On voltage threshold

#### Example for a Targeted Uvlo on of 35 V:

Let's start with a Rdet of  $30.1~k\Omega$ . This gives a Ruvlo of  $144~k\Omega$  made with a Ruvlo2 of  $4.99~k\Omega$  and a Ruvlo1 of  $140~k\Omega$  (closest values from E96 series). Note that there is a pull down current of  $2.5~\mu A$  typ on the UVLO. Assuming the previous example, this pull down current will create a (non critical) systematic offset of 350~mV on the Uvlon\_on level of 35~V.

The external UVLO hysteresis on the NCP1093 is about 15 percent typical.

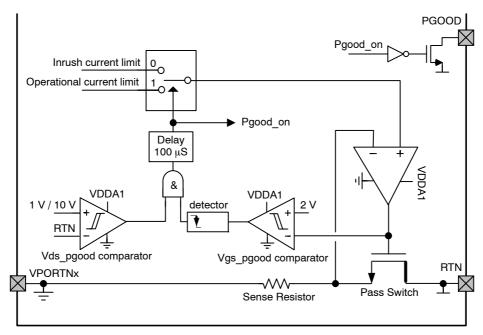

#### **Inrush and Operational Current Limitations**

Both inrush and operational current limit are defined by an external Rinrush resistor connected between INRUSH and VPORTN. The low inrush current limit allows smooth charge of large dc-dc converter input capacitor by limiting the power dissipation over the internal pass switch. In power mode, the operational current limit protects the pass switch and the PD application against excessive transient current and failure on the dc-dc converter output.

Once the input supply reached the Vulvo\_on level, the charge of Cpd capacitor starts with a current limitation set to to the INRUSH level. When this capacitor is fully charged, the current limit switches without any spikes from the inrush current to the operational current level and the power good indicator on PGOOD pin is turned on. The capacitor is considered to be fully charged once the following conditions are satisfied:

- 1. The drain-source voltage of the Pass Switch has decreased below the *Vds\_pgood\_on* level (typical 1 V)

- The gate-source voltage of the Pass Switch is sufficiently high (above 2 V typical) which means the current in the pass switch has decreased below the current limit.

This mechanism is depicted in the following Figure 7.

Figure 7. Inrush and Operational Current Limitation Selection Mechanism

The operational current limit and the power good indicator stays active as long as RTN voltage stays below the vds\_pgood\_off threshold (10 V typical) and the input supply stay above the Vulvo\_off level. Therefore, fast and large voltage step lower than 10 V are tolerated on the input without interruption of the converter controller. Higher input transient will not affect the behavior if RTN does not exceed 10 V for more than 100  $\mu$ S. Such input voltage steps may be introduced by a PSE which is switched to a higher power supply. In case RTN is still above 10 V after this delay, the power good is turned off and the pass switch current limit falls back to the inrush level.

#### **PGOOD Indicator**

The NCP1093/94 integrate a Power Good indicator circuitry indicating the end of the dc-dc converter input capacitor charge, and the enabling of the operational current limit. This indicator is implemented on the PGOOD pin which goes in open drain state when active and which is pulled to ground during turn off.

A possible usage of this PGOOD pin is illustrated in Figure 8. During the inrush phase, the converter controller is forced in standby mode due to the PGOOD pin forcing low the under voltage lock out pin of the controller. Once the Cpd capacitor is fully charged, PGOOD goes in open drain state, allowing the start up sequence of the converter controller.

Figure 8. Power GOOD Implementation

#### NCLASS\_AT Dual Event Classification Indicator

The *nCLASS AT* active low open drain output pin should be used to notify to the microprocessor of the Powered Device that the PSE did a one or two event Hardware Classification.

If a 2 event Hardware classification has been done and once the PD application is supplied by the HIPO DC/DC, the

*nCLASS\_AT* will be pulled low to RTN (ground connection of the DC/DC controller converter).

Otherwise, nCLASS\_AT will be in high impedance mode. The following Scheme illustrates how the *nCLass\_AT* pin may be configured with the processor of the Powered Device. An optocoupler is here used to guarantee to the full isolation between the cable and the application.

Figure 9. nClass AT indicator / possible implementation with the Powered Device

As soon as the application is powered by the DC/DC and after its initialization, the microprocessor will check if the PD interface detected a 2 event hardware classification by reading its digital input (*IN1* in this example). If this *IN1* pin is low, the application knows that the type 2 PSE, and therefore it can consume power till the level specified by the IEEE802.3at standard. Otherwise the application will have to perform a Layer 2 classification with the PSE.

Hereafter are described several scenarios for which HIPO will not enable its *nCLASS\_AT* pin during the Powered Mode:

- The PSE skipped the classification phase

- The PSE did a 1 event hardware classification (it can be a type 1 PSE or a type 2 PSE with Layer 2 only)

- The PSE did a 2 event hardware classification but it didn't well control the input voltage in the Mark voltage (it crossed the Reset range for example).

#### **Auxiliary Supply**

To support application connected to non-PoE enabled networks and minimize the bill of materials, the NCP1093 supports drawing power from an external supply and allows simplified designs with PoE or auxiliary supply priorities.

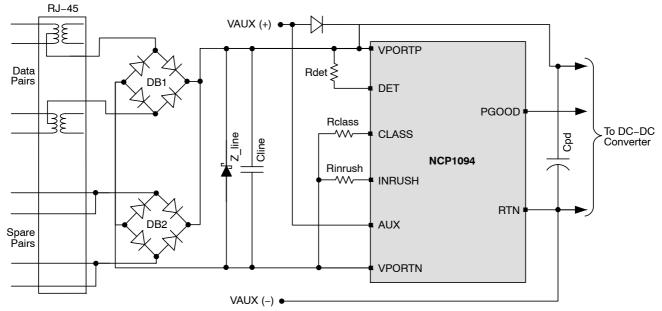

In most of the cases, the auxiliary supply is connected between VPORTP and RTN with a serial diode between VPORTP and VAUX, as shown in Figure 10.

Figure 10. Auxiliary Supply Dominant PD Interface

The NCP1094 offers an AUX input pin which turns off the pass switch when pulled high. This feature is useful for PD applications where the auxiliary supply has to be dominant over the PoE supply. When the auxiliary supply is inserted on a POE powered application, the pass switch disconnection will move the current path from the PSE to the rear auxiliary supply. Since the current delivered by the PSE will goes below the DC MPS level (specified in IEEE 802.3 af/at standard), the PSE will disconnect the PoE–PD

and the application will remain supplied by the auxiliary supply. The transition will happens without any power conversion interruption since the PGOOD indicator stays active (high impedance state).

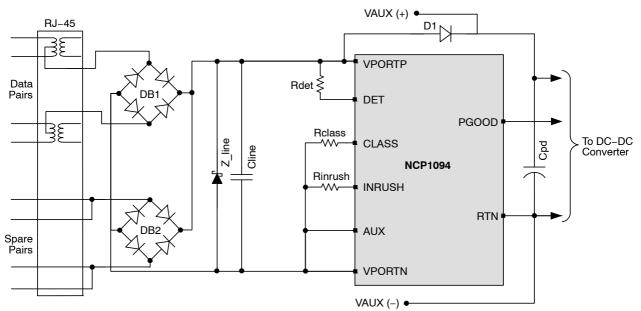

Next Figure 11 depicts an other PD application where the POE supply is dominant over the VAUX supply. A diode D1 has been added in order to not corrupt the PD detection signature when the dc-dc converter is supplied by VAUX.

Figure 11. PoE Supply Dominant PD Interface

#### **Thermal Shutdown**

The NCP1093/94 include a thermal shutdown which protect the device in case of high junction temperature. Once the thermal shutdown (TSD) threshold is exceeded, the classification block, the pass switch and the PGOOD indicator are disabled. The NCP109X returns automatically to normal operation once the die temperature has fallen below the TSD low limit.

## **Company or Product Inquiries**

For more information about ON Semiconductor's Power over Ethernet products visit our Web site at <a href="http://www.onsemi.com">http://www.onsemi.com</a>.

#### **PACKAGE DIMENSIONS**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

All brand names and product names appearing in this document are registered trademarks or trademarks of their respective holders.

ON Semiconductor and a registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

## Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А