## Le58QL061/063 Quad Low Voltage Subcriber Line Audio-Processing Circuit - Ve580 Series Data Sheet

## Features

- Low-power, 3.3 V CMOS technology with 5 V tolerant digital inputs

- Pin programmable PCM/MPI or GCI interface

- Software and coefficient compatible to the Le79Q061/063 QSLAC device

- Standard PCM/microprocessor interface (PCM/MPI mode)

- Single or Dual PCM ports available

- Time slot assigner (up to 128 channels per port)

- Clock slot and transmit clock edge options

- Optional supervision on the PCM highway

- 1.536, 1.544, 2.048, 3.072, 3.088, 4.096, 6.144, 6.176, or 8.192 MHz master clock derived from MCLK or PCLK

- µP access to PCM data

- Real Time Data with interrupt (open drain or TTL)

- Broadcast mode

- General Circuit Interface (GCI mode)

- Control and PCM data on a single port

- 2.048 Mbits/s data rate

- 2.048 MHz or 4.096 MHz clock option

- Performs the functions of four codec/filters

- Software programmable:

- SLIC device input impedance and Transhybrid balance

- Transmit and receive gains and Equalization

- Programmable Digital I/O pins with debouncing

- A-law, µ-law, or linear coding

- Built-in test modes with loopback, tone generation, and µP access to PCM data

- Mixed state (analog and digital) impedance scaling

- Performance guaranteed over a 12 dB gain range

- Supports multiplexed SLIC device outputs

| Document ID#: 080754 |    |                              | Version 8                                               | June 2011            |

|----------------------|----|------------------------------|---------------------------------------------------------|----------------------|

|                      |    | Orde<br>Device               | ering Information<br>Package <sup>1</sup> (Green)       | Packing <sup>2</sup> |

|                      |    | Le58QL061BVC<br>Le58QL063HVC | 44-pin TQFP<br>64-pin LQFP                              | Trays<br>Trays       |

| 1                    |    | 0 1 0                        | neets RoHS Directive 200.<br>minimize the environment   |                      |

| 2                    | 2. | , ,                          | tape and reel packing syst<br>rdering Part Number) wher | ,                    |

- 256 kHz or 293 kHz chopper clock for Zarlink SLIC devices with switching regulator

- Maximum channel bandwidth for V.90 modems

## Applications

· Codec function on telephone switch line cards

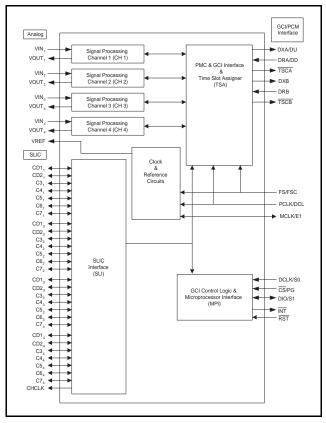

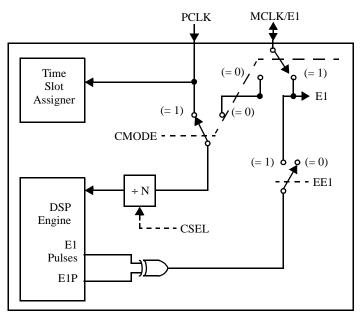

Figure 1 - Block Diagram

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2009-2011, Zarlink Semiconductor Inc. All Rights Reserved.

## Description

The Le58QL061/063 Quad Low Voltage Subscriber Line Audio-Processing Circuit (QLSLAC<sup>™</sup>) devices integrate the key functions of analog line cards into high-performance, very-programmable, four-channel codec-filter devices. The QLSLAC devices are based on the proven design of Zarlink's reliable SLAC<sup>™</sup> device families. The advanced architecture of the QLSLAC devices implements four independent channels and employs digital filters to allow software control of transmission, thus providing a cost-effective solution for the audio-processing function of programmable line cards. The QLSLAC devices are software and coefficient compatible to the QSLAC devices.

Advanced submicron CMOS technology makes the Le58QL061/063 QLSLAC devices economical, with both the functionality and the low power consumption needed in line card designs to maximize line card density at minimum cost. When used with four Zarlink SLIC devices, a QLSLAC device provides a complete software-configurable solution to the BORSCHT functions.

The Le58QL061/063 device supports the feature set of the Le58QL02/021/031 device and provides a General Circuit Interface as a programmable mode.

## **Related Literature**

- 080753 Le58QL02/021/031 QLSLAC™ Data Sheet

- 080761 QSLAC<sup>™</sup> to QLSLAC<sup>™</sup> Design Conversion Guide

- 080758 QSLAC<sup>™</sup> to QLSLAC<sup>™</sup> Guide to New Designs

## **Revision History**

Below are the changes from the September 2007 version to the June 2011 version.

| Page Item                              |                      | Description                                      |

|----------------------------------------|----------------------|--------------------------------------------------|

| 1                                      | Ordering Information | Obsoleted Le58QL061FJC package.                  |

| 32 9.1, "GCI Timing<br>Specifications" |                      | Corrected t <sub>sD</sub> Data Setup Min. to 20. |

## **Table of Contents**

| 1.0 Product Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0 Block Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                                                                                                          |

| 2.1 Clock and Reference Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                                                                                          |

| 2.2 Microprocessor Interface (MPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                            |

| 2.3 Time Slot Assigner (TSA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                            |

| 2.4 Signal Processing Channels (CHx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                            |

| 2.5 SLIC Device Interface (SLI).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                                                                                                          |

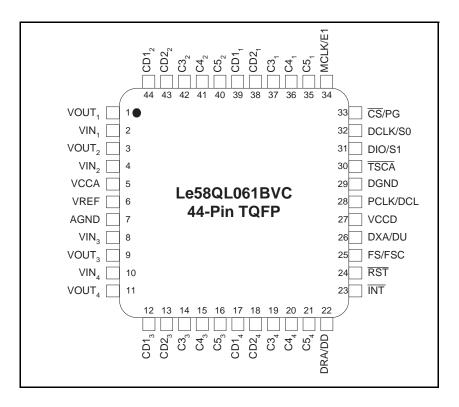

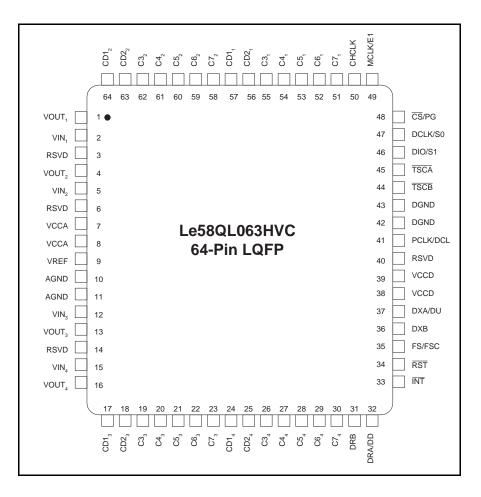

| 3.0 Connection Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                                                                                                                                          |

| 4.0 Pin Descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .11                                                                                                                                                                        |

| 5.0 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 14                                                                                                                                                                       |

| 5.1 Package Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                            |

| 6.0 Operating Ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                            |

| 6.1 Environmental Ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                            |

| 6.2 Electrical Ranges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                            |

| 7.0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                            |

| 7.1 Transmission Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                            |

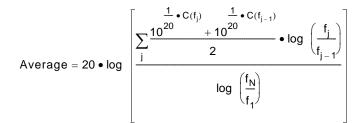

| 7.2 Attenuation Distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                            |

| 7.3 Group Delay Distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                            |

| 7.4 Gain Linearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                            |

| 7.5 Total Distortion Including Quantizing Distortion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 22                                                                                                                                                                       |

| 7.6 Discrimination Against Out-of-Band Input Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 22                                                                                                                                                                       |

| 7.7 Discrimination Against 12- and 16-kHz Metering Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                            |

| 7.8 Spurious Out-of-Band Signals at the Analog Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                            |

| 7.9 Overload Compression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 24                                                                                                                                                                       |

| 8.0 Switching Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 25                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                            |

| 9.0 Switching Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                            |

| 9.1 GCI Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 32                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 32                                                                                                                                                                       |

| 9.1 GCI Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 32<br>. 33                                                                                                                                                               |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br>10.0 OPERATING THE QLSLAC DEVICE .<br>10.1 Power-Up Sequence .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 32<br>. 33<br><b>. 35</b><br>. 35                                                                                                                                        |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br>10.0 OPERATING THE QLSLAC DEVICE .<br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 32<br>. 33<br><b>. 35</b><br>. 35<br>. 35                                                                                                                                |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 32<br>. 33<br><b>. 35</b><br>. 35<br>. 35<br>. 36                                                                                                                        |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .<br>10.4 SLIC Device Control and Data Lines .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 32<br>. 33<br><b>. 35</b><br>. 35<br>. 36<br>. 36                                                                                                                        |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b><br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .<br>10.4 SLIC Device Control and Data Lines .<br>10.5 Clock Mode Operation .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 32<br>. 33<br><b>. 35</b><br>. 35<br>. 35<br>. 36<br>. 36<br>. 36                                                                                                        |

| 9.1 GCI Timing Specifications.<br>9.2 GCI Waveforms.<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence.<br>10.2 PCM and GCI State Selection.<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode).<br>10.4 SLIC Device Control and Data Lines.<br>10.5 Clock Mode Operation.<br>10.6 E1 Multiplex Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 38                                                                                                               |

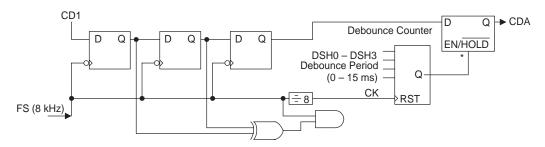

| 9.1 GCI Timing Specifications.<br>9.2 GCI Waveforms.<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence.<br>10.2 PCM and GCI State Selection.<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode).<br>10.4 SLIC Device Control and Data Lines.<br>10.5 Clock Mode Operation.<br>10.6 E1 Multiplex Operation.<br>10.7 Debounce Filters Operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 32<br>. 33<br><b>. 35</b><br>. 35<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40                                                                                                |

| 9.1 GCI Timing Specifications.<br>9.2 GCI Waveforms.<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence.<br>10.2 PCM and GCI State Selection.<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode).<br>10.4 SLIC Device Control and Data Lines.<br>10.5 Clock Mode Operation.<br>10.6 E1 Multiplex Operation.<br>10.7 Debounce Filters Operation.<br>10.8 Real-Time Data Register Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42                                                                                               |

| 9.1 GCI Timing Specifications.<br>9.2 GCI Waveforms.<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence.<br>10.2 PCM and GCI State Selection.<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode).<br>10.4 SLIC Device Control and Data Lines.<br>10.5 Clock Mode Operation.<br>10.6 E1 Multiplex Operation.<br>10.7 Debounce Filters Operation.<br>10.8 Real-Time Data Register Operation.<br>10.9 Interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42                                                                       |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .<br>10.4 SLIC Device Control and Data Lines .<br>10.5 Clock Mode Operation .<br>10.6 E1 Multiplex Operation .<br>10.7 Debounce Filters Operation .<br>10.8 Real-Time Data Register Operation .<br>10.9 Interrupt .<br>10.10 Interrupt Mask Register .                                                                                                                                                                                                                                                                                                                                                                                                         | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42<br>. 42                                                               |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b><br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .<br>10.4 SLIC Device Control and Data Lines .<br>10.5 Clock Mode Operation .<br>10.6 E1 Multiplex Operation .<br>10.7 Debounce Filters Operation .<br>10.8 Real-Time Data Register Operation .<br>10.9 Interrupt .<br>10.10 Interrupt Mask Register .<br>10.11 Active State .                                                                                                                                                                                                                                                                                                                                                                                   | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42<br>. 42                                                       |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .<br>10.4 SLIC Device Control and Data Lines .<br>10.5 Clock Mode Operation .<br>10.6 E1 Multiplex Operation .<br>10.7 Debounce Filters Operation .<br>10.8 Real-Time Data Register Operation .<br>10.9 Interrupt .<br>10.10 Interrupt Mask Register .<br>10.11 Active State .<br>10.12 Inactive State .                                                                                                                                                                                                                                                                                                                                                       | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42                                               |

| 9.1 GCI Timing Specifications.<br>9.2 GCI Waveforms.<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence.<br>10.2 PCM and GCI State Selection.<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode).<br>10.4 SLIC Device Control and Data Lines.<br>10.5 Clock Mode Operation.<br>10.6 E1 Multiplex Operation.<br>10.7 Debounce Filters Operation.<br>10.8 Real-Time Data Register Operation.<br>10.9 Interrupt.<br>10.10 Interrupt Mask Register.<br>10.11 Active State.<br>10.12 Inactive State.<br>10.13 Chopper Clock.                                                                                                                                                                                                                                                                                                                                             | . 32<br>. 33<br>. <b>35</b><br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42                                |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b><br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .<br>10.4 SLIC Device Control and Data Lines .<br>10.5 Clock Mode Operation .<br>10.6 E1 Multiplex Operation .<br>10.7 Debounce Filters Operation .<br>10.8 Real-Time Data Register Operation .<br>10.9 Interrupt .<br>10.10 Interrupt Mask Register .<br>10.11 Active State .<br>10.12 Inactive State .<br>10.13 Chopper Clock .<br>10.14 Reset States .                                                                                                                                                                                                                                                                                                        | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 43<br>43 |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b><br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .<br>10.4 SLIC Device Control and Data Lines .<br>10.5 Clock Mode Operation .<br>10.6 E1 Multiplex Operation .<br>10.7 Debounce Filters Operation .<br>10.8 Real-Time Data Register Operation .<br>10.9 Interrupt .<br>10.10 Interrupt Mask Register .<br>10.11 Active State .<br>10.12 Inactive State .<br>10.13 Chopper Clock .<br>10.14 Reset States .<br><b>11.0 Signal Processing</b> .                                                                                                                                                                                                                                                                     | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 43<br>. 43<br>. 44       |

| <ul> <li>9.1 GCI Timing Specifications.</li> <li>9.2 GCI Waveforms.</li> <li>10.0 OPERATING THE QLSLAC DEVICE.</li> <li>10.1 Power-Up Sequence.</li> <li>10.2 PCM and GCI State Selection.</li> <li>10.3 Channel Enable (EC) Register (PCM/MPI Mode).</li> <li>10.4 SLIC Device Control and Data Lines.</li> <li>10.5 Clock Mode Operation.</li> <li>10.6 E1 Multiplex Operation.</li> <li>10.7 Debounce Filters Operation.</li> <li>10.8 Real-Time Data Register Operation</li> <li>10.9 Interrupt.</li> <li>10.10 Interrupt Mask Register.</li> <li>10.11 Active State.</li> <li>10.12 Inactive State.</li> <li>10.13 Chopper Clock.</li> <li>10.14 Reset States</li> <li>11.0 Signal Processing</li> <li>11.1 Overview of Digital Filters</li> </ul>                                                                                                                                  | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 43<br>. 43<br>. 44               |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .<br>10.4 SLIC Device Control and Data Lines .<br>10.5 Clock Mode Operation .<br>10.6 E1 Multiplex Operation .<br>10.7 Debounce Filters Operation .<br>10.8 Real-Time Data Register Operation .<br>10.9 Interrupt .<br>10.10 Interrupt Mask Register .<br>10.11 Active State .<br>10.12 Inactive State .<br>10.13 Chopper Clock .<br>10.14 Reset States .<br><b>11.0 Signal Processing .</b><br>11.1 Overview of Digital Filters .<br>11.2 Two-Wire Impedance Matching .                                                                                                                                                                                       | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 43<br>. 43<br>. 44<br>. 44       |

| <ul> <li>9.1 GCI Timing Specifications .</li> <li>9.2 GCI Waveforms.</li> <li>10.0 OPERATING THE QLSLAC DEVICE .</li> <li>10.1 Power-Up Sequence .</li> <li>10.2 PCM and GCI State Selection .</li> <li>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .</li> <li>10.4 SLIC Device Control and Data Lines .</li> <li>10.5 Clock Mode Operation .</li> <li>10.6 E1 Multiplex Operation .</li> <li>10.7 Debounce Filters Operation .</li> <li>10.8 Real-Time Data Register Operation .</li> <li>10.9 Interrupt .</li> <li>10.10 Interrupt Mask Register .</li> <li>10.11 Active State .</li> <li>10.12 Inactive State .</li> <li>10.13 Chopper Clock .</li> <li>10.14 Reset States .</li> <li>11.0 Signal Processing .</li> <li>11.1 Overview of Digital Filters .</li> <li>11.2 Two-Wire Impedance Matching .</li> <li>11.3 Frequency Response Correction and Equalization .</li> </ul> | . 32<br>. 33<br>. 35<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 38<br>. 40<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42<br>. 42                               |

| 9.1 GCI Timing Specifications .<br>9.2 GCI Waveforms .<br><b>10.0 OPERATING THE QLSLAC DEVICE</b> .<br>10.1 Power-Up Sequence .<br>10.2 PCM and GCI State Selection .<br>10.3 Channel Enable (EC) Register (PCM/MPI Mode) .<br>10.4 SLIC Device Control and Data Lines .<br>10.5 Clock Mode Operation .<br>10.6 E1 Multiplex Operation .<br>10.7 Debounce Filters Operation .<br>10.8 Real-Time Data Register Operation .<br>10.9 Interrupt .<br>10.10 Interrupt Mask Register .<br>10.11 Active State .<br>10.12 Inactive State .<br>10.13 Chopper Clock .<br>10.14 Reset States .<br><b>11.0 Signal Processing .</b><br>11.1 Overview of Digital Filters .<br>11.2 Two-Wire Impedance Matching .                                                                                                                                                                                       | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36                                                                               |

| <ul> <li>9.1 GCI Timing Specifications.</li> <li>9.2 GCI Waveforms.</li> <li>10.0 OPERATING THE QLSLAC DEVICE.</li> <li>10.1 Power-Up Sequence.</li> <li>10.2 PCM and GCI State Selection.</li> <li>10.3 Channel Enable (EC) Register (PCM/MPI Mode).</li> <li>10.4 SLIC Device Control and Data Lines.</li> <li>10.5 Clock Mode Operation.</li> <li>10.6 E1 Multiplex Operation.</li> <li>10.6 E1 Multiplex Operation.</li> <li>10.8 Real-Time Data Register Operation.</li> <li>10.9 Interrupt.</li> <li>10.10 Interrupt Mask Register.</li> <li>10.11 Active State.</li> <li>10.12 Inactive State.</li> <li>10.13 Chopper Clock.</li> <li>10.14 Reset States.</li> <li>11.0 Signal Processing.</li> <li>11.1 Overview of Digital Filters</li> <li>11.3 Frequency Response Correction and Equalization.</li> <li>11.4 Transhybrid Balancing.</li> </ul>                                | . 32<br>. 33<br>. 35<br>. 35<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36                                                                               |

## **Table of Contents**

| 11.8 Data Upstream Interface (GCI Mode)                                                 | . 46 |

|-----------------------------------------------------------------------------------------|------|

| 11.9 Receive Signal Processing                                                          |      |

| 11.10 Receive PCM Interface (PCM/MPI Mode)                                              |      |

| 11.11 Data Downstream Interface (GCI Mode)                                              |      |

| 11.12 Analog Impedance Scaling Network (AISN)                                           | . 47 |

| 11.13 Speech Coding                                                                     | . 48 |

| 11.14 Double PCLK (DPCK) Operation (PCM/MPI Mode)                                       | . 48 |

| 11.15 Signaling on the PCM Highway (PCM/MPI Mode)                                       | . 48 |

| 11.16 Robbed-Bit Signaling Compatibility (PCM/MPI Mode)                                 |      |

| 11.17 Default Filter Coefficients                                                       | . 50 |

| 12.0 Command Description and Formats                                                    | . 50 |

| 12.1 Command Field Summary.                                                             | . 50 |

| 12.2 Microprocessor Interface Description                                               |      |

| 13.0 Summary of MPI Commands                                                            | . 54 |

| 14.0 MPI Command Structure                                                              |      |

| 14.1 00h Deactivate (Standby State).                                                    |      |

| 14.2 02h Software Reset.                                                                |      |

| 14.3 04h Hardware Reset                                                                 |      |

| 14.4 06h No Operation                                                                   |      |

| 14.5 0Eh Activate Channel (Operational State).                                          |      |

| 14.6 40/41h Write/Read Transmit Time Slot and PCM Highway Selection.                    |      |

| 14.7 42/43h Write/Read Receive Time Slot and PCM Highway Selection                      |      |

| 14.8 44/45h Write/Read Transmit Clock Slot, Receive Clock Slot, and Transmit Clock Edge |      |

| 14.9 46/47h Write/Read Chip Configuration Register                                      |      |

| 14.10 4A/4Bh Write/Read Channel Enable and Operating Mode Register                      |      |

| 14.11 4D/4Fh Read Real-Time Data Register.                                              |      |

| 14.12 50/51h Write/Read AISN and Analog Gains                                           |      |

| 14.13 52/53h Write/Read SLIC Device Input/Output Register                               |      |

| 14.14 54/55h Write/Read SLIC Device Input/Output Direction, Read Status Bits.           |      |

| 14.15 60/61h Write/Read Operating Functions                                             |      |

| 14.16 6C/6Dh Write/Read Interrupt Mask Register                                         |      |

| 14.17 70/71h Write/Read Operating Conditions                                            |      |

| 14.18 73h Read Revision Code Number (RCN)                                               |      |

| 14.19 80/81h Write/Read GX Filter Coefficients                                          | . 63 |

| 14.20 82/83h Write/Read GR Filter Coefficients                                          |      |

| 14.21 84/85h Write/Read Z Filter Coefficients (FIR and IIR)                             | . 64 |

| 14.22 86/87h Write/Read B1 Filter Coefficients                                          | . 65 |

| 14.23 88/89h Write/Read X Filter Coefficients                                           | . 66 |

| 14.24 8A/8Bh Write/Read R Filter Coefficients                                           | . 67 |

| 14.25 96/97h Write/Read B2 Filter Coefficients (IIR)                                    | . 68 |

| 14.26 98/99h Write/Read FIR Z Filter Coefficients (FIR only)                            | . 69 |

| 14.27 9A/9Bh Write/Read IIR Z Filter Coefficients (IIR only).                           | . 70 |

| 14.28 C8/C9h Write/Read Debounce Time Register                                          | .71  |

| 14.29 CDh Read Transmit PCM Data (PCM/MPI Mode Only)                                    | .71  |

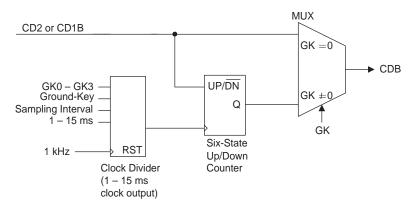

| 14.30 E8/E9h Write/Read Ground Key Filter                                               | . 72 |

| 15.0 General Circuit Interface (GCI) Specifications                                     | .72  |

| 15.1 GCI General Description                                                            |      |

| 15.2 GCI Format and Command Structure                                                   | . 73 |

| 15.3 Signaling and Control (SC) Channel                                                 |      |

| 15.4 Monitor Channel                                                                    |      |

| 15.5 Programming with the Monitor Channel                                               | . 79 |

| 15.6 Channel Identification Command (CIC)                                               |      |

|                                                                                         |      |

## **Table of Contents**

| 15.7 General Structure of Other Commands                | 81                |

|---------------------------------------------------------|-------------------|

| 16.0 Summary of Monitor Channel Commands (GCI Commands) | 82                |

| 16.1 TOP (Transfer Operation) Command                   | 83                |

| 16.2 SOP (Status Operation) Command                     | 83                |

| 16.3 SOP Control Byte Command Format                    | 84                |

| 16.4 COP (Coefficient Operation) Command                | 90                |

| 16.5 Details of COP, CSD Data Commands                  | 91                |

| 17.0 Programmable Filters                               | 98                |

| 17.1 User Test States and Operating Conditions          | . 100             |

| 17.2 A-Law and µ-Law Companding                         | . 100             |

| 18.0 APPLICATIONS                                       | . 103             |

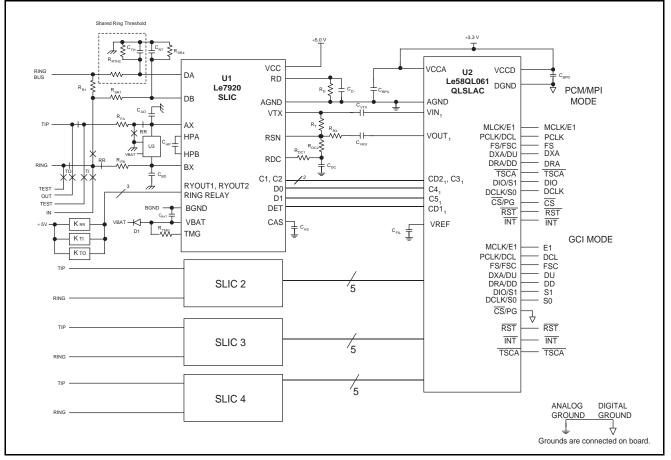

| 19.0 Application Circuit                                | . 104             |

| 20.0 Line Card Parts List                               | . 105             |

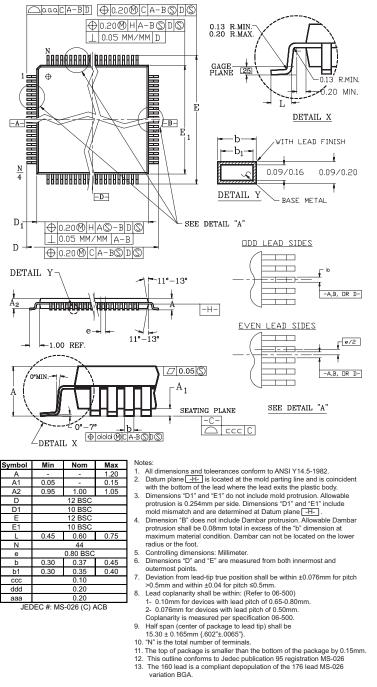

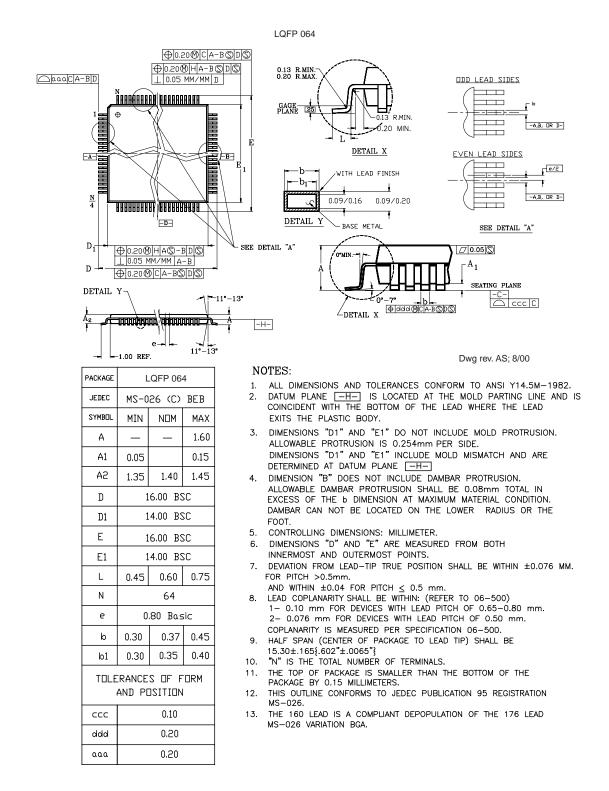

| 21.0 Physical Dimensions                                | . 106             |

| 21.1 44-Pin TQFP                                        | . 10 <del>6</del> |

# List of Figures

| Figure 1 - Block Diagram                                                        | 1   |

|---------------------------------------------------------------------------------|-----|

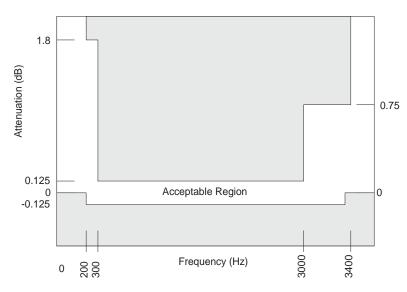

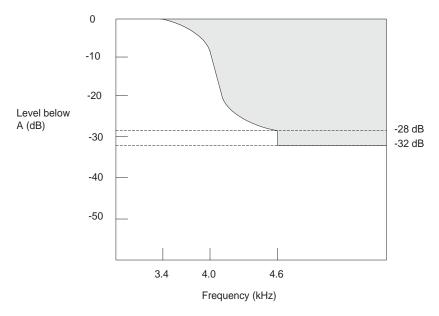

| Figure 2 - Transmit Path Attenuation vs. Frequency                              | 19  |

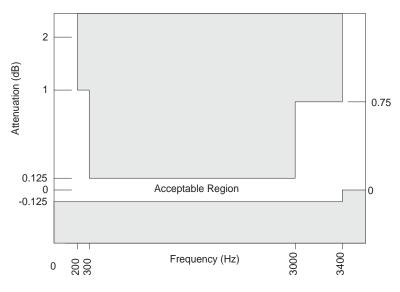

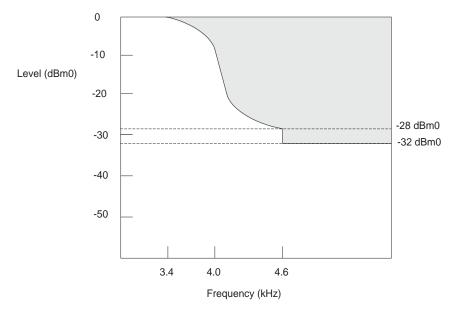

| Figure 3 - Receive Path Attenuation vs. Frequency                               | 20  |

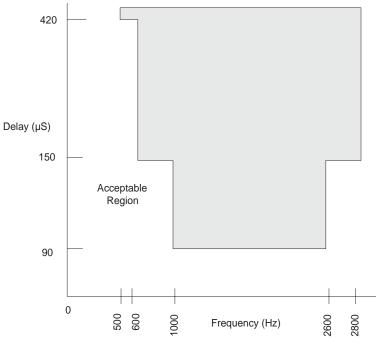

| Figure 4 - Group Delay Distortion                                               |     |

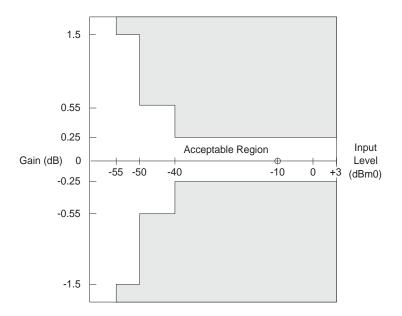

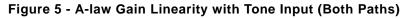

| Figure 5 - A-law Gain Linearity with Tone Input (Both Paths)                    |     |

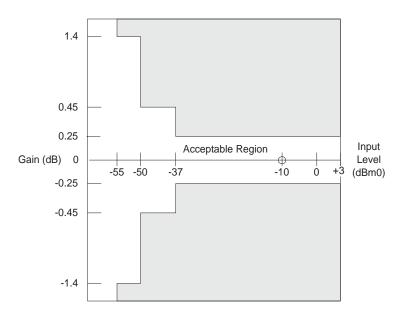

| Figure 6 - µ-law Gain Linearity with Tone Input (Both Paths)                    |     |

| Figure 7 - Total Distortion with Tone Input (Both Paths)                        |     |

| Figure 8 - Discrimination Against Out-of-Band Signals                           | 23  |

| Figure 9 - Spurious Out-of-Band Signals                                         |     |

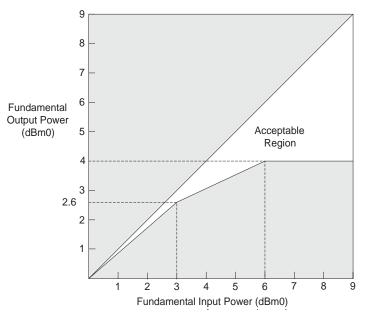

| Figure 10 - Analog-to-Analog Overload Compression                               | 24  |

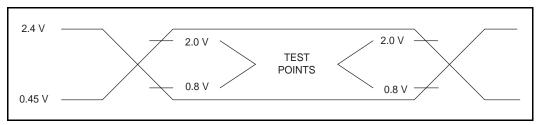

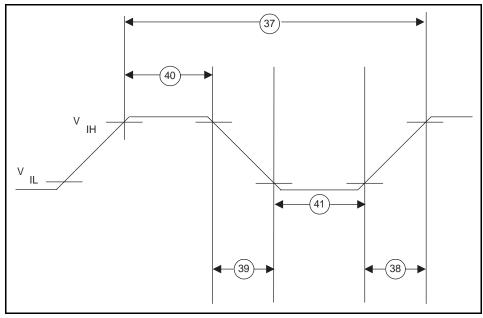

| Figure 11 - Input and Output Waveforms for AC Tests.                            |     |

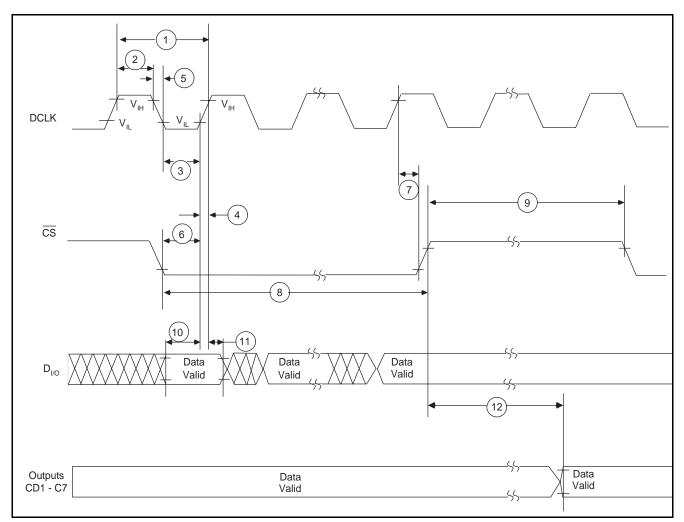

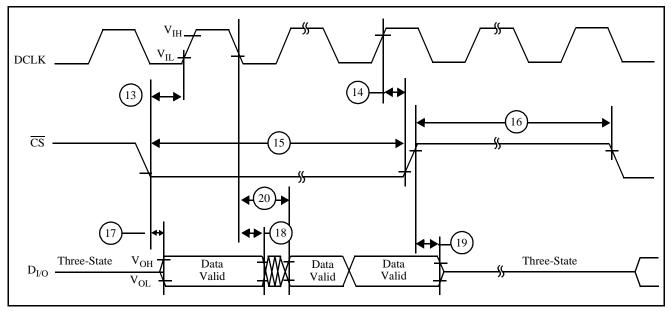

| Figure 12 - Microprocessor Interface (Input Mode)                               | 28  |

| Figure 13 - Microprocessor Interface (Output Mode)                              |     |

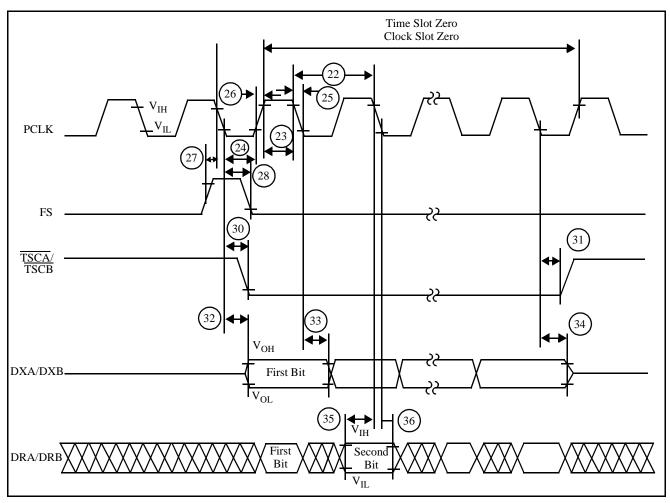

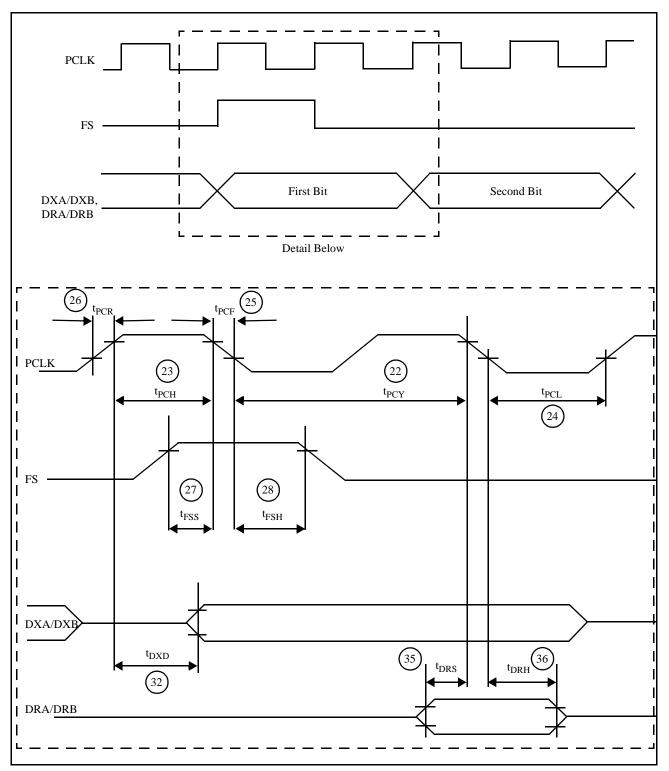

| Figure 14 - PCM Highway Timing for XE = 0 (Transmit on Negative PCLK Edge)      | 29  |

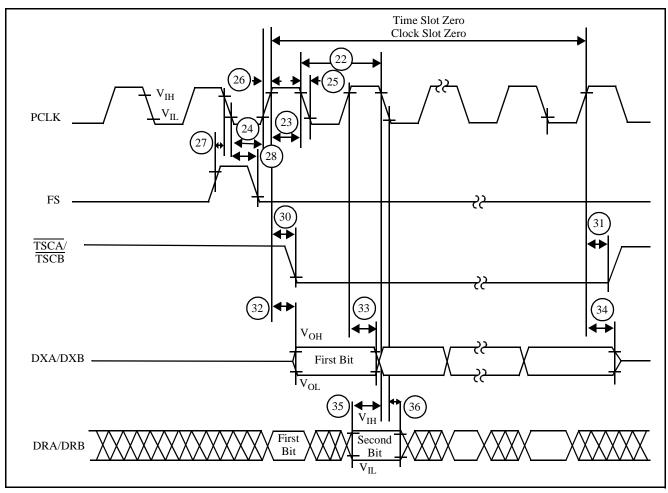

| Figure 15 - PCM Highway Timing for XE = 1 (Transmit on Positive PCLK Edge)      | 30  |

| Figure 16 - Double PCLK PCM Timing                                              | 31  |

| Figure 17 - Master Clock Timing                                                 |     |

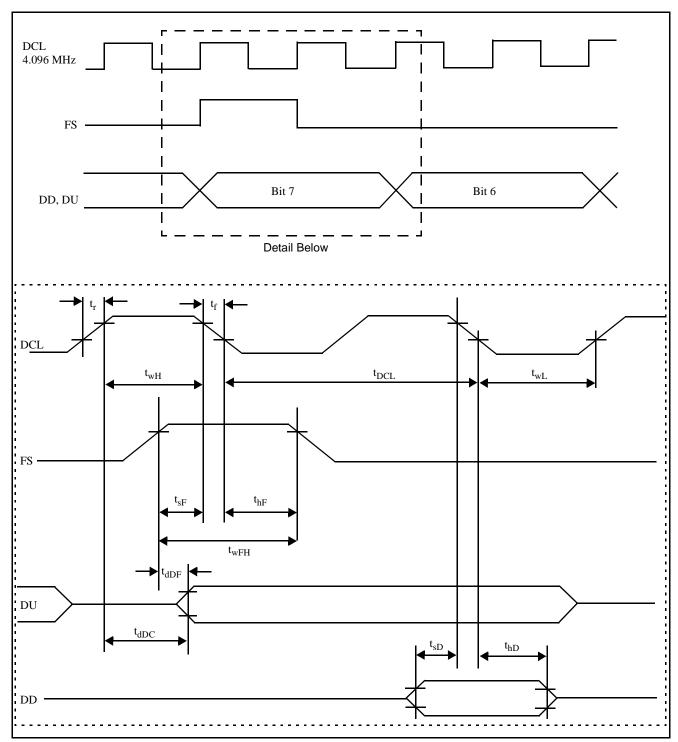

| Figure 18 - 4.096 MHz DCL Operation                                             |     |

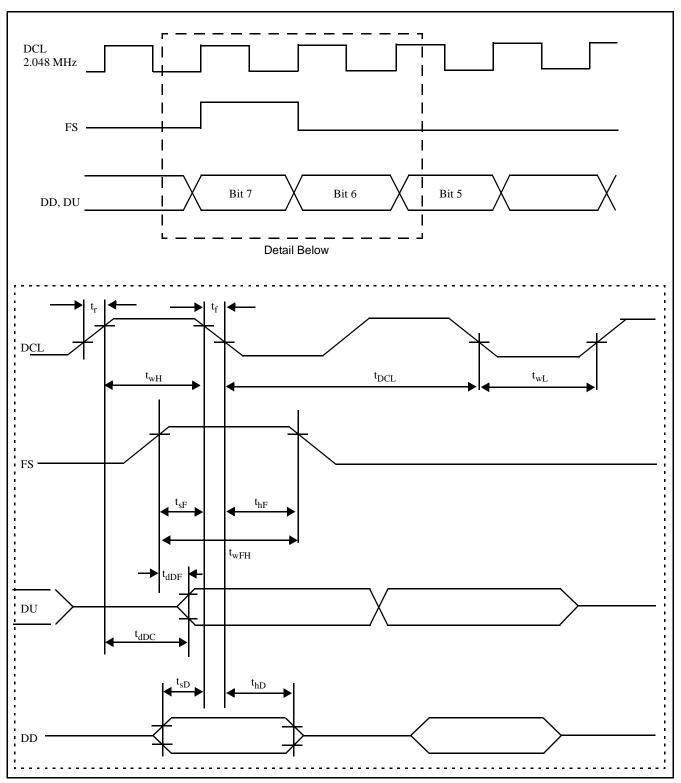

| Figure 19 - 2.048 MHz DCL Operation                                             |     |

| Figure 20 - Clock Mode Options (PCM/MPI Mode)                                   |     |

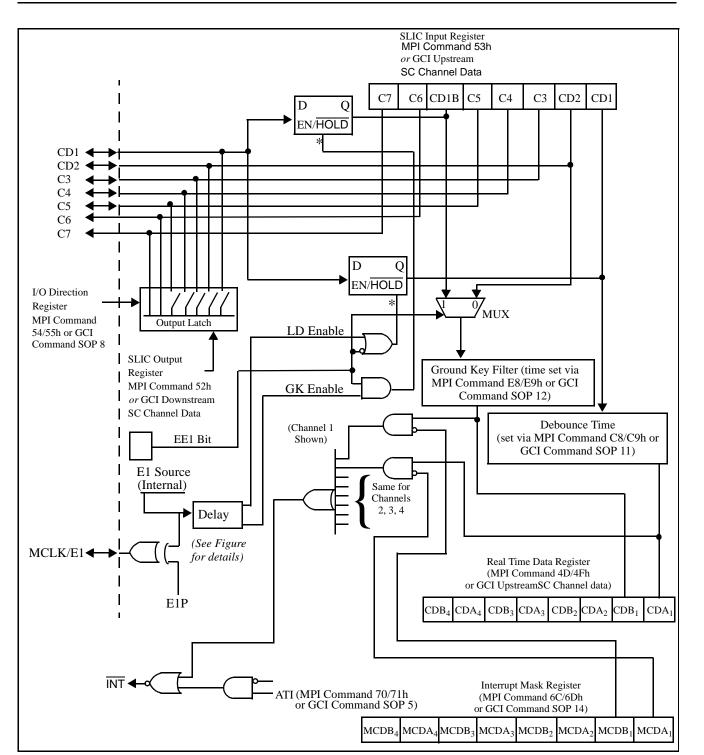

| Figure 21 - SLIC Device I/O, E1 Multiplex and Real-Time Data Register Operation | 39  |

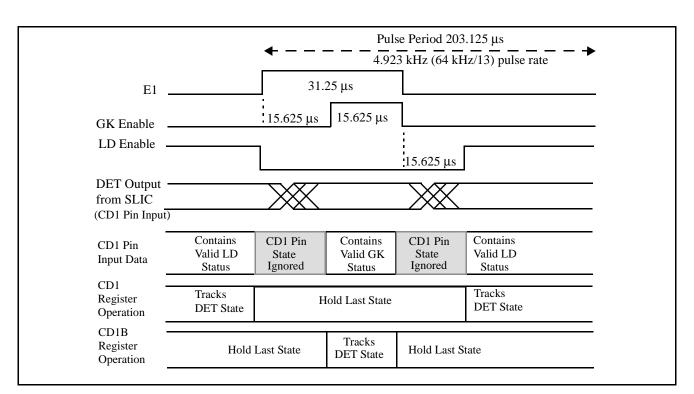

| Figure 22 - E1 Multiplex Internal Timing                                        |     |

| Figure 23 - MPI Real-Time Data Register                                         |     |

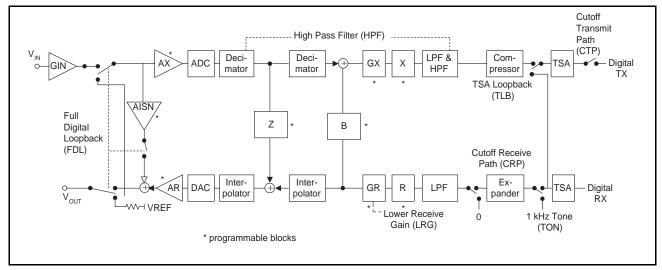

| Figure 24 - QLSLAC Device Transmission Block Diagram                            | 44  |

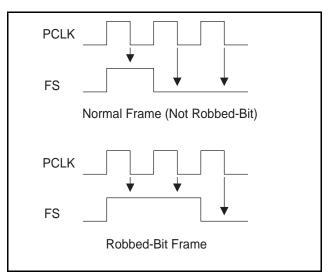

| Figure 25 - Robbed-Bit Frame                                                    | 49  |

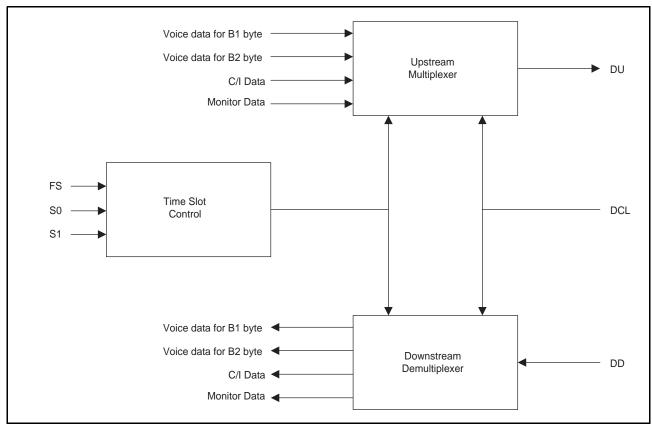

| Figure 26 - Time Slot Control and GCI Interface                                 | 73  |

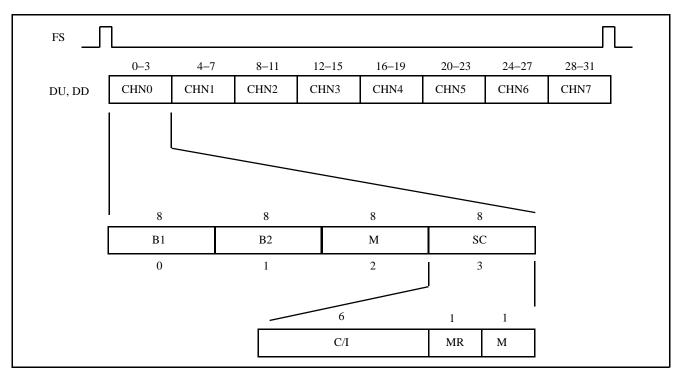

| Figure 27 - Multiplexed GCI Time Slot Structure                                 | 74  |

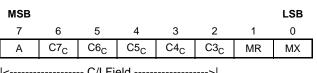

| Figure 28 - Security Procedure for C/I Downstream Bytes                         | 75  |

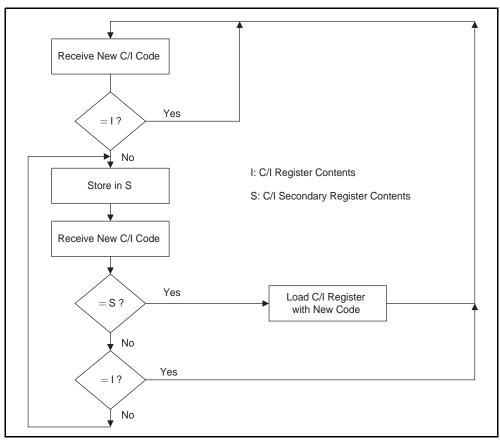

| Figure 29 - Maximum Speed Monitor Handshake Timing                              | 77  |

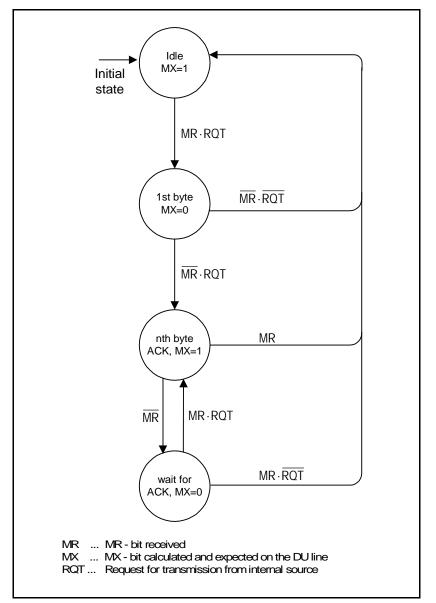

| Figure 30 - Monitor Transmitter Mode Diagram                                    |     |

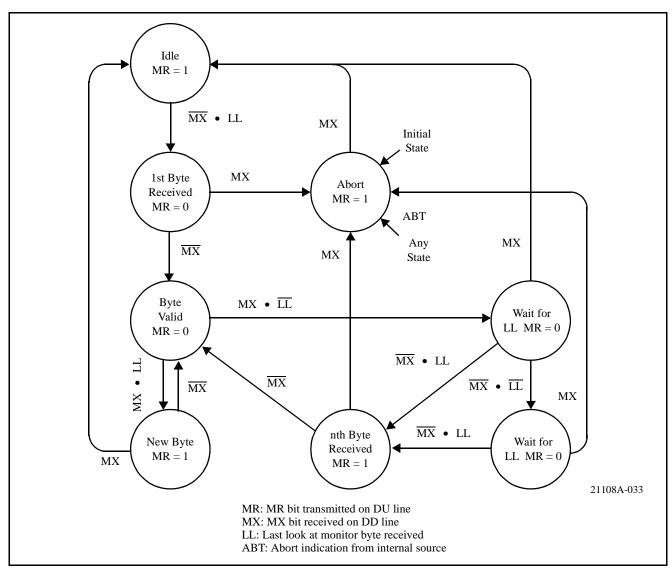

| Figure 31 - Monitor Receiver State Diagram                                      |     |

| Figure 32 - Le7920 SLIC/QLSLAC Device Application Circuit.                      | 104 |

## List of Tables

| Table 1 - QLSLAC Device Features    Image: Comparison of the sector of the secto  | 8   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2 - 0 dBm0 Voltage Definitions with Unity Gain in X, R, GX, GR, AX and AR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18  |

| Table 3 - PCM/GCI Mode Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35  |

| Table 4 - Channel Parameters    Image: Channel Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50  |

| Table 5 - Channel Monitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 52  |