# 2.7 V to 5.5 V, 140 µA, Rail-to-Rail Voltage Output 10-Bit DAC in a SOT-23

Data Sheet AD5310

#### **FEATURES**

Single 10-bit DAC

6-lead SOT-23 and 8-lead µSOIC packages

Micropower operation: 140 µA @ 5 V

Power-down to 200 nA @ 5 V, 50 nA @ 3 V

2.7 V to 5.5 V power supply

Guaranteed monotonic by design

Reference derived from power supply

Power-on reset to 0 V

Three power-down functions

Low power serial interface with Schmitt triggered inputs

On-chip output buffer amplifier, rail-to-rail operation

SYNC interrupt facility

Qualified for automotive applications

#### **APPLICATIONS**

Portable battery-powered instruments

Digital gain and offset adjustment

Programmable voltage and current sources

Programmable attenuators

#### **GENERAL DESCRIPTION**

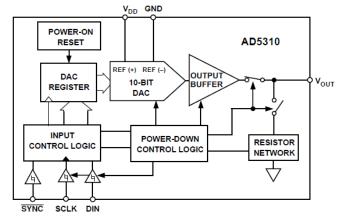

The AD5310¹ is a single, 10-bit, buffered voltage output DAC that operates from a single 2.7 V to 5.5 V supply, consuming 115  $\mu$ A at 3 V. Its on-chip precision output amplifier allows rail-to-rail output swing. The AD5310 utilizes a versatile 3-wire serial interface that operates at clock rates of up to 30 MHz and is compatible with standard SPI $^{\text{\tiny TM}}$ , QSPI $^{\text{\tiny TM}}$ , MICROWIRE $^{\text{\tiny SM}}$ , and DSP interface standards.

The reference for AD5310 is derived from the power supply inputs and, therefore, provides the widest dynamic output range. The part incorporates a power-on reset circuit that ensures that the DAC output powers up to 0 V and remains there until a valid write takes place to the device. The part contains a power-down feature, which reduces the current consumption of the device to 200 nA at 5 V and provides software-selectable output loads while in power-down mode. The part is put into power-down mode over the serial interface.

The low power consumption of this part in normal operation makes it ideally suited for portable, battery-operated equipment. The power consumption is 0.7 mW at 5 V, reducing to 1  $\mu W$  in power-down mode.

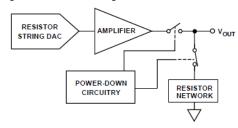

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

The AD5310 is one of a family of pin-compatible DACs. The AD5300 is the 8-bit version, and the AD5320 is the 12-bit version. The AD5300/AD5310/AD5320 are available in 6-lead SOT-23 packages and 8-lead  $\mu$ SOIC packages.

#### **PRODUCT HIGHLIGHTS**

- 1. Available in 6-lead SOT-23 and 8-lead μSOIC packages.

- 2. Low power, single-supply operation. This part operates from a single 2.7 V to 5.5 V supply and typically consumes 0.35 mW at 3 V and 0.7 mW at 5 V, making it ideal for battery-powered applications.

- 3. The on-chip output buffer amplifier allows the output of the DAC to swing rail-to-rail with a slew rate of 1 V/ $\mu$ s.

- 4. Reference derived from the power supply.

- 5. High speed serial interface with clock speeds of up to 30 MHz. Designed for very low power consumption. The interface only powers up during a write cycle.

- 6. Power-down capability. When powered down, the DAC typically consumes 50 nA at 3 V and 200 nA at 5 V.

<sup>&</sup>lt;sup>1</sup> Patent pending; protected by U.S. Patent No. 5684481.

# **TABLE OF CONTENTS**

| reatures                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| Functional Block Diagram                     | 1  |

| General Description                          | 1  |

| Product Highlights                           | 1  |

| Revision History                             | 2  |

| Specifications                               | 3  |

| Timing Characteristics                       | 4  |

| Absolute Maximum Ratings                     | 5  |

| ESD Caution                                  | 5  |

| Pin Configurations and Function Descriptions | 6  |

| Typical Performance Characteristics          | 7  |

| Terminology                                  | 10 |

| Theory of Operation                          | 11 |

| D/A Section                                  | 11 |

| Resistor String                              | 11 |

|                                              |    |

| Output Amplifier                             | 11 |

|----------------------------------------------|----|

| Serial Interface                             | 11 |

| Input Shift Register                         | 11 |

| SYNC Interrupt                               | 12 |

| Power-On Reset                               | 12 |

| Power-Down Modes                             | 12 |

| Microprocessor Interfacing                   | 12 |

| Applications Information                     | 14 |

| Using REF19x as a Power Supply for AD5310    | 14 |

| Bipolar Operation Using the AD5310           | 14 |

| Using AD5310 with an Opto-Isolated Interface | 14 |

| Power Supply Bypassing and Grounding         | 15 |

| Outline Dimensions                           | 16 |

| Ordering Guide                               | 16 |

| Automotive Products                          | 16 |

#### **REVISION HISTORY**

#### 7/12—Rev. A to Rev. B

| Updated Format                                   | Universal |

|--------------------------------------------------|-----------|

| Changes to Features                              |           |

| Change to Figure 9 Caption                       |           |

| Changes to AD5310 to ADSP-2101 Interface Section |           |

| and Figure 27                                    | 12        |

| Updated Outline Dimensions                       | 16        |

| Changes to Ordering Guide                        | 16        |

| Added Automotive Products Section                | 16        |

|                                                  |           |

5/99—Rev. 0 to Rev. A

## **SPECIFICATIONS**

$V_{DD} = 2.7 \ V \ to \ 5.5 \ V; temperature \ range = -40 ^{\circ}C \ to \ +105 ^{\circ}C \ R_{L} = 2 \ k\Omega \ to \ GND; C_{L} = 500 \ pF \ to \ GND; all \ specifications \ T_{MIN} \ to \ T_{MAX} \ unless \ T_{MIN} \ to \ T_{MAX} \ to \$ otherwise noted

Table 1.

| Parameter                                  | Min | Тур   | Max      | Unit          | Test Conditions/Comments                                          |

|--------------------------------------------|-----|-------|----------|---------------|-------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>            |     |       |          |               |                                                                   |

| Resolution                                 | 10  |       |          | Bits          |                                                                   |

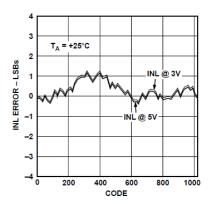

| Relative Accuracy                          |     |       | ±4       | LSB           | See Figure 5                                                      |

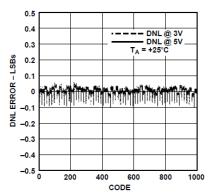

| Differential Nonlinearity                  |     |       | ±0.5     | LSB           | Guaranteed monotonic by design (see Figure 6)                     |

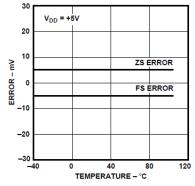

| Zero Code Error                            |     | 5     | 40       | mV            | All 0s loaded to DAC register (see Figure 9)                      |

| Full-Scale Error                           |     | -0.15 | -1.25    | % of FSR      | All 1s loaded to DAC register (see Figure 9)                      |

| Gain Error                                 |     |       | ±1.25    | % of FSR      |                                                                   |

| Zero Code Error Drift                      |     | -20   |          | μV/°C         |                                                                   |

| Gain Temperature Coefficient               |     | -5    |          | ppm of FSR/°C |                                                                   |

| OUTPUT CHARACTERISTICS <sup>2</sup>        |     |       |          |               |                                                                   |

| Output Voltage Range                       | 0   |       | $V_{DD}$ | V             |                                                                   |

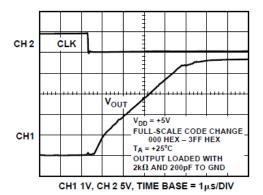

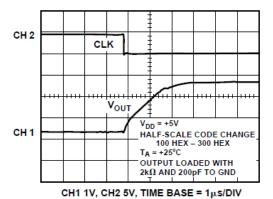

| Output Voltage Settling Time               |     | 6     | 8        | μs            | 1/4 scale to 3/4 scale change (100 hex to 300 hex)                |

| Slew Rate                                  |     | 1     |          | V/µs          | $R_L = 2 \text{ k}\Omega$ ; 0 pF < $C_L$ < 500 pF (see Figure 19) |

| Capacitive Load Stability                  |     | 470   |          | pF            | $R_L = \infty$                                                    |

|                                            |     | 1000  |          | pF            | $R_L = 2 k\Omega$                                                 |

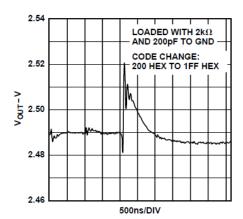

| Digital-to-Analog Glitch Impulse           |     | 20    |          | nV-s          | 1 LSB change around major carry (see Figure 22)                   |

| Digital Feedthrough                        |     | 0.5   |          | nV-s          |                                                                   |

| DC Output Impedance                        |     | 1     |          | Ω             |                                                                   |

| Short-Circuit Current                      |     | 50    |          | mA            | $V_{DD} = 5 V$                                                    |

|                                            |     | 20    |          | mA            | $V_{DD} = 3 V$                                                    |

| Power-Up Time                              |     | 2.5   |          | μs            | Coming out of power-down mode, $V_{DD} = 5 \text{ V}$             |

|                                            |     | 5     |          | μs            | Coming out of power-down mode, $V_{DD} = 3 \text{ V}$             |

| LOGIC INPUTS <sup>2</sup>                  |     |       |          |               |                                                                   |

| Input Current                              |     |       | ±1       | μΑ            |                                                                   |

| V <sub>INL</sub> , Input Low Voltage       |     |       | 0.8      | V             | $V_{DD} = 5 V$                                                    |

| V <sub>INL</sub> , Input Low Voltage       |     |       | 0.6      | V             | $V_{DD} = 3 V$                                                    |

| V <sub>INH</sub> , Input High Voltage      | 2.4 |       |          | V             | $V_{DD} = 5 V$                                                    |

| V <sub>INH</sub> , Input High Voltage      | 2.1 |       |          | V             | $V_{DD} = 3 V$                                                    |

| Pin Capacitance                            |     |       | 3        | pF            |                                                                   |

| POWER REQUIREMENTS                         |     |       |          |               |                                                                   |

| $V_{DD}$                                   | 2.7 |       | 5.5      | V             |                                                                   |

| I <sub>DD</sub> (Normal Mode)              |     |       |          |               | DAC active and excluding load current                             |

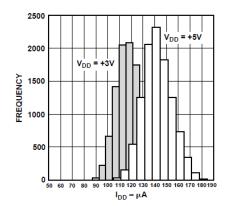

| $V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}$ |     | 140   | 250      | μΑ            | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                              |

| $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ |     | 115   | 200      | μΑ            | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                              |

| I <sub>DD</sub> (All Power-Down Modes)     |     |       |          |               |                                                                   |

| $V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}$ |     | 0.2   | 1        | μΑ            | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                              |

| $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ |     | 0.05  | 1        | μA            | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                              |

| Power Efficiency                           |     |       |          |               |                                                                   |

| louт/I <sub>DD</sub>                       |     | 93    |          | %             | $I_{LOAD} = 2 \text{ mA}, V_{DD} = 5 \text{ V}$                   |

<sup>&</sup>lt;sup>1</sup> Linearity calculated using a reduced code range of 12 to 1011. Output unloaded. <sup>2</sup> Guaranteed by design and characterization; not production tested.

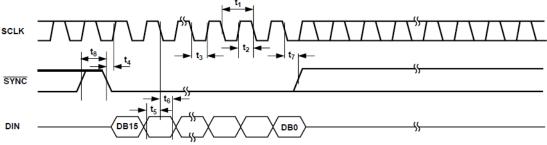

#### **TIMING CHARACTERISTICS**

$V_{\text{DD}}$  = 2.7 V to 5.5 V; all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$  unless otherwise noted

Table 2.

|                             | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> |                                  |        |                                       |

|-----------------------------|----------------------------------------------|----------------------------------|--------|---------------------------------------|

| Parameter <sup>1, 2</sup>   | V <sub>DD</sub> = 2.7 V to 3.6 V             | V <sub>DD</sub> = 3.6 V to 5.5 V | Unit   | Test Conditions/Comments              |

| t <sub>1</sub> <sup>3</sup> | 50                                           | 33                               | ns min | SCLK cycle time                       |

| $t_2$                       | 13                                           | 13                               | ns min | SCLK high time                        |

| t <sub>3</sub>              | 22.5                                         | 13                               | ns min | SCLK low time                         |

| t <sub>4</sub>              | 0                                            | 0                                | ns min | SYNC to SCLK rising edge setup time   |

| <b>t</b> <sub>5</sub>       | 5                                            | 5                                | ns min | Data setup time                       |

| t <sub>6</sub>              | 4.5                                          | 4.5                              | ns min | Data hold time                        |

| t <sub>7</sub>              | 0                                            | 0                                | ns min | SCLK falling edge to SYNC rising edge |

| t <sub>8</sub>              | 50                                           | 33                               | ns min | Minimum SYNC high time                |

$<sup>^{1}</sup>$  All input signals are specified with tr = tf = 5 ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2.  $^{2}$  See Figure 2.

$<sup>^3</sup>$  Maximum SCLK frequency is 30 MHz at  $V_{DD}$  = 3.6 V to 5.5 V and 20 MHz at  $V_{DD}$  = 2.7 V to 3.6 V.

Figure 2. Serial Write Operation

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C unless otherwise noted

#### Table 3.

| Table 3.                                  |                                            |

|-------------------------------------------|--------------------------------------------|

| Parameter                                 | Rating                                     |

| V <sub>DD</sub> to GND                    | −0.3 V to +7 V                             |

| Digital Input Voltage to GND              | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Vout to GND                               | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Operating Temperature Range               |                                            |

| Industrial (B Version)                    | −40°C to +105°C                            |

| Storage Temperature Range                 | −65°C to +150°C                            |

| Junction Temperature (T <sub>J</sub> Max) | +150°C                                     |

| SOT-23 Package                            |                                            |

| Power Dissipation                         | $(T_J max - T_A)/\theta_{JA}$              |

| $\theta_{JA}$ Thermal Impedance           | 240°C/W                                    |

| Lead Temperature, Soldering               |                                            |

| Vapor Phase (60 sec)                      | 215℃                                       |

| Infrared (15 sec)                         | 220°C                                      |

| μSOIC Package                             |                                            |

| Power Dissipation                         | $(T_J max - T_A)/\theta_{JA}$              |

| $\theta_{JA}$ Thermal Impedance           | 206°C/W                                    |

| $\theta_{JC}$ Thermal Impedance           | 44°C/W                                     |

| Lead Temperature, Soldering               |                                            |

| Vapor Phase (60 sec)                      | 215°C                                      |

| Infrared (15 sec)                         | 220°C                                      |

|                                           | •                                          |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

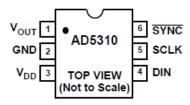

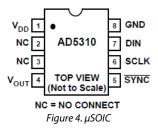

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. SOT-23

**Table 4. SOT-23 Pin Function Descriptions**

| Pin No. | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>OUT</sub> | Analog Output Voltage from DAC. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                                                  |

| 2       | GND              | Ground Reference Point for All Circuitry on the Part.                                                                                                                                                                                                                                                                                                                                                                                             |

| 3       | $V_{DD}$         | Power Supply Input. These parts can be operated from 2.5 V to 5.5 V, and VDD should be decoupled to GND.                                                                                                                                                                                                                                                                                                                                          |

| 4       | DIN              | Serial Data Input. This device has a 16-bit shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                                                                                      |

| 5       | SCLK             | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates of up to 30 MHz.                                                                                                                                                                                                                                                                                |

| 6       | SYNC             | Level Triggered Control Input (Active Low). This is the frame synchronization signal for the input data. When SYNC goes low, it enables the input shift register, and data is transferred in on the falling edges of the following clocks. The DAC is updated following the 16th clock cycle unless SYNC is taken high before this edge, in which case the rising edge of SYNC acts as an interrupt and the write sequence is ignored by the DAC. |

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 5. Typical INL

Figure 6. Typical DNL

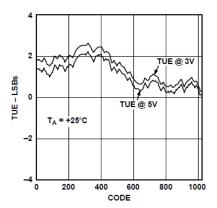

Figure 7. Typical Total Unadjusted Error

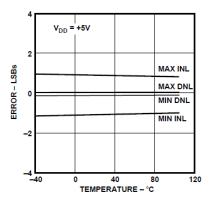

Figure 8. INL Error and DNL Error vs. Temperature

Figure 9. Zero Code Error and Full-Scale Error vs. Temperature

Figure 10.  $I_{DD}$  Histogram with  $V_{DD} = 3 V$  and  $V_{DD} = 5 V$

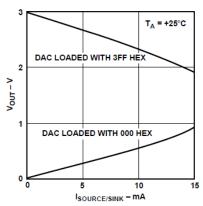

Figure 11. Source and Sink Current Capability with  $V_{DD} = 3 V$

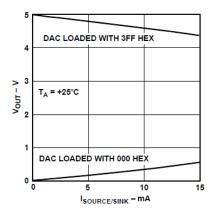

Figure 12. Source and Sink Current Capability with  $V_{DD} = 5 V$

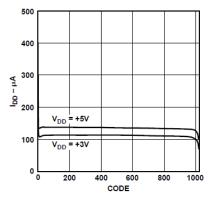

Figure 13. Supply Current vs. Code

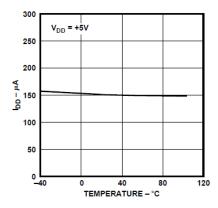

Figure 14. Supply Current vs. Temperature

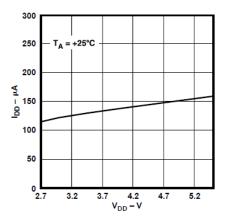

Figure 15. Supply Current vs. Supply Voltage

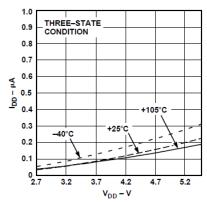

Figure 16. Power-Down Current vs. Supply Voltage

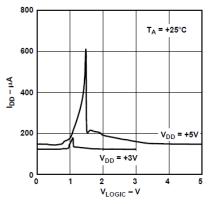

Figure 17. Supply Current vs. Logic Input Voltage

Figure 18. Full-Scale Settling Time

Figure 19. Half-Scale Settling Time

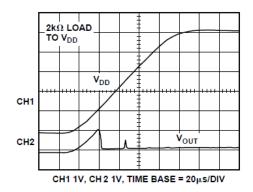

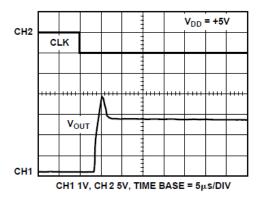

Figure 20. Power-On Reset to 0 V

Figure 21. Exiting Power-Down (200 Hex Loaded)

Figure 22. Digital-to-Analog Glitch Impulse

#### **TERMINOLOGY**

#### **Relative Accuracy**

For the DAC, relative accuracy or integral nonlinearity (INL) is a measure of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. A typical INL vs. code plot is shown in Figure 5.

#### **Differential Nonlinearity**

Differential nonlinearity (DNL) is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB maximum ensures monotonicity. This DAC is guaranteed monotonic by design. A typical DNL vs. code plot is shown in Figure 6.

#### Zero Code Error

Zero code error is a measure of the output error when zero code (000 hex) is loaded to the DAC register. Ideally, the output should be 0 V. The zero code error is always positive in the AD5310 because the output of the DAC cannot go below 0 V. It is due to a combination of the offset errors in the DAC and output amplifier. Zero code error is expressed in mV. A plot of zero code error vs. temperature is shown in Figure 9.

#### **Full-Scale Error**

Full-scale error is a measure of the output error when full-scale code (3FF Hex) is loaded to the DAC register. Ideally, the output should be  $V_{\text{DD}}-1$  LSB. Full-scale error is expressed as a percentage of the full-scale range. A plot of full-scale error vs. temperature is shown in Figure 9.

#### **Gain Error**

Gain error is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal expressed as a percentage of the full-scale range.

#### **Total Unadjusted Error**

Total unadjusted error (TUE) is a measure of the output error that takes all the various errors into account. A typical TUE vs. code plot is shown in Figure 7.

#### Zero Code Error Drift

Zero code error drift is a measure of the change in zero code error with a change in temperature. It is expressed in  $\mu V/^{\circ}C$ .

#### **Gain Error Drift**

Gain error drift is a measure of the change in gain error with changes in temperature. It is expressed in (ppm of full-scale range)/°C.

#### Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nV-s and is measured when the digital input code is changed by 1 LSB at the major carry transition (1FF hex to 200 hex). See Figure 22.

#### Digital Feedthrough

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC but is measured when the DAC output is not updated. It is specified in nV-s and is measured with a full-scale code change on the data bus, that is, from all 0s to all 1s and vice versa.

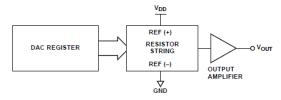

# THEORY OF OPERATION D/A SECTION

The AD5310 DAC is fabricated on a CMOS process. The architecture consists of a string DAC followed by an output buffer amplifier. Because there is no reference input pin, the power supply  $(V_{\rm DD})$  acts as the reference. Figure 23 shows a block diagram of the DAC architecture.

Figure 23. DAC Architecture

Because the input coding to the DAC is straight binary, the ideal output voltage is given by

$$V_{OUT} = V_{DD} \times \left(\frac{D}{1024}\right)$$

where *D* is the decimal equivalent of the binary code that is loaded to the DAC register; it can range from 0 to 1023.

Figure 24. Resistor String

#### RESISTOR STRING

The resistor string section is shown in Figure 24. It is simply a string of resistors, each of value R. The code loaded to the DAC register determines at what node on the string the voltage is tapped off to be fed into the output amplifier. The voltage is tapped off by closing one of the switches connecting the string

to the amplifier. Because it is a string of resistors, it is guaranteed monotonic.

#### **OUTPUT AMPLIFIER**

The output buffer amplifier is capable of generating rail-to-rail voltages on its output, which results in an output range of 0 V to V<sub>DD</sub>. It is capable of driving a load of 2 k $\Omega$  in parallel with 1000 pF to GND. The source and sink capabilities of the output amplifier can be seen in Figure 11 and Figure 12. The slew rate is 1 V/ $\mu$ s with a half-scale settling time of 6  $\mu$ s with the output loaded.

#### **SERIAL INTERFACE**

The AD5310 has a 3-wire serial interface (SYNC, SCLK, and DIN) that is compatible with SPI, QSPI, and MICROWIRE interface standards, as well as most DSPs. See Figure 2 for a timing diagram of a typical write sequence.

The write sequence begins by bringing the SYNC line low. Data from the DIN line is clocked into the 16-bit shift register on the falling edge of SCLK. The serial clock frequency can be as high as 30 MHz, making the AD5310 compatible with high speed DSPs. On the 16th falling clock edge, the last data bit is clocked in and the programmed function is executed (that is, a change in DAC register contents and/or a change in the mode of operation). At this stage, the SYNC line can be kept low or be brought high. In either case, it must be brought high for a minimum of 33 ns before the next write sequence so that a falling edge of SYNC can initiate the next write sequence. Because the SYNC buffer draws more current when  $V_{\rm IN}$  = 2.4 V than it does when  $V_{\rm IN}$  = 0.8 V, SYNC should be idled low between write sequences for even lower power operation of the part. As previously mentioned, however, it must be brought high again just before the next write sequence.

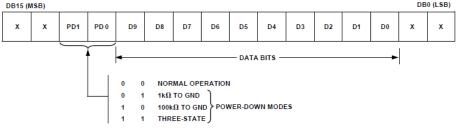

#### **INPUT SHIFT REGISTER**

The input shift register is 16 bits wide (see Figure 25). The first two bits are don't cares. The next two bits are control bits that control which mode of operation the part is in (normal mode or one of the three power-down modes). There is a more complete description of the various modes in the Power-Down Modes section. The next 10 bits are the data bits. These are transferred to the DAC register on the 16th falling edge of SCLK. Finally, the last two bits are don't cares.

Figure 25. Input Register Contents

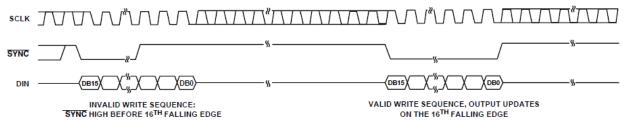

#### **SYNC INTERRUPT**

In a normal write sequence, the SYNC line is kept low for at least 16 falling edges of SCLK, and the DAC is updated on the 16th falling edge. However, if SYNC is brought high before the 16th falling edge, this acts as an interrupt to the write sequence. The shift register is reset, and the write sequence is seen as invalid. Neither an update of the DAC register contents or a change in the operating mode occurs (see Figure 28).

#### **POWER-ON RESET**

The AD5310 contains a power-on reset circuit that controls the output voltage during power-up. The DAC register is filled with 0s, and the output voltage is 0 V. It remains there until a valid write sequence is performed to the DAC. This is useful in applications where it is important to know the state of the output of the DAC while it is in the process of powering up.

#### **POWER-DOWN MODES**

The AD5310 contains four separate modes of operation. These modes are software programmable by setting two bits (DB13 and DB12) in the control register. Table 5 shows how the state of the bits corresponds to the mode of operation of the device.

Table 5. Modes of Operation for the AD5310

| Operating Mode        | DB13 | DB12 |

|-----------------------|------|------|

| Normal Operation      | 0    | 0    |

| Power-Down Modes      |      |      |

| 1 $k\Omega$ to GND    | 0    | 1    |

| 100 k $\Omega$ to GND | 1    | 0    |

| Three-State           | 1    | 1    |

When both bits are set to 0, the part works normally with its normal power consumption of 140  $\mu$ A at 5 V. However, for the three power-down modes, the supply current falls to 200 nA at 5 V (50 nA at 3 V). Not only does the supply current fall, but the output stage is also internally switched from the output of the amplifier to a resistor network of known values. This has the advantage of knowing the output impedance of the part when

the part is in power-down mode. There are three options. The output is connected internally to GND through a 1 k $\Omega$  resistor, a 100 k $\Omega$  resistor, or it is left open-circuited (three-state). The output stage is illustrated in Figure 26.

Figure 26. Output Stage During Power-Down

The bias generator, the output amplifier, the resistor string, and other associated linear circuitry are all shut down when the power-down mode is activated. However, the contents of the DAC register are unaffected when in power-down. The time to exit power-down is typically 2.5  $\mu s$  for  $V_{\rm DD}=5~V$  and 5  $\mu s$  for  $V_{\rm DD}=3~V$  (see Figure 21).

#### MICROPROCESSOR INTERFACING

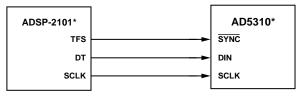

#### AD5310 to ADSP-2101 Interface

Figure 27 shows a serial interface between the AD5310 and the ADSP-2101. The ADSP-2101 should be set up to operate in the SPORT transmit alternate framing mode. The ADSP-2101SPORT is programmed through the SPORT control register and should be configured as follows: internal clock operation, active low framing, 16-bit word length. Transmission is initiated by writing a word to the Tx register after the SPORT has been enabled.

\*ADDITIONAL PINS OMITTED FOR CLARITY

Figure 27. AD5310 to ADSP-2101 Interface

Figure 28. SYNC Interrupt Facility

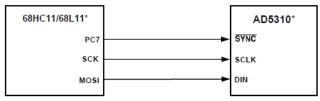

#### AD5310 to 68HC11/68L11 Interface

Figure 29 shows a serial interface between the AD5310 and the 68HC11/68L11 microcontroller. SCK of the 68HC11/68L11 drives the SCLK of the AD5310, while the MOSI output drives the serial data line of the DAC. The SYNC signal is derived from a port line (PC7). The setup conditions for correct operation of this interface are as follows: the 68HC11/68L11 should be configured so that its CPOL bit is a 0 and its CPHA bit is a 1. When data is being transmitted to the DAC, the SYNC line is taken low (PC7). With this 68HC11/68L11 configuration, data appearing on the MOSI output is valid on the falling edge of SCK. Serial data from the 68HC11/68L11 is transmitted in 8-bit bytes with only eight falling clock edges occurring in the transmit cycle. Data is transmitted MSB first. To load data to the AD5310, PC7 is left low after the first eight bits are transferred, a second serial write operation is performed to the DAC, and PC7 is taken high at the end of this procedure.

\*ADDITIONAL PINS OMITTED FOR CLARITY

Figure 29. AD5310 to 68HC11/68L11 Interface

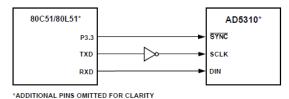

#### AD5310 to 80C51/80L51 Interface

Figure 30 shows a serial interface between the AD5310 and the 80C51/80L51 microcontroller. The setup for the interface is as follows: TXD of the 80C51/80L51 drives SCLK of the AD5310 while RXD drives the serial data line of the part. The SYNC signal is again derived from a bit-programmable pin on the port. In this case, Port Line P3.3 is used. When data is to be

transmitted to the AD5310, P3.3 is taken low. The 80C51/80L51 transmits data only in 8-bit bytes; therefore, only eight falling clock edges occur in the transmit cycle. To load data to the DAC, P3.3 is left low after the first eight bits are transmitted, and a second write cycle is initiated to transmit the second byte of data. P3.3 is taken high following the completion of this cycle. The 80C51/80L51 outputs the serial data in a format that has the LSB first. The AD5310 requires that the MSB of data be received first. The 80C51/80L51 transmit routine should take this into account.

Figure 30. AD5310 to 80C51/80L51 Interface

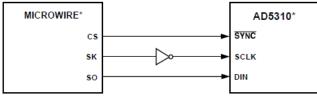

#### **AD5310** to MICROWIRE Interface

Figure 31 shows an interface between the AD5310 and any MICROWIRE-compatible device. Serial data is shifted out on the falling edge of the serial clock and is clocked into the AD5310 on the rising edge of the SK.

\*ADDITIONAL PINS OMITTED FOR CLARITY

Figure 31. AD5310 to MICROWIRE Interface

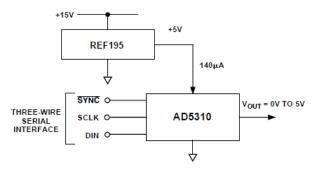

# APPLICATIONS INFORMATION USING REF19x AS A POWER SUPPLY FOR AD5310

Because the supply current required by the AD5310 is extremely low, an alternative option is to use a REF19x voltage reference (REF195 for 5 V or REF193 for 3 V) to supply the required voltage to the part (see Figure 32). This is especially useful if the power supply is quite noisy or if the system supply voltages are at some value other than 5 V or 3 V (for example, 15 V). The REF19x outputs a steady supply voltage for the AD5310. If the low dropout REF195 is used, the current that it needs to supply to the AD5310 is 140  $\mu A$ . This is with no load on the output of the DAC. When the DAC output is loaded, the REF195 also needs to supply the current to the load. The total current required (with a 5 k $\Omega$  load on the DAC output) is

$$140 \,\mu\text{A} + (5 \,\text{V}/5 \,\text{k}\Omega) = 1.14 \,\text{mA}$$

The load regulation of the REF195 is typically 2 ppm/mA, which results in an error of 2.3 ppm (11.5  $\mu$ V) for the 1.14 mA current drawn from it. This corresponds to a 0.002 LSB error.

Figure 32. REF195 as Power Supply to AD5310

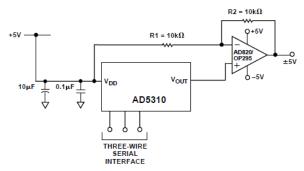

#### **BIPOLAR OPERATION USING THE AD5310**

The AD5310 is designed for single-supply operation but a bipolar output range is also possible using the circuit shown in Figure 33. This circuit results in an output voltage range of  $\pm 5$  V. Rail-to-rail operation at the amplifier output is achievable using an AD820 or an OP295 as the output amplifier. The output voltage for any input code can be calculated as follows:

$$V_{O} = \left[V_{DD} \times \left(\frac{D}{1024}\right) \times \left(\frac{RI + R2}{RI}\right) - V_{DD} \times \left(\frac{R2}{RI}\right)\right]$$

where D represents the input code in decimal (0 to 1023).

With  $V_{DD} = 5$  V,  $R1 = R2 = 10 \text{ k}\Omega$ ,

$$V_O = \left(\frac{10 \times D}{1024}\right) - 5 \text{ V}$$

This is an output voltage range of  $\pm 5$  V, with 000 hex corresponding to a -5 V output and 3FF hex corresponding to a +5 V output.

Figure 33. Bipolar Operation with the AD5310

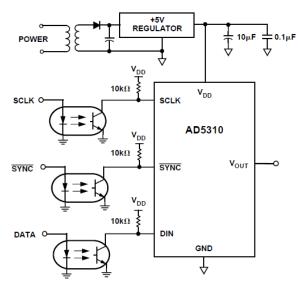

# USING AD5310 WITH AN OPTO-ISOLATED INTERFACE

In process control applications in industrial environments, it is often necessary to use an opto-isolated interface to protect and isolate the controlling circuitry from any hazardous commonmode voltages that may occur in the area where the DAC is functioning. Opto-isolators provide isolation in excess of 3 kV. Because the AD5310 uses a 3-wire serial logic interface, it only requires three opto-isolators to provide the required isolation (see Figure 34). The power supply to the part also needs to be isolated. This is done by using a transformer. On the DAC side of the transformer, a 5 V regulator provides the 5 V supply required for the AD5310.

Figure 34. AD5310 with an Opto-Isolated Interface

#### POWER SUPPLY BYPASSING AND GROUNDING

When accuracy is important in a circuit, it is helpful to carefully consider the power supply and ground return layout on the board. The printed circuit board containing the AD5310 should have separate analog and digital sections, each having their own area of the board. If the AD5310 is in a system where other devices require an AGND to DGND connection, the connection should be made at one point only. This ground point should be as close as possible to the AD5310.

The power supply to the AD5310 should be bypassed with 10  $\mu F$  and 0.1  $\mu F$  capacitors. The capacitors should be physically as close as possible to the device, with the 0.1  $\mu F$  capacitor ideally right up against the device. The 10  $\mu F$  capacitors are the tantalum bead type. It is important that the 0.1  $\mu F$  capacitor has low effective series resistance (ESR) and effective series inductance (ESI), such as is the case with common ceramic types of capacitors. This

$0.1~\mu F$  capacitor provides a low impedance path to ground for high frequencies caused by transient currents due to internal logic switching.

The power supply line itself should have as large a trace as possible to provide a low impedance path and to reduce glitch effects on the supply line. Clocks and other fast switching digital signals should be shielded from other parts of the board by digital ground. Avoid crossover of digital and analog signals if possible. When traces cross on opposite sides of the board, ensure that they run at right angles to each other to reduce feedthrough effects through the board. The best board layout technique is the microstrip technique, where the component side of the board is dedicated to the ground plane only and the signal traces are placed on the solder side. However, this is not always possible with a 2-layer board.

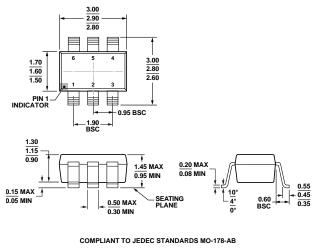

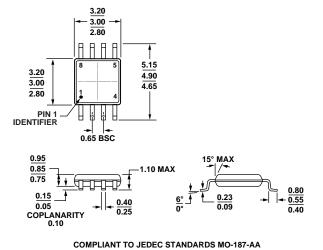

### **OUTLINE DIMENSIONS**

Figure 35. 6-Lead Small Outline Transistor Package [SOT-23] (RJ-6) Dimensions shown in millimeters

Figure 36. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | Package Description | Package Option | Branding Information |

|-----------------------|-------------------|---------------------|----------------|----------------------|

| AD5310BRTZ-REEL       | -40°C to +105°C   | 6-Lead SOT-23       | RJ-6           | D3B                  |

| AD5310BRTZ-REEL7      | -40°C to +105°C   | 6-Lead SOT-23       | RJ-6           | D3B                  |

| AD5310BRTZ-500RL7     | -40°C to +105°C   | 6-Lead SOT-23       | RJ-6           | D3B                  |

| AD5310BRT-REEL        | -40°C to +105°C   | 6-Lead SOT-23       | RJ-6           | D3B                  |

| AD5310BRT-REEL7       | -40°C to +105°C   | 6-Lead SOT-23       | RJ-6           | D3B                  |

| AD5310BRT-500RL7      | -40°C to +105°C   | 6-Lead SOT-23       | RJ-6           | D3B                  |

| AD5310WBRTZ-REEL7     | -40°C to +105°C   | 6-Lead SOT-23       | RJ-6           | DJW                  |

| AD5310BRMZ            | -40°C to +105°C   | 8-Lead MSOP         | RM-8           | D3B                  |

| AD5310BRMZ-REEL7      | -40°C to +105°C   | 8-Lead MSOP         | RM-8           | D3B                  |

| AD5310BRM             | -40°C to +105°C   | 8-Lead MSOP         | RM-8           | D3B                  |

| AD5310BRM-REEL        | -40°C to +105°C   | 8-Lead MSOP         | RM-8           | D3B                  |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

#### **AUTOMOTIVE PRODUCTS**

The AD5310WBRTZ-REEL7 model is available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that this automotive model may have specifications that differ from the commercial models; therefore, designers should review the Specifications section of this data sheet carefully. Only the automotive grade product shown is available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for this model.

<sup>&</sup>lt;sup>2</sup> W = Qualified for Automotive Applications.

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А