# 7/8-Bit Single/Dual I<sup>2</sup>C Digital POT with Nonvolatile Memory

#### **Features**

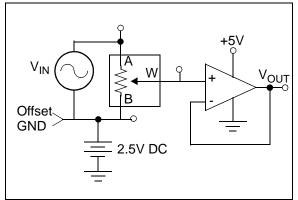

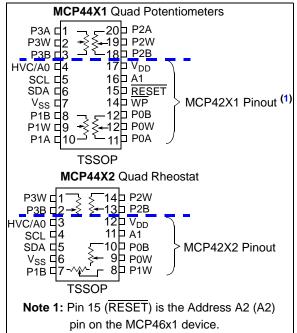

- · Single or Dual Resistor Network Options

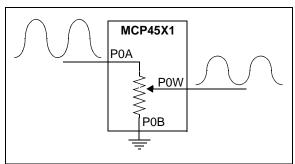

- Potentiometer or Rheostat Configuration Options

- · Resistor Network Resolution

- 7-bit: 128 Resistors (129 Steps)

- 8-bit: 256 Resistors (257 Steps)

- RAB Resistances Options of:

- 5 kΩ

- 10 kΩ

- 50 kΩ

- 100 kΩ

- Zero-Scale to Full-Scale Wiper Operation

- Low Wiper Resistance: 75Ω (typical)

- · Low Tempco:

- Absolute (Rheostat): 50 ppm typical (0°C to 70°C)

- Ratiometric (Potentiometer): 15 ppm typical

- · Nonvolatile Memory

- Automatic Recall of Saved Wiper Setting

- WiperLock™ Technology

- 10 General Purpose Memory Locations

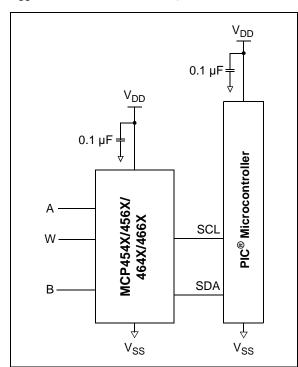

- I<sup>2</sup>C Serial Interface

- 100 kHz, 400 kHz and 3.4 MHz Support

- · Serial Protocol Allows:

- High-Speed Read/Write to Wiper

- Read/Write to EEPROM

- Write Protect to be Enabled/Disabled

- WiperLock to be Enabled/Disabled

- Resistor Network Terminal Disconnect Feature via the Terminal Control (TCON) Register

- · Write Protect Feature:

- Hardware Write Protect (WP) Control Pin

- Software Write Protect (WP) Configuration Bit

- Brown-out Reset Protection (1.5V typical)

- Serial Interface Inactive Current (2.5 uA typical)

- · High-Voltage Tolerant Digital Inputs: Up to 12.5V

- Wide Operating Voltage:

- 2.7V to 5.5V Device Characteristics Specified

- 1.8V to 5.5V Device Operation

- Wide Bandwidth (-3dB) Operation:

- 2 MHz (typ.) for 5.0  $k\Omega$  Device

- Extended Temperature Range (-40°C to +125°C)

### Description

The MCP45XX and MCP46XX devices offer a wide range of product offerings using an I<sup>2</sup>C interface. This family of devices support 7-bit and 8-bit resistor networks, nonvolatile memory configurations, and Potentiometer and Rheostat pinouts.

WiperLock Technology allows application-specific calibration settings to be secured in the EEPROM.

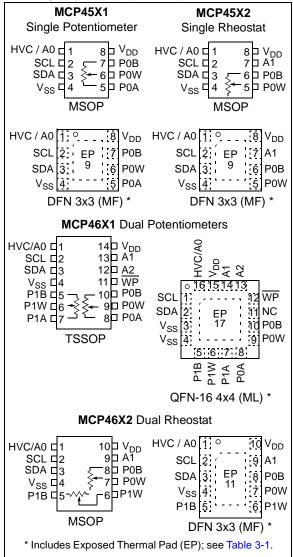

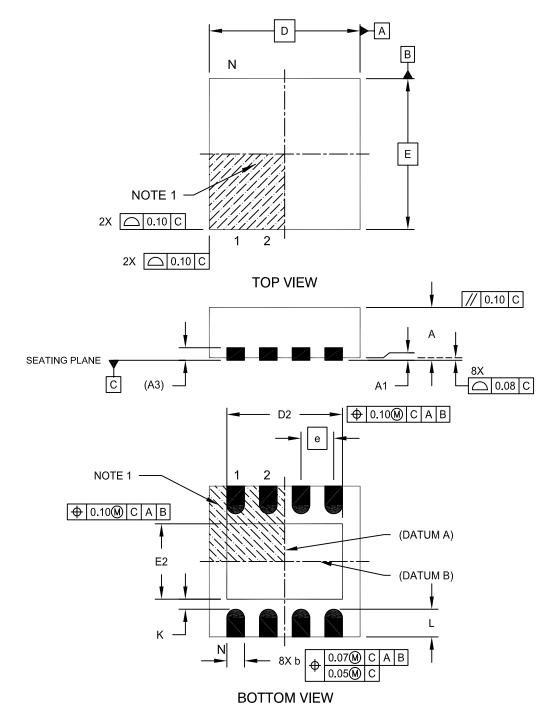

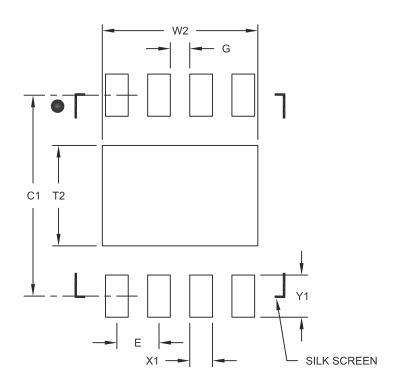

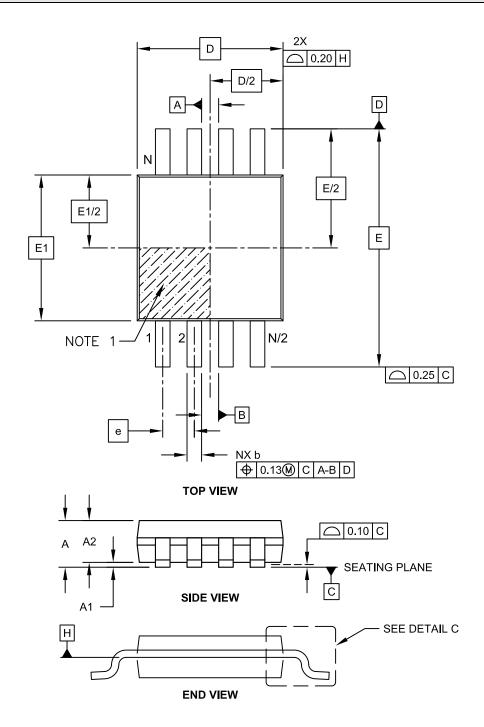

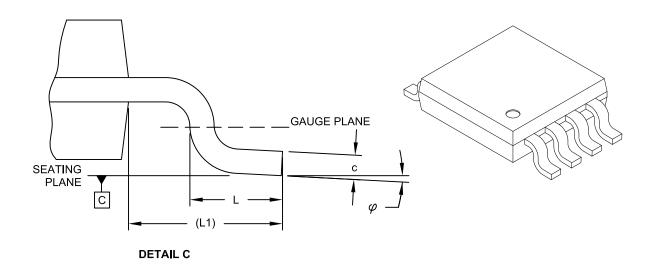

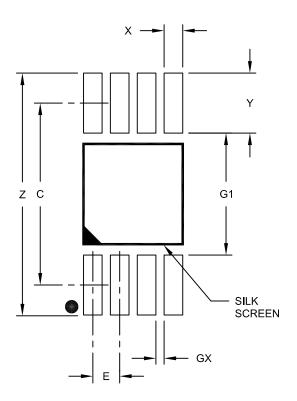

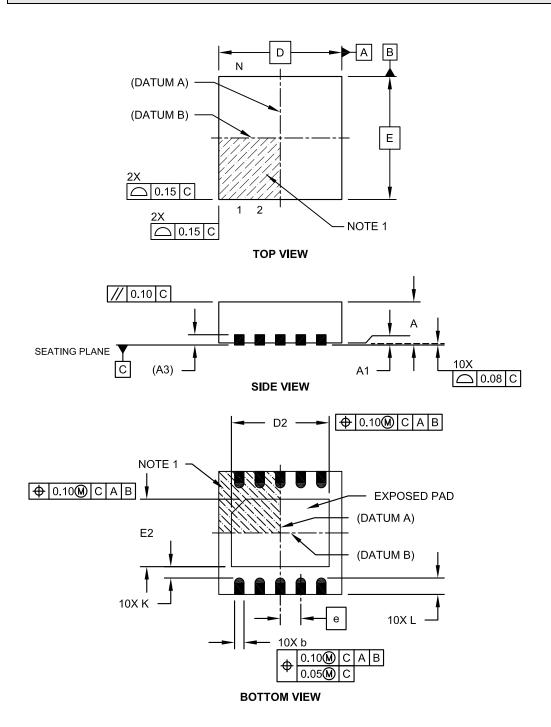

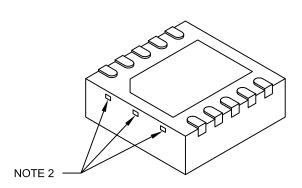

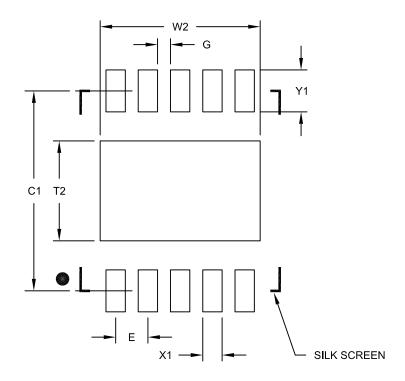

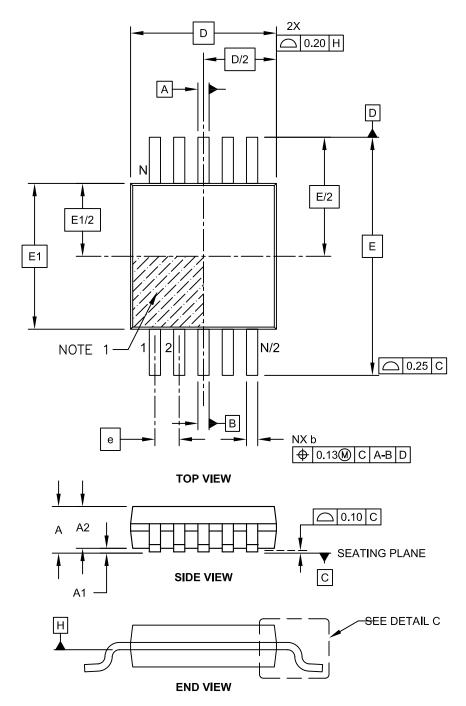

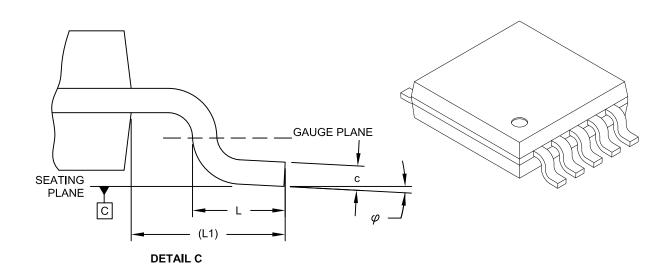

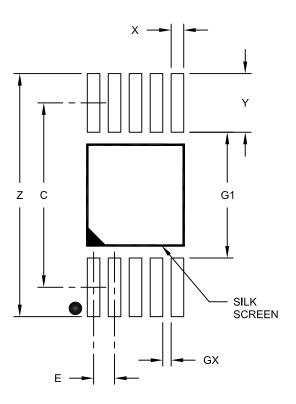

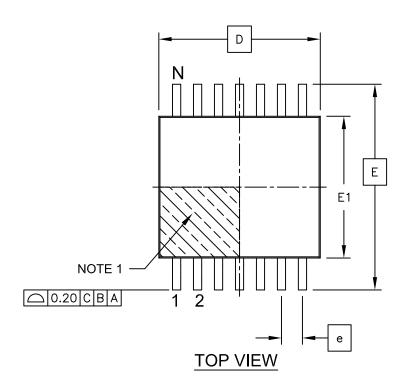

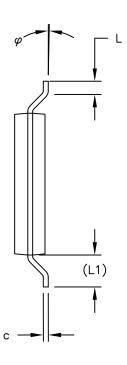

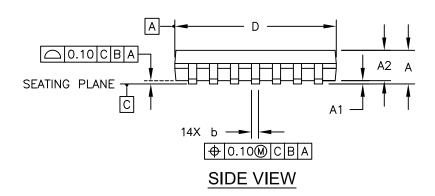

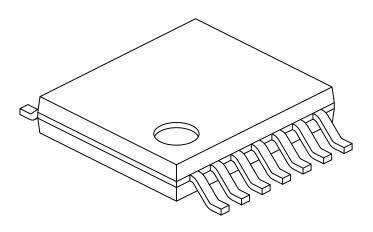

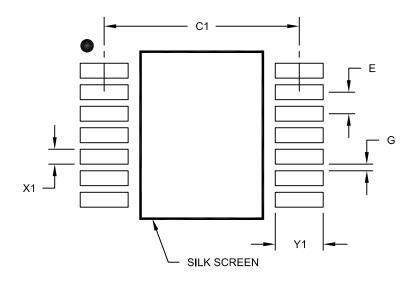

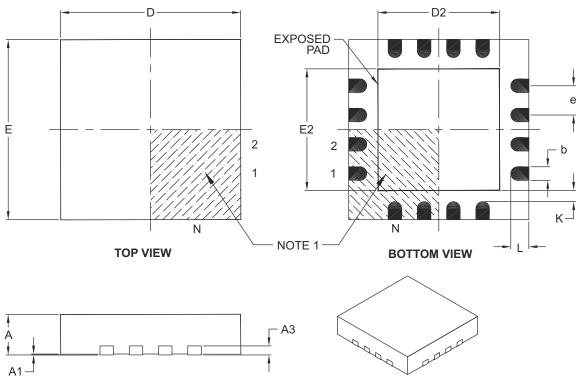

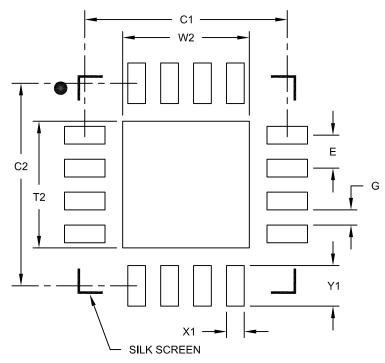

### Package Types (top view)

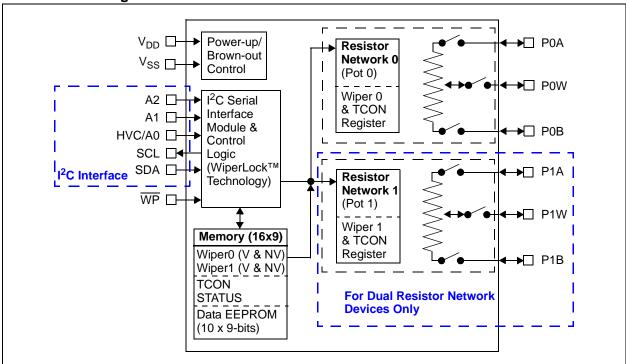

### **Device Block Diagram**

#### **Device Features**

|                        | <u>s</u>  |                        | _ 0                  | >              | sg<br>g                 | oer<br>J             | Resistance (typic              | cal)                             | sd         | W                                                    |

|------------------------|-----------|------------------------|----------------------|----------------|-------------------------|----------------------|--------------------------------|----------------------------------|------------|------------------------------------------------------|

| Device                 | # of POTs | Wiper<br>Configuration | Control<br>Interface | Memory<br>Type | WiperLock<br>Technology | POR Wiper<br>Setting | $R_{AB}$ Options (k $\Omega$ ) | Wiper<br>- R <sub>W</sub><br>(Ω) | # of Steps | V <sub>DD</sub><br>Operating<br>Range <sup>(2)</sup> |

| MCP4531 (3)            | 1         | Potentiometer (1)      | I <sup>2</sup> C     | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0         | 75                               | 129        | 1.8V to 5.5V                                         |

| MCP4532 (3)            | 1         | Rheostat               | I <sup>2</sup> C     | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0         | 75                               | 129        | 1.8V to 5.5V                                         |

| MCP4541                | 1         | Potentiometer (1)      | I <sup>2</sup> C     | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0         | 75                               | 129        | 2.7V to 5.5V                                         |

| MCP4542                | 1         | Rheostat               | I <sup>2</sup> C     | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0         | 75                               | 129        | 2.7V to 5.5V                                         |

| MCP4551 (3)            | 1         | Potentiometer (1)      | I <sup>2</sup> C     | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0         | 75                               | 257        | 1.8V to 5.5V                                         |

| MCP4552 (3)            | 1         | Rheostat               | I <sup>2</sup> C     | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0         | 75                               | 257        | 1.8V to 5.5V                                         |

| MCP4561                | 1         | Potentiometer (1)      | I <sup>2</sup> C     | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0         | 75                               | 257        | 2.7V to 5.5V                                         |

| MCP4562                | 1         | Rheostat               | I <sup>2</sup> C     | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0         | 75                               | 257        | 2.7V to 5.5V                                         |

| MCP4631 (3)            | 2         | Potentiometer (1)      | I <sup>2</sup> C     | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0         | 75                               | 129        | 1.8V to 5.5V                                         |

| MCP4632 <sup>(3)</sup> | 2         | Rheostat               | I <sup>2</sup> C     | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0         | 75                               | 129        | 1.8V to 5.5V                                         |

| MCP4641                | 2         | Potentiometer (1)      | I <sup>2</sup> C     | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0         | 75                               | 129        | 2.7V to 5.5V                                         |

| MCP4642                | 2         | Rheostat               | I <sup>2</sup> C     | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0         | 75                               | 129        | 2.7V to 5.5V                                         |

| MCP4651 (3)            | 2         | Potentiometer (1)      | I <sup>2</sup> C     | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0         | 75                               | 257        | 1.8V to 5.5V                                         |

| MCP4652 (3)            | 2         | Rheostat               | I <sup>2</sup> C     | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0         | 75                               | 257        | 1.8V to 5.5V                                         |

| MCP4661                | 2         | Potentiometer (1)      | I <sup>2</sup> C     | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0         | 75                               | 257        | 2.7V to 5.5V                                         |

| MCP4662                | 2         | Rheostat               | I <sup>2</sup> C     | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0         | 75                               | 257        | 2.7V to 5.5V                                         |

Note 1: Floating either terminal (A or B) allows the device to be used as a Rheostat (variable resistor).

- 2: Analog characteristics only tested from 2.7V to 5.5V unless otherwise noted.

- 3: Please check Microchip web site for device release and availability

### 1.0 ELECTRICAL CHARACTERISTICS

### 1.1 Absolute Maximum Ratings†

| <u> </u>                                                                                |                                |

|-----------------------------------------------------------------------------------------|--------------------------------|

| Voltage on V <sub>DD</sub> with respect to V <sub>SS</sub>                              | 0.6V to +7.0V                  |

| Voltage on HVC/A0, A1, A2, SCL, SDA and WP with respect to V <sub>SS</sub>              | 0.6V to 12.5V                  |

| Voltage on all other pins (PxA, PxW, and PxB) with respect to V <sub>SS</sub>           | 0.3V to V <sub>DD</sub> + 0.3V |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ , $V_I > V_{DD}$ , $V_I > V_{PP}$ ON HV pins) | ±20 mA                         |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{DD}$ )                          | ±20 mA                         |

| Maximum output current sunk by any Output pin                                           | 25 mA                          |

| Maximum output current sourced by any Output pin                                        | 25 mA                          |

| Maximum current out of V <sub>SS</sub> pin                                              | 100 mA                         |

| Maximum current into V <sub>DD</sub> pin                                                | 100 mA                         |

| Maximum current into PxA, PxW & PxB pins                                                | ±2.5 mA                        |

| Storage temperature                                                                     | 65°C to +150°C                 |

| Ambient temperature with power applied                                                  | 40°C to +125°C                 |

| Package power dissipation ( $T_A = +50^{\circ}C$ , $T_J = +150^{\circ}C$ )              |                                |

| MSSOP-8                                                                                 | 473 mW                         |

| MSSOP-10                                                                                | 495 mW                         |

| DFN-8 (3x3)                                                                             | 1.76W                          |

| DFN-10 (3x3)                                                                            | 1.87W                          |

| TSSOP-14                                                                                | 1.00W                          |

| QFN-16 (4x4)                                                                            | 2.18W                          |

| Soldering temperature of leads (10 seconds)                                             | +300°C                         |

| ESD protection on all pins                                                              | ≥4 kV (HBM),                   |

|                                                                                         | ≥ 300V (MM)                    |

| Maximum Junction Temperature (T <sub>J</sub> )                                          | +150°C                         |

|                                                                                         |                                |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### AC/DC CHARACTERISTICS

| DC Characteristics                                                                   | Operating All parame V <sub>DD</sub> = +2. | Standard Operating Conditions (unless otherwise specified) Operating Temperature $-40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq +125^{\circ}\text{C} \text{ (extended)}$ All parameters apply across the specified operating ranges unless noted. $V_{\text{DD}} = +2.7\text{V to } 5.5\text{V}, 5 \text{ k}\Omega, 10 \text{ k}\Omega, 50 \text{ k}\Omega, 100 \text{ k}\Omega \text{ devices}.$ Typical specifications represent values for $V_{\text{DD}} = 5.5\text{V}, T_{\text{A}} = +25^{\circ}\text{C}.$ |          |                           |       |                                                                                                                                                                              |  |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameters                                                                           | Sym                                        | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Тур      | Max                       | Units | Conditions                                                                                                                                                                   |  |  |  |

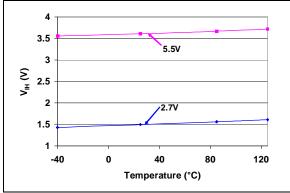

| Supply Voltage                                                                       | $V_{DD}$                                   | 2.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _        | 5.5                       | V     |                                                                                                                                                                              |  |  |  |

|                                                                                      |                                            | 1.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _        | 2.7                       | V     | Serial Interface only.                                                                                                                                                       |  |  |  |

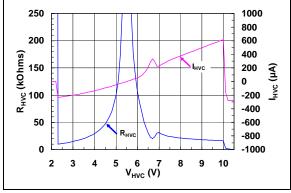

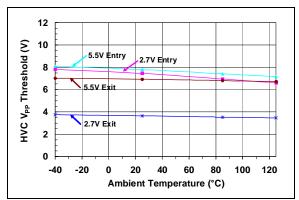

| HVC pin voltage range                                                                | $V_{HV}$                                   | V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _        | 12.5V                     | V     | V <sub>DD</sub> ≥ The HVC pin will be at one of three input levels                                                                                                           |  |  |  |

|                                                                                      |                                            | V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _        | V <sub>DD</sub> +<br>8.0V | V     | V <sub>DD</sub> < (V <sub>IL</sub> , V <sub>IH</sub> or V <sub>IHH</sub> ). ( <b>Note 6</b> )<br>4.5V                                                                        |  |  |  |

| VDD Start Voltage<br>to ensure Wiper<br>Reset                                        | $V_{BOR}$                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _        | 1.65                      | V     | RAM retention voltage (V <sub>RAM</sub> ) < V <sub>BOR</sub>                                                                                                                 |  |  |  |

| VDD Rise Rate to<br>ensure Power-on<br>Reset                                         | $V_{DDRR}$                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (Note 9) |                           | V/ms  |                                                                                                                                                                              |  |  |  |

| Delay after device<br>exits the reset state<br>(V <sub>DD</sub> > V <sub>BOR</sub> ) | T <sub>BORD</sub>                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10       | 20                        | μs    |                                                                                                                                                                              |  |  |  |

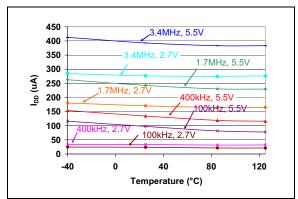

| Supply Current (Note 10)                                                             | I <sub>DD</sub>                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _        | 600                       | μА    | Serial Interface Active,<br>$HVC/A0 = V_{IH}$ (or $V_{IL}$ ) (Note 11)<br>Write all 0's to Volatile Wiper 0<br>$V_{DD} = 5.5V$ , $F_{SCL} = 3.4$ MHz                         |  |  |  |

|                                                                                      |                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _        | 250                       | μА    | Serial Interface Active,<br>$HVC/A0 = V_{IH}$ (or $V_{IL}$ ) (Note 11)<br>Write all 0's to Volatile Wiper 0<br>$V_{DD} = 5.5V$ , $F_{SCL} = 100$ kHz                         |  |  |  |

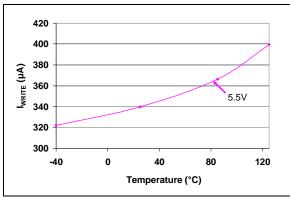

|                                                                                      |                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _        | 575                       | μА    | EE Write Current (Write Cycle)<br>(Nonvolatile device only),<br>$V_{DD} = 5.5V$ , $F_{SCL} = 400$ kHz,<br>Write all 0's to Nonvolatile Wiper 0<br>$SCL = V_{IL}$ or $V_{IH}$ |  |  |  |

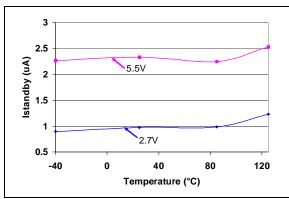

|                                                                                      |                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.5      | 5                         | μА    | Serial Interface Inactive,<br>(Stop condition, SCL = SDA = $V_{IH}$ ),<br>Wiper = 0<br>$V_{DD}$ = 5.5V, HVC/A0 = $V_{IH}$                                                    |  |  |  |

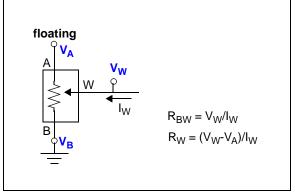

- Note 1: Resistance is defined as the resistance between terminal A to terminal B.

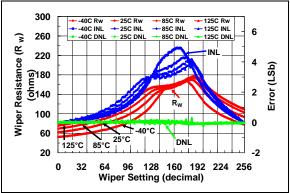

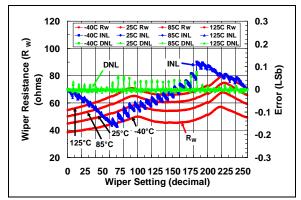

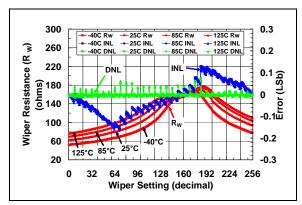

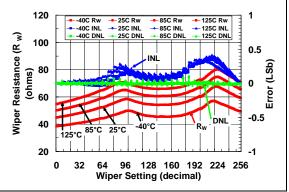

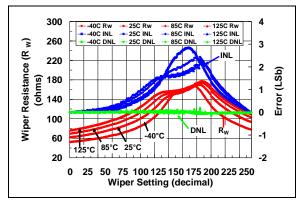

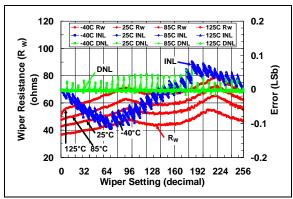

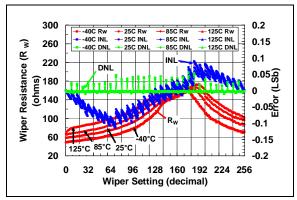

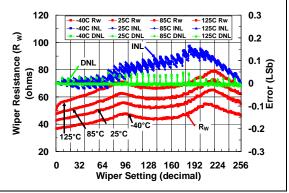

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP4XX1 only.

- 4: MCP4XX2 only, includes  $V_{WZSE}$  and  $V_{WFSE}$ .

- 5: Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- **6:** This specification by design.

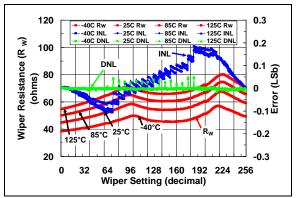

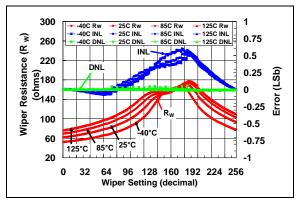

- 7: Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly overvoltage and temperature.

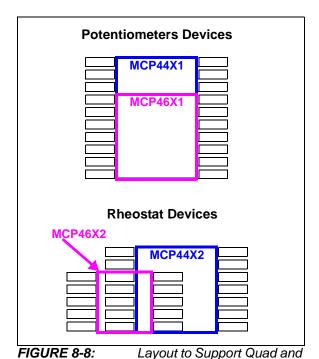

- 8: The MCP4XX1 is externally connected to match the configurations of the MCP45X2 and MCP46X2, and then tested.

- 9: POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 = V<sub>IHH</sub>, the I<sub>DD</sub> current is less due to current into the HVC/A0 pin. See I<sub>PU</sub> specification.

|                                                                       | DC Characteristics                                          |                                                                                                                                                                                                                                                                                                                      | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40^{\circ}\text{C} \le T_{\text{A}} \le +125^{\circ}\text{C}$ (extended) |                 |        |                      |                                                                           |  |  |  |  |

|-----------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|----------------------|---------------------------------------------------------------------------|--|--|--|--|

| DC Characteristics                                                    | S                                                           | All parameters apply across the specified operating ranges unless noted. $V_{DD} = +2.7 \text{V to } 5.5 \text{V}, 5 \text{ k}\Omega, 10 \text{ k}\Omega, 50 \text{ k}\Omega, 100 \text{ k}\Omega \text{ devices}.$ Typical specifications represent values for $V_{DD} = 5.5 \text{V}, T_A = +25 ^{\circ}\text{C}.$ |                                                                                                                                                                |                 |        |                      |                                                                           |  |  |  |  |

| Parameters                                                            | Sym                                                         | Min                                                                                                                                                                                                                                                                                                                  | Тур                                                                                                                                                            | Max             | Units  |                      | Conditions                                                                |  |  |  |  |

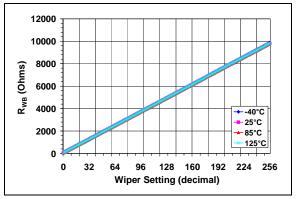

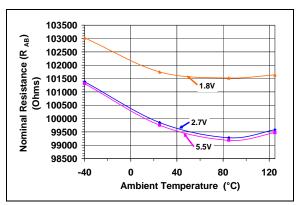

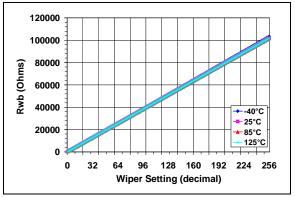

| Resistance                                                            | R <sub>AB</sub>                                             | 4.0                                                                                                                                                                                                                                                                                                                  | 5                                                                                                                                                              | 6.0             | kΩ     | -502 de              | vices (Note 1)                                                            |  |  |  |  |

| (± 20%)                                                               |                                                             | 8.0                                                                                                                                                                                                                                                                                                                  | 10                                                                                                                                                             | 12.0            | kΩ     | -103 de              | vices (Note 1)                                                            |  |  |  |  |

|                                                                       |                                                             | 40.0                                                                                                                                                                                                                                                                                                                 | 50                                                                                                                                                             | 60.0            | kΩ     | -503 de              | vices (Note 1)                                                            |  |  |  |  |

|                                                                       |                                                             | 80.0                                                                                                                                                                                                                                                                                                                 | 100                                                                                                                                                            | 120.0           | kΩ     | -104 de              | vices (Note 1)                                                            |  |  |  |  |

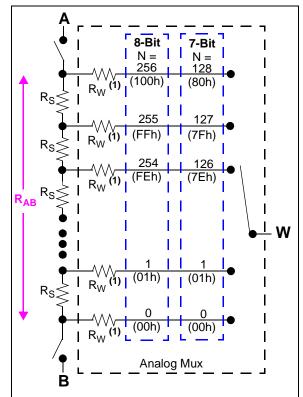

| Resolution                                                            | N                                                           |                                                                                                                                                                                                                                                                                                                      | 257                                                                                                                                                            |                 | Taps   | 8-bit                | No Missing Codes                                                          |  |  |  |  |

|                                                                       |                                                             |                                                                                                                                                                                                                                                                                                                      | 129                                                                                                                                                            |                 | Taps   | 7-bit                | No Missing Codes                                                          |  |  |  |  |

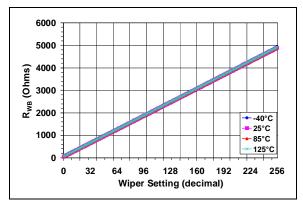

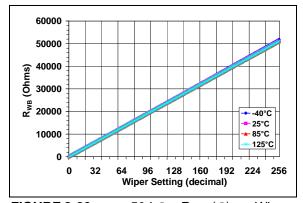

| Step Resistance                                                       | R <sub>S</sub>                                              | 1                                                                                                                                                                                                                                                                                                                    | R <sub>AB</sub> / (256)                                                                                                                                        | 1               | Ω      | 8-bit                | Note 6                                                                    |  |  |  |  |

|                                                                       |                                                             | 1                                                                                                                                                                                                                                                                                                                    | R <sub>AB</sub> / (128)                                                                                                                                        | 1               | Ω      | 7-bit                | Note 6                                                                    |  |  |  |  |

| Nominal<br>Resistance Match                                           | R <sub>AB0</sub> - R <sub>AB1</sub>  /<br>  R <sub>AB</sub> |                                                                                                                                                                                                                                                                                                                      | 0.2                                                                                                                                                            | 1.25            | %      | MCP46X1 devices only |                                                                           |  |  |  |  |

|                                                                       | R <sub>BW0</sub> - R <sub>BW1</sub>  <br>                   | I                                                                                                                                                                                                                                                                                                                    | 0.25                                                                                                                                                           | 1.5             | %      |                      | <b>K2</b> devices only,<br>Full-Scale                                     |  |  |  |  |

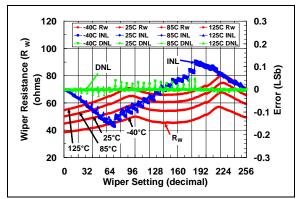

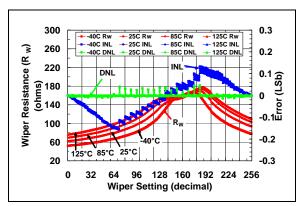

| Wiper Resistance                                                      | R <sub>W</sub>                                              |                                                                                                                                                                                                                                                                                                                      | 75                                                                                                                                                             | 160             | Ω      | $V_{DD} = 5$         | $.5 \text{ V}, I_{\text{W}} = 2.0 \text{ mA}, \text{ code} = 00 \text{h}$ |  |  |  |  |

| (Note 3, Note 4)                                                      |                                                             |                                                                                                                                                                                                                                                                                                                      | 75                                                                                                                                                             | 300             | Ω      | $V_{DD} = 2$         | $.7 \text{ V}, I_{\text{W}} = 2.0 \text{ mA}, \text{ code} = 00 \text{h}$ |  |  |  |  |

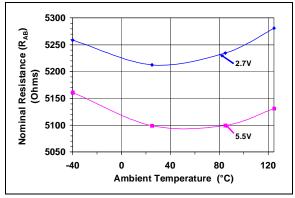

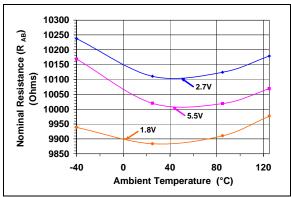

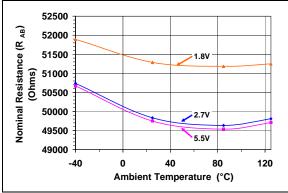

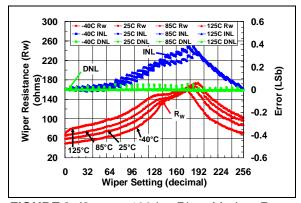

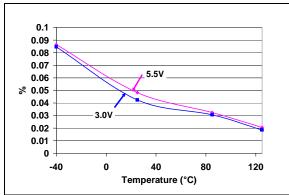

| Nominal                                                               | ΔR <sub>AB</sub> /ΔT                                        | _                                                                                                                                                                                                                                                                                                                    | 50                                                                                                                                                             | _               | ppm/°C | $T_A = -20$          | °C to +70°C                                                               |  |  |  |  |

| Resistance<br>Tempco                                                  |                                                             |                                                                                                                                                                                                                                                                                                                      | 100                                                                                                                                                            |                 | ppm/°C | $T_A = -40$          | °C to +85°C                                                               |  |  |  |  |

| Теттрсо                                                               |                                                             | _                                                                                                                                                                                                                                                                                                                    | 150                                                                                                                                                            | _               | ppm/°C | $T_A = -40$          | °C to +125°C                                                              |  |  |  |  |

| Ratiometeric<br>Tempco                                                | $\Delta V_{WB}/\Delta T$                                    | _                                                                                                                                                                                                                                                                                                                    | 15                                                                                                                                                             | _               | ppm/°C | Code =               | Code = Mid-scale (80h or 40h)                                             |  |  |  |  |

| Resistor Terminal<br>Input Voltage<br>Range (Terminals<br>A, B and W) | $V_{A,}V_{W,}V_{B}$                                         | Vss                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                              | V <sub>DD</sub> | V      | Note 5,              | Note 6                                                                    |  |  |  |  |

- Note 1: Resistance is defined as the resistance between terminal A to terminal B.

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP4XX1 only.

- 4: MCP4XX2 only, includes V<sub>WZSE</sub> and V<sub>WFSE</sub>.

- **5:** Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- 6: This specification by design.

- 7: Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly overvoltage and temperature.

- 8: The MCP4XX1 is externally connected to match the configurations of the MCP45X2 and MCP46X2, and then tested.

- **9:** POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 =  $V_{IHH}$ , the  $I_{DD}$  current is less due to current into the HVC/A0 pin. See  $I_{PU}$  specification.

| DC Characteristics               | 3               | Standard Operating Conditions (unless otherwise specified) Operating Temperature $-40^{\circ}\text{C} \le T_{\text{A}} \le +125^{\circ}\text{C}$ (extended) All parameters apply across the specified operating ranges unless noted. $V_{\text{DD}} = +2.7 \text{V}$ to 5.5V, 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ devices. Typical specifications represent values for $V_{\text{DD}} = 5.5 \text{V}$ , $T_{\text{A}} = +25^{\circ}\text{C}$ . |     |       |       |                                           |                                                             |  |  |

|----------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|-------------------------------------------|-------------------------------------------------------------|--|--|

| Parameters                       | Sym             | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Тур | Max   | Units | Cor                                       | nditions                                                    |  |  |

| Maximum current through Terminal | I <sub>T</sub>  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1   | 2.5   | mA    | Terminal A                                | I <sub>AW</sub> ,<br>W = Full-Scale (FS)                    |  |  |

| (A, W or B)<br>Note 6            |                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 2.5   | mA    | Terminal B                                | I <sub>BW</sub> ,<br>W = Zero Scale (ZS)                    |  |  |

|                                  |                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _   | 2.5   | mA    | Terminal W                                | I <sub>AW</sub> or I <sub>BW</sub> ,<br>W = FS or ZS        |  |  |

|                                  |                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1   | 1.38  | mA    |                                           | $I_{AB}, V_{B} = 0V,$ $V_{A} = 5.5V,$ $R_{AB(MIN)} = 4000$  |  |  |

|                                  |                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1   | 0.688 | mA    | Terminal A<br>and                         | $I_{AB}, V_B = 0V,$ $V_A = 5.5V,$ $R_{AB(MIN)} = 8000$      |  |  |

|                                  |                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _   | 0.138 | mA    | Terminal B                                | $I_{AB}, V_{B} = 0V,$ $V_{A} = 5.5V,$ $R_{AB(MIN)} = 40000$ |  |  |

|                                  |                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 0.069 | mA    |                                           | $I_{AB}, V_B = 0V,$ $V_A = 5.5V,$ $R_{AB(MIN)} = 80000$     |  |  |

| Leakage current                  | I <sub>WL</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100 | _     | nA    | MCP4XX1 PxA = PxW = PxB = V <sub>SS</sub> |                                                             |  |  |

| into A, W or B                   |                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100 | _     | nA    | MCP4XX2 PxB =                             | $PxW = V_{SS}$                                              |  |  |

|                                  |                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100 |       | nA    | Terminals Disconnected (R1HW = R0HW = 0)  |                                                             |  |  |

- Note 1: Resistance is defined as the resistance between terminal A to terminal B.

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP4XX1 only.

- 4: MCP4XX2 only, includes  $V_{WZSE}$  and  $V_{WFSE}$ .

- 5: Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- **6:** This specification by design.

- 7: Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly overvoltage and temperature.

- 8: The MCP4XX1 is externally connected to match the configurations of the MCP45X2 and MCP46X2, and then tested.

- **9:** POR/BOR is not rate dependent.

- 10: Supply current is independent of current through the resistor network.

- 11: When HVC/A0 =  $V_{IHH}$ , the  $I_{DD}$  current is less due to current into the HVC/A0 pin. See  $I_{PU}$  specification.

### AC/DC CHARACTERISTICS (CONTINUED)

| DC Characteristics                       | Operating All parame V <sub>DD</sub> = +2. | Standard Operating Conditions (unless otherwise specified) Operating Temperature $-40^{\circ}\text{C} \leq \text{T}_{A} \leq +125^{\circ}\text{C} \text{ (extended)}$ All parameters apply across the specified operating ranges unless noted. $V_{DD} = +2.7 \text{V to } 5.5 \text{V}, 5 \text{ k}\Omega, 10 \text{ k}\Omega, 50 \text{ k}\Omega, 100 \text{ k}\Omega \text{ devices.}$ Typical specifications represent values for $V_{DD} = 5.5 \text{V}, T_{A} = +25^{\circ}\text{C}.$ |      |      |       |        |       |                                                     |  |

|------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------|-------|-----------------------------------------------------|--|

| Parameters                               | Sym                                        | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Тур  | Max  | Units |        | Con   | nditions                                            |  |

| Full-Scale Error                         | $V_{WFSE}$                                 | -6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.1 |      | LSb   | 5 kΩ   | 8-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

| (MCP4XX1 only)                           |                                            | -4.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.1 | 1    | LSb   |        | 7-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

| (8-bit code = 100h,<br>7-bit code = 80h) |                                            | -3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.1 | 1    | LSb   | 10 kΩ  | 8-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

|                                          |                                            | -2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.1 | 1    | LSb   |        | 7-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

|                                          |                                            | -0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.1 |      | LSb   | 50 kΩ  | 8-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

|                                          |                                            | -0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.1 |      | LSb   |        | 7-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

|                                          |                                            | -0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.1 | 1    | LSb   | 100 kΩ | 8-bit | $3.0V \leq V_{DD} \leq 5.5V$                        |  |

|                                          |                                            | -0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.1 | 1    | LSb   |        | 7-bit | $3.0V \leq V_{DD} \leq 5.5V$                        |  |

| Zero-Scale Error                         | $V_{WZSE}$                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +0.1 | +6.0 | LSb   | 5 kΩ   | 8-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

| (MCP4XX1 only)                           |                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +0.1 | +3.0 | LSb   |        | 7-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

| (8-bit code = 00h,<br>7-bit code = 00h)  |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | +0.1 | +3.5 | LSb   | 10 kΩ  | 8-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

| . 2.1 0000 = 0011)                       |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | +0.1 | +2.0 | LSb   |        | 7-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

|                                          |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | +0.1 | +0.8 | LSb   | 50 kΩ  | 8-bit | $3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$ |  |

Resistance is defined as the resistance between terminal A to terminal B.

-1

-0.5

-0.5

-0.25

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP4XX1 only.

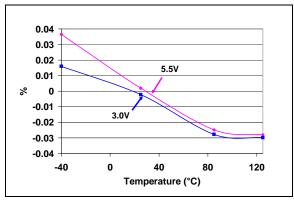

Potentiometer

Non-linearity

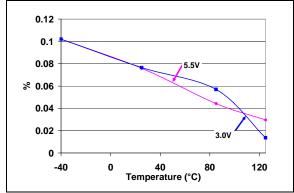

Differential

Non-linearity

Potentiometer

Integral

4: MCP4XX2 only, includes  $V_{WZSE}$  and  $V_{WFSE}$ .

INL

DNL

5: Resistor terminals A, W and B's polarity with respect to each other is not restricted.

+0.1

+0.1

+0.1

±0.5

±0.25

±0.25

±0.125

+0.5

+0.5

+0.5

+1

+0.5

+0.5

+0.25

LSb

LSb

LSb

LSb

LSb

LSb

LSb

7-bit

8-bit 7-bit

(Note 2)

(Note 2)

$3.0V \leq V_{DD} \leq 5.5V$

$3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}$

MCP4XX1 devices only

MCP4XX1 devices only

100  $k\Omega$

8-bit

7-bit

8-bit

7-bit

$3.0 V \leq V_{DD} \leq 5.5 V$  $3.0V \leq V_{DD} \leq 5.5V$

$3.0V \leq V_{DD} \leq 5.5V$

- **6:** This specification by design.

- 7: Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly overvoltage and temperature.

- 8: The MCP4XX1 is externally connected to match the configurations of the MCP45X2 and MCP46X2, and then tested.

- 9: POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 = V<sub>IHH</sub>, the I<sub>DD</sub> current is less due to current into the HVC/A0 pin. See I<sub>PU</sub> specification.

| DC Characteristics | Operating All parame V <sub>DD</sub> = +2. | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $-40^{\circ}\text{C} \le T_{\text{A}} \le +125^{\circ}\text{C}$ (extended)  All parameters apply across the specified operating ranges unless noted. $V_{\text{DD}} = +2.7\text{V}$ to 5.5V, 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ devices. |     |   |     |        |       |            |  |  |

|--------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|-----|--------|-------|------------|--|--|

| Parameters         | Sym                                        | Typical specifications represent values for $V_{DD} = 5.5V$ , $T_A = +25$ °C.  Min Typ Max Units Conditions                                                                                                                                                                                                                                           |     |   |     |        |       |            |  |  |

| Bandwidth -3 dB    | BW                                         | _                                                                                                                                                                                                                                                                                                                                                     | 2   | _ | MHz | 5 kΩ   | 8-bit | Code = 80h |  |  |

| (See Figure 2-58,  |                                            | _                                                                                                                                                                                                                                                                                                                                                     | 2   | _ | MHz |        | 7-bit | Code = 40h |  |  |

| load = 30 pF)      |                                            | _                                                                                                                                                                                                                                                                                                                                                     | 1   | _ | MHz | 10 kΩ  | 8-bit | Code = 80h |  |  |

|                    |                                            | _                                                                                                                                                                                                                                                                                                                                                     | 1   | _ | MHz |        | 7-bit | Code = 40h |  |  |

|                    |                                            | _                                                                                                                                                                                                                                                                                                                                                     | 200 | _ | kHz | 50 kΩ  | 8-bit | Code = 80h |  |  |

|                    |                                            | _                                                                                                                                                                                                                                                                                                                                                     | 200 | _ | kHz |        | 7-bit | Code = 40h |  |  |

|                    |                                            | _                                                                                                                                                                                                                                                                                                                                                     | 100 | _ | kHz | 100 kΩ | 8-bit | Code = 80h |  |  |

|                    |                                            | _                                                                                                                                                                                                                                                                                                                                                     | 100 | _ | kHz |        | 7-bit | Code = 40h |  |  |

- Note 1: Resistance is defined as the resistance between terminal A to terminal B.

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP4XX1 only.

- 4: MCP4XX2 only, includes V<sub>WZSE</sub> and V<sub>WFSE</sub>.

- 5: Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- **6:** This specification by design.

- **7:** Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly overvoltage and temperature.

- 8: The MCP4XX1 is externally connected to match the configurations of the MCP45X2 and MCP46X2, and then tested.

- 9: POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 =  $V_{IHH}$ , the  $I_{DD}$  current is less due to current into the HVC/A0 pin. See  $I_{PU}$  specification.

| DC Characteristics                     |       |                                                                                                                                                                                                                                                       | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ (extended) |        |       |        |       |                                                    |  |  |  |

|----------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|----------------------------------------------------|--|--|--|

|                                        |       | All parameters apply across the specified operating ranges unless noted. $V_{DD}$ = +2.7V to 5.5V, 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ devices. Typical specifications represent values for $V_{DD}$ = 5.5V, $T_A$ = +25°C. |                                                                                                                                                                       |        |       |        |       |                                                    |  |  |  |

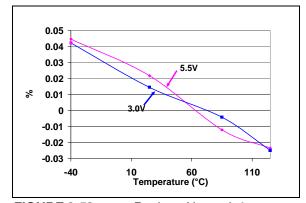

| Parameters                             | Sym   | Min                                                                                                                                                                                                                                                   | Тур                                                                                                                                                                   | Max    | Units |        | Con   | ditions                                            |  |  |  |

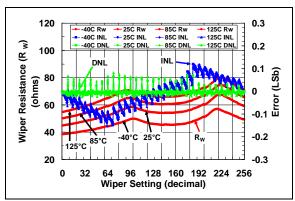

| Rheostat Integral                      | R-INL | -1.5                                                                                                                                                                                                                                                  | ±0.5                                                                                                                                                                  | +1.5   | LSb   | 5 kΩ   | 8-bit | 5.5V, I <sub>W</sub> = 900 μA                      |  |  |  |

| Non-linearity MCP45X1 (Note 4, Note 8) |       | -8.25                                                                                                                                                                                                                                                 | +4.5                                                                                                                                                                  | +8.25  | LSb   |        |       | 3.0V, I <sub>W</sub> = 480 μA<br>( <b>Note 7</b> ) |  |  |  |

| MCP4XX2 devices                        |       | -1.125                                                                                                                                                                                                                                                | ±0.5                                                                                                                                                                  | +1.125 | LSb   |        | 7-bit | $5.5V$ , $I_W = 900 \mu A$                         |  |  |  |

| only (Note 4)                          |       | -6.0                                                                                                                                                                                                                                                  | +4.5                                                                                                                                                                  | +6.0   | LSb   |        |       | 3.0V, I <sub>W</sub> = 480 μA<br>( <b>Note 7</b> ) |  |  |  |

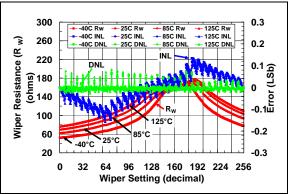

|                                        |       | -1.5                                                                                                                                                                                                                                                  | ±0.5                                                                                                                                                                  | +1.5   | LSb   | 10 kΩ  | 8-bit | 5.5V, I <sub>W</sub> = 450 μA                      |  |  |  |

|                                        |       | -5.5                                                                                                                                                                                                                                                  | +2.5                                                                                                                                                                  | +5.5   | LSb   |        |       | 3.0V, I <sub>W</sub> = 240 μA<br>( <b>Note 7</b> ) |  |  |  |

|                                        |       | -1.125                                                                                                                                                                                                                                                | ±0.5                                                                                                                                                                  | +1.125 | LSb   |        | 7-bit | $5.5V$ , $I_W = 450 \mu A$                         |  |  |  |

|                                        |       | -4.0                                                                                                                                                                                                                                                  | +2.5                                                                                                                                                                  | +4.0   | LSb   |        |       | 3.0V, I <sub>W</sub> = 240 μA<br>( <b>Note 7</b> ) |  |  |  |

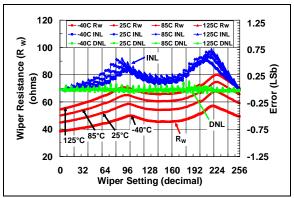

|                                        |       | -1.5                                                                                                                                                                                                                                                  | ±0.5                                                                                                                                                                  | +1.5   | LSb   | 50 kΩ  | 8-bit | 5.5V, I <sub>W</sub> = 90 μA                       |  |  |  |

|                                        |       | -2.0                                                                                                                                                                                                                                                  | +1                                                                                                                                                                    | +2.0   | LSb   |        |       | 3.0V, I <sub>W</sub> = 48 μA<br>( <b>Note 7</b> )  |  |  |  |

|                                        |       | -1.125                                                                                                                                                                                                                                                | ±0.5                                                                                                                                                                  | +1.125 | LSb   |        | 7-bit | $5.5V$ , $I_W = 90 \mu A$                          |  |  |  |

|                                        |       | -1.5                                                                                                                                                                                                                                                  | +1                                                                                                                                                                    | +1.5   | LSb   |        |       | 3.0V, I <sub>W</sub> = 48 μA<br>( <b>Note 7</b> )  |  |  |  |

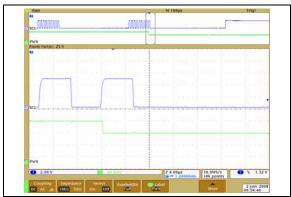

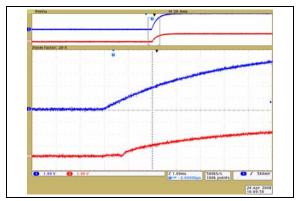

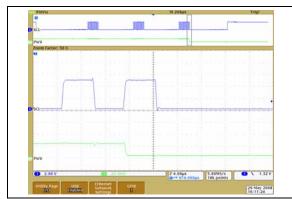

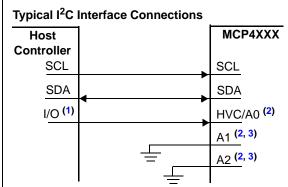

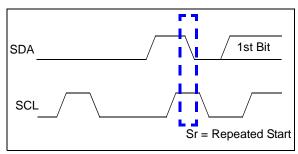

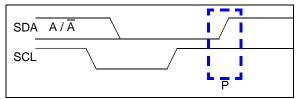

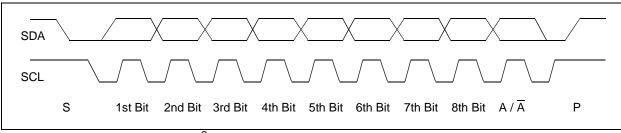

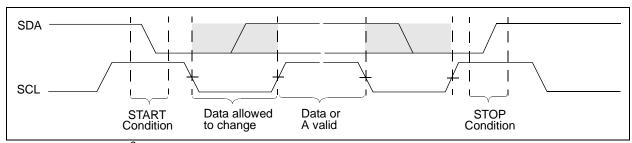

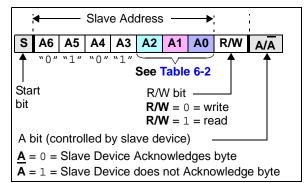

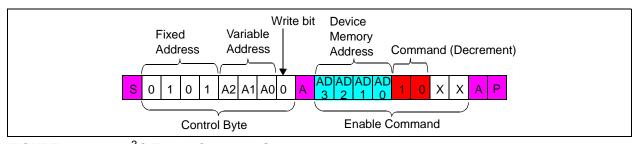

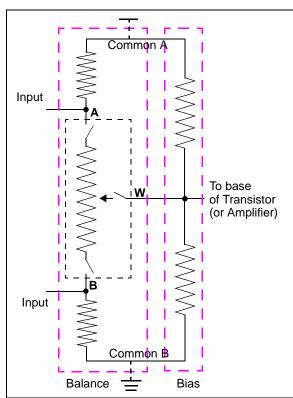

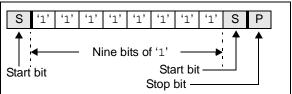

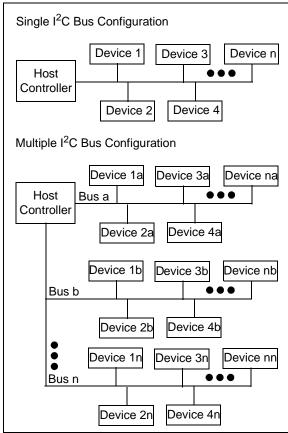

|                                        |       | -1.0                                                                                                                                                                                                                                                  | ±0.5                                                                                                                                                                  | +1.0   | LSb   | 100 kΩ | 8-bit | 5.5V, I <sub>W</sub> = 45 μA                       |  |  |  |