# Flexible 512 Channel DX with Enhanced

**Data Sheet**

Features April 2006

- 512 channel x 512 channel non-blocking switch at 2.048 Mbps, 4.096 Mbps or 8.192 Mbps operation

- Rate conversion between the ST-BUS inputs and ST-BUS outputs

- Integrated Digital Phase-Locked Loop (DPLL) meets Telcordia GR-1244-CORE Stratum 4 enhanced specifications

- DPLL provides automatic reference switching, jitter attenuation, holdover and free run functions

- Per-stream ST-BUS input with data rate selection of 2.048 Mbps, 4.096 Mbps or 8.192 Mbps

- Per-stream ST-BUS output with data rate selection of 2.048 Mbps, 4.096 Mbps or 8.192 Mbps; the output data rate can be different than the input data rate

- Per-stream high impedance control output for every ST-BUS output with fractional bit advancement

- Per-stream input channel and input bit delay programming with fractional bit delay

- Ordering Information

ZL50010/QCC 160 Pin LQFP Trays

ZL50010/GDC 144 Ball LBGA Trays

ZL50010QCG1 160 Pin LQFP\* Trays, Bake & Drypack

ZL50010GDG2 144 Ball LBGA\*\* Trays, Bake & Drypack

\*Pb Free Matte Tin

\*\*Pb Free Tin/Silver/Coppoer

-40°C to +85°C

- Per-stream output channel and output bit delay programming with fractional bit advancement

- Multiple frame pulse outputs and reference clock outputs

- Per-channel constant throughput delay

- Per-channel high impedance output control

- · Per-channel message mode

- Per-channel Pseudo Random Bit Sequence (PRBS) pattern generation and bit error detection

- Control interface compatible to Motorola nonmultiplexed CPUs

- Connection memory block programming capability

- IEEE-1149.1 (JTAG) test port

- 3.3 V I/O with 5 V tolerant input

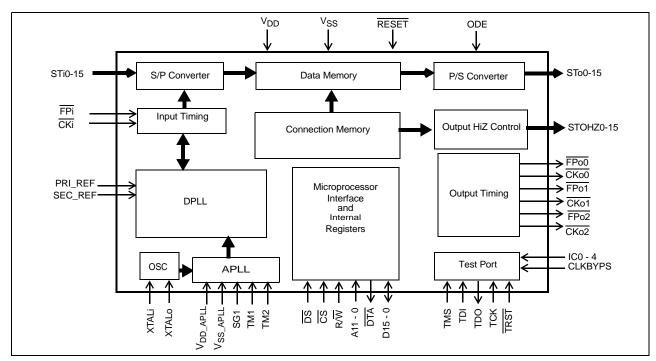

Figure 1 - ZL50010 Functional Block Diagram

Zarlink Semiconductor US Patent No. 5,602,884, UK Patent No. 0772912, France Brevete S.G.D.G. 0772912; Germany DBP No. 69502724.7-08

### **Applications**

- Small and medium digital switching platforms

- Access Servers

- Time Division Multiplexers

- Computer Telephony Integration

- Digital Loop Carriers

### **Description**

The device has 16 ST-BUS inputs (STi0-15) and 16 ST-BUS outputs (STo0-15). It is a non-blocking digital switch with 512 64 kbps channels and performs rate conversion between the ST-BUS inputs and ST-BUS outputs. The ST-BUS inputs accept serial input data streams with the data rate of 2.048 Mbps, 4.096 Mbps or 8.192 Mbps on a per-stream basis. The ST-BUS outputs deliver serial output data streams with the data rate of 2.048 Mbps, 4.096 Mbps or 8.192 Mbps on a per-stream basis. The device also provides 16 high impedance control outputs (STOHZ 0-15) to support the use of external high impedance control buffers.

The ZL50010 has features that are programmable on a per-stream or per-channel basis including message mode, input bit delay, output bit advancement, constant throughput delay and high impedance output control.

The on-chip DPLL meets Telcordia GR-1244-CORE Stratum 4 enhanced specifications (Stratum 4E). It accepts two dedicated timing reference inputs at either 8 kHz, 1.544 MHz or 2.048 MHz. Alternatively, one reference can be replaced by an internal 8 kHz signal derived from the ST-BUS input frame boundary. The DPLL provides automatic reference switching, jitter attenuation, holdover and free run functions. It can be used as a system's ST-BUS timing source which is synchronized to the network. The DPLL can also be bypassed so that the device operates under system timing.

## ZL50010

## **Table of Contents**

|     | tures                                                                  |      |

|-----|------------------------------------------------------------------------|------|

| App | lications                                                              | 2    |

| Des | cription                                                               | 2    |

| Cha | nges Summary                                                           | 8    |

|     | Device Overview                                                        |      |

|     | Functional Description                                                 |      |

| 2.0 | 2.1 ST-BUS Input Data Rate and Input Timing                            |      |

|     | 2.1.1 ST-BUS Input Operation Mode                                      |      |

|     | 2.1.2 Frame Pulse Input and Clock Input Timing                         |      |

|     | 2.1.3 ST-BUS Input Timing.                                             |      |

|     | 2.1.4 Improved Input Jitter Tolerance with Frame Boundary Determinator |      |

|     | 2.2 ST-BUS Output Data Rate and Output Timing                          |      |

|     | 2.2.1 ST-BUS Output Operation Mode                                     |      |

|     | 2.2.2 Frame Pulse Output and Clock Output Timing                       |      |

|     | 2.2.3 ST-BUS Output Timing                                             |      |

|     | 2.3 Serial Data Input Delay and Serial Data Output Offset              | . 23 |

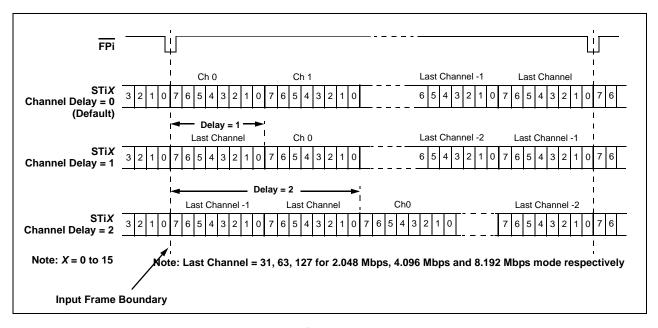

|     | 2.3.1 Input Channel Delay Programming                                  |      |

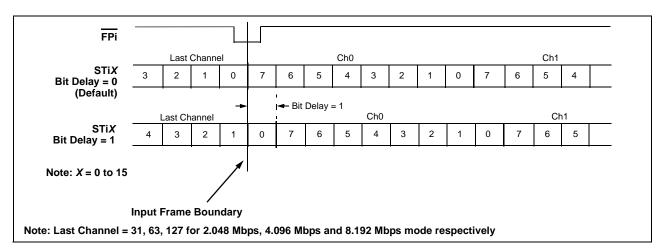

|     | 2.3.2 Input Bit Delay Programming                                      |      |

|     | 2.3.3 Fractional Input Bit Delay Programming                           |      |

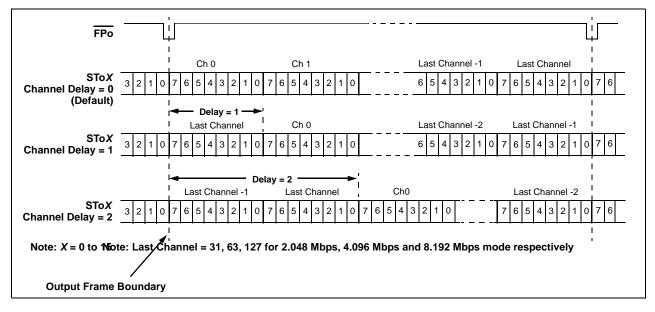

|     | 2.3.4 Output Channel Delay Programming                                 |      |

|     | 2.3.5 Output Bit Delay Programming                                     | . 25 |

|     | 2.3.6 Fractional Output Bit Advancement Programming                    |      |

|     | 2.3.7 External High Impedance Control, STOHZ 0 to 15                   | . 26 |

|     | 2.4 Data Delay Through The Switching Paths                             | . 27 |

|     | 2.5 Connection Memory Description                                      |      |

|     | 2.5.1 Connection Memory Block Programming                              | . 29 |

|     | 2.6 Bit Error Rate (BER) Test                                          | . 30 |

|     | 2.7 Quadrant frame programming                                         |      |

|     | 2.8 Microprocessor Port                                                |      |

|     | 2.9 Digital Phase-Locked Loop (DPLL) Operation                         |      |

|     | 2.9.1 DPLL Master Mode                                                 |      |

|     | 2.9.1.1 Master Mode Reference Inputs                                   |      |

|     | 2.9.1.2 Master Mode Reference Switching                                |      |

|     | 2.9.1.3 DPLL Status Reporting.                                         |      |

|     | 2.9.1.4 Master Mode Output Offset Adjustment                           |      |

|     | 2.9.2 DPLL Freerun Mode                                                |      |

|     | 2.9.3 DPLL Bypass Mode                                                 |      |

|     | 2.10 DPLL Functional Description                                       |      |

|     | 2.10.1 CKi/FPi Synchronizer and PRI_REF Select Mux Circuits            |      |

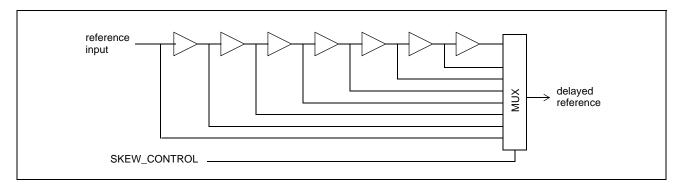

|     | 2.10.3 Skew Control Circuit                                            |      |

|     | 2.10.3 Skew Control Circuit.                                           |      |

|     | 2.10.5 LOS Control Circuit                                             |      |

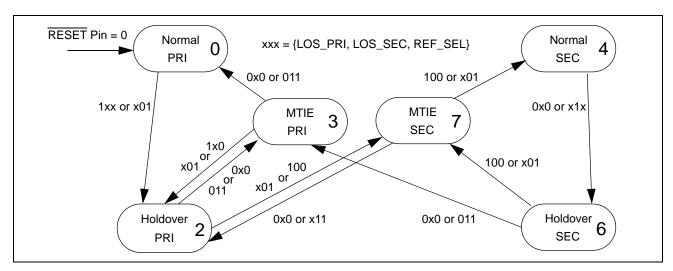

|     | 2.10.6 State Machine Circuit.                                          |      |

|     | 2.10.7 Maximum Time Interval Error (MTIE) Circuit                      |      |

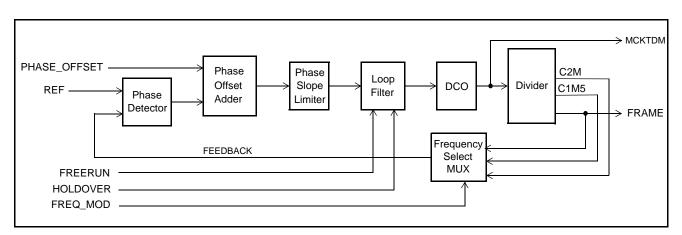

|     | 2.10.8 Phase-Locked Loop (PLL) Circuit                                 |      |

|     | 2.11 DPLL Performance                                                  |      |

|     | 2.11.1 Intrinsic Jitter                                                |      |

|     | 2.11.2 DPLL Jitter Tolerance                                           |      |

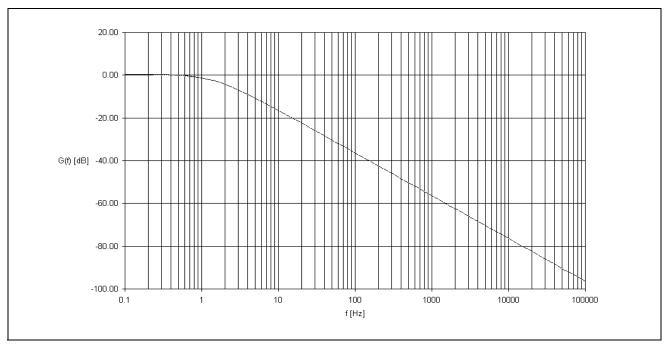

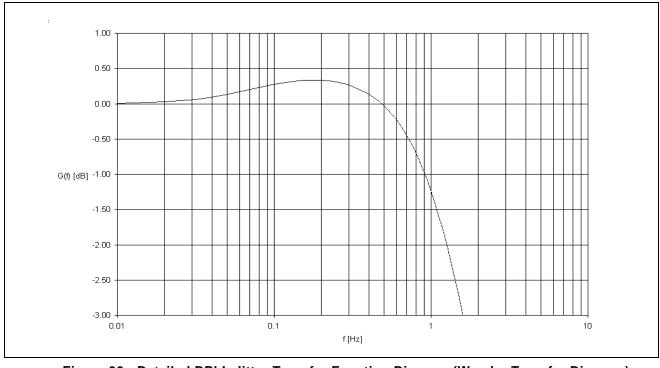

|     | 2.11.3 Jitter Transfer                                                 |      |

|     | 2.11.4 Frequency Accuracy                                              |      |

|     | 2.11.5 Holdover Accuracy                                               |      |

|     | •                                                                      | _    |

## **Table of Contents**

| 2.11.6 Locking Range                                 | 43 |

|------------------------------------------------------|----|

| 2.11.7 Phase Slope                                   |    |

| 2.11.8 MTIE                                          |    |

| 2.11.9 Phase Lock Time                               |    |

| 2.12 Alignment Between Input and Output Frame Pulses | 44 |

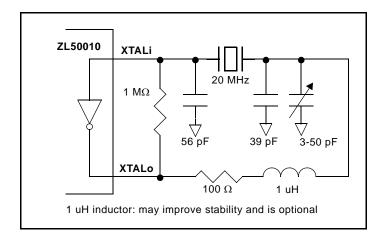

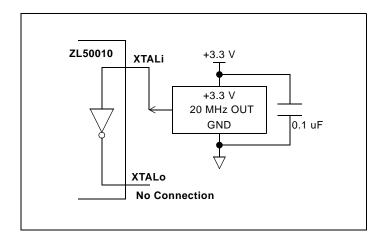

| 3.0 Oscillator Requirements                          | 45 |

| 3.1 External Crystal Oscillator                      |    |

| 3.2 External Clock Oscillator                        |    |

| 4.0 Device Reset and Initialization                  | 47 |

| 5.0 JTAG Support                                     |    |

| 5.1 Test Access Port (TAP)                           |    |

| 5.2 Instruction Register                             |    |

| 5.3 Test Data Register                               |    |

| 5.4 BSDL                                             |    |

| 6.0 Register Address Mapping                         | 49 |

| 7.0 Detail Register description                      |    |

| 8.0 Memory Address Mappings                          |    |

| 9.0 Connection Memory Bit Assignment                 |    |

| 3.0 CONTICUON MENOTY DIL ASSIGNICATION               | // |

# **List of Figures**

| Figure 1 - ZL50010 Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                  |

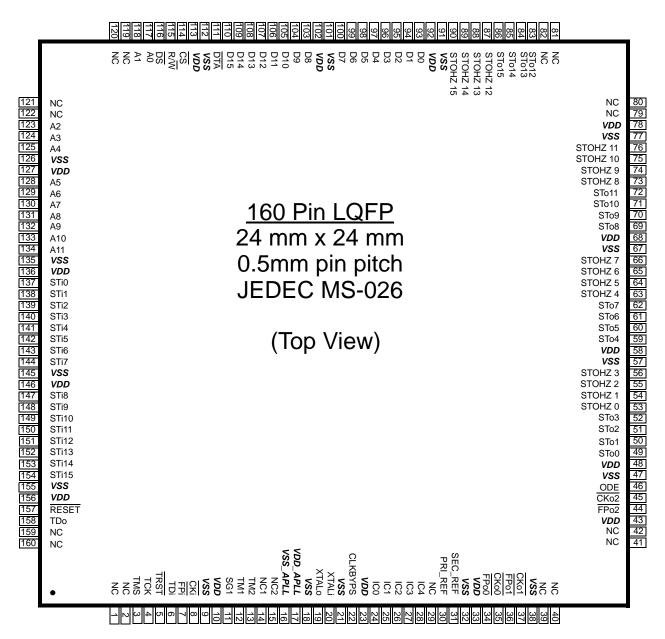

| Figure 2 - 24 mm x 24 mm LQFP (JEDEC MS-026) Pinout Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                                                                                |

| Figure 3 - 13 mm x 13 mm 144 Ball LBGA Pinout Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |

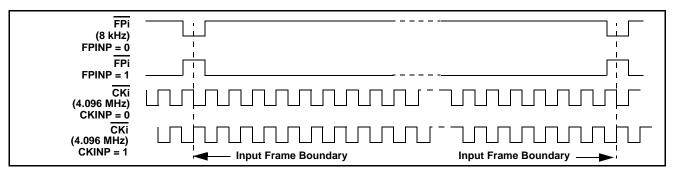

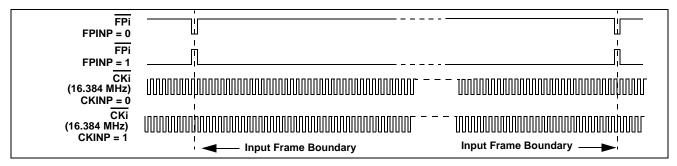

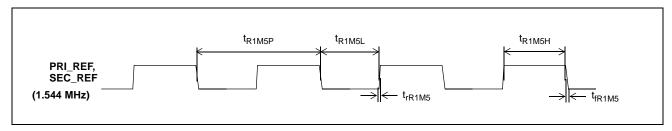

| Figure 4 - Input Timing when (CKIN2 to CKIN0 Bits = 010) in the Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 17                                                                                                             |

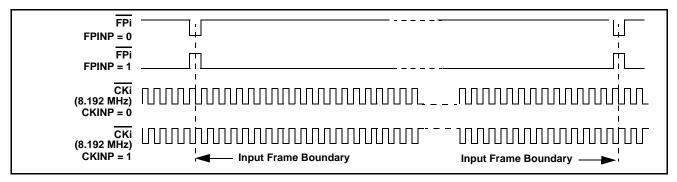

| Figure 5 - Input Timing when (CKIN2 to CKIN0 Bits = 001) in the Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 17                                                                                                             |

| Figure 6 - Input Timing when (CKIN2 to CKIN0 Bits = 000) in the Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 17                                                                                                             |

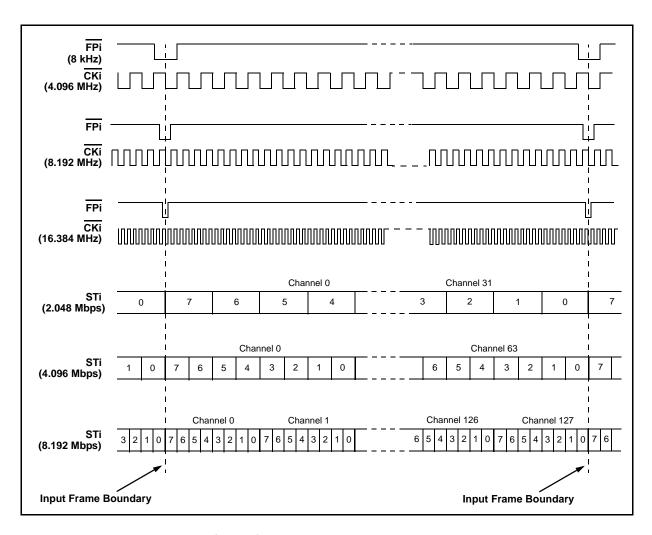

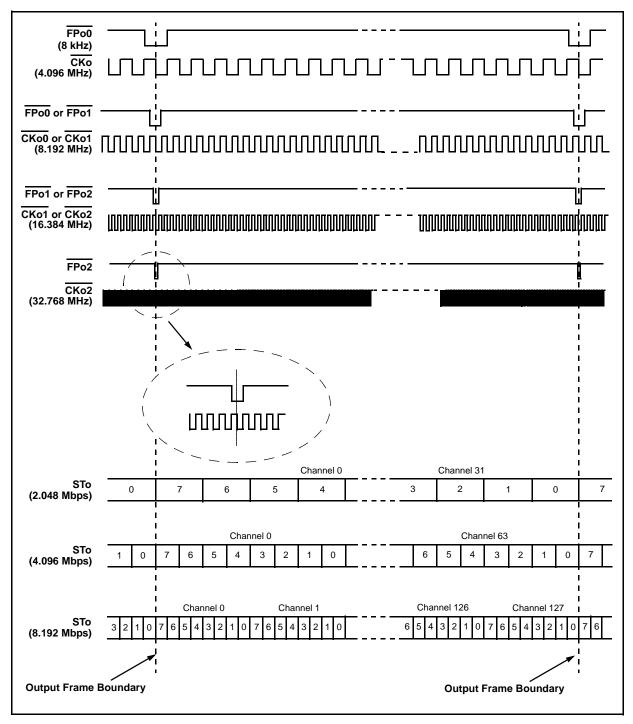

| Figure 7 - ST-BUS Input Timing for Various Input Data Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 18                                                                                                             |

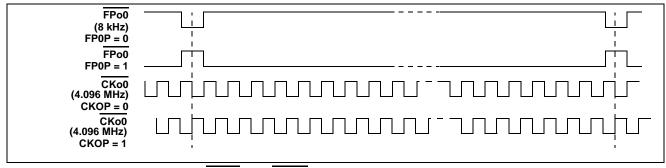

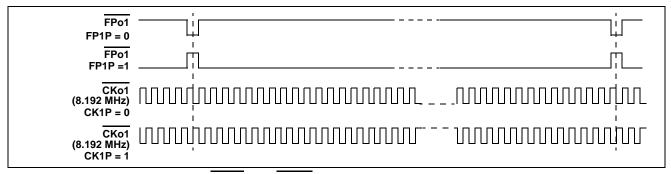

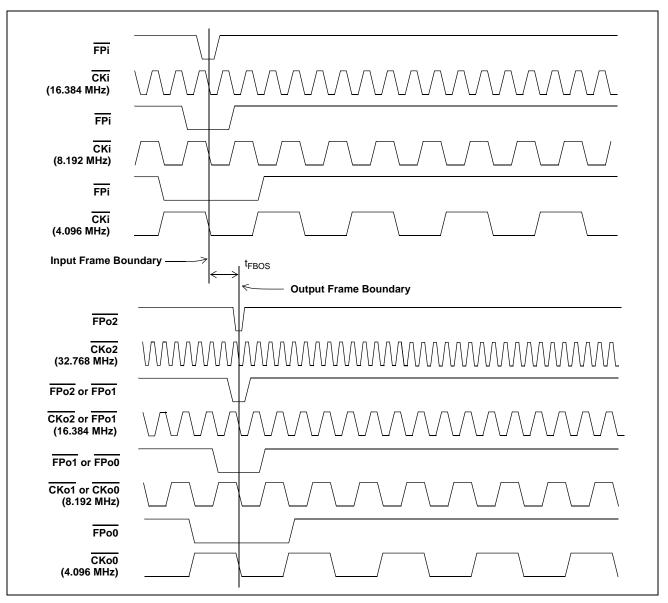

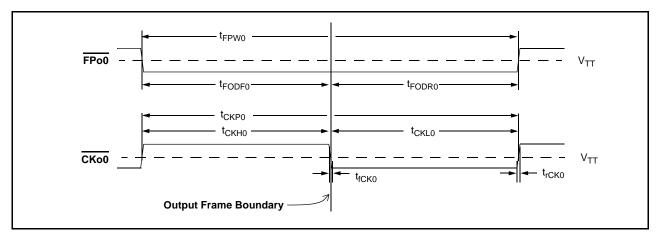

| Figure 8 - FPo0 and CKo0 Output Timing when the CKFP0 Bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 20                                                                                                             |

| Figure 9 - FPo0 and CKo0 Output Timing when the CKFP0 Bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 20                                                                                                             |

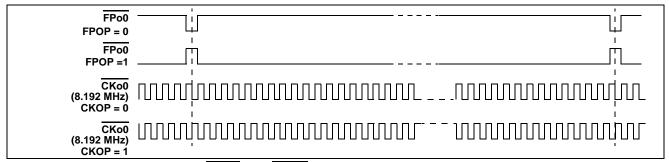

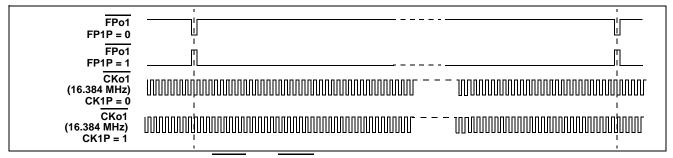

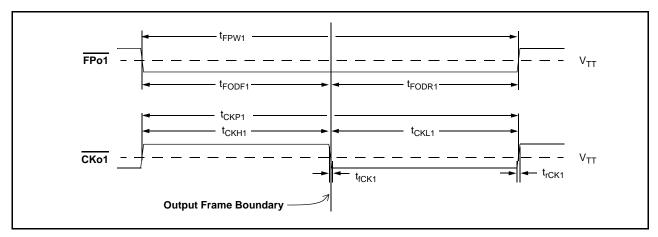

| Figure 10 - FPo1 and CKo1 Output Timing when the CKFP1 Bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 20                                                                                                             |

| Figure 11 - FPo1 and CKo1 Output Timing when the CKFP1 Bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                  |

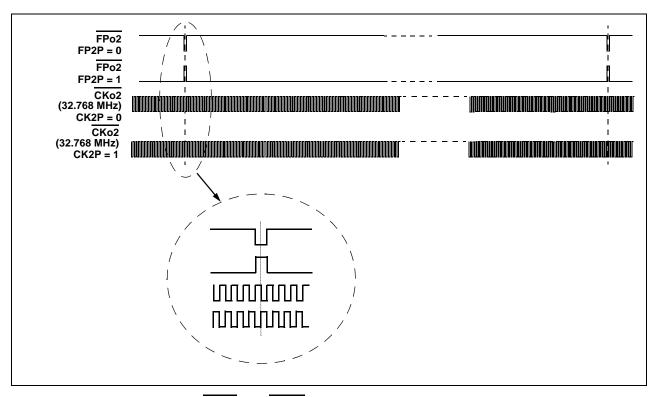

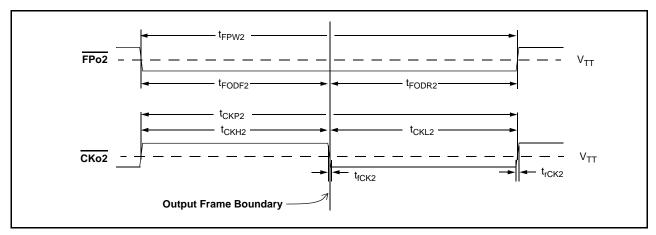

| Figure 12 - FPo2 and CKo2 Output Timing when the CKFP2 Bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 21                                                                                                             |

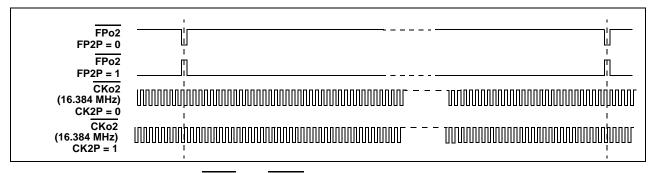

| Figure 13 - FPo2 and CKo2 Output Timing when the CKFP2 Bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                  |

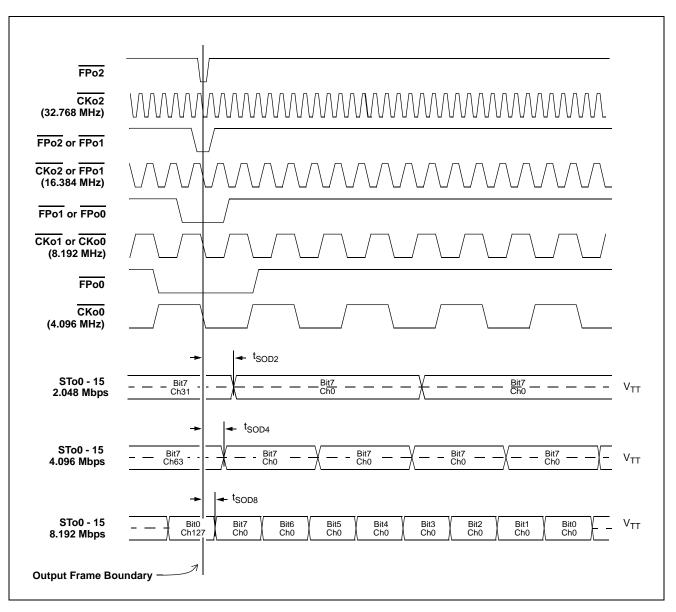

| Figure 14 - ST-BUS Output Timing for Various Output Data Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                  |

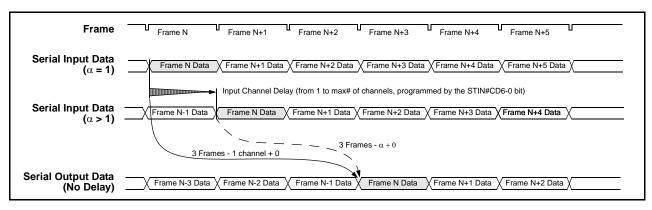

| Figure 15 - Input Channel Delay Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                  |

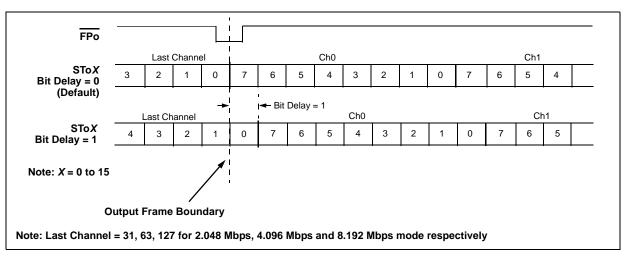

| Figure 16 - Input Bit Delay Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                  |

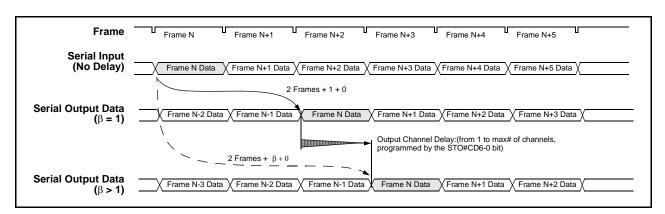

| Figure 17 - Output Channel Delay Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                  |

| Figure 18 - Output Bit Delay Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                  |

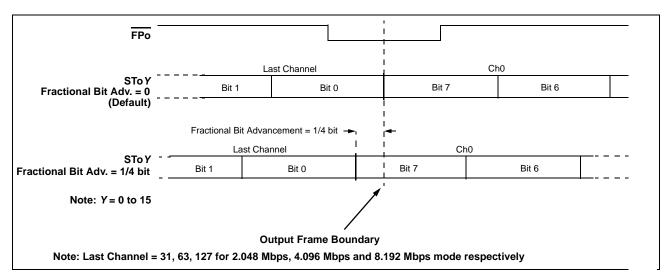

| Figure 19 - Fractional Output Bit Advancement Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                  |

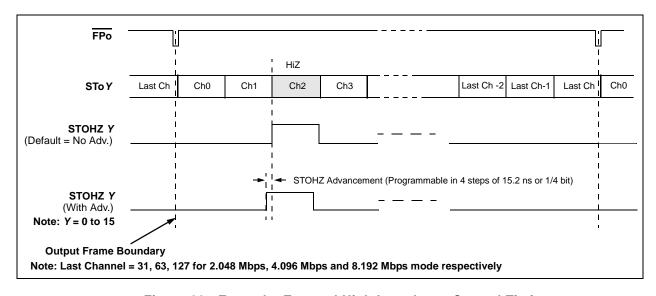

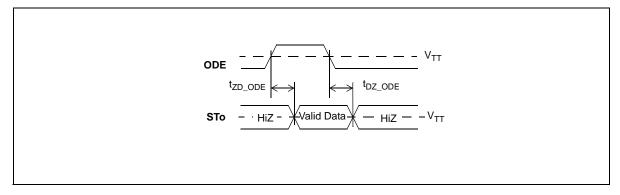

| Figure 20 - Example: External High Impedance Control Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                  |

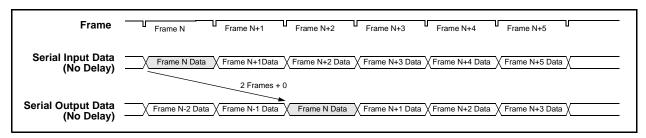

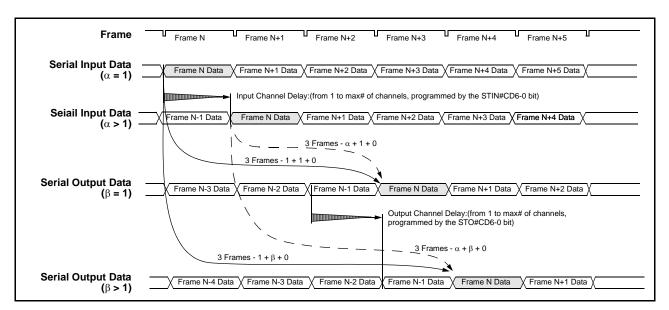

| Figure 21 - Data Throughput Delay when Input and Output Channel Delay are Disabled for Input Ch0 Switche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                  |

| Output Ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                  |

| Figure 22 - Data Throughput Delay when Input Channel Delay is Enabled and Output Channel Delay is Disab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                  |

| for Input Ch0 Switched to Output Ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                  |

| Figure 23 - Data Throughput Delay when Input Channel Delay is Disabled and Output Channel Delay is Enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                  |

| for Input Ch0 Switch to Output Ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |

| Figure 24 - Data Throughput Delay when Input and Output Channel Delay are Enabled for Input Ch0 Switche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | d to                                                                                                             |

| Output Ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                  |

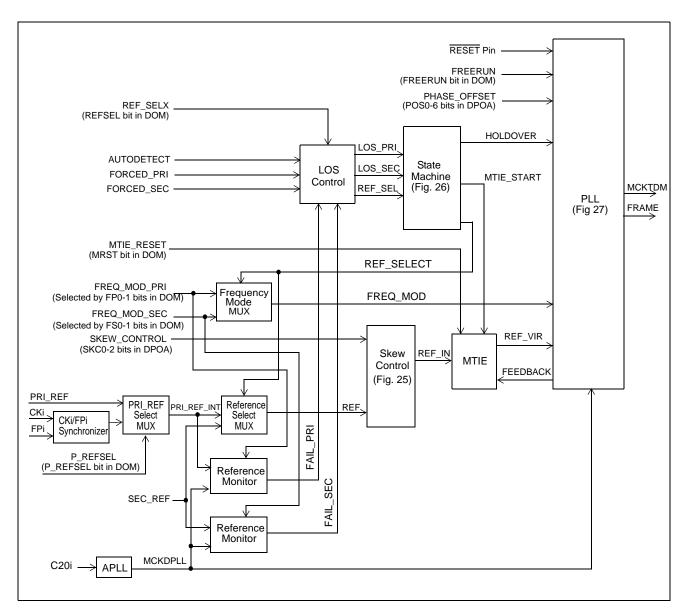

| Figure 25 - DPLL Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 36                                                                                                             |

| Figure 26 - Skew Control Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 37                                                                                                             |

| Figure 27 - State Machine Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                  |

| rigure 27 - State Machine Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                  |

| Figure 28 - Block Diagram of the PLL Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 38                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 38                                                                                                             |

| Figure 28 - Block Diagram of the PLL Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 38<br>. 39<br>. 42                                                                                             |

| Figure 28 - Block Diagram of the PLL Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 38<br>. 39<br>. 42                                                                                             |

| Figure 28 - Block Diagram of the PLL Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 38<br>. 39<br>. 42<br>. 42                                                                                     |

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram)  Figure 31 - Crystal Oscillator Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 38<br>. 39<br>. 42<br>. 42<br>. 45                                                                             |

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 38<br>. 39<br>. 42<br>. 42<br>. 45<br>. 46                                                                     |

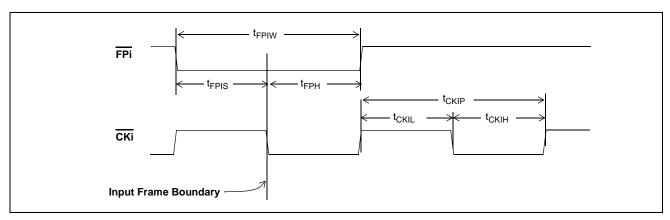

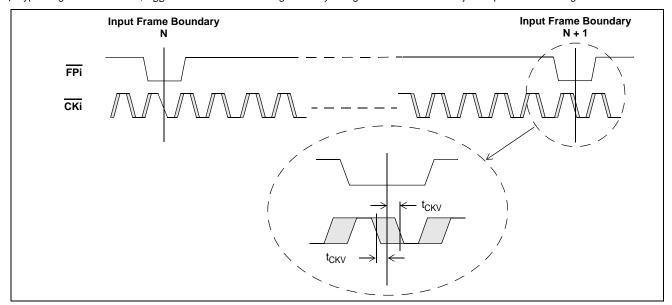

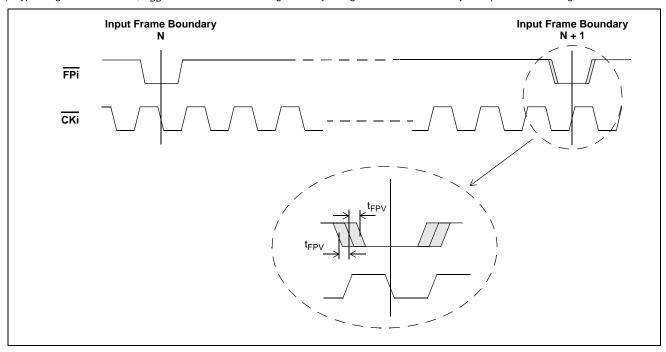

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 38<br>. 39<br>. 42<br>. 45<br>. 46<br>. 73                                                                     |

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 38<br>. 39<br>. 42<br>. 45<br>. 46<br>. 73<br>. 74                                                             |

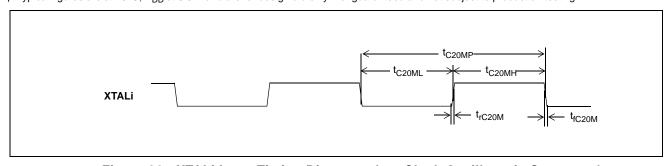

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation .  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected .                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 38<br>. 39<br>. 42<br>. 45<br>. 46<br>. 73<br>. 74                                                             |

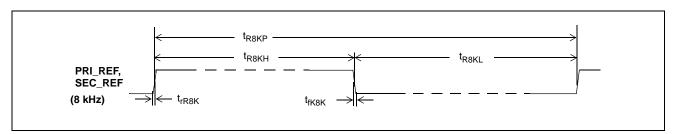

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation .  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected .  Figure 37 - Reference Input Timing Diagram when the Input Frequency = 8 kHz .                                                                                                                                                                                                                                                                                                                                                                | . 38<br>. 39<br>. 42<br>. 45<br>. 45<br>. 73<br>. 73<br>. 74<br>. 74                                             |

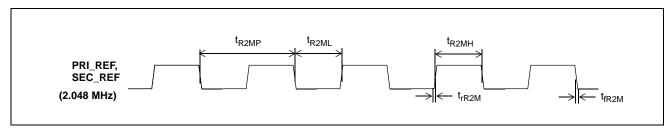

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation .  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected .  Figure 37 - Reference Input Timing Diagram when the Input Frequency = 8 kHz .  Figure 38 - Reference Input Timing Diagram when the Input Frequency = 2.048 MHz .                                                                                                                                                                                                                                                                             | . 38<br>. 39<br>. 42<br>. 45<br>. 46<br>. 73<br>. 74<br>. 75                                                     |

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation .  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected .  Figure 37 - Reference Input Timing Diagram when the Input Frequency = 8 kHz .  Figure 38 - Reference Input Timing Diagram when the Input Frequency = 2.048 MHz .  Figure 39 - Reference Input Timing Diagram when the Input Frequency = 1.544 Hz                                                                                                                                                                                             | . 38<br>. 39<br>. 42<br>. 45<br>. 73<br>. 73<br>. 74<br>. 75<br>. 75                                             |

| Figure 28 - Block Diagram of the PLL Module.  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies.  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram)  Figure 31 - Crystal Oscillator Circuit.  Figure 32 - External Clock Oscillator Circuit  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram.  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation.  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected  Figure 37 - Reference Input Timing Diagram when the Input Frequency = 8 kHz.  Figure 38 - Reference Input Timing Diagram when the Input Frequency = 2.048 MHz.  Figure 39 - Reference Input Timing Diagram when the Input Frequency = 1.544 Hz  Figure 40 - Input and Output Frame Boundary Offset                                                                                                                                                        | . 388<br>. 399<br>. 422<br>. 455<br>. 466<br>. 73<br>. 74<br>. 74<br>. 75<br>. 75<br>. 75                        |

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram)  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation .  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected .  Figure 37 - Reference Input Timing Diagram when the Input Frequency = 8 kHz .  Figure 38 - Reference Input Timing Diagram when the Input Frequency = 2.048 MHz .  Figure 39 - Reference Input Timing Diagram when the Input Frequency = 1.544 Hz .  Figure 40 - Input and Output Frame Boundary Offset .  Figure 41 - FPo0 and CKo0 Timing Diagram .                                                                                           | . 388<br>. 399<br>. 422<br>. 455<br>. 466<br>. 73<br>. 744<br>. 755<br>. 755<br>. 766<br>. 77                    |

| Figure 28 - Block Diagram of the PLL Module.  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies.  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram)  Figure 31 - Crystal Oscillator Circuit  Figure 32 - External Clock Oscillator Circuit  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram.  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation.  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected  Figure 37 - Reference Input Timing Diagram when the Input Frequency = 8 kHz.  Figure 38 - Reference Input Timing Diagram when the Input Frequency = 1.544 Hz.  Figure 40 - Input and Output Frame Boundary Offset  Figure 41 - FPo0 and CKo0 Timing Diagram.  Figure 42 - FPo1 and CKo1 Timing Diagram.                                                                                                                                                    | . 388<br>. 399<br>. 422<br>. 452<br>. 466<br>. 73<br>. 744<br>. 755<br>. 756<br>. 777<br>. 78                    |

| Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation .  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected .  Figure 37 - Reference Input Timing Diagram when the Input Frequency = 8 kHz .  Figure 38 - Reference Input Timing Diagram when the Input Frequency = 2.048 MHz .  Figure 39 - Reference Input Timing Diagram when the Input Frequency = 1.544 Hz .  Figure 40 - Input and Output Frame Boundary Offset .  Figure 41 - FP00 and CK00 Timing Diagram .  Figure 42 - FP01 and CK01 Timing Diagram .  Figure 43 - FP02 and CK02 Timing Diagram . | . 388<br>. 399<br>. 422<br>. 452<br>. 466<br>. 733<br>. 744<br>. 755<br>. 755<br>. 757<br>. 777<br>. 788<br>. 79 |

| Figure 28 - Block Diagram of the PLL Module.  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies.  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram)  Figure 31 - Crystal Oscillator Circuit  Figure 32 - External Clock Oscillator Circuit  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram.  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation.  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected  Figure 37 - Reference Input Timing Diagram when the Input Frequency = 8 kHz.  Figure 38 - Reference Input Timing Diagram when the Input Frequency = 1.544 Hz.  Figure 40 - Input and Output Frame Boundary Offset  Figure 41 - FPo0 and CKo0 Timing Diagram.  Figure 42 - FPo1 and CKo1 Timing Diagram.                                                                                                                                                    | . 388<br>. 399<br>. 422<br>. 455<br>. 466<br>. 733<br>. 744<br>. 755<br>. 756<br>. 777<br>. 788<br>. 799<br>. 80 |

ZL50010

# **List of Figures**

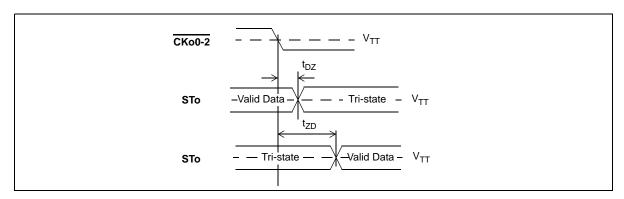

| Figure 46 - Serial Output and External Control  | 82 |

|-------------------------------------------------|----|

| Figure 47 - Output Driver Enable (ODE)          | 82 |

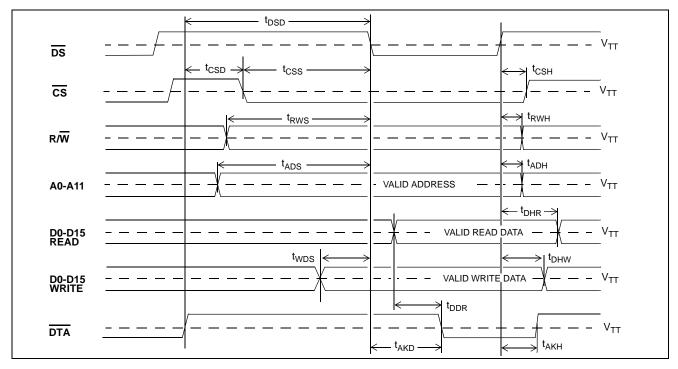

| Figure 48 - Motorola Non-Multiplexed Bus Timing | 83 |

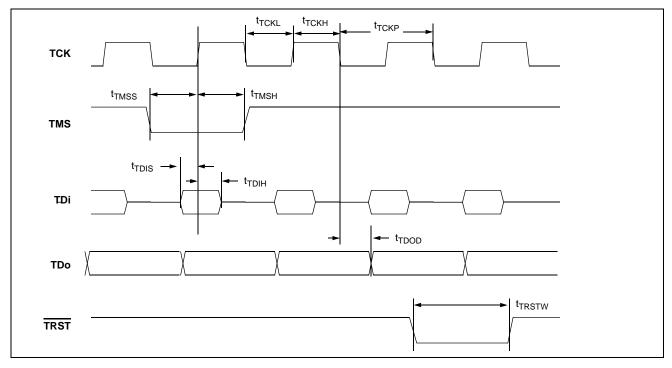

| Figure 49 - JTAG Test Port Timing Diagram       | 84 |

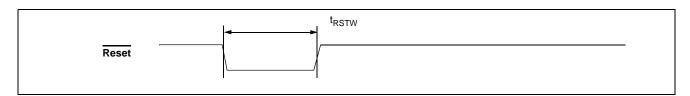

| Figure 50 - Reset Pin Timing Diagram.           | 84 |

## ZL50010

## **List of Tables**

| Table 1 - FPi and CKi Input Programming                                      |            |

|------------------------------------------------------------------------------|------------|

| Table 2 - FPo0 and CKo0 Output Programming                                   | 19         |

| Table 3 - FPo1 and CKo1 Output Programming                                   | 19         |

| Table 4 - FPo2 and CKo2 Output Programming                                   | 19         |

| Table 5 - Variable Range for Input Streams                                   | 27         |

| Table 6 - Variable Range for Output Streams                                  | 27         |

| Table 7 - Data Throughput Delay                                              | 27         |

| Table 8 - Connection Memory in Block Programming Mode                        | 30         |

| Table 9 - Definition of the Four Quadrant Frames                             | 31         |

| Table 10 - Quadrant Frame 0 LSB Replacement                                  |            |

| Table 11 - Quadrant Frame 1 LSB Replacement                                  |            |

| Table 12 - Quadrant Frame 2 LSB Replacement                                  | 31         |

| Table 13 - Quadrant Frame 3 LSB Replacement                                  | 32         |

| Table 14 - DPLL Operating Mode Settings                                      | 33         |

| Table 15 - LOS Outputs in the Failure Detect Modes                           |            |

| Table 16 - Address Map for Device Specific Registers                         | <b>5</b> 0 |

| Table 17 - Control Register (CR) Bits                                        |            |

| Table 18 - Internal Mode Selection (IMS) Register Bits                       | 53         |

| Table 19 - BER Start Receiving Register (BSRR) Bits                          | 54         |

| Table 20 - BER Length Register (BLR) Bits                                    |            |

| Table 21 - BER Count Register (BCR) Bits                                     |            |

| Table 22 - DPLL Operation Mode (DOM) Register Bits                           | 56         |

| Table 23 - DPLL Output Adjustment (DPOA) Register Bits                       |            |

| Table 24 - DPLL House Keeping (DHKR) Register Bits                           |            |

| Table 25 - Stream Input Control Register 0 to 7 (SICR0 to SICR7)             |            |

| Table 26 - Stream Input Control Register 8 to 15 (SICR8 to SICR15)           |            |

| Table 27 - Stream Input Delay Register 0 to 7 (SIDR0 to SIDR7)               |            |

| Table 28 - Stream Input Delay Register 8 to 15 (SIDR8 to SIDR15)             |            |

| Table 29 - Stream Output Control Register 0 to 7 (SOCR0 to SOCR7)            |            |

| Table 30 - Stream Output Control Register 8 to 15 (SOCR8 to SOCR15)          |            |

| Table 31 - Stream Output Offset Register 0 to 7 (SOOR0 to SOOR7)             |            |

| Table 32 - Stream Output Offset Register 8 to 15 (SOOR8 to SOOR15)           |            |

| Table 33 - Address Map for Memory Locations (512x512 DX, MSB of address = 1) |            |

| Table 34 - Connection Memory Bit Assignment when the CMM bit = 0             | 70         |

| Table 35 - Connection Memory Bits Assignment when the CMM bit = 1            | 70         |

### **Changes Summary**

The following table captures the changes from the July 2004 issue.

| Page       | Item                                                                                                                                | Change                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 12, 35, 45 | <ul><li>(1) Pin Descritpion - Signal XTALi</li><li>(2) 2.9.3 "DPLL Bypass Mode"</li><li>(3) 3.0 "Oscillator Requirements"</li></ul> | Clarified initialization input clock requirement in DPLL Bypass mode.                                                   |

| 18         | 2.1.4 "Improved Input Jitter Tolerance with Frame Boundary Determinator"                                                            | Added a new section to describe the improved input jitter tolerance with the frame boundary determinator.               |

| 51         | Table 17 - "Control Register (CR) Bits" - bits "FBDMODE" and "FBDEN"                                                                | Renamed bit 15 from Unused to FBDMODE and<br>added description to clarify the frame boundary<br>determinator operation. |

|            |                                                                                                                                     | Clarified FBDEN description.                                                                                            |

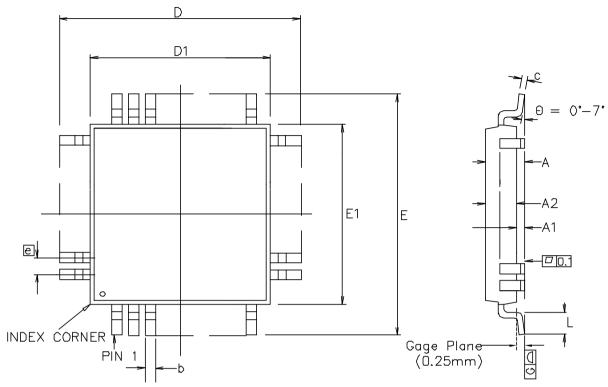

Figure 2 - 24 mm x 24 mm LQFP (JEDEC MS-026) Pinout Diagram

### PINOUT DIAGRAM: (as viewed through top of package)

A1 corner identified by metallized marking, mould indent, ink dot or right-angled corner

| \ | 1           | 2           | 3           | 4           | 5   | 6   | 7           | 8            | 9    | 10   | 11    | 12    |

|---|-------------|-------------|-------------|-------------|-----|-----|-------------|--------------|------|------|-------|-------|

| Α | ODE         | FPo2        | FPo0        | SEC_<br>REF | IC1 | IC0 | XTALi       | XTALo        | TM1  | CKi  | TDi   | TCK   |

| В | CKo2        | CKo1        | FPo1        | CKo0        | IC3 | IC2 | CLK<br>BYPS | VDD_<br>APLL | SG1  | FPi  | TRST  | TMS   |

| С | STo2        | STo1        | STOHZ<br>0  | PRI_<br>REF | NC  | NC  | IC4         | NC2          | NC1  | TM2  | TDo   | STi15 |

| D | STo3        | STo0        | STOHZ<br>1  | VSS         | VDD | VDD | VDD         | VSS_<br>APLL | VSS  | STi8 | RESET | STi14 |

| Е | STo5        | STo4        | STOHZ<br>3  | STOHZ<br>2  | VSS | VSS | VSS         | VSS          | VDD  | STi9 | STi13 | STi12 |

| F | STo6        | STo7        | STOHZ<br>4  | VDD         | VSS | VSS | VSS         | VSS          | VDD  | STi7 | STi10 | STi11 |

| G | STOHZ<br>6  | STOHZ<br>7  | STOHZ<br>5  | VDD         | VSS | VSS | VSS         | VSS          | STi1 | STi6 | STi5  | STi4  |

| Н | STo9        | STo10       | STo8        | VDD         | VSS | VSS | VSS         | VSS          | STi0 | DS   | STi2  | STi3  |

| J | STo11       | STOHZ<br>11 | STOHZ<br>8  | VSS         | D2  | VDD | VDD         | VDD          | A10  | A9   | A8    | A11   |

| K | STOHZ<br>9  | STOHZ<br>15 | STo15       | STOHZ<br>13 | D1  | D5  | CS          | D10          | D11  | A5   | A4    | A7    |

| L | STOHZ<br>10 | STo12       | STo13       | D3          | D15 | D4  | D7          | D12          | D14  | A2   | A3    | A6    |

| М | STo14       | STOHZ<br>12 | STOHZ<br>14 | D0          | DTA | D6  | D8          | D9           | D13  | A0   | A1    | R/W   |

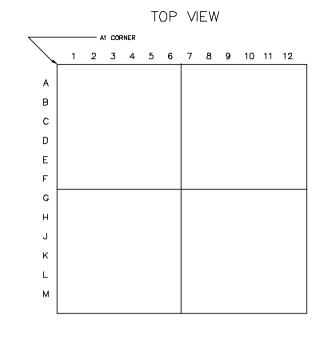

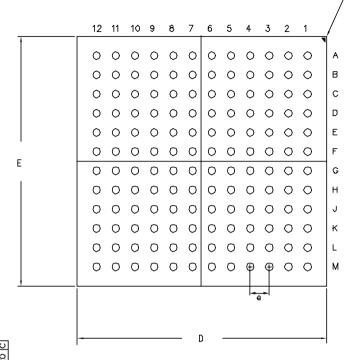

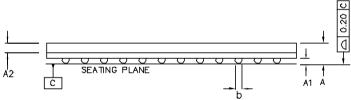

Figure 3 - 13 mm x 13 mm 144 Ball LBGA Pinout Diagram

## **Pin Description**

| -<br>                                                                                 |                                                                                      |                       |                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |