POWER MANAGEMENT SYSTEM DEVICE

# RN5T568C-E4

**Product Specifications**

**Rev1.1**

2017.11.08

RICOH Electronic Devices Co., Ltd.

This specification is subject to change without notice.

# Table of Contents

| 1. | Outl  | utline                                 |    |  |  |  |

|----|-------|----------------------------------------|----|--|--|--|

| 2. | Feat  | Feature                                |    |  |  |  |

| 3. | Bloc  | k Diagram                              | 6  |  |  |  |

| 4. | Elec  | trical Characteristics                 | 7  |  |  |  |

| 4. | 1     | Absolute Maximum Ratings               | 7  |  |  |  |

| 4. |       | Recommendation of Operating Conditions |    |  |  |  |

| 4. |       | I/O Electrical Characteristics         |    |  |  |  |

| 4. |       | Consumption Current                    |    |  |  |  |

| 5. | Pac   | kage information                       | 11 |  |  |  |

| 5. | 1     | Pin Configuration                      | 11 |  |  |  |

| 5. | 2     | QFN0707-48 Package                     | 12 |  |  |  |

| 6. | Pin l | Description                            | 13 |  |  |  |

| 7. | Pow   | ver Control                            | 14 |  |  |  |

| 7. | .1    | State Machine Diagram                  | 14 |  |  |  |

| 7. | 2     | State Machine Description              |    |  |  |  |

| 7. | 3     | Power On Sequence                      | 16 |  |  |  |

| 7. | 4     | Power Off Sequence                     | 17 |  |  |  |

| 7. | 5     | Sleep Entry/Exit Sequence              | 18 |  |  |  |

| 7. | 6     | Repower-on Sequence                    | 20 |  |  |  |

| 7. | 7     | Shutdown Factor                        | 21 |  |  |  |

| 7. | 8     | Shutdown Sequence                      | 21 |  |  |  |

| 7. | 9     | Power-on/off History                   | 23 |  |  |  |

| 7. | 10    | Watchdog Timer Function                | 24 |  |  |  |

| 7. | 11    | Power Control Block Interrupt Request  | 24 |  |  |  |

| 7. | 12    | PWRON Long Press Operation             | 25 |  |  |  |

| 7. | 13    | Power-on Signal Output by GPIO0-3      | 25 |  |  |  |

| 7. | 14    | Voltage Detector                       | 26 |  |  |  |

| 7. | 15    | Overheat Detection Block               | 27 |  |  |  |

| 8. | Reg   | ulators                                | 28 |  |  |  |

| 8. | 1     | Regulators Table                       | 28 |  |  |  |

| 8. | 2     | DCDC Electrical Characteristics        | 29 |  |  |  |

| 8. | 3     | LDO Electrical Characteristics         | 32 |  |  |  |

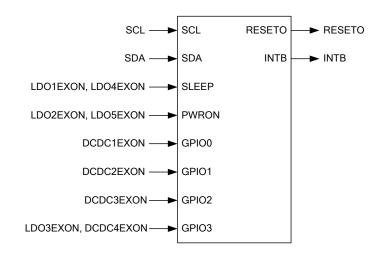

| 9.  | МО   | DE                                                          | 37 |

|-----|------|-------------------------------------------------------------|----|

| 9.  | 1    | Normal MODE                                                 | 37 |

| 9.  | 2    | Parts MODE                                                  | 38 |

| 10. | GPI  | IO                                                          | 40 |

| 11. | I2C  | -Bus interface                                              | 43 |

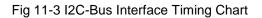

| 11  | 1.1  | I2C-Bus Operation                                           | 43 |

| 11  | 1.2  | AC Characteristics of I2C-Bus                               | 44 |

| 11  | 1.3  | I2C-Bus Data Transmission and its Acknowledge               | 45 |

| 11  | 1.4  | I2C-Bus Slave Address                                       | 45 |

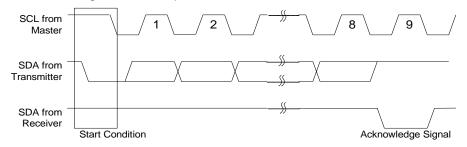

| 11  | 1.5  | I2C-Bus Data Transmission Read Format (Fast Speed mode)     | 46 |

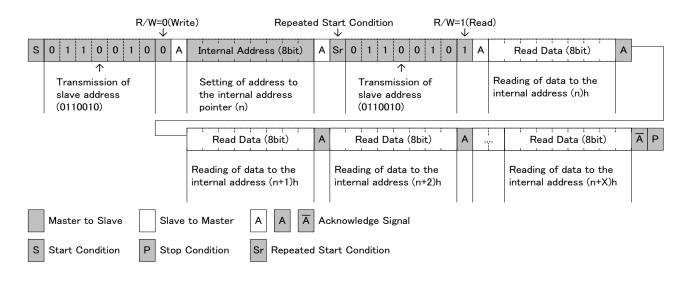

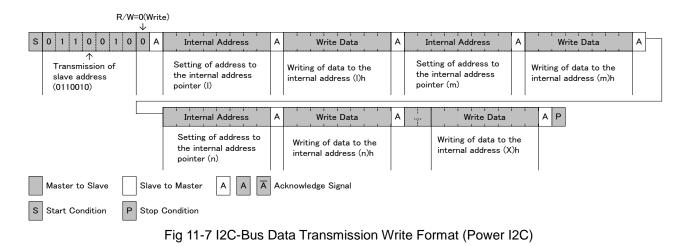

| 11  | I.6  | I2C-Bus Data Transmission Write Format (Fast Speed mode)    | 46 |

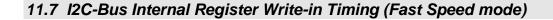

| 11  | 1.7  | I2C-Bus Internal Register Write-in Timing (Fast Speed mode) | 47 |

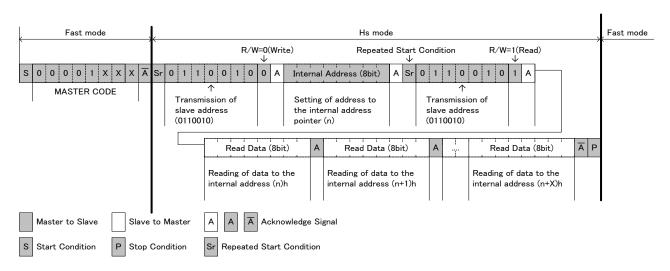

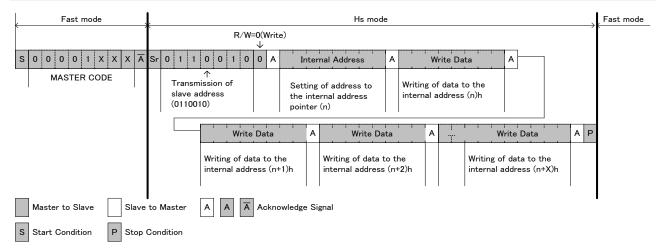

| 11  | l.8  | I2C-Bus Data Transmission Read Format (Hs mode)             | 48 |

| 11  | 1.9  | I2C-Bus Data Transmission Write Format (Hs mode)            | 48 |

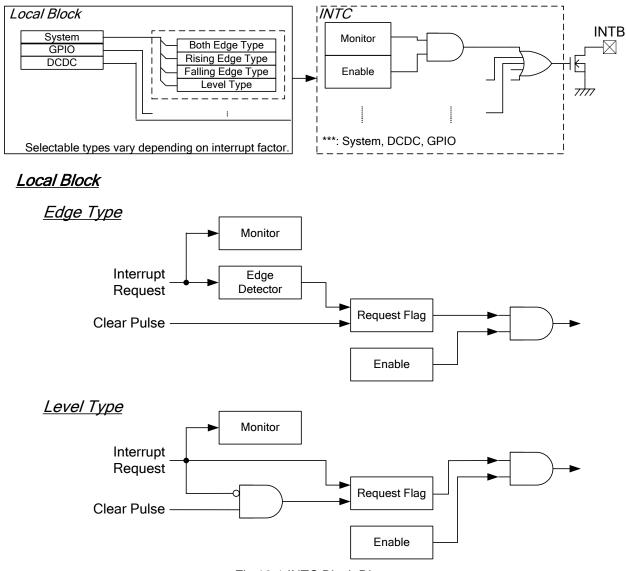

| 12. | Inte | rrupt Controller (INTC)                                     | 49 |

| 12  | 2.1  | Interrupt Controller Block Diagram                          | 49 |

| 13. | Reg  | jisters                                                     | 50 |

| 13  | 3.1  | Registers Map                                               | 50 |

| 13  | 3.2  | SYSTEM                                                      | 52 |

| 13  | 3.3  | I2C                                                         | 55 |

| 13  | 3.4  | Power Control                                               | 56 |

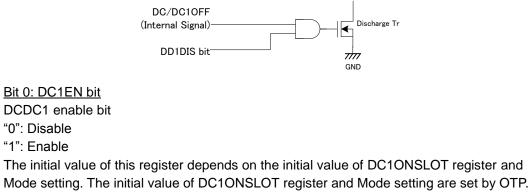

| 13  | 3.5  | DCDC                                                        | 69 |

| 13  | 3.6  | LDO                                                         | 80 |

| 13  | 3.7  | GPIO                                                        | 88 |

| 13  | 3.8  | INTC                                                        | 93 |

| 13  | 3.9  | SYSTEM OPTION                                               | 95 |

# 1. Outline

This IC is the power management IC for GPS-PND/STB/POS/Panel Computer and so on. It integrates four high-efficiency step-down DCDC converters, seven low dropout regulators, power control logic, I2C-Bus Interface, voltage detections, thermal shut-down, and etc.

# 2. Feature

# System

- ✓ I2C-Bus interface @3.4MHz and 400kHz

- ✓ Detector Function (System/IO, UVLO, DETVSB)

- Thermal Shutdown Function

- ✓ Watchdog timer

- ✓ Power on key input for System's power up

- Power on reset output for CPU

- ✓ Flexible power-on/off sequence by OTP

- ✓ Flexible DCDCx and LDOx default-on/off control by OTP

•High Efficiency Step-down DC/DC Converters

|              | noy olop dom |          |            |

|--------------|--------------|----------|------------|

| $\checkmark$ | DC/DC1       | 0.6-3.5V | Max 3000mA |

| $\checkmark$ | DC/DC2       | 0.6-3.5V | Max 3000mA |

| $\checkmark$ | DC/DC3       | 0.6-3.5V | Max 2000mA |

|              |              |          |            |

| $\checkmark$ | DC/DC4 | 0.6-3.5V | Max 2000mA |

|--------------|--------|----------|------------|

|              |        |          |            |

✓ Soft-start circuit

•Low Drop Voltage Regulators

| $\checkmark$ | LDO1 | 0.9-3.5V | Max 300mA |

|--------------|------|----------|-----------|

| $\checkmark$ | LDO2 | 0.9-3.5V | Max 300mA |

| $\checkmark$ | LDO3 | 0.6-3.5V | Max 300mA |

| $\checkmark$ | LDO4 | 0.9-3.5V | Max 200mA |

| $\checkmark$ | LDO5 | 0.9-3.5V | Max 200mA |

LDORTC1 1.2-3.5V Max 30mA (AlwaysOn, For coin battery)

- LDORTC2 0.9-3.5V Max 10mA (AlwaysOn)

- Over current Protection and Short circuit Protection.

# •4ch-GPIO

- Supports interrupt function (level/edge) for input signals

- Outputs power-on signal for external devices

- ✓ Power on/off input for System's power up/down

- ✓ DCDCx and LDOx can be controlled by external input

- ✓ GPIO2 can output LDORTC2

- GPIO0 and GPIO1 have maximum 15mA sink for LED.

- GPIOx have Output C32KOUT of internal clock for external devices.

- Interrupt Controller (INTC)

- •Package QFN0707-48 (0.5mm pitch)

- •Process CMOS

#### OTP selected list

|         | OTP Function | Setting                 |

|---------|--------------|-------------------------|

|         | I2CSLV       | 2: 32h                  |

|         | SLEEPPOL     | 0: Non-Inversion        |

|         | PWRONPOL     | 0: Non-Inversion        |

| Γ       |              |                         |

| System  | VINDAC       | 4: 3.0V                 |

| OTP     | VINHYSSEL    | 1: 200mV                |

| Setting | VINRRESET    | 1: ERSTB                |

|         | IODAC        | 1: 1.60V                |

|         |              |                         |

|         | PREVINDAC    | <b>6</b> :3.5(↑)/3.4(↓) |

|         | OVTEMP       | 0: 105/85°C             |

| Explanation:                                                                 |   |

|------------------------------------------------------------------------------|---|

| The settings of I2C slave address (A3-A1).                                   |   |

| SLEEP pin polarity selection ( Default High active )                         |   |

| PWRON pin polarity selection ( Default High active )                         |   |

|                                                                              |   |

| System Voltage Detection for Power-ON permit.                                |   |

| Hysteresis Voltage for VINDET (System Voltage Detection for Power-ON permit) |   |

| VINDAC/VINHYS Reset selection                                                |   |

| VDDIO Voltage Detection ( Power OFF factor )                                 | - |

|                                                                              |   |

| System Voltage Pre-Detection (Interrupt output)                              |   |

| initial temperature of Overheat Detection(Interrupt output)                  |   |

DD1LIM

|         | OTP Function | Setting          |

|---------|--------------|------------------|

| GPIO    | GPIO3POL     | 0: Non-Inversion |

| OTP     | GPIO2POL     | 0: Non-Inversion |

| setting | GPIO1POL     | 0: Non-Inversion |

| setting | GPIO0POL     | 0: Non-Inversion |

|           | OTP Function  | Setting     |

|-----------|---------------|-------------|

|           | LDORTC1AWON   | 1: AlwaysOn |

|           |               |             |

|           | LDORTC10NSLOT | 0: Enable   |

|           | LDO50NSLOT    | 0: Enable   |

| Sequence, | LDO40NSLOT    | 0: Enable   |

| DCDC,     | LDO3ONSLOT    | 0: Enable   |

| LDO       | LDO2ONSLOT    | 0: Enable   |

| OTP       | LDO10NSLOT    | 0: Enable   |

| settings  |               |             |

|           | DC4ONSLOT     | 0: Enable   |

|           | DC3ONSLOT     | 0: Enable   |

|           | DC2ONSLOT     | 0: Enable   |

|           | DC10NSLOT     | 0: Enable   |

| OTP Function | Setting |

|--------------|---------|

| LRTCDAC      | 3.30V   |

|              |         |

-

Explanation: GPIO3 input's polarity ( Default High Active ) GPIO2 input's polarity ( Default High Active ) GPIO1 input's polarity ( Default High Active ) GPIO0 input's polarity ( Default High Active )

| L5DAC | 3.30V  |

|-------|--------|

| L4DAC | 3.30V  |

| L3DAC | 2.50V  |

| L2DAC | 3.30V  |

| L1DAC | 1.80V  |

|       |        |

|       | 1.801/ |

| DD4DAC | 1.80V |

|--------|-------|

| DD3DAC | 1.20V |

| DD2DAC | 1.10V |

| DD1DAC | 1.10V |

| Explanation                                |      |

|--------------------------------------------|------|

| LDORTC1 Always-ON or I2C Control / Initial | VOUT |

| The setting of initial ON/OFF for RTCLDO1 (Select "0:Enable" for AwaysON) |                                                |                                  |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------------|----------------------------------|--|--|--|--|

| The setting of LD                                                         | The setting of LDO5 Pin Control / Initial VOUT |                                  |  |  |  |  |

| The setting of LD                                                         | 004 Pin C                                      | ontrol / Initial VOUT            |  |  |  |  |

| The setting of LD                                                         | 003 Pin C                                      | ontrol / Initial VOUT            |  |  |  |  |

| The setting of LD                                                         | 002 Pin C                                      | ontrol / Initial VOUT            |  |  |  |  |

| The setting of LD                                                         | 001Pin Co                                      | ontrol / Initial VOUT            |  |  |  |  |

|                                                                           |                                                |                                  |  |  |  |  |

| DD4LIM                                                                    | 1: 2.3A                                        | Pin control /VOUT /Limit Current |  |  |  |  |

| DD3LIM                                                                    | 1: 2.3A                                        | Pin control /VOUT /Limit Current |  |  |  |  |

| DD2LIM                                                                    | 1: 3.2A                                        | Pin control /VOUT /Limit Current |  |  |  |  |

| DDALINA                                                                   | 4.0.04                                         |                                  |  |  |  |  |

| 1: 2.3A | Pin control /VOUT /Limit Current |

|---------|----------------------------------|

| 1: 2.3A | Pin control /VOUT /Limit Current |

| 1: 3.2A | Pin control /VOUT /Limit Current |

| 1: 3.2A | Pin control /VOUT /Limit Current |

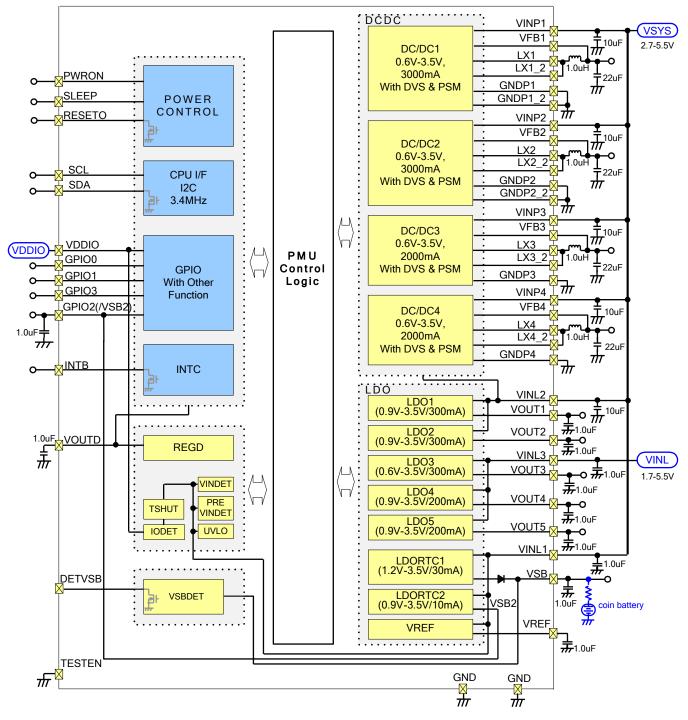

# 3. Block Diagram

Fig 3-1 Block Diagram

# 4. Electrical Characteristics

# 4.1 Absolute Maximum Ratings

Exposure to the condition exceeded absolute maximum ratings may cause the permanent damages and affect the reliability and safety of both device and systems using the device. The functional operations cannot be guaranteed beyond specified values in the recommended conditions.

| Symbol           | Parameter              | Condition                     | Min    | Max              | Units       |

|------------------|------------------------|-------------------------------|--------|------------------|-------------|

| $V_{PS1}$        | Power Supply Voltage 1 | VINP1-4, VINL1-3pin           | -0.3   | 6.0              | V           |

| $V_{PS2}$        | Power Supply Voltage 2 | VDDIO pin                     | -0.3   | 4.5              | V           |

|                  |                        | PWRON, SLEEP pin              | -0.3   | VINL1 + 0.3      | V           |

|                  |                        | SDA, SCL pin                  | -0.3   | 4.5              | V           |

| VINPUT           | Input Voltage Range    | GPIO0-1 pin                   | -0.3   | VINL1 + 0.3 /    | V           |

|                  |                        |                               |        | VDDIO + 0.3      |             |

|                  |                        | GPIO2-3 pin                   | -0.3   | VINL1 + 0.3      | V           |

|                  |                        | RESETO, INTB,GPIO2-3 pin      | -0.3   | VINL1 + 0.3      | V           |

| Max              | Output Valtage Denge   | GPIO0-1 pin                   | -0.3   | VINL1 + 0.3 /    | V           |

| Voutput          | Output Voltage Range   |                               |        | VDDIO + 0.3      |             |

|                  |                        | DETVSB pin                    | -0.3   | VSB*+ 0.3        | V           |

| T <sub>stg</sub> | Storage Temperature    | -                             | -55    | 125              | degrees C   |

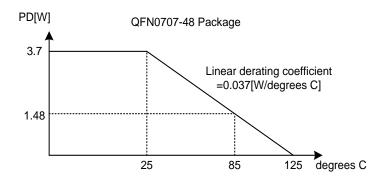

| PD               | Package Allowable      | QFN0707-48(0.5mm pitch)       | 0      | 3700             | mW          |

|                  | Dissipation            | T <sub>a</sub> = 25 degrees C |        |                  |             |

|                  |                        | *VSB                          | : LDOF | RTC1_Output or C | oin Battery |

Table 4-1 Absolute Maximum Ratings

Fig 4-1 Maximum Package Allowable Dissipation

# 4.2 Recommendation of Operating Conditions

| Symbol | Parameter                | Condition                   | Min  | Тур | Max | Units     |

|--------|--------------------------|-----------------------------|------|-----|-----|-----------|

| VSYS   | Power Supply Voltage     | VINP1-4, VINL1-2 pin *1     | 2.7  | 3.6 | 5.5 | V         |

| VINL   | Power Supply Voltage     | VINL3 pin *2                | 1.7  | 3.6 | 5.5 | V         |

| VDDIO  | Power Supply Voltage     | VDDIO pin<br>(VSYS > VDDIO) | 1.7  | 1.8 | 3.4 | V         |

| VSB    | Power Supply Voltage     | VSB pin                     | 1.45 | 3.1 | 3.4 | V         |

| *GND*  | Ground                   | GND                         |      | 0   |     | V         |

| Та     | Temperature of Operation | -                           | -40  |     | 85  | degrees C |

Note\*1:VINP1-4 and VINL2 must be equal to VINL1.

However, if POWROFF state, VINP1-4 and VINL2 is possible to power-off

(Only Parts Mode and then Input pin level must be GND.)

Note\*2:VINL3 must be less than or equal to VINL1.

Table 4-2 Recommendation of Operating Conditions

# 4.3 I/O Electrical Characteristics

| Symbol    | Parameter                         | Condition       | Min       | Тур | Max       | Units |

|-----------|-----------------------------------|-----------------|-----------|-----|-----------|-------|

| VINL1 NMC | OS Input Pin: PWRON,SLEEP, GP     | IO0, GPIO1, GPI | 02, GPI03 |     |           |       |

| VIL       | Low level input voltage           |                 |           |     | 0.4       | V     |

| VIH       | High level input voltage          |                 | 1.4       |     | VINL1     | V     |

| VINL1 Nch | Open Drain output Pin : RESETO    |                 |           |     |           |       |

| VOL       | Low level output voltage          | lout = 2mA      |           |     | 0.4       | V     |

| Vto       | Tolerant                          |                 |           |     | VINL1     | V     |

| VINL1 CMC | )S input/output Pin : GPIO0, GPIO | 1, GPI02, GPI03 | 3         |     |           | •     |

| VIL       | Low level input voltage           |                 |           |     | VINL1*0.2 | V     |

| VIH       | High level input voltage          |                 | VINL1*0.8 |     | VINL1     | V     |

| VOL       | Low level output voltage          | lout = 4mA      |           |     | 0.4       | V     |

| VOH       | High level output voltage         | lout = -4mA     | VINL1-0.4 |     |           | V     |

| VINL1 Nch | Open Drain output Pin : INTB, GP  | IO0, GPIO1, GPI | 02, GPI03 |     |           |       |

| VOL       | Low level output voltage          | lout = 4mA      |           |     | 0.4       | V     |

| Vto       | Tolerant                          |                 |           |     | VINL1     | V     |

| VINL1 Nch | Open Drain output Pin: GPIO0, GI  | PIO1 (for LED)  |           |     |           |       |

| VOL       | Low level output voltage          | lout = 15mA     |           |     | 0.4       | V     |

| Vto       | Tolerant                          |                 |           |     | VINL1     | V     |

| VSB Nch O | pen Drain output Pin: DETVSB      |                 |           |     |           |       |

| VOL       | Low level output voltage          | lout = 1mA      |           |     | 0.2       | V     |

| Vto       | Tolerant                          |                 |           |     | VSB       | V     |

| Symbol   | Parameter                                 | Condition        | Min            | Тур | Max        | Units |  |

|----------|-------------------------------------------|------------------|----------------|-----|------------|-------|--|

| VOUTD CN | VOUTD CMOS input Pin (Schmitt Input): SCL |                  |                |     |            |       |  |

| VIL      | Low level input voltage                   |                  |                |     | VOUTD *0.3 | V     |  |

| VIH      | High level input voltage                  |                  | VOUTD *0.7     |     | 3.4        | V     |  |

| ΔVI      | Hysteresis                                |                  | VOUTD *0.1     |     |            | V     |  |

| VOUTD CN | 10S input/output Pin(Schmitt Input        | / Nch Open Drail | n output) : SD | 4   |            |       |  |

| VIL      | Low level input voltage                   |                  |                |     | VOUTD *0.3 | V     |  |

| VIH      | High level input voltage                  |                  | VOUTD *0.7     |     | 3.4        | V     |  |

| ΔVI      | Hysteresis                                |                  | VOUTD *0.1     |     |            | V     |  |

| VOL      | Low level output voltage                  | lout = 3mA       |                |     | 0.4        | V     |  |

| VDDIO CM | OS input/output Pin : GPIO0, GPI0         | D1               |                |     |            |       |  |

| VIL      | Low level input voltage                   |                  |                |     | VDDIO*0.2  | V     |  |

| VIH      | High level input voltage                  |                  | VDDIO*0.8      |     | VDDIO      | V     |  |

| VOL      | Low level output voltage                  | lout = 4mA       |                |     | 0.4        | V     |  |

| VOH      | High level output voltage                 | lout = -4mA      | VDDIO-0.4      |     |            | V     |  |

\*VOUTD : REGD\_Output (1.8V)

Table 4-3 I/O Electrical Characteristics

# 4.4 Consumption Current

| Symb<br>ol | Parameter | Condition | Min | Тур | Max | Units |

|------------|-----------|-----------|-----|-----|-----|-------|

| la-        | Standby   | PowerOff  |     | 15  |     |       |

| Ist        | current   | (Note*1)  |     | 15  |     | μA    |

|            | Operating | PowerOn   |     | 250 |     |       |

| IOP        | current   | (Note*1)  |     | 350 |     | μA    |

|            | Sleep     | Sleep     |     | 100 |     |       |

| ISLP       | current   | (Note*1)  |     | 100 |     | μA    |

Operating Conditions (unless otherwise specified)  $T_a = 25$  degrees C,  $V_{IN} = 3.6V$ , No-load

Table 4-4 Consumption Current

Note\*1) Each condition is below. (It is possible to change the enabled LDO/DCDC at PowerOn/Sleep.)

|                | PowerOFF | PowerON | Sleep  |

|----------------|----------|---------|--------|

| LDO1           | -        | 0       | -      |

| LDO2           | -        | 0       | -      |

| LDO3           | -        | 0       | 0      |

| LDO4           | -        | 0       | 0      |

| LDO5           | -        | 0       | -      |

| LDORTC1        | 0        | 0       | 0      |

| LDORTC2        | -        | -       | -      |

| VREF           | 0        | 0       | 0      |

| DCDC1          | -        | 0       | -      |

| DCDC2          | -        | 0       | O(ECO) |

| DCDC3          | -        | -       | -      |

| DCDC4          | -        | -       | -      |

| UVLO           | 0        | 0       | 0      |

| VINDET         | 0        | 0       | 0      |

| IODET          | 0        | 0       | 0      |

| PREVINDET      | 0        | 0       | 0      |

| VSBDET         | 0        | 0       | 0      |

| TSHUT          | 0        | 0       | 0      |

| REGD           | 0        | 0       | 0      |

| Internal Logic | 0        | 0       | 0      |

# 5. Package information

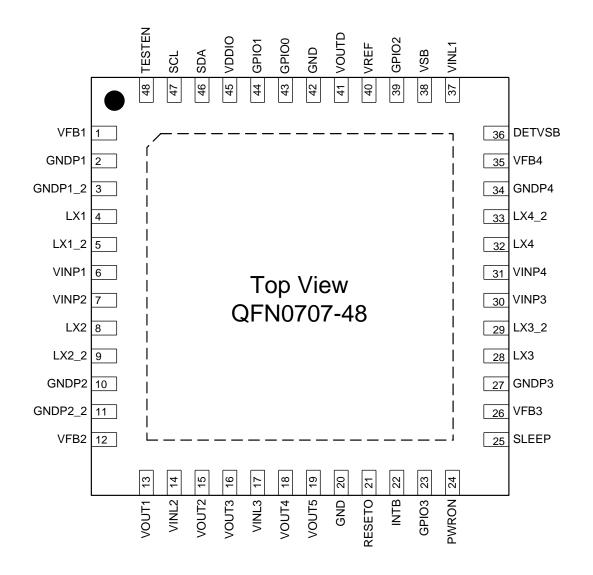

# 5.1 Pin Configuration

Fig 5-1 Pin Configuration

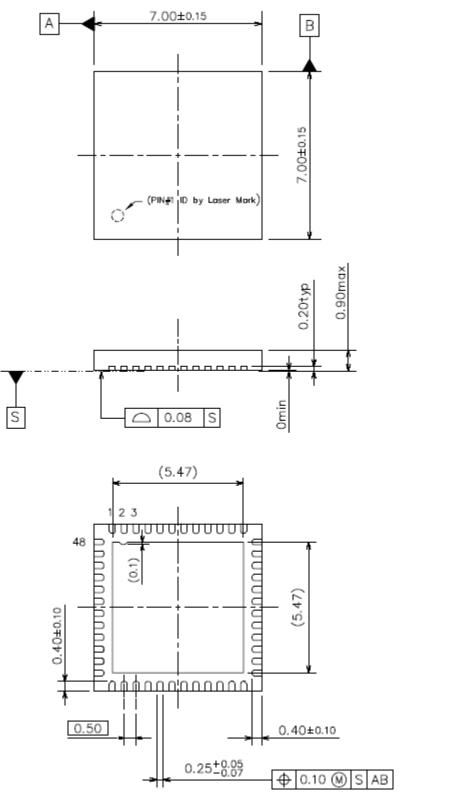

# 5.2 QFN0707-48 Package

UNIT: mm

Fig 5-2 Package Diagram (QFN0707-48pin, 0.5mm pitch)

# 6. Pin Description

| No.  | Pin Name  | Function                                          | I/O  | D/A  | Rese | t State | Note          |

|------|-----------|---------------------------------------------------|------|------|------|---------|---------------|

| INU. | Fill Name | Function                                          | (*1) | (*2) | (*   | 3)      | NOLE          |

| 1    | VFB1      | DC/DC1 Output voltage feedback input              | I/O  | Α    |      |         |               |

| 2    | GNDP1     | GND for DC/DC1                                    | -    | G    |      |         |               |

| 3    | GNDP1_2   | GND for DC/DC1                                    | -    | G    |      |         |               |

| 4    | LX1       | DC/DC1 switch output                              | 0    | Α    |      |         |               |

| 5    | LX1_2     | DC/DC1 switch output                              | 0    | А    |      |         |               |

| 6    | VINP1     | Power supply for DC/DC                            | -    | Р    |      |         |               |

| 7    | VINP2     | Power supply for DC/DC2                           | -    | Р    |      |         |               |

| 8    | LX2       | DC/DC2 switch output                              | 0    | А    |      |         |               |

| 9    | LX2_2     | DC/DC2 switch output                              | 0    | Α    |      |         |               |

| 10   | GNDP2     | GND for DC/DC2                                    | -    | G    |      |         |               |

| 11   | GNDP2_2   | GND for DC/DC2                                    | -    | G    |      |         |               |

| 12   | VFB2      | DC/DC2 Output voltage feedback input              | I/O  | Α    |      |         |               |

| 13   | VOUT1     | LDO1 output                                       | 0    | Α    |      |         |               |

| 14   | VINL2     | Power supply for LDO1,2 and DCDC analog           | -    | Р    |      |         |               |

| 15   | VOUT2     | LDO2 output                                       | 0    | Α    |      |         |               |

| 16   | VOUT3     | LDO3 output                                       | 0    | Α    |      |         |               |

| 17   | VINL3     | Power supply for LDO3.4 and LDO5                  | -    | Р    |      |         |               |

| 18   | VOUT4     | LDO4 output                                       | 0    | Α    |      |         |               |

| 19   | VOUT5     | LDO5 output                                       | 0    | Α    |      |         |               |

| 20   | GND       | GND for Logic circuit, analog circuit, IO and etc | -    | G    |      |         |               |

| 21   | RESETO    | Host Reset output                                 | 0    | D    | 0    | Low     | NOD           |

| 22   | INTB      | Interrupt request output                          | 0    | D    | 0    | Hi-z    | NOD           |

| 23   | GPIO3     | General purpose I/O Note*                         | 1/0  | D    | *4   | *4      | *4            |

| 24   | PWRON     | External power on signal input                    | 1    | D    | 1    | -       | 1.4V to VINL1 |

| 25   | SLEEP     | Stand-by mode control signal input                | 1    | D    | 1    | -       | 1.4V to VINL1 |

| 26   | VFB3      | DC/DC3 Output voltage feedback input              | I/O  | A    |      |         |               |

| 27   | GNDP3     | GND for DC/DC3                                    | -    | G    |      |         |               |

| 28   | LX3       | DC/DC3 switch output                              | 0    | A    |      |         |               |

| 29   | LX3_2     | DC/DC3 switch output                              | 0    | A    |      |         |               |

| 30   | VINP3     | Power supply for DC/DC3                           | -    | P    |      |         |               |

| 31   | VINP4     | Power supply for DC/DC4                           | -    | P    |      |         |               |

| 32   | LX4       | DC/DC4 switch output                              | 0    | A    |      |         |               |

| 33   | LX4 2     | DC/DC4 switch output                              | 0    | A    |      |         |               |

| 34   | GNDP4     | GND for DC/DC4                                    |      | G    |      |         |               |

| 35   | VFB4      | DC/DC4 Output voltage feedback input              | I/O  | A    |      |         |               |

| 36   | DETVSB    | Voltage detection VSB output (Nch-opendrain)      | 0    | D    | 0    | -       | NOD           |

| 37   | VINL1     | Power supply for LDORTC1,2, VREF, DET, IO and etc | -    | P    |      |         | NOD           |

| 38   | VINET     | LDORTC1 output                                    | 0    | A    |      |         |               |

| 39   | -         | General purpose I/O Note*                         | 1/0  | D    | *4   | *4      | *4            |

| 40   | VREF      | Bypass capacitor connecting pin                   | 0    | A    | 4    |         | 4             |

| 40   | VOUTD     | Capacitor connection for built-in Regulator       | 0    | A    |      |         |               |

| 41   | GND       | GND for Logic circuit,analog circuit, IO and etc  | -    | G    |      |         |               |

| 42   | GND       |                                                   | -    | G    |      |         |               |

| 43   | GPIO0     | General purpose I/O Note*                         | I/O  | D    | *4   | *4      | *4            |

| 44   | GPIO1     | General purpose I/O Note*                         | I/O  | D    | *4   | *4      | *4            |

| 45   | VDDIO     | Power supply for CPU IF                           | -    | Р    |      |         |               |

| 46   | SDA       | I2C-Bus Data input/Output                         | I/O  | D    | I    | -       | Schmitt,NOD   |

| 47   | SCL       | I2C-Bus Clock input                               | 1    | D    | Ι    | -       | CMOS          |

| 48   | TESTEN    | For TEST (Connect to GND)                         | 1    | D    |      | PD      | CMOS Schmitt  |

Note\*1: I:Input, O:Output

Note\*2: A:Analog, D:Digital, P:Power, G:Ground

Note\*3: Reset State: RESETO=Low.

Note\*4: GP00-GP03: "Input" or "Output" is selectable by OTP. Input/Output type (CMOS or NMOS or Analog or Nch Open Drain Output) is selectable by OTP. Refer to the chapter of GPIO for detail.

#### Table 6-1 Pin Description

# 7. Power Control

This PMU has the power-on/off sequence that can be flexibly set by OTP. The default on/off, timing, and voltage of DCDCx and LDOx are programmable. In addition, GPIO0-GPIO3 pins output the power-on/off signal to external LDO/DCDC by the setting of OTP.

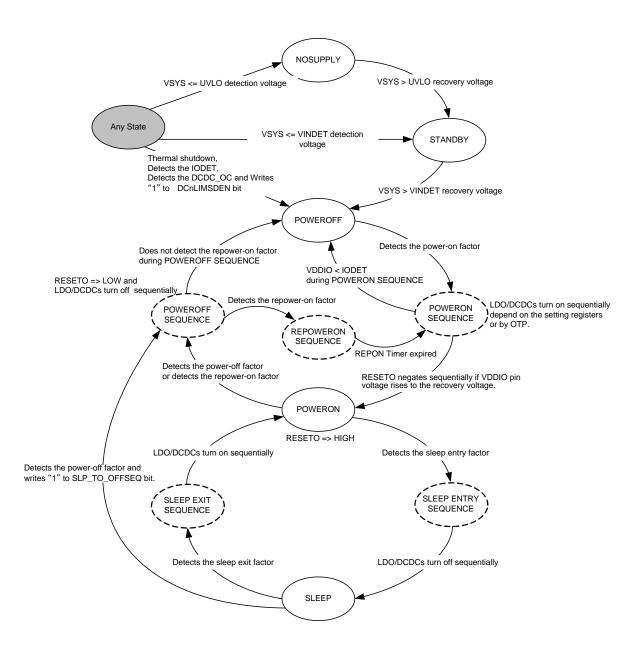

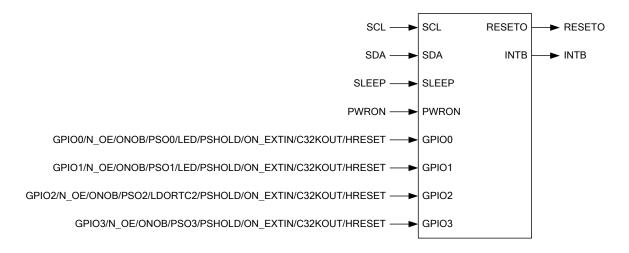

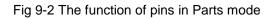

# 7.1 State Machine Diagram

# 7.2 State Machine Description

The state machine will step through the following statuses:

#### NOSUPPLY

The power supply to VSYS falls below the UVLO detection voltage.

#### **STANDBY**

The power supply to VSYS rises above the UVLO recovery voltage, followed by LDORTC1 turns on.

#### POWEROFF

The power supply to VSYS rises above the VINDET recovery voltage.

This PMU is always monitoring the power-on factor, and if the factor is detected, it will start the power-on sequence.

#### **POWERON SEQUENCE**

LDO/DCDCs turn on sequentially according to a pre-programmed order by OTP. And RESETO will be pulled up high sequentially if VDDIO pin voltage rises to the recovery voltage. Even if VDDIO pin voltage falls below the IODET detection voltage during POWERON SEQUENCE state, it will change to POWEROFF state.

#### POWERON

RESETO is pulled up high. CPU can control this PMU through some control pins or I2C Interface. In this state, this PMU is always monitoring the power-off or the repower-on factors.

#### POWEROFF SEQUENCE

This PMU will change to this state by detecting the power-off factor in POWERON state. In this state, RESETO pin is output low level and all LDO/DCDCs turn off sequentially in reverse order of power-on sequence.

#### **REPOWERON SEQUENCE**

This PMU will change to this state by detecting the repower-on factor. RESETO pin is output low level, and all LDO/DCDCs turn off sequentially in reverse order of power-on sequence. After turnoff is completed, repower-on timer starts, and it will change to POWERON SEQUENCE state when repower-on timer expired.

#### **SLEEP ENTRY / EXIT SEQUENCE**

This PMU will change to this state by detecting the deep sleep entry/exit factor. LDO/DCDCs turn off/on sequentially and enter or exit SLEEP. Refer to SLEEP ENTRY / EXIT SEQUENCE section.

#### <u>SLEEP</u>

This PMU will change to this state through SLEEP ENTRY SEQUENCE. In this state, it operates the low power consumption.

#### **Shutdown**

If this PMU detects conditions shown below, this PMU will change to NOSUPPLY state or STANDBY state or POWEROFF state regardless of the current state

- Low input voltage under the UVLO detection voltage

- Low input voltage under the VINDET detection voltage

- Low input voltage under the IODET detection voltage

(Shutdown operation is disabled during POWERON/OFF and REPOWERON SEQUENCE.)

- Abnormal temperature

- Over current of DCDCx

(Shutdown operation is disabled during POWERON/OFF SEQUENCE.)

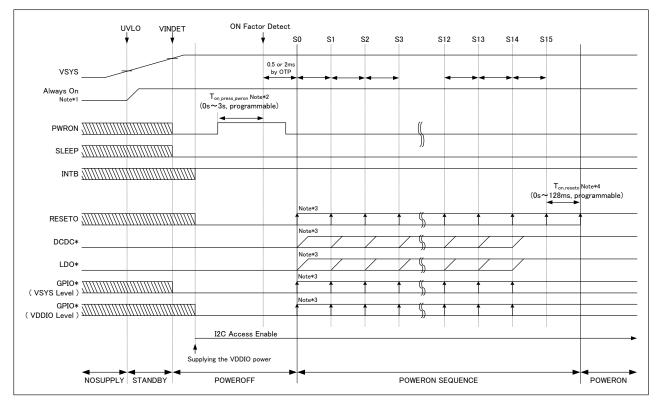

# 7.3 Power On Sequence

This PMU's power is turned on by detecting the power-on factor at the POWEROFF state. The default settings of the resources as shown below are programmable. The slot duration can be selected in 0.5ms and 2ms by OTP.

[Controllable resources] DCDC1-4, LDO1-5, RESETO, PSO0-3(GPIO0-3)

[Power-on factor]

PWRON: ON EXTIN(GPIO\*): High level input more than certain time to PWRON pin. High input to ON\_EXTIN pin.

Note : This PMU powers on/off according to the on/off sequence. The interrupt is output when these pins are asserted. The power-on/off history is stored by the history register.

Note\*1: Always On is VREF/REGD. Only LDORTC2 default on/off is programmable by OTP.

LDORTC1 power-on timing is programmable either always-on or power-on sequence on by OTP.

Note\*2: Initial values of register can be configured by OTP. (0sec/100us/20ms/128ms/1sec/2sec/3sec)

Note\*3: DCDCx/LDOx/GPIOx power-on timing is programmable by OTP. (S0 to S14)

RESETO release timing is programmable by OTP. (S0 to S15)

Selected slot of DCDCx/LDOx/GPIOx must be set before RESETO release slot.

Note\*4: RESETO has extra time (0sec/32ms/64ms/128ms) by OTP when it is programmed S15.

Note\*: PWRON polarity is programmable by OTP.

Fig 7-2 Power-on Sequence

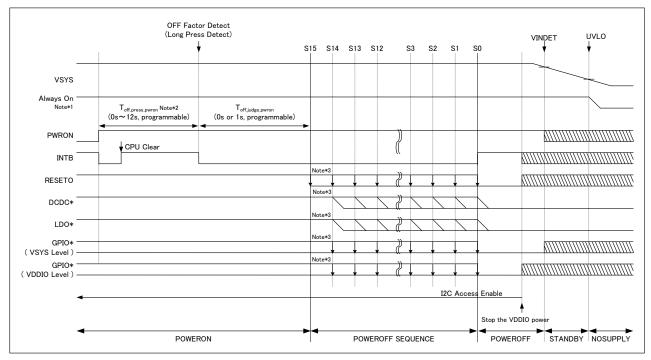

# 7.4 Power Off Sequence

This PMU's power is turn off by detecting the power-off factor at the POWERON or SLEEP state.

#### [Power-off factor]

| Long power on key press:        | High level input more than certain time to PWRON pin. |

|---------------------------------|-------------------------------------------------------|

| Watchdog timer:                 | The internal watchdog timer expires.                  |

| <swpwroff> register:</swpwroff> | The CPU writes a dedicated register.                  |

| N_OE(GPIO*):                    | High level input more than certain time to N_OE pin.  |

| PSHOLD(GPIO*):                  | Low input to PSHOLD pin.                              |

Note\*1: Always On is VREF/REGD. Only LDORTC2 default on/off is programmable by OTP.

LDORTC1 power-on timing is programmable either always-on or power-on sequence on by OTP.

Note\*2: This value can be selected by register. (0sec/1sec/2sec/4sec/6sec/8sec/10sec/12sec)

Note\*3: The power-off timing reverse order of the power-on sequence.

Selected slot of DCDCx/LDOx/GPIOx must set after RESETO assert slot.

Fig 7-3 Power-off Sequence

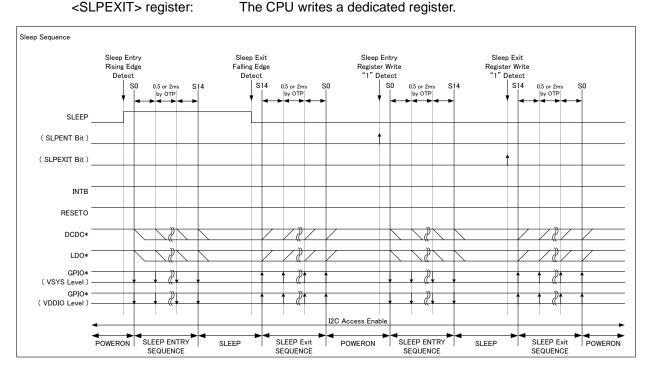

# 7.5 Sleep Entry/Exit Sequence

This PMU is changed to the SLEEP state by detecting the sleep-entry factor at the PWRON and PWRON SEQUENCE state.

The state change timing of some resources as shown below is programmable.

[Controllable resources]

| Active/Sleep Control:   | DCDC1-4, LDO1-5, PSO0-3(GPIO0-3) |

|-------------------------|----------------------------------|

| Output Voltage Control: | DCDC1-4, LDO1-5                  |

And, this PMU is changed to the PWRON state by detecting the Sleep-exit factor at the SLEEP state. The state change timing of some resources is performed in reverse order of the sleep-entry sequence.

[Sleep-entry factor]

SLEEP:

High input to SLEEP pin. The CPU writes a dedicated register.

[Sleep-exit factor]

SLEEP:

Low input to SLEEP pin. The CPU writes a dedicated register.

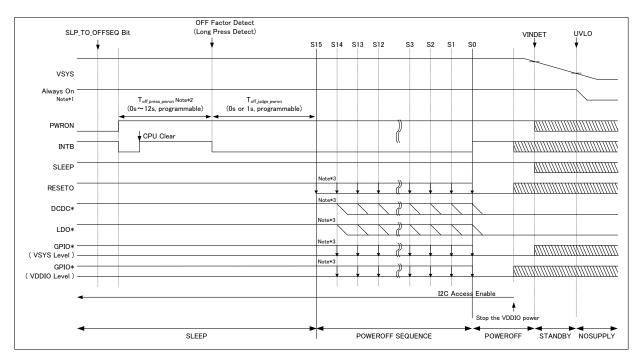

Fig 7-4 Sleep Entry/Exit Sequence

This PMU is changed to the PWROFF SEQUENCE state by detecting PWRON long press at the SLEEP state. It is necessary to write the <SLP\_TO\_OFFSEQ> register in advance.

The state change timing of some resources is performed in reverse order of the power-on sequence.

Note\*1: Always On is VREF/REGD. Only LDORTC2 default on/off is programmable by OTP.

LDORTC1 power-on timing is programmable either always-on or power-on sequence on by OTP.

Note\*2: This value can be selected by register. (0sec/1sec/2sec/4sec/6sec/8sec/10sec/12sec)

Note\*3: The power-off timing is in reverse order of the power-on sequence.

Fig 7-5 Sleep to Power-off Sequence

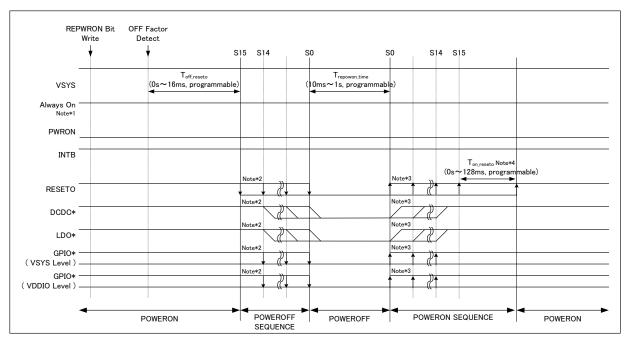

# 7.6 Repower-on Sequence

Once the repower-on factor is detected, this PMU executes the power-on sequence after executing the power-off sequence without the power-on factor.

This PMU does not change to POWERON state, when VDDIO pin voltage falls below the IODET detection voltage or repower-on timer is not expired. repower-on timer is selectable 10ms-1s. It is the waiting time for the all regulator's output capacitor to discharge.

[Repower-on factor]

```

Long power on key press:

Watchdog timer:

<SWPWROFF> register:

N_OE(GPIO*):

HRESET(GPIO*):

```

High level input more than certain time to PWRON pin. The internal watchdog timer expires. The CPU writes a dedicated register. High level input more than certain time to N\_OE pin. High level input to HRESET pin. After power off by detecting HRESET, this PMU repower-on regardless of setting value of REPWRON bit.

The state transition time from finishing the repower-on sequence to POWERON SEQUENCE state can be controlled by repower-on timer.

Note\*1: Always On is VREF/REGD. Only LDORTC2 default on/off is programmable by OTP.

LDORTC1 power-on timing is programmable either always-on or power-on sequence on by OTP.

Note\*2: The power-off timing reverse order of the power-on sequence.

Note\*3: DCDCx/LDOx/GPIOx power-on timing is programmable by OTP(S0 to S14).

Note\*4: RESETO has extra time (0/32/64/128ms) by OTP when it is programmed S15.

Fig 7-6 Repower-on Sequence

# 7.7 Shutdown Factor

The following factors trigger a shutdown, and each state is transited to NOSUPPLY State/STANDBY State/ POWEROFF State.

The transition to POWERON State is enabled when each recovery condition for each shutdown factor is met.

|   | Shutdown Factor                         | State of<br>Transition | Recovery Condition from Shutdown |

|---|-----------------------------------------|------------------------|----------------------------------|

| 1 | UVLO detection                          | NOSUPPLY               | UVLO release                     |

| 2 | VINDET detection                        | STANDBY                | VINDET release                   |

| 3 | Temperature's abnormal detection        | POWEROFF               | Temperature's normal detection   |

| 4 | DCDCx current limit detection<br>Note*1 | POWEROFF               | DCDCx current normal detection   |

| 5 | IODET(VDDIO monitor) detection*2        | POWEROFF               | IODET release                    |

Note\*1: This PMU shuts down if over-current continues for 2ms.

Shutdown operation is disabled during POWERON/OFF SEQUENCE.

Note\*2: Shutdown operation is disabled during POWERON/OFF SEQUENCE, REPOWERON SEQUENCE.

Table 7-1 Shutdown Factor & Recovery Condition

# 7.8 Shutdown Sequence

This PMU is forcibly powered off when the shutdown factor is detected. All LDO/DCDCs are turned off at once. Until the shutdown condition is recovered, this PMU does not accept the power-on factors. For the reset condition of register, refer to the register map.

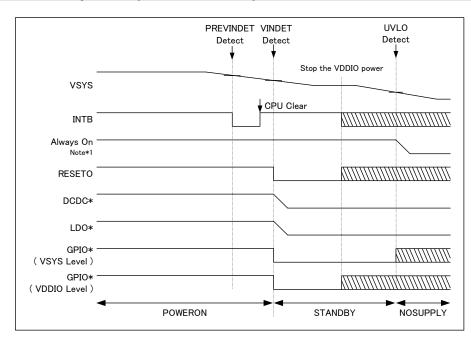

# 7.8.1 Shutdown Sequence (VINDET, UVLO)

Note\*1: Always On is VREF/REGD. Only LDORTC2 default on/off is programmable by OTP.

LDORTC1 power-on timing is programmable either always-on or power-on sequence on by OTP.

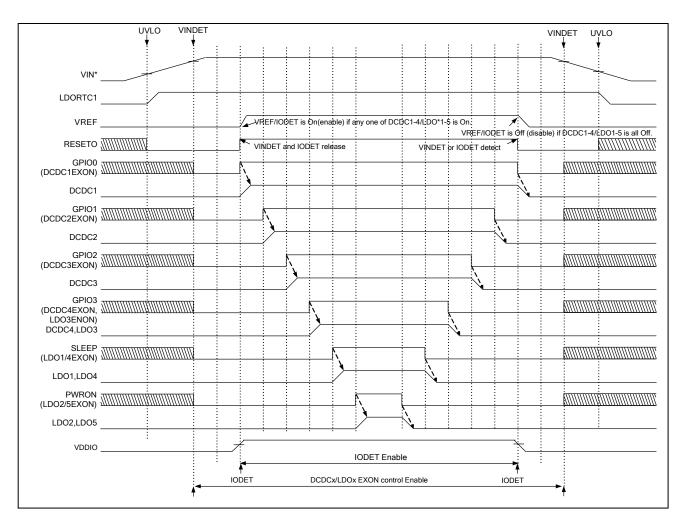

Fig 7-7 Shutdown Sequence (VINDET, UVLO detection)

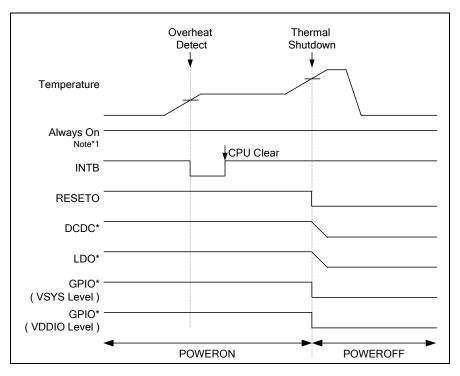

# 7.8.2 Shutdown Sequence (Abnormal temperature)

Note\*1: Always On is VREF/REGD. Only LDORTC2 default on/off is programmable by OTP.

LDORTC1 power-on timing is programmable either always-on or power-on sequence on by OTP.

Fig 7-8 Shutdown Sequence (Abnormal temperature)

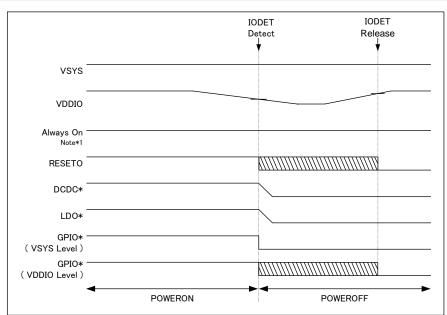

# 7.8.3 Shutdown Sequence (IODET)

Note\*1: Always On is VREF/REGD. Only LDORTC2 default on/off is programmable by OTP.

LDORTC1 power-on timing is programmable either always-on or power-on sequence on by OTP. Note\*2:IODET is invalid when VDDIO is not selected as the power supply of both GPIO0 and GPIO1. Fig 7-9 Shutdown Sequence (IODET)

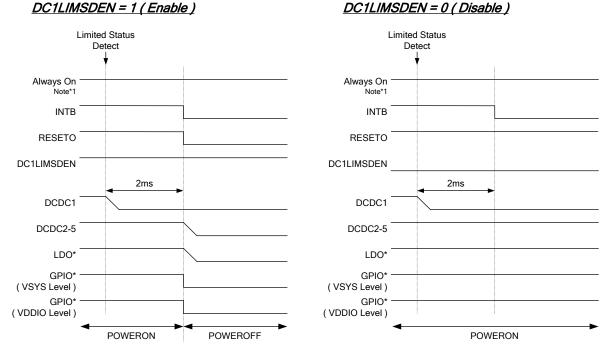

# 7.8.4 Shutdown Sequence (DCDCx current limit detection)

Note\*1: Always On is VREF/REGD. Only LDORTC2 default on/off is programmable by OTP.

LDORTC1 power-on timing is programmable either always-on or power-on sequence on by OTP.

Fig 7-10 Shutdown Sequence (DCDC1 current limit detection)

# 7.9 Power-on/off History

This PMU has the register which monitors the power-on/off factor. After this PMU powers on, CPU can recognize the power-on factor and power-off factor by reading PONHIS register and POFFHIS register.

The power-on factors as below are stored when the power-on sequence starts.

PWRON / ON\_EXTIN(GPIO\*) / HRESET(GPIO\*)

The power-off /repower-on factors stored when the power-off sequence starts.

Long power on key press / Watchdog / SWPWROFF / N\_OE(GPIO\*) / PSHOLD(GPIO\*) / HRESET(GPIO\*)

The shutdown factors as below are stored immediately before the power-off.

TSHUT / VINDET / IODET / DCDC current limit

The repower-on factors as below are stored when the power-off sequence is finished

Repower-on

# 7.10 Watchdog Timer Function

This PMU integrates a watchdog timer in order to power off the system when the CPU becomes hung-up. If the CPU does not access the WATCHDOG register until the watchdog timer expired, this PMU output interrupt. And then if the CPU does not clear the interrupt within 1sec, this PMU is transition to POWEROFF SEQUENCE.

A watchdog timer expiring time is programmable from 1 to 128 seconds with a default value of 128 seconds by dedicated register.

# 7.11 Power Control Block Interrupt Request

Power control block provides the interrupt requests to INTC block by the following pin input change or the transition state detection:

- PWRON pin input

- •Outputs the interrupt when PWRON pin input signal changes (See next section). Selectable both-edge/level interrupt type (Default level).

- •Outputs 2nd interrupt after PWRON pin input signal changes (See next section). The interrupt is falling-edge type. If it is not cleared, this PMU powers off.

- Abnormal temperature detection

- •Outputs the interrupt when overheat detection circuit detects the abnormal temperature. Selectable both-edge/level interrupt type (Default level).

- Watchdog timer overflow

- •Outputs the interrupt when the watchdog timer expires.

- PREVINDET (Pre detection)

- •Outputs the interrupt when PREVINDET detects the pre detection voltage. Selectable both-edge/level interrupt type (Default level).

The initial state of all the interrupt request signals from power control block is disabled.

It is necessary to set the interrupt enable bit of each interrupt factor if the interrupt request output to INTC block is permitted. Even if the interrupt output is disabled, CPU can read the each interrupt factor by PWRIRQ register.

For the details of interrupt, refer to the interrupt controller (INTC).

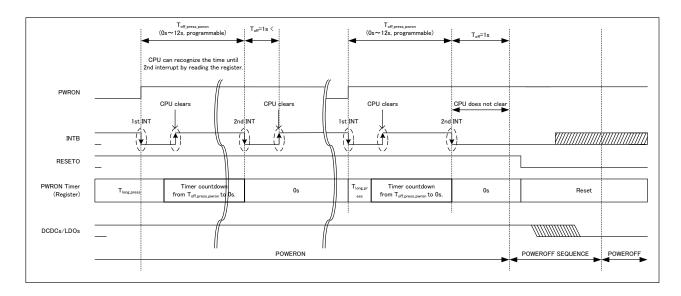

# 7.12 PWRON Long Press Operation

This PMU can output two interrupts by changing the PWRON pin input signal during POWERON state. If CPU does not clear the 2nd interrupt, this PMU changes to the POWEROFF state. For other detailed operations, refer to the appendix.

# 7.13 Power-on Signal Output by GPIO0-3

This PMU can output the power-on signal from GPIO0-3 pin. This function is selected by OTP. The signals output by GPIO0-3 are asserted sequentially according to a pre-programmed order by OTP. For example, these signals are used for operating external regulators. On SLEEP Entry/Exit sequence, these signals are programmable by the register.

# 7.14 Voltage Detector

#### UVLO

| Symbol               | Parameter              | Condition             | MIN  | TYP  | MAX  | Unit |

|----------------------|------------------------|-----------------------|------|------|------|------|

| V <sub>Release</sub> | UVLO Threshold Voltage | VINL1 Voltage Rising  |      | 2.30 |      | V    |

| V <sub>Detect</sub>  | UVLO Threshold Voltage | VINL1 Voltage Falling | -10% | 2.20 | +10% | V    |

| V <sub>Hys</sub>     | UVLO Hysteresis        |                       |      | 100  |      | mV   |

• VINL1 < V<sub>Detect</sub> : Transition to NOSUPPLY state.

#### VINDET

| Symbol               | Parameter                | Condition             | MIN | TYP  | MAX | Unit |

|----------------------|--------------------------|-----------------------|-----|------|-----|------|

| V <sub>Release</sub> | VINDET Threshold Voltage | VINL1 Voltage Rising  |     | 2.90 |     | V    |

| V <sub>Detect</sub>  | VINDET Threshold Voltage | VINL1 Voltage Falling | -3% | 2.70 | +3% | V    |

| V <sub>Hys</sub>     | VINDET Hysteresis        |                       |     | 200  |     | mV   |

• VINL1 < V<sub>Detect</sub> : Transition to STANDBY state or NOSUPPLY state.

$\cdot\,V_{\text{Detect}}$  voltage is selected by OTP and register.

### PREVINDET

| Symbol               | Parameter                   | Condition             | MIN | TYP  | MAX | Unit |

|----------------------|-----------------------------|-----------------------|-----|------|-----|------|

| V <sub>Release</sub> | PREVINDET Threshold Voltage | VINL1 Voltage Rising  |     | 2.85 |     | V    |

| V <sub>Detect</sub>  | PREVINDET Threshold Voltage | VINL1 Voltage Falling | -3% | 2.80 | +3% | V    |

| V <sub>Hys</sub>     | PREVINDET Hysteresis        |                       |     | 50   |     | mV   |

• VINL1 < V<sub>Detect</sub> : Generate interrupt to INTB.

• V<sub>Detect</sub> voltage is selected by OTP and register.

### IODET

| Symbol               | Parameter               | Condition             | MIN | TYP  | MAX | Unit |

|----------------------|-------------------------|-----------------------|-----|------|-----|------|

| V <sub>Release</sub> | IODET Threshold Voltage | VDDIO Voltage Rising  |     | 1.65 |     | V    |

| VDetect              | IODET Threshold Voltage | VDDIO Voltage Falling | -3% | 1.60 | +3% | V    |

| V <sub>Hys</sub>     | IODET Hysteresis        |                       |     | 50   |     | mV   |

• V<sub>Detect</sub> voltage is selected by OTP and register.

#### POWER MANAGEMENT SYSTEM DEVICE

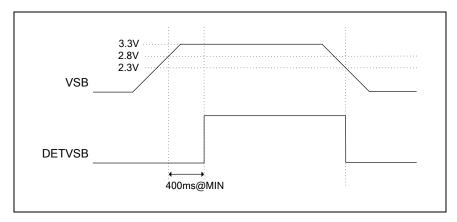

VSBDET

| v : |                      |                          |                     |      |     |      |      |  |  |  |

|-----|----------------------|--------------------------|---------------------|------|-----|------|------|--|--|--|

|     | Symbol               | Parameter                | Condition           | MIN  | TYP | MAX  | Unit |  |  |  |

|     | V <sub>Release</sub> | VSBDET Threshold Voltage | VSB Voltage Rising  |      | 2.8 |      | V    |  |  |  |

|     | V <sub>Detect</sub>  | VSBDET Threshold Voltage | VSB Voltage Falling | 2.13 | 2.3 | 2.47 | V    |  |  |  |

|     | V <sub>Hys</sub>     | VSBDET Hysteresis        |                     |      | 500 |      | mV   |  |  |  |

# After VSB output (LDORTC1) rises, DETVSB signal turns to "H" after 400ms from the detection voltage is detected. DETVSB is Nch-opendrain output pin.

Fig 7-12 Voltage Detection timing

# 7.15 Overheat Detection Block

#### Overheat Detection

| Symbol               | Parameter             | Condition | MIN | TYP                      | MAX | Unit      |

|----------------------|-----------------------|-----------|-----|--------------------------|-----|-----------|

| T <sub>Detect</sub>  | Detection Temperature | -         | -   | 135<br>125<br>115<br>105 | -   | Degrees C |

| T <sub>Recover</sub> | Recover Temperature   | -         |     | T <sub>Detect</sub> -20  |     | Degrees C |

• Chip Temperature > T<sub>Detect</sub> : Generate interrupt to INTB.

•T<sub>Detect</sub> temperature is selected by OTP and register.

#### Thermal Shutdown

| Symbol               | Parameter             | Condition | MIN | TYP | MAX | Unit      |

|----------------------|-----------------------|-----------|-----|-----|-----|-----------|

| T <sub>Detect</sub>  | Detection Temperature | -         | -   | 140 | -   | Degrees C |

| T <sub>Recover</sub> | Recover Temperature   | -         |     | 110 |     | Degrees C |

• Chip Temperature > T<sub>Detect</sub> : Transition to POWEROFF state.

# 8. Regulators

# 8.1 Regulators Table

| Symbol                 | DCDC1    | DCDC2    | DCDC3    | DCDC4    |

|------------------------|----------|----------|----------|----------|

| Initial Output Voltage | 0.6-3.5V | 0.6-3.5V | 0.6-3.5V | 0.6-3.5V |

| Maximum Output Current | 3000mA   | 3000mA   | 2000mA   | 2000mA   |

| External Inductor      | 1.0µH    | 1.0µH    | 1.0µH    | 1.0µH    |

| External Capacitor     | 22µF     | 22µF     | 22µF     | 22µF     |

| Output Control         | I2C      | I2C      | I2C      | I2C      |

Table 8-1 Regulator Table (DC/DC)

| Symbol                 | LDO1     | LDO2     | LDO3     | LDO4     |

|------------------------|----------|----------|----------|----------|

| Initial Output Voltage | 0.9-3.5V | 0.9-3.5V | 0.6-3.5V | 0.9-3.5V |

| Maximum Output Current | 300mA    | 300mA    | 300mA    | 200mA    |

| External Capacitor     | 1µF      | 1µF      | 1µF      | 1µF      |

| Output Control         | I2C      | I2C      | I2C      | I2C      |

| Symbol                 | LDO5     | LDORTC1       | LDORTC2       |  |

|------------------------|----------|---------------|---------------|--|

| Initial Output Voltage | 0.9-3.5V | 1.2-3.5V      | 0.9-3.5V      |  |

| Maximum Output Current | 200mA    | 30mA          | 10mA          |  |

| External Capacitor     | 1µF      | 1uF           | 1uF           |  |

| Output Control         | I2C      | Always-On/I2C | Always-On/I2C |  |

Table 8-2 Regulator Table (LDO)

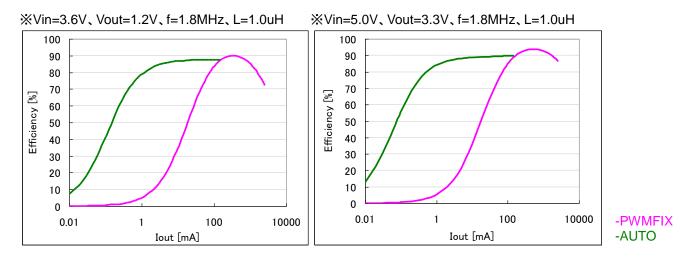

# 8.2 DCDC Electrical Characteristics

#### 8.2.1 DCDC1-2 Electrical Characteristics

| Operating Conditions (unless otherwise specified) –40 degrees C < Ta < 85 degrees C |                               |                                                                                                                                                                        |        |                |      |      |     |       |

|-------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|------|------|-----|-------|

| Symbol                                                                              | Parameter                     | Condi                                                                                                                                                                  | ition  |                | Min  | Тур  | Max | Units |

| Vin                                                                                 | Input voltage range           | -                                                                                                                                                                      |        |                | 2.7  | 3.6  | 5.5 | V     |

|                                                                                     | Output voltage range          | -                                                                                                                                                                      |        |                | 0.6  | 1.2  | 3.5 | V     |

| Vout                                                                                | Voltage setting step width    | -                                                                                                                                                                      |        |                |      | 12.5 |     | mV    |

| Vaccu                                                                               | Output voltage accuracy       | 1mA < $I_{OUT}$ < Iomax $V_{OUT}$ < 1.0VAuto/PSM/PWM Mode $1.0 \leq V_{OUT}$                                                                                           |        | -20            | 0    | 20   | mV  |       |

| vaccu                                                                               | Output voltage accuracy       |                                                                                                                                                                        |        | -2             | 0    | 2    | %   |       |

| Vrip                                                                                | Output ripple voltage         | Auto Mode I                                                                                                                                                            | lout=1 | mA             |      | 25   |     | mV    |

| vnp                                                                                 |                               | PWM N                                                                                                                                                                  | Mode   |                | -10  |      | 10  | mV    |

| Fosc                                                                                | Switching frequency           | PWM Mode                                                                                                                                                               |        |                |      | 1.8  |     | MHz   |

|                                                                                     |                               | Auto/PWM Mode<br>V <sub>OUT</sub> < 3.5V, V <sub>IN</sub> = V <sub>OUT</sub> +1V<br>Auto/PWM Mode<br>V <sub>OUT</sub> < 2.4V, V <sub>IN</sub> = V <sub>OUT</sub> +1.1V |        | 1000           |      |      | mA  |       |

| lout_max                                                                            | Maximum output current        |                                                                                                                                                                        |        | 2000           |      |      | mA  |       |

|                                                                                     |                               | Auto/PWM Mode<br>Vout < 1.5V, Vin > 2.8V                                                                                                                               |        | 3000           |      |      | mA  |       |

|                                                                                     |                               | PSM N                                                                                                                                                                  | Mode   |                | 10   |      |     | mA    |

| llim1                                                                               | Limit current                 |                                                                                                                                                                        |        |                | 3200 |      |     | mA    |

| Vpeak                                                                               | Output transition<br>response | 10→400mA@<br>Vin=3.6V,V                                                                                                                                                | -      |                |      |      | 5   | %     |

|                                                                                     |                               | Auto Mode                                                                                                                                                              | Ιοι    | лт <b>=0mA</b> |      | 45   |     | μA    |

| lss                                                                                 | Consumption current           | PSM Mode I <sub>OUT</sub> =0mA                                                                                                                                         |        |                | 25   |      | μA  |       |

| Cin                                                                                 | Input Capacitor               |                                                                                                                                                                        |        |                |      | 10   |     | μF    |

| Cout                                                                                | Output Capacitor              | Output Ca                                                                                                                                                              | apacit | or             |      | 22   |     | μF    |

| L                                                                                   | External Inductor             |                                                                                                                                                                        |        |                |      | 1.0  |     | μH    |

Operating Conditions (unless otherwise specified) –40 degrees C < Ta < 85 degrees C

# Table 8-3 DCDC1-2 Electrical Characteristic

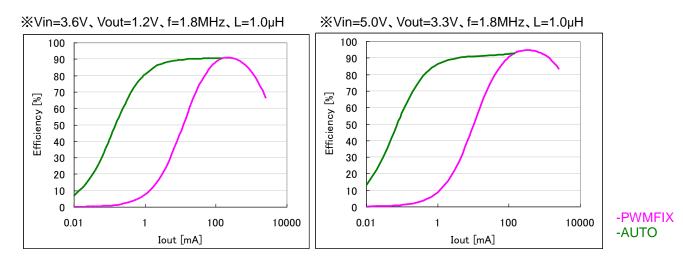

#### 8.2.2 DCDC3-4 Electrical Characteristics

| Symbol               | Parameter                     | Condi                                       | Ŭ      |                | Min  | Тур  | Max | Units |

|----------------------|-------------------------------|---------------------------------------------|--------|----------------|------|------|-----|-------|

| VIN                  | Input voltage range           | -                                           |        | 2.7            | 3.6  | 5.5  | V   |       |

| Output voltage range |                               | -                                           |        |                | 0.6  | 1.2  | 3.5 | V     |

| Vout                 | Voltage setting step width    | -                                           | -      |                |      | 12.5 |     | mV    |

| Vaccu                | Output voltage accuracy       | 1mA < lout < lom                            | ax     | Vout<1.0V      | -20  | 0    | 20  | mV    |

| Vaccu                | Output voltage accuracy       | Auto/PSM/PWM M                              | lode   | 1.0≦Vou⊤       | -2   | 0    | 2   | %     |

| Varia                |                               | Auto Mode I                                 | lout=1 | mA             |      | 25   |     | mV    |

| Vrip                 | Output ripple voltage         | PWM                                         | Mode   |                | -10  |      | 10  | mV    |

| Fosc                 | Switching frequency           | PWM Mode                                    |        |                | 1.8  |      | MHz |       |

|                      |                               | Auto/PWN<br>V <sub>OUT</sub> < 3.5V, V      |        |                | 500  |      |     | mA    |

| lout_max             | Maximum output current        | Auto/PWM Mode<br>Vout < 3.1, VIN= Vout+1.1V |        | 1000           |      |      | mA  |       |

|                      |                               | Auto/PWN<br>Vo∪⊤ < 1.5V,                    |        |                | 2000 |      |     | mA    |

|                      |                               | PSM N                                       | Mode   |                | 10   |      |     | mA    |

| llim1                | Limit current                 |                                             |        |                | 2300 |      |     | mA    |

| Vpeak                | Output transition<br>response | 10→400mA@ΔT=1.0μs,<br>Vin=3.6V,Vou⊤ =1.2V   |        |                |      | 5    | %   |       |

| 1                    | Consumption current           | Auto Mode                                   | Ιοι    | лт <b>=0mA</b> |      | 45   |     | μA    |

| lss                  |                               | PSM Mode                                    | lou    | лт <b>=0mA</b> |      | 25   |     | μA    |

| Cin                  | Input Capacitor               |                                             |        |                | 10   |      | μF  |       |

| Cout                 | Output Capacitor              | Output Capacitor                            |        | or             |      | 22   |     | μF    |

| L                    | External Inductor             |                                             |        |                |      | 1.0  |     | μH    |

Operating Conditions (unless otherwise specified) -40 degrees C < Ta < 85 degrees C

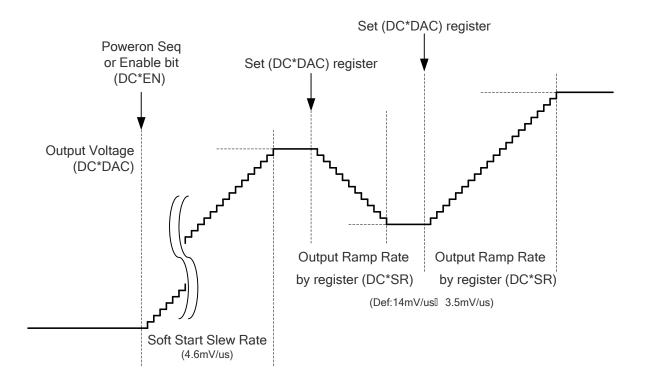

### 8.2.3 RAMP Control Operation

This function starts by setting DC\*DAC register. The ramp rate is controllable by DC\*SR bit.

Fig 8-1 Ramp up/down Control Timing Chart

# 8.3 LDO Electrical Characteristics

# 8.3.1 LDO1-2 Electrical Characteristics

Operating Conditions (unless otherwise specified) Vin=3.6V, Cout= $1.0\mu$ F, Ta = 25 degrees C

| Symbol             | Parameter                     | Condition                                                                             | Min  | Тур | Max | Units |

|--------------------|-------------------------------|---------------------------------------------------------------------------------------|------|-----|-----|-------|

| Vin                | Input Voltage Range           | -                                                                                     | 2.7  | 3.6 | 5.5 | V     |

| Vout               | Output Voltage<br>Range       | 50µA <iout<ioutmax< td=""><td>0.9</td><td></td><td>3.5</td><td>V</td></iout<ioutmax<> | 0.9  |     | 3.5 | V     |

| VOUT               | Voltage setting step<br>width |                                                                                       |      | 50  |     | mV    |

| Vaccu              | Output Voltage<br>Accuracy    | V <sub>OUT</sub> =all output range<br>Iout=1mA                                        | -1.5 |     | 1.5 | %     |

| IOUTMAX            | Output Current                | -                                                                                     |      |     | 300 | mA    |

| I <sub>LIM</sub>   | Limit Current                 |                                                                                       | 350  |     |     | mA    |

| Vdiff              | Dropout Voltage               | Vout setting = VIN, IOUT= IOUTMAX                                                     |      |     | 0.2 | V     |

| Vline              | Line Regulation               | 2.7 <vin<5.5v,<br>I<sub>OUT</sub>=1mA</vin<5.5v,<br>                                  |      |     | 0.2 | %/V   |

| Vload              | Load Regulation               | 100uA < lout < loutmax                                                                |      |     | 30  | mV    |

| Vtr                | Transient Response            | IOUT=100uA <> IOUTMAX / 2                                                             |      | 10  |     | mV    |

| RR                 | Ripple Rejection              | f=217~1kHz, Iout= Ioutmax / 2<br>Vdiff>0.6V                                           |      | 70  |     | dB    |

| O <sub>Noise</sub> | Output Noise                  | Iouт= Iouтмах / 2<br>BW=10Hz-100kHz, Vout=1.2V                                        |      | 25  |     | uVrms |

| Iss                | Supply Current                | Iout=0mA                                                                              |      | 100 |     | μA    |

| IOFF               | Standby current               | Iout=0mA                                                                              |      |     | 1   | μA    |

| Tr                 | Rising time                   | Vout × 0.9, Iout=0mA                                                                  |      |     | 500 | us    |

| Tf                 | Falling time                  | Vout × 0.1, Iout=0mA                                                                  |      |     | 500 | us    |

| Cout               | Output Capacitor              |                                                                                       |      | 1.0 |     | μF    |

Table 8-5 LDO1-2 Electrical Characteristic

### 8.3.2 LDO3 Electrical Characteristics

| Symbol             | Parameter                     | Condition                                                                             | Min  | Тур | Max | Units |

|--------------------|-------------------------------|---------------------------------------------------------------------------------------|------|-----|-----|-------|

| VIN                | Input Voltage Range           | -                                                                                     | 1.7  | 3.6 | 5.5 | V     |

| Vout               | Output Voltage<br>Range       | 50µA <iout<ioutmax< td=""><td>0.6</td><td></td><td>3.5</td><td>V</td></iout<ioutmax<> | 0.6  |     | 3.5 | V     |

|                    | Voltage setting step<br>width |                                                                                       |      | 50  |     | mV    |

| Vaccu              | Output Voltage<br>Accuracy    | Vout=all output range<br>Iout=1mA                                                     | -1.5 |     | 1.5 | %     |

| IOUTMAX            | Output Current                | -                                                                                     |      |     | 300 | mA    |

| I <sub>LIM</sub>   | Limit Current                 |                                                                                       | 350  |     |     | mA    |

| Vdiff              | Dropout Voltage               | Vout setting = $V_{IN}$ , $I_{OUT}$ = $I_{OUTMAX}$                                    |      |     | 0.3 | V     |

| Vline              | Line Regulation               | 1.7 <vin<5.5v,<br>I₀u⊤=1mA</vin<5.5v,<br>                                             |      |     | 0.2 | %/V   |

| Vload              | Load Regulation               | 100uA < lout < loutmax                                                                |      |     | 30  | mV    |

| Vtr                | Transient Response            | IOUT=100uA <> IOUTMAX / 2                                                             |      | 40  |     | mV    |

| RR                 | Ripple Rejection              | f=217~1kHz, Iout= Ioutmax / 2<br>Vdiff>0.6V                                           |      | 60  |     | dB    |

| O <sub>Noise</sub> | Output Noise                  | Iout= Ioutmax / 2<br>BW=10Hz-100kHz<br>Vout=1.2V                                      |      | 60  |     | uVrms |

| lss                | Supply Current                | Iout=0mA                                                                              |      | 20  |     | μA    |

| IOFF               | Standby current               | Iout=0mA                                                                              |      |     | 1   | μA    |

| Tr                 | Rising time                   | Vout × 0.9, Iout=0mA                                                                  |      |     | 500 | us    |

| T <sub>f</sub>     | Falling time                  | V <sub>OUT</sub> × 0.1, I <sub>OUT=</sub> 0mA                                         |      |     | 500 | us    |

| Cout               | Output Capacitor              |                                                                                       |      | 1.0 |     | μF    |

Operating Conditions (unless otherwise specified) Vin=3.6V, Cout=1.0µF, Ta = 25 degrees C

Table 8-6 LDO3 Electrical Characteristic

### 8.3.3 LDO4-5 Electrical Characteristics

| Symbol             | Parameter                     | Condition                                                                             | Min  | Тур | Max | Units |

|--------------------|-------------------------------|---------------------------------------------------------------------------------------|------|-----|-----|-------|

| Vin                | Input Voltage Range           | -                                                                                     | 1.7  | 3.6 | 5.5 | V     |

| Vout               | Output Voltage<br>Range       | 50µA <iout<ioutmax< td=""><td>0.9</td><td></td><td>3.5</td><td>V</td></iout<ioutmax<> | 0.9  |     | 3.5 | V     |

|                    | Voltage setting step<br>width |                                                                                       |      | 50  |     | mV    |

| Vaccu              | Output Voltage<br>Accuracy    | Vout=all output range<br>Iout=1mA                                                     | -1.5 |     | 1.5 | %     |

| IOUTMAX            | Output Current                | -                                                                                     |      |     | 200 | mA    |

| I <sub>LIM</sub>   | Limit Current                 |                                                                                       | 250  |     |     | mA    |

| Vdiff              | Dropout Voltage               | Vout setting = $V_{IN}$ , $I_{OUT}$ = $I_{OUTMAX}$                                    |      |     | 0.4 | V     |

| Vline              | Line Regulation               | 2.7 <vin<5.5v,<br>I<sub>OUT</sub>=1mA</vin<5.5v,<br>                                  |      |     | 0.2 | %/V   |

| Vload              | Load Regulation               | 100uA < lout < loutmax                                                                |      |     | 30  | mV    |

| Vtr                | Transient Response            | IOUT=100uA <> IOUTMAX / 2                                                             |      | 40  |     | mV    |

| RR                 | Ripple Rejection              | f=217~1kHz, Iout= Ioutmax / 2<br>Vdiff>0.6V                                           |      | 60  |     | dB    |

| O <sub>Noise</sub> | Output Noise                  | Iout= Ioutmax / 2<br>BW=10Hz-100kHz<br>Vout=1.2V                                      |      | 50  |     | uVrms |

| lss                | Supply Current                | Iout=0mA                                                                              |      | 20  |     | μA    |

| IOFF               | Standby current               | Iout=0mA                                                                              |      |     | 1   | μA    |

| Tr                 | Rising time                   | Vout × 0.9, Iout=0mA                                                                  |      |     | 500 | us    |

| T <sub>f</sub>     | Falling time                  | V <sub>OUT</sub> × 0.1, I <sub>OUT=</sub> 0mA                                         |      |     | 500 | us    |

| Cout               | Output Capacitor              |                                                                                       |      | 1.0 |     | μF    |

Operating Conditions (unless otherwise specified) Vin=3.6V, Cout=1.0µF, Ta = 25 degrees C

Table 8-7 LDO4-5 Electrical Characteristic

#### 8.3.4 LDORTC1 Electrical Characteristics

| Symbol               | Parameter                     | Condition                                                                             | Min  | Тур | Max | Units |

|----------------------|-------------------------------|---------------------------------------------------------------------------------------|------|-----|-----|-------|

| VIN                  | Input Voltage Range           | -                                                                                     | 2.2  | 3.6 | 5.5 | V     |

|                      | Output Voltage<br>Range       | 50µA <iout<ioutmax< td=""><td>1.2</td><td></td><td>3.5</td><td>V</td></iout<ioutmax<> | 1.2  |     | 3.5 | V     |

| Vout                 | Voltage setting step<br>width |                                                                                       |      | 50  |     | mV    |

| Vaccu                | Output Voltage<br>Accuracy    | Vout=all output range<br>Iout=1mA                                                     | -1.5 |     | 1.5 | %     |

| IOUTMAX1             | Output Current                |                                                                                       |      |     | 30  | mA    |

| I <sub>OUTMAX2</sub> | Output Current                | $4.5V < V_{IN} < 5.5V$                                                                |      |     | 100 | mA    |

| Vdiff                | Dropout Voltage               | Vout setting = VIN, IOUT= IOUTMAX1                                                    |      |     | 0.8 | V     |

| LIM                  | Limit Current                 |                                                                                       | 110  |     |     | mA    |

| Vdiff                | Dropout Voltage               | Vout setting = VIN, IOUT= IOUTMAX                                                     |      |     | 0.2 | V     |

| lss                  | Supply Current                | Iout=0mA                                                                              |      | 2   |     | μA    |

| IOFF                 | Standby current               | Iout=0mA                                                                              |      |     | 1   | μA    |

| Cout                 | Output Capacitor              |                                                                                       |      | 1.0 |     | μF    |

Operating Conditions (unless otherwise specified) Vin=3.6V, Cout=1.0µF, Ta = 25 degrees C

Table 8-8 LDORTC1 Electrical Characteristic

#### 8.3.5 LDORTC2 Electrical Characteristics

| Symbol           | Parameter                     | Condition                                                                             | Min  | Тур | Max | Units |

|------------------|-------------------------------|---------------------------------------------------------------------------------------|------|-----|-----|-------|

| VIN              | Input Voltage Range           | -                                                                                     | 2.2  | 3.6 | 5.5 | V     |

| Vout             | Output Voltage<br>Range       | 50µA <iout<ioutmax< td=""><td>0.9</td><td></td><td>3.5</td><td>V</td></iout<ioutmax<> | 0.9  |     | 3.5 | V     |

| VOUT             | Voltage setting step<br>width |                                                                                       |      | 50  |     | mV    |

| Vaccu            | Output Voltage<br>Accuracy    | Vout=all output range<br>Iout=1mA                                                     | -1.5 |     | 1.5 | %     |

| IOUTMAX          | Output Current                | -                                                                                     |      |     | 10  | mA    |

| I <sub>LIM</sub> | Limit Current                 |                                                                                       | 20   |     |     | mA    |

| Vdiff            | Dropout Voltage               | Vout setting = $V_{IN}$ , $I_{OUT}$ = $I_{OUTMAX}$                                    |      |     | 0.2 | V     |

| I <sub>SS</sub>  | Supply Current                | I <sub>OUT</sub> =0mA                                                                 |      | 1   |     | μA    |

| I <sub>OFF</sub> | Standby current               | Iout=0mA                                                                              |      |     | 1   | μA    |

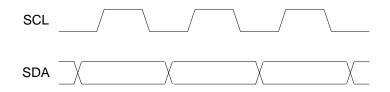

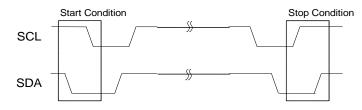

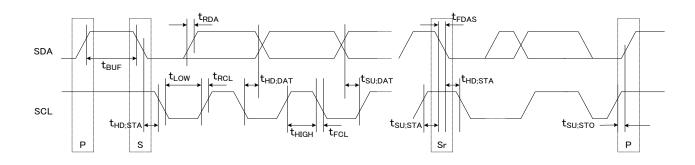

| Cout             | Output Capacitor              |                                                                                       |      | 1.0 |     | μF    |