LTC6945

# Ultralow Noise and Spurious 0.35GHz to 6GHz Integer-N Synthesizer

# FEATURES

- Low Noise Integer-N PLL

- 350MHz to 6GHz VCO Input Range

- –226dBc/Hz Normalized In-Band Phase Noise Floor

- –274dBc/Hz Normalized In-Band 1/f Noise

- -157dBc/Hz Wideband Output Phase Noise Floor

- Excellent Spurious Performance

- Output Divider (1 to 6, 50% Duty Cycle)

- Low Noise Reference Buffer

- Output Buffer Muting

- Charge Pump Supply from 3.15V to 5.25V

- Charge Pump Current from 250µA to 11.2mA

- Configurable Status Output

- SPI Compatible Serial Port Control

- PLLWizard<sup>™</sup> Software Design Tool Support

## **APPLICATIONS**

- Wireless Base Stations (LTE, WiMAX, W-CDMA, PCS)

- Broadband Wireless Access

- Microwave Data Links

- Military and Secure Radio

- Test and Measurement

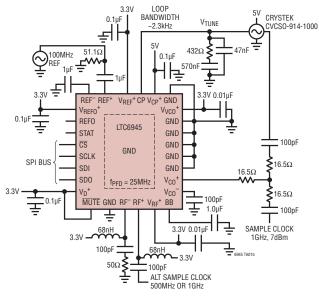

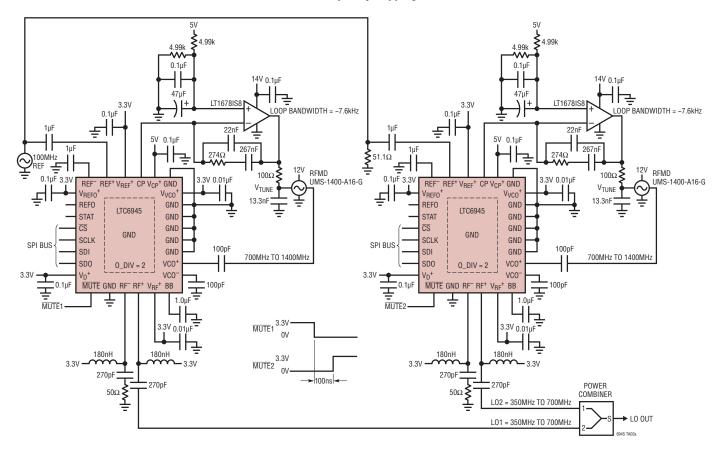

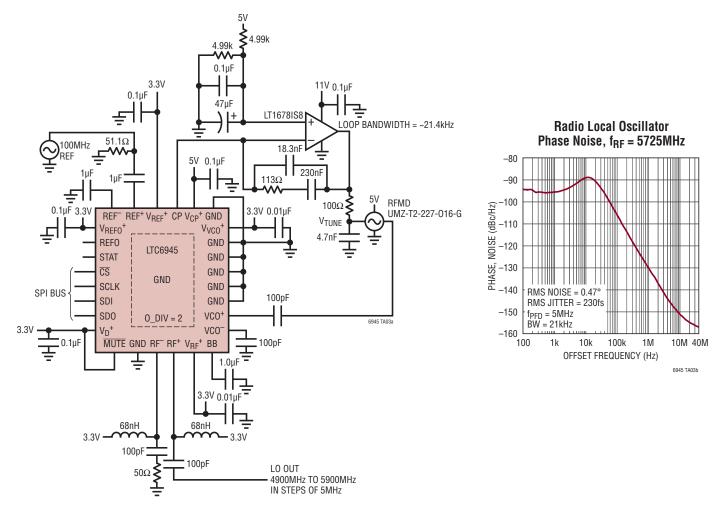

# TYPICAL APPLICATION

LTC6945 Data Converter Sample Clock

# DESCRIPTION

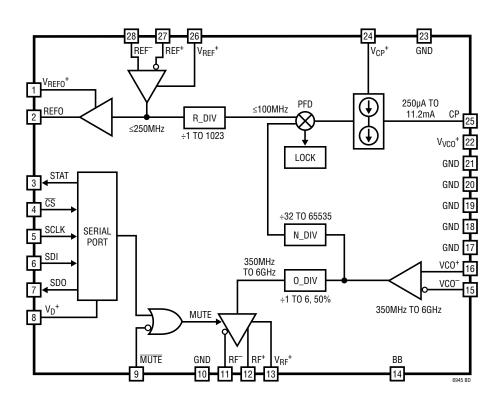

The LTC<sup>®</sup>6945 is a high performance, low noise, 6GHz phaselocked loop (PLL), including a reference divider, phasefrequency detector (PFD) with phase-lock indicator, charge pump, integer feedback divider and VCO output divider.

The part features a buffered, programmable VCO output divider with a range of 1 through 6. The differential, low noise output buffer has user-programmable output power ranging from –6dBm to 3dBm, and may be muted through either a digital input pin or software.

The low noise reference buffer outputs a typical 0dBm square wave directly into a  $50\Omega$  impedance from 10MHz to 250MHz, or may be disabled through software.

The ultralow noise charge pump contains selectable high and low voltage clamps useful for VCO monitoring, and also may be set to provide a  $V^+/2$  bias.

All device settings are controlled through a SPI-compatible serial port.

∠7, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PLLWizard is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

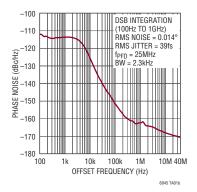

#### **1GHz Sample Clock Phase Noise**

# **ABSOLUTE MAXIMUM RATINGS**

### (Note 1)

#### Supply Voltages

| ouppij voltugoo                                                                                                 |                                      |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------|

| V <sup>+</sup> (V <sub>REF</sub> <sup>+</sup> , V <sub>REF0</sub> <sup>+</sup> , V <sub>RF</sub> <sup>+</sup> , | $V_{VCO}^+$ , $V_D^+$ ) to GND3.6V   |

| V <sub>CP</sub> <sup>+</sup> to GND                                                                             | 5.5V                                 |

| Voltage on CP Pin                                                                                               | GND - 0.3V to $V_{CP}^+$ + 0.3V      |

| Voltage on All Other Pins                                                                                       | GND - 0.3V to V <sup>+</sup> + 0.3V  |

| <b>Operating Junction Temper</b>                                                                                | ature Range, T <sub>J</sub> (Note 2) |

| LTC6945I                                                                                                        | –40°C to 105°C                       |

| Junction Temperature, T <sub>JM</sub>                                                                           | 4χ 125°C                             |

| Storage Temperature Range                                                                                       | e –65°C to 150°C                     |

|                                                                                                                 |                                      |

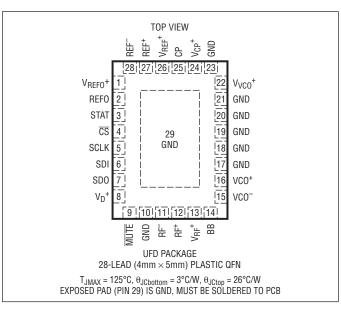

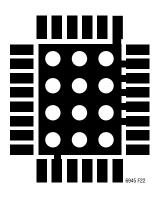

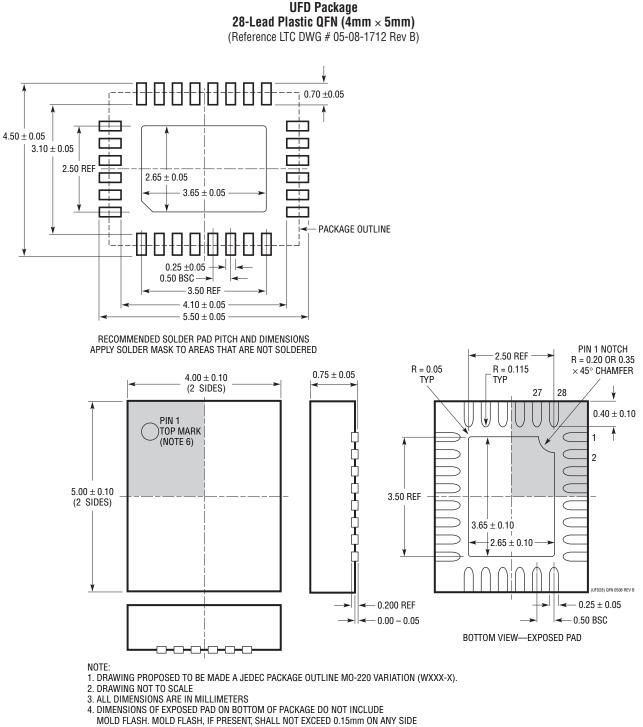

# PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING | PACKAGE DESCRIPTION             | JUNCTION TEMPERATURE RANGE |

|------------------|-------------------|--------------|---------------------------------|----------------------------|

| LTC6945IUFD#PBF  | LTC6945IUFD#TRPBF | 6945         | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 105°C             |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

### ELECTRICAL CHARACTERISTICS

The • denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{REF}^+ = V_{REF0}^+ = V_D^+ = V_{RF}^+ = V_{VC0}^+ = 3.3V$ ,  $V_{CP}^+ = 5V$  unless otherwise specified. All voltages are with respect to GND.

| SYMBOL            | PARAMETER                        | CONDITIONS                               |   | MIN  | ТҮР  | MAX  | UNITS            |

|-------------------|----------------------------------|------------------------------------------|---|------|------|------|------------------|

| Reference         | Inputs (REF+, REF <sup>-</sup> ) |                                          |   |      |      |      |                  |

| f <sub>REF</sub>  | Input Frequency                  |                                          |   | 10   |      | 250  | MHz              |

| V <sub>REF</sub>  | Input Signal Level               | Single-Ended, 1µF AC-Coupling Capacitors | • | 0.5  | 2    | 2.7  | V <sub>P-P</sub> |

|                   | Input Slew Rate                  |                                          | • | 20   |      |      | V/µs             |

|                   | Input Duty Cycle                 |                                          |   |      | 50   |      | %                |

|                   | Self-Bias Voltage                |                                          | • | 1.65 | 1.85 | 2.25 | V                |

|                   | Input Resistance                 | Differential                             | • | 6.2  | 8.4  | 11.6 | kΩ               |

|                   | Input Capacitance                | Differential                             |   |      | 3    |      | pF               |

| Reference         | Output (REFO)                    |                                          |   |      |      |      |                  |

| f <sub>REFO</sub> | Output Frequency                 |                                          | • | 10   |      | 250  | MHz              |

| P <sub>REF0</sub> | Output Power                     | $f_{REFO} = 10MHz, R_{LOAD} = 50\Omega$  | • | -0.2 |      | 3.2  | dBm              |

|                   | Output Impedance, Disabled       |                                          |   |      | 800  |      | Ω                |

|                   | ,                                |                                          |   |      |      |      | 6945fa           |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{REF}^+ = V_{REF0}^+ = V_{D}^+ = V_{RF}^+ = V_{VC0}^+ = 3.3V$ ,  $V_{CP}^+ = 5V$  unless otherwise specified. All voltages are with respect to GND.

| SYMBOL                | PARAMETER                                               | CONDITIONS                                                                                                                                                                                                                 |             | MIN                          | ТҮР                         | MAX                      | UNITS                    |

|-----------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------|-----------------------------|--------------------------|--------------------------|

| VCO Input (           | VCO+, VCO <sup>-</sup> )                                | ·                                                                                                                                                                                                                          |             |                              |                             | 1                        |                          |

| f <sub>VCO</sub>      | Input Frequency                                         |                                                                                                                                                                                                                            |             | 350                          |                             | 6000                     | MHz                      |

| P <sub>VCOI</sub>     | Input Power Level                                       | $R_Z = 50\Omega$ , Single-Ended                                                                                                                                                                                            |             | -8                           | 0                           | 6                        | dBm                      |

|                       | Input Resistance                                        | Single-Ended, Each Input                                                                                                                                                                                                   |             | 97                           | 121                         | 145                      | Ω                        |

| RF Output (           | RF <sup>+</sup> , RF <sup>−</sup> )                     | ·                                                                                                                                                                                                                          |             |                              |                             |                          |                          |

| f <sub>RF</sub>       | Output Frequency                                        |                                                                                                                                                                                                                            |             | 350                          |                             | 6000                     | MHz                      |

| 0                     | Output Divider Range                                    | All Integers Included                                                                                                                                                                                                      |             | 1                            |                             | 6                        |                          |

|                       | Output Duty Cycle                                       |                                                                                                                                                                                                                            |             |                              | 50                          |                          | %                        |

|                       | Output Resistance                                       | Single-Ended, Each Output to V <sub>RF</sub> <sup>+</sup>                                                                                                                                                                  |             | 111                          | 136                         | 159                      | Ω                        |

|                       | Output Common Mode Voltage                              |                                                                                                                                                                                                                            | •           | 2.4                          |                             | V <sub>RF</sub> +        | V                        |

| P <sub>RF(SE)</sub>   | Output Power, Single-Ended,<br>f <sub>RF</sub> = 900MHz | $\begin{array}{l} RFO[1:0] = 0,  R_{Z} = 50\Omega,  LC  Match \\ RFO[1:0] = 1,  R_{Z} = 50\Omega,  LC  Match \\ RFO[1:0] = 2,  R_{Z} = 50\Omega,  LC  Match \\ RFO[1:0] = 3,  R_{Z} = 50\Omega,  LC  Match \\ \end{array}$ | •<br>•<br>• | -9.7<br>-6.8<br>-3.9<br>-1.2 |                             | 6.0<br>3.6<br>0.4<br>2.3 | dBm<br>dBm<br>dBm<br>dBm |

|                       | Output Power, Muted                                     | $R_Z = 50\Omega$ , Single-Ended, $f_{RF} = 900MHz$ , $0 = 2 \text{ to } 6$                                                                                                                                                 |             |                              |                             | -60                      | dBm                      |

|                       | Mute Enable Time                                        |                                                                                                                                                                                                                            | •           |                              |                             | 110                      | ns                       |

|                       | Mute Disable Time                                       |                                                                                                                                                                                                                            |             |                              |                             | 170                      | ns                       |

| Phase/Freq            | uency Detector                                          |                                                                                                                                                                                                                            |             |                              |                             |                          |                          |

| f <sub>PFD</sub>      | Input Frequency                                         |                                                                                                                                                                                                                            |             |                              |                             | 100                      | MHz                      |

| Lock Indica           | tor, Available on the STAT Pin and via the              | SPI-Accessible Status Register                                                                                                                                                                                             |             |                              |                             |                          |                          |

| t <sub>LWW</sub>      | Lock Window Width                                       | LKWIN[1:0] = 0<br>LKWIN[1:0] = 1<br>LKWIN[1:0] = 2<br>LKWIN[1:0] = 3                                                                                                                                                       |             |                              | 3.0<br>10.0<br>30.0<br>90.0 |                          | ns<br>ns<br>ns           |

| t <sub>LWHYS</sub>    | Lock Window Hysteresis                                  | Increase in t <sub>LWW</sub> Moving from Locked State to Unlocked State                                                                                                                                                    |             |                              | 22                          |                          | %                        |

| Charge Pun            | np                                                      |                                                                                                                                                                                                                            | 1           |                              |                             | 1                        |                          |

| I <sub>CP</sub>       | Output Current Range                                    | 12 Settings (See Table 5)                                                                                                                                                                                                  |             | 0.25                         |                             | 11.2                     | mA                       |

|                       | Output Current Source/Sink Accuracy                     | $V_{CP} = V_{CP}^{+}/2$ , All Settings                                                                                                                                                                                     |             |                              |                             | ±6                       | %                        |

|                       | Output Current Source/Sink Matching                     | $I_{CP} = 250 \mu A \text{ to } 1.4 \text{mA}, V_{CP} = V_{CP}^{+}/2$<br>$I_{CP} = 2 \text{mA} \text{ to } 11.2 \text{mA}, V_{CP} = V_{CP}^{+}/2$                                                                          |             |                              |                             | ±3.5<br>±2               | %                        |

|                       | Output Current vs Output Voltage<br>Sensitivity         | (Note 3)                                                                                                                                                                                                                   | •           |                              | 0.1                         | 1.0                      | %/V                      |

|                       | Output Current vs Temperature                           | $V_{CP} = V_{CP}^{+}/2$                                                                                                                                                                                                    |             |                              | 170                         |                          | ppm/°C                   |

|                       | Output Hi-Z Leakage Current                             | $I_{CP} = 700\mu$ A, CPCLO = CPCHI = 0 (Note 3)<br>$I_{CP} = 11.2$ mA, CPCLO = CPCHI = 0 (Note 3)                                                                                                                          |             |                              | 0.5<br>5                    |                          | nA<br>nA                 |

| V <sub>CLMP(LO)</sub> | Low Clamp Voltage                                       | CPCLO = 1                                                                                                                                                                                                                  |             |                              | 0.84                        |                          | V                        |

| V <sub>CLMP(HI)</sub> | High Clamp Voltage                                      | CPCHI = 1, Referred to $V_{CP}^+$                                                                                                                                                                                          |             |                              | -0.96                       |                          | V                        |

| V <sub>MID</sub>      | Mid-Supply Output Bias Ratio                            | Referred to $(V_{CP}^+ - GND)$                                                                                                                                                                                             |             |                              | 0.48                        |                          | V/V                      |

| Reference (           | R) Divider                                              |                                                                                                                                                                                                                            |             |                              |                             | 1                        |                          |

| R                     | Divide Range                                            | All Integers Included                                                                                                                                                                                                      |             | 1                            |                             | 1023                     | Counts                   |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_{REF}^+ = V_{REF0}^+ = V_{D}^+ = V_{RF}^+ = V_{VC0}^+ = 3.3$ V,  $V_{CP}^+ = 5$ V unless otherwise specified. All voltages are with respect to GND.

| SYMBOL                | PARAMETER                                                                                               | CONDITIONS                                                                        |   | MIN  | ТҮР        | MAX        | UNITS    |

|-----------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---|------|------------|------------|----------|

| VCO (N) Div           | vider                                                                                                   |                                                                                   |   |      |            |            |          |

| Ν                     | Divide Range                                                                                            | All Integers Included                                                             |   | 32   |            | 65535      | Counts   |

| Digital Pin           | Specifications                                                                                          |                                                                                   |   |      |            |            |          |

| V <sub>IH</sub>       | High Level Input Voltage                                                                                | MUTE, CS, SDI, SCLK                                                               |   | 1.55 |            |            | V        |

| V <sub>IL</sub>       | Low Level Input Voltage                                                                                 | MUTE, CS, SDI, SCLK                                                               |   |      |            | 0.8        | V        |

| V <sub>IHYS</sub>     | Input Voltage Hysteresis                                                                                | MUTE, CS, SDI, SCLK                                                               |   |      | 250        |            | mV       |

|                       | Input Current                                                                                           | MUTE, CS, SDI, SCLK                                                               |   |      |            | ±1         | μA       |

| I <sub>OH</sub>       | High Level Output Current                                                                               | SDO and STAT, $V_{OH} = V_D^+ - 400 \text{mV}$                                    |   |      | -2.3       | -1.4       | mA       |

| l <sub>OL</sub>       | Low Level Output Current                                                                                | SDO and STAT, V <sub>OL</sub> = 400mV                                             |   | 1.8  | 3.4        |            | mA       |

|                       | SDO Hi-Z Current                                                                                        |                                                                                   |   |      |            | ±1         | μA       |

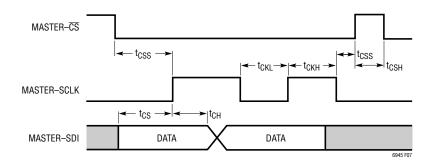

| Digital Tim           | ing Specifications (See Figures 8 and 9                                                                 | )                                                                                 |   |      |            |            |          |

| t <sub>CKH</sub>      | SCLK High Time                                                                                          |                                                                                   |   | 25   |            |            | ns       |

| t <sub>CKL</sub>      | SCLK Low Time                                                                                           |                                                                                   |   | 25   |            |            | ns       |

| t <sub>CSS</sub>      | CS Setup Time                                                                                           |                                                                                   |   | 10   |            |            | ns       |

| t <sub>CSH</sub>      | CS High Time                                                                                            |                                                                                   |   | 10   |            |            | ns       |

| t <sub>CS</sub>       | SDI to SCLK Setup Time                                                                                  |                                                                                   |   | 6    |            |            | ns       |

| t <sub>CH</sub>       | SDI to SCLK Hold Time                                                                                   |                                                                                   |   | 6    |            |            | ns       |

| t <sub>DO</sub>       | SCLK to SDO Time                                                                                        | To V <sub>IH</sub> /V <sub>IL</sub> /Hi-Z with 30pF Load                          |   |      |            | 16         | ns       |

| Power Supp            | oly Voltages                                                                                            |                                                                                   |   |      |            |            |          |

|                       | V <sub>REF</sub> <sup>+</sup> Supply Range                                                              |                                                                                   |   | 3.15 | 3.3        | 3.45       | V        |

|                       | V <sub>REFO</sub> <sup>+</sup> Supply Range                                                             |                                                                                   |   | 3.15 | 3.3        | 3.45       | V        |

|                       | V <sub>D</sub> <sup>+</sup> Supply Range                                                                |                                                                                   |   | 3.15 | 3.3        | 3.45       | V        |

|                       | V <sub>RF</sub> <sup>+</sup> Supply Range                                                               |                                                                                   |   | 3.15 | 3.3        | 3.45       | V        |

|                       | V <sub>VCO</sub> <sup>+</sup> Supply Range                                                              |                                                                                   |   | 3.15 | 3.3        | 3.45       | V        |

|                       | V <sub>CP</sub> <sup>+</sup> Supply Range                                                               |                                                                                   |   | 3.15 |            | 5.25       | V        |

| Power Supp            | oly Currents                                                                                            |                                                                                   |   |      |            |            |          |

| I <sub>DD</sub>       | V <sub>D</sub> <sup>+</sup> Supply Current                                                              | Digital Inputs at Supply Levels                                                   |   |      |            | 500        | μA       |

| I <sub>CC(CP)</sub>   | V <sub>CP</sub> <sup>+</sup> Supply Current                                                             | I <sub>CP</sub> = 11.2mA<br>I <sub>CP</sub> = 1.0mA                               | • |      | 34<br>12   | 39<br>14.5 | mA<br>mA |

|                       |                                                                                                         | PDALL = 1                                                                         |   |      | 235        | 385        | μA       |

| I <sub>CC(REFO)</sub> | V <sub>REFO</sub> <sup>+</sup> Supply Currents                                                          | REFO Enabled, $R_Z = \infty$                                                      |   |      | 7.8        | 9.0        | mA       |

| I <sub>CC</sub>       | Sum V <sub>REF</sub> <sup>+</sup> , V <sub>RF</sub> <sup>+</sup> , V <sub>VCO</sub> <sup>+</sup> Supply | RF Muted, $OD[2:0] = 1$                                                           | • |      | 70         | 78         | mA       |

|                       | Currents                                                                                                | RF Enabled, RFO[1:0] =0, OD[2:0] = 1<br>RF Enabled, RFO[1:0] = 3, OD[2:0] = 1     |   |      | 79<br>88   | 88<br>98   | mA<br>mA |

|                       |                                                                                                         | RF Enabled, RF0[1:0] =3, OD[2:0] = 2                                              |   |      | 105        | 117        | mA       |

|                       |                                                                                                         | RF Enabled, RFO[1:0] =3, OD[2:0] = 3<br>RF Enabled, RFO[1:0] =3, OD[2:0] = 4 to 6 | • |      | 111<br>116 | 124<br>128 | mA<br>mA |

|                       |                                                                                                         | PDALL = 1                                                                         |   |      | 202        | 396        | μA       |

LINEAR

### **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{REF}^+ = V_{REF0}^+ = V_D^+ = V_{RF}^+ = V_{VC0}^+ = 3.3V$ ,  $V_{CP}^+ = 5V$  unless otherwise specified. All voltages are with respect to GND.

| SYMBOL                    | PARAMETER                                  | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                 | MIN | ТҮР                                          | MAX | UNITS                                                    |

|---------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------|-----|----------------------------------------------------------|

| Phase Noise               | and Spurious                               | ·                                                                                                                                                                                                                                                                                                                                                                          |     |                                              |     |                                                          |

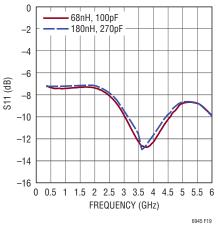

| L <sub>M(MIN)</sub>       | Output Phase Noise Floor (Note 5)          | $ \begin{array}{l} RFO[1:0] = 3,  OD[2:0] = 1,  f_{RF} = 6GHz \\ RFO[1:0] = 3,  OD[2:0] = 2,  f_{RF} = 3GHz \\ RFO[1:0] = 3,  OD[2:0] = 3,  f_{RF} = 2GHz \\ RFO[1:0] = 3,  OD[2:0] = 4,  f_{RF} = 1.5GHz \\ RFO[1:0] = 3,  OD[2:0] = 5,  f_{RF} = 1.2GHz \\ RFO[1:0] = 3,  OD[2:0] = 5,  f_{RF} = 1.2GHz \\ RFO[1:0] = 3,  OD[2:0] = 6,  f_{RF} = 1.0GHz \\ \end{array} $ |     | -155<br>-155<br>-156<br>-156<br>-157<br>-157 |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz |

| L <sub>M(NORM)</sub>      | Normalized In-Band Phase Noise Floor       | I <sub>CP</sub> = 11.2mA (Notes 6, 7, 8)                                                                                                                                                                                                                                                                                                                                   |     | -226                                         |     | dBc/Hz                                                   |

| L <sub>M(NORM -1/f)</sub> | Normalized In-Band 1/f Phase Noise         | I <sub>CP</sub> = 11.2mA (Notes 6, 9)                                                                                                                                                                                                                                                                                                                                      |     | -274                                         |     | dBc/Hz                                                   |

| L <sub>M(IB)</sub>        | In-Band Phase Noise Floor                  | (Notes 6, 7, 8, 10)                                                                                                                                                                                                                                                                                                                                                        |     | -99                                          |     | dBc/Hz                                                   |

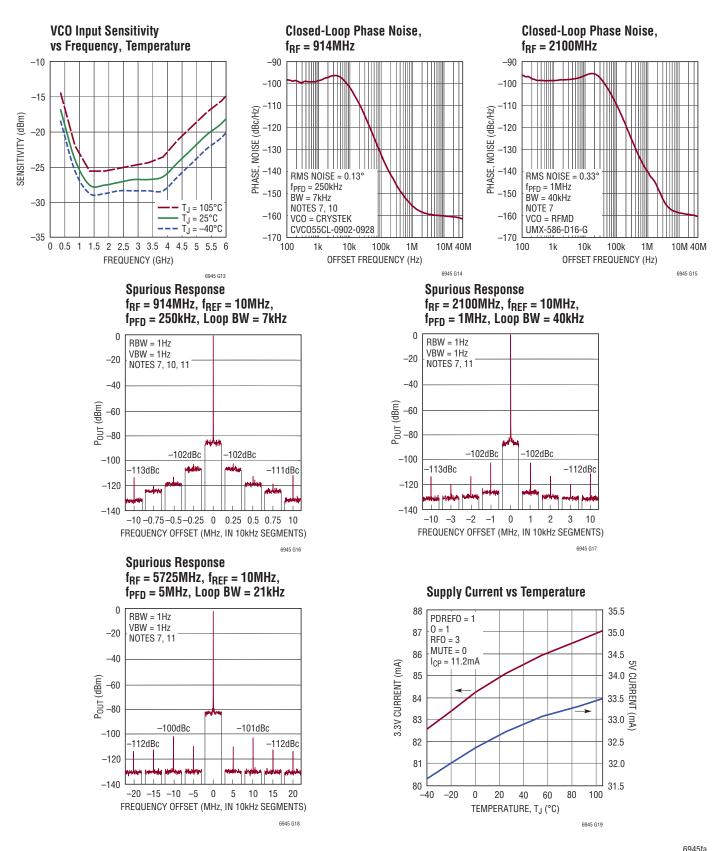

|                           | Integrated Phase Noise from 100Hz to 40MHz | (Notes 4, 7, 10)                                                                                                                                                                                                                                                                                                                                                           |     | 0.13                                         |     | °RMS                                                     |

|                           | Spurious                                   | Reference Spur, PLL locked (Notes 4, 7, 10, 11)                                                                                                                                                                                                                                                                                                                            |     | -102                                         |     | dBc                                                      |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC69451 is guaranteed to meet specified performance limits over the full operating junction temperature range of -40°C to 105°C. Under maximum operating conditions, air flow or heat sinking may be required to maintain a junction temperature of 105°C or lower. It is strongly recommended that the exposed pad (Pin 29) be soldered directly to the ground plane with an array of thermal vias as described in the Applications Information section.

**Note 3:** For  $0.9V \le V_{CP} \le (V_{CP}^+ - 0.9V)$ .

Note 4: VCO is Crystek CVC055CL-0902-0928.

Note 5:  $f_{VCO} = 6GHz$ ,  $f_{OFFSET} = 40MHz$ .

Note 6: Measured inside the loop bandwidth with the loop locked. Note 7: Reference frequency supplied by Wenzel 501-04608A,  $f_{REF} = 10MHz$ ,  $P_{REF} = 13dBm$ .

Note 8: Output phase noise floor is calculated from normalized phase noise floor by  $L_{M(OUT)} = -226 + 10\log_{10}(f_{PFD}) + 20\log_{10}(f_{RF}/f_{PFD})$ . Note 9: Output 1/f phase noise is calculated from normalized 1/f phase noise by  $L_{M(OUT - 1/f)} = -274 + 20log_{10} (f_{RF}) - 10log_{10} (f_{OFFSET})$ . Note 10: I<sub>CP</sub> = 11.2mA, f<sub>PFD</sub> = 250kHz, f<sub>RF</sub> = 914MHz, FILT[1:0] = 3, Loop BW = 7kHz.

Note 11: Measured using DC1649.

# TYPICAL PERFORMANCE CHARACTERISTICS

#### **REFO Output Power vs Frequency** 4 T.I = 105°C T<sub>J</sub> = 25°C 3 T.i = -40°C 2 1 Pout (dBm) 0 -1 -2 -3 -4 0 25 50 75 100 125 150 175 200 225 250 FREQUENCY (MHz) 6945 G02

# **TYPICAL PERFORMANCE CHARACTERISTICS**

## **TYPICAL PERFORMANCE CHARACTERISTICS**

# PIN FUNCTIONS

$V_{REF0}$ <sup>+</sup> (Pin 1): 3.15V to 3.45V Positive Supply Pin for REFO Circuitry. This pin should be bypassed directly to the ground plane using a 0.1µF ceramic capacitor as close to the pin as possible.

**REFO (Pin 2):** Reference Frequency Output. This produces a low noise square wave, buffered from the REF<sup>±</sup> differential inputs. The output is self-biased and must be AC-coupled with a 22nF capacitor.

**STAT (Pin 3):** Status Output. This signal is a configurable logical OR combination of the UNLOCK, LOCK, THI and TLO status bits, programmable via the STATUS register. See the Operations section for more details.

**CS** (Pin 4): Serial Port Chip Select. This CMOS input initiates a serial port communication burst when driven low, ending the burst when driven back high. See the Operations section for more details.

**SCLK (Pin 5):** Serial Port Clock. This CMOS input clocks serial port input data on its rising edge. See the Operations section for more details.

**SDI (Pin 6):** Serial Port Data Input. The serial port uses this CMOS input for data. See the Operations section for more details.

**SDO (Pin 7):** Serial Port Data Output. This CMOS threestate output presents data from the serial port during a read communication burst. Optionally attach a resistor of >200k to GND to prevent a floating output. See the Operations section for more details.

$V_D^+$  (Pin 8): 3.15V to 3.45V Positive Supply Pin for Serial Port Circuitry. This pin should be bypassed directly to the ground plane using a 0.1µF ceramic capacitor as close to the pin as possible.

**MUTE (Pin 9):** RF Mute. The CMOS active-low input mutes the RF<sup>±</sup> differential outputs while maintaining internal bias levels for quick response to de-assertion.

**GND (Pins 10, 17, 18, 19, 20, 21):** Negative Power Supply (Ground). These pins should be tied directly to the ground plane with multiple vias for each pin.

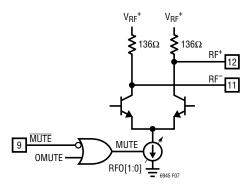

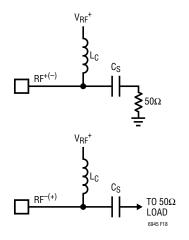

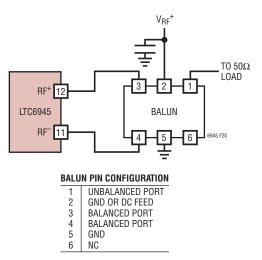

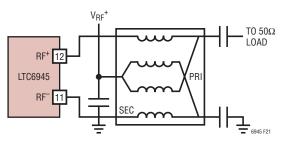

**RF<sup>-</sup>, RF<sup>+</sup> (Pins 11, 12):** RF Output Signals. The VCO output divider is buffered and presented differentially on these pins. The outputs are open collector, with  $136\Omega$  (typical) pull-up resistors tied to V<sub>RF</sub><sup>+</sup> to aid impedance matching. If used single-ended, the unused output should be terminated to  $50\Omega$ . See the Applications Information section for more details on impedance matching.

$V_{RF}^+$  (Pin 13): 3.15V to 3.45V Positive Supply Pin for RF Circuitry. This pin should be bypassed directly to the ground plane using a 0.01µF ceramic capacitor as close to the pin as possible.

**BB (Pin 14):** RF Reference Bypass. This output must be bypassed with a  $1.0\mu$ F ceramic capacitor to GND. Do not couple this pin to any other signal.

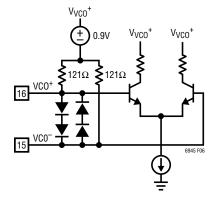

**VCO<sup>-</sup>, VCO<sup>+</sup>** (Pins 15, 16): VCO Input Signals. The differential signal placed on these pins is buffered with a low noise amplifier and fed to the internal output and feedback dividers. These self-biased inputs must be AC-coupled and present a single-ended  $121\Omega$  (typical) resistance to aid impedance matching. They may be used single-ended by bypassing VCO<sup>-</sup> to GND with a capacitor. See the Applications Information section for more details on impedance matching.

$V_{VCO}^+$  (Pin 22): 3.15V to 3.45V Positive Supply Pin for VCO Circuitry. This pin should be bypassed directly to the ground plane using a 0.01µF ceramic capacitor as close to the pin as possible.

**GND (23):** Negative Power Supply (Ground). This pin is attached directly to the die attach paddle (DAP) and should be tied directly to the ground plane.

$V_{CP}$  + (Pin 24): 3.15V to 5.25V Positive Supply Pin for Charge Pump Circuitry. This pin should be bypassed directly to the ground plane using a 0.1µF ceramic capacitor as close to the pin as possible.

**CP (Pin 25):** Charge Pump Output. This bi-directional current output is normally connected to the external loop filter. See the Applications Information section for more details.

### PIN FUNCTIONS

$V_{REF}^+$  (Pin 26): 3.15V to 3.45V Positive Supply Pin for Reference Input Circuitry. This pin should be bypassed directly to the ground plane using a 0.1µF ceramic capacitor as close to the pin as possible.

**REF<sup>+</sup>**, **REF<sup>-</sup>** (**Pins 27, 28**): Reference Input Signals. This differential input is buffered with a low noise amplifier, which feeds the reference divider and reference buffer. They are self-biased and must be AC-coupled with  $1\mu$ F

capacitors. If used single-ended, bypass REF<sup>-</sup> to GND with a  $1\mu$ F capacitor. If the single-ended signal is greater than  $2.7V_{P-P}$ , bypass REF<sup>-</sup> to GND with a 47pF capacitor.

**GND (Exposed Pad Pin 29):** Negative Power Supply (Ground). The package exposed pad must be soldered directly to the PCB land. The PCB land pattern should have multiple thermal vias to the ground plane for both low ground inductance and also low thermal resistance.

# **BLOCK DIAGRAM**

The LTC6945 is a high performance PLL, and, combined with an external high performance VCO, can produce low noise LO signals up to 6GHz. It is able to achieve superior integrated phase noise performance due to its extremely low in-band phase noise performance.

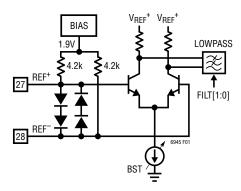

### **REFERENCE INPUT BUFFER**

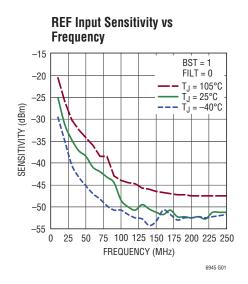

The PLL's reference frequency is applied differentially on pins REF<sup>+</sup> and REF<sup>-</sup>. These high impedance inputs are self-biased and must be AC-coupled with 1µF capacitors (see Figure 1 for a simplified schematic). Alternatively, the inputs may be used single-ended by applying the reference frequency at REF<sup>+</sup> and bypassing REF<sup>-</sup> to GND with a 1µF capacitor. If the single-ended signal is greater than  $2.7V_{P-P}$ , then use a 47pF capacitor for the GND bypass.

Figure 1. Simplified REF Interface Schematic

A high quality signal must be applied to the REF<sup>±</sup> inputs as they provide the frequency reference to the entire PLL. To achieve the part's in-band phase noise performance. apply a CW signal of at least 6dBm into 50 $\Omega$ , or a square wave of at least  $0.5V_{P-P}$  with slew rate of at least  $40V/\mu s$ .

Additional options are available through serial port register h08 to further refine the application. Bits FILT[1:0] control the reference input buffer's lowpass filter, and should be set based upon fREF to limit the reference's wideband noise. The FILT[1:0] bits must be set correctly to reach the L<sub>M(NORM)</sub> normalized in-band phase noise floor. See Table 1 for recommended settings.

The BST bit should be set based upon the input signal level to prevent the reference input buffer from saturating. See Table 2 for recommended settings and the Applications Information section for programming examples.

| Table 1. | FILT[1:0] | Programming |

|----------|-----------|-------------|

|----------|-----------|-------------|

| 1 1 5 5   |                  |

|-----------|------------------|

| FILT[1:0] | f <sub>REF</sub> |

| 3         | <20MHz           |

| 2         | NA               |

| 1         | 20MHz to 50MHz   |

| 0         | >50MHz           |

#### Table 2. BST Programming

| BST | V <sub>REF</sub>     |

|-----|----------------------|

| 1   | <2.0V <sub>P-P</sub> |

| 0   | ≥2.0V <sub>P-P</sub> |

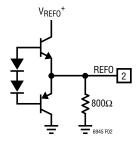

### **REFERENCE OUTPUT BUFFER**

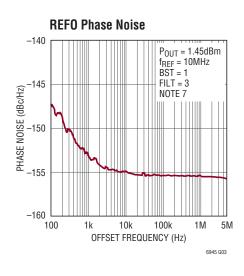

The reference output buffer produces a low noise square wave with a noise floor of -155dBc/Hz (typical) at 10MHz. Its output is low impedance, and produces 2dBm typical output power into a  $50\Omega$  load at 10MHz. Larger output swings will result if driving larger impedances. The output is self-biased, and must be AC-coupled with a 22nF capacitor (see Figure 2 for a simplified schematic). The buffer may be powered down by using bit PDREFO found in the serial port Power register h02.

Figure 2. Simplified REFO Interface Schematic

### **REFERENCE (R) DIVIDER**

A 10-bit divider, R DIV, is used to reduce the frequency seen at the PFD. Its divide ratio R may be set to any integer from 1 to 1023, inclusive. Use the RD[9:0] bits found in registers h03 and h04 to directly program the R divide ratio. See the Applications Information section for the relationship between R and the f<sub>REF</sub>, f<sub>PED</sub>, f<sub>VCO</sub> and f<sub>RF</sub> frequencies.

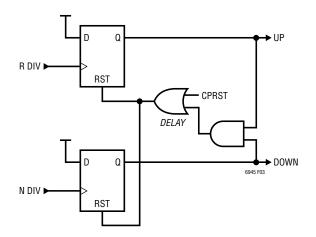

### PHASE/FREQUENCY DETECTOR (PFD)

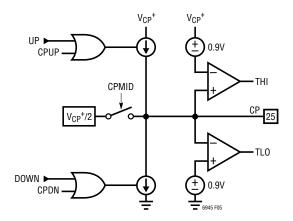

The phase/frequency detector (PFD), in conjunction with the charge pump, produces source and sink current pulses proportional to the phase difference between the outputs of the R and N dividers. This action provides the necessary feedback to phase-lock the loop, forcing a phase alignment at the PFD's inputs. The PFD may be disabled with the CPRST bit which prevents UP and DOWN pulses from being produced. See Figure 3 for a simplified schematic of the PFD.

Figure 3. Simplified PFD Schematic

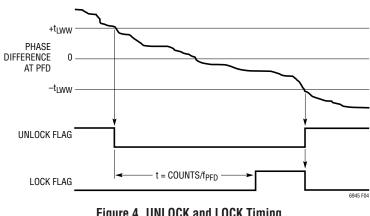

### LOCK INDICATOR

The lock indicator uses internal signals from the PFD to measure phase coincidence between the R and N divider output signals. It is enabled by setting the LKEN bit in the serial port register h07, and produces both LOCK and UNLOCK status flags, available through both the STAT output and serial port register h00.

The user sets the phase difference lock window time, t<sub>IWW</sub>, for a valid LOCK condition with the LKWIN[1:0] bits. See Table 3 for recommended settings for different fpen frequencies and the Applications Information section for examples.

#### Table 3. LKWIN[1:0] Programming

| LKWIN[1:0] | t <sub>LWW</sub> | f <sub>PFD</sub> |

|------------|------------------|------------------|

| 0          | 3ns              | >5MHz            |

| 1          | 10ns             | ≤5MHz            |

| 2          | 30ns             | ≤1.7MHz          |

| 3          | 90ns             | ≤550kHz          |

The PFD phase difference must be less than t<sub>I WW</sub> for the COUNTS number of successive counts before the lock indicator asserts the LOCK flag. The LKCT[1:0] bits found in register h09 are used to set COUNTS depending upon the application. See Table 4 for LKCT[1:0] programming and the Applications Information section for examples.

#### Table 4. LKCT[1:0] Programming

| LKCT[1:0] | COUNTS |

|-----------|--------|

| 0         | 32     |

| 1         | 128    |

| 2         | 512    |

| 3         | 2048   |

When the PFD phase difference is greater than  $t_{IWW}$ , the lock indicator immediately asserts the UNLOCK status flag and clears the LOCK flag, indicating an out-of-lock condition. The UNLOCK flag is immediately de-asserted when the phase difference is less than  $t_{LWW}$ . See Figure 4 for more details.

Figure 4. UNLOCK and LOCK Timing

### **CHARGE PUMP**

The charge pump, controlled by the PFD, forces sink (DOWN) or source (UP) current pulses onto the CP pin, which should be connected to an appropriate loop filter. See Figure 5 for a simplified schematic of the charge pump.

Figure 5. Simplified Charge Pump Schematic

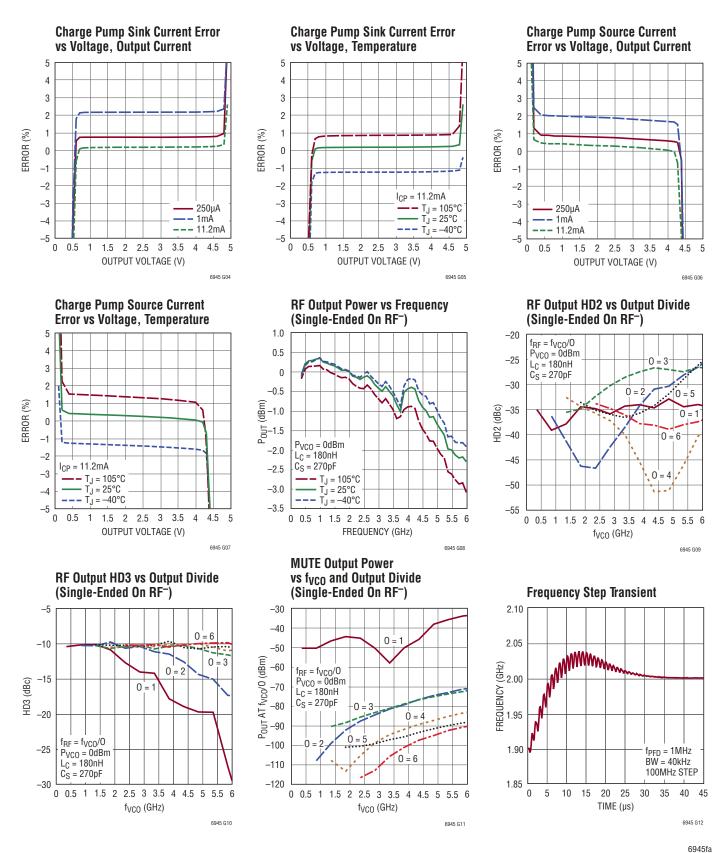

The output current magnitude  $I_{CP}$  may be set from 250µA to 11.2mA using the CP[3:0] bits found in serial port register h09. A larger  $I_{CP}$  can result in lower in-band noise due to the lower impedance of the loop filter components. See Table 5 for programming specifics and the Applications Information section for loop filter examples.

### Table 5. CP[3:0] Programming

| CP[3:0]  | I <sub>CP</sub> |

|----------|-----------------|

| 0        | 250µA           |

| 1        | 350µA           |

| 2        | 500µA           |

| 3        | 700µA           |

| 4        | 1.0mA           |

| 5        | 1.4mA           |

| 6        | 2.0mA           |

| 7        | 2.8mA           |

| 8        | 4.0mA           |

| 9        | 5.6mA           |

| 10       | 8.0mA           |

| 11       | 11.2mA          |

| 12 to 15 | Invalid         |

|          |                 |

The CPINV bit found in register hOA should be set for applications requiring signal inversion from the PFD, such

as for loops using negative-slope tuning oscillators, or inverting op amps in conjunction with positive-slope tuning oscillators. A passive loop filter as shown in Figure 15, used in conjunction with a positive-slope VCO, requires CPINV = 0.

### **CHARGE PUMP FUNCTIONS**

The charge pump contains additional features to aid in system start-up and monitoring. See Table 6 for a summary.

### Table 6. CP Function Bit Descriptions

| BIT    | DESCRIPTION                      |  |  |  |

|--------|----------------------------------|--|--|--|

| CPCHI  | Enable High Voltage Output Clamp |  |  |  |

| CPCLO  | Enable Low Voltage Output Clamp  |  |  |  |

| CPDN   | Force Sink Current               |  |  |  |

| CPINV  | Invert PFD Phase                 |  |  |  |

| CPMID  | Enable Mid-Voltage Bias          |  |  |  |

| CPRST  | Reset PFD                        |  |  |  |

| CPUP   | Force Source Current             |  |  |  |

| CPWIDE | Extend Current Pulse Width       |  |  |  |

| THI    | High Voltage Clamp Flag          |  |  |  |

| TLO    | Low Voltage Clamp Flag           |  |  |  |

|        |                                  |  |  |  |

The CPCHI and CPCLO bits found in register hOA enable the high and low voltage clamps, respectively. When CPCHI is enabled and the CP pin voltage exceeds approximately  $V_{CP}^+ - 0.9V$ , the THI status flag is set, and the charge pump sourcing current is disabled. Alternately, when CPCLO is enabled and the CP pin voltage is less than approximately 0.9V, the TLO status flag is set, and the charge pump sinking current is disabled. See Figure 5 for a simplified schematic.

The CPMID bit also found in register h0A enables a resistive  $V_{CP}^{+/2}$  output bias which may be used to prebias troublesome loop filters into a valid voltage range before attempting to lock the loop. When using CPMID, it is recommended to also assert the CPRST bit, forcing a PFD reset. Both CPMID and CPRST must be set to "0" for normal operation.

The CPUP and CPDN bits force a constant  $I_{CP}$  source or sink current, respectively, on the CP pin. The CPRST bit may also be used in conjunction with the CPUP and CPDN

bits, allowing a pre-charge of the loop to a known state, if required. CPUP, CPDN, and CPRST must be set to "0" to allow the loop to lock.

The CPWIDE bit extends the charge pump output current pulse width by increasing the PFD reset path's delay value (see Figure 3). CPWIDE is normally set to 0.

### VCO INPUT BUFFER

The VCO frequency is applied differentially on pins VCO<sup>+</sup> and VCO<sup>-</sup>. The inputs are self-biased and must be AC-coupled. Alternatively, the inputs may be used single-ended by applying the VCO frequency at VCO<sup>+</sup> and bypassing VCO<sup>-</sup> to GND with a capacitor. Each input provides a single-ended

Figure 6. Simplified VCO Interface Schematic

121 $\Omega$  resistance to aid in impedance matching at high frequencies. See the Applications Information section for matching guidelines.

### VCO (N) DIVIDER

The 16-bit N divider provides the feedback from the VCO input buffer to the PFD. Its divide ratio N may be set to any integer from 32 to 65535, inclusive. Use the ND[15:0] bits found in registers h05 and h06 to directly program the N divide ratio. See the Applications Information section for the relationship between N and the  $f_{REF}$ ,  $f_{PFD}$ ,  $f_{VCO}$  and  $f_{RF}$  frequencies.

### **OUTPUT (0) DIVIDER**

The 3-bit O divider can reduce the frequency from the VCO input buffer to the RF output buffer to extend the output frequency range. Its divide ratio O may be set to any integer from 1 to 6, inclusive, outputting a 50% duty cycle even with odd divide values. Use the OD[2:0] bits found in register h08 to directly program the 0 divide ratio. See the Applications Information section for the relationship between O and the  $f_{REF}$ ,  $f_{PFD}$ ,  $f_{VCO}$  and  $f_{RF}$  frequencies.

### **RF OUTPUT BUFFER**

The low noise, differential output buffer produces a differential output power of –6dBm to 3dBm, settable with bits RFO[1:0] according to Table 7. The outputs may be combined externally, or used individually. Terminate any unused output with a  $50\Omega$  resistor to V<sub>BF</sub><sup>+</sup>.

### Table 7. RFO[1:0] Programming

|          | 1 3                            |                                |

|----------|--------------------------------|--------------------------------|

| RF0[1:0} | P <sub>RF</sub> (Differential) | P <sub>RF</sub> (Single-Ended) |

| 0        | –6dBm                          | –9dBm                          |

| 1        | –3dBm                          | –6dBm                          |

| 2        | 0dBm                           | –3dBm                          |

| 3        | 3dBm                           | 0dBm                           |

Each output is open collector with  $136\Omega$  pull-up resistors to V<sub>RF</sub><sup>+</sup>, easing impedance matching at high frequencies. See Figure 7 for circuit details and the Applications Information section for matching guidelines. The buffer may be muted with either the OMUTE bit, found in register h02, or by forcing the MUTE input low.

Figure 7. Simplified RF Interface Schematic

6945f

### SERIAL PORT

The SPI-compatible serial port provides control and monitoring functionality. A configurable status output, STAT, gives additional instant monitoring.

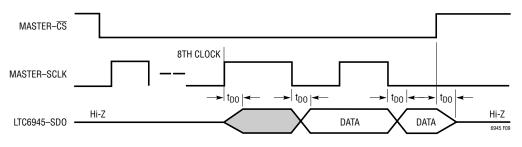

### **Communication Sequence**

The serial bus is comprised of  $\overline{CS}$ , SCLK, SDI and SDO. Data transfers to the part are accomplished by the serial bus master device first taking  $\overline{CS}$  low to enable the LTC6945's port. Input data applied on SDI is clocked on the rising edge of SCLK, with all transfers MSB first. The communication burst is terminated by the serial bus master returning  $\overline{CS}$  high. See Figure 8 for details.

Data is read from the part during a communication burst using SDO. Readback may be multidrop (more than one LTC6945 connected in parallel on the serial bus), as SDO is three-stated (Hi-Z) when  $\overline{CS} = 1$ , or when data is not being read from the part. *If the LTC6945 is not used in a multidrop configuration, or if the serial port master is not capable of setting the SDO line level between read sequences, it is recommended to attach a high value resistor of greater than 200k between SDO and GND to ensure the line returns to a known level during Hi-Z states. See Figure 9 for details.*

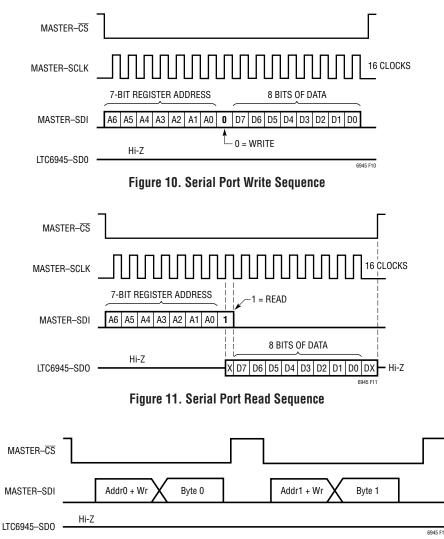

### Single Byte Transfers

The serial port is arranged as a simple memory map, with status and control available in 12, byte-wide registers. All data bursts are comprised of at least two bytes. The 7 most significant bits of the first byte are the register address, with an LSB of 1 indicating a read from the part, and LSB of 0 indicating a write to the part. The subsequent byte, or bytes, is data from/to the specified register address. See Figure 10 for an example of a detailed write sequence, and Figure 11 for a read sequence.

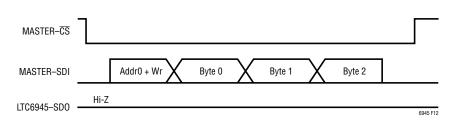

Figure 12 shows an example of two write communication bursts. The first byte of the first burst sent from the serial bus master on SDI contains the destination register address (Addr0) and an LSB of "0" indicating a write. The next byte is the data intended for the register at address Addr0.  $\overline{CS}$  is then taken high to terminate the transfer. The first byte of the second burst contains the destination register address (Addr1) and an LSB indicating a write. The next byte on SDI is the data intended for the register at address Addr1.  $\overline{CS}$  is then taken high to terminate the transfer.

Figure 8. Serial Port Write Timing Diagram

Figure 9. Serial Port Read Timing Diagram

### **Multiple Byte Transfers**

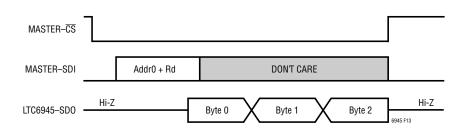

More efficient data transfer of multiple bytes is accomplished by using the LTC6945's register address autoincrement feature as shown in Figure 13. The serial port master sends the destination register address in the first byte and its data in the second byte as before, but continues sending bytes destined for subsequent registers. Byte 1's address is Addr0+1, Byte 2's address is Addr0+2, and so on. If the resister address pointer attempts to increment past 11 (h0B), it is automatically reset to 0.

An example of an auto-increment read from the part is shown in Figure 14. The first byte of the burst sent from the serial bus master on SDI contains the destination register address (Addr0) and an LSB of "1" indicating a read. Once the LTC6945 detects a read burst, it takes SDO out of the Hi-Z condition and sends data bytes sequentially, beginning with data from register Addr0. The part ignores all other data on SDI until the end of the burst.

### **Multidrop Configuration**

Several LTC6945s may share the serial bus. In this multidrop configuration, SCLK, SDI and SDO are common between all parts. The serial bus master must use a separate  $\overline{CS}$  for each LTC6945 and ensure that only one device has  $\overline{CS}$  asserted at any time. It is recommended to attach a high value resistor to SDO to ensure the line returns to a known level during Hi-Z states.

# LTC6945

# OPERATION

Figure 13. Serial Port Auto-Increment Write

Figure 14. Serial Port Auto-Increment Read

### Serial Port Registers

The memory map of the LTC6945 may be found in Table 8, with detailed bit descriptions found in Table 9. The register address shown in hexadecimal format under the ADDR column is used to specify each register. Each register is denoted as either read-only (R) or read-write (R/W). The register's default value on device power-up or after a reset is shown at the right.

The read-only register at address h00 is used to determine different status flags. These flags may be instantly output on the STAT pin by configuring register h01. See the STAT Output section for more information.

The read-only register at address hOB is a ROM byte for device identification.

### STAT Output

The STAT output pin is configured with the x[5:0] bits of register h01. These bits are used to bit-wise mask, or enable, the corresponding status flags of status register h00, according to Equation 1. The result of this bit-wise Boolean operation is then output on the STAT pin:

STAT = OR (Reg00[5,2:0] AND Reg01[5,2:0]) (1)

or expanded:

STAT = (UNLOCK AND x[5]) OR (LOCK AND x[2]) OR (THI AND x[1]) OR (TLO AND x[0])

For example, if the application requires STAT to go high whenever the LOCK or THI flags are set, then x[2] and x[1] should be set to "1", giving a register value of h6.

### **Block Power-Down Control**

The LTC6945's power-down control bits are located in register h02, described in Table 9. Different portions of the device may be powered down independently. *Care must be taken with the LSB of the register, the POR (power-on reset) bit. When written to a "1", this bit forces a full reset of the part's digital circuitry to its power-up default state.*

### Table 8. Serial Port Register Contents

| ADDR | MSB      | [6]      | [5]     | [4]     | [3]     | [2]     | [1]     | LSB     | R/W | DEFAULT |

|------|----------|----------|---------|---------|---------|---------|---------|---------|-----|---------|

| h00  | *        | *        | UNLOCK  | *       | *       | LOCK    | THI     | TL0     | R   |         |

| h01  | *        | *        | x[5]    | *       | *       | x[2]    | x[1]    | x[0]    | R/W | h04     |

| h02  | PDALL    | PDPLL    | *       | PDOUT   | PDREFO  | *       | OMUTE   | POR     | R/W | h0E     |

| h03  | *        | *        | *       | *       | *       | *       | RD[9]   | RD[8]   | R/W | h00     |

| h04  | RD[7]    | RD[6]    | RD[5]   | RD[4]   | RD[3]   | RD[2]   | RD[1]   | RD[0]   | R/W | h01     |

| h05  | ND[15]   | ND[14]   | ND[13]  | ND[12]  | ND[11]  | ND[10]  | ND[9]   | ND[8]   | R/W | h00     |

| h06  | ND[7]    | ND[6]    | ND[5]   | ND[4]   | ND[3]   | ND[2]   | ND[1]   | ND[0]   | R/W | hFA     |

| h07  | *        | *        | *       | *       | *       | *       | *       | LKEN    | R/W | h01     |

| h08  | BST      | FILT[1]  | FILT[0] | RF0[1]  | RF0[0]  | OD[2]   | OD[1]   | OD[0]   | R/W | hF9     |

| h09  | LKWIN[1] | LKWIN[0] | LKCT[1] | LKCT[0] | CP[3]   | CP[2]   | CP[1]   | CP[0]   | R/W | h9B     |

| h0A  | CPCHI    | CPCLO    | CPMID   | CPINV   | CPWIDE  | CPRST   | CPUP    | CPDN    | R/W | hE4     |

| h0B  | REV[2]   | REV[1]   | REV[0]  | PART[4] | PART[3] | PART[2] | PART[1] | PART[0] | R   | h40     |

\*unused

### Table 9. Serial Port Register Bit Field Summary

| BITS       | DESCRIPTION                        | DEFAULT |

|------------|------------------------------------|---------|

| BST        | REF Buffer Boost Current           | 1       |

| CP[3:0]    | CP Output Current                  | hB      |

| CPCHI      | CP Enable Hi Voltage Output Clamp  | 1       |

| CPCLO      | CP Enable Low Voltage Output Clamp | 1       |

| CPDN       | CP Pump Down Only                  | 0       |

| CPINV      | CP Invert Phase                    | 0       |

| CPMID      | CP Bias to Mid-Rail                | 1       |

| CPRST      | CP Three-State                     | 1       |

| CPUP       | CP Pump Up Only                    | 0       |

| CPWIDE     | CP Extend Pulse Width              | 0       |

| FILT[1:0]  | REF Input Buffer Filter            | h3      |

| LKCT[1:0]  | PLL Lock Cycle Count               | h1      |

| LKEN       | PLL Lock Indicator Enable          | 1       |

| LKWIN[1:0] | PLL Lock Indicator Window          | h2      |

| LOCK       | PLL Lock Indicator Flag            |         |

| ND[15:0]   | N Divider Value (ND[15:0] > 31)    | h00FA   |

| BITS      | DESCRIPTION                                        | DEFAULT |

|-----------|----------------------------------------------------|---------|

| OD[2:0]   | Output Divider Value (0 < OD[2:0] < 7)             | h1      |

| OMUTE     | Mutes RF Output                                    | 1       |

| PART[4:0] | Part Code                                          | h00     |

| PDALL     | Full Chip Power-Down                               | 0       |

| PDOUT     | Powers Down O_DIV, RF Output Buffer                | 0       |

| PDPLL     | Powers Down REF, REFO, R_DIV, PFD,<br>CPUMP, N_DIV | 0       |

| PDREFO    | Powers Down REFO                                   | 1       |

| POR       | Force Power-On Reset Register Initialization       | 0       |

| RD[9:0]   | R Divider Value (RD[9:0] > 0)                      | h001    |

| REV[2:0]  | Rev Code                                           |         |

| RF0[1:0]  | RF Output Power                                    | h3      |

| THI       | CP Clamp High Flag                                 |         |

| TL0       | CP Clamp Low Flag                                  |         |

| UNLOCK    | PLL Unlock Flag                                    |         |

| x[5,2:0]  | STAT Output OR Mask                                | h04     |

### INTRODUCTION

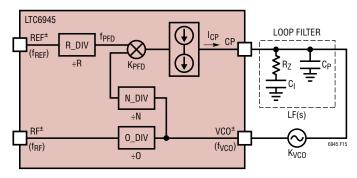

A PLL is a complex feedback system that may conceptually be considered a frequency multiplier. The system multiplies the frequency input at REF<sup>±</sup> and outputs a higher frequency at RF<sup>±</sup>. The PFD, charge pump, N divider, and external VCO and loop filter form a feedback loop to accurately control the output frequency (see Figure 15). The R and O dividers are used to set the output frequency resolution.

Figure 15. PLL Loop Diagram

### **OUTPUT FREQUENCY**

When the loop is locked, the frequency  $f_{VCO}$  (in Hz) produced at the output of the VCO is determined by the reference frequency  $f_{REF}$ , and the R and N divider values, given by Equation 2:

$$f_{VCO} = \frac{f_{REF} \bullet N}{R}$$

(2)

Here, the PFD frequency  $f_{\mbox{\scriptsize PFD}}$  produced is given by the following equation:

$$f_{PFD} = \frac{f_{REF}}{R}$$

(3)

and f<sub>VCO</sub> may be alternatively expressed as:

$f_{VCO} = f_{PFD} \bullet N$

The output frequency  $f_{\text{RF}}$  produced at the output of the O divider is given by Equation 4:

$$f_{\rm RF} = \frac{f_{\rm VCO}}{0} \tag{4}$$

Using the above equations, the output frequency resolution  $f_{STEP}$  produced by a unit change in N is given by Equation 5:

$$f_{\text{STEP}} = \frac{f_{\text{REF}}}{R \bullet 0} \tag{5}$$

### LOOP FILTER DESIGN

A stable PLL system requires care in selecting the external loop filter values. The Linear Technology PLLWizard application, available from www.linear.com, aids in design and simulation of the complete system.

The loop design should use the following algorithm:

- Determine the output frequency, f<sub>RF</sub>, and frequency step size, f<sub>STEP</sub>, based on application constraints. Using Equations 2, 3, 4 and 5, change f<sub>REF</sub>, N, R and O until the application frequency constraints are met. Use the minimum R value that still satisfies the constraints.

- 2. Select the loop bandwidth BW constrained by  $f_{PFD}$ . A stable loop requires that BW is less than  $f_{PFD}$  by at least a factor of 10.

- Select loop filter component R<sub>Z</sub> and charge pump current I<sub>CP</sub> based on BW and the VCO gain factor K<sub>VCO</sub>.

BW (in Hz) is approximated by the following equation:

$$\mathsf{BW} \cong \frac{\mathsf{I}_{\mathsf{CP}} \bullet \mathsf{R}_Z \bullet \mathsf{K}_{\mathsf{VCO}}}{2 \bullet \pi \bullet \mathsf{N}} \tag{6}$$

or:

$$\mathsf{R}_{\mathsf{Z}} = \frac{2 \bullet \pi \bullet \mathsf{BW} \bullet \mathsf{N}}{\mathsf{I}_{\mathsf{CP}} \bullet \mathsf{K}_{\mathsf{VCO}}}$$

where  $K_{VCO}$  is in Hz/V,  $I_{CP}$  is in Amps, and  $R_Z$  is in Ohms.  $K_{VCO}$  is the VCO's frequency tuning sensitivity, and may be determined from the VCO specifications. Use  $I_{CP} = 11.2$ mA to lower in-band noise unless component values force a lower setting.

4. Select loop filter components  $C_I$  and  $C_P$  based on BW and  $R_Z$ . A reliable loop can be achieved by using the following equations for the loop capacitors (in Farads):

$$C_{I} = \frac{3.5}{2 \bullet \pi \bullet BW \bullet R_{Z}}$$

(7)

$$C_{\rm P} = \frac{1}{7 \bullet \pi \bullet \rm{BW} \bullet \rm{R}_{\rm Z}}$$

(8)

### LOOP FILTERS USING AN OPAMP

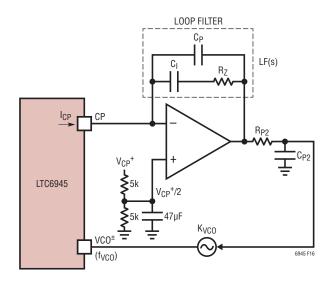

Some VCO tune voltage ranges are greater than the LTC6945's charge pump voltage range. An active loop filter using an op amp can increase the tuning voltage range. To maintain the LTC6945's high performance, care must be given to picking an appropriate op amp.

The op amp input common mode voltage should be biased within the LTC6945 charge pump's voltage range, while its output voltage should achieve the VCO tuning range. See Figure 16 for an example op amp loop filter.

The op amp's input bias current is supplied by the charge pump; minimizing this current keeps spurs related to  $f_{PFD}$  low. The input bias current should be less than the charge pump leakage (found in the Electrical Characteristics section) to avoid increasing spurious products.

Figure 16. Op Amp Loop Filter

Op amp noise sources are highpass filtered by the PLL loop filter and should be kept at a minimum, as their effect raises the total system phase noise beginning near the loop bandwidth. Choose a low noise op amp whose input-referred voltage noise is less than the thermal noise of  $R_Z$ . Additionally, the gain bandwidth of the op amp should be at least 15 times the loop bandwidth to limit phase margin degradation. The LT1678 is an op amp that works very well in most applications.

An additional R-C lowpass filter (formed by  $R_{P2}$  and  $C_{P2}$ in Figure 16) connected at the input of the VCO will limit the op amp noise sources. The bandwidth of this filter should be placed approximately 15 to 20 times the PLL loop bandwidth to limit loop phase margin degradation.  $R_{P2}$  should be small (preferably much less than  $R_Z$ ) to minimize its noise impact on the loop. However, picking too small of a value can make the op amp unstable as it has to drive the capacitor in this filter.

### **DESIGN AND PROGRAMMING EXAMPLE**

This programming example uses the DC1649. Assume the following parameters of interest :

$f_{REF}$  = 100MHz at 7dBm into 50 $\Omega$   $f_{STEP}$  = 250kHz  $f_{VCO}$  = 902MHz to 928MHz  $K_{VCO}$  = 15MHz/V to 21.6MHz/V  $f_{RF}$  = 914MHz

### **Determining Divider Values**

Following the Loop Filter Design algorithm, first determine all the divider values. Using Equations 2, 3, 4 and 5, calculate the following values:

400

3656

The next step in the algorithm is to determine the openloop bandwidth. BW should be at least 10× smaller than  $f_{PFD}$ . Wider loop bandwidths could have lower integrated phase noise, depending on the VCO phase noise signature, while narrower bandwidths will likely have lower spurious power. Use a factor of 25 for this design:

$$\mathsf{BW} = \frac{250\mathsf{kHz}}{25} = 10\mathsf{kHz}$$

### Loop Filter Component Selection

Now set loop filter resistor  $R_Z$  and charge pump current  $I_{CP}$ . Because the  $K_{VCO}$  varies over the VCO's frequency range, using the  $K_{VCO}$  geometric mean gives good results. Using an  $I_{CP}$  of 11.2mA,  $R_Z$  is determined:

$$K_{VC0} = 10^{6} \cdot \sqrt{15 \cdot 21.6} = 18MHz / V$$

$$R_{Z} = \frac{2 \cdot \pi \cdot 10k \cdot 3656}{11.2m \cdot 18M}$$

$$R_{Z} = 1.14k$$

Now calculate  $C_I$  and  $C_P$  from Equations 7 and 8:

$$C_{I} = \frac{3.5}{2 \bullet \pi \bullet 10k \bullet 1.14k} = 48.9nF$$

$$C_{P} = \frac{1}{7 \bullet \pi \bullet 10k \bullet 1.14k} = 3.99nF$$

### **Status Output Programming**

This example will use the STAT pin to monitor a phase lock condition. Program x[2] = 1 to force the STAT pin high whenever the LOCK bit asserts:

Reg01 = h04

### Power Register Programming

For correct PLL operation all internal blocks should be enabled, but PDREFO should be set if the REFO pin is not being used. OMUTE may remain asserted (or the  $\overline{MUTE}$  pin held low) until programming is complete. For PDREFO = 1 and OMUTE = 1:

Reg02 = h0A

### **Divider Programming**

Program registers Reg03 to Reg06 with the previously determined R and N divider values:

| Reg03 = h01 |  |

|-------------|--|

| Reg04 = h90 |  |

| Reg05 = h0E |  |

| Reg06 = h48 |  |

### Reference Input Settings and Output Divider Programming

From Table 1, FILT = 0 for a 100MHz reference frequency.

Next, convert 7dBm into  $V_{P-P}$ . For a CW tone, use the following equation with R = 50:

$$V_{\mathsf{P}-\mathsf{P}} \simeq \sqrt{\mathsf{R}} \bullet 10^{(\mathsf{dBm}-21)/20} \tag{9}$$

This gives  $V_{P\text{-}P}$  = 1.41V, and, according to Table 2, set BST = 1.

Now program Reg08, assuming maximum  $RF^{\pm}$  output power (RF0[1:0] = 3 according to Table 7) and OD[2:0] = 1:

Reg08 = h99

### Lock Detect and Charge Pump Current Programming

Next determine the lock indicator window from  $f_{PFD}$ . From Table 3, LKWIN[1:0] = 3 for a  $t_{LWW}$  of 90ns. The LTC6945 will consider the loop "locked" as long as the phase coincidence at the PFD is within 8°, as calculated below:

phase =

$$360^{\circ} \cdot t_{LWW} \cdot f_{PFD} = 360 \cdot 90n \cdot 250k \approx 8^{\circ}$$

LKWIN[1:0] may be set to a smaller value to be more conservative. However, the inherent phase noise of the loop could cause false "unlocks" for too small a value.

Choosing the correct COUNTS depends upon the ratio of the bandwidth of the loop to the PFD frequency (BW/f<sub>PFD</sub>). Smaller ratios dictate larger COUNTS values. A COUNTS value of 128 will work for the ratio of 1/25. From Table 4, LKCT[1:0] = 1 for 128 counts.

Using Table 5 with the previously selected  $I_{CP}$  of 11.2mA, gives CP[3:0] = 11. This is enough information to program Reg09:

Reg09 = hDB

To enable the lock indicator, write Reg07:

Reg07 = h01

### **Charge Pump Function Programming**

The DC1649 includes an LT1678I op amp in the loop filter. This allows the circuit to reach the voltage range specified for the VCO's tuning input. However, it also adds an inversion in the loop transfer function. Compensate for this inversion by setting CPINV = 1.

This example does not use the additional voltage clamp features to allow fault condition monitoring. The loop feedback provided by the op amp will force the charge pump output to be equal to the op amp positive input pin's voltage. Disable the charge pump voltage clamps by setting CPCHI = 0 and CPCLO = 0. Disable all the other charge pump functions (CPMID, CPRST, CPUP and CPDN) to allow the loop to lock:

Reg0A = h10

The loop should now lock. Now unmute the output by setting OMUTE = 0 (assumes the  $\overline{\text{MUTE}}$  pin is high):

Reg02 = h08

### **REFERENCE SOURCE CONSIDERATIONS**

A high quality signal must be applied to the REF<sup>±</sup> inputs as they provide the frequency reference to the entire PLL. As mentioned previously, to achieve the part's in-band phase noise performance, apply a CW signal of at least 6dBm into 50 $\Omega$ , or a square wave of at least 0.5V<sub>P-P</sub> with slew rate of at least 40V/µs.

The LTC6945 may be driven single-ended to CMOS levels (greater than  $2.7V_{P-P}$ ). Apply the reference signal directly without a DC-blocking capacitor at REF<sup>+</sup>, and bypass REF<sup>-</sup> to GND with a 47pF capacitor. The BST bit must also be set to "0", according to guidelines given in Table 2.

The LTC6945 achieves an in-band normalized phase noise floor of -226 dBc/Hz (typical). To calculate its equivalent input phase noise floor L<sub>M(IN)</sub>, use Equation 10:

$$L_{M(IN)} = -226 + 10 \bullet \log_{10}(f_{REF})$$

(10)

For example, using a 10MHz reference frequency gives an input phase noise floor of -156dBc/Hz. The reference frequency source's phase noise must be approximately 3dB better than this to prevent limiting the overall system performance.

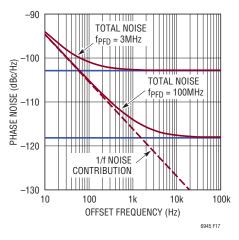

### **IN-BAND OUTPUT PHASE NOISE**

The in-band phase noise produced at  $f_{\text{RF}}$  may be calculated by using Equation 11.

$$L_{M(OUT)} = -226 + 10 \cdot \log_{10} (f_{PFD})$$

$$+20 \cdot \log_{10} \left( \frac{f_{RF}}{f_{PFD}} \right)$$

(11)

or

$$\begin{split} L_{M(OUT)} &= -226 + 10 \bullet \log_{10} \left( f_{PFD} \right) \\ &+ 20 \bullet \log_{10} \left( \frac{N}{O} \right) \end{split}$$

As seen for a given PFD frequency  $f_{PFD}$ , the output in-band phase noise increases at a 20dB-per-decade rate with the N divider count. So, for a given output frequency  $f_{RF}$ ,  $f_{PFD}$  should be as large as possible (or N should be as small as possible) while still satisfying the application's frequency step size requirements.