# Analog/Digital Dimmable Power Factor Corrected Quasi-Resonant Primary Side Current-Mode Controller for LED Lighting

The NCL30086 is a power factor corrected flyback controller targeting isolated and non-isolated "Smart-dimmable" constant current LED drivers. The controller operates in a quasi-resonant mode to provide optimal efficiency. The current control algorithm supports flyback, buck-boost, and SEPIC topologies. Thanks to a novel control method, the device is able to tightly regulate a constant LED current from the primary side. This removes the need for secondary side feedback circuitry, biasing and an optocoupler.

The device is highly integrated with a minimum number of external components. A robust suite of safety protection is built in to simplify the design. This device is specifically intended for very compact space efficient designs and supports analog and PWM dimming with a dedicated dimming input intended to control the average LED current. To ensure reliable operation at elevated temperatures, a user configurable current foldback circuit is also provided. The NCL30086 is housed in the SOIC10 which has the same body size as a standard SOIC8.

#### **Features**

- Quasi-resonant Peak Current-mode Control Operation

- Constant Current Control with Primary Side Feedback

- Tight LED Constant Current Regulation of ±2% Typical

- Power Factor Correction

- Analog or PWM dimming

- Line Feedforward for Enhanced Regulation Accuracy

- Low Start-up Current (10 μA typ.)

- Wide V<sub>cc</sub> Range

- 300 mA / 500 mA Totem Pole Driver with 12 V Gate Clamp

- Robust Protection Features

- ◆ Brown–Out Detection

- OVP on V<sub>CC</sub>

- Programmable Over Voltage / LED Open Circuit Protection

- ♦ Cycle-by-cycle Peak Current Limit

- Winding Short Circuit Protection

- Secondary Diode Short Protection

- Output Short Circuit Protection

- Current Sense (CS) Short Detection

- User programmable NTC Based Thermal Foldback

- Thermal Shutdown

## ON Semiconductor®

www.onsemi.com

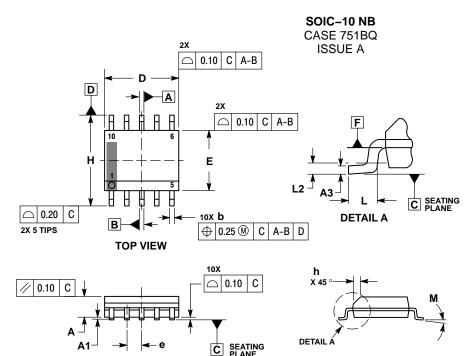

SOIC-10 CASE 751BQ

#### MARKING DIAGRAM

L30086x = Specific Device Code

x = A, B, C, D

A = Assembly Location

L = Wafer Lot Y = Year

W = Work Week

= Pb-Free Package

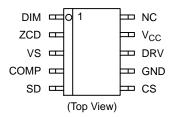

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 27 of this data sheet.

- -40 to 125°C Operating Junction Temperature

- Pb-Free, Halide-Free Product

- Four Versions: NCL30086A, B, C and D (See Table 1)

## **Typical Applications**

- Integral LED Bulbs

- LED Light Engines

- LED Driver Power Supplies

- Smart LED Lighting Applications

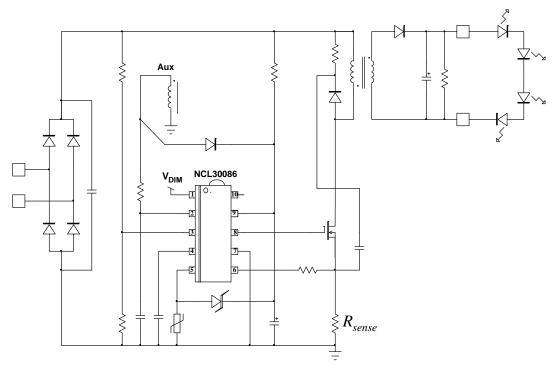

Figure 1. Typical Application Schematic in a Flyback Converter

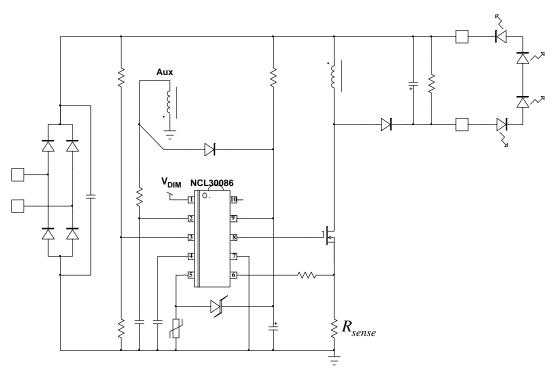

Figure 2. Typical Application Schematic in a Buck-Boost Converter

Table 1. FOUR NCL30086 VERSIONS

| Part Number | Protection Mode | Current Regulation<br>Reference Voltage<br>(V <sub>REF</sub> ) | Recommended for (*):                                                                                             |

|-------------|-----------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| NCL30086A   | Latching-off    | 250 mV                                                         | Isolated converters.   Non-isolated converters with $ V_{out} \leq \sqrt{2} \cdot (V_{in,rms})_{LL} $            |

| NCL30086B   | Auto-recovery   | 250 mV                                                         | Isolated converters. Non–isolated converters with $V_{out} \leq \sqrt{2} \cdot (V_{in,rms})_{LL}$                |

| NCL30086C   | Latching-off    | 200 mV                                                         | Non–isolated converters with ${\rm V_{out}} > \sqrt{2}  \cdot  ({\rm V_{in,rms}})_{\rm LL}$                      |

| NCL30086D   | Auto-recovery   | 200 mV                                                         | Non–isolated converters with $\label{eq:Vout} V_{\text{out}} > \sqrt{2}  \cdot  (V_{\text{in,rms}})_{\text{LL}}$ |

<sup>\*(</sup>V<sub>in,rms</sub>)<sub>LL</sub> designates the lowest line rms voltage. Refer to ANDxxxx/D for more details. (http://www.onsemi.com/pub\_link/Collateral/ANDxxxx-D.PDF).

# **Table 2. PIN FUNCTION DESCRIPTION**

| Pin No | Pin Name | Function                         | Pin Description                                                                                                                                                                                                                                            |

|--------|----------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DIM      | Analog / PWM Dimming             | This pin is used for analog or PWM dimming control. An analog signal that can be varied between $V_{\text{DIM0}}$ and $V_{\text{DIM100}}$ or a PWM signal can be used to adjust the LED current.                                                           |

| 2      | ZCD      | Zero Crossing Detection          | Connected to the auxiliary winding, this pin detects the core reset event.                                                                                                                                                                                 |

| 3      | VS       | Input Voltage Sensing            | This pin monitors the input voltage rail for: Power Factor Correction Valley lockout Brownout Detection                                                                                                                                                    |

| 4      | COMP     | Filtering Capacitor              | This pin receives a filtering capacitor for power factor correction. Typical values ranges from 1 – 4.7 $\mu\text{F}.$                                                                                                                                     |

| 5      | SD       | Thermal Foldback and<br>Shutdown | Connecting an NTC to this pin allows the user to program thermal current fold-back threshold and slope. A Zener diode can also be used to pull-up the pin and stop the controller for adjustable OVP protection.                                           |

| 6      | CS       | Current Sense                    | This pin monitors the primary peak current.                                                                                                                                                                                                                |

| 7      | GND      | -                                | Controller ground pin.                                                                                                                                                                                                                                     |

| 8      | DRV      | Driver Output                    | The driver's output to an external MOSFET                                                                                                                                                                                                                  |

| 9      | Vcc      | IC Supply Pin                    | This pin is the positive supply of the IC. The circuit starts to operate when $V_{CC}$ exceeds 18 V and turns off when $V_{CC}$ goes below 8.8 V (typical values). After start–up, the operating range is 9.4 V up to 26 V ( $V_{CC(OVP)}$ minimum level). |

| 10     | NC       | _                                | -                                                                                                                                                                                                                                                          |

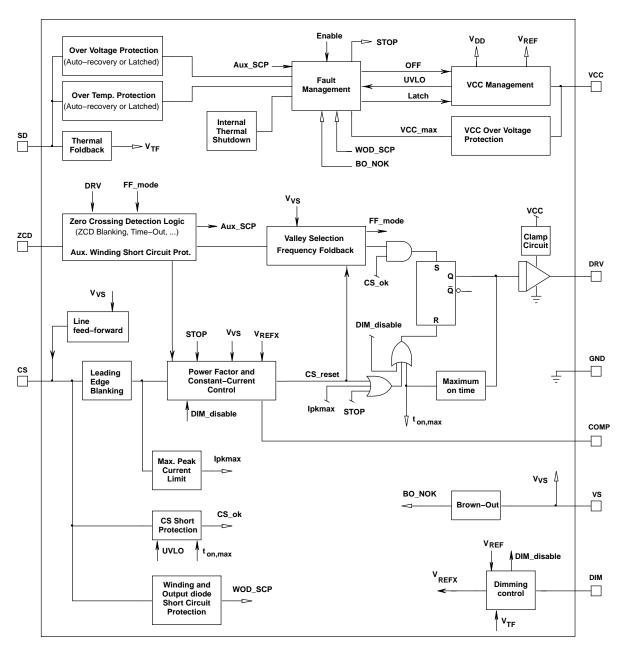

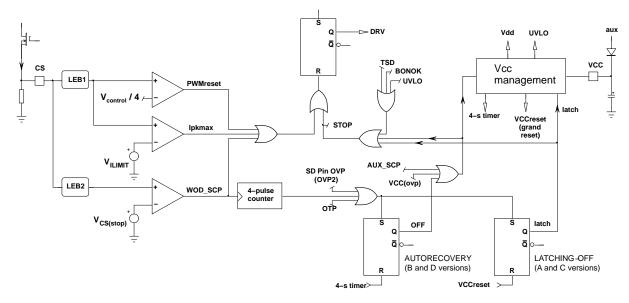

# **Internal Circuit Architecture**

Figure 3. Internal Circuit Architecture

Table 3. MAXIMUM RATINGS TABLE(S)

| Symbol                                         | Rating                                                                                                                           | Value                                         | Unit    |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------|

| V <sub>CC(MAX)</sub>                           | Maximum Power Supply voltage, $V_{\rm CC}$ pin, continuous voltage Maximum current for $V_{\rm CC}$ pin                          | -0.3 to 30<br>Internally limited              | V<br>mA |

| V <sub>DRV(MAX)</sub><br>I <sub>DRV(MAX)</sub> | Maximum driver pin voltage, DRV pin, continuous voltage Maximum current for DRV pin                                              | -0.3, V <sub>DRV</sub> (Note 1)<br>-300, +500 | V<br>mA |

| V <sub>MAX</sub><br>I <sub>MAX</sub>           | Maximum voltage on low power pins (except DRV and $V_{CC}$ pins) Current range for low power pins (except DRV and $V_{CC}$ pins) | -0.3, 5.5 (Notes 2 and 5)<br>-2, +5           | V<br>mA |

| $R_{\theta J-A}$                               | Thermal Resistance Junction-to-Air                                                                                               | 180                                           | °C/W    |

| $T_{J(MAX)}$                                   | Maximum Junction Temperature                                                                                                     | 150                                           | °C      |

|                                                | Operating Temperature Range                                                                                                      | -40 to +125                                   | °C      |

|                                                | Storage Temperature Range                                                                                                        | -60 to +150                                   | °C      |

|                                                | ESD Capability, HBM model (Note 3)                                                                                               | 3.5                                           | kV      |

|                                                | ESD Capability, MM model (Note 3)                                                                                                | 250                                           | V       |

|                                                | ESD Capability, CDM model (Note 3)                                                                                               | 2                                             | kV      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- V<sub>DRV</sub> is the DRV clamp voltage V<sub>DRV(high)</sub> when V<sub>CC</sub> is higher than V<sub>DRV(high)</sub>. V<sub>DRV</sub> is V<sub>CC</sub> otherwise.

This level is low enough to guarantee not to exceed the internal ESD diode and 5.5–V Zener diode. More positive and negative voltages can be applied if the pin current stays within the -2 mA / 5 mA range.

- 3. This device contains ESD protection and exceeds the following tests: Human Body Model 3500 V per JEDEC Standard JESD22–A114E, Machine Model Method 250 V per JEDEC Standard JESD22–A115B, Charged Device Model 2000 V per JEDEC Standard JESD22–C101E.

- 4. This device contains latch-up protection and has been tested per JEDEC Standard JESD78D, Class I and exceeds ±100 mA.

- 5. Recommended maximum V<sub>S</sub> voltage for optimal operation is 4 V. –0.3 V to +4.0 V is hence, the V<sub>S</sub> pin recommended range.

**Table 4. ELECTRICAL CHARACTERISTICS** (Unless otherwise noted: For typical values  $T_J = 25^{\circ}C$ ,  $V_{CC} = 12 \text{ V}$ ,  $V_{ZCD} = 0 \text{ V}$ ,  $V_{CS} = 0 \text{ V}$ .  $V_{CS} = 15 \text{ V}$ ) For min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ .  $V_{CC} = 12 \text{ V}$ )

| Description                                                                                                                           | Test Condition                                                                                       | Symbol                                                                               | Min                   | Тур                   | Max                   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|------|

| STARTUP AND SUPPLY CIRCUITS                                                                                                           |                                                                                                      |                                                                                      |                       |                       |                       |      |

| Supply Voltage Startup Threshold Minimum Operating Voltage Hysteresis V <sub>CC(on)</sub> – V <sub>CC(off)</sub> Internal logic reset | V <sub>CC</sub> rising<br>V <sub>CC</sub> rising<br>V <sub>CC</sub> falling                          | V <sub>CC(on)</sub> V <sub>CC(off)</sub> V <sub>CC(HYS)</sub> V <sub>CC(reset)</sub> | 16.0<br>8.2<br>8<br>4 | 18.0<br>8.8<br>–<br>5 | 20.0<br>9.4<br>-<br>6 | V    |

| V <sub>CC</sub> Over Voltage Protection Threshold                                                                                     |                                                                                                      | $V_{CC(OVP)}$                                                                        | 25.5                  | 26.8                  | 28.5                  | V    |

| $V_{CC(off)}$ noise filter $V_{CC(reset)}$ noise filter                                                                               |                                                                                                      | $t_{VCC(off)}$<br>$t_{VCC(reset)}$                                                   |                       | 5<br>20               | -                     | μs   |

| Startup current                                                                                                                       |                                                                                                      | I <sub>CC(start)</sub>                                                               | -                     | 13                    | 30                    | μΑ   |

| Startup current in fault mode                                                                                                         |                                                                                                      | I <sub>CC(Fault)</sub>                                                               |                       | 58                    | 75                    | μΑ   |

| Supply Current Device Disabled/Fault Device Enabled/No output load on DRV pin Device Switching                                        | $V_{CC} > V_{CC(off)}$ $F_{sw} = 65 \text{ kHz}$ $C_{DRV} = 470 \text{ pF}, F_{sw} = 65 \text{ kHz}$ | I <sub>CC1</sub><br>I <sub>CC2</sub><br>I <sub>CC3</sub>                             | 0.8<br>_<br>_         | 1.0<br>2.6<br>3.0     | 1.2<br>4.0<br>4.5     | mA   |

| CURRENT SENSE                                                                                                                         |                                                                                                      |                                                                                      |                       |                       |                       |      |

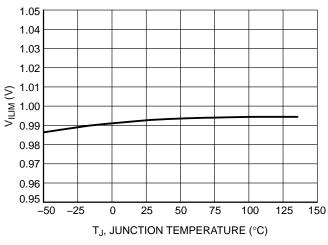

| Maximum Internal current limit                                                                                                        |                                                                                                      | $V_{ILIM}$                                                                           | 0.95                  | 1.00                  | 1.05                  | V    |

| Leading Edge Blanking Duration for V <sub>ILIM</sub>                                                                                  |                                                                                                      | t <sub>LEB</sub>                                                                     | 240                   | 300                   | 360                   | ns   |

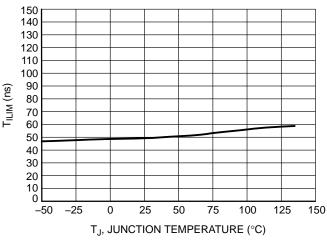

| Propagation delay from current detection to gate off–state                                                                            |                                                                                                      | t <sub>ILIM</sub>                                                                    | -                     | 100                   | 150                   | ns   |

- 6. Guaranteed by Design

- A NTC is generally placed between the SD and GND pins. Parameters R<sub>TF(start)</sub>, R<sub>TF(stop)</sub>, R<sub>OTP(off)</sub> and R<sub>OTP(on)</sub> give the resistance the NTC must exhibit to respectively, enter thermal foldback, stop thermal foldback, trigger the OTP limit and allow the circuit recovery after an OTP situation.

- 8. At startup, when  $V_{CC}$  reaches  $V_{CC(on)}$ , the controller blanks OTP for more than 250  $\mu$ s to avoid detecting an OTP fault by allowing the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin.

$\begin{tabular}{ll} \textbf{Table 4. ELECTRICAL CHARACTERISTICS} & (Unless otherwise noted: For typical values $T_J=25^{\circ}C$, $V_{CC}=12$ V, $V_{ZCD}=0$ V, $V_{CS}=0$ V, $V_{SD}=1.5$ V) For min/max values $T_J=-40^{\circ}C$ to $+125^{\circ}C$, $V_{CC}=12$ V) $ (V_{CS}=1.5)$ V (V_{$

| Description                                                    | Test Condition                                                                                     | Symbol                               | Min            | Тур            | Max            | Unit |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------|----------------|----------------|----------------|------|

| CURRENT SENSE                                                  |                                                                                                    |                                      |                |                |                |      |

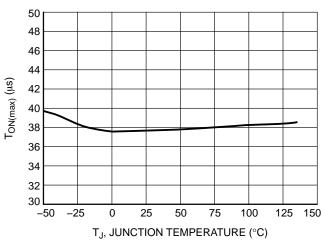

| Maximum on-time                                                |                                                                                                    | t <sub>on(MAX)</sub>                 | 26             | 36             | 46             | μS   |

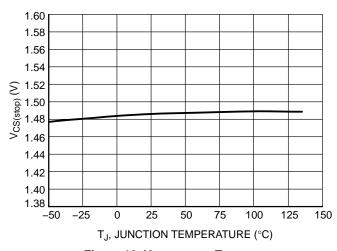

| Threshold for immediate fault protection activation            |                                                                                                    | V <sub>CS(stop)</sub>                | 1.35           | 1.50           | 1.65           | V    |

| Leading Edge Blanking Duration for V <sub>CS(stop)</sub>       |                                                                                                    | t <sub>BCS</sub>                     | _              | 150            | -              | ns   |

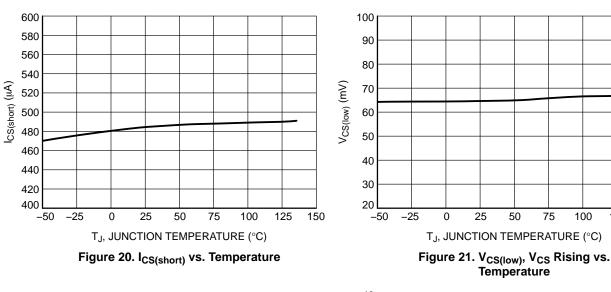

| Current source for CS to GND short detection                   |                                                                                                    | I <sub>CS(short)</sub>               | 400            | 500            | 600            | μΑ   |

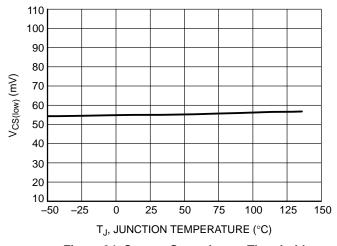

| Current sense threshold for CS to GND short detection          | V <sub>CS</sub> rising                                                                             | V <sub>CS(low)</sub>                 | 30             | 65             | 100            | mV   |

| GATE DRIVE                                                     |                                                                                                    |                                      |                |                |                |      |

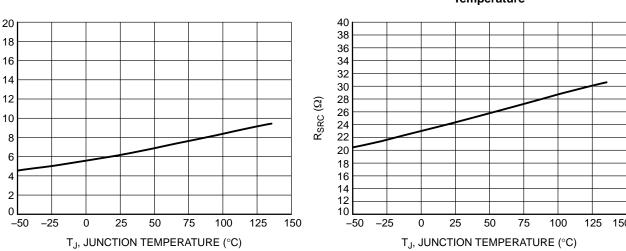

| Drive Resistance<br>DRV Sink<br>DRV Source                     |                                                                                                    | R <sub>SNK</sub><br>R <sub>SRC</sub> | _<br>_         | 13<br>30       | -<br>-         | Ω    |

| Drive current capability DRV Sink (Note 6) DRV Source (Note 6) |                                                                                                    | I <sub>SNK</sub><br>I <sub>SRC</sub> | -<br>-         | 500<br>300     | -<br>-         | mA   |

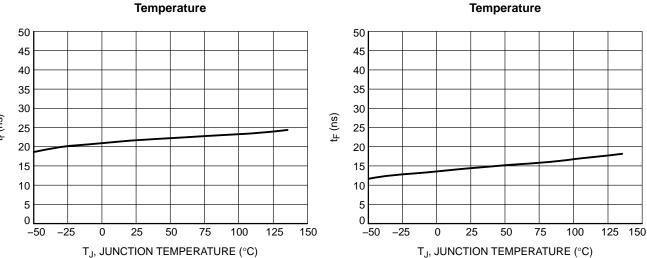

| Rise Time (10% to 90%)                                         | C <sub>DRV</sub> = 470 pF                                                                          | t <sub>r</sub>                       | -              | 40             | -              | ns   |

| Fall Time (90% to 10%)                                         | C <sub>DRV</sub> = 470 pF                                                                          | t <sub>f</sub>                       | -              | 30             | -              | ns   |

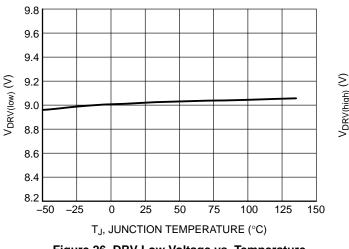

| DRV Low Voltage                                                | $V_{CC} = V_{CC(off)} + 0.2 \text{ V}$<br>$C_{DRV} = 470 \text{ pF}, R_{DRV} = 33 \text{ k}\Omega$ | $V_{DRV(low)}$                       | 8              | _              | -              | V    |

| DRV High Voltage                                               | $V_{CC} = V_{CC(MAX)}$ $C_{DRV} = 470 \text{ pF}, R_{DRV} = 33 \text{ k}\Omega$                    | $V_{DRV(high)}$                      | 10             | 12             | 14             | V    |

| ZERO VOLTAGE DETECTION CIRCUIT                                 |                                                                                                    |                                      |                |                |                |      |

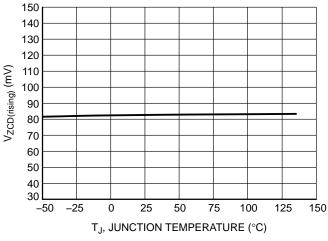

| Upper ZCD threshold voltage                                    | V <sub>ZCD</sub> rising                                                                            | V <sub>ZCD(rising)</sub>             | -              | 90             | 150            | mV   |

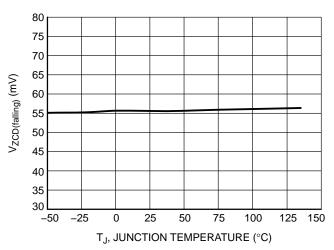

| Lower ZCD threshold voltage                                    | V <sub>ZCD</sub> falling                                                                           | V <sub>ZCD(falling)</sub>            | 35             | 55             | -              | mV   |

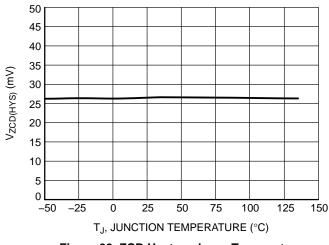

| ZCD hysteresis                                                 |                                                                                                    | V <sub>ZCD(HYS)</sub>                | 15             | -              | -              | mV   |

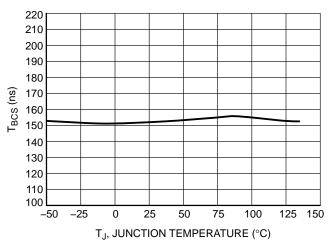

| Propagation Delay from valley detection to DRV high            | V <sub>ZCD</sub> falling                                                                           | T <sub>DEM</sub>                     | -              | 100            | 300            | ns   |

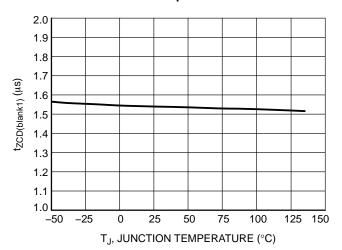

| Blanking delay after on-time                                   | V <sub>REFX</sub> > 30% V <sub>REF</sub>                                                           | T <sub>ZCD(blank1)</sub>             | 1.12           | 1.50           | 1.88           | μS   |

| Blanking delay at light load                                   | V <sub>REFX</sub> < 25% V <sub>REF</sub>                                                           | T <sub>ZCD(blank2)</sub>             | 0.56           | 0.75           | 0.94           | μs   |

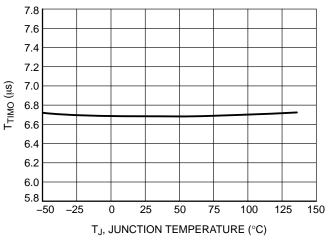

| Timeout after last DEMAG transition                            |                                                                                                    | T <sub>TIMO</sub>                    | 5.0            | 6.5            | 8.0            | μs   |

| Pulling-down resistor                                          | $V_{ZCD} = V_{ZCD(falling)}$                                                                       | R <sub>ZCD(PD)</sub>                 | -              | 200            | -              | kΩ   |

| CONSTANT CURRENT AND POWER FACTOR CO                           | ONTROL                                                                                             |                                      |                |                |                |      |

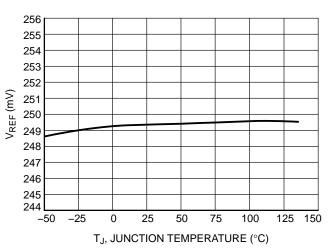

| Reference Voltage at T <sub>J</sub> = 25°C                     | A and B versions<br>C and D versions                                                               | $V_{REF}$                            | 245<br>195     | 250<br>200     | 255<br>205     | mV   |

| Reference Voltage T <sub>J</sub> = 25°C to 100°C               | A and B versions<br>C and D versions                                                               | V <sub>REF</sub>                     | 242.5<br>192.5 | 250.0<br>200.0 | 257.5<br>207.5 | mV   |

| Reference Voltage $T_J = -40^{\circ}C$ to $125^{\circ}C$       | A and B versions<br>C and D versions                                                               | $V_{REF}$                            | 240<br>190     | 250<br>200     | 260<br>210     | mV   |

| Current sense lower threshold                                  | V <sub>CS</sub> falling                                                                            | V <sub>CS(low)</sub>                 | 20             | 50             | 100            | mV   |

| V <sub>control</sub> to current setpoint division ratio        |                                                                                                    | V <sub>ratio</sub>                   | -              | 4              | _              | _    |

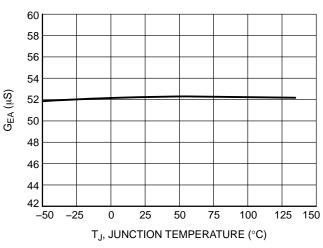

| Error amplifier gain                                           | V <sub>REFX</sub> = V <sub>REF</sub>                                                               | G <sub>EA</sub>                      | 40             | 50             | 60             | μS   |

<sup>6.</sup> Guaranteed by Design

A NTC is generally placed between the SD and GND pins. Parameters R<sub>TF(start)</sub>, R<sub>TF(stop)</sub>, R<sub>OTP(off)</sub> and R<sub>OTP(on)</sub> give the resistance the NTC must exhibit to respectively, enter thermal foldback, stop thermal foldback, trigger the OTP limit and allow the circuit recovery after an OTP situation.

<sup>8.</sup> At startup, when  $V_{CC}$  reaches  $V_{CC(on)}$ , the controller blanks OTP for more than 250  $\mu$ s to avoid detecting an OTP fault by allowing the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin.

**Table 4. ELECTRICAL CHARACTERISTICS** (Unless otherwise noted: For typical values  $T_J = 25^{\circ}C$ ,  $V_{CC} = 12$  V,  $V_{ZCD} = 0$  V,  $V_{CS} = 0$  V,  $V_{SD} = 1.5$  V) For min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 12$  V)

| Description                                                                             | Test Condition                                                   | Symbol                   | Min  | Тур         | Max  | Unit |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------|------|-------------|------|------|

| CONSTANT CURRENT AND POWER FACTOR CONTROL                                               |                                                                  |                          |      |             |      |      |

| Error amplifier current capability                                                      | $V_{REFX} = V_{REF}$ (no dimming)<br>$V_{REFX} = 25\%^* V_{REF}$ | I <sub>EA</sub>          |      | ±60<br>±240 |      | μΑ   |

| COMP Pin Start-up Current Source                                                        | COMP pin grounded                                                | I <sub>EA_STUP</sub>     |      | 140         |      | μΑ   |

| LINE FEED FORWARD                                                                       |                                                                  |                          |      |             |      |      |

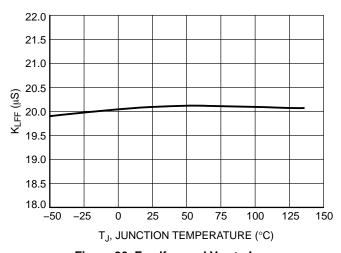

| V <sub>VS</sub> to I <sub>CS(offset)</sub> conversion ratio                             |                                                                  | K <sub>LFF</sub>         | 18   | 20          | 22   | μS   |

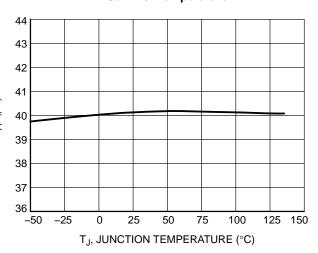

| Line feed-forward current on CS pin                                                     | DRV high, V <sub>VS</sub> = 2 V                                  | I <sub>FF</sub>          | 35   | 40          | 45   | μΑ   |

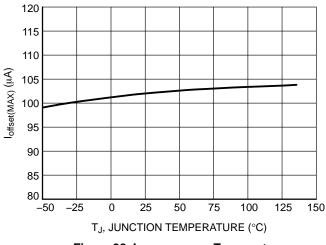

| Offset current maximum value                                                            |                                                                  | I <sub>offset(MAX)</sub> | 80   | 100         | 120  | μΑ   |

| VALLEY LOCKOUT SECTION                                                                  |                                                                  |                          |      |             |      |      |

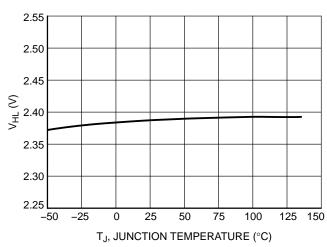

| Threshold for high- line range (HL) detection                                           | V <sub>VS</sub> rising                                           | $V_{HL}$                 | 2.28 | 2.40        | 2.52 | V    |

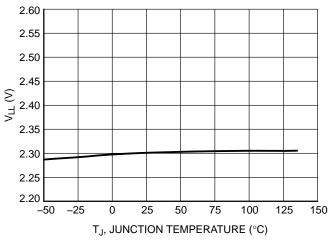

| Threshold for low–line range (LL) detection                                             | V <sub>VS</sub> falling                                          | $V_{LL}$                 | 2.18 | 2.30        | 2.42 | V    |

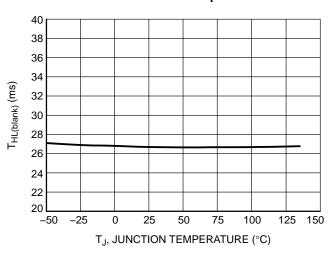

| Blanking time for line range detection                                                  |                                                                  | t <sub>HL(blank)</sub>   | 15   | 25          | 35   | ms   |

| FREQUENCY FOLDBACK                                                                      |                                                                  |                          |      |             |      |      |

| Minimum additional dead time in frequency fold-<br>back mode                            |                                                                  | t <sub>FF1LL</sub>       | 1.4  | 2.0         | 2.6  | μS   |

| Additional dead time                                                                    | V <sub>REFX</sub> = 5% V <sub>REF</sub>                          | t <sub>FF2HL</sub>       | _    | 40          | -    | μs   |

| Additional dead time                                                                    | V <sub>REFX</sub> = 0% V <sub>REF</sub>                          | t <sub>FF3HL</sub>       | 90   |             | -    | μs   |

| FAULT PROTECTION                                                                        |                                                                  |                          |      |             |      |      |

| Thermal Shutdown (Note 6)                                                               | F <sub>SW</sub> = 65 kHz                                         | T <sub>SHDN</sub>        | 130  | 150         | 170  | °C   |

| Thermal Shutdown Hysteresis                                                             |                                                                  | T <sub>SHDN(HYS)</sub>   | _    | 50          | -    | °C   |

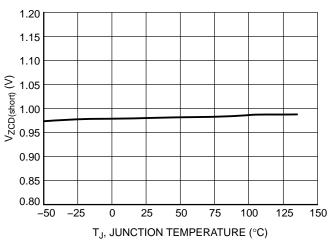

| Threshold voltage for output short circuit or aux. winding short circuit detection      |                                                                  | V <sub>ZCD(short)</sub>  | 0.8  | 1.0         | 1.2  | V    |

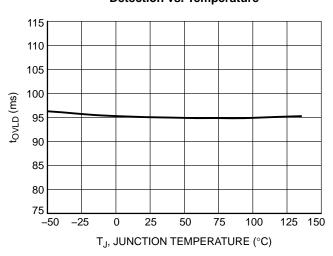

| Short circuit detection Timer                                                           | $V_{ZCD} < V_{ZCD(short)}$                                       | t <sub>OVLD</sub>        | 70   | 90          | 110  | ms   |

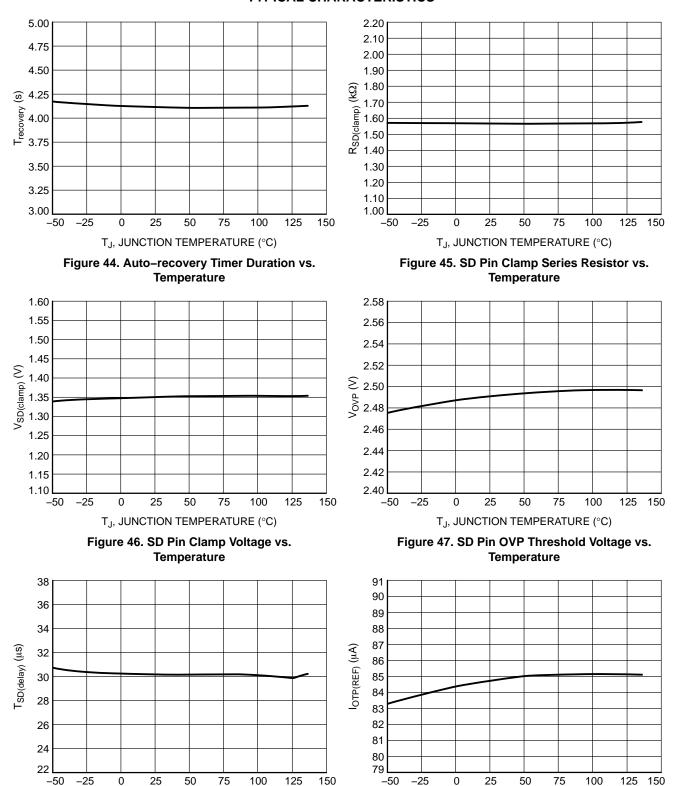

| Auto-recovery timer duration                                                            |                                                                  | t <sub>recovery</sub>    | 3    | 4           | 5    | S    |

| SD pin Clamp series resistor                                                            |                                                                  | R <sub>SD(clamp)</sub>   |      | 1.6         |      | kΩ   |

| Clamped voltage                                                                         | SD pin open                                                      | V <sub>SD(clamp)</sub>   | 1.13 | 1.35        | 1.57 | V    |

| SD pin detection level for OVP                                                          | V <sub>SD</sub> rising                                           | V <sub>OVP</sub>         | 2.35 | 2.50        | 2.65 | V    |

| Delay before OVP or OTP confirmation                                                    |                                                                  | T <sub>SD(delay)</sub>   | 22.5 | 30.0        | 37.5 | μs   |

| Reference current for direct connection of an NTC (Note 8)                              |                                                                  | I <sub>OTP(REF)</sub>    | 80   | 85          | 90   | μΑ   |

| Fault detection level for OTP (Note 7)                                                  | V <sub>SD</sub> falling                                          | V <sub>OTP(off)</sub>    | 0.47 | 0.50        | 0.53 | V    |

| SD pin level for operation recovery after an OTP detection                              | V <sub>SD</sub> rising                                           | V <sub>OTP(on)</sub>     | 0.66 | 0.70        | 0.74 | V    |

| OTP blanking time when circuit starts operating (Note 8)                                |                                                                  | t <sub>OTP(start)</sub>  | 250  |             | 370  | μS   |

| SD pin voltage where thermal fold–back starts (V <sub>REF</sub> is decreased)           |                                                                  | V <sub>TF(start)</sub>   | 0.94 | 1.00        | 1.06 | V    |

| SD pin voltage at which thermal fold–back stops ( $V_{REF}$ is clamped to $V_{REF50}$ ) |                                                                  | V <sub>TF(stop)</sub>    | 0.64 | 0.69        | 0.74 | V    |

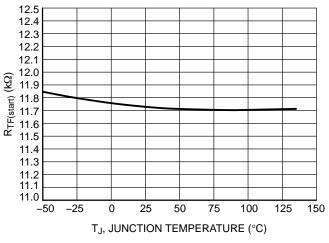

| V <sub>TF(start)</sub> over I <sub>OTP(REF)</sub> ratio (Note 7)                        | $T_J = +25^{\circ}C \text{ to } +125^{\circ}C$                   | R <sub>TF(start)</sub>   | 10.8 | 11.7        | 12.6 | kΩ   |

<sup>6.</sup> Guaranteed by Design

<sup>7.</sup> A NTC is generally placed between the SD and GND pins. Parameters R<sub>TF(start)</sub>, R<sub>TF(stop)</sub>, R<sub>OTP(off)</sub> and R<sub>OTP(on)</sub> give the resistance the NTC must exhibit to respectively, enter thermal foldback, stop thermal foldback, trigger the OTP limit and allow the circuit recovery after an OTP situation

an OTP situation.

At startup, when V<sub>CC</sub> reaches V<sub>CC(on)</sub>, the controller blanks OTP for more than 250 μs to avoid detecting an OTP fault by allowing the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin.

| Description                                                                        | Test Condition                                 | Symbol                   | Min  | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------|------------------------------------------------|--------------------------|------|------|------|------|

| FAULT PROTECTION                                                                   |                                                | •                        | •    | •    | •    | •    |

| V <sub>TF(stop)</sub> over I <sub>OTP(REF)</sub> ratio (Note 7)                    | $T_J = +25^{\circ}C \text{ to } +125^{\circ}C$ | R <sub>TF(stop)</sub>    | 7.4  | 8.1  | 8.8  | kΩ   |

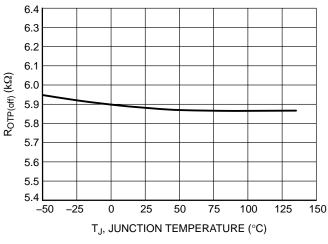

| V <sub>OTP(off)</sub> over I <sub>OTP(REF)</sub> ratio (Note 7)                    | $T_J = +25^{\circ}C \text{ to } +125^{\circ}C$ | R <sub>OTP(off)</sub>    | 5.4  | 5.9  | 6.4  | kΩ   |

| V <sub>OTP(on)</sub> over I <sub>OTP(REF)</sub> ratio (Note 7)                     | $T_J = +25^{\circ}C \text{ to } +125^{\circ}C$ | R <sub>OTP(on)</sub>     | 7.5  | 8.1  | 8.7  | kΩ   |

| $V_{REFX} @ V_{SD} = 600 \text{ mV}$ (as percentage of $V_{REF}$ )                 | SD pin falling (no OTP detection)              | V <sub>REF(50)</sub>     | 40   | 50   | 60   | %    |

| BROWN-OUT                                                                          |                                                | •                        |      |      |      |      |

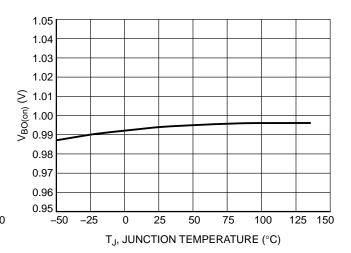

| Brown-Out ON level (IC start pulsing)                                              | V <sub>S</sub> rising                          | V <sub>BO(on)</sub>      | 0.95 | 1.00 | 1.05 | V    |

| Brown-Out OFF level (IC shuts down)                                                | V <sub>S</sub> falling                         | V <sub>BO(off)</sub>     | 0.85 | 0.90 | 0.95 | V    |

| BO comparators delay                                                               |                                                | t <sub>BO(delay)</sub>   |      | 30   |      | μs   |

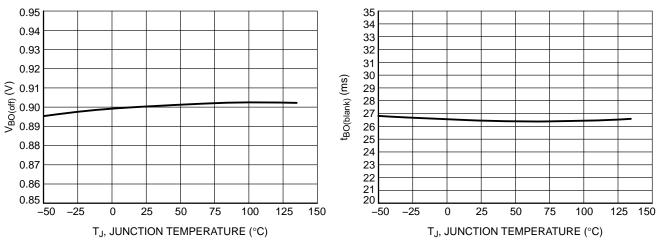

| Brown-Out blanking time                                                            |                                                | t <sub>BO(blank)</sub>   | 15   | 25   | 35   | ms   |

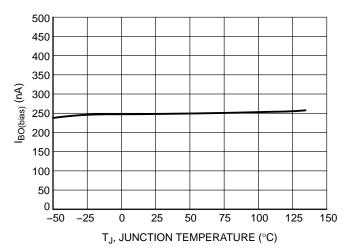

| V <sub>S</sub> pin Pulling-down Current                                            | $V_S = V_{BO(on)}$                             | I <sub>BO(bias)</sub>    | 50   | 250  | 450  | nA   |

| DIMMING SECTION                                                                    |                                                |                          |      |      |      |      |

| DIM pin voltage for zero output current (OFF voltage)                              | V <sub>DIM</sub> falling                       | V <sub>DIMO</sub>        | 0.66 | 0.70 | 0.74 | V    |

| DIM pin voltage for maximum output current (V <sub>REFX</sub> = V <sub>REF</sub> ) | V <sub>DIM</sub> rising                        | V <sub>DIM100</sub>      | -    | 2.45 | 2.60 | V    |

| DIM pin voltage for 50% output current (V <sub>REFX</sub> = 125 mV)                | V <sub>DIM</sub> rising or falling             | V <sub>DIM50</sub>       | 1.35 | 1.57 | 1.75 | V    |

| Dimming range                                                                      |                                                | V <sub>DIM(range)</sub>  |      | 1.75 |      | V    |

| Dimming pin pull-up current source                                                 |                                                | I <sub>DIM(pullup)</sub> | 7.5  | 9.6  | 12   | μΑ   |

<sup>6.</sup> Guaranteed by Design

A NTC is generally placed between the SD and GND pins. Parameters R<sub>TF(start)</sub>, R<sub>TF(stop)</sub>, R<sub>OTP(off)</sub> and R<sub>OTP(on)</sub> give the resistance the NTC must exhibit to respectively, enter thermal foldback, stop thermal foldback, trigger the OTP limit and allow the circuit recovery after an OTP situation.

At startup, when V<sub>CC</sub> reaches V<sub>CC(on)</sub>, the controller blanks OTP for more than 250 μs to avoid detecting an OTP fault by allowing the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin.

9.4 9.3

9.2

9.1 9.0 Vcc(off) (V) 8.9 8.8 8.7 8.6 8.5 8.4 8.3 8.2 125 150 -50 -25 25 75 100 50 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

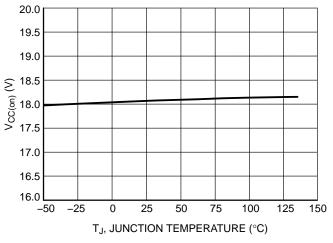

Figure 4. V<sub>CC</sub> Start-up Threshold vs. Temperature

Figure 5. V<sub>CC</sub> Minimum Operating Voltage vs. Temperature

Figure 6. Hysteresis (V<sub>CC(on)</sub> – V<sub>CC(off)</sub>) vs. Temperature

Figure 7. V<sub>CC(reset)</sub> vs. Temperature

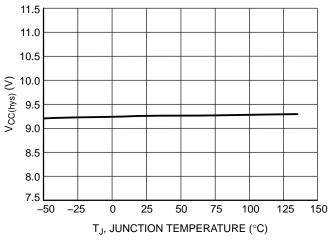

#### **TYPICAL CHARACTERISTICS**

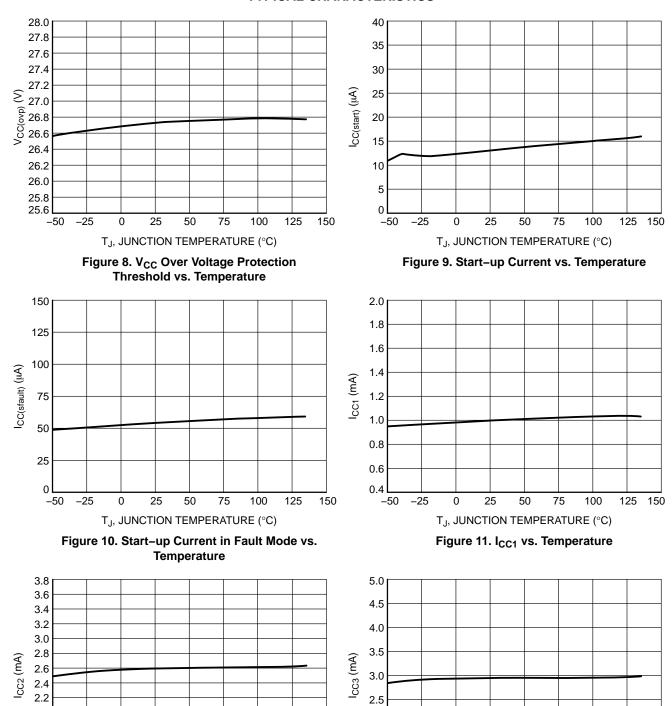

T<sub>J</sub>, JUNCTION TEMPERATURE (°C) **Figure 12. I<sub>CC2</sub> vs. Temperature**

50

75

100

2.0

1.8 1.6

1.4 1.2

-50

-25

T<sub>J</sub>, JUNCTION TEMPERATURE (°C) **Figure 13. I<sub>CC3</sub> vs. Temperature**

50

75

100

150

125

25

150

2.0

1.5

1.0

-50

-25

#### **TYPICAL CHARACTERISTICS**

400 380

360 340 320 300 280 260 240 220 200 25 125 150 -50 -2550 75 100 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 14. Maximum Internal Current Limit vs. Temperature

Figure 15. Leading Edge Blanking vs. Temperature

Figure 16. Current Limit Propagation Delay vs. Temperature

Figure 17. Maximum On-time vs. Temperature

Figure 18. V<sub>CS(stop)</sub> vs. Temperature

Figure 19. Leading Edge Blanking Duration for  $V_{CS(stop)}$  vs. Temperature

#### **TYPICAL CHARACTERISTICS**

Figure 22. Sink Gate Drive Resistance vs. **Temperature**

R<sub>SNK</sub> (Ω)

Figure 24. Gate Drive Rise Time vs. **Temperature**

Figure 25. Gate Drive Fall Time (C<sub>DRV</sub> = 470 pF) vs. Temperature

Figure 23. Source Gate Drive Resistance vs.

100

125 150

15.0 14.5 14.0 13.5 (V) (high) (V) 13.0 12.5 12.0 11.5 11.0 10.5 10.0 -25 25 50 75 100 125 150 -50 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 26. DRV Low Voltage vs. Temperature

Figure 27. DRV High Voltage vs. Temperature

Figure 28. Upper ZCD Threshold Voltage vs. Temperature

Figure 29. Lower ZCD Threshold vs. Temperature

Figure 30. ZCD Hysteresis vs. Temperature

Figure 31. ZCD Blanking Delay vs. Temperature

Figure 32. ZCD Time-out vs. Temperature

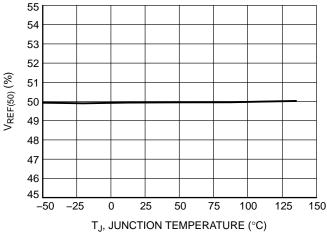

Figure 33. Reference Voltage vs. Temperature (A and B versions)

Figure 34. Current Sense Lower Threshold (V<sub>CS</sub> Falling) vs. Temperature

Figure 35. Error Amplifier Trans-conductance

Gain vs. Temperature

Figure 36. Feedforward  $V_{VS}$  to  $I_{CS(offset)}$  Conversion Ratio vs. Temperature

Figure 37. Line Feedforward Current on CS Pin (@ V<sub>VS</sub> = 2 V) vs. Temperature

Figure 38. I<sub>offset(MAX)</sub> vs. Temperature

Figure 39. Threshold for High-line Range Detection vs. Temperature

Figure 40. Threshold for Low-line Range Detection vs. Temperature

Figure 41. Blanking Time for Low-line Range Detection vs. Temperature

Figure 42. Threshold Voltage for Output Short Circuit Detection vs. Temperature

Figure 43. Short Circuit Detection Timer vs.

Temperature

$T_J$ , JUNCTION TEMPERATURE (°C) Figure 48.  $T_{SD(delay)}$  vs. Temperature

T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 49. I<sub>OTP(REF)</sub> vs. Temperature

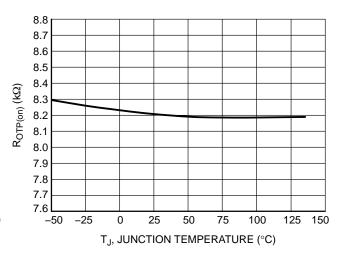

8.8 8.7 8.6 8.5 8.4  $R_{TF(stop)}$  (k $\Omega$ ) 8.3 8.2 8.1 8.0 7.9 7.8 7.7 7.6 -25 125 150 -50 25 50 75 100 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 50. R<sub>TF(start)</sub> vs. Temperature

Figure 51. R<sub>TF(stop)</sub> vs. Temperature

Figure 52. R<sub>OTP(off)</sub> vs. Temperature

Figure 53. R<sub>OTP(on)</sub> vs. Temperature

Figure 54. Ratio  $V_{REF(50)}$  over  $V_{REF}$  vs. Temperature

Figure 55. Brown-out ON Level vs.

Temperature

Figure 56. Brown-out OFF Level vs. Temperature

Figure 57. Brown-out Blanking Time vs. Temperature

Figure 58. V<sub>S</sub> Pin Pulling-down Current vs. Temperature

#### **Application Information**

The NCL30086 is a driver for power–factor corrected flyback and non–isolated buck–boost/ SEPIC converters. It implements a current–mode, quasi–resonant architecture including valley lockout and frequency fold–back capabilities for maintaining high–efficiency performance over a wide load range. A proprietary circuitry ensures both accurate regulation of the output current (without the need for a secondary–side feedback) and near–unity power factor correction. The circuit contains a suite of powerful protections to ensure a robust LED driver design without the need of extra external components or overdesign

- Quasi–Resonance Current–Mode Operation: implementing quasi–resonance operation in peak current–mode control, the NCL30086 optimizes the efficiency by turning on the MOSFET when its drain–source voltage is minimal (valley). In light–load conditions, the circuit changes valleys to reduce the switching losses. For a stable operation, the valley at which the MOSFET switches on remains locked until the input voltage or the output current set–point significantly changes.

- Primary-Side Constant-Current Control with

Power Factor Correction: a proprietary circuitry allows the LED driver to achieve both near-unity power factor correction and accurate regulation of the output current without requiring any secondary-side feedback (no optocoupler needed). A power factor as high as 0.99 and an output current deviation below ±2% are typically obtained.

- Linear or PWM dimming: the DIM pin allows implementing both analog and PWM dimming.

- Main protection features:

- Over Temperature Thermal Fold-back/

Shutdown/Over Voltage Protection: the

NCL30086 features a gradual current foldback to

protect the driver from excessive temperature down

to 50% of the programmed current. If the

temperature continues to rise after this point to a

second level, the controller stops operating. This

mode would only be expected to be reached under

normal conditions if there is a severe fault. The first

and second temperature thresholds depend on the

- NTC connected to the circuit SD pin. The SD pin can also be used to shutdown the device by pulling this pin below the V<sub>OTP(off)</sub> min level. A Zener diode can also be used to pull–up the pin and stop the controller for adjustable OVP protection. Both protections are latching–off (A and C versions) or auto–recovery (the circuit can recover operation after 4–s delay has elapsed B and D versions).

- Cycle-by-cycle peak current limit: when the current sense voltage exceeds the internal threshold V<sub>ILIM</sub>, the MOSFET is immediately turned off.

- Winding or Output Diode Short–Circuit

Protection: an additional comparator senses the CS signal and stops the controller if it exceeds 150% x V<sub>ILIM</sub> for 4 consecutive cycles. This feature can protect the converter if a winding is shorted or if the output diode is shorted or simply if the transformer saturates. This protection is latching–off (A and C versions) or auto–recovery (B and D versions).

- Output Short-circuit protection: if the ZCD pin voltage remains low for a 90-ms time interval, the controller detects that the output or the ZCD pin is grounded and hence, stops operation. This protection is latching-off (A and C versions) or auto-recovery (B and D versions).

- Open LED protection: if the V<sub>CC</sub> pin voltage exceeds the OVP threshold, the controller shuts down and waits 4 seconds before restarting switching operation.

- Floating or Short Pin Detection: NCL30086

protections aid in pass safety tests. For instance, the

circuit stops operating when the CS pin is grounded

or open.

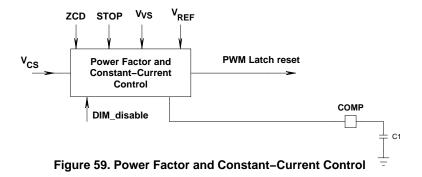

#### **Power Factor and Constant Current Control**

The NCL30086 embeds an analog/digital block to control the power factor and regulate the output current by monitoring the ZCD,  $V_S$  and CS pin voltages (signals ZCD,  $V_S$  and  $V_{CS}$  of Figure 59). This circuitry generates the current setpoint ( $V_{CONTROL}/4$ ) and compares it to the current sense signal ( $V_{CS}$ ) to dictate the MOSFET turning off event when  $V_{CS}$  exceeds  $V_{CONTROL}/4$ .

The  $V_S$  pin provides the sinusoidal reference necessary for shaping the input current. The obtained current reference is further modulated so that when averaged over a half–line period, it is equal to the output current reference ( $V_{REFX}$ ). This averaging process is made by an internal Operational Trans–conductance Amplifier (OTA) and the capacitor connected to the COMP pin (C1 in Figure 59). Typical COMP capacitance is 2.2  $\mu$ F and should not be less than 1  $\mu$ F to ensure stability. The COMP ripple does not affect the power factor performance as the circuit digitally eliminates it when generating the current setpoint.

If the  $V_S$  pin properly conveys the sinusoidal shape, power factor will be close to 1. Also, the Total Harmonic Distortion (THD) will be low, especially if the output voltage ripple is small. In any case, the output current will be well regulated following the equation below:

$$I_{out} = \frac{V_{REFX}}{2N_{PS}R_{sense}}$$

(eq. 1)

Where:

- $N_{PS}$  is the secondary to primary transformer turns  $N_{PS} = N_S / N_P$

- R<sub>sense</sub> is the current sense resistor (see Figure 1).

- V<sub>REFX</sub> is the output current internal reference. V<sub>REFX</sub> = V<sub>REF</sub> (250 mV in A and B versions and 200 mV in C and D versions, typically) at full load.

The output current reference ( $V_{REFX}$ ) is  $V_{REF}$  unless thermal fold–back is activated by the SD pin voltage being reduced below 1 V typical (see "protections" section) or unless the DIM pin voltage is below  $V_{DIM100}$  (see analog dimming section).

If a major fault is detected, the circuit enters the latched-off or auto-recovery mode and the COMP pin is grounded (except in an UVLO condition). This ensures a clean start-up when the circuit resumes operation.

#### Start-up Sequence

Generally an LED lamp is expected to emit light in < 1 sec and typically within 300 ms. The start—up phase consists of

the time to charge the  $V_{CC}$  capacitor, initiate startup and begin switching and the time to charge the output capacitor until sufficient current flows into the LED string. To speed-up this phase, the following defines the start-up sequence:

- The COMP pin is grounded when the circuit is off. The average COMP voltage needs to exceed the V<sub>S</sub> pin peak value to have the LED current properly regulated (whatever the current target is). To speed—up the COMP capacitance charge and shorten the start—up phase, an internal 80-μA current source adds to the OTA sourced current (60 μA max typically) to charge up the COMP capacitance. The 80-μA current source remains on until the OTA starts to sink current as a result of the COMP pin voltage sufficient rise. At that moment, the COMP pin being near its steady-state value, it is only driven by the OTA.

- If V<sub>CC</sub> drops below the V<sub>CC(off)</sub> threshold because the circuit fails to start—up properly on the first attempt, a new attempt takes place as soon as V<sub>CC</sub> is recharged to V<sub>CC(on)</sub>. The COMP voltage is not reset at that moment. Instead, the new attempt starts with the COMP level obtained at the end of the previous operating phase.

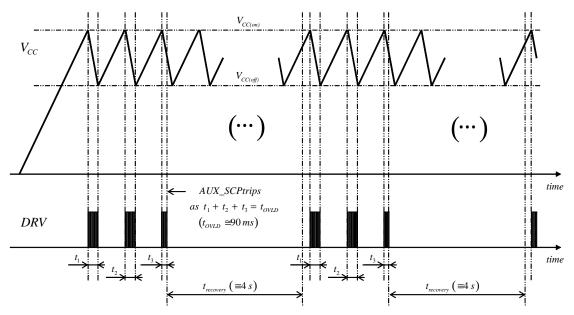

- If the load is shorted, the circuit will operate in hiccup mode with V<sub>CC</sub> oscillating between V<sub>CC(off)</sub> and V<sub>CC(on)</sub> until the AUX\_SCP protection trips (AUX\_SCP is triggered if the ZCD pin voltage does not exceed 1 V within a 90-ms operation period of time thus indicating a short to ground of the ZCD pin or an excessive load preventing the output voltage from rising). The NCL30086A and NCL3006C latch off in this case. With the B and D versions, the AUX\_SCP protection forces the 4-s auto-recovery delay to reduce the operation duty-ratio. Figure 60 illustrates a start-up sequence with the output shorted to ground, in this second case.

Figure 60. Start-up Sequence in a Load Short-circuit Situation (auto-recovery versions)

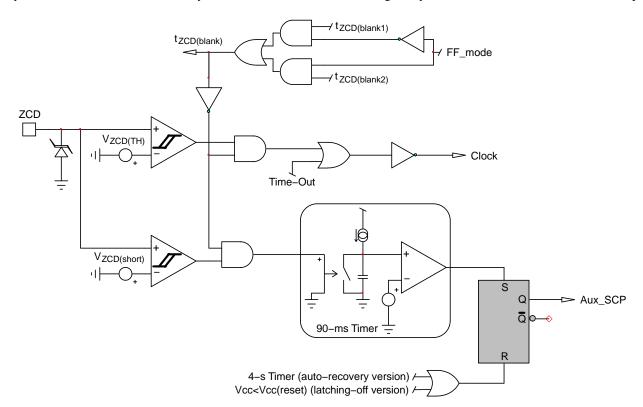

## **Zero Crossing Detection Block**

The ZCD pin detects when the drain-source voltage of the power MOSFET reaches a valley by crossing below the 55-mV internal threshold ( $V_{ZCD(TH)}$ ). At startup or in case of extremely damped free oscillations, the ZCD comparator may not be able to detect the valleys. To avoid such a

situation, the NCL30086 features a time—out circuit that generates pulses if the voltage on ZCD pin stays below the 55–mV threshold for 6.5 µs nominal. The time—out also acts as a substitute clock for the valley detection and simulates a missing valley in case the free oscillations are too damped.

Figure 61. Zero Current Detection Block

If the ZCD pin or the auxiliary winding happen to be shorted, the time–out function would normally make the controller keep switching and hence lead to improper LED current value. The "AUX\_SCP" protection prevents such a stressful operation: a secondary timer starts counting that is only reset when the ZCD voltage exceeds the V<sub>ZCD(short)</sub> threshold (1 V typically). If this timer reaches 90 ms (no ZCD voltage pulse having exceeded V<sub>ZCD(short)</sub> for this time period), the controller detects a fault and stops operation for 4 seconds (B and D versions) or latches off (A and C versions).

The "clock" shown in Figure 61 is used by the "valley selection frequency foldback" circuitry of the block diagram (Figure 3), to generate the next DRV pulse (if no fault prevents it):

• Immediately when the clock occurs in QR mode at low line or valley 2 at high line (full load)

After the appropriate number of "clock" pulses in thermal foldback mode

For an optimal operation, the maximum ZCD level should be maintained below 5 V to stay safely below the built in clamping voltage of the pin.

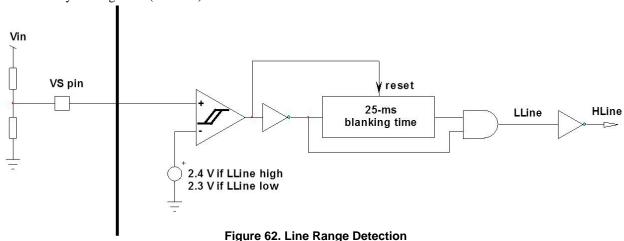

#### **Line Range Detection**

As sketched in Figure 62, this circuit detects the low–line range if the  $V_S$  pin remains below the  $V_{LL}$  threshold (2.3 V typical) for more than the 25–ms blanking time. High–line is detected as soon as the  $V_S$  pin voltage exceeds  $V_{HL}$  (2.4 V typical). These levels roughly correspond to 184–V rms and 192–V rms line voltages if the external resistors divider applied to the  $V_S$  pin is designed to provide a 1–V peak value at 80 V rms.

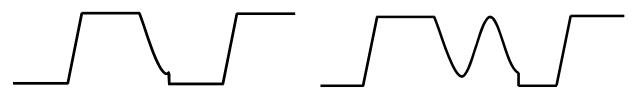

In the low-line range, conduction losses are generally dominant. Adding a dead-time would further increase these losses. Hence, only a short dead-time is necessary to reach the MOSFET valley. In high-line conditions, switching losses generally are the most critical. It is thus efficient to skip one valley to lower the switching frequency. Hence, under normal operation, the NCL30086 optimizes the

efficiency over the line range by turning on the MOSFET at the first valley in low-line conditions and at the second valley in the high-line case. This is illustrated by Figure 63 that sketches the MOSFET Drain-Source voltage in both cases. In the event that thermal foldback is activated, additional valleys can be skipped as the power is reduced.

Figure 63. Full-load Operation - Quasi-resonant Mode in low line (left), turn on at valley 2 when in high line (right)

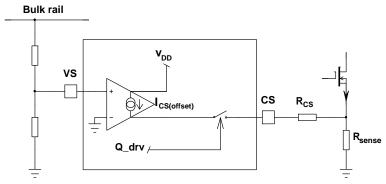

#### Line Feedforward

To compensate for current regulation errors due to AC line variation, the NCL30086 includes a method to add line feedforward adjustment. As illustrated by Figure 64, the input voltage is sensed by the  $V_S$  pin and converted into a

current. By adding an external resistor in series between the sense resistor and the CS pin, a voltage offset proportional to the input voltage is added to the CS signal for the MOSFET on-time.

Figure 64. Line Feed-Forward Schematic

In Figure 64, Q\_drv designates the output of the PWM latch which is high for the on-time and low otherwise.

#### **PWM or Linear Dimming Detection**

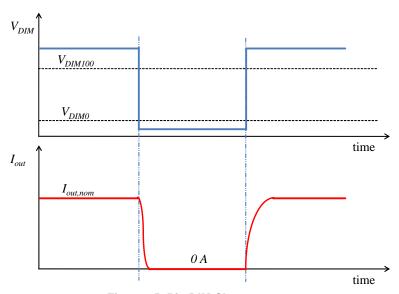

The DIM pin of the NCL30086 is provided to implement linear and/or PWM dimming of the LED current.

Applying a voltage on the DIM pin voltage ( $V_{DIM}$ ) forces the output current internal reference to operate in one of three regions:

$$V_{REFX} = 0$$

if  $V_{DIM} \le V_{DIM0}$  (eq.

$$V_{REFX} = V_{REF}$$

if  $V_{DIM} \ge V_{DIM100}$

$$V_{REFX} = \frac{V_{DIM} - V_{DIM0}}{V_{DIM100} - V_{DIM0}} V_{REF}$$

otherwise

$V_{DIM0}$  and  $V_{DIM100}$  respectively, are 0.7 V and 2.45 V typically.

The output current can then be controlled by the DIM pin as follows:

$$\begin{split} &I_{out} = 0 & \text{if } V_{DIM} \leq V_{DIM0} \text{ (eq. 3)} \\ &I_{out} = I_{out,nom} = \frac{V_{REF}}{2 \ N_{PS} R_{sense}} & \text{if } V_{DIM} \geq V_{DIM100} \\ &I_{out} = \frac{V_{DIM} - V_{DIM0}}{V_{DIM100} - V_{DIM0}} I_{out,nom} & \text{otherwise} \end{split}$$

#### Where

- N<sub>PS</sub> is the secondary to primary transformer turns

N<sub>PS</sub> = N<sub>S</sub>/N<sub>P</sub>

- R<sub>sense</sub> is the current sense resistor (see Figure 1).

- V<sub>REF</sub> is the output current internal reference (250 mV typically)

- I<sub>out,nom</sub> is the full-load output current.

The DRV output is disabled whenever the DIM pin voltage is lower than  $V_{DIM0}$  and the output current setpoint is maximal when  $V_{DIM}$  exceeds  $V_{DIM100}.$  Thus, for PWM dimming, a PWM signal with a low–state value below  $V_{DIM0}$  and a high–state value above  $V_{DIM100}$  should be applied.

In this case, the output current will be:

$$I_{out} \cong I_{out,nom} \cdot d$$

(eq. 4)

Where d is the duty ratio of the DIM pin signal.

Figure 65. Pin DIM Chronograms

Notes:

• The current does not immediately reach its new target value when the PWM dimming signal state changes due to system time constants like the time necessary to charge or discharge the output capacitor to the required level. The output current settling time can hence affect the obtained output current, particularly if the PWM signal frequency is high.

• If either the high–state

$$(V_{DIM(high)})$$

or low–state level  $(V_{DIM(low)})$  of the input or both are between  $V_{DIM0}$  and  $V_{DIM100}$ , the output current will be proportionally reduced as both analog and PWM dimming are simultaneous active, thus the output current will be:

$$\begin{split} I_{out} &\cong \left(\frac{V_{DIM(high)} - V_{DIM0}}{V_{DIM100} - V_{DIM0}}d + \frac{V_{DIM(low)} - V_{DIM0}}{V_{DIM100} - V_{DIM0}}(1-d)\right) \\ I_{out} &\cong \frac{V_{DIM(high)} - V_{DIM0}}{V_{DIM100} - V_{DIM0}}d \cdot I_{out,nom} & \text{if } V_{DIM0} \leq V_{DIM(high)} \leq V_{DIM(high)} \leq V_{DIM(low)} \leq V_$$

$$\begin{split} &\text{if } V_{\text{DIM0}} \leq V_{\text{DIM(high)}} \leq V_{\text{DIM100}} \text{ and } V_{\text{DIM(low)}} \leq V_{\text{DIM0}} \\ &\text{if } V_{\text{DIM(high)}} \geq V_{\text{DIM100}} \text{ and } V_{\text{DIM0}} \leq V_{\text{DIM(low)}} \leq V_{\text{DIM100}} \end{split}$$

• If thermal foldback is activated as well, the current reduction is cumulative. For instance, if the DIM pin voltage and the thermal foldback respectively, reduces the output current setpoint by 50% and 20% respectively, the output current will be 80%\*50% that is 40% of its nominal level.

The DIM pin is pulled up internally by a 10-uA current source. Thus, if the pin is let open, the controller is able to start.

For any power factor corrected single stage architecture there will be a component of line ripple (100 / 120 Hz) on the output. If PWM dimming is used, it is recommended to select the dimming frequency to be sufficiently high not to generating beat frequencies that could create optical artifacts.

>> As a general rule, the minimum PWM frequency should be at least 2.5x the line ripple frequency and not be set near multiples of the line frequency.

#### **Protections**

The circuit incorporates a full suite of protection features listed below to make the LED driver very rugged.

#### **Output Short Circuit Situation**

An overload fault is detected if the ZCD pin voltage remains below V<sub>ZCD(short)</sub> for 90 ms. In such a situation, the circuit stops generating pulses until the 4-s delay auto-recovery time has elapsed (B and D versions) or latches off (A and C versions).

#### **Winding or Output Diode Short Circuit Protection**

If a transformer winding happens to be shorted, the primary inductance will collapse leading the current to ramp up in a very abrupt manner. The V<sub>ILIM</sub> comparator (current limitation threshold) will trip to open the MOSFET and eventually stop the current rise. However, because of the abnormally steep slope of the current, internal propagation delays and the MOSFET turn-off time, a current rise > 50% of the nominal maximum value set by V<sub>ILIM</sub> is possible. As illustrated in Figure 66, an additional circuit monitors for this current overshoot to detect a winding short circuit. The leading edge blanking (LEB) time for short circuit protection (LEB2) is significantly faster than the LEB time for cycle-by-cycle protection (LEB1). Practically, if four consecutive switching periods lead the CS pin voltage to exceed ( $V_{CS(stop)} = 150\% * V_{ILIM}$ ), the controller enters the auto-recovery mode (4-s operation interruption between active bursts with versions B and D) or latches off (versions A and C).

Figure 66. Winding Short Circuit Protection, Max. Peak Current Limit Circuits

## **V<sub>CC</sub>** Over Voltage Protection

The circuit stops generating pulses if  $V_{CC}$  exceeds  $V_{CC(OVP)}$  and enters auto-recovery mode. This feature protects the circuit in the event that the output LED string is disconnected or an individual LED in the string happens to fail open.

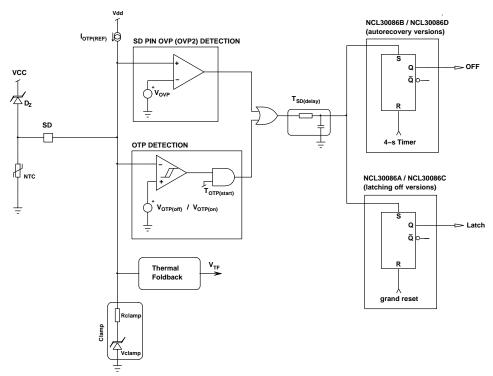

## **Programmable Over Voltage Protection (OVP2)**

In addition to the  $V_{CC}$  OVP protection, it is possible to connect a Zener diode between  $V_{CC}$  and the SD pin to implement programmable  $V_{CC}$  OVP monitoring (D<sub>Z</sub> of Figure 67). The triggering level is ( $V_{Z}+V_{OVP}$ ) where  $V_{OVP}$  is the 2.5–V internal threshold. If this protection trips, the NCL30086A and NCL30086C latch off while the NCL30086B and NCL30086D enter the auto–recovery mode.

Figure 67. Thermal Foldback and OVP/OTP Circuitry

The SD pin is clamped to about 1.35 V ( $V_{clamp}$ ) through a 1.6–k $\Omega$  resistor ( $R_{clamp}$ ). It is then necessary to inject about

$$\left(\frac{V_{OVP} - V_{clamp}}{R_{clamp}}\right)$$

that is

$$\left(\frac{2.50 - 1.35}{1.6 \text{ k}} \cong 700 \,\mu\text{A}\right)$$

typically, to trigger the OVP protection. This current helps ensure an accurate detection by using the Zener diode far from its knee region.

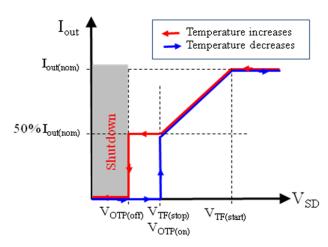

# Programmable Over Temperature Foldback Protection (OTP)

Connect an NTC between the SD pin and ground to detect an over–temperature condition. In response to a high temperature (detected if  $V_{SD}$  drops below  $V_{TF(start)}$ ), the circuit gradually reduces the LED current down to 50% (> 50% reduction in output power) of its initial value when  $V_{SD}$  reaches  $V_{TF(stop)}$ , in accordance with the characteristic of Figure 68 (Note 9).

At this point, if the temperature continues to rise and the secondary OTP level is reached, ( $V_{SD}$  drop below  $V_{OTP}$ ), the circuit latches off (A and C versions) or enters auto–recovery mode (B and D versions) and cannot resume operation until  $V_{SD}$  exceeds  $V_{OTP(on)}$  to provide some temperature hysteresis (around  $10^{\circ}\text{C}$  typically). The OTP thresholds nearly correspond to the following resistances of the NTC:

- Thermal foldback starts when  $R_{NTC} \le R_{TF(start)}$ (11.7 k $\Omega$ , typically)

- Thermal foldback stops when  $R_{NTC} \le R_{TF(stop)}$  (8.0 k $\Omega$ , typically)

- OTP triggers when  $R_{NTC} \le R_{OTP(off)}$  (5.9 k $\Omega$ , typically)

- OTP is removed when  $R_{NTC} \le R_{OTP(on)}$  (8.0 k $\Omega$ , typically) (Note 10)

Figure 68. Output Current Reduction versus SD Pin Voltage

At startup, when  $V_{CC}$  reaches  $V_{CC(on)}$ , the OTP comparator is blanked for at least 180  $\mu s$  which allows the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin. This avoids flickering of the LED light during turn on.

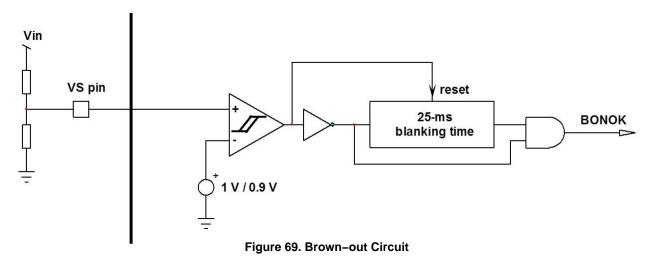

#### **Brown-Out Protection**

The NCL30086 prevents operation when the line voltage is too low for proper operation. As sketched in Figure 69, the circuit detects a brown–out situation if the  $V_S$  pin remains below the  $V_{BO(off)}$  threshold (0.9 V typical) for more than the 25–ms blanking time. In this case, the controller stops operating. Operation resumes as soon as the  $V_S$  pin voltage exceeds  $V_{BO(on)}$  (1.0 V typical) and  $V_{CC}$  is higher than  $V_{CC(on)}$ . To ease recovery, the circuit overrides the  $V_{CC}$  normal sequence (no need for  $V_{CC}$  cycling down below  $V_{CC(off)}$ ). Instead, its consumption immediately reduces to  $I_{CC(start)}$  so that  $V_{CC}$  rapidly charges up to  $V_{CC(on)}$  and the circuit re–starts operation.

- 9. The above mentioned initial value is the output current before the system enters the thermal foldback, that is, its maximum level if PWM or analog dimming is not engaged or a lower one based on the dimming value.

- 10. This condition is sufficient for operation recovery of the B and D versions. For the A and C versions which latches off when OTP is triggered, the circuit further needs to be reset by the V<sub>CC</sub> drop below V<sub>CC(reset)</sub>.

#### Die Over Temperature (TSD)

The circuit stops operating if the junction temperature  $(T_J)$  exceeds 150°C typically. The controller remains off until  $T_J$  goes below nearly 100°C.

#### **Pin Connection Faults**

The circuit addresses most pin connection fault cases:

#### • CS Pin Short to Ground

The circuit senses the CS pin impedance every time it starts—up and after DRV pulses terminated by the 36– $\mu s$  maximum on–time. If the measured impedance does not exceed 120  $\Omega$  typically, the circuit stops operating. In practice, it is recommended to place a minimum of 250  $\Omega$  in series between the CS pin and the current sense resistor to take into account parasitics.

#### • Fault of the GND Connection

If the GND pin is properly connected, the supply current drawn from the positive terminal of the  $V_{CC}$  capacitor, flows out of the GND pin to return to the negative terminal of the  $V_{CC}$  capacitor. If the GND pin is not connected, the circuit ESD diodes offer another return path. The accidental non–connection of the GND pin is monitored by detecting that one of the ESD diode is conducting. Practically, the ESD diode of CS pin is monitored. If such a fault is detected for 200  $\mu$ s, the circuit stops generating DRV pulses.

More generally, incorrect pin connection situations (open, grounded, shorted to adjacent pin) are covered by ANDxxxx.

#### **Fault Management**

OFF Mode

The circuit turns off in the case of an incorrect feeding of the circuit: "UVLO high". The UVLO signal becomes high when VCC drops below VCC(off) and remains high until VCC exceeds VCC(on).

The circuit also turns off whenever a major faulty condition prevents it from operating:

- Severe OTP (V<sub>SD</sub> level below V<sub>OTP(off)</sub>)

- V<sub>CC</sub> OVP

- OVP2 (additional OVP provided by SD pin)

- Output diode short circuit protection: "WOD\_SCP high"

- Output / Auxiliary winding Short circuit protection: "Aux\_SCP high"

- Die over temperature (TSD)

In this mode, the DRV pulses generation is interrupted.

In the case of a latching–off fault, the circuit stops pulsing until the LED driver is unplugged and  $V_{CC}$  drops below  $V_{CC(reset)}$ . At that moment, the circuit resumes operation.

In the auto-recovery case, the circuit cannot generate DRV pulses for the auto-recovery 4–s delay. When this time has elapsed, the circuit recovers operation as soon as the  $V_{CC}$  voltage has exceeded  $V_{CC(on)}$ . In the B and D versions, all these protections are auto-recovery. The SD pin OTP and OVP, WOD\_SCP and AUX\_SCP functions are latching off in the A and C versions (see Table 5).

**Table 5. PROTECTION MODES**

|            | AUX_SCP       | WOD_SCP       | SD Pin OTP    | SD Pin OVP    |

|------------|---------------|---------------|---------------|---------------|

| NCL30086A* | Latching off  | Latching off  | Latching off  | Latching off  |

| NCL30086B  | Auto-recovery | Auto-recovery | Auto-recovery | Auto-recovery |

| NCL30086C* | Latching off  | Latching off  | Latching off  | Latching off  |

| NCL30086D* | Auto-recovery | Auto-recovery | Auto-recovery | Auto-recovery |

#### **ORDERING INFORMATION**

| Device         | Package Type          | Shipping           |

|----------------|-----------------------|--------------------|

| NCL30086ADR2G* |                       |                    |

| NCL30086BDR2G  | SOIC-8                | 2500 / Tong & Dool |

| NCL30086CDR2G* | (Pb-Free/Halide Free) | 2500 / Tape & Reel |

| NCL30086DDR2G* |                       |                    |

<sup>\*</sup>Please contact local sales representative for availability

#### PACKAGE DIMENSIONS

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- CONTROLLING DIMENSION: MILLIMETERS. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.10mm TOTAL IN EXCESS OF 'b' AT MAXIMUM MATERIAL CONDITION. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR CATTER DESCRIPTIONS OF THE PROTRUSIONS.

- GATE BURRS SHALL NOT EXCEED 0.15mm PER SIDE. DIMENSIONS D AND E ARE DE-TERMINED AT DATUM F. DIMENSIONS A AND B ARE TO BE DETERM-

- INED AT DATUM F.

A1 IS DEFINED AS THE VERTICAL DISTANCE

- FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

|     | MILLIN | MILLIMETERS |  |  |  |  |

|-----|--------|-------------|--|--|--|--|

| DIM | MIN    | MAX         |  |  |  |  |

| Α   | 1.25   | 1.75        |  |  |  |  |

| A1  | 0.10   | 0.25        |  |  |  |  |

| А3  | 0.17   | 0.25        |  |  |  |  |

| b   | 0.31   | 0.51        |  |  |  |  |

| D   | 4.80   | 5.00        |  |  |  |  |

| Е   | 3.80   | 4.00        |  |  |  |  |

| е   | 1.00   | BSC         |  |  |  |  |

| Н   | 5.80   | 6.20        |  |  |  |  |

| h   | 0.37   | 7 REF       |  |  |  |  |

| L   | 0.40   | 1.27        |  |  |  |  |

| L2  | 0.25   | 0.25 BSC    |  |  |  |  |

| М   | 0° 8°  |             |  |  |  |  |

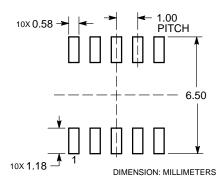

#### RECOMMENDED **SOLDERING FOOTPRINT\***

**END VIEW**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the (III) are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

SIDE VIEW

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

## Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А