# XRT8001

## WAN Clock for T1 and E1 Systems

October 2001-1

#### **GENERAL DESCRIPTION**

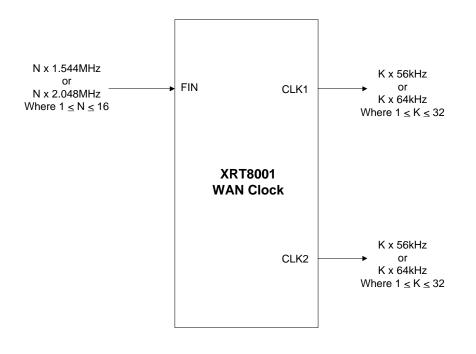

The XRT8001 WAN Clock is a dual-phase-locked loop chip that generates two very low jitter output clock signals that can be used for synchronization clocks in wide area networking systems. The XRT8001 has preprogrammed multipliers and dividers that are selected via the serial port. It generates two integer multiples of 8kHz, 56kHz, and 64kHz while locked onto an incoming reference of 1.54MHz (T1), 2.048MHz (E1), 8kHz, 56kHz, or 64kHz

The XRT8001 WAN Clock can be configured to operate in one of six modes:

- 1. The Forward/Master Mode

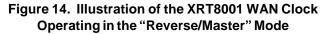

- 2. The Reverse/Master Mode

- 3. The "Fractional T1/E1" Reverse/Master Mode

- 4. The "E1 to T1 Forward/Master" Mode

- 5. The "High Speed Reverse" Mode

- 6. The "Slave" Mode

#### FEATURES

- Dual Phased Locked Loops with Pre-Programmed Multipliers and Dividers

- Pre-Programmed with Popular Frequency Conversions for Communications Systems

- Generates Output Clock Frequencies Ranging From 8kHz up to 16.384MHz

- Serial Port Control for Optimal Performance

- Sync Output: 8kHz or 64kHz

- Low Jitter

- Cascadable (Master / Slave Modes)

- No External Components Needed

- Pin Compatible with the XRT8000

- Low Power (3.3V or 5V): 40 100mW

- - 40°C to +85°C Temperature Range

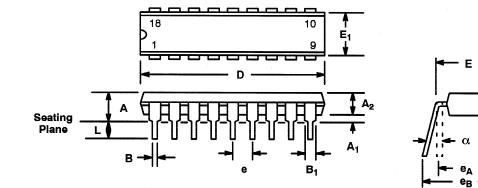

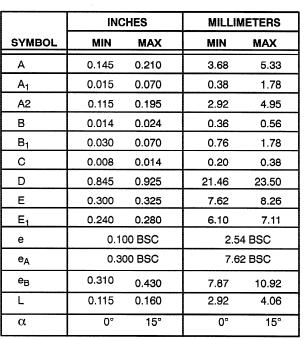

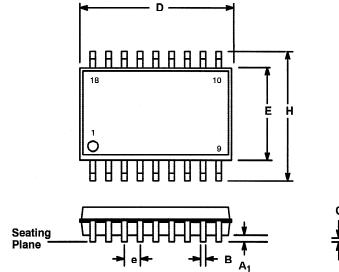

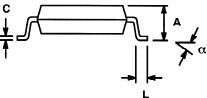

- 18-Lead PDIP or SOIC Packages

#### **APPLICATIONS**

- T1/E1 Access Equipment (DSU/CSU)

- Frame Relay Access Devices (FRAD)

- Basic Rate and Primary Rate ISDN Equipment

- ISDN Routers

- Terminals

- Remote Access Servers

- T1/E1 Concentrators

- T1/E1 Multiplexers

- T1/E1 Clock Rate Converters

- Internal Timing Generators

- System Synchronizers

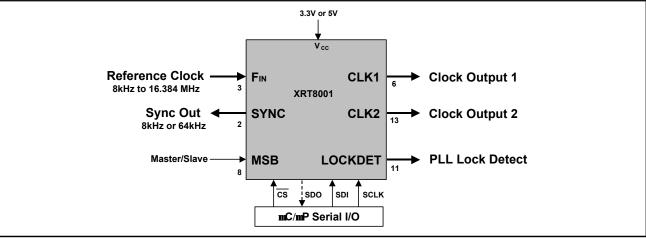

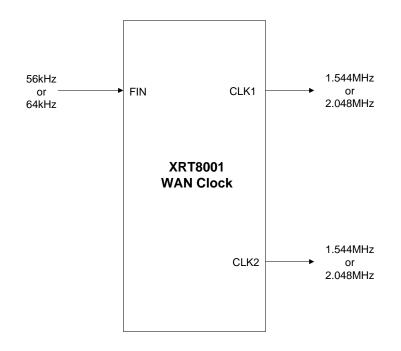

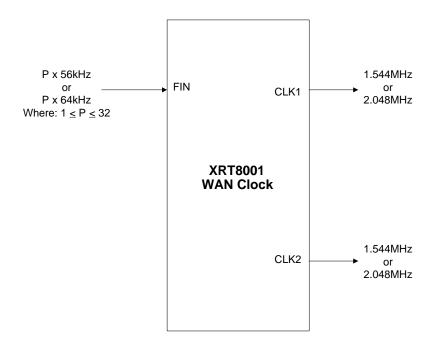

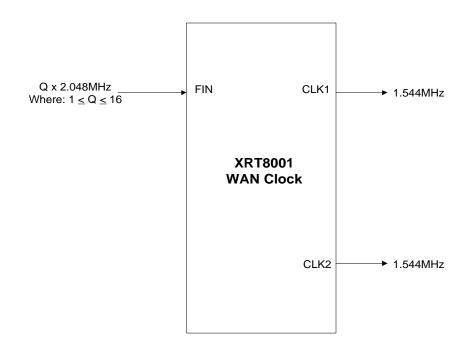

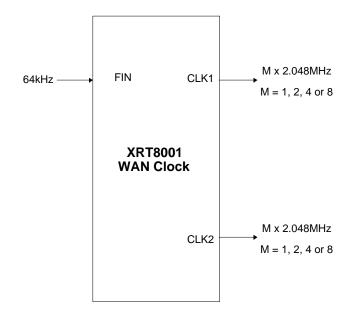

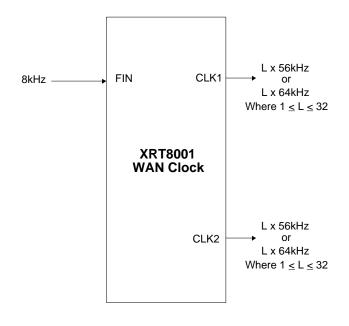

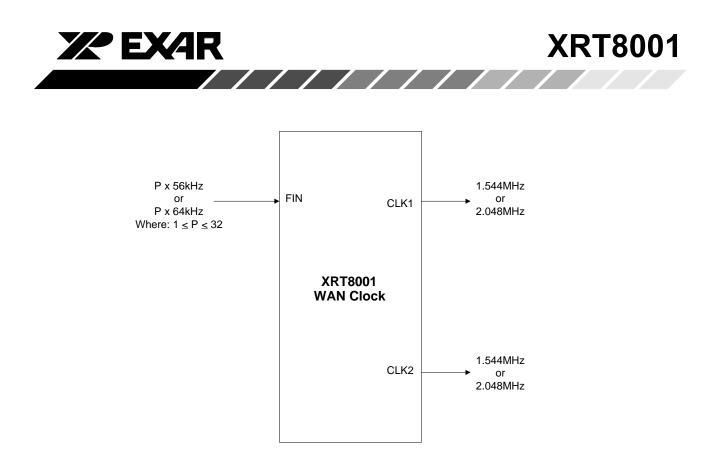

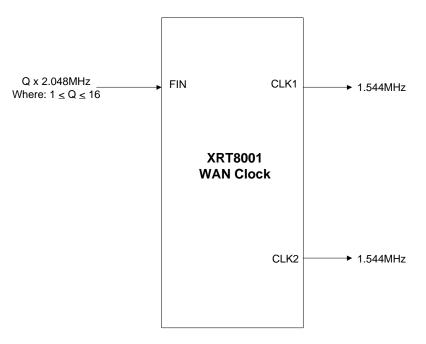

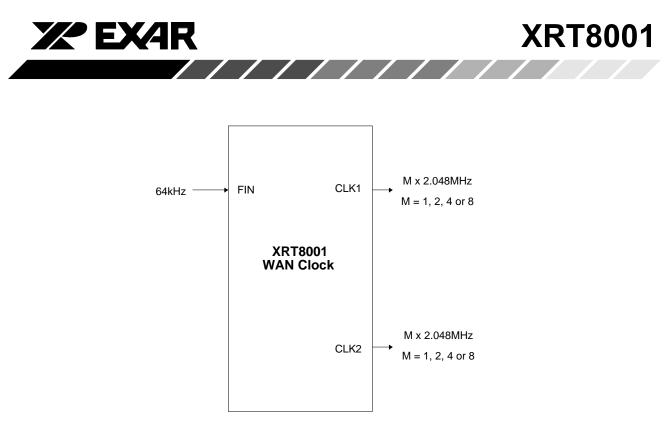

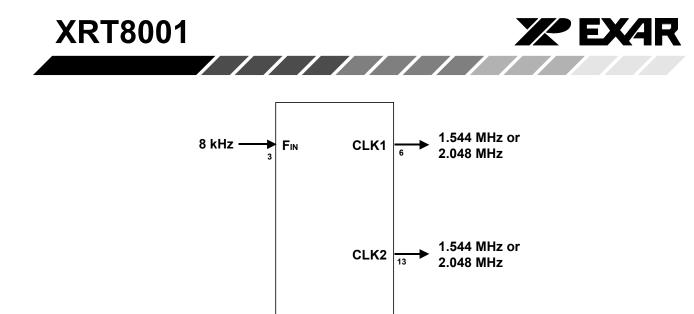

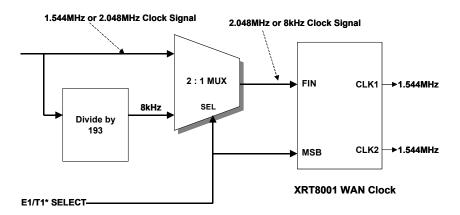

#### Figure 1. System Diagram

#### **ORDERING INFORMATION**

Rev. 1.01

| Part Number | Package                    | Operating Temperature Range |

|-------------|----------------------------|-----------------------------|

| XRT8001IP   | 18-Lead 300 Mil PDIP       | -40°C to +85°C              |

| XRT8001ID   | 18-Lead 300 Mil JEDEC SOIC | -40°C to +85°C              |

EXAR Corporation, 48720 Kato Road, Fremont, CA 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

**XRT8001**

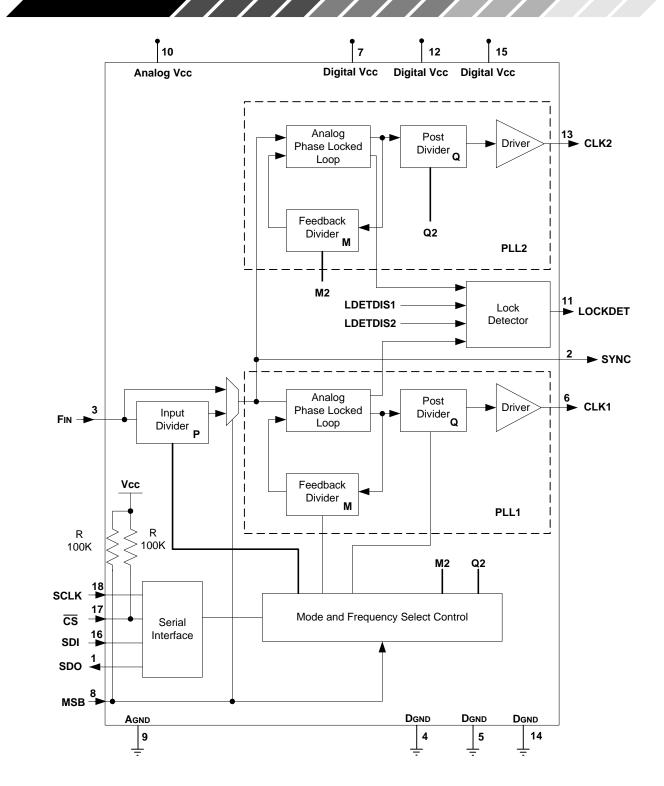

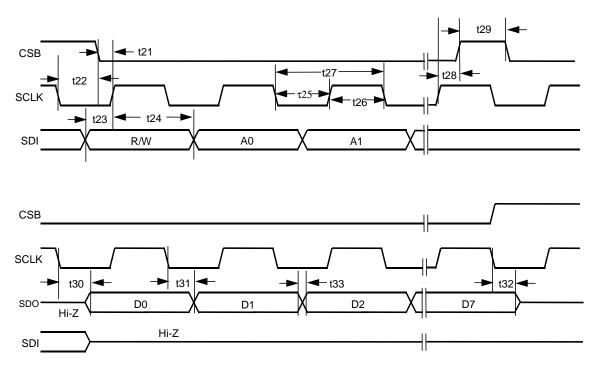

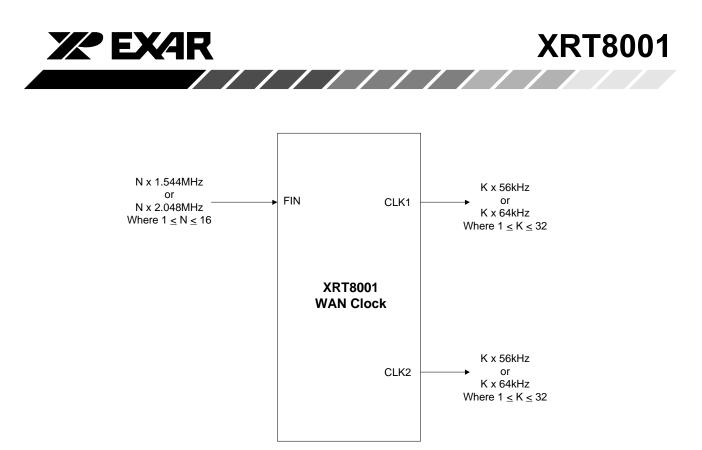

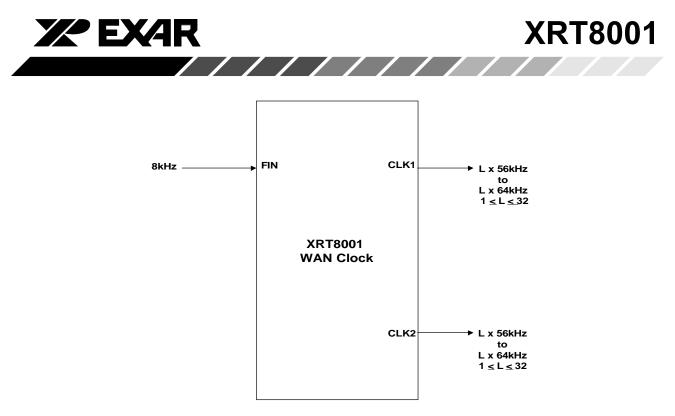

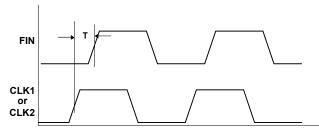

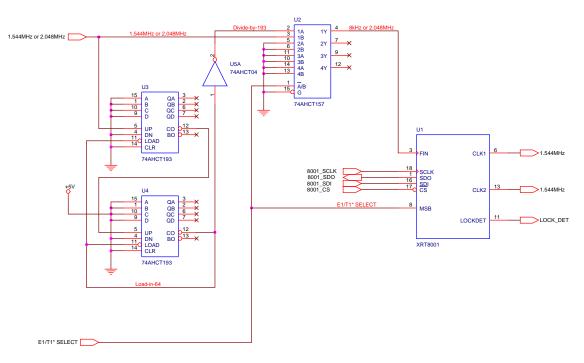

Figure 2. XRT8001 Block Diagram

Rev. 1.01

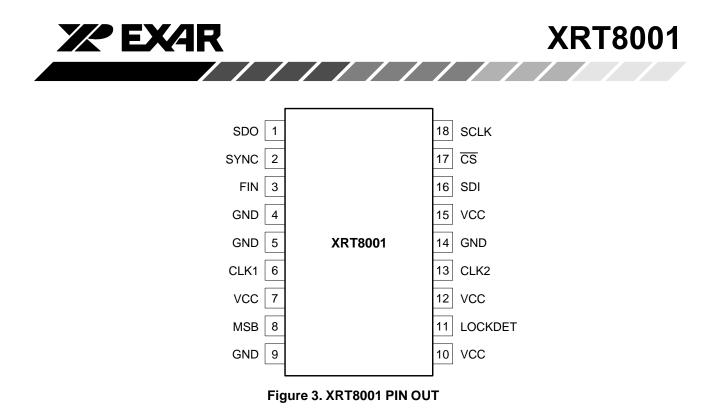

| PIN DESCRIPTION |  |

|-----------------|--|

| Pin # | Name            | Туре | Description                                                                                                                                                                                                                                                                                                                         |  |

|-------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | SDO             | Ö    | Serial Data Output from the Microprocessor Serial Interface<br>This pin will serially output the contents of the specified Command<br>Register, during "Read" Operations. The data, on this pin, will be<br>updated on the falling edge of the SCLK input signal. This pin will be tri-<br>stated upon completion of data transfer. |  |

| 2     | SYNC            | 0    | <b>Sync Output -</b> The XRT8001 will typically output an 8kHz clock signative via this output pin.                                                                                                                                                                                                                                 |  |

|       |                 |      | However, when the XRT8001 is operating in the "High Speed - Reverse" Mode, then this device will simply output a 64kHz clock signal.                                                                                                                                                                                                |  |

| 3     | FIN             | I    | <b>Reference Clock Input -</b> The Reference Timing signal (from which the CLK1 and CLK2 output signals are derived) is to be input via this pin.                                                                                                                                                                                   |  |

| 4     | GND             | -    | Digital Ground                                                                                                                                                                                                                                                                                                                      |  |

| 5     | GND             | -    | Digital Ground                                                                                                                                                                                                                                                                                                                      |  |

| 6     | CLK1            | 0    | <b>Clock Output 1 -</b> The XRT8001 will drive the desired "synthesized" signal via this output pin. This output signal will have a 50 <u>+</u> 5% duty cycle.                                                                                                                                                                      |  |

|       |                 |      | <b>Note:</b> This output pin is tri-stated unless the "CLK1EN" bit-field (within Command Register CR4) has been set to "1".                                                                                                                                                                                                         |  |

| 7     | V <sub>cc</sub> | -    | Digital Power Supply                                                                                                                                                                                                                                                                                                                |  |

Rev. 1.01

### PIN DESCRIPTION (CONT'D)

| Pin # | Name    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8     | MSB     | I    | <b>Master/Slave Mode Select Input</b> - Setting this input pin "HIGH" configures the XRT8001 to operate in the "MASTER" Mode. Conversely, setting this input pin "LOW" configures the XRT8001 to operate in the "SLAVE" Mode.                                                                                                                                                                                                                      |  |

| 9     | GND     | -    | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 10    | VCC     | -    | Analog Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 11    | LOCKDET | Ο    | <b>Lock Detect Output -</b> This output indicates whether or not the "selected" internal PLL(s) are "in-lock" or are "out-of-lock".                                                                                                                                                                                                                                                                                                                |  |

|       |         |      | By default, this output pin is "high" when both PLLs are in-lock" and will go toggle "low" if either one of the PLLs is "out-of-lock".                                                                                                                                                                                                                                                                                                             |  |

|       |         |      | However, the XRT8001 also permits the user to configure this output pin to reflect the state of any one of the PLLs within the chip. (See Table 3.)                                                                                                                                                                                                                                                                                                |  |

| 12    | VCC     | -    | Digital Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 13    | CLK2    | Ο    | <b>Clock Output 2 -</b> The XRT8001 will drive the desired "synthesized signal via this output pin. This output signal will have a 50 <u>+</u> 5% ducycle.                                                                                                                                                                                                                                                                                         |  |

|       |         |      | <b>Note:</b> This output pin is tri-stated unless the "CLK1EN" bit-field (within Command Register CR4) has been set to "1".                                                                                                                                                                                                                                                                                                                        |  |

| 14    | GND     | -    | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 15    | VCC     | -    | Digital Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 16    | SDI     | I    | <b>Microprocessor Serial Interface – Serial Data Input</b><br>Whenever, the user wishes to read or write data into the Command<br>Registers, over the Microprocessor Serial Interface, the user is expected<br>to apply the "Read/Write" bit, the Address Values (of the Command<br>Registers) and Data Value to be written (during "Write" Operations) to<br>this pin.<br>This input will be sampled on the rising edge of the SCLK pin (pin 18). |  |

| 17    | ĊŚ      | I    | Microprocessor Serial Interface – Chip Select Input:<br>The Local Microprocessor must assert this pin (e.g., set it to "0") in order<br>to enable communication with the XRT8001 via the Microprocessor<br>Serial Interface.                                                                                                                                                                                                                       |  |

|       |         |      | <b>Note:</b> This pin is internally pulled "high".                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 18    | SCLK    | I    | <b>Microprocessor Serial Interface-Clock Signal</b><br>This signal will be used to sample the data, on the SDI pin, on the rising<br>edge of this signal. Additionally, during "Read" operations, the<br>Microprocessor Serial Interface will update the SDO output on the falling<br>edge of this signal.                                                                                                                                         |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Range          | 7V                    |

|-----------------------|-----------------------|

| Voltage at any Pin    | GND -0.3V to Vcc+0.3V |

| Operating Temperature | 40°C to +85°C         |

| Storage Temperature   | 40°C to +85°C         |

| Package Dissipation   | 500mW                 |

| Symbol          | Parameter                              | Min. | Тур. | Max. | Units | Condition                                |

|-----------------|----------------------------------------|------|------|------|-------|------------------------------------------|

| V <sub>IL</sub> | Input Low Level                        |      |      | 0.8  | V     |                                          |

| V <sub>IH</sub> | Input High Level                       | 2.0  |      |      | V     |                                          |

| V <sub>ol</sub> | Output Low Level (CLK1, CLK2)          |      |      | 0.4  | V     | I <sub>oL</sub> = -6.0mA                 |

| V <sub>OH</sub> | Output High Level (CLK1, CLK2)         | 2.4  |      |      | V     | I <sub>oL</sub> = 6.0mA                  |

| V <sub>ol</sub> | Output Low Level (LOCKDET, SYNC)       |      |      | 0.4  | V     | I <sub>oL</sub> = -3.0mA                 |

| V <sub>OH</sub> | Output High Level (LOCKDET, SYNC)      | 2.4  |      |      | V     | I <sub>oL</sub> = 3.0mA                  |

| I <sub>IL</sub> | Input Low Current (CSB, MSB)           |      |      | -150 | mA    |                                          |

| I <sub>IH</sub> | Input High Current (CSB, MSB)          |      |      | 10   | mA    | $V_{IN} = V_{CC}$                        |

| I <sub>IL</sub> | Input Low Current (except CSB, MSB)    | -10  |      |      | mA    |                                          |

| I <sub>IH</sub> | Input High Current (except CSB, MSB)   |      |      | 10   | mA    | $V_{IN} = V_{CC}$                        |

| I <sub>cc</sub> | Operating Current                      |      | 11   | 30   | mA    | 3.3V, No Load, CLk1, CLK2 = 8 x 2.048MHz |

|                 |                                        |      | 20   | 35   | mA    | 5V, No Load, CLk1, CLK2 = 8 x 2.048MHz   |

| R <sub>IN</sub> | Internal Pull-up Resistance (CSB, MSB) | 50   | 100  | 150  | kW    |                                          |

#### DC ELECTRICAL CHARACTERISTICS (Except Microprocessor Serial Interface)<sup>1</sup>

#### Note:

1. 5V tolerant input considerations when operating from 3.3V:

When the XRT8001 is powered at 3.3V, it can tolerate 5V-level signals via its inputs. However, the user should be aware the XRT8001 contains a "Factory-Test" Mode. This mode is enabled whenever the MSB (Master-Slave select) input pin is pulled to about 2V above VDD.

Therefore, if the user is powering the XRT8001 at 3.3V but is applying a 5.25V signal to the MSB input pin, then it is possible that the XRT8001 could be configured to operate in this "Factory-Test" Mode. Since all "Factory-Test" Mode registers are reset to "0", upon chip power, this should not be a problem for the user.

However, if the user performs write operations to "non-defined" address locations within the XRT8001, then the user may observe strange operation from the XRT8001. The user must make sure that when the Microcontroller performs WRITE operations to the XRT8001, it is only performing these WRITE operations to the Address Locations defined in the XRT8001 Data Sheet.

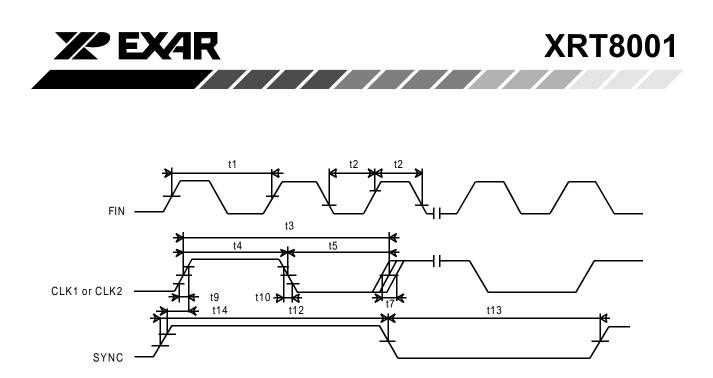

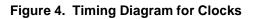

#### AC ELECTRICAL CHARACTERISTICS (See Figure 4.)

| Input Frequency         0.008         32.7         MHz         3.3V           12         Minimum Input Signal "High" to<br>"Low" Duration         12         ns           13         Output Frequency         56         16.384         kHz           16'         Duty Cycle         47.5         50         52.5         %         VCC/2 switch point; 30pF Load           17'         Jitter Added 8kHz - 40kHz         0.01         0.02         UI         53, Output = 1.544MHz (0.025 UI)           17'         Jitter Added 10Hz - 40kHz         0.03         -         UI         53, Output = 1.544MHz (0.025 UI)           17'         Jitter Added 20Hz - 100kHz         0.03         0.05         UI         33, Output = 1.544MHz (0.05 UI)           17'         Jitter Added 20Hz - 100kHz         0.03         0.05         UI         3.33, Output = 2.048MHz (1.5 UI)           17'         Jitter Added 18kHz - 100kHz         0.01         0.07         UI         3.33, Output = 2.048MHz (1.2 UI)           17'         Jitter Added 18kHz - 100kHz         0.01         0.07         UI         3.33, Output = 2.048MHz (1.2 UI)           17'         Jitter Added 18kHz - 100kHz         0.01         0.07         UI         S.30F load measured at 20/80%           112         SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Symbol             | Parameter                      | Min.  | Тур.  | Max.   | Units | Conditions                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------|-------|-------|--------|-------|-------------------------------|

| 12         Minimum Input Signal "High" to<br>"Low" Duration         12         ns           3         Output Frequency         56         16,384         KHz           161         Duty Cycle         47.5         50         52.5         %         VCC/2 switch point, 30pF Load           171         Jitter Added 8Hz – 40kHz         0.01         0.02         UI         3.3V, Output = 1.544MHz (0.025 UI)           174         Jitter Added 10Hz – 40kHz         0.03         -         UI         3.V, Output = 1.544MHz (0.025 UI)           174         Jitter Added 20Hz – 40kHz         0.03         -         UI         3.3V, Output = 1.544MHz (0.05 UI) <sup>3</sup> 174         Broadband Jitter         0.03         0.05         UI         3.3V, Output = 1.544MHz (0.05 UI) <sup>3</sup> 174         Jitter Added 20Hz – 100kHz         0.07         UI         3.3V, Output = 2.048MHz (1.5 UI) <sup>3</sup> 174         Jitter Added 18kHz – 100kHz         0.037         0.03         UI         3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 174         Jitter Added 18kHz – 100kHz         0.037         0.03         UI         3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 176         Ditck Output Rise Time         10ns         ns         3.00F         Ioad measured at 20/80%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t1                 | Input Frequency                | 0.008 |       | 32.7   | MHz   | 3.3V                          |

| "Low" Duration         Solution         Solution           13         Output Frequency         56         16,384         kHz           16         Duty Cycle         47.5         50         52.5         %         VCC/2 switch point, 30pF Load           17 <sup>14</sup> Jitter Added 8kHz – 40kHz         0.01         0.02         UI         3.3V, Output = 1.544MHz (0.025 UI)           17 <sup>14</sup> Jitter Added 10Hz – 40kHz         0.03         0.03         UI         3.3V, Output = 1.544MHz (0.025 UI)           17 <sup>14</sup> Broadband Jitter         0.03         0.05         UI         3.3V, Output = 1.544MHz (0.05 UI)           17 <sup>14</sup> Jitter Added 20Hz – 100kHz         0.03         0.07         UI         3.3V, Output = 2.048MHz (1.5 UI) <sup>3</sup> 17 <sup>14</sup> Jitter Added 18kHz – 100kHz         0.07         UI         3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 17 <sup>14</sup> Jitter Added 18kHz – 100kHz         0.007         UI         3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 17 <sup>4</sup> Jitter Time         1010s         ns         3.30V         Sayuet = 2.048MHz (0.2 UI) <sup>3</sup> 17 <sup>4</sup> Jitter Added 18kHz – 100kHz         0.007         UI         3.3V. Output = 2.048MHz (0.2 UI) <sup>3</sup> 17         Jitter Added 18kHz – 100kHz <td></td> <td></td> <td>0.008</td> <td></td> <td>32.7</td> <td>MHz</td> <td>5V</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                | 0.008 |       | 32.7   | MHz   | 5V                            |

| 13         Output Frequency         56         16,384         kHz           16'         Duty Cycle         47.5         50         52.5         %         VCC/2 switch point, 30pF Load           17'         Jitter Added 8kHz – 40kHz         0.01         0.02         UI         3.V, Output = 1.544MHz (0.025 UI)           17'         Jitter Added 10Hz – 40kHz         0.03         UI         5.V, Output = 1.544MHz (0.025 UI)           17'         Broadband Jitter         0.03         UI         3.3V, Output = 1.544MHz (0.025 UI)           17'         Broadband Jitter         0.03         0.05         UI         3.3V, Output = 1.544MHz (0.05 UI)           17'         Jitter Added 20Hz – 100kHz         0.07         UI         3.3V, Output = 1.544MHz (0.05 UI)           17'         Jitter Added 18kHz – 100kHz         0.07         UI         S.V, Output = 2.048MHz (0.2 UI)^3           17'         Jitter Added 18kHz – 100kHz         0.007         UI         S.V, Output = 2.048MHz (0.2 UI)^3           17'         Jitter Added 18kHz – 100kHz         0.007         UI         S.V, Output = 1.544MHz (0.2 UI)^3           17'         Jitter Added 18kHz – 100kHz         0.007         S.00F         UI         S.V Output = 1.544MHz (0.2 UI)^3           17'         S.V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t2                 | Minimum Input Signal "High" to | 12    |       |        | ns    |                               |

| 161         Duty Cycle         47.5         50         52.5         %         VCC/2 switch point, 30pF Load           174         Jitter Added 8kHz – 40kHz         0.01         0.02         UI         3.3V, Output = 1.544MHz (0.025 UI)           174         Jitter Added 10Hz – 40kHz         0.03         –         UI         3.3V, Output = 1.544MHz (0.025 UI)           174         Broadband Jitter         0.03         –         UI         3.3V, Output = 1.544MHz (0.05 UI)           174         Jitter Added 20Hz – 100kHz         0.03         0.05         UI         5V, Output = 2.048MHz (0.05 UI)           174         Jitter Added 18kHz – 100kHz         0.07         UI         3.3V, Output = 2.048MHz (1.5 UI) <sup>3</sup> 174         Jitter Added 18kHz – 100kHz         0.03         UI         3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 174         Jitter Added 18kHz – 100kHz         0.03         UI         3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 175         Jitter Added 18kHz – 100kHz         0.03         UI         3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 175         Jitter Added 18kHz – 100kHz         0.03         UI         3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 176         Clock Output Rise Time         10ms         ns         30pF load measured at 20/80%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    | "Low" Duration                 |       |       |        |       |                               |

| 17 <sup>4</sup> Jitter Added 8kHz – 40kHz       0.01       0.02       UI       3.3V, Output = 1.544MHz (0.025 UI)         17 <sup>4</sup> Jitter Added 10Hz – 40kHz       0.03       0.02       UI       3.3V, Output = 1.544MHz (0.025 UI)         17 <sup>4</sup> Jitter Added 10Hz – 40kHz       0.03       0.03       UI       3.3V, Output = 1.544MHz (0.025 UI)         17 <sup>4</sup> Broadband Jitter       0.03       0.05       UI       3.3V, Output = 1.544MHz (0.052 UI)         17 <sup>4</sup> Jitter Added 20Hz – 100kHz       0.03       0.05       UI       3.3V, Output = 1.544MHz (0.05 UI)         17 <sup>4</sup> Jitter Added 18kHz – 100kHz       0.07       UI       3.3V, Output = 1.544MHz (0.02 UI) <sup>3</sup> 17 <sup>4</sup> Jitter Added 18kHz – 100kHz       0.07       UI       3.3V, Output = 1.544MHz (0.02 UI) <sup>3</sup> 17 <sup>4</sup> Jitter Added 18kHz – 100kHz       0.07       UI       3.3V, Output = 1.544MHz (0.2 UI) <sup>3</sup> 18       Capture Time       10.07       UI       3.3V, Output = 1.544MHz (0.2 UI) <sup>3</sup> 18       Capture Time       100s       ns       3.3V         11 <sup>2</sup> SVNC Output Signal Duty Cycle       40       60       %       VCC/2 switch point         11 <sup>2</sup> SYNC Output Signal Pix Cycle       10       100       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t3                 | Output Frequency               | 56    |       | 16,384 | kHz   |                               |

| Image: constraint of the second sec       | t61                |                                | 47.5  | 50    | 52.5   | %     |                               |

| 17*       Jitter Added 10Hz - 40kHz       0.03       UI       3.3V, Output = 1.544MHz (0.025 UI)         17*       Broadband Jitter       0.03       0.05       UI       3.3V, Output = 1.544MHz (0.05 UI)         17*       Broadband Jitter       0.03       0.05       UI       3.3V, Output = 1.544MHz (0.05 UI)         17*       Jitter Added 20Hz - 100kHz       0.03       0.07       UI       3.3V, Output = 2.048MHz (1.5 UI)         17*       Jitter Added 18kHz - 100kHz       0.03       UI       3.3V, Output = 2.048MHz (0.2 UI)         17*       Jitter Added 18kHz - 100kHz       0.07       UI       3.3V, Output = 2.048MHz (0.2 UI)         17*       Jitter Added 18kHz - 100kHz       0.007       0.03       UI       5V, Output = 2.048MHz (0.2 UI)         18       Capture Time       40       ms       3.3V       0.007         19       Clock Output Signal Duty Cycle       40       ms       30PF load measured at 20/80%         112       SYNC Output Signal - ½ Cycle       10ns       ns       30PF load measured at 20/80%         112       SYNC Output Signal - ½ Cycle       1420       ns       See Table 8 for values of "t"         123       SYNC Output Signal - ½ Cycle       1420       ns       See Table 8 for values of "t"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t74                | Jitter Added 8kHz – 40kHz      |       | 0.01  |        | UI    |                               |

| $ \begin{array}{ c c c c c } \hline \hline$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                |       | 0.01  | 0.02   | UI    |                               |

| 17 <sup>4</sup> Broadband Jitter       0.03       0.05       UI       3.3V, Output = 1.544MHz (0.05 UI) <sup>3</sup> 17 <sup>4</sup> Jitter Added 20Hz – 100kHz       0.07       UI       3.3V, Output = 2.048MHz (0.05 UI) <sup>3</sup> 17 <sup>4</sup> Jitter Added 18kHz – 100kHz       0.07       UI       3.3V, Output = 2.048MHz (1.5 UI) <sup>3</sup> 17 <sup>4</sup> Jitter Added 18kHz – 100kHz       0.07       0.03       UI       3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 17 <sup>4</sup> Jitter Added 18kHz – 100kHz       0.03       0.03       UI       3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 17 <sup>4</sup> Jitter Added 18kHz – 100kHz       0.03       UI       3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 18       Capture Time       40       ms       3.3V         18       Capture Time       10ns       ns       30pF load measured at 20/80%         10       Clock Output Signal Duty Cycle       40       fo       %       VCC/2 switch point         112       SYNC Output Signal Duty Cycle       40       fo       %       VCC/2 switch point         112       SYNC Output Signal Duty Cycle       40       fo       %       VCC/2 switch point         113       SYNC Output Signal + ½ Cycle       1       t+20       ns       See Table 8 for values of "t"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t74                | Jitter Added 10Hz – 40kHz      |       |       |        |       |                               |

| Image: space of the second s       |                    |                                |       |       | -      |       |                               |

| 174       Jitter Added 20Hz - 100kHz       0.07       UI       3.3V, Output = 2.048MHz (1.5 UI) <sup>3</sup> 174       Jitter Added 18kHz - 100kHz       0.07       UI       5V, Output = 2.048MHz (1.5 UI) <sup>3</sup> 174       Jitter Added 18kHz - 100kHz       0.03       UI       3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 174       Jitter Added 18kHz - 100kHz       0.007       0.03       UI       5V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 174       Jitter Added 18kHz - 100kHz       0.007       0.03       UI       5V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 18       Capture Time       40       ms       3.3V       0utput = 2.048MHz (0.2 UI) <sup>3</sup> 18       Clock Output Rise Time       10ns       ns       30PF load measured at 20/80%         101       Clock Output Signal Duty Cycle       40       60       %       VCC/2 switch point         112       SYNC Output Signal - ½ Cycle       10       10       ns       See Table 8 for values of "t"         113       SYNC Output Signal - ½ Cycle       1       1       1       Delay Time between the rising edge of SCLK       50       ns       1         121       CSB Low to Rising Edge of SCLK       50       ns       1       1       1         122       CSB High to Rising Ed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t74                | Broadband Jitter               |       |       |        |       |                               |

| Image: space of the second space of the second space of the        |                    |                                |       | 0.035 |        |       |                               |

| 17 <sup>4</sup> Jitter Added 18kHz - 100kHz       0.03       UI       3.3V, Output = 2.048MHz (0.2 UI) <sup>3</sup> 18       Capture Time       40       ms       3.3V         18       Capture Time       40       ms       5V         19       Clock Output Rise Time       10ns       ns       30pF load measured at 20/80%         110       Clock Output Signal Duty Cycle       40       ms       30pF load measured at 20/80%         111 <sup>2</sup> SYNC Output Signal + ½ Cycle       10ns       ns       30pF load measured at 20/80%         111 <sup>2</sup> SYNC Output Signal + ½ Cycle       10ns       ns       See Table 8 for values of "t"         113       SYNC Output Signal + ½ Cycle       1       1420       ns       See Table 8 for values of "t"         114       Delay Time between the rising edge of SCLK       50       ns       See Table 8 for values of "t"         121       CSB Low to Rising Edge of SCLK       50       ns       See Table 8 for values of "t"         122       CSB Light o Rising Edge of SCLK Setup Time       50       ns       See Table 8 for values of "t"         122       CSB Light to Rising Edge of SCLK Hold Time       50       ns       See Table 8 for values of "t"         123       SDI to Rising Edge of SCLK Hold Time <t< td=""><td>t74</td><td>Jitter Added 20Hz – 100kHz</td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | t74                | Jitter Added 20Hz – 100kHz     |       |       |        |       |                               |

| Image: second        |                    |                                |       | 0.01  |        |       |                               |

| 18         Capture Time         40         ms         3.3V           19         Clock Output Rise Time         10ns         ns         30pF load measured at 20/80%           110         Clock Output Signal Duty Cycle         40         60         %         VCC/2 switch point           112         SYNC Output Signal Duty Cycle         40         60         %         VCC/2 switch point           112         SYNC Output Signal - ½ Cycle         10ns         ns         See Table 8 for values of "t"           113         SYNC Output Signal - ½ Cycle         1         1         ns         See Table 8 for values of "t"           114         Delay Time between the rising edge of SCLK         50         ns         See Table 8 for values of "t"           114         Delay Time         Super of SYNC and the Rising edge of SCLK         50         ns           121         CSB Low to Rising Edge of SCLK         50         ns         1           122         CSB High to Rising Edge of SCLK         20         ns         1           123         SDI to Rising Edge of SCLK Hold Time         50         ns         1           125         SCLK "Low" Time         240         ns         1           126         SCLK Period         500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t74                | Jitter Added 18kHz – 100kHz    |       |       |        |       |                               |

| Image: second |                    |                                |       | 0.007 |        | UI    |                               |

| 19       Clock Output Rise Time       10ns       ns       30pF load measured at 20/80%         110       Clock Output Fall Time       10ns       ns       30pF load measured at 20/80%         111       SYNC Output Signal Duty Cycle       40       60       %       VCC/2 switch point         112       SYNC Output Signal - ½ Cycle       60       %       VCC/2 switch point         113       SYNC Output Signal - ½ Cycle       1       50       7         113       SYNC Output Signal - ½ Cycle       1       50       7         114       Delay Time between the rising edge of CLK1 and CLK2       1+20       ns       See Table 8 for values of "t"         121       CSB Low to Rising Edge of SCLK       50       ns       10       10         122       CSB High to Rising Edge of SCLK       20       ns       10       10         123       SDI to Rising Edge of SCLK Setup Time       50       ns       12       10       10         123       SDI to Rising Edge of SCLK Hold Time       50       ns       12       12       SCLK "Low" Time       240       10       11         124       SDI to Rising Edge of SCLK       50       ns       12       12       SCLK Period       50       ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t8                 | Capture Time                   |       |       | -      |       |                               |

| 110       Clock Output Fall Time       10ns       ns       30pF load measured at 20/80%         111 <sup>2</sup> SYNC Output Signal Duty Cycle       40       60       %       VCC/2 switch point         111 <sup>2</sup> SYNC Output Signal + ½ Cycle       1       1       1       1       1         113       SYNC Output Signal - ½ Cycle       1       1       1       1       1         114       Delay Time between the rising edge of SYNC and the Rising edge of CLK1 and CLK2       1+20       ns       See Table 8 for values of "t"         121       CSB Low to Rising Edge of SCLK       50       ns       Setup Time       1         122       CSB High to Rising Edge of SCLK       20       ns       ns       1         123       SDI to Rising Edge of SCLK Setup Time       50       ns       1       1         123       SDI to Rising Edge of SCLK Hold Time       50       ns       1       1         124       SDI to Rising Edge of SCLK Hold Time       50       ns       1       1         125       SCLK "Low" Time       240       ns       1       1       1       1         127       SCLK Period       500       ns       1       1       1       1       1 <td>-</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                  |                                |       |       |        |       |                               |

| t112SYNC Output Signal Duty Cycle4060%VCC/2 switch point112SYNC Ouput Signal + ½ Cycle </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>•</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                |       |       |        |       | •                             |

| 112       SYNC Ouput Signal + ½ Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |                                |       |       |        |       | •                             |

| t13SYNC Output Signal – ½ CycleImage: CycleImage: CycleImage: Cyclet14Delay Time between the rising<br>edge of of SYNC and the Rising<br>edge of of LK1 and CLK2t-20t+20nsSee Table 8 for values of "t"t21CSB Low to Rising Edge of SCLK<br>Setup Time50nsnsSee Table 8 for values of "t"t22CSB High to Rising Edge of SCLK<br>Hold Time20nsnst23SDI to Rising Edge of SCLK Setup Time<br>Hold Time50nsnst24SDI to Rising Edge of SCLK Hold Time<br>SCLK "Low" Time240nsnst25SCLK "Low" Time240ns1t26SCLK Period500ns1t27SCLK Period500ns1t28CSB Low to Rising Edge of SCLK<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |                                | 40    |       | 60     | %     | VCC/2 switch point            |

| 114Delay Time between the rising<br>edge of of SYNC and the Rising<br>edge of CLK1 and CLK2t-20t+20nsSee Table 8 for values of "t"121CSB Low to Rising Edge of SCLK<br>Setup Time50nsns122CSB High to Rising Edge of SCLK<br>Hold Time20nsns123SDI to Rising Edge of SCLK Setup Time<br>Hold Time50nsns124SDI to Rising Edge of SCLK Hold Time<br>SCLK "Low" Time50nsns125SCLK "Low" Time<br>SCLK "High" Time240nsns126SCLK "High" Time<br>Hold Time240nsns127SCLK Period500nsns128CSB Low to Rising Edge of SCLK<br>Hold Time50nsns129CSB "Inactive" Time<br>Falling Edge of SCLK to SDO Valid Time200ns130Falling Edge of SCLK to SDO Valid Time<br>of CSB to High Z100ns133Rise/Fall time of SDO Output40ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                                |       |       |        |       |                               |

| edge of of SYNC and the Rising<br>edge of CLK1 and CLK2Image: CSB Low to Rising Edge of SCLK<br>Setup Time50<br>Rnst22CSB High to Rising Edge of SCLK<br>Hold Time20<br>Rnsnst23SDI to Rising Edge of SCLK Setup Time50nst24SDI to Rising Edge of SCLK Hold Time50nst25SCLK "Low" Time240nst26SCLK "High" Time240nst27SCLK Period500nst28CSB Low to Rising Edge of SCLK50nst29CSB "Inactive" Time250nst30Falling Edge of SCLK to SDO Valid Time200nst31Falling Edge of SCLK, or rising edge<br>of CSB to High Z100nst33Rise/Fall time of SDO Output140ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |                                |       |       | 1 00   |       |                               |

| edge of CLK1 and CLK2Image: CSB Low to Rising Edge of SCLK50nst21CSB Low to Rising Edge of SCLK20nst22CSB High to Rising Edge of SCLK Setup Time20nst23SDI to Rising Edge of SCLK Setup Time50nst24SDI to Rising Edge of SCLK Hold Time50nst25SCLK "Low" Time240nst26SCLK "High" Time240nst27SCLK Period500nst28CSB Low to Rising Edge of SCLK50nst29CSB "Inactive" Time250nst30Falling Edge of SCLK to SDO Valid Time200nst31Falling Edge of SCLK, or rising edge100nst33Rise/Fall time of SDO OutputJ40ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | t14                |                                | t-20  |       | t+20   | ns    | See Table 8 for values of "t" |

| 121CSB Low to Rising Edge of SCLK<br>Setup Time50ns122CSB High to Rising Edge of SCLK<br>Hold Time20ns123SDI to Rising Edge of SCLK Setup Time<br>SDI to Rising Edge of SCLK Hold Time50ns124SDI to Rising Edge of SCLK Hold Time<br>SCLK "Low" Time240ns125SCLK "Low" Time240ns126SCLK "High" Time240ns127SCLK Period500ns128CSB Low to Rising Edge of SCLK<br>Hold Time50ns129CSB "Inactive" Time250ns130Falling Edge of SCLK to SDO Valid Time200ns131Falling Edge of SCLK to SDO Invalid Time100ns132Falling Edge of SCLK, or rising edge<br>of CSB to High Z100ns133Rise/Fall time of SDO Output40ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                |       |       |        |       |                               |

| Setup TimeImage: Setup TimeImage: Setup TimeImage: Setup TimeImage: Setup TimeImage: Setup TimeImage: Setup Time122CSB High to Rising Edge of SCLK Setup Time50Image: Setup TimeImage: Setup TimeImage: Setup Time123SDI to Rising Edge of SCLK Hold Time50Image: Setup TimeImage: Setup TimeImage: Setup Time124SDI to Rising Edge of SCLK Hold Time50Image: Setup TimeImage: Setup TimeImage: Setup Time125SCLK "Low" Time240Image: Setup TimeImage: Setup TimeImage: Setup Time126SCLK "High" Time240Image: Setup TimeImage: Setup Time127SCLK Period500Image: Setup TimeImage: Setup Time128CSB Low to Rising Edge of SCLK50Image: Image: Setup TimeImage: Setup Time129CSB "Inactive" Time250Image: Image: Image: Setup TimeImage: Image: Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101                |                                | 50    |       |        |       |                               |

| t22CSB High to Rising Edge of SCLK<br>Hold Time20nst23SDI to Rising Edge of SCLK Setup Time50nst24SDI to Rising Edge of SCLK Hold Time50nst25SCLK "Low" Time240nst26SCLK "High" Time240nst27SCLK Period500nst28CSB Low to Rising Edge of SCLK500nst29CSB "Inactive" Time250nst30Falling Edge of SCLK to SDO Valid Time200nst31Falling Edge of SCLK to SDO Invalid Time100nst32Falling Edge of SCLK, or rising edge<br>of CSB to High Z100nst33Rise/Fall time of SDO Output40ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t21                |                                | 50    |       |        | ns    |                               |

| Hold TimeImage: Solito Rising Edge of SCLK Setup Time50Image: Solito Rising Edge of SCLK Hold Time50Image: Rising Edge of SCLK Hold Time124SDI to Rising Edge of SCLK Hold Time50Image: Rising Edge of SCLK Hold Time50Image: Rising Edge of SCLK125SCLK "Low" Time240Image: Rising Edge of SCLKImage: Rising Edge of SCLKImage: Rising Edge of SCLK126SCLK Period500Image: Rising Edge of SCLKImage: Rising Edge of SCLKImage: Rising Edge of SCLK128CSB Low to Rising Edge of SCLK50Image: Rising Edge of Rising Edge of SCLKImage: Rising Edge of Rising Edge of SCLK129CSB "Inactive" Time250Image: Rising Edge of Rising Edge of SCLK to SDO Valid TimeImage: Rising Edge of Rising Edg                                                                                                                                                                                                                                                                                                                                                      |                    | •                              |       |       |        |       |                               |

| t23SDI to Rising Edge of SCLK Setup Time50nst24SDI to Rising Edge of SCLK Hold Time50nst25SCLK "Low" Time240nst26SCLK Wilgh" Time240nst27SCLK Period500nst28CSB Low to Rising Edge of SCLK50nsHold Time250nst29CSB "Inactive" Time250nst30Falling Edge of SCLK to SDO Valid Time200nst31Falling Edge of SCLK to SDO Invalid Time100nst33Rise/Fall time of SDO Output40ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t22                |                                | 20    |       |        | ns    |                               |

| t24SDI to Rising Edge of SCLK Hold Time50nst25SCLK "Low" Time240nst26SCLK "High" Time240nst27SCLK Period500nst28CSB Low to Rising Edge of SCLK50nsHold Time250nst29CSB "Inactive" Time250nst30Falling Edge of SCLK to SDO Valid Time200nst31Falling Edge of SCLK to SDO Invalid Time100nst32Falling Edge of SCLK, or rising edge<br>of CSB to High Z100nst33Rise/Fall time of SDO Output40ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                |       |       |        |       |                               |

| t25SCLK "Low" Time240nst26SCLK "High" Time240nst27SCLK Period500nst28CSB Low to Rising Edge of SCLK50nsHold Time250nst29CSB "Inactive" Time250nst30Falling Edge of SCLK to SDO Valid Time200nst31Falling Edge of SCLK to SDO Invalid Time100nst32Falling Edge of SCLK, or rising edge<br>of CSB to High Z100nst33Rise/Fall time of SDO Output40ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    | ÷ ÷                            |       |       |        | ns    |                               |

| t26SCLK "High" Time240nst27SCLK Period500nst28CSB Low to Rising Edge of SCLK50nsHold Time250nst29CSB "Inactive" Time250nst30Falling Edge of SCLK to SDO Valid Time200nst31Falling Edge of SCLK to SDO Invalid Time100nst32Falling Edge of SCLK, or rising edge<br>of CSB to High Z100nst33Rise/Fall time of SDO Output40ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                |       |       |        | ns    |                               |