SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

- Advanced LinCMOS™ Silicon-Gate **Technology**

- 8-Bit Resolution

- **Differential Reference Inputs**

- **Parallel Microprocessor Interface**

- **Conversion and Access Time Over Temperature Range** Read Mode . . . 2.5 us Max

- No External Clock or Oscillator **Components Required**

- **On-Chip Track and Hold**

- Single 5-V Supply

- **TLC0820A Is Direct Replacement for** National Semiconductor ADC0820C/CC and Analog Devices AD7820K/B/T

#### description

The TLC0820AC and the TLC0820AI are Advanced LinCMOS™ 8-bit analog-to-digital converters each consisting of two 4-bit flash converters, a 4-bit digital-to-analog converter, a summing (error) amplifier, control logic, and a result latch circuit. The modified flash technique allows low-power integrated circuitry to complete an 8-bit conversion in 1.18 µs over temperature. The on-chip track-and-hold circuit has a 100-ns sample window and allows these devices to convert continuous analog signals having slew rates of up to 100 mV/µs without external sampling components. TTL-compatible 3-state output drivers and two modes of operation allow

**FN PACKAGE**

NC-No internal connection

interfacing to a variety of microprocessors. Detailed information on interfacing to most popular microprocessors is readily available from the factory.

#### **AVAILABLE OPTIONS**

| I |               | TOTAL         |             | PACKA                            | GE                              |                    |

|---|---------------|---------------|-------------|----------------------------------|---------------------------------|--------------------|

|   | TA            | l             |             | PLASTIC<br>SMALL OUTLINE<br>(DW) | PLASTIC<br>CHIP CARRIER<br>(FN) | PLASTIC DIP<br>(N) |

|   | 0°C to 70°C   | ±1 LSB        | TLC0820ACDB | TLC0820ACDW                      | TLC0820ACFN                     | TLC0820ACN         |

|   | −40°C to 85°C | 85°C ±1 LSB — |             | TLC0820AIDW                      | TLC0820AIFN                     | TLC0820AIN         |

Advanced LinCMOS is a trademark of Texas Instruments Incorporated.

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

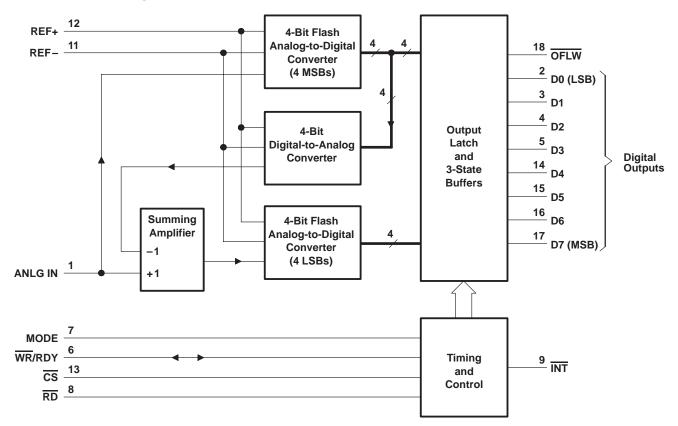

# functional block diagram

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

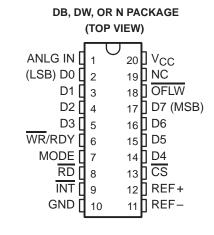

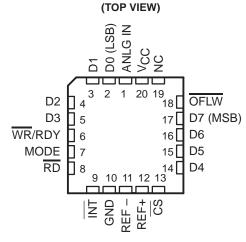

# **Terminal Functions**

| TERMINAL |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ANLG IN  | 1   | 1   | Analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CS       | 13  | ı   | Chip select. CS must be low in order for RD or WR to be recognized by the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D0       | 2   | 0   | Digital, 3-state output data, bit 1 (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D1       | 3   | 0   | Digital, 3-state output data, bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D2       | 4   | 0   | Digital, 3-state output data, bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D3       | 5   | 0   | Digital, 3-state output data, bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D4       | 14  | 0   | Digital, 3-state output data, bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D5       | 15  | 0   | Digital, 3-state output data, bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D6       | 16  | 0   | Digital, 3-state output data, bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D7       | 17  | 0   | Digital, 3-state output data, bit 8 (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GND      | 10  |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ĪNT      | 9   | 0   | Interrupt. In the write-read mode, the interrupt output ( $\overline{\text{INT}}$ ) going low indicates that the internal count-down delay time, $t_{d(int)}$ , is complete and the data result is in the output latch. The delay time $t_{d(int)}$ is typically 800 ns starting after the rising edge of $\overline{\text{WR}}$ (see operating characteristics and Figure 3). If $\overline{\text{RD}}$ goes low prior to the end of $t_{d(int)}$ , $\overline{\text{INT}}$ goes low at the end of $t_{d(RL)}$ and the conversion results are available sooner (see Figure 2). $\overline{\text{INT}}$ is reset by the rising edge of either $\overline{\text{RD}}$ or $\overline{\text{CS}}$ .        |

| MODE     | 7   | I   | Mode select. MODE is internally tied to GND through a 50-μA current source, which acts like a pulldown resistor. When MODE is low, the read mode is selected. When MODE is high, the write-read mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NC       | 19  |     | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OFLW     | 18  | 0   | Overflow. Normally OFLW is a logical high. However, if the analog input is higher than V <sub>fef+</sub> , OFLW will be low at the end of conversion. It can be used to cascade two or more devices to improve resolution (9 or 10 bits).                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RD       | 8   | I   | Read. In the write-read mode with $\overline{CS}$ low, the 3-state data outputs D0 through D7 are activated when $\overline{RD}$ goes low. $\overline{RD}$ can also be used to increase the conversion speed by reading data prior to the end of the internal count-down delay time. As a result, the data transferred to the output latch is latched after the falling edge of $\overline{RD}$ . In the read mode with $\overline{CS}$ low, the conversion starts with $\overline{RD}$ going low. $\overline{RD}$ also enables the 3-state data outputs on completion of the conversion. RDY going into the high-impedance state and $\overline{INT}$ going low indicate completion of the conversion. |

| REF-     | 11  | I   | Reference voltage. REF – is placed on the bottom of the resistor ladder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| REF+     | 12  | I   | Reference voltage. REF+ is placed on the top of the resistor ladder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Vcc      | 20  |     | Power supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WR/RDY   | 6   | I/O | Write ready. In the write-read mode with $\overline{CS}$ low, the conversion is started on the falling edge of the $\overline{WR}$ input signal. The result of the conversion is strobed into the output latch after the internal count-down delay time, $t_{d(int)}$ , provided that the $\overline{RD}$ input does not go low prior to this time. The delay time $t_{d(int)}$ is approximately 800 ns. In the read mode, RDY (an open-drain output) goes low after the falling edge of $\overline{CS}$ and goes into the high-impedance state when the conversion is strobed into the output latch. It is used to simplify the interface to a microprocessor system.                                  |

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>CC</sub> (see Note 1)                                      | 10 V                               |

|-----------------------------------------------------------------------------------|------------------------------------|

| Input voltage range, all inputs (see Note 1)                                      | -0.2 V to V <sub>CC</sub> +0.2 V   |

| Output voltage range, all outputs (see Note 1)                                    | -0.2 V to V <sub>CC</sub> +0.2 V   |

| Operating free-air temperature range: TLC0820AC                                   | 0°C to 70°C                        |

| TLC0820AI                                                                         | $-40^{\circ}$ C to $85^{\circ}$ C  |

| Storage temperature range                                                         | $-65^{\circ}$ C to $150^{\circ}$ C |

| Case temperature for 10 seconds: FN package                                       | 260°C                              |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: DB, DW or N package | e 260°C                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltages are with respect to network GND.

# recommended operating conditions

|                                                             |                                    |                | MIN                | NOM | MAX                  | UNIT |

|-------------------------------------------------------------|------------------------------------|----------------|--------------------|-----|----------------------|------|

| Supply voltage, V <sub>CC</sub>                             | 4.5 5                              |                |                    |     |                      |      |

| Analog input voltage                                        |                                    |                | -0.1               |     | V <sub>CC</sub> +0.1 | V    |

| Positive reference voltage, V <sub>ref+</sub>               |                                    |                | V <sub>ref</sub> _ |     | VCC                  | V    |

| Negative reference voltage, V <sub>ref</sub> _              |                                    |                | GND                |     | V <sub>ref+</sub>    | V    |

| High level input valtage VIII                               | V <sub>CC</sub> = 4.75 V to 5.25 V | CS, WR/RDY, RD | 2                  |     |                      | V    |

| High-level input voltage, V <sub>IH</sub>                   | VCC = 4.73 V 10 3.23 V             | MODE           | 3.5                |     |                      | V    |

| Low level input voltage. Viv                                | Va a 4.75 V to 5.25 V              | CS, WR/RDY, RD |                    |     | 0.8                  | V    |

| Low-level input voltage, V <sub>IL</sub>                    | V <sub>CC</sub> = 4.75 V to 5.25 V | MODE           |                    |     | 1.5                  | V    |

| Pulse duration, write in write-read mode, $t_{W(W)}$ (see F | igures 2, 3, and 4)                |                | 0.5                |     | 50                   | μs   |

| Operating two air temperature T.                            | TLC0820AC                          | 0              |                    | 70  | °C                   |      |

| Operating free-air temperature, T <sub>A</sub>              | TLC0820AI                          |                | -40                |     | 85                   | 30   |

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

# electrical characteristics at specified operating free-air temperature, $V_{CC} = 5 \text{ V}$ (unless otherwise noted)

|                                       | PARAMETER                                       |                                     | TEST CONDITIONS                                        | T <sub>A</sub> † | MIN   | TYP    | MAX  | UNIT |

|---------------------------------------|-------------------------------------------------|-------------------------------------|--------------------------------------------------------|------------------|-------|--------|------|------|

| .,                                    | High-level output voltage                       | D0-D7, $\overline{\text{INT}}$ , or | $V_{CC} = 4.75 \text{ V},$ $I_{OH} = -360 \mu\text{A}$ | Full range       | 2.4   |        |      | .,   |

| VOH                                   |                                                 | OFLW                                | V <sub>CC</sub> = 4.75 V,                              | Full range       | 4.5   |        |      | V    |

|                                       |                                                 |                                     | I <sub>OH</sub> = -10 μA                               | 25°C             | 4.6   |        |      |      |

| Vol                                   | Low-level output voltage                        | D0-D7, OFLW, INT,                   | $V_{CC} = 5.25 \text{ V},$                             | Full range       |       |        | 0.4  | ٧    |

| VOL                                   | Low-level output voltage                        | or WR/RDY                           | I <sub>OL</sub> = 1.6 mA                               | 25°C             |       |        | 0.34 | V    |

|                                       |                                                 | CS or RD                            | ]                                                      | Full range       |       | 0.005  | 1    |      |

|                                       |                                                 | WR/RDY                              |                                                        | Full range       |       |        | 3    |      |

| lіН                                   | High-level input current                        | WICKET                              | V <sub>IH</sub> = 5 V                                  | 25°C             |       | 0.1    | 0.3  | μΑ   |

|                                       |                                                 | MODE                                |                                                        | Full range       |       |        | 200  |      |

|                                       |                                                 |                                     |                                                        | 25°C             |       | 50     | 170  |      |

| I <sub>IL</sub>                       | Low-level input current                         | CS, WR/RDY, RD, or MODE             | V <sub>IL</sub> = 0                                    | Full range       |       | -0.005 | -1   | μΑ   |

|                                       | Off-state (high-impedance-state) output current |                                     | V <sub>O</sub> = 5 V                                   | Full range       |       |        | 3    |      |

|                                       |                                                 | D0-D7 or WR/RDY                     | ΛO = 2 Λ                                               | 25°C             |       | 0.1    | 0.3  | μΑ   |

| loz                                   |                                                 |                                     | V <sub>O</sub> = 0                                     | Full range       |       |        | -3   |      |

|                                       |                                                 |                                     | AO = 0                                                 | 25°C             |       | -0.1   | -0.3 |      |

|                                       |                                                 | -                                   | CS at 5 V, V <sub>I</sub> = 5 V                        | Full range       |       |        | 3    |      |

| ١.                                    | Analog input current                            |                                     | CS  at  S  V,  V  = S  V                               | 25°C             |       |        | 0.3  | μА   |

| l <sub>l</sub>                        | Analog input current                            | CS at 5 V, $V_I = 0$                | Full range                                             |                  |       | -3     | μΑ   |      |

|                                       |                                                 |                                     | CS  at $S$ $V$ , $V$ $  = 0$                           | 25°C             |       |        | -0.3 |      |

|                                       |                                                 | D0-D7, OFLW, INT,                   | V <sub>O</sub> = 5 V                                   | Full range       | 7     |        |      |      |

|                                       |                                                 | or WR/RDY                           | V() = 5 V                                              | 25°C             | 8.4   | 14     |      |      |

| loo                                   | Short-circuit output current                    | D0-D7 or OFLW                       |                                                        | Full range       | -6    |        |      | mA   |

| los                                   | Short-circuit output current                    | DO-D7 OF OFLW                       | V <sub>O</sub> = 0                                     | 25°C             | -7.2  | -12    |      | ША   |

|                                       |                                                 | INT                                 | ] VO = 0                                               | Full range       | -4.5  |        |      |      |

|                                       |                                                 | IINI                                |                                                        | 25°C             | - 5.3 | -9     |      |      |

| ъ,                                    | Poforonco reciptanco                            |                                     |                                                        | Full range       | 1.25  |        | 6    | kΩ   |

| R <sub>ref</sub> Reference resistance |                                                 |                                     |                                                        | 25°C             | 1.4   | 2.3    | 5.3  | K22  |

| loc                                   | Supply current                                  |                                     | CS, WR/RDY, and RD at 0 V                              | Full range       |       |        | 15   | mA   |

| ICC                                   | очрріу сипені                                   | RD at 0 V                           | 25°C                                                   |                  | 7.5   | 13     | IIIA |      |

| C.                                    | Input capacitance                               | D0-D7                               |                                                        | Full range       |       | 5      |      | pF   |

| Ci                                    | приссараснансе                                  | ANLG IN                             |                                                        | i uli range      |       | 45     |      | ρı   |

| Co                                    | Output capacitance                              | D0-D7                               |                                                        | Full range       |       |        | 5    | pF   |

<sup>†</sup> Full range is as specified in recommended operating conditions.

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

# operating characteristics, $V_{CC}$ = 5 V, $V_{ref+}$ = 5 V, $V_{ref-}$ = 0, $t_r$ = $t_f$ = 20 ns, $T_A$ = 25°C (unless otherwise noted)

|                      | PARAMETER                                       | TEST                                        | CONDITIONS†                         | MIN  | TYP         | MAX             | UNIT |

|----------------------|-------------------------------------------------|---------------------------------------------|-------------------------------------|------|-------------|-----------------|------|

| ksvs                 | Supply-voltage sensitivity                      | $V_{CC} = 5 V \pm 5\%$ ,                    | $T_A = MIN \text{ to } MAX$         | ±    | 1/16        | ±1/4            | LSB  |

|                      | Total unadjusted error‡                         | MODE at 0 V,                                | $T_A = MIN \text{ to } MAX$         |      |             | 1               | LSB  |

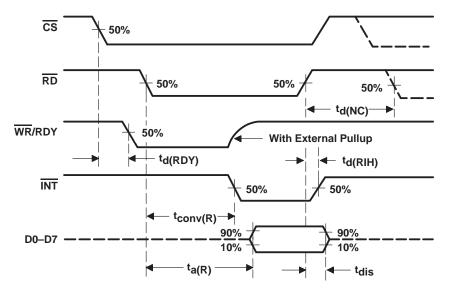

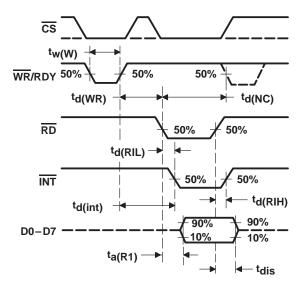

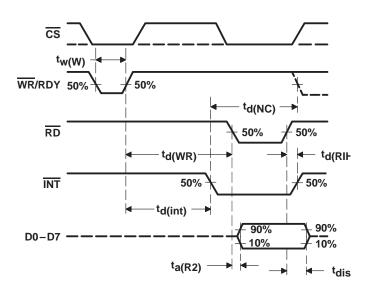

| tconv(R)             | Conversion time, read mode                      | MODE at 0 V,                                | See Figure 1                        |      | 1.6         | 2.5             | μs   |

| <sup>t</sup> a(R)    | Access time, RD↓ to data valid                  | MODE at 0 V,                                | See Figure 1                        | tcon | v(R)<br>+20 | tconv(R)<br>+50 | ns   |

|                      | . = . =                                         | MODE at 5 V,                                | C <sub>L</sub> = 15 pF              |      | 190         | 280             |      |

| <sup>t</sup> a(R1)   | Access time, RD↓ to data valid                  | td(WR) < td(int),<br>See Figure 2           | C <sub>L</sub> = 100 pF             |      | 210         | 320             | ns   |

| 4                    | Access for a DD to determine                    | MODE at 5 V,                                | C <sub>L</sub> = 15 pF              |      | 70          | 120             |      |

| ta(R2)               | Access time, RD↓ to data valid                  | td(WR) > td(int),<br>See Figure 3           | C <sub>L</sub> = 100 pF             |      | 90          | 150             | ns   |

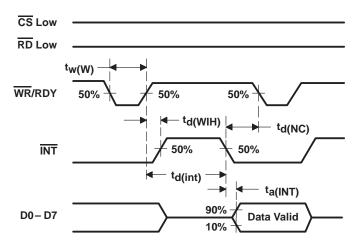

| ta(INT)              | Access time, INT ↓ to data valid                | MODE at 5 V,                                | See Figure 4                        |      | 20          | 50              | ns   |

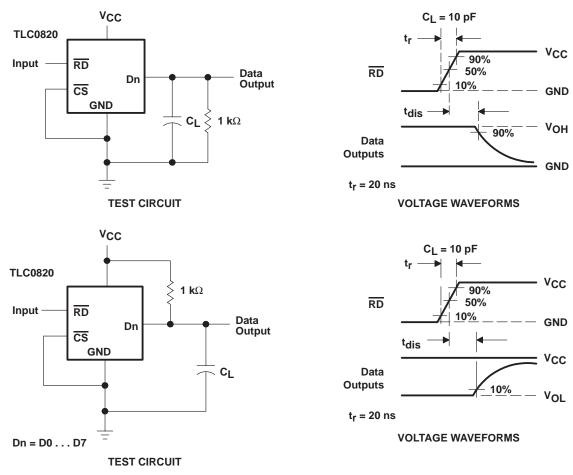

| t <sub>dis</sub>     | Disable time, RD↑ to data valid                 | R <sub>L</sub> = 1 kΩ,<br>See Figures 1, 2, | C <sub>L</sub> = 10 pF,<br>3, and 5 |      | 70          | 95              | ns   |

| <sup>t</sup> d(int)  | Delay time, WR/RDY↑ to INT↓                     | MODE at 5 V,<br>See Figures 2, 3,           | C <sub>L</sub> = 50 pF,<br>and 4    |      | 800         | 1300            | ns   |

| t <sub>d</sub> (NC)  | Delay time, to next conversion                  | See Figures 1, 2,                           | 3, and 4                            | 500  |             |                 | ns   |

| t <sub>d(WR)</sub>   | Delay time, WR/RDY↑ to RD↓ in write-read mode   | See Figure 2                                |                                     | 0.4  |             |                 | μs   |

| <sup>t</sup> d(RDY)  | Delay time, CS↓ to WR/RDY↓                      | MODE at 0 V,<br>See Figure 1                | C <sub>L</sub> = 50 pF,             |      | 50          | 100             | ns   |

| t <sub>d</sub> (RIH) | Delay time, RD↑ to INT↑                         | C <sub>L</sub> = 50 pF,                     | See Figures 1, 2, and 3             |      | 125         | 225             | ns   |

| td(RIL)              | Delay time, RD $\downarrow$ to INT $\downarrow$ | MODE at 5 V,<br>See Figure 2                | $t_{d(WR)} < t_{d(int)}$            |      | 200         | 290             | ns   |

| td(WIH)              | Delay time, WR/RDY↑ to INT↑                     | MODE at 5 V,<br>See Figure 4                | C <sub>L</sub> = 50 pF,             |      | 175         | 270             | ns   |

|                      | Slew-rate tracking                              |                                             |                                     |      | 0.1         |                 | V/µs |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>‡</sup> Total unadjusted error includes offset, full-scale, and linearity errors.

#### PARAMETER MEASUREMENT INFORMATION

Figure 1. Read-Mode Waveforms (MODE Low)

Figure 2. Write-Read-Mode Waveforms [MODE High and t<sub>d(WR)</sub> < t<sub>d(int)</sub>]

Figure 3. Write-Read-Mode Waveforms [MODE High and  $t_{d(WR)} > t_{d(int)}$ ]

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

#### PARAMETER MEASUREMENT INFORMATION

Figure 4. Write-Read-Mode Waveforms (Stand-Alone Operation, MODE High, and RD Low)

Figure 5. Test Circuit and Voltage Waveforms

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

# PRINCIPLES OF OPERATION

The TLC0820AC and TLC0820AI each employ a combination of sampled-data comparator techniques and flash techniques common to many high-speed converters. Two 4-bit flash analog-to-digital conversions are used to give a full 8-bit output.

The recommended analog input voltage range for conversion is -0.1 V to  $V_{CC} + 0.1 \text{ V}$ . Analog input signals that are less than  $V_{ref-} + 1/2 \text{ LSB}$  or greater than  $V_{ref+} - 1/2 \text{ LSB}$  convert to 00000000 or 111111111, respectively. The reference inputs are fully differential with common-mode limits defined by the supply rails. The reference input values define the full-scale range of the analog input. This allows the gain of the ADC to be varied for ratiometric conversion by changing the  $V_{ref-}$  and  $V_{ref-}$  voltages.

The device operates in two modes, read (only) and write-read, that are selected by MODE. The converter is set to the read (only) mode when MODE is low. In the read mode,  $\overline{WR}/RDY$  is used as an output and is referred to as the ready terminal. In this mode, a low on  $\overline{WR}/RDY$  while  $\overline{CS}$  is low indicates that the device is busy. Conversion starts on the falling edge of  $\overline{RD}$  and is completed no more than 2.5  $\mu$ s later when  $\overline{INT}$  falls and  $\overline{WR}/RDY$  returns to the high-impedance state. Data outputs also change from high-impedance to active states at this time. After the data is read,  $\overline{RD}$  is taken high,  $\overline{INT}$  returns high, and the data outputs return to their high-impedance states.

When MODE is high, the converter is set to the write-read mode and  $\overline{WR}/RDY$  is referred to as the write terminal. Taking  $\overline{CS}$  and  $\overline{WR}/RDY$  low selects the converter and initiates measurement of the input signal. Approximately 600 ns after  $\overline{WR}/RDY$  returns high, the conversion is completed. Conversion starts on the rising edge of  $\overline{WR}/RDY$  in the write-read mode.

The high-order 4-bit flash ADC measures the input by means of 16 comparators operating simultaneously. A high-precision 4-bit DAC then generates a discrete analog voltage from the result of that conversion. After a time delay, a second bank of comparators does a low-order conversion on the analog difference between the input level and the high-order DAC output. The results from each of these conversions enter an 8-bit latch and are output to the 3-state output buffers on the falling edge of  $\overline{RD}$ .

# SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

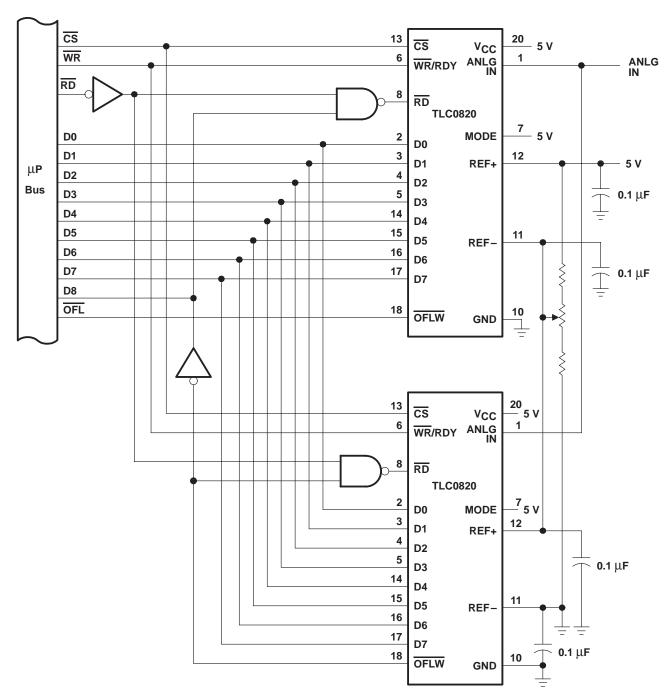

# **APPLICATION INFORMATION**

Figure 6. Configuration for 9-Bit Resolution

10-Jun-2014

# **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish (6) | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Sample |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|----------------------|--------------------|--------------|-------------------------|--------|

| TLC0820ACDB      | ACTIVE | SSOP         | DB                 | 20   | 70             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM | 0 to 70      | P0820A                  | Sample |

| TLC0820ACDBR     | ACTIVE | SSOP         | DB                 | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM |              | P0820A                  | Sample |

| TLC0820ACDW      | ACTIVE | SOIC         | DW                 | 20   | 25             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM |              | TLC0820A                | Sample |

| TLC0820ACDWG4    | ACTIVE | SOIC         | DW                 | 20   | 25             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM |              | TLC0820A                | Sample |

| TLC0820ACDWR     | ACTIVE | SOIC         | DW                 | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM |              | TLC0820A                | Sample |

| TLC0820ACDWRG4   | ACTIVE | SOIC         | DW                 | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM |              | TLC0820A                | Sample |

| TLC0820ACFN      | ACTIVE | PLCC         | FN                 | 20   | 46             | Green (RoHS<br>& no Sb/Br) | CU SN                | Level-1-260C-UNLIM |              | TLC0820AC               | Sample |

| TLC0820ACN       | ACTIVE | PDIP         | N                  | 20   | 20             | Pb-Free<br>(RoHS)          | CU NIPDAU            | N / A for Pkg Type |              | TLC0820ACN              | Sample |

| TLC0820ACNE4     | ACTIVE | PDIP         | N                  | 20   | 20             | Pb-Free<br>(RoHS)          | CU NIPDAU            | N / A for Pkg Type |              | TLC0820ACN              | Sample |

| TLC0820AIDW      | ACTIVE | SOIC         | DW                 | 20   | 25             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM |              | TLC0820AI               | Sample |

| TLC0820AIDWG4    | ACTIVE | SOIC         | DW                 | 20   | 25             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM |              | TLC0820AI               | Sample |

| TLC0820AIDWR     | ACTIVE | SOIC         | DW                 | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM |              | TLC0820AI               | Sample |

| TLC0820AIDWRG4   | ACTIVE | SOIC         | DW                 | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM |              | TLC0820AI               | Sample |

| TLC0820AIFN      | ACTIVE | PLCC         | FN                 | 20   | 46             | Green (RoHS<br>& no Sb/Br) | CU SN                | Level-1-260C-UNLIM |              | TLC0820AI               | Sample |

| TLC0820AIN       | ACTIVE | PDIP         | N                  | 20   | 20             | Pb-Free<br>(RoHS)          | CU NIPDAU            | N / A for Pkg Type |              | TLC0820AIN              | Sample |

| TLC0820AINE4     | ACTIVE | PDIP         | N                  | 20   | 20             | Pb-Free<br>(RoHS)          | CU NIPDAU            | N / A for Pkg Type |              | TLC0820AIN              | Sample |

<sup>(1)</sup> The marketing status values are defined as follows: **ACTIVE:** Product device recommended for new designs.

# PACKAGE OPTION ADDENDUM

10-Jun-2014

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jan-2013

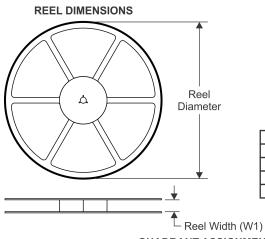

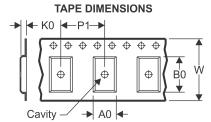

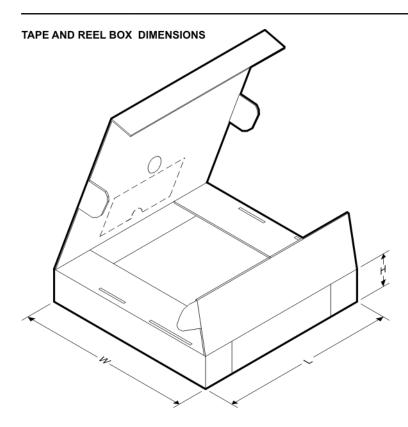

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

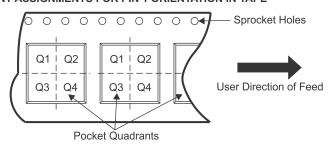

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLC0820ACDBR | SSOP            | DB                 | 20 | 2000 | 330.0                    | 16.4                     | 8.2        | 7.5        | 2.5        | 12.0       | 16.0      | Q1               |

| TLC0820ACDWR | SOIC            | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8       | 13.3       | 2.7        | 12.0       | 24.0      | Q1               |

| TLC0820AIDWR | SOIC            | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8       | 13.3       | 2.7        | 12.0       | 24.0      | Q1               |

www.ti.com 3-Jan-2013

\*All dimensions are nominal

| 7 till dillitorioriorio di o mominidi |              |                 |      |      |             |            |             |

|---------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                                | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TLC0820ACDBR                          | SSOP         | DB              | 20   | 2000 | 367.0       | 367.0      | 38.0        |

| TLC0820ACDWR                          | SOIC         | DW              | 20   | 2000 | 367.0       | 367.0      | 45.0        |

| TLC0820AIDWR                          | SOIC         | DW              | 20   | 2000 | 367.0       | 367.0      | 45.0        |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom Amplifiers amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="https://www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="https://example.com/omap">e2e.ti.com/omap</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А