# High-Speed 12-Bit ADC With External Reference Input Part

### **General Description**

The MX7672 is a 12-bit, high-speed, BiCMOS, analog-todigital converter (ADC) that performs conversions in as little as  $3\mu$ s while consuming only 110mW of power. The MX7672 is a plug-in replacement for AD7672.

The MX7672 requires an external -5V reference. A buffered reference input minimizes reference current requirements and allows a single reference to drive several ADCs. External reference specifications can be chosen to suit the accuracy of the application. The ADC clock can be driven from either a crystal or an external clock source, such as a microprocessor ( $\mu$ P) clock.

Average input range is pin-selectable for 0 to +5V, 0 to +10V, or  $\pm$ 5V, making the ADC ideal for data-acquisition and analog input/output cards. A high-speed digital interface (125ns data-access time) with three-state data outputs is compatible with most µPs.

### **Applications**

- Telecommunications

- Sonar and Radar Signal Processing

- High-Speed Data-Acquisition Systems

- Personal Computer I/O Boards

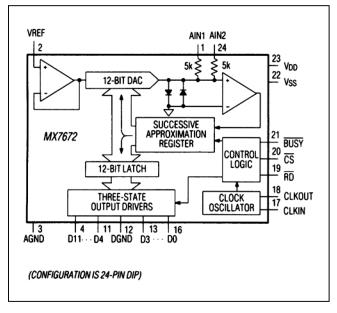

### **Functional Diagram**

### Features

- Plug-In Replacement for AD7672

- 12-Bit Resolution and Accuracy

- Fast Conversion Time

- MX7672\_03 3µs

- MX7672\_05 5µs

- MX7672\_10 10µs

- Operates with +5V and -12V Supplies

- Buffered Reference Input

- Low 110mW Power Consumption

- Choice of +5V, +10V, or ±5V Input Ranges

- Fast 125ns Bus-Access Time

Ordering Information appears at end of data sheet.

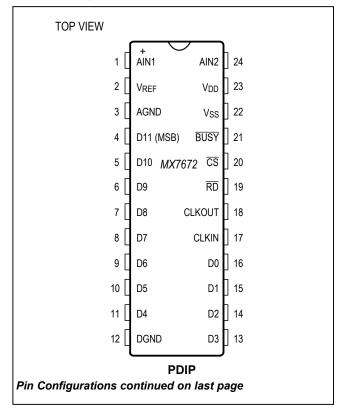

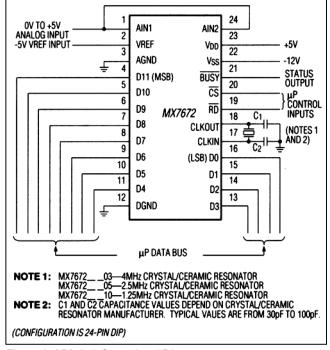

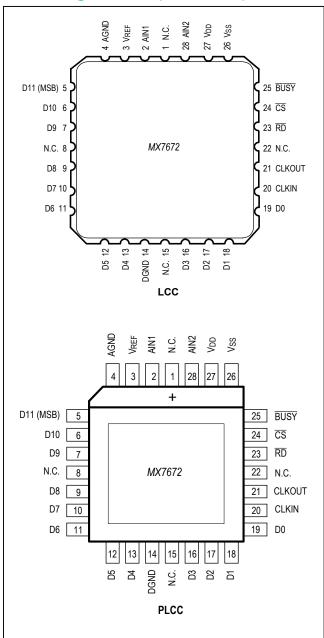

### **Pin Configurations**

# High-Speed 12-Bit ADC With External Reference Input Part

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to DGND0.3V to +7V                             |

|----------------------------------------------------------------|

| V <sub>SS</sub> to DGND+0.3V to -17V                           |

| AGND to DGND0.3V to $(V_{DD} + 0.3V)$                          |

| AIN1, AIN2 to AGND15V to +15V                                  |

| $V_{REF}$ to AGND( $V_{SS}$ - 0.3V) to ( $V_{DD}$ + 0.3V)      |

| Digital Input Voltage to DGND                                  |

| (CLKIN, <del>CS</del> , <del>RD</del> )                        |

| Digital Output Voltage to DGND                                 |

| (D11–D0, <u>BUSY</u> , CLKOUT)0.3V to (V <sub>DD</sub> + 0.3V) |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )          |

| PDIP (derate 13.3mW/°C above +70°C)1067mW                      |

| PLCC (derate 10.5mW/°C above +70°C)842mW                       |

| LCC (derate 10.2mW/°C above +70°C)816mW                        |

| Operating Temperature Ranges      |                |

|-----------------------------------|----------------|

| MX7672K_/L                        | 0°C to +70°C   |

| MX7672B_/C                        | 40°C to +85°C  |

| MX7672T_/U                        | 55°C to +125°C |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    |                |

| PDIP, LCC                         | +260°C         |

| PLCC                              | +245°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

(V<sub>DD</sub> = +5V ±5%, V<sub>SS</sub> = -12V ±10%, V<sub>REF</sub> = -5V, slow-memory mode;  $f_{CLK}$  = 4MHz for MX7672\_ 03,  $f_{CLK}$  = 2.5MHz for MX7672\_ 05,  $f_{CLK}$  = 1.25MHz for MX7672\_ 10;  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                 | SYMBOL | CONDITIONS          |                                 |    | ТҮР | MAX  | UNITS |

|---------------------------|--------|---------------------|---------------------------------|----|-----|------|-------|

| ACCURACY (Note 1)         | ·      |                     |                                 |    |     |      |       |

| Resolution                | N      |                     |                                 | 12 |     |      | Bits  |

|                           |        |                     | MX7672C/L                       |    |     | ±1/2 |       |

| Integral Nanlinggrity     | INL    | Tootod range (E)/   | MX7672U, T <sub>A</sub> = +25°C |    |     | ±1/2 |       |

| Integral Nonlinearity     |        | Tested range ±5V    | MX7672U                         |    |     | ±3/4 | - LSB |

|                           |        |                     | MX7672B/K/T                     |    |     | ±1   |       |

| Differential Nonlinearity | DNL    | 12 bits, no missing | codes over temperature          |    |     | ±0.9 | LSB   |

|                           |        | MX7672C/L/U         | T <sub>A</sub> = +25°C          |    |     | ±3   |       |

| Unipolar Offset Error     |        | WIX7072C/L/U        | $T_A = T_{MIN}$ to $T_{MAX}$    |    |     | ±4   | - LSB |

|                           |        | MX7672B/K/T         | T <sub>A</sub> = +25°C          |    |     | ±5   | – LSB |

|                           |        |                     | $T_A = T_{MIN}$ to $T_{MAX}$    |    |     | ±6   |       |

|                           |        | MX7672C/L/U         | T <sub>A</sub> = +25°C          |    |     | ±4   | – LSB |

| Unipolar Gain Error       |        | MX7672B/K/T         | $T_A = T_{MIN}$ to $T_{MAX}$    |    |     | ±6   |       |

|                           |        |                     | T <sub>A</sub> = +25°C          |    |     | ±5   |       |

|                           |        |                     | $T_A = T_{MIN}$ to $T_{MAX}$    |    |     | ±7   |       |

|                           |        | MX7672C/L/U         | T <sub>A</sub> = +25°C          |    |     | ±3   |       |

| Bipolar Zero Error        |        |                     | $T_A = T_{MIN}$ to $T_{MAX}$    |    |     | ±4   | - LSB |

|                           |        | MX7672B/K/T         | T <sub>A</sub> = +25°C          |    |     | ±5   |       |

|                           |        |                     | $T_A = T_{MIN}$ to $T_{MAX}$    |    |     | ±6   |       |

| Bipolar Gain Error        |        | MX7672C/L/U         | T <sub>A</sub> = +25°C          |    |     | ±4   |       |

|                           |        |                     | $T_A = T_{MIN}$ to $T_{MAX}$    |    |     | ±6   | - LSB |

|                           |        | MX7672B/K/T         | T <sub>A</sub> = +25°C          |    |     | ±5   | LJD   |

|                           |        |                     | $T_A = T_{MIN}$ to $T_{MAX}$    |    |     | ±7   |       |

# High-Speed 12-Bit ADC With External Reference Input Part

### **Electrical Characteristics (continued)**

$(V_{DD} = +5V \pm 5\%, V_{SS} = -12V \pm 10\%, V_{REF} = -5V, \text{ slow-memory mode; } f_{CLK} = 4MHz \text{ for } MX7672\_03, f_{CLK} = 2.5MHz \text{ for } MX7672\_05, f_{CLK} = 1.25MHz \text{ for } MX7672\_10; T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.})$

| PARAMETER                                           | SYMBOL            | CONDITIONS                                                                  |                                    | MIN   | ТҮР  | MAX   | UNITS    |

|-----------------------------------------------------|-------------------|-----------------------------------------------------------------------------|------------------------------------|-------|------|-------|----------|

|                                                     |                   | MX7672_03                                                                   |                                    |       |      | 3.125 |          |

|                                                     |                   | Synchronous Clk<br>(12.5 clks)                                              | MX767205                           |       |      | 5     | LSB      |

|                                                     |                   |                                                                             | MX7672_10                          |       |      | 10    | 1        |

| Conversion Time                                     | <sup>t</sup> CONV |                                                                             | MX7672_03                          | 3.0   |      | 3.25  |          |

|                                                     |                   | Asynchronous Clk<br>(12 to 13 clks)                                         | MX767205                           | 4.8   |      | 5.2   | LSB      |

|                                                     |                   |                                                                             | MX7672_10                          | 9.6   |      | 10.4  | 1        |

| ANALOG AND REFERENCE IN                             | PUTS              |                                                                             |                                    |       |      |       |          |

| Analog Input Current (AIN1/                         |                   | Unipolar input range                                                        | es 0 to +5V, 0 to +10V             |       |      | 3.5   |          |

| AIN2)                                               |                   | Bipolar range ±5V                                                           |                                    |       |      | ±1.75 | - mA     |

| V <sub>REF</sub> Input Range (Note 2)               |                   |                                                                             |                                    | -5.05 |      | -4.95 | V        |

| V <sub>REF</sub> Input Current                      |                   |                                                                             |                                    |       |      | ±3    | μA       |

| LOGIC                                               |                   |                                                                             |                                    |       |      |       |          |

| Input Low Voltage                                   | V <sub>INL</sub>  | CS, RD, CLKIN                                                               |                                    |       |      | 0.8   | V        |

| Input High Voltage                                  | V <sub>INH</sub>  | CS, RD, CLKIN                                                               |                                    | 2.4   |      |       | V        |

| Innut Current                                       | I <sub>IN</sub>   | $\overline{CS}$ , $\overline{RD}$ ; $V_{IN}$ = 0V to $V_{DD}$               |                                    |       |      | ±10   |          |

| Input Current                                       |                   | CLKIN; V <sub>IN</sub> = 0V to                                              |                                    |       | ±20  | - μΑ  |          |

| Input Capacitance (Note 2)                          | C <sub>IN</sub>   |                                                                             |                                    |       |      | 10    | pF       |

| Output Low Voltage                                  | V <sub>OL</sub>   | D11–D0, BUSY, CLKOUT, I <sub>SINK</sub> = 1.6mA                             |                                    |       |      | 0.4   | V        |

| Output High Voltage                                 | V <sub>OH</sub>   | D11–D0, BUSY, CLKOUT,<br>I <sub>SOURCE</sub> = 200µA                        |                                    | 4.0   |      |       | V        |

| High-Impedance State Leakage<br>Current             | <sup>I</sup> LKG  | D11–D0, $V_{OUT}$ = 0V to $V_{DD}$                                          |                                    |       |      | ±10   | μΑ       |

| High-Impedance State Output<br>Capacitance (Note 2) | C <sub>OUT</sub>  |                                                                             |                                    |       |      | 15    | pF       |

| POWER REQUIREMENTS                                  |                   | 1                                                                           |                                    | 1     |      |       | 4        |

| 0 1 1 1 1                                           | V <sub>DD</sub>   |                                                                             |                                    | 4.75  | 5    | 5.25  | <u> </u> |

| Supply Voltage                                      | V <sub>SS</sub>   |                                                                             |                                    | -13.2 | -12  | -10.8 | - V      |

|                                                     | I <sub>DD</sub>   | $\overline{\text{CS}} = \overline{\text{RD}} = V_{\text{DD}}, V_{\text{A}}$ | $V_{\rm IN1} = V_{\rm AIN2} = 5V,$ |       |      | 7     |          |

| Supply Current                                      | I <sub>SS</sub>   | BUSY = HIGH                                                                 |                                    |       |      | -12   | - mA     |

| Power Dissipation                                   | PD                | V <sub>DD</sub> = 5V, V <sub>SS</sub> = -12V                                |                                    | 1     | 110  | 179   | mW       |

| Power-Supply Rejection,<br>V <sub>DD</sub> Only     |                   | FS change, V <sub>SS</sub> = -12V, V <sub>DD</sub> = 4.75V<br>to 5.25V      |                                    |       | ±1/4 | ±2    | LSB      |

| Power-Supply Rejection,<br>V <sub>SS</sub> Only     |                   | FS change, V <sub>DD</sub> = 8<br>to -13.2V                                 | 5V, V <sub>SS</sub> = -10.8V       |       | ±1/2 | ±1    | LSB      |

# High-Speed 12-Bit ADC With External Reference Input Part

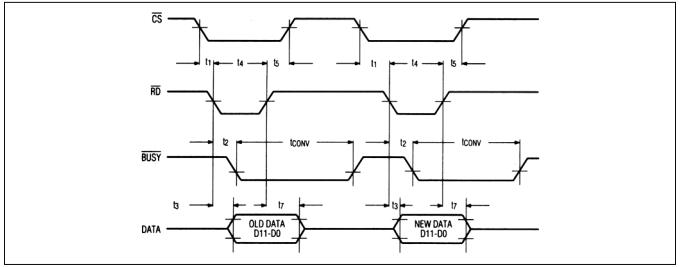

### **Timing Characteristics**

$(V_{DD} = +5V, V_{SS} = -12V, 100\%$  production tested, unless otherwise noted.) (Note 3, Figures 7, 9, 10)

| PARAMETER                                   | SYMBOL          | CONDITIONS             | T <sub>A</sub> = +25°C<br>ALL GRADES |     | T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub><br>MX7672K/L/B/C |                | T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub><br>MX7672T/U |     | UNITS          |     |     |    |

|---------------------------------------------|-----------------|------------------------|--------------------------------------|-----|------------------------------------------------------------------------|----------------|--------------------------------------------------------------------|-----|----------------|-----|-----|----|

|                                             |                 |                        | MIN                                  | TYP | MAX                                                                    | MIN            | TYP                                                                | MAX | MIN            | TYP | MAX |    |

| CS to RD Setup Time<br>(Note 2)             | t <sub>1</sub>  |                        | 0                                    |     |                                                                        | 0              |                                                                    |     | 0              |     |     | ns |

| RD to BUSY Delay                            | t <sub>2</sub>  | C <sub>L</sub> = 50pF  |                                      | 70  | 190                                                                    |                |                                                                    | 230 |                |     | 270 | ns |

| Data-Access Time (Note 4)                   | t <sub>3</sub>  | C <sub>L</sub> = 100pF |                                      | 50  | 125                                                                    |                |                                                                    | 150 |                |     | 170 | ns |

| RD Pulse Width (Note 2)                     | t <sub>4</sub>  |                        | t <sub>3</sub>                       |     |                                                                        | t <sub>3</sub> |                                                                    |     | t <sub>3</sub> |     |     | ns |

| CS to RD Hold Time<br>(Note 2)              | t <sub>5</sub>  |                        | 0                                    |     |                                                                        | 0              |                                                                    |     | 0              |     |     | ns |

| Data-Setup Time After<br>BUSY (Note 4)      | t <sub>6</sub>  | C <sub>L</sub> = 100pF |                                      | 40  | 70                                                                     |                |                                                                    | 90  |                |     | 100 | ns |

| Bus-Relinquish Time<br>(Note 5)             | t7              |                        |                                      | 30  | 75                                                                     |                |                                                                    | 85  |                |     | 90  | ns |

| Delay Between Read<br>Operations            | t <sub>8</sub>  |                        | 200                                  |     |                                                                        | 200            |                                                                    |     | 200            |     |     | ns |

| CLKIN to BUSY Delay<br>(Note 2)             | t9              |                        |                                      |     | 120                                                                    |                |                                                                    | 150 |                |     | 180 | ns |

| RD to CLKIN Setup/Hold<br>Time (Notes 2, 6) | <sup>t</sup> 10 |                        | 25                                   |     | 100                                                                    | 25             |                                                                    | 100 | 25             |     | 100 | ns |

Note 1: V<sub>DD</sub> = +5V, V<sub>SS</sub> = -12V, 1 LSB = FS/4096. Performance over power-supply tolerance is guaranteed by power-supply rejection test.

Note 2: Guaranteed by design.

Note 3: All inputs are 0 to +5V swing with  $t_r = t_f = 5ns (10\% to 90\% of +5V)$  and timed from a voltage level of +1.6V.

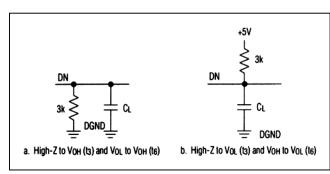

**Note 4:**  $t_3$  and  $t_6$  are measured with the load circuits of Figure 1 and defined as the time required for an output to cross +0.8V or +2.4V.

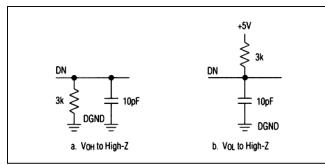

Note 5: t<sub>7</sub> is defined as the time required for the data lines to change 0.5V when loaded with the circuit of Figure 2.

Note 6: For predictable conversion times, RD to CLKIN falling edge must be outside this window. If t<sub>10</sub> < 25ns, conversion will skip first falling CLKIN edge and start on second falling CLKIN edge. If t<sub>10</sub> > 100ns, conversion will start on first falling CLKIN edge.

# High-Speed 12-Bit ADC With External Reference Input Part

## **Pin Description**

| PIN    |              |                  | FUNCTION                                                                                                                                              |  |  |  |

|--------|--------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 24-PIN | 28-PIN       | NAME             | FUNCTION                                                                                                                                              |  |  |  |

| _      | 1, 8, 15, 22 | N.C.             | No Connection                                                                                                                                         |  |  |  |

| 1      | 2            | AIN1             | Analog Input                                                                                                                                          |  |  |  |

| 2      | 3            | V <sub>REF</sub> | Voltage-Reference Input                                                                                                                               |  |  |  |

| 3      | 4            | AGND             | Analog Ground                                                                                                                                         |  |  |  |

| 4–11   | 5–13         | D11–D4           | Three-State Data Outputs. They are active when $\overline{CS}$ and $\overline{RD}$ are low. D11 is the most significant bit.                          |  |  |  |

| 12     | 14           | DGND             | Digital Ground                                                                                                                                        |  |  |  |

| 13–16  | 16–19        | D3–D0            | Three-State Data Outputs                                                                                                                              |  |  |  |

| 17     | 20           | CLKIN            | Clock Input. Connect an external TTL-compatible clock to CLKIN. Alternatively, insert a crystal or ceramic resonator between CLKIN and CLKOUT.        |  |  |  |

| 18     | 21           | CLKOUT           | Clock Output. When using an external clock, an inverted CLKIN signal appears on CLKOUT. See CLKIN description.                                        |  |  |  |

| 19     | 23           | RD               | $\overline{\text{READ}}$ Input. Along with $\overline{\text{CS}}$ , this active-low signal enables the three-state drivers and starts a conversion.   |  |  |  |

| 20     | 24           | CS               | $\overline{\text{CHIP SELECT}}$ . Along with $\overline{\text{RD}}$ , this active-low signal enables the three-state drivers and starts a conversion. |  |  |  |

| 21     | 25           | BUSY             | BUSY. Low while a conversion is in progress. BUSY indicates converter status.                                                                         |  |  |  |

| 22     | 26           | V <sub>SS</sub>  | Negative Supply, -12V                                                                                                                                 |  |  |  |

| 23     | 27           | V <sub>DD</sub>  | Positive Supply, +5V                                                                                                                                  |  |  |  |

| 24     | 28           | AIN2             | Analog Input                                                                                                                                          |  |  |  |

Figure 1. Load Circuits for Access Time

Figure 2. Load Circuits for Bus-Relinquish Time

Figure 3. MX7672 Operational Diagram

# High-Speed 12-Bit ADC With External Reference Input Part

### **Detailed Description**

#### **Converter Operation**

The MX7672 uses a successive approximation technique to convert an analog input to a 12-bit digital output code. The control logic provides easy interface to most  $\mu$ Ps (Figure 3).

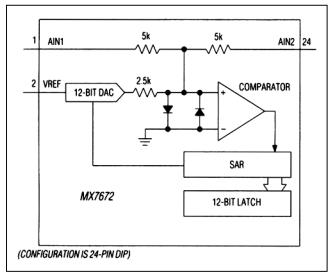

Figure 4 shows the MX7672 analog-equivalent circuit. The internal digital-to-analog converter (DAC) is controlled by a successive approximation register (SAR), has an output impedance of  $2.5k\Omega$ , and connects directly to the comparator input. The analog inputs AIN1 and AIN2 connect to the same comparator input through  $5k\Omega$  resistors.

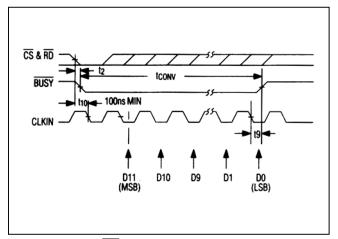

A conversion starts at the falling edge of  $\overline{CS}$  and  $\overline{RD}$  and cannot be restarted after initiation. The  $\overline{BUSY}$  output goes low when the conversion starts and can be used to control an external sample-and-hold when measuring wide bandwidth input signals.

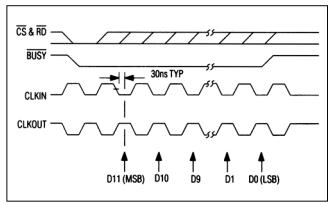

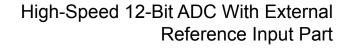

The SAR is set, asynchronously with the clock input, to half scale when  $\overline{CS}$  and  $\overline{RD}$  go low. At the second falling edge of CLKIN (or rising edge of CLKOUT) following a conversion start, the output of the comparator is latched into the SAR most significant bit (MSB/D11) (Figure 5). The MSB is kept if the analog input is greater than half scale or dropped if it is smaller. The next bit (D10) is then set with the DAC output either at 1/4 scale (if the MSB was dropped) or 3/4 scale (if the MSB was kept). The conversion continues in this manner until the LSB is tried. At conversion end, following a falling CLKIN signal,  $\overline{BUSY}$ goes high, and the SAR result is latched into three-state output buffers.

Figure 4. MX7672 AIN Inputs

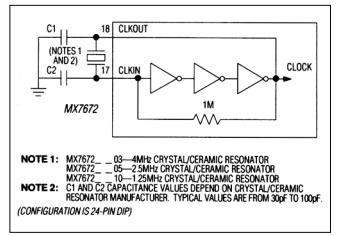

### Clock

#### Internal Clock Oscillator

Figure 6 shows the MX7672 clock circuitry. Minimize the capacitive load on the CLKOUT pin for low power dissipation and to avoid digital coupling of the CLKOUT buffer current to the comparator. CLKOUT should be left open if an external clock source is used to drive CLKIN. Connect a crystal/ceramic resonator between CLKOUT and CLKIN if the internal oscillator is used.

### **Control Inputs Synchronization**

When  $\overline{\text{RD}}$  is not synchronized with the ADC clock, the conversion time can vary from 12 to 13 clock cycles. The SAR changes state on the falling edge of the CLKIN input (or rising edge on the CLKOUT pin). Use the following guidelines to ensure a fixed conversion time: The MX7672  $\overline{\text{RD}}$  input should go low at the rising edge of CLKIN. In this case, the conversion lasts 12.5 clock cycles, and

Figure 5. Operating Waveforms Using an External Clock Source for CLKIN

Figure 6. MX7672 Internal Clock Circuit

the conversion time is 3.125µs when  $f_{CLK} = 4MHz$ , 5µs when  $f_{CLK} = 2.5MHz$ , and 10µs when  $f_{CLK} = 1.25MHz$ . The delay from the falling edge of  $\overline{RD}$  to the falling edge of CLKIN must not be less than 100ns to ensure the 12.5 clock cycle conversion time (Figure 7). This gives the external sample-and-hold 1.5 clock cycles to settle from hold transients. An additional 1/2 clock cycle of settling can be allowed for the sample-and-hold by having  $\overline{RD}$  go low at the falling edge of CLKIN. This results in a 13-cycle conversion time (3.25µs, 5.2µs, and 10.4µs).

### **Digital Interface**

#### **Timing and Control**

$\overline{\text{CS}}$  and  $\overline{\text{RD}}$  control conversion start and data-read operations. Figure 8 shows the logic equivalent for the conversion and the data-output control circuitry. A logic-low at both inputs starts a conversion. Once a conversion is in progress, it cannot be restarted. The  $\overline{\text{BUSY}}$  output remains low during the entire conversion cycle.

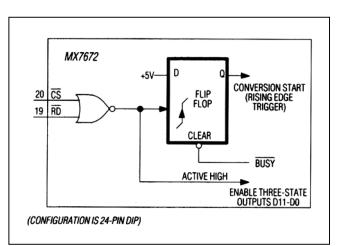

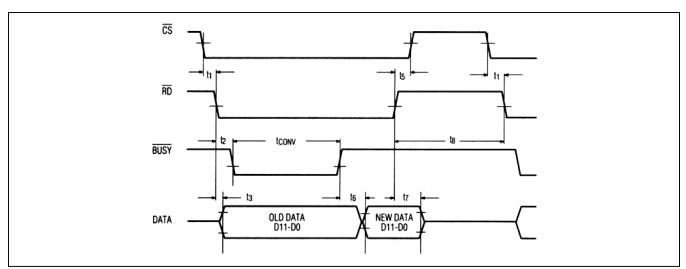

Figures 9 and 10 outline the two interface modes (slow memory and ROM). Slow-memory mode is for  $\mu$ Ps that can be forced into a wait state for periods as long as the MX7672 conversion time. ROM mode is for  $\mu$ Ps that cannot be forced into a wait state. In both interface modes, a processor read operation to the ADC address starts the conversion. In the ROM mode, a second read operation accesses the conversion result.

#### **Slow-Memory Mode**

The timing diagram in Figure 9 illustrates slow-memory mode, which is designed for  $\mu$ Ps with a wait state.  $\overline{CS}$  and  $\overline{RD}$  go low, triggering a conversion, and are kept low until the conversion is complete.  $\overline{BUSY}$  responds by going low, and data from the previous conversion remains on the three-state data outputs. At conversion end,  $\overline{BUSY}$  returns high, and the output latches transfer the new conversion results to the three-state data outputs. The  $\mu$ P completes the read operation by taking  $\overline{CS}$  and  $\overline{RD}$  high.

#### **ROM Mode**

The ROM mode avoids placing the  $\mu$ P into a wait state. A conversion begins with a read operation. While  $\overline{CS}$  and  $\overline{RD}$  are low, data from the last conversion is available on the data outputs. A second read operation reads the new data and begins the conversion process again. A delay at least as long as the MX7672 conversion time must be allowed between read operations. The data on the output bus is in a parallel format in either mode.

### **Application Hints**

### **Digital Bus Noise**

If the data bus connected to the ADC is active during a conversion, coupling from the data pins to the ADC comparator may cause LSBs of error. Using slow-memory mode avoids this problem by placing the  $\mu$ P into a wait state during the conversion. In ROM mode, if the data bus is active during the conversion, use three-state drivers to isolate the bus from the ADC.

Figure 7. MX7672 RD and CLKIN for Synchronous Operation and Conversion Time of 12.5 Clock Cycles

Figure 8. Logic for Control Inputs CS and RD Internal

# High-Speed 12-Bit ADC With External Reference Input Part

### **ROM Mode**

Digital noise is generated in the ADC when  $\overline{RD}$  or  $\overline{CS}$  go high, and the output data drivers are disabled after a conversion is started. This noise will feed into the ADC comparator and cause large errors if it coincides with the time the SAR is latching a bit decision. To avoid this problem,  $\overline{RD}$  and  $\overline{CS}$  should be active for less than one clock cycle. In other words, the  $\overline{RD}$  and  $\overline{CS}$  low pulse should be less than 250ns for the MX7672\_\_03, 400ns for the MX7672\_\_05, and 1µs for the MX7672\_\_10. If this cannot be done, the  $\overline{RD}$  or  $\overline{CS}$  signal must go high at a rising edge of CLKIN, since the comparator output is always latched at falling edges of CLKIN.

#### **Physical Layout**

For the best system performance, PCBs should be used for the MX7672; wire-wrap boards are not recommended. Separate the digital-analog-signal lines as much as possible in the board layout. Do not run analog and digital lines parallel to each other or digital lines underneath the MX7672 package.

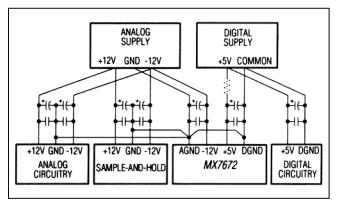

#### Grounding

Figure 11 shows the recommended system ground connections. Establish a single-point analog ground (star ground), separate from the logic ground, at AGND of the MX7672. Connect all other analog grounds and DGND of the MX7672 to this star ground (no other digital grounds should be connected to this point). For noise-free operation of the ADC, use a low-impedance ground return to the power supply from this star ground.

#### **Power-Supply Bypassing**

The ADC's high-speed comparator is sensitive to high-frequency noise in the V<sub>DD</sub> and V<sub>SS</sub> power supplies. These supplies should be bypassed to the analog star ground with 0.1µF and 10µF bypass capacitors with minimum lead length for supply noise rejection. If the +5V power supply is very noisy, a small (10 $\Omega$  to 20 $\Omega$ ) resistor can be connected (Figure 11) to filter external noise.

#### **Driving the Analog Input**

The input signal leads to AIN and the input return leads to AGND should be as short as possible to minimize input noise coupling. Use shielded cables if the leads must be long.

The input impedance at each AIN is typically  $5k\Omega$ . The amplifier driving AIN must have low enough DC output impedance for low gain error. Furthermore, low AC output impedance is needed since the analog input current is modulated at the clock rate during a conversion (up to 4MHz for MX7672\_\_03, 2.5MHz for MX7672\_\_05, or 1.25MHz for the MX7672\_\_10). The output impedance of

the driving amplifier is equal to its open-loop output impedance divided by the loop gain at the frequency of interest.

**MX7672\_\_05/10** - The MX7672\_\_05/10 maximum clock rate of 2.5MHz makes it possible to drive AIN with amplifiers like the OP42, AD711 or a Maxim OP27. A MAX400 or a Maxim OP07 can also be used up to 1.25MHz clock rate.

**MX7672\_03** - The MX7672\_03, with a maximum 4MHz clock rate, might exhibit settling problems with the above amplifiers. An LF356, LF400, or LT1056 can be used to drive the input. Alternatively, an emitter follower buffer inside the feedback loop of a Maxim OP27, an OP42, or an AD711 improves high-frequency output impedance.

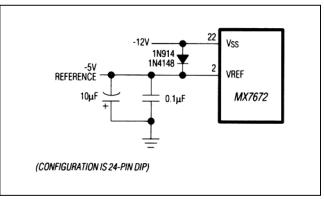

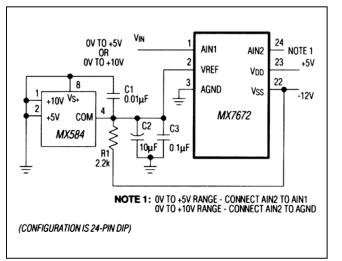

#### **Reference Input**

$V_{REF}$  connects to an external -5V source. This may be either a precision negative reference, a positive reference (such as the MX584) connected as a two-terminal device to provide -5V (Figure 16), or an existing system reference. The allowed input range at REFIN is -5.1V to -4.9V.  $V_{REF}$  (and AIN2 in bipolar input operation) should be bypassed to ground with a 10µF electrolytic capacitor in parallel with a 0.1µF ceramic capacitor.

If the external reference is biased from a power supply other than  $V_{SS}$ , care must be taken to ensure that  $V_{SS}$  is applied to the ADC before  $V_{REF}$ . If supply sequencing is uncertain, connect a diode between  $V_{SS}$  and  $V_{REF}$ , as shown in Figure 12. No diode is needed if the reference source is powered from the same supply as  $V_{SS}$ .

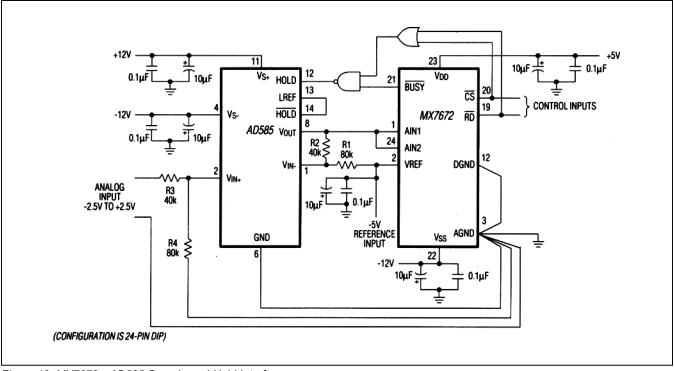

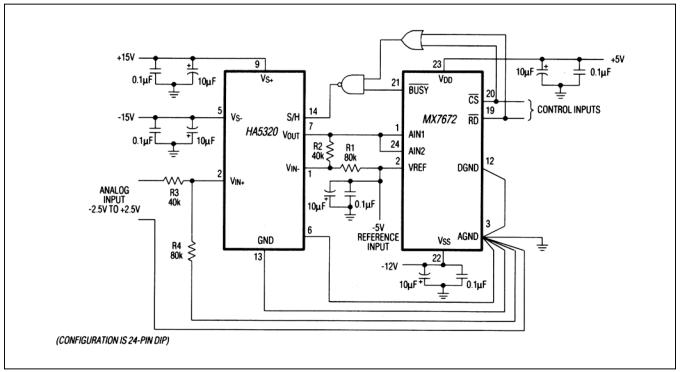

### MX7672 to Sample-and-Hold Interface

The analog input to the ADC must be stable to within 1/2 LSB during the entire conversion for specified 12-bit accuracy. This limits the input-signal bandwidth to less than 6Hz for sinusoidal inputs, even when using the faster MX7672\_03. A sample-and-hold should be used for higher bandwidth signals.

The BUSY output from the MX7672 may be used to provide the TRACK/HOLD signal to the sample-and-hold amplifier. However, since the ADC's DAC is switched at approximately the same time as the BUSY signal goes low, sample-and-hold transients caused by DAC switching may result in code-dependent errors due to sample-and-hold aperture delay. Adding a NAND (inverted AND) gate ensures that the sample-and-hold is switched to the hold mode BEFORE any disturbances occur (Figures 13 and 14). The NAND gate solution works only if the width of the RD pulse is wider than the RD to BUSY delay in the MX7672. If this is not the case, use a flip-flop, which is set by the falling edge of RD and reset by the rising edge of BUSY.

# High-Speed 12-Bit ADC With External Reference Input Part

Figure 9. Slow-Memory Mode Timing Diagram

Figure 10. ROM-Mode Timing Diagram

Figure 11. Power-Supply Grounding Practice

Figure 12. V<sub>REF</sub>/V<sub>SS</sub> Diode Clamp (See Reference Input section)

# High-Speed 12-Bit ADC With External Reference Input Part

Figure 13. MX7672—AD585 Sample-and-Hold Interface

Figure 14. MX7672—HA5320 Sample-and-Hold Interface

# High-Speed 12-Bit ADC With External Reference Input Part

For synchronous  $\overline{RD}$  and CLKIN, the hold settling time allowed for the sample-and-hold is 375ns (MX7672\_03), 600ns (MX7672\_05), and 1.5µs (MX7672\_10).

The maximum sampling rate is 125kHz with a 2.5MHz clock and 64.5kHz with a 1MHz clock, allowing for a  $3\mu$ s sample-and-hold acquisition time.

Although this circuit works well for the 1MHz clock rate, a faster sample-and-hold amplifier, such as the HA5320, is recommended at a 2.5MHz clock rate.

**MX7672\_03**—Figure 14 is the MX7672\_03 to HA5320 interface. The maximum sampling rate is 210kHz wtth a 4MHz clock, which allows a 1.5µs acquisition time. The HA5320 can also be replaced by a HA5330 for higher throughput.

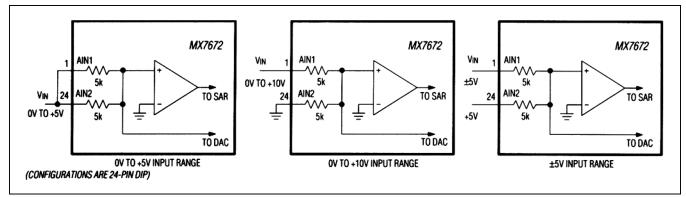

### **Analog Input Ranges**

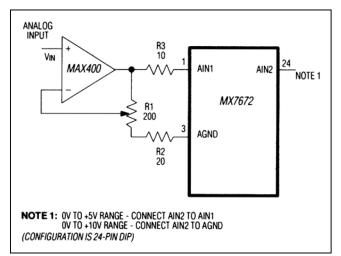

The MX7672 provides three selectable analog input ranges: 0 to +5V, 0 to +10V, and  $\pm5V$ . Figure 15 shows the

configuration for the two analog inputs (AIN1 and AIN2) for these ranges.

#### **Unipolar Operation**

Figure 16 shows unipolar operation using an MX584 voltage reference configured for -5V.

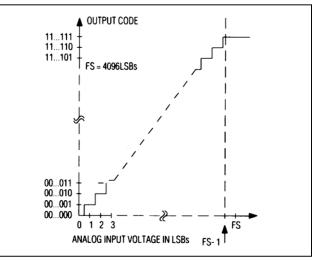

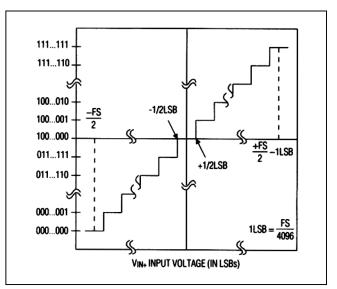

Figure 17 shows the nominal input/output transfer function of the MX7672. Code transitions occur halfway between successive integer LSB values. The output coding is binary with 1 LSB = Full Scale (FS)/4096. FS is either +5V or +10V, based on the analog input configurations.

### **Offset and Full-Scale Adjustment**

In applications requiring offset and FS range adjustment, use the circuit in Figure 18. **Note:** The amplifier shown could also be a sample-and-hold. Offset should be adjusted first. Apply  $\frac{1}{2}$  LSB (0.61mV) at the analog input (AIN1 or AIN2) and adjust the offset of the amplifier until

Figure 15. Analog Input Range Configurations

Figure 16. Unipolar Operation Using an MX584 Reference

Figure 17. MX7672 Ideal Unipolar Transfer Function

the digital output code changes between 0000 0000 0000 and 0000 0000 0001.

0V to +5V range: 1/2 LSB = 0.61mV

0V to +10V range: 1/2 LSB = 1.22mV

To adjust the full-scale range, apply FS - 3/2 LSB (last code transition) at the analog input and adjust R1 until the output code switches between 1111 1111 1110 and 1111 1111 1111.

0V to +5V range: FS - 3/2 LSB = 4.99817V 0V to +10V range: FS - 3/2 LSB = 9.99634V

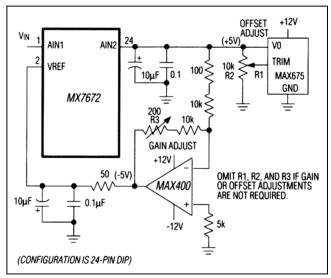

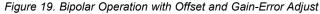

#### **Bipolar Operation**

The bipolar input range is ±5V.  $V_{\rm IN}$  is applied to AIN1. +5V to AIN2, and -5V to  $V_{\rm REF}$ . This requires two reference voltages: -5V for the  $V_{\rm REF}$  input and +5V for the AIN2 input. Figure 19 shows these reference voltages are produced from a MAX675 reference and a MAX400 op amp configured as an inverting amplifier.

The ideal input/output transfer characteristic after offset and gain adjustment is shown in Figure 20. The LSB is 2.44mV (10V/4096).

The resistors used in bipolar applications should be the same type from the same manufacturer to obtain low temperature drifts. 0.1% resistors are recommended for applications where offset and full-scale adjustments must be made in bipolar circuits. If low tolerances are used, larger value potentiometers must be used, which results in poor trim resolution and higher temperature drift.

### **Offset and Gain Adjustment**

In bipolar operation, the offset is trimmed at negative full scale and should always be adjusted first. For offset,

Figure 18. Unipolar Operation with Gain Adjust

## High-Speed 12-Bit ADC With External Reference Input Part

apply -FS/2 +  $\frac{1}{2}$  LSB (-4.99878V) at V<sub>IN</sub> and adjust the 10k $\Omega$  potentiometer (Figure 18) until the output code switches between 0000 0000 0000 and 0000 0000 0001.

Gain is adjusted at full scale or bipolar zero. For full-scale adjustment, apply FS/2 - 3/2 LSBs (4.99634V) to V<sub>IN</sub> and adjust the 200 $\Omega$  potentiometer until the output code switches between 1111 1111 1110 and 1111 1111 1111.

Alternatively, to adjust gain at bipolar zero, apply -1.22mV at V<sub>IN</sub> and adjust the 200 $\Omega$  potentiometer until the output code switches between 0111 1111 1111 and 1000 0000 0000.

Figure 20. Ideal Input/Output Transfer Characteristic for Bipolar Operation

# High-Speed 12-Bit ADC With External Reference Input Part

### **Pin Configurations (continued)**

### **Ordering Information**

| PART                        | TEMP RANGE      | PIN-<br>PACKAGE      | LINEARITY<br>(LSB) |  |  |  |  |  |

|-----------------------------|-----------------|----------------------|--------------------|--|--|--|--|--|

| 3µs MAXIMUM CONVERSION TIME |                 |                      |                    |  |  |  |  |  |

| MX7672KN03+                 | 0°C to +70°C    | 24 PDIP              | ±1                 |  |  |  |  |  |

| MX7672KP03+                 | 0°C to +70°C    | 28 PLCC <sup>+</sup> | ±1                 |  |  |  |  |  |

| MX7672BE03+                 | -40°C to +85°C  | 28 LCC <sup>+</sup>  | ±1                 |  |  |  |  |  |

| 5µs MAXIMUM                 | CONVERSION TIM  | IE                   |                    |  |  |  |  |  |

| MX7672KN05+                 | 0°C to +70°C    | 24 PDIP              | ±1                 |  |  |  |  |  |

| MX7672LN05+                 | 0°C to +70°C    | 24 PDIP              | ±1⁄2               |  |  |  |  |  |

| MX7672KP05+                 | 0°C to +70°C    | 28 PLCC <sup>+</sup> | ±1                 |  |  |  |  |  |

| MX7672LP05+                 | 0°C to +70°C    | 28 PLCC <sup>+</sup> | ±1⁄2               |  |  |  |  |  |

| MX7672TE05+                 | -55°C to +125°C | 28 LCC <sup>+*</sup> | ±1                 |  |  |  |  |  |

| MX7672UE05+                 | -55°C to +125°C | 28 LCC <sup>+*</sup> | ±3/4               |  |  |  |  |  |

| 10µs MAXIMUM                | CONVERSION TI   | ME                   |                    |  |  |  |  |  |

| MX7672KN10+                 | 0°C to +70°C    | 24 PDIP              | ±1                 |  |  |  |  |  |

| MX7672LN10+                 | 0°C to +70°C    | 24 PDIP              | ±1/2               |  |  |  |  |  |

| MX7672KP10+                 | 0°C to +70°C    | 28 PLCC <sup>+</sup> | ±1                 |  |  |  |  |  |

| MX7672LP10+                 | 0°C to +70°C    | 28 PLCC <sup>+</sup> | ±1⁄2               |  |  |  |  |  |

| MX7672TE10+                 | -55°C to +125°C | 28 LCC <sup>+*</sup> | ±1                 |  |  |  |  |  |

| MX7672UE10+                 | -55°C to +125°C | 28 LCC <sup>+*</sup> | ±3/4               |  |  |  |  |  |

+Denotes a lead(Pb)-free/RoHS-compliant package.

†Contact factory for availability.

\*Contact factory for processing to MIL-STD-883.

### **Chip Information**

PROCESS: BiCMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 24 PDIP         | N24+3           | <u>21-0043</u> | —                   |

| 28 PLCC         | Q28+2           | <u>21-0049</u> | 90-0235             |

| 28 LCC          | L28+2           | 21-4497        | <u>90-0178</u>      |

# High-Speed 12-Bit ADC With External Reference Input Part

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                      | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------------------------------|------------------|

| 0                  | 4/91             | Initial release                                  | —                |

| 1                  | 1/12             | Remove CERDIP packages from Ordering Information | 1, 13            |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

«JONHON» (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«FORSTAR» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный) Факс: 8 (812) 320-03-32 Электронная почта: ocean@oceanchips.ru Web: http://oceanchips.ru/ Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А