# MLX90288

#### Datasheet

#### 1. Features and Benefits

- Surface mounted device

- Analog ratiometric output

- Measurement range from ±6.5mT to ±650mT bipolar full scale

- Digital IIR filtering for accurate bandwidth

- Offset trimming possible outside output range

- 1st and 2nd order magnet TC compensation

- Reverse polarity and overvoltage protection

- Extensive diagnostic features

# 2. Application Examples

- Rotary position sensor

- Linear position sensor

- Proximity sensor

## 3. Description

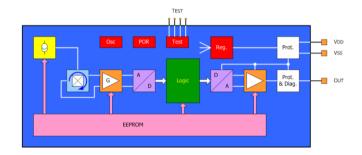

The MLX90288 is a cost-effective monolithic programmable linear Hall sensor which provides an analog ratiometric output signal proportional to the magnetic flux density that is applied perpendicular to the die surface. The MLX90288 is fully programmable (offset, sensitivity, clamping levels, magnet temperature drift, digital IIR filtering ...) through the connector, using the PTC-04 programming tool. It supports both linear and quadratic magnet TC compensation.

Figure 1: gives the block diagram

[DOC. № 3901090288]

# **Contents**

| 1. Features and Benefits                                                                                                                                                                                                                                 | 1                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2. Application Examples                                                                                                                                                                                                                                  | 1                    |

| 3. Description                                                                                                                                                                                                                                           | 1                    |

| 4. Ordering Information                                                                                                                                                                                                                                  | 4                    |

| 5. Glossary of Terms                                                                                                                                                                                                                                     | 5                    |

| 6. Pin Definitions and Descriptions                                                                                                                                                                                                                      | 5                    |

| 6.1. Pin Definition for SOIC-8                                                                                                                                                                                                                           | 5                    |

| 6.2. Pin Definition for TSSOP-14                                                                                                                                                                                                                         | 6                    |

| 7. Absolute Maximum Ratings                                                                                                                                                                                                                              | 7                    |

| 8. General Electrical Specifications                                                                                                                                                                                                                     | 8                    |

| 9. Timing Specification                                                                                                                                                                                                                                  | 9                    |

| 10. Transfer Characteristic Specification                                                                                                                                                                                                                | 10                   |

| 11. Accuracy Specification                                                                                                                                                                                                                               | 11                   |

| 12. Diagnostic Specification                                                                                                                                                                                                                             | 12                   |

| 13. Startup, Undervoltage, Overvoltage and Reset Specification                                                                                                                                                                                           | 13                   |

| 14. EMC/ESD Specification                                                                                                                                                                                                                                | 15                   |

|                                                                                                                                                                                                                                                          |                      |

| 15. EEPROM Mapping                                                                                                                                                                                                                                       | 15                   |

| 15. EEPROM Mapping                                                                                                                                                                                                                                       |                      |

| 15. EEPROM Mapping                                                                                                                                                                                                                                       | 15                   |

| 15.1. EEPROM Description                                                                                                                                                                                                                                 | 15                   |

| 15.1. EEPROM Description                                                                                                                                                                                                                                 | 15<br>16             |

| 15.1. EEPROM Description                                                                                                                                                                                                                                 | 15<br>16<br>16       |

| 15.1. EEPROM Description                                                                                                                                                                                                                                 | 15<br>16<br>16<br>16 |

| 15.1. EEPROM Description                                                                                                                                                                                                                                 |                      |

| 15.1. EEPROM Description  15.2. Melexis Programmed Parameters  15.2.1. OSCTRIM [4:0]  15.2.2. TRIMCTAT [4:0]  15.2.3. ITRIM[2:0]  15.2.4. IPLATE[3:0]  15.2.5. TC1ST[6:0]  15.2.6. TC2ND[5:0]  15.2.7. TC3RD[2:0]  15.2.8. PLATEPOL                      |                      |

| 15.1. EEPROM Description  15.2. Melexis Programmed Parameters  15.2.1. OSCTRIM [4:0]  15.2.2. TRIMCTAT [4:0]  15.2.3. ITRIM[2:0]  15.2.4. IPLATE[3:0]  15.2.5. TC1ST[6:0]  15.2.6. TC2ND[5:0]  15.2.7. TC3RD[2:0]  15.2.8. PLATEPOL  15.2.9. OFFCST[4:0] |                      |

| 15.1. EEPROM Description  15.2. Melexis Programmed Parameters  15.2.1. OSCTRIM [4:0]                                                                                                                                                                     |                      |

#### Datasheet

| 21. Disclaimer                                                  |    |

|-----------------------------------------------------------------|----|

| 20. Contact                                                     |    |

| 19.6. TSSOP-14 Recommended Application Diagram                  | 27 |

| 19.5. SOIC-8 Recommended Application Diagram                    |    |

| 19.4. TSSOP-14 Package Marking                                  |    |

| 19.3. SOIC-8 Package Marking                                    |    |

| 19.2. TSSOP-14 Package Dimensions                               |    |

| 19.1. SOIC-8 Package Dimensions                                 |    |

| 19. Package Specification                                       |    |

| 18. ESD Precautions                                             |    |

| 17. Standard Information                                        |    |

| 16.4. Quadratic Compensation (2nd Order) - CAB and DAA versions |    |

| 16.3. Quadratic Compensation (2nd Order) - CAA                  |    |

| 16.2. Linear Compensation (1st Order)                           |    |

| 16.1. Introduction                                              |    |

| 16. Thermal Sensitivity Drift Compensation                      |    |

| 15.3.14. CSTID[15:0]                                            |    |

| 15.3.13. YA[13:0]                                               |    |

| 15.3.12. FINEGAIN[12:0]                                         |    |

| 15.3.11. ATTN2P5                                                |    |

| 15.3.10. ROUGHGAIN[1:0]                                         |    |

| 15.3.9. CLPHigh[9:0]                                            |    |

| 15.3.8. CLPLow[8:0]                                             |    |

| 15.3.7. TEMPTC[7:0]                                             |    |

| 15.3.6. TEMPOFF[9:0]                                            |    |

| 15.3.5. SECONDORDERTC                                           |    |

| 15.3.4. TEMPSENSOR                                              |    |

| 15.3.3. FILTCODE[3:0]                                           |    |

| 15.3.2. DIAGINFAULT                                             |    |

| 15.3.1. FAULTONCLIP                                             |    |

| 15.3. Customer Programmable Parameters                          |    |

# 4. Ordering Information

| Product  | Temperature | Package | Option Code | Packing Form | Definition |

|----------|-------------|---------|-------------|--------------|------------|

| MLX90288 | S           | DC      | CAB-000     | RE           |            |

| MLX90288 | K           | DC      | CAA-000     | RE           |            |

| MLX90288 | L           | DC      | CAA-000     | RE           |            |

| MLX90288 | L           | DC      | DAA-000     | RE           |            |

| MLX90288 | L           | GO      | CAB-002     | RE           |            |

Table 1: Ordering Codes

# Legend:

| Temperature Code: | S: from -20°C to 85°C  K: from -40°C to 125°C  L: from -40°C to 150°C                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package Code:     | DC: for SOIC-8 package GO: for TSSOP-14 package                                                                                                            |

| Option Code:      | CAA-000: Not recommended for new designs  CAB-000: Recommended for new designs  CAB-002: Recommended for new designs  DAA-000: Recommended for new designs |

| Packing Form:     | RE: Tape on Reel                                                                                                                                           |

| Ordering Example: | MLX90288LDC-DAA-000-RE                                                                                                                                     |

Table 2: Order codes Description

# 5. Glossary of Terms

| Gauss (G), Tesla (T) | Units for the magnetic flux density – 1 mT = 10 G |

|----------------------|---------------------------------------------------|

| ТС                   | Temperature Coefficient (in ppm/Deg.C.)           |

| ADC                  | Analog-to-Digital Converter                       |

| DAC                  | Digital-to-Analog Converter                       |

| LSB                  | Least Significant Bit                             |

| MSB                  | Most Significant Bit                              |

| DNL                  | Differential Non-Linearity                        |

| INL                  | Integral Non-Linearity                            |

| DSP                  | Digital Signal Processing                         |

| EMC                  | Electro-Magnetic Compatibility                    |

| FSM                  | Finite State Machine                              |

| OBD                  | On Board Diagnostic                               |

| N/C                  | Not Connected                                     |

Table 3: Glossary of Terms

# **6. Pin Definitions and Descriptions**

# 6.1. Pin Definition for SOIC-8

| Pin # | Name    | Description                |

|-------|---------|----------------------------|

| 1     | VDD     | Supply                     |

| 2     | VSS     | Ground                     |

| 3     | N/C     | Not connected              |

| 4     | OUT     | Analog + PTC communication |

| 5     | IDDQ    | Test                       |

| 6     | TESTOUT | Test                       |

| 7     | MUST0   | Test                       |

| 8     | MUST1   | Test                       |

REVISION 7 - 02-APR-2020 Page 5 of 28

Table 4: Pinout definition for SOIC-8 package

# 6.2. Pin Definition for TSSOP-14

| Pin # | Name    | Description                             |

|-------|---------|-----------------------------------------|

| 1     | MUST0   | Test Die 1                              |

| 2     | MUST1   | Test Die 1                              |

| 3     | VDD1    | Supply Die 1                            |

| 4     | VSS1    | Ground Die 1                            |

| 5     | OUT2    | Analog Output + PTC communication Die 2 |

| 6     | TESTOUT | Test Die 2                              |

| 7     | IDDQ    | Test Die 2                              |

| 8     | MUST0   | Test Die 2                              |

| 9     | MUST1   | Test Die 2                              |

| 10    | VDD2    | Supply Die 2                            |

| 11    | VSS2    | Ground Die 2                            |

| 12    | OUT1    | Analog Output + PTC communication Die 1 |

| 13    | IDDQ    | Test Die 1                              |

| 14    | TESTOUT | Test Die 1                              |

Table 5: Pinout definition for TSSOP-14 package

# 7. Absolute Maximum Ratings

| Item                                      | Symbol              | Rating (per die)                                                      |

|-------------------------------------------|---------------------|-----------------------------------------------------------------------|

| Supply Forward-Voltage                    | $V_{DDFWD}$         | + 30 V (continuous)<br>(Breakdown at + 40 V)                          |

| Supply Forward-Current                    | $I_{DDFWD}$         | + 20 mA                                                               |

| Supply Reverse-Voltage                    | $V_{\text{DDREV}}$  | <ul><li>– 14.5 V (continuous)</li><li>(Breakdown at – 19 V)</li></ul> |

| Supply Reverse-Current                    | I <sub>DDREV</sub>  | – 2 mA                                                                |

| Output Forward-Voltage                    | $V_{\text{OUTFWD}}$ | + 18 V                                                                |

| Output Forward-Current                    | I <sub>OUTFWD</sub> | – 60 mA                                                               |

| Output Reverse-Voltage                    | $V_{\text{OUTREV}}$ | – 14 V                                                                |

| Output Reverse-Current                    | I <sub>OUTREV</sub> | + 20 mA                                                               |

| Storage Temperature Range (Non-Operating) | T <sub>s</sub>      | -55°C to +165°C                                                       |

| Operating Ambient Temperature Range       | $T_A$               | -40°C to +150°C                                                       |

| Junction Temperature                      | TJ                  | +165°C                                                                |

| Package Thermal Resistance                | $R_{TH}$            | 100 K/W                                                               |

| Maximum Flux Density                      | $B_{MAX}$           | 2Т                                                                    |

Table 6: Absolute maximum ratings

Exceeding the absolute maximum ratings may cause permanent damage. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

REVISION 7 - 02-APR-2020 Page 7 of 28

# 8. General Electrical Specifications

General electrical specifications are valid for the selected temperature range and supply voltage range [4.5;5.5] V unless otherwise noted. Values are per-die.

| Parameter                            | Symbol                 | Remark                              | Min | Тур | Max  | Unit      |

|--------------------------------------|------------------------|-------------------------------------|-----|-----|------|-----------|

| Supply Voltage                       | $V_{DD}$               | Guaranteed spec operation           | 4.5 | 5   | 5.5  | V         |

| Supply Current                       | $I_{DD}$               | Worst case (min $R_{PD}$ , max VDD) | -   | 8.8 | 10   | mA        |

| Regulated Voltage                    | $V_{REG}$              | Internal voltage                    | 3.0 | 3.3 | 3.6  | V         |

| Reset Voltage                        | $V_{\text{PORRISE}}$   | Output is high impedant for         | 2.5 |     | 3.4  | V         |

| neset voltage                        | $V_{PORFALL}$          | $V_{POR} < V_{DD} < V_{UNDER}$      | 2.4 |     | 3.3  | V         |

| Undervoltage Threshold               | V <sub>UNDERRISE</sub> | Operating if $V_{DD} > V_{UNDER}$   | 3.4 |     | 4.4  | V         |

| Undervoltage Inreshold               | $V_{UNDERFALL}$        |                                     | 3.3 |     | 4.3  | V         |

| Programming Voltage <sup>(1)</sup>   | $V_{PROG}$             | Device not locked                   | 7.2 |     | 7.8  | V         |

| Overvoltage Threshold <sup>(2)</sup> | $V_{\text{OVER}}$      | Disconnect $V_{PROT}$ from $V_{DD}$ | 7.9 |     | 13.5 | V         |

| Load Resistance Range                | $R_{PD}$               | Pull-down to GND                    | 8   | 10  | 330  | kΩ        |

| Load capacitor range                 | $C_L$                  | Between OUT and GND                 | 47  |     | 1000 | nF        |

| Output Saturation                    | $V_{SATHI}$            | Including R <sub>PD</sub>           | 96  |     | 100  | $%V_{DD}$ |

| Voltage <sup>(3)</sup>               | $V_{SATLO}$            | Including R <sub>PD</sub>           | 0   |     | 2    | $%V_{DD}$ |

| Output Current                       | I <sub>OUTLIMGND</sub> | Output amplifier sourcing strength  | 2   | 5   | 8    | mA        |

| Limitation <sup>(4)</sup>            | I <sub>OUTLIMVDD</sub> | Output amplifier sinking strength   | 2   | 5   | 8    | mA        |

REVISION 7 - 02-APR-2020 Page 8 of 28

[DOC. № 3901090288]

<sup>&</sup>lt;sup>1</sup>The programming voltage defines the threshold at which the ASIC goes into PTC mode, where the output pin becomes bidirectional. Write access is eventually defined by the locking bits as described in subsequent sections.

<sup>&</sup>lt;sup>2</sup>The overvoltage threshold will disconnect all internal supplies (Vana, Vdig & Vprot) from VDD; the output becomes high impedant.

$<sup>^3</sup>$ The saturation voltage is the rail voltage the output amplifier can reach actively with  $R_{PD}$  connected.

<sup>&</sup>lt;sup>4</sup>The maximum current the output stage can deliver to keep its DC value, in case the output is pulled to one of the rails by means of an external power supply, while  $V_{DD} = 5V$ .

| Parameter                                                | Symbol              | Remark                                         | Min | Тур | Max               | Unit |

|----------------------------------------------------------|---------------------|------------------------------------------------|-----|-----|-------------------|------|

| Supply Current Limitation                                | I <sub>VDDLIM</sub> | Same condition as above                        | 5   |     | 18                | mA   |

| Output Diagnostic Band<br>Leakage Current <sup>(5)</sup> | I <sub>DIAGLO</sub> | Leakage current over $T_A$<br>$V_{DD}$ =5 $V$  |     |     | 500               | nA   |

| Output Diagnostic Level                                  | $V_{DIAGLO}$        | Leakage current over $T_{A}$ and $V_{DD}$ span |     |     | R <sub>PD</sub> x | V    |

Table 7: Electrical specifications

# 9. Timing Specification

| Parameter                             | Symbol               | Remark                                                                   | Min   | Тур  | Max   | Unit |

|---------------------------------------|----------------------|--------------------------------------------------------------------------|-------|------|-------|------|

| Power Supply Slew Rate                | VDDSR                | External supply VDD                                                      | 5e-6  |      | 5     | V/µs |

| Startup time <sup>(6)</sup>           | t <sub>STARTUP</sub> |                                                                          | 200   | 500  | 800   | μs   |

| Main Oscillator Frequency             | Fosc                 | Tolerance ± 10%                                                          | 900   | 1000 | 1100  | kHz  |

| Conversion Rate                       | $t_{CONV}$           | Acquisition of Hall and<br>Temperature signals (no<br>digital filtering) | 130   | 144  | 158   | μs   |

|                                       | $f_{\text{CONV}}$    |                                                                          | 6.33  | 7    | 7.7   | kHz  |

| Programmable Filtering <sup>(7)</sup> | BW                   | Tempsensor enabled                                                       | 0.004 |      | 1.114 | kHz  |

| Output Amplifier Rise Time            | t <sub>RISEPP</sub>  | $R_L$ = 8 k $\Omega$ to Ground                                           |       | 300  |       | μs   |

REVISION 7 - 02-APR-2020 Page 9 of 28

<sup>&</sup>lt;sup>5</sup>The leakage current is in fact the current sourced by the output in case of an OBD detection (broken ground), where the output goes into high-Z mode. For better contacting at the connectors over lifetime and bigger rail-to-rail operation, the smaller pull-down resistors from this specification are recommended at ECU side.

<sup>&</sup>lt;sup>6</sup>Startup time is defined as the time between crossing the POR level and having the first DAC output update. It includes loading of the parameters from EEPROM, checking the CRC validity, initializations and the signal latency between the first Hall plate acquisition and the DAC output update.

<sup>&</sup>lt;sup>7</sup>Filtering is programmable with the FILTCODE parameter in EEPROM. The filter consists of an IIR filter in the digital. For more details about the corresponding bandwidths, see subsequent sections.

| Parameter                                           | Symbol              | Remark                                                    | Min | Тур | Max | Unit |

|-----------------------------------------------------|---------------------|-----------------------------------------------------------|-----|-----|-----|------|

| (10%-90%) <sup>(8)</sup>                            |                     | C <sub>L</sub> = 330 nF to Ground                         |     |     |     |      |

| Output Amplifier Fall Time (90%-10%) <sup>(8)</sup> | t <sub>FALLPP</sub> | $R_L$ = 330 k $\Omega$ to Ground $C_L$ = 330 nF to Ground |     | 200 |     | μs   |

|                                                     |                     | EE Parameter Erase + Write                                |     |     | 15  | ms   |

| Calibration Time <sup>(9)</sup>                     | $t_{\text{CALIB}}$  | EE Full Read                                              |     | 180 |     | ms   |

|                                                     |                     | RAM Write                                                 |     |     | 3   | ms   |

Table 8: Timing specifications

# 10. Transfer Characteristic Specification

| Parameter                                  | Symbol          | Remark                                                      | Min   | Тур | Max  | Unit                 |

|--------------------------------------------|-----------------|-------------------------------------------------------------|-------|-----|------|----------------------|

| Output Clamping Range                      | CLAMPLO         | 9 bits <sup>(10)</sup>                                      | 0     |     | 50   | $%V_{DD}$            |

|                                            | СьамрНі         | 10 bits <sup>(10)</sup>                                     | 0     |     | 100  | $%V_{DD}$            |

| Output Quiescent (Offset)<br>Voltage Range | V <sub>oq</sub> | 14 bits (YA setting) (10)                                   | - 200 |     | 200  | $%V_{DD}$            |

| Sensitivity Range                          | S               | RG[2] = $1^{(10)}$<br>For full-scale output <sup>(11)</sup> | ±0.14 |     | ±1.9 | %V <sub>DD</sub> /mT |

Table 9: Transfer characteristic specifications

REVISION 7 - 02-APR-2020 Page 10 of 28

<sup>&</sup>lt;sup>8</sup>Rise and fall times are measured for worst case conditions, hence the difference in Rload for both parameters. These specifications are only defined by the output amplifier and its load. The output amplifier (Gain=2) is given a step response at the input from 5%VDD to 45%VDD and the rise/fall times are measured as the time between reaching 10% and 90% of the step response DC output voltages (10%VDD to 90%VDD).

<sup>&</sup>lt;sup>9</sup>Calibration times measured at room temperature with PTC-04 and DB-HALL03 daughterboard, FIR090288AAMLX firmware loaded onto the PTC-04 and on a MLX90288 in the recommended application diagram from subsequent sections at 10kbit/s.

<sup>&</sup>lt;sup>10</sup>Please refer to subsequent sections for more detailed information.

<sup>&</sup>lt;sup>11</sup>The full-scale output corresponds to 100%Vdd output range. This corresponds to 100% of the ADC range when FINEGAIN is set to 1 (1024LSB) in a bipolar application. The DSP chain can additionally increase sensitivity by a factor 4.

# 11. Accuracy Specification

| Parameter                                  | Symbol               | Remark                            | Min         | Тур        | Max   | Unit                 |

|--------------------------------------------|----------------------|-----------------------------------|-------------|------------|-------|----------------------|

| Output DAC Resolution                      | LSB <sub>DAC</sub>   | 12 bits                           |             | 0.0244     |       | $%V_{DD}$            |

| Output DAC Linearity                       | $DNL_{DAC}$          |                                   | -1          |            | +1    | $LSB_DAC$            |

|                                            | $INL_DAC$            |                                   | -2          |            | + 2   | $LSB_DAC$            |

| Ratiometric Error <sup>(12)</sup>          | Outratiom            | with TEMPTC=0                     | -0.1 +0.1 % |            |       |                      |

| Rationiethe Life                           | Ouratiom             | with TEMPTC=128                   | -0.2        |            | + 0.2 | $%V_{DD}$            |

| Output Noise <sup>(13)</sup>               |                      | RG = 4, FG = 800<br>FILTCODE = 4  |             | 0.12       | 0.18  | $mV_{RMS}$           |

|                                            | 0                    | RG = 7, FG = 800<br>FILTCODE = 4  |             | 0.13       | 0.2   | ${\sf mV}_{\sf RMS}$ |

|                                            | Out <sub>noise</sub> | RG = 4, FG = 4095<br>FILTCODE = 4 | 1.1         | $mV_{RMS}$ |       |                      |

|                                            |                      | RG = 7, FG = 4095<br>FILTCODE = 4 |             | 1          | 1.5   | $mV_{RMS}$           |

| Thermal Output Quiescent<br>(Offset) Drift |                      | RG = 4                            | - 10        |            | + 10  | $LSB_DAC$            |

|                                            | $\Delta^{T}V_{OQ}$   | RG = 5                            | - 10        |            | + 10  | LSB <sub>DAC</sub>   |

|                                            | ΔV <sub>OQ</sub>     | RG = 6                            | - 15        |            | + 15  | $LSB_DAC$            |

|                                            |                      | RG = 7                            | - 20        |            | + 20  | $LSB_DAC$            |

REVISION 7 - 02-APR-2020 Page 11 of 28

<sup>&</sup>lt;sup>12</sup>Ratiometric performance of the IC is measured as a difference in output voltage (expressed as %VDD) between the nominal case with VDD = 5V and the limits of the supply ratiometric operating range (4.5V and 5.5V). The difference between TEMPTC = 0 (or TEMPSENSOR disabled altogether) and TEMPTC = 128 originates in the fact that the on-chip temperature is also a function of the supply voltage. Since the TEMPTC changes the gain of the IC to compensate for the magnet TC, and it relies on the fact that the on-chip temperature is the same as the magnet temperature, an extra error occurs compared to TEMPTC = 0 case.

<sup>&</sup>lt;sup>13</sup>The noise measurements are performed on the recommended application diagram depicted under Section 10, with a supply voltage of 5V at room temperature. Increased capacitance values compared to the recommended application diagram, contribute to lower output noise. For peak-to-peak values, the RMS value is typically multiplied by a factor of 6.

| Parameter                                              | Symbol        | Remark                                                                    | Min   | Тур   | Max   | Unit   |

|--------------------------------------------------------|---------------|---------------------------------------------------------------------------|-------|-------|-------|--------|

| Thermal Sensitivity Drift <sup>(14)</sup> $\Delta^T S$ |               | No magnet TC                                                              | - 150 | 0     | + 150 | ppm/°C |

|                                                        | $\Delta^{T}S$ | Using 1 <sup>st</sup> and 2 <sup>nd</sup> order magnet TC <sup>(15)</sup> | - 200 |       | + 200 | ppm/°C |

| Sensitivity Thermal<br>Hysteresis                      | $\Delta^{H}S$ | After full thermal excursion                                              | -0.5  | ± 0.2 | + 0.5 | %      |

Table 10: Accuracy specifications

# 12. Diagnostic Specification

| Parameter                                   | Symbol              | Remark                                      | Min         | Тур | Max                | Unit      |

|---------------------------------------------|---------------------|---------------------------------------------|-------------|-----|--------------------|-----------|

| ADC Clipping Signaling <sup>(16)</sup> DIAG | DIAC                | DIAGINFAULT = 0                             | -           | -   | $V_{SATLO}$        | $%V_{DD}$ |

|                                             | DIAGCLIP            | DIAGINFAULT = 1                             | $V_{SATHI}$ | -   | -                  | $%V_{DD}$ |

| ADC Clipping Criterion <sup>(16)</sup>      | $N_{\text{CLIP}}$   | ADC clipping count before Diagnostic is set | -           | 4   | -                  | Count     |

| CRC Fail Signaling                          | DIAC                | DIAGINFAULT = 0                             | -           | -   | $V_{\text{SATLO}}$ | $%V_{DD}$ |

|                                             | DIAG <sub>PAR</sub> | DIAGINFAULT = 1                             | $V_{SATHI}$ | -   | -                  | $%V_{DD}$ |

| CRC Fail Criterion                          | $N_{\text{CRC}}$    | CRC Fail count before<br>Diagnostic is set  | -           | 3   | -                  | Count     |

REVISION 7 - 02-APR-2020 Page 12 of 28

<sup>&</sup>lt;sup>14</sup>The Sensitivity Thermal Drift is within these boundaries for all ICs with the default setting for gain compensation i.e. fixed to 1, which is obtained by setting TEMPTC to 0, but leaving the TEMPSENSOR bit set (see Subsequent Section). If the value is not fixed to 1, the sensitivity of the IC will exhibit a sensitivity thermal drift curve such as the one shown in the section on magnet compensation (if SECONDORDERTC is set) or with a linear temperature coefficient (if SECONDORDERTC is cleared) depending on the setting of TEMPTC, but ±150ppm/°C.

<sup>&</sup>lt;sup>15</sup>This limit is an indication of what can be achieved for a typical magnet. The main assumption is that the magnet strength monotonically decreases over temperature. Then, the 2nd order implementation as described in subsequent sections has been designed to work up to ferrite magnets with a magnet TC of -2000ppm/°C. Please contact Melexis when in doubt over the achievable specification for your magnet.

<sup>&</sup>lt;sup>16</sup>ADC clipping is only flagged if the FAULTONCLIP bit in EEPROM is set. If the bit is cleared, the ADC will clamp at either the maximum code or the minimum code, depending on the clipping condition. Reporting after 4 sequential clipping conditions is required for an EMC robust design. Clipping reporting does not apply to ADC values of the temperature signal.

| Parameter                              | Symbol                | Remark                     | Min | Тур | Max                 | Unit      |

|----------------------------------------|-----------------------|----------------------------|-----|-----|---------------------|-----------|

| Broken V <sub>SS</sub> <sup>(17)</sup> | $V_{\text{OUTbrVSS}}$ | Over R <sub>PD</sub> range | -   | -   | $V_{\text{DIAGLO}}$ | $%V_{DD}$ |

| Broken V <sub>DD</sub> <sup>(17)</sup> | $V_{\text{OUTbrVDD}}$ | Over R <sub>PD</sub> range | -   | -   | $V_{DIAGLO}$        | $%V_{DD}$ |

Table 11: Diagnostic level specifications

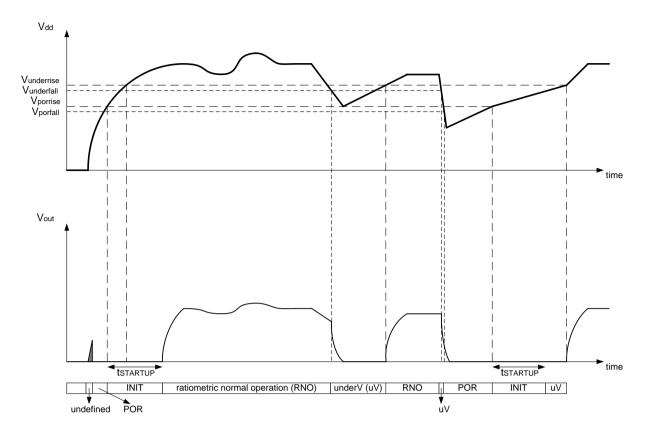

## 13. Startup, Undervoltage, Overvoltage and Reset Specification

During power-up (supply rising from 0V upwards) the MLX90288 remains in a zone where the output is undefined (grey triangular area in the plot) because there is no active circuitry putting the output stage in a specific condition. Most likely the output remains close to the low rail because of the passive external pull-down, but it cannot be predicted what happens exactly inside the IC at this point. This is also depicted in the signal waveforms of this section.

The POR phase is the phase where the supply is still below VPORRISE, but above the undefined region. In this case the digital is in a reset state, which puts all flip-flops in a known state, and the output is high impedant. Due to the external pull-down resistive load, the output is at the low rail.

When the supply rises above the VPORRISE threshold (which has built-in hysteresis: for the falling edge, VPORFALL), an initialization occurs which includes loading all EEPROM settings into RAM. After this initialization phase, the chip will start its FSM program and provide a valid output signal, for as long as the supply voltage is above the VUNDERRISE threshold (which has built-in hysteresis: for the falling edge, VUNDERFALL). If the supply is below this threshold, the output remains in high impedant state, corresponding to an output voltage at the low rail.

Whenever the MLX90288 goes from normal operation to undervoltage or via undervoltage to reset state, and vice versa, the output has a settling time which is a function of both the output load and the driving capability. On top of this, there is a startup time (tSTARTUP) in case the chip comes out of reset.

REVISION 7 - 02-APR-2020 Page 13 of 28

$<sup>^{17}</sup>$ Diagnostics that are the result of a passive settling because the output stage becomes high impedant (such as broken wire) are governed by the RC time constant of the capacitive load on the output and the  $R_{PD}$  resistor at ECU side. The OBD detection time is negligible in comparison to the settling time in case of a broken wire. The settling time should be taken as 4 times the RC time constant. E.g. with a load of 330nF and 330kOhm, the RC time constant equals 109ms. Settling time then corresponds to 4 RC time constants, i.e. 436ms.

Figure 2: Operating, undervoltage and reset functionality

In case the supply is raised above the VPROGRISE threshold (which has built-in hysteresis: for the falling edge, VPROGFALL), but below the VOVER threshold, the IC goes in programming mode: the output becomes high impedant and after proper commands coming from the programming unit (PTC04), the IC can respond on the output pin as well. The communication protocol on the output (PTC-04 communication) is bidirectional. If the supply is higher than the VOVER threshold, the internal regulated supply is disconnected from the external supply, as are most blocks of the IC. A reset will be the result when the supply is restored.

REVISION 7 - 02-APR-2020 Page 14 of 28

# 14. EMC/ESD Specification

| Parameter                                     | Symbol             | Remark | Min | Тур | Max   | Unit |

|-----------------------------------------------|--------------------|--------|-----|-----|-------|------|

| Micro-interrupt without reset <sup>(18)</sup> | μΙ                 |        | -   | -   | 0.1   | μs   |

| ESD Human Body Model <sup>(19)</sup>          | $ESD_HBM$          |        |     |     | ± 2   | kV   |

| ESD Charged Device<br>Model <sup>(20)</sup>   | ESD <sub>CDM</sub> |        |     |     | ± 500 | V    |

Table 12: EMC/ESD Specifications

# 15. EEPROM Mapping

## 15.1. EEPROM Description

All calibration parameters on the MLX90288 are stored in a 32 x 16bit non-volatile EEPROM.

The EEPROM parameters from the first 29 addresses are stored with triple redundancy, to correct if any EEPROM bit would lose its content, by using majority voting. Consequently, an EEPROM word in this part of EEPROM only holds the information of 5 calibration bits + 1 locking bit at index 15. The EEPROM word stored at address 0 thus looks like this:

#### {LOCK0,PARAM[4:0],PARAM[4:0],PARAM[4:0]}

If bit index 15 is set, the EEPROM word is permanently locked, making it impossible to overwrite the given address in PTC mode.

ID bits from the last 3 addresses are not stored with redundancy. The MLXID is not programmable in PTC mode, hence guaranteeing traceability of the parts.

There are no constraints on the EEPROM readout in PTC mode.

By default a part from the Melexis factory is delivered with the EEPROM delivered in a dual-redundancy configuration. The third redundancy is utilized for additional calibration parameters at end of line programming. Upon programming the sensor all parameters are covered by triple redundancy as described above.

REVISION 7 - 02-APR-2020 Page 15 of 28

<sup>&</sup>lt;sup>18</sup> If the digital regulated voltage drops below POR level, the ASIC will reset nearly immediately; this is a necessity from a DFMEA point of view. The only way to make the ASIC immune for longer micro-interrupts is to have external components (Rseries and Csupply) filtering these micro-interrupts for the ASIC. Introducing an Rseries in the supply line will have a negative impact on ratiometricity.

<sup>&</sup>lt;sup>19</sup> ESD HBM test performed on all pins according to JEDEC-22-A-114 standard.

<sup>&</sup>lt;sup>20</sup> ESD CDM test performed on all pins according to AEC-Q100-011 standard.

## 15.2. Melexis Programmed Parameters

## 15.2.1. OSCTRIM [4:0]

- Will be calibrated at MLX production

- Trims oscillator frequency around 1 MHz

#### 15.2.2. TRIMCTAT [4:0]

- Will be calibrated at MLX production

- Trims PTAT and CTAT to have both current sources at the same level at 25°C

- This calibration is necessary to allow correct TC1 trimming with a single measurement at either hot or cold

- The calibration compensates mismatch in both PTAT and CTAT current sources

## 15.2.3. ITRIM[2:0]

- Will be calibrated at MLX production

- Trims the current reference used throughout the analog part to a predefined value

## 15.2.4. IPLATE[3:0]

- Will be calibrated at MLX production

- Defines the current through the Hall plates, impacting the total gain

# 15.2.5. TC1ST[6:0]

- Will be calibrated at end of line programming

- Programming first order sensitivity temperature drift compensation

- Piecewise linear compensation between hot and cold temperatures = TC1ST

#### 15.2.6. TC2ND[5:0]

- Will be calibrated at end of line programming

- Programming piecewise linear sensitivity temperature drift compensation

- It is like an additional TC1 starting at 25 °C +/-30 °C

- Piecewise linear compensation for hot temperatures = TC1ST + TC2ND

#### 15.2.7. TC3RD[2:0]

- Will be calibrated at end of line programming

- Programming piecewise linear sensitivity temperature drift compensation

- It is like an additional TC1 starting at 5 °C

- Piecewise linear compensation for cold temperatures = TC1ST + TC2ND + 2\*TC3RD

#### 15.2.8. PLATEPOL

- Will be calibrated at MLX production

- Changes the polarity of the Hall plates, inverting the sensing nodes

- Changing the plate polarity will make the MLX production calibration void

- Changing the polarity of the output signal is recommended to be achieved by changing the FINEGAIN MSB

#### 15.2.9. OFFCST[4:0]

- Will be calibrated at MLX production

- Residual offset calibration (at Integrator stage) to make sure that the ADC input is at half of the ADC span

when no field is applied

- Analog compensation, sign magnitude number

## 15.2.10. OFFDRIFT[5:0]

- Will be calibrated at MLX production and at end of line programming via the Melexis solver tool

- Compensates linearly for residual offset temperature drift at the Integrator stage

- Analog compensation, sign magnitude number

## 15.2.11. XA[13:0]

- Will be calibrated at MLX production

- Gain-dependent offset, should not be modified after calibration

- Removes the residual offset of the ADC output when no field is applied

#### 15.2.12. MLXID[31:0]

- Melexis ID bits for traceability

- Cannot be overwritten in PTC mode

#### 15.2.13. CRC[9:0]

- Standard CRC10 for data integrity

- Polynomial is  $x^{10} + x^9 + x^5 + x^4 + x^1 + 1$

- EEPROM data is fed LSB first, per address (5bits, after majority voting) sequentially

The CRC integrity will be preserved by the PSF software when using the PTC04. It could not be changed manually

## 15.3. Customer Programmable Parameters

#### 15.3.1. FAULTONCLIP

- Enable error reporting if ADC is clipping for 4 or more successive times

- The diagnostic side for this error is defined by DIAGINFAULT

REVISION 7 - 02-APR-2020 Page 17 of 28

#### 15.3.2. DIAGINFAULT

- Defines to which side the output will go in case of an active error such as CRC fail or ADC clipping, the latter only in case FAULTONCLIP is set

- The thresholds are specified under the section on diagnostics.

## 15.3.3. FILTCODE[3:0]

The digital IIR filter offers noise reduction and low pass filtering with programmable cut off frequency

| FILTCODE[3:0] | Cut-off frequency [Hz] |

|---------------|------------------------|

| 0             | 1114                   |

| 1             | 557                    |

| 2             | 279                    |

| 3             | 139                    |

| 4             | 70                     |

| 5             | 35                     |

| 6             | 17                     |

| 7             | 9                      |

| 8             | 4                      |

Table 13: Filter cut-off frequencies

- For Filter code from 9 to 15, the rounding error becomes too high versus the resolution so those codes are not to be used.

- This table only applies in case the temperature sensor is enabled, otherwise the cut-off frequency should be multiplied by a factor of 2 since no more temperature ADC's are performed anymore.

#### 15.3.4. TEMPSENSOR

- Enables digital gain compensation over temperature (See Section 16)

- Requires proper calibration of TEMPOFF and TEMPTC, as well as the SECONDORDERTC

#### 15.3.5. SECONDORDERTC

Chooses between linear gain compensation over temperature (cleared) and ROM based 2nd order compensation (set) as described under the section on magnet compensation

REVISION 7 - 02-APR-2020 Page 18 of 28

## 15.3.6. TEMPOFF[9:0]

- Will be calibrated at MLX production and at end of line programming via the Melexis solver tool

- Defines the offset of the GainMag temperature compensation as described under Section 16

## 15.3.7. TEMPTC[7:0]

- Will be calibrated at MLX production and at end of line programming via the Melexis solver tool

- Defines the slope of the GainMag temperature compensation as described under Section 16

## 15.3.8. CLPLow[8:0]

- Low clamp level programmability range from 0% to 50% of VDD

- Resolution is 1/4<sup>th</sup> of the output DAC resolution, i.e. 0.098% of VDD

## 15.3.9. CLPHigh[9:0]

- High clamp level programmability range from 0% to 100% of VDD

- Resolution is 1/4th of the output DAC resolution, i.e. 0.098% of VDD

#### 15.3.10. ROUGHGAIN[1:0]

These 2 bits control the gain of the MAIN AMPLIFIER

#### 15.3.11. ATTN2P5

Enables the attenuation in the analog chain by a factor of 4.5

## 15.3.12. FINEGAIN[12:0]

- Sign-magnitude 13bit digital fine gain (not 2's complement!)

- The code 1024 (400h) corresponds to a gain of 1

- The code 5120 (1400h) corresponds to a gain of -1

- The MSB is a sign bit

- FINEGAIN range is therefore from -4095 (1FFFh) to +4095 (FFFh), which corresponds to a gain range of -3.999

to +3.999

#### 15.3.13. YA[13:0]

- Output offset programming, not gain dependent

- Defines the offset on the output in case no field is applied, inside a range of -200%Vdd to +200% Vdd with the 12-bit resolution of the output DAC, i.e. 0.0244% of VDD

#### 15.3.14. CSTID[15:0]

Customer ID bits for traceability

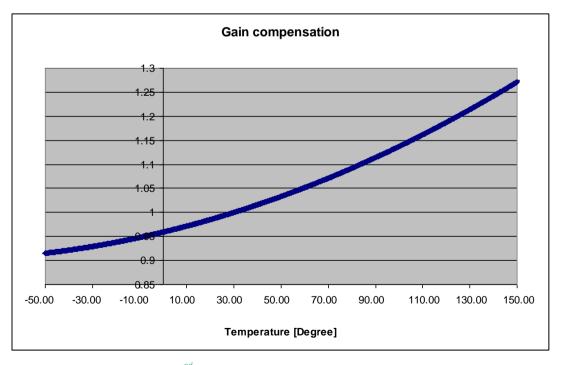

# 16. Thermal Sensitivity Drift Compensation

#### 16.1. Introduction

The embedded temperature sensor is digitized via the main path ADC before each analog amplified Hall sensor voltage ADC in case TEMPSENSOR is enabled. This temperature information is used to generate either an address for a ROM Look-up Table to obtain a quadratic temperature compensation (SECONDORDERTC=1), or a value proportional to the temperature that allows a linear IC gain compensation (SECONDORDERTC=0). Both compensations rely on the TEMPOFF and TEMPTC parameters.

#### 16.2. Linear Compensation (1st Order)

The conventional linear temperature compensation proves to be adequate for small application temperature ranges and/or small magnet temperature coefficients. In such cases the error induced by the linear approach are limited and prove to be good enough for the desired system sensitivity drift.

## 16.3. Quadratic Compensation (2nd Order) - CAA

This look up table is stored in ROM and contains the inverse transfer function of a specific magnetic flux density over temperature. It should be used for magnets with temperature coefficients lower than **-1500** ppm/degC, as is typically the case for plastic bonded magnets. Such magnet temperature coefficients cannot optimally be compensated by the linear method. However, Melexis tooling together with the stored compensation characteristic enable improved thermal drift compensation.

The correction factor GainMag is multiplied with the measured magnetic flux density. This multiplication results in a (nearly) temperature independent sensitivity of the entire system (magnet + IC).

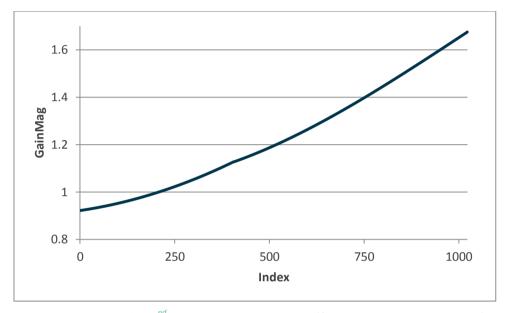

Figure 3: ROM table - 2<sup>nd</sup> order gain compensation (for illustrative purposes only)

REVISION 7 - 02-APR-2020 Page 20 of 28

## 16.4. Quadratic Compensation (2nd Order) - CAB and DAA versions

This look up table is stored in ROM and contains the inverse transfer function of a specific magnetic flux density over temperature. It should be used for magnets with temperature coefficients lower than **-2000** ppm/degC, as is typically the case for plastic bonded ferrite magnets. Such magnet temperature coefficients cannot optimally be compensated by the linear method. However, Melexis tooling together with the stored compensation characteristic enable improved thermal drift compensation.

The correction factor GainMag is multiplied with the measured magnetic flux density. This multiplication results in a (nearly) temperature independent sensitivity of the entire system (magnet + IC).

Figure 4: ROM table - 2<sup>nd</sup> order gain compensation (for illustrative purposes only)

The factory calibration performed by Melexis targets a specific magnet TC, which serves as accurate basis for any delta calibration that should be performed when using a magnet with a different TC. This is performed via the solver software provided by Melexis. The solver enables customers to address different sections in the lookup table for different temperature ranges. This flexibility is to ensure a good match between magnet TC and applied compensation.

REVISION 7 - 02-APR-2020 Page 21 of 28

#### 17. Standard Information

Our products are classified and qualified regarding soldering technology, solderability and moisture sensitivity level according to standards in place in Semiconductor industry.

For further details about test method references and for compliance verification of selected soldering method for product integration, Melexis recommends reviewing on our web site the General Guidelines soldering recommendation (<a href="http://www.melexis.com/en/quality-environment/soldering">http://www.melexis.com/en/quality-environment/soldering</a>).

For all soldering technologies deviating from the one mentioned in above document (regarding peak temperature, temperature gradient, temperature profile etc.), additional classification and qualification tests have to be agreed upon with Melexis.

For package technology embedding trim and form post-delivery capability, Melexis recommends consulting the dedicated trim & form recommendation application note: "Lead Trimming and Forming Recommendations" (<a href="https://www.melexis.com/en/documents/documentation/application-notes/application-note-lead-trimming-and-forming-recommendations">https://www.melexis.com/en/documents/documentation/application-notes/application-note-lead-trimming-and-forming-recommendations</a>).

Melexis is contributing to global environmental conservation by promoting lead free solutions. For more information on qualifications of RoHS compliant products (RoHS = European directive on the Restriction Of the use of certain Hazardous Substances) please visit the quality page on our website: <a href="http://www.melexis.com/en/quality-environment">http://www.melexis.com/en/quality-environment</a>.

#### 18. ESD Precautions

Electronic semiconductor products are sensitive to Electro Static Discharge (ESD). Always observe Electro Static Discharge control procedures whenever handling semiconductor products.

REVISION 7 - 02-APR-2020 Page 22 of 28

# 19. Package Specification

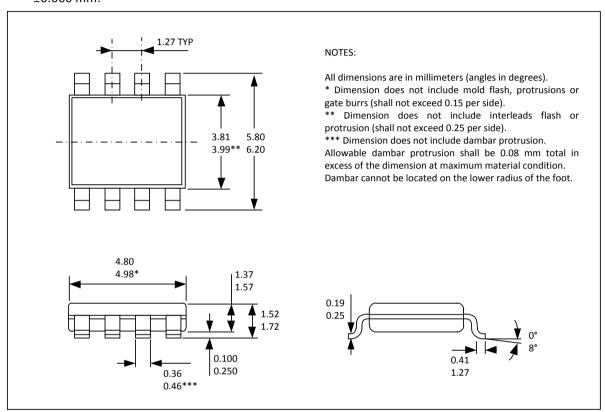

## 19.1. SOIC-8 Package Dimensions

- Package Type: SOIC-8 (8-pin Small Outline Integrated Circuit Package)

- Die placement accuracy is ± 2 mils = ±50 microns.

- Hall plate position from the top of the package (from CMOS topside to mold compound edge) is 0.460 mm

±0.060 mm.

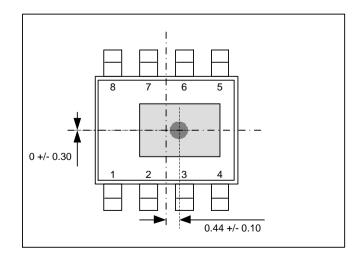

Figure 5: SOIC-8 Physical Dimensions

Figure 6: SOIC-8 Hall Plate Location

REVISION 7 - 02-APR-2020 Page 23 of 28

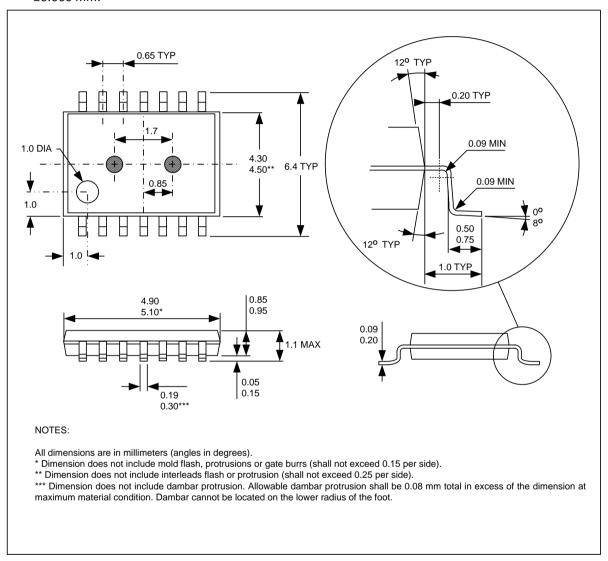

## 19.2. TSSOP-14 Package Dimensions

- Package Type: TSSOP-14 (14-pin Thin Shrink Small Outline Package)

- Die location:

- Distance between hall plates = 1700 microns.

- Die placement accuracy is ± 2 mils = ±50 microns.

- Hall plate position from the top of the package (from CMOS topside to mold compound edge) is 0.300 mm

±0.060 mm.

Figure 7: TSSOP-14 Package Dimensions

The dual-die package Hall plates are positioned on the longitudinal axis of symmetry. They are both at equal distance of the package center, subject to the above mentioned die placement tolerance of  $\pm$  50 microns.

REVISION 7 - 02-APR-2020 Page 24 of 28

Datasheet

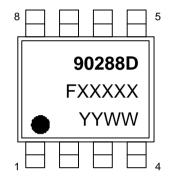

## 19.3. SOIC-8 Package Marking

The package is labeled for traceability purposes, as depicted in this section's figure.

The first line is reserved for the project number at Melexis, 90288 followed by the IC silicon version (C or D). The line below refers to the wafer fab. The bottom line is the date code indicating when the bare dies were packaged at the assembly house. The black dot indicates the position of pin #1.

- FXXXXX = 5-digit lot number ("F" = Fab Identifier)

- YYWW = last 2 digits of the year, followed by the calendar week

Figure 8: SOIC-8 Package markings

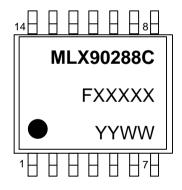

## 19.4. TSSOP-14 Package Marking

The package is labeled for traceability purposes.

Figure 9: TSSOP-14 Package markings

The first line is reserved for the project number at Melexis, MX90288 followed by the IC silicon version (C or D). The line below refers to the wafer fab. The bottom line is the date code indicating when the bare dies were packaged at the assembly house. The black dot indicates the position of pin #1.

- FXXXXX = 5-digit lot number ("F" = Fab Identifier)

- YYWW = last 2 digits of the year, followed by the calendar week

REVISION 7 - 02-APR-2020 Page 25 of 28

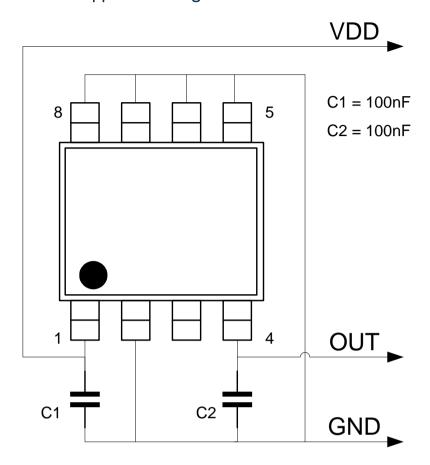

## 19.5. SOIC-8 Recommended Application Diagram

Figure 10: SOIC-8 Recommended Application Diagram

The test pins (#5, #6, #7, and #8) need to be grounded to avoid the risk of the chip going into test mode because of RF/noise entering the test controller on these pins. The test input pins have an internal pull-down resistor.

The recommended application diagram is not a mandatory design guide. For better ESD and EMC performance external components can be modified for as long as the electrical specifications are followed under previous sections. For good EMC performance the components should be placed as close as possible to the IC.

REVISION 7 - 02-APR-2020 Page 26 of 28

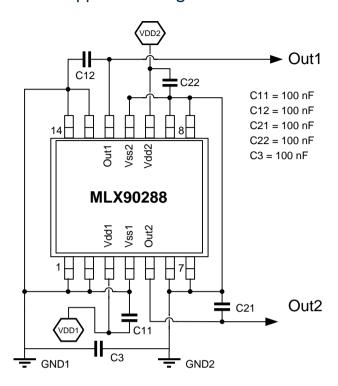

## 19.6. TSSOP-14 Recommended Application Diagram

Figure 11: TSSOP-14 Recommended Application Diagram

The test pins (#1, #2, #6, #7, #8, #9, #13, and #14) need to be grounded to avoid the risk of the chip going into test mode because of RF/noise entering the test controller on these pins. The test input pins have an internal pull-down resistor.

The recommended application diagram is not a mandatory design guide. For better ESD and EMC performance external components can be modified for as long as the electrical specifications are followed. For good EMC performance the components should be placed as close as possible to the ASIC. For good ESD performance the components should block as much as possible at the module connector side.

REVISION 7 - 02-APR-2020 Page 27 of 28

#### 20. Contact

For the latest version of this document, go to our website at www.melexis.com.

For additional information, please contact our Direct Sales team and get help for your specific needs:

| Europe, Africa | Telephone: +32 13 67 04 95      |

|----------------|---------------------------------|

|                | Email: sales_europe@melexis.com |

| Americas       | Telephone: +1 603 223 2362      |

|                | Email: sales_usa@melexis.com    |

| Asia           | Email: sales_asia@melexis.com   |

#### 21. Disclaimer

The information furnished by Melexis herein ("Information") is believed to be correct and accurate. Melexis disclaims (i) any and all liability in connection with or arising out of the furnishing, performance or use of the technical data or use of the product(s) as described herein ("Product") (ii) any and all liability, including without limitation, special, consequential or incidental damages, and (iii) any and all warranties, express, statutory, implied, or by description, including warranties of fitness for particular purpose, non-infringement and merchantability. No obligation or liability shall arise or flow out of Melexis' rendering of technical or other services.

The Information is provided "as is" and Melexis reserves the right to change the Information at any time and without notice. Therefore, before placing orders and/or prior to designing the Product into a system, users or any third party should obtain the latest version of the relevant information to verify that the information being relied upon is current.

Users or any third party must further determine the suitability of the Product for its application, including the level of reliability required and determine whether it is fit for a particular purpose.

The Information is proprietary and/or confidential information of Melexis and the use thereof or anything described by the Information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights. This document as well as the Product(s) may be subject to export control regulations. Please be aware that export might require a prior authorization from competent authorities.

The Product(s) are intended for use in normal commercial applications. Unless otherwise agreed upon in writing, the Product(s) are not designed, authorized or warranted to be suitable in applications requiring extended temperature range and/or unusual environmental requirements. High reliability applications, such as medical life-support or life-sustaining equipment are specifically not recommended by Melexis.

The Product(s) may not be used for the following applications subject to export control regulations: the development, production, processing, operation, maintenance, storage, recognition or proliferation of 1) chemical, biological or nuclear weapons, or for the development, production, maintenance or storage of missiles for such weapons: 2) civil firearms, including spare parts or ammunition for such arms; 3) defense related products, or other material for military use or for law enforcement; 4) any applications that, alone or in combination with other goods, substances or organisms could cause serious harm to persons or goods and that can be used as a means of violence in an armed conflict or any similar violent situation.

The Products sold by Melexis are subject to the terms and conditions as specified in the Terms of Sale, which can be found at https://www.melexis.com/en/legal/terms-and-conditions.

This document supersedes and replaces all prior information regarding the Product(s) and/or previous versions of this document.

Melexis NV © - No part of this document may be reproduced without the prior written consent of Melexis. (2020)

ISO/TS 16949 and ISO14001 Certified

REVISION 7 - 02-APR-2020 Page 28 of 28

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А