### intel Intel386TM DX MICROPROCESSOR 32-BIT CHMOS MICROPROCESSOR WITH INTEGRATED MEMORY MANAGEMENT

- Flexible 32-Bit Microprocessor - 8, 16, 32-Bit Data Types — 8, 16, 32-ыт раса турсс — 8 General Purpose 32-Bit Registers

- Very Large Address Space

- 4 Gigabyte Physical

- 64 Terabyte Virtual

- 4 Gigabyte Maximum Segment Size

- Integrated Memory Management Unit

- Virtual Memory Support

- Optional On-Chip Paging

- 4 Levels of Protection

- Fully Compatible with 80286

- Object Code Compatible with All 8086 **Family Microprocessors**

- Virtual 8086 Mode Allows Running of 8086 Software in a Protected and Paged System

- Hardware Debugging Support

- Optimized for System Performance

- Pipelined Instruction Execution

- On-Chip Address Translation Caches

- 20. 25 and 33 MHz Clock

- 40, 50 and 66 Megabytes/Sec Bus Bandwidth

- Numerics Support via Intel387™ DX Math Coprocessor

- **Complete System Development** Support

- -Software: C, PL/M, Assembler **System Generation Tools**

- Debuggers: PSCOPE, ICE™-386

- High Speed CHMOS IV Technology

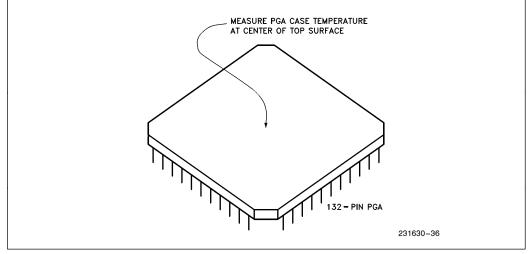

- 132 Pin Grid Array Package

- **132 Pin Plastic Quad Flat Package**

(See Packaging Specification, Order #231369)

The Intel386 DX Microprocessor is an entry-level 32-bit microprocessor designed for single-user applications and operating systems such as MS-DOS and Windows. The 32-bit registers and data paths support 32-bit addresses and data types. The processor addresses up to four gigabytes of physical memory and 64 terabytes (2\*\*46) of virtual memory. The integrated memory management and protection architecture includes address translation registers, multitasking hardware and a protection mechanism to support operating systems. Instruction pipelining, on-chip address translation, ensure short average instruction execution times and maximum system throughput.

The Intel386 DX CPU offers new testability and debugging features. Testability features include a self-test and direct access to the page translation cache. Four new breakpoint registers provide breakpoint traps on code execution or data accesses, for powerful debugging of even ROM-based systems.

Object-code compatibility with all 8086 family members (8086, 8088, 80186, 80188, 80286) means the Intel386 DX offers immediate access to the world's largest microprocessor software base.

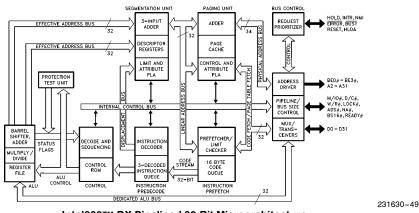

#### Intel386™ DX Pipelined 32-Bit Microarchitecture

Intel386™ DX and Intel387™ DX are Trademarks of Intel Corporation. MS-DOS and Windows are Trademarks of MICROSOFT Corporation.

\*Other brands and names are the property of their respective owners. Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata. COPYRIGHT © INTEL CORPORATION, 1995 December 1995 Order Number: 231630-011

### Intel386™ DX MICROPROCESSOR 32-BIT CHMOS MICROPROCESSOR WITH INTEGRATED MEMORY MANAGEMENT

### CONTENTS

PAGE

| 1. | PIN ASSIGNMENT         1.1 Pin Description Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|    | BASE ARCHITECTURE         2.1 Introduction         2.2 Register Overview         2.3 Register Descriptions         2.4 Instruction Set         2.5 Addressing Modes         2.6 Data Types         2.7 Memory Organization         2.8 I/O Space         2.9 Interrupts         2.10 Reset and Initialization         2.11 Testability         2.12 Debugging Support                                                                                                                                                                                                        | . 8<br>. 9<br>15<br>18<br>20<br>22<br>23<br>24<br>27<br>28<br>28 |

|    | <b>REAL MODE ARCHITECTURE</b> 3.1 Real Mode Introduction         3.2 Memory Addressing         3.3 Reserved Locations         3.4 Interrupts         3.5 Shutdown and Halt                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>33<br>34<br>34<br>34                                       |

| 4. | PROTECTED MODE ARCHITECTURE         4.1 Introduction         4.2 Addressing Mechanism         4.3 Segmentation         4.4 Protection         4.5 Paging         4.6 Virtual 8086 Environment                                                                                                                                                                                                                                                                                                                                                                                | 34<br>35<br>36<br>46<br>52                                       |

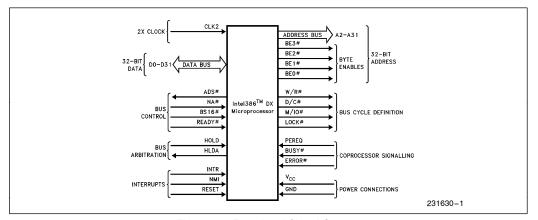

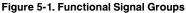

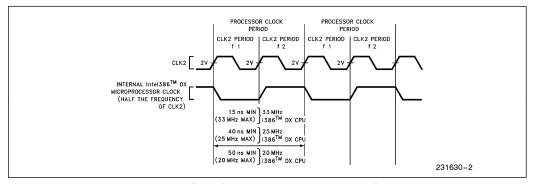

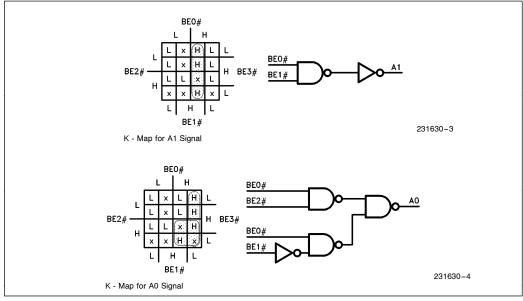

| 5. | FUNCTIONAL DATA         5.1 Introduction         5.2 Signal Description         5.2.1 Introduction         5.2.2 Clock (CLK2)         5.2.3 Data Bus (D0 through D31)         5.2.4 Address Bus (BEO# through BE3#, A2 through A31)         5.2.5 Bus Cycle Definition Signals (W/R#, D/C#, M/IO, LOCK#)         5.2.6 Bus Control Signals (ADS#, READY#, NA#, BS16#)         5.2.7 Bus Arbitration Signals (HOLD, HLDA)         5.2.8 Coprocessor Interface Signals (PEREQ, BUSY#, ERROR#)         5.2.9 Interrupt Signals (INTR, NMI, RESET)         5.2.10 Signal Summary | 61<br>61<br>62<br>62<br>62<br>63<br>64<br>65<br>65<br>66         |

### CONTENTS

### PAGE

| 5. FUNCTIONAL DATA (Continued)                   |   |

|--------------------------------------------------|---|

| 5.3. Bus Transfer Mechanism                      | 7 |

| 5.3.1 Introduction                               | 7 |

| 5.3.2 Memory and I/O Spaces                      | 8 |

| 5.3.3 Memory and I/O Organization                | 9 |

| 5.3.4 Dynamic Data Bus Sizing6                   | 9 |

| 5.3.5 Interfacing with 32- and 16-bit Memories   | 0 |

| 5.3.6 Operand Alignment 7                        | 1 |

| 5.4 Bus Functional Description7                  |   |

| 5.4.1 Introduction                               |   |

| 5.4.2 Address Pipelining                         |   |

| 5.4.3 Read and Write Cycles                      | 6 |

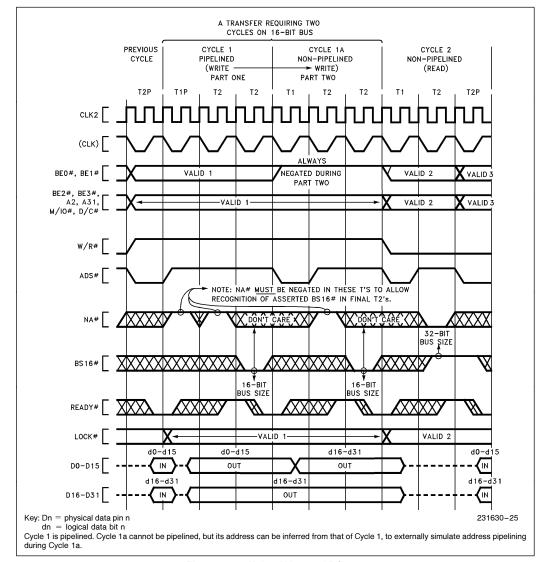

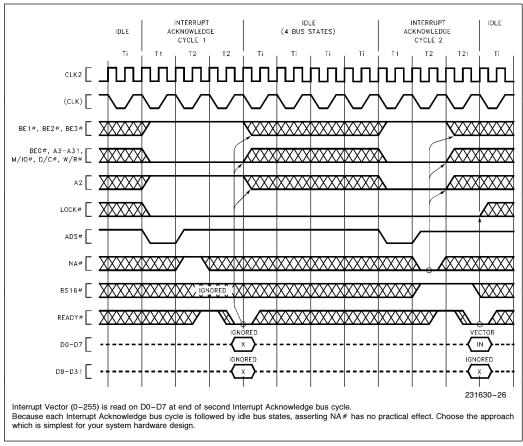

| 5.4.4 Interrupt Acknowledge (INTA) Cycles        |   |

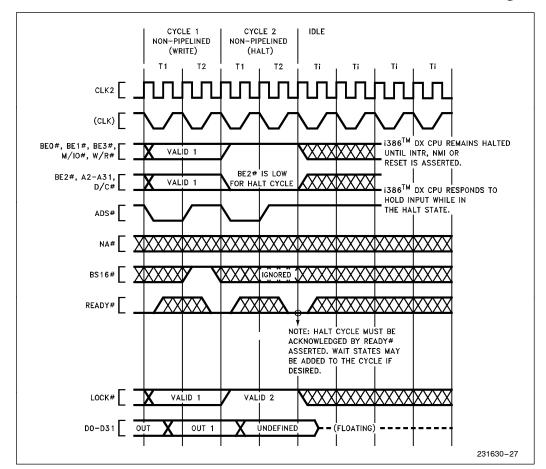

| 5.4.5 Halt Indication Cycle                      | 8 |

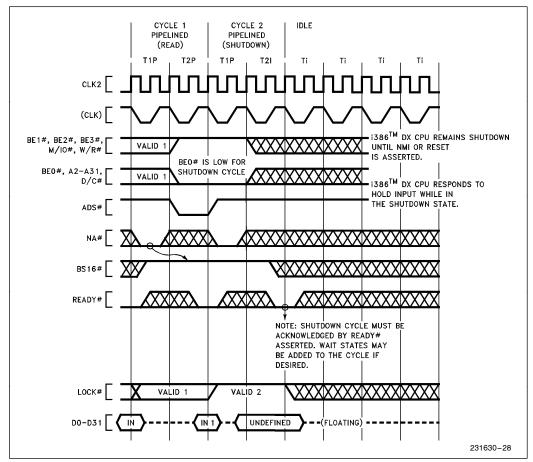

| 5.4.6 Shutdown Indication Cycle                  |   |

| 5.5 Other Functional Descriptions                | 0 |

| 5.5.1 Entering and Exiting Hold Acknowledge      |   |

| 5.5.2 Reset during Hold Acknowledge              |   |

| 5.5.3 Bus Activity During and Following Reset    | 0 |

| 5.7 Component and Revision Identifiers           | 2 |

| 5.8 Coprocessor Interface                        |   |

| 5.8.1 Software Testing for Coprocessor Presence  | 4 |

|                                                  |   |

| 6. INSTRUCTION SET                               | 5 |

| 6.1 Instruction Encoding and Clock Count Summary | 5 |

| 6.2 Instruction Encoding Details                 |   |

| 7. DESIGNING FOR ICE™-386 DX EMULATOR USE        | 7 |

| 8. MECHANICAL DATA                               | 9 |

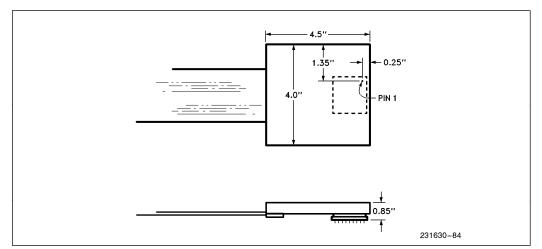

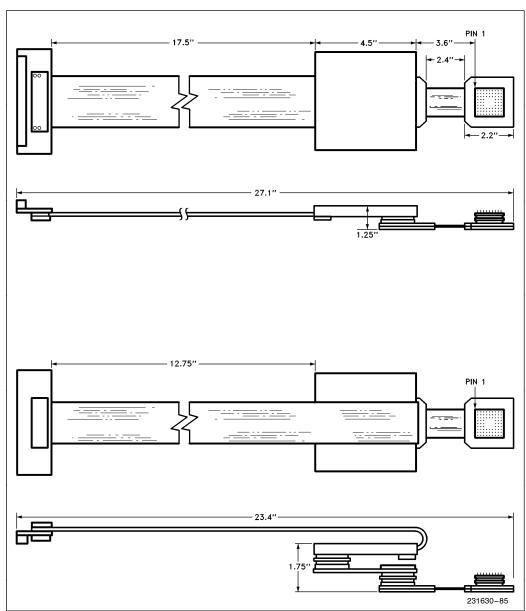

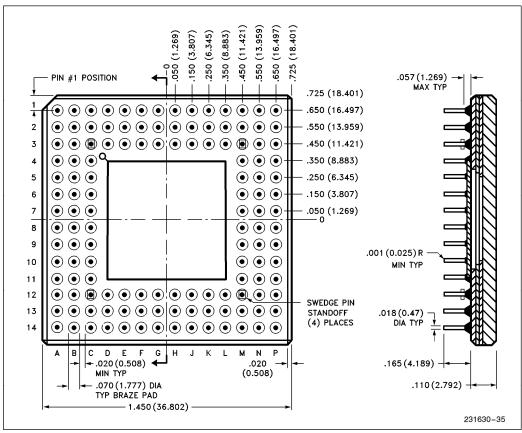

| 8.1 Introduction 11                              |   |

| 8.2 Package Dimensions and Mounting11            | 9 |

| 8.3 Package Thermal Specification                |   |

| 9. ELECTRICAL DATA                               | 2 |

| 9.1 Introduction                                 |   |

| 9.2 Power and Grounding                          |   |

| 9.3 Maximum Ratings                              |   |

| 9.4 D.C. Specifications                          |   |

| 9.5 A.C. Specifications                          |   |

| <b>10. REVISION HISTORY</b>                      |   |

|                                                  | 1 |

NOTE:

This is revision 011; This supercedes all previous revisions.

### Intel386TM DX MICROPROCESSOR

### **1. PIN ASSIGNMENT**

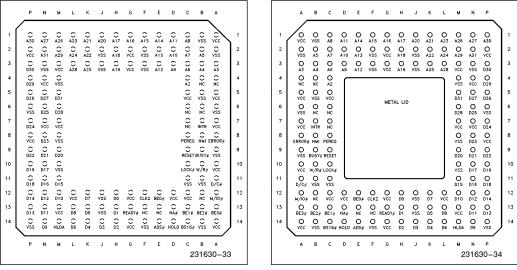

The Intel386 DX pinout as viewed from the top side of the component is shown by Figure 1-1. Its pinout as viewed from the Pin side of the component is Figure 1-2.  $V_{CC}$  and GND connections must be made to multiple  $V_{CC}$  and  $V_{SS}$  (GND) pins. Each  $V_{CC}$  and  $V_{SS}$  must be connected to the appropriate voltage level. The circuit board should include  $V_{CC}$  and GND planes for power distribution and all  $V_{CC}$  and  $V_{SS}$  pins must be connected to the appropriate plane.

#### NOTE:

Pins identified as "N.C." should remain completely unconnected.

Figure 1-1. Intel386™ DX PGA Pinout—View from Top Side

| Signa | Signal/Pin Signal/Pin |       | Signal/Pin Signal/Pi |     | al/Pin | Signal/         | Signa | l/Pin           | Signal/Pin |                 |     |

|-------|-----------------------|-------|----------------------|-----|--------|-----------------|-------|-----------------|------------|-----------------|-----|

| A2    | C4                    | A24   | L2                   | D6  | L14    | D28             | M6    | V <sub>CC</sub> | C12        | V <sub>SS</sub> | F2  |

| A3    | A3                    | A25   | K3                   | D7  | K12    | D29             | P4    |                 | D12        |                 | F3  |

| A4    | B3                    | A26   | M1                   | D8  | L13    | D30             | P3    |                 | G2         |                 | F14 |

| A5    | B2                    | A27   | N1                   | D9  | N14    | D31             | M5    |                 | G3         |                 | J2  |

| A6    | C3                    | A28   | L3                   | D10 | M12    | D/C#            | A11   |                 | G12        |                 | J3  |

| A7    | C2                    | A29   | M2                   | D11 | N13    | ERROR#          | A8    |                 | G14        |                 | J12 |

| A8    | C1                    | A30   | P1                   | D12 | N12    | HLDA            | M14   |                 | L12        |                 | J13 |

| A9    | D3                    | A31   | N2                   | D13 | P13    | HOLD            | D14   |                 | M3         |                 | M4  |

| A10   | D2                    | ADS#  | E14                  | D14 | P12    | INTR            | B7    |                 | M7         |                 | M8  |

| A11   | D1                    | BE0#  | E12                  | D15 | M11    | LOCK#           | C10   |                 | M13        |                 | M10 |

| A12   | E3                    | BE1#  | C13                  | D16 | N11    | M/IO#           | A12   |                 | N4         |                 | N3  |

| A13   | E2                    | BE2#  | B13                  | D17 | N10    | NA#             | D13   |                 | N7         |                 | P6  |

| A14   | E1                    | BE3#  | A13                  | D18 | P11    | NMI             | B8    |                 | P2         |                 | P14 |

| A15   | F1                    | BS16# | C14                  | D19 | P10    | PEREQ           | C8    |                 | P8         | W/R#            | B10 |

| A16   | G1                    | BUSY# | B9                   | D20 | M9     | READY#          | G13   | V <sub>SS</sub> | A2         | N.C.            | A4  |

| A17   | H1                    | CLK2  | F12                  | D21 | N9     | RESET           | C9    |                 | A6         |                 | B4  |

| A18   | H2                    | D0    | H12                  | D22 | P9     | V <sub>CC</sub> | A1    |                 | A9         |                 | B6  |

| A19   | H3                    | D1    | H13                  | D23 | N8     |                 | A5    |                 | B1         |                 | B12 |

| A20   | J1                    | D2    | H14                  | D24 | P7     |                 | A7    |                 | B5         |                 | C6  |

| A21   | K1                    | D3    | J14                  | D25 | N6     |                 | A10   |                 | B11        |                 | C7  |

| A22   | K2                    | D4    | K14                  | D26 | P5     |                 | A14   |                 | B14        |                 | E13 |

| A23   | L1                    | D5    | K13                  | D27 | N5     |                 | C5    |                 | C11        |                 | F13 |

Table 1-1. Intel386™ DX PGA Pinout—Functional Grouping

### **1.1 PIN DESCRIPTION TABLE**

The following table lists a brief description of each pin on the Intel386 DX. The following definitions are used in these descriptions:

- # The named signal is active LOW.

- I Input signal.

- O Output signal.

- I/O Input and Output signal.

- No electrical connection.

For a more complete description refer to Section 5.2 Signal Description.

| Symbol                          | Туре | Name and Function                                                                                                                                                                             |

|---------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK2                            | I    | CLK2 provides the fundamental timing for the Intel386 DX.                                                                                                                                     |

| D <sub>31</sub> -D <sub>0</sub> | 1/0  | <b>DATA BUS</b> inputs data during memory, I/O and interrupt acknowledge read cycles and outputs data during memory and I/O write cycles.                                                     |

| A <sub>31</sub> -A <sub>2</sub> | 0    | ADDRESS BUS outputs physical memory or port I/O addresses.                                                                                                                                    |

| BE0#-BE3#                       | 0    | BYTE ENABLES indicate which data bytes of the data bus take part in a bus cycle.                                                                                                              |

| W/R#                            | 0    | WRITE/READ is a bus cycle definition pin that distinguishes write cycles from read cycles.                                                                                                    |

| D/C#                            | 0    | <b>DATA/CONTROL</b> is a bus cycle definition pin that distinguishes data cycles, either memory or I/O, from control cycles which are: interrupt acknowledge, halt, and instruction fetching. |

| M/IO#                           | 0    | <b>MEMORY I/O</b> is a bus cycle definition pin that distinguishes memory cycles from input/output cycles.                                                                                    |

| LOCK#                           | 0    | <b>BUS LOCK</b> is a bus cycle definition pin that indicates that other system bus masters are denied access to the system bus while it is active.                                            |

| ADS#                            | 0    | <b>ADDRESS STATUS</b> indicates that a valid bus cycle definition and address (W/R#, D/C#, M/IO#, BE0#, BE1#, BE2#, BE3# and $A_{31}-A_2$ ) are being driven at the Intel386 DX pins.         |

| NA#                             | I    | NEXT ADDRESS is used to request address pipelining.                                                                                                                                           |

| READY#                          | I    | BUS READY terminates the bus cycle.                                                                                                                                                           |

| BS16#                           | I    | <b>BUS SIZE 16</b> input allows direct connection of 32-bit and 16-bit data buses.                                                                                                            |

| HOLD                            | I    | <b>BUS HOLD REQUEST</b> input allows another bus master to request control of the local bus.                                                                                                  |

| Symbol          | Туре | Name and Function                                                                                                                                                                     |

|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HLDA            | 0    | <b>BUS HOLD ACKNOWLEDGE</b> output indicates that the Intel386 DX has surrendered control of its local bus to another bus master.                                                     |

| BUSY#           | I    | BUSY signals a busy condition from a processor extension.                                                                                                                             |

| ERROR#          | I    | ERROR signals an error condition from a processor extension.                                                                                                                          |

| PEREQ           | I    | <b>PROCESSOR EXTENSION REQUEST</b> indicates that the processor extension has data to be transferred by the Intel386 DX.                                                              |

| INTR            | I    | <b>INTERRUPT REQUEST</b> is a maskable input that signals the Intel386 DX to suspend execution of the current program and execute an interrupt acknowledge function.                  |

| NMI             | I    | <b>NON-MASKABLE INTERRUPT REQUEST</b> is a non-maskable input that signals the Intel386 DX to suspend execution of the current program and execute an interrupt acknowledge function. |

| RESET           | I    | <b>RESET</b> suspends any operation in progress and places the Intel386 DX in a known reset state. See <b>Interrupt Signals</b> for additional information.                           |

| N/C             | _    | <b>NO CONNECT</b> should always remain unconnected. Connection of a N/C pin may cause the processor to malfunction or be incompatible with future steppings of the Intel386 DX.       |

| V <sub>CC</sub> | I    | <b>SYSTEM POWER</b> provides the +5V nominal D.C. supply input.                                                                                                                       |

| V <sub>SS</sub> | I    | SYSTEM GROUND provides 0V connection from which all inputs and outputs are measured.                                                                                                  |

### 1.1 PIN DESCRIPTION TABLE (Continued)

### 2. BASE ARCHITECTURE

### 2.1 INTRODUCTION

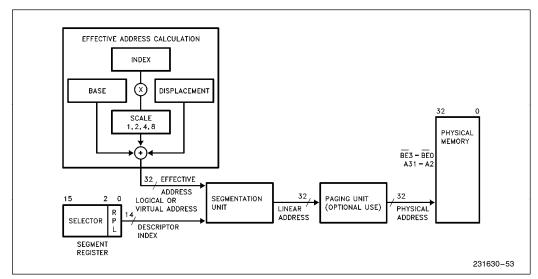

The Intel386 DX consists of a central processing unit, a memory management unit and a bus interface.

The central processing unit consists of the execution unit and instruction unit. The execution unit contains the eight 32-bit general purpose registers which are used for both address calculation, data operations and a 64-bit barrel shifter used to speed shift, rotate, multiply, and divide operations. The multiply and divide logic uses a 1-bit per cycle algorithm. The multiply algorithm stops the iteration when the most significant bits of the multiplier are all zero. This allows typical 32-bit multiplies to be executed in under one microsecond. The instruction unit decodes the instruction opcodes and stores them in the decoded instruction queue for immediate use by the execution unit.

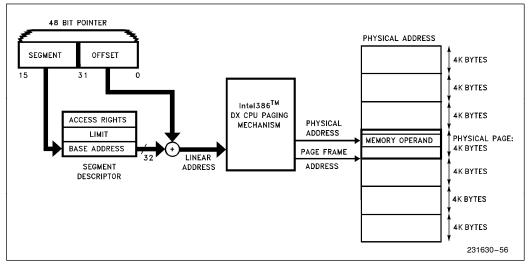

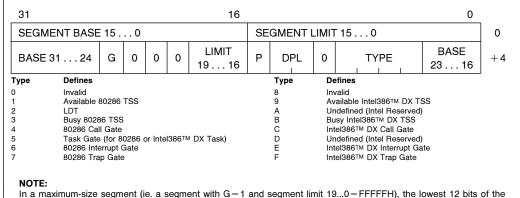

The memory management unit (MMU) consists of a segmentation unit and a paging unit. Segmentation allows the managing of the logical address space by providing an extra addressing component, one that allows easy code and data relocatability, and efficient sharing. The paging mechanism operates beneath and is transparent to the segmentation process, to allow management of the physical address space. Each segment is divided into one or more 4K byte pages. To implement a virtual memory system, the Intel386 DX supports full restartability for all page and segment faults.

Memory is organized into one or more variable length segments, each up to four gigabytes in size. A given region of the linear address space, a segment, can have attributes associated with it. These attributes include its location, size, type (i.e. stack, code or data), and protection characteristics. Each task on an Intel386 DX can have a maximum of 16,381 segments of up to four gigabytes each, thus providing 64 terabytes (trillion bytes) of virtual memory to each task.

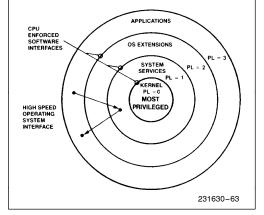

The segmentation unit provides four-levels of protection for isolating and protecting applications and the operating system from each other. The hardware enforced protection allows the design of systems with a high degree of integrity.

The Intel386 DX has two modes of operation: Real Address Mode (Real Mode), and Protected Virtual Address Mode (Protected Mode). In Real Mode the Intel386 DX operates as a very fast 8086, but with

32-bit extensions if desired. Real Mode is required primarily to setup the processor for Protected Mode operation. Protected Mode provides access to the sophisticated memory management, paging and privilege capabilities of the processor.

Within Protected Mode, software can perform a task switch to enter into tasks designated as Virtual 8086 Mode tasks. Each such task behaves with 8086 semantics, thus allowing 8086 software (an application program, or an entire operating system) to execute. The Virtual 8086 tasks can be isolated and protected from one another and the host Intel386 DX operating system, by the use of paging, and the I/O Permission Bitmap.

Finally, to facilitate high performance system hardware designs, the Intel386 DX bus interface offers address pipelining, dynamic data bus sizing, and direct Byte Enable signals for each byte of the data bus. These hardware features are described fully beginning in Section 5.

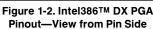

### 2.2 REGISTER OVERVIEW

The Intel386 DX has 32 register resources in the following categories:

- General Purpose Registers

- Segment Registers

- Instruction Pointer and Flags

- Control Registers

- System Address Registers

- Debug Registers

- Test Registers.

The registers are a superset of the 8086, 80186 and 80286 registers, so all 16-bit 8086, 80186 and 80286 registers are contained within the 32-bit Intel386 DX.

Figure 2-1 shows all of Intel386 DX base architecture registers, which include the general address and data registers, the instruction pointer, and the flags register. The contents of these registers are task-specific, so these registers are automatically loaded with a new context upon a task switch operation.

The base architecture also includes six directly accessible segments, each up to 4 Gbytes in size. The segments are indicated by the selector values placed in Intel386 DX segment registers of Figure 2-1. Various selector values can be loaded as a program executes, if desired.

Figure 2-1. Intel386™ DX Base Architecture Registers

The selectors are also task-specific, so the segment registers are automatically loaded with new context upon a task switch operation.

The other types of registers, Control, System Address, Debug, and Test, are primarily used by system software.

### 2.3 REGISTER DESCRIPTIONS

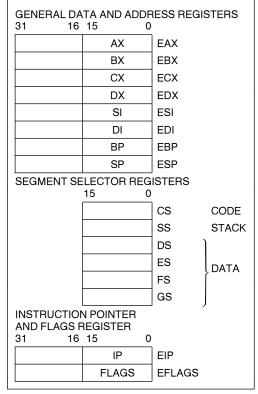

### 2.3.1 General Purpose Registers

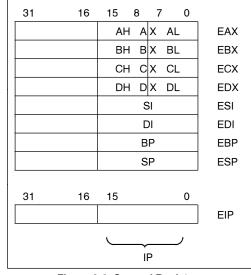

**General Purpose Registers:** The eight general purpose registers of 32 bits hold data or address quantities. The general registers, Figure 2-2, support data operands of 1, 8, 16, 32 and 64 bits, and bit fields of 1 to 32 bits. They support address operands of 16 and 32 bits. The 32-bit registers are named EAX, EBX, ECX, EDX, ESI, EDI, EBP, and ESP.

The least significant 16 bits of the registers can be accessed separately. This is done by using the 16bit names of the registers AX, BX, CX, DX, SI, DI,

### Intel386™ DX MICROPROCESSOR

BP, and SP. When accessed as a 16-bit operand, the upper 16 bits of the register are neither used nor changed.

Finally 8-bit operations can individually access the lowest byte (bits 0–7) and the higher byte (bits 8–15) of general purpose registers AX, BX, CX and DX. The lowest bytes are named AL, BL, CL and DL, respectively. The higher bytes are named AH, BH, CH and DH, respectively. The individual byte accessibility offers additional flexibility for data operations, but is not used for effective address calculation.

Figure 2-2. General Registers and Instruction Pointer

### 2.3.2 Instruction Pointer

The instruction pointer, Figure 2-2, is a 32-bit register named EIP. EIP holds the offset of the next instruction to be executed. The offset is always relative to the base of the code segment (CS). The lower 16 bits (bits 0-15) of EIP contain the 16-bit instruction pointer named IP, which is used by 16-bit addressing.

### 2.3.3 Flags Register

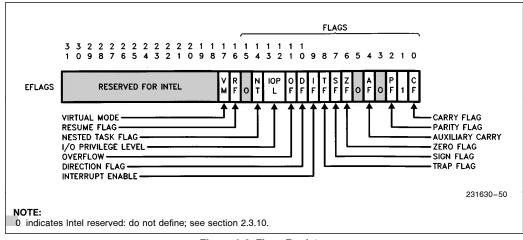

The Flags Register is a 32-bit register named EFLAGS. The defined bits and bit fields within EFLAGS, shown in Figure 2-3, control certain operations and indicate status of the Intel386 DX. The lower 16 bits (bit 0–15) of EFLAGS contain the 16-bit flag register named FLAGS, which is most useful when executing 8086 and 80286 code.

### Intel386<sup>TM</sup> DX MICROPROCESSOR

Figure 2-3. Flags Register

- VM (Virtual 8086 Mode, bit 17)

- The VM bit provides Virtual 8086 Mode within Protected Mode. If set while the Intel386 DX is in Protected Mode, the Intel386 DX will switch to Virtual 8086 operation, handling segment loads as the 8086 does, but generating exception 13 faults on privileged opcodes. The VM bit can be set only in Protected Mode, by the IRET instruction (if current privilege level = 0) and by task switches at any privilege level. The VM bit is unaffected by POPF. PUSHF always pushes a 0 in this bit, even if executing in virtual 8086 Mode. The EFLAGS image pushed during interrupt processing or saved during task switches will contain a 1 in this bit if the interrupted code was executing as a Virtual 8086 Task.

- RF (Resume Flag, bit 16)

The RF flag is used in conjunction with the debug register breakpoints. It is checked at instruction boundaries before breakpoint processing. When RF is set, it causes any debug fault to be ignored on the next instruction. RF is then automatically reset at the successful completion of every instruction (no faults are signalled) except the IRET instruction, the POPF instruction, (and JMP, CALL, and INT instructions causing a task switch). These instructions set RF to the value specified by the memory image. For example, at the end of the breakpoint service routine, the IRET

instruction can pop an EFLAG image having the RF bit set and resume the program's execution at the breakpoint address without generating another breakpoint fault on the same location.

NT (Nested Task, bit 14)

This flag applies to Protected Mode. NT is set to indicate that the execution of this task is nested within another task. If set, it indicates that the current nested task's Task State Segment (TSS) has a valid back link to the previous task's TSS. This bit is set or reset by control transfers to other tasks. The value of NT in EFLAGS is tested by the IRET instruction to determine whether to do an inter-task return or an intra-task return. A POPF or an IRET instruction **will** affect the setting of this bit according to the image popped, at any privilege level.

IOPL (Input/Output Privilege Level, bits 12-13)

This two-bit field applies to Protected Mode. IOPL indicates the numerically maximum CPL (current privilege level) value permitted to execute I/O instructions without generating an exception 13 fault or consulting the I/O Permission Bitmap. It also indicates the maximum CPL value allowing alteration of the IF (INTR Enable Flag) bit when new values are popped into the EFLAG register. POPF and IRET instruction can alter the IOPL field when executed at CPL = 0. Task switches can always alter the IOPL field, when the new flag image is loaded from the incoming task's TSS.

DF

- OF (Overflow Flag, bit 11) OF is set if the operation resulted in a signed overflow. Signed overflow occurs when the operation resulted in carry/borrow **into** the sign bit (high-order bit) of the result but did not result in a carry/borrow **out of** the highorder bit, or vice-versa. For 8/16/32 bit operations, OF is set according to overflow at bit 7/15/31, respectively.

- (Direction Flag, bit 10) DF defines whether ESI and/or EDI registers postdecrement or postincrement during the string instructions. Postincrement occurs if DF is reset. Postdecrement occurs if DF is set.

- IF (INTR Enable Flag, bit 9)

The IF flag, when set, allows recognition of external interrupts signalled on the INTR pin. When IF is reset, external interrupts signalled on the INTR are not recognized. IOPL indicates the maximum CPL value allowing alteration of the IF bit when new values are popped into EFLAGS or FLAGS.

TF (Trap Enable Flag, bit 8)

TF controls the generation of exception 1 trap when single-stepping through code. When TF is set, the Intel386 DX generates an exception 1 trap after the next instruction is executed. When TF is reset, exception 1 traps occur only as a function of the breakpoint addresses loaded into debug registers DR0–DR3.

SF (Sign Flag, bit 7)

SF is set if the high-order bit of the result is set, it is reset otherwise. For 8-, 16-, 32-bit operations, SF reflects the state of bit 7, 15, 31 respectively. Intel386™ DX MICROPROCESSOR

ZF (Zero Flag, bit 6)

ZF is set if all bits of the result are 0. Otherwise it is reset.

AF (Auxiliary Carry Flag, bit 4)

The Auxiliary Flag is used to simplify the addition and subtraction of packed BCD quantities. AF is set if the operation resulted in a carry out of bit 3 (addition) or a borrow into bit 3 (subtraction). Otherwise AF is reset. AF is affected by carry out of, or borrow into bit 3 only, regardless of overall operand length: 8, 16 or 32 bits.

PF (Parity Flags, bit 2)

PF is set if the low-order eight bits of the operation contains an even number of "1's" (even parity). PF is reset if the low-order eight bits have odd parity. PF is a function of only the low-order eight bits, regardless of operand size.

CF (Carry Flag, bit 0)

CF is set if the operation resulted in a carry out of (addition), or a borrow into (subtraction) the high-order bit. Otherwise CF is reset. For 8-, 16- or 32-bit operations, CF is set according to carry/borrow at bit 7, 15 or 31, respectively.

Note in these descriptions, "set" means "set to 1," and "reset" means "reset to 0."

### 2.3.4 Segment Registers

Six 16-bit segment registers hold segment selector values identifying the currently addressable memory segments. Segment registers are shown in Figure 2-4. In Protected Mode, each segment may range in size from one byte up to the entire linear and physi-

|     | SEGMENT<br>REGISTERS |               |    |          | DESC | RIPTOR  | REGIST | ERS (I   | LOAI | DED | AU   | тол   | ΛAT  | ICAL | LY)  |     |               |

|-----|----------------------|---------------|----|----------|------|---------|--------|----------|------|-----|------|-------|------|------|------|-----|---------------|

| $-$ | ~~~~                 | $\overline{}$ | 1  |          |      |         |        |          |      |     |      | (     | Dthe | r    |      |     | $\overline{}$ |

|     |                      |               |    |          |      |         |        |          |      |     |      | Se    | gme  | ent  |      |     |               |

| 15  |                      | 0             |    | Physical | Base | Address | Segmer | nt Limit |      | Att | ribu | tes f | rom  | Des  | crip | tor |               |

|     | Selector             | CS            | s_ |          |      |         |        |          |      |     |      |       |      |      |      | _   |               |

|     | Selector             | s             | s_ |          |      |         |        |          |      |     |      |       |      |      | —    |     | —             |

|     | Selector             | DS            | S- |          |      |         |        |          |      |     |      |       |      |      | —    | —   | _             |

|     | Selector             | ES            | S- |          |      |         |        |          |      |     |      |       |      |      | —    | —   | —             |

|     | Selector             | FS            | S- |          |      |         |        |          |      |     |      |       |      |      | —    | _   | —             |

|     | Selector             | G             | s- |          |      |         |        |          |      |     |      |       |      |      | —    | —   | —             |

Figure 2-4. Intel386™ DX Segment Registers, and Associated Descriptor Registers

cal space of the machine, 4 Gbytes ( $2^{32}$  bytes). If a maximum sized segment is used (limit = FFFFFFFH) it should be Dword aligned (i.e., the least two significant bits of the segment base should be zero). This will avoid a segment limit violation (exception 13) caused by the wrap around. In Real Address Mode, the maximum segment size is fixed at 64 Kbytes ( $2^{16}$  bytes).

The six segments addressable at any given moment are defined by the segment registers CS, SS, DS, ES, FS and GS. The selector in CS indicates the current code segment; the selector in SS indicates the current stack segment; the selectors in DS, ES, FS and GS indicate the current data segments.

### 2.3.5 Segment Descriptor Registers

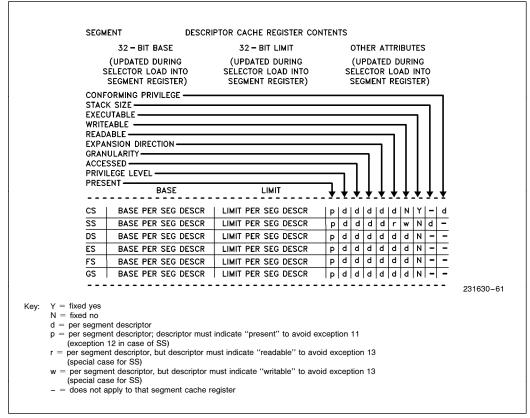

The segment descriptor registers are not programmer visible, yet it is very useful to understand their content. Inside the Intel386 DX, a descriptor register (programmer invisible) is associated with each programmer-visible segment register, as shown by Figure 2-4. Each descriptor register holds a 32-bit segment base address, a 32-bit segment limit, and the other necessary segment attributes.

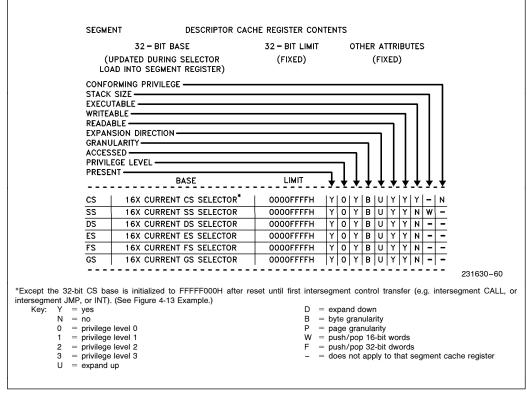

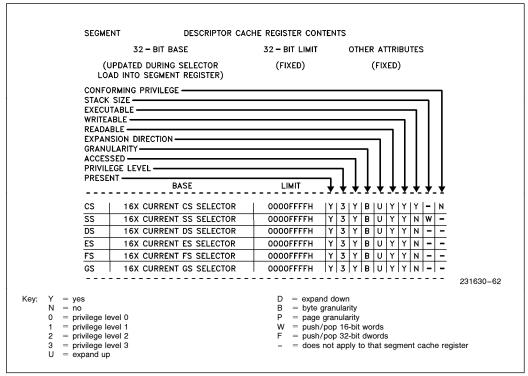

When a selector value is loaded into a segment register, the associated descriptor register is automatically updated with the correct information. In Real Address Mode, only the base address is updated directly (by shifting the selector value four bits to the left), since the segment maximum limit and attributes are fixed in Real Mode. In Protected Mode, the base address, the limit, and the attributes are all updated per the contents of the segment descriptor indexed by the selector.

Whenever a memory reference occurs, the segment descriptor register associated with the segment being used is automatically involved with the memory reference. The 32-bit segment base address becomes a component of the linear address calculation, the 32-bit limit is used for the limit-check operation, and the attributes are checked against the type of memory reference requested.

### 2.3.6 Control Registers

The Intel386 DX has three control registers of 32 bits, CR0, CR2 and CR3, to hold machine state of a global nature (not specific to an individual task). These registers, along with System Address Registers described in the next section, hold machine state that affects all tasks in the system. To access the Control Registers, load and store instructions are defined.

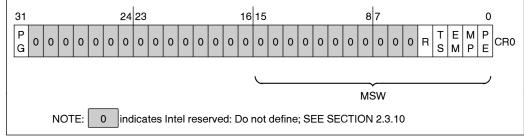

### CR0: Machine Control Register (includes 80286 Machine Status Word)

CR0, shown in Figure 2-5, contains 6 defined bits for control and status purposes. The low-order 16 bits of CR0 are also known as the Machine Status Word, MSW, for compatibility with 80286 Protected Mode. LMSW and SMSW instructions are taken as special aliases of the load and store CR0 operations, where only the low-order 16 bits of CR0 are involved. For compatibility with 80286 operating systems the Intel386 DX LMSW instructions work in an identical fashion to the LMSW instruction on the 80286. (i.e. It only operates on the low-order 16-bits of CR0 and it ignores the new bits in CR0.) New Intel386 DX operating systems should use the MOV CR0, Reg instruction.

The defined CR0 bits are described below.

PG (Paging Enable, bit 31)

the PG bit is set to enable the on-chip paging unit. It is reset to disable the on-chip paging unit.

R (reserved, bit 4)

This bit is reserved by Intel. When loading CR0 care should be taken to not alter the value of this bit.

Figure 2-5. Control Register 0

# intel

TS (Task Switched, bit 3)

TS is automatically set whenever a task switch operation is performed. If TS is set, a coprocessor ESCape opcode will cause a Coprocessor Not Available trap (exception 7). The trap handler typically saves the Intel387 DX coprocessor context belonging to a previous task, loads the Intel387 DX coprocessor state belonging to the current task, and clears the TS bit before returning to the faulting coprocessor opcode.

EM (Emulate Coprocessor, bit 2)

The EMulate coprocessor bit is set to cause all coprocessor opcodes to generate a Coprocessor Not Available fault (exception 7). It is reset to allow coprocessor opcodes to be executed on an actual Intel387 DX coprocessor (this is the default case after reset). Note that the WAIT opcode is not affected by the EM bit setting.

MP (Monitor Coprocessor, bit 1)

The MP bit is used in conjunction with the TS bit to determine if the WAIT opcode will generate a Coprocessor Not Available fault (exception 7) when TS = 1. When both MP = 1 and TS = 1, the WAIT opcode generates a trap. Otherwise, the WAIT opcode does not generate a trap. Note that TS is automatically set whenever a task switch operation is performed.

PE (Protection Enable, bit 0)

The PE bit is set to enable the Protected Mode. If PE is reset, the processor operates again in Real Mode. PE may be set by loading MSW or CR0. PE can be reset only by a load into CR0. Resetting the PE bit is typically part of a longer instruction sequence needed for proper transition from Protected Mode to Real Mode. Note that for strict 80286 compatibility, PE cannot be reset by the LMSW instruction.

### **CR1: reserved**

CR1 is reserved for use in future Intel processors.

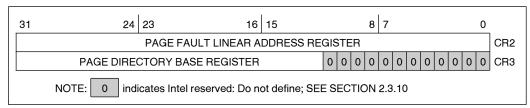

#### **CR2: Page Fault Linear Address**

CR2, shown in Figure 2-6, holds the 32-bit linear address that caused the last page fault detected. The error code pushed onto the page fault handler's stack when it is invoked provides additional status information on this page fault.

#### CR3: Page Directory Base Address

CR3, shown in Figure 2-6, contains the physical base address of the page directory table. The Intel386 DX page directory table is always pagealigned (4 Kbyte-aligned). Therefore the lowest twelve bits of CR3 are ignored when written and they store as undefined.

A task switch through a TSS which **changes** the value in CR3, or an explicit load into CR3 with any value, will invalidate all cached page table entries in the paging unit cache. Note that if the value in CR3 does not change during the task switch, the cached page table entries are not flushed.

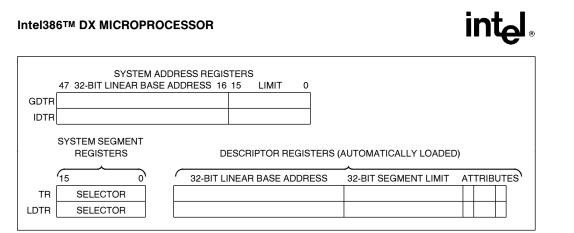

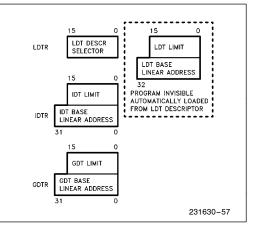

### 2.3.7 System Address Registers

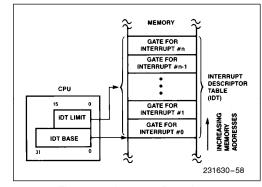

Four special registers are defined to reference the tables or segments supported by the 80286 CPU and Intel386 DX protection model. These tables or segments are:

- GDT (Global Descriptor Table),

- IDT (Interrupt Descriptor Table),

- LDT (Local Descriptor Table),

- TSS (Task State Segment).

The addresses of these tables and segments are stored in special registers, the System Address and System Segment Registers illustrated in Figure 2-7. These registers are named GDTR, IDTR, LDTR and TR, respectively. Section 4 **Protected Mode Architecture** describes the use of these registers.

### GDTR and IDTR

These registers hold the 32-bit linear base address and 16-bit limit of the GDT and IDT, respectively.

The GDT and IDT segments, since they are global to all tasks in the system, are defined by 32-bit linear addresses (subject to page translation if paging is enabled) and 16-bit limit values.

Figure 2-6. Control Registers 2 and 3

Figure 2-7. System Address and System Segment Registers

### LDTR and TR

These registers hold the 16-bit selector for the LDT descriptor and the TSS descriptor, respectively.

The LDT and TSS segments, since they are taskspecific segments, are defined by selector values stored in the system segment registers. Note that a segment descriptor register (programmer-invisible) is associated with each system segment register.

### 2.3.8 Debug and Test Registers

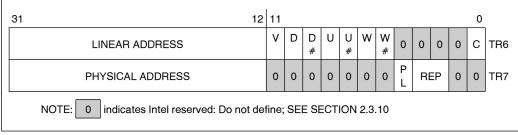

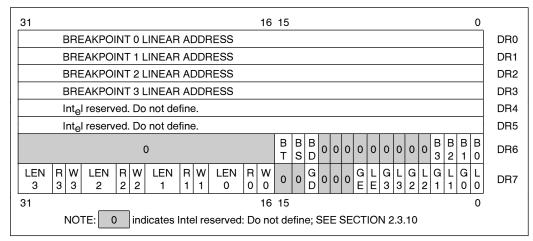

**Debug Registers:** The six programmer accessible debug registers provide on-chip support for debugging. Debug Registers DR0–3 specify the four linear breakpoints. The Debug Control Register DR7 is used to set the breakpoints and the Debug Status Register DR6, displays the current state of the breakpoints. The use of the debug registers is described in section 2.12 **Debugging support.**

| DEBUG REGISTERS                             |     |

|---------------------------------------------|-----|

| 31 0                                        |     |

| LINEAR BREAKPOINT ADDRESS 0                 | DR0 |

| LINEAR BREAKPOINT ADDRESS 1                 | DR1 |

| LINEAR BREAKPOINT ADDRESS 2                 | DR2 |

| LINEAR BREAKPOINT ADDRESS 3                 | DR3 |

| Int <sub>e</sub> l reserved. Do not define. | DR4 |

| Int <sub>e</sub> l reserved. Do not define. | DR5 |

| BREAKPOINT STATUS                           | DR6 |

| BREAKPOINT CONTROL                          | DR7 |

| TEST REGISTERS (FOR PAGE CACH<br>31 0       | HE) |

| TEST CONTROL                                | TR6 |

| TEST STATUS                                 | TR7 |

|                                             |     |

Figure 2-8. Debug and Test Registers

**Test Registers:** Two registers are used to control the testing of the RAM/CAM (Content Addressable Memories) in the Translation Lookaside Buffer portion of the Intel386 DX. TR6 is the command test register, and TR7 is the data register which contains the data of the Translation Lookaside buffer test. Their use is discussed in section 2.11 **Testability.**

Figure 2-8 shows the Debug and Test registers.

### 2.3.9 Register Accessibility

There are a few differences regarding the accessibility of the registers in Real and Protected Mode. Table 2-1 summarizes these differences. See Section 4 **Protected Mode Architecture** for further details.

#### 2.3.10 Compatibility

#### VERY IMPORTANT NOTE: COMPATIBILITY WITH FUTURE PROCESSORS

In the preceding register descriptions, note certain Intel386 DX register bits are Intel reserved. When reserved bits are called out, treat them as fully undefined. This is essential for your software compatibility with future processors! Follow the guidelines below:

- 1) Do not depend on the states of any undefined bits when testing the values of defined register bits. Mask them out when testing.

- Do not depend on the states of any undefined bits when storing them to memory or another register.

- 3) Do not depend on the ability to retain information written into any undefined bits.

- 4) When loading registers always load the undefined bits as zeros.

### Intel386<sup>TM</sup> DX MICROPROCESSOR

|                   |      |              | -      | •               |                             |       |  |  |

|-------------------|------|--------------|--------|-----------------|-----------------------------|-------|--|--|

| Register          |      | e in<br>Mode |        | e in<br>ed Mode | Use in<br>Virtual 8086 Mode |       |  |  |

| negister          | Load | Store        | Load   | Store           | Load                        | Store |  |  |

| General Registers | Yes  | Yes          | Yes    | Yes             | Yes                         | Yes   |  |  |

| Segment Registers | Yes  | Yes          | Yes    | Yes             | Yes                         | Yes   |  |  |

| Flag Register     | Yes  | Yes          | Yes    | Yes             | IOPL*                       | IOPL* |  |  |

| Control Registers | Yes  | Yes          | PL = 0 | PL = 0          | No                          | Yes   |  |  |

| GDTR              | Yes  | Yes          | PL = 0 | Yes             | No                          | Yes   |  |  |

| IDTR              | Yes  | Yes          | PL = 0 | Yes             | No                          | Yes   |  |  |

| LDTR              | No   | No           | PL = 0 | Yes             | No                          | No    |  |  |

| TR                | No   | No           | PL = 0 | Yes             | No                          | No    |  |  |

| Debug Control     | Yes  | Yes          | PL = 0 | PL = 0          | No                          | No    |  |  |

| Test Registers    | Yes  | Yes          | PL = 0 | PL = 0          | No                          | No    |  |  |

#### Table 2-1. Register Usage

#### NOTES:

PL = 0: The registers can be accessed only when the current privilege level is zero.

\*IOPL: The PUSHF and POPF instructions are made I/O Privilege Level sensitive in Virtual 8086 Mode.

However, registers which have been previously stored may be reloaded without masking.

Depending upon the values of undefined register bits will make your software dependent upon the unspecified Intel386 DX handling of these bits. Depending on undefined values risks making your software incompatible with future processors that define usages for the Intel386 DXundefined bits. AVOID ANY SOFTWARE DEPEN-DENCE UPON THE STATE OF UNDEFINED Intel386 DX REGISTER BITS.

### 2.4 INSTRUCTION SET

### 2.4.1 Instruction Set Overview

The instruction set is divided into nine categories of operations:

Data Transfer Arithmetic Shift/Rotate String Manipulation Bit Manipulation

Control Transfer

High Level Language Support

Operating System Support

Processor Control

These Intel386 DX instructions are listed in Table 2-2.

All Intel386 DX instructions operate on either 0, 1, 2, or 3 operands; where an operand resides in a register, in the instruction itself, or in memory. Most zero operand instructions (e.g. CLI, STI) take only one byte. One operand instructions generally are two bytes long. The average instruction is 3.2 bytes long. Since the Intel386 DX has a 16-byte instruction queue, an average of 5 instructions will be pre-fetched. The use of two operands permits the following types of common instructions:

Register to Register

Memory to Register

Immediate to Register

Register to Memory

Immediate to Memory.

The operands can be either 8, 16, or 32 bits long. As a general rule, when executing code written for the Intel386 DX (32-bit code), operands are 8 or 32 bits; when executing existing 80286 or 8086 code (16-bit code), operands are 8 or 16 bits. Prefixes can be added to all instructions which override the default length of the operands, (i.e. use 32-bit operands for 16-bit code), or 16-bit operands for 32-bit code).

For a more elaborate description of the instruction set, refer to the *Intel386 DX Programmer's Reference Manual.*

### 2.4.2 Intel386<sup>™</sup> DX Instructions

| Table 2-2a. Data Transfer |                                               |  |  |  |  |  |

|---------------------------|-----------------------------------------------|--|--|--|--|--|

|                           | GENERAL PURPOSE                               |  |  |  |  |  |

| MOV                       | Move operand                                  |  |  |  |  |  |

| PUSH                      | Push operand onto stack                       |  |  |  |  |  |

| POP                       | Pop operand off stack                         |  |  |  |  |  |

| PUSHA                     | Push all registers on stack                   |  |  |  |  |  |

| POPA                      | Pop all registers off stack                   |  |  |  |  |  |

| XCHG                      | Exchange Operand, Register                    |  |  |  |  |  |

| XLAT                      | Translate                                     |  |  |  |  |  |

|                           | CONVERSION                                    |  |  |  |  |  |

| MOVZX                     | Move byte or Word, Dword, with zero extension |  |  |  |  |  |

| MOVSX                     | Move byte or Word, Dword, sign extended       |  |  |  |  |  |

| CBW                       | Convert byte to Word, or Word to Dword        |  |  |  |  |  |

| CWD                       | Convert Word to DWORD                         |  |  |  |  |  |

| CWDE                      | Convert Word to DWORD extended                |  |  |  |  |  |

| CDQ                       | Convert DWORD to QWORD                        |  |  |  |  |  |

|                           | INPUT/OUTPUT                                  |  |  |  |  |  |

| IN                        | Input operand from I/O space                  |  |  |  |  |  |

| OUT                       | Output operand to I/O space                   |  |  |  |  |  |

|                           | ADDRESS OBJECT                                |  |  |  |  |  |

| LEA                       | Load effective address                        |  |  |  |  |  |

| LDS                       | Load pointer into D segment register          |  |  |  |  |  |

| LES                       | Load pointer into E segment register          |  |  |  |  |  |

| LFS                       | Load pointer into F segment register          |  |  |  |  |  |

| LGS                       | Load pointer into G segment register          |  |  |  |  |  |

| LSS                       | Load pointer into S (Stack) segment register  |  |  |  |  |  |

|                           | FLAG MANIPULATION                             |  |  |  |  |  |

| LAHF                      | Load A register from Flags                    |  |  |  |  |  |

| SAHF                      | Store A register in Flags                     |  |  |  |  |  |

| PUSHF                     | Push flags onto stack                         |  |  |  |  |  |

| POPF                      | Pop flags off stack                           |  |  |  |  |  |

| PUSHFD                    | Push EFlags onto stack                        |  |  |  |  |  |

| POPFD                     | Pop EFlags off stack                          |  |  |  |  |  |

| CLC                       | Clear Carry Flag                              |  |  |  |  |  |

| CLD                       | Clear Direction Flag                          |  |  |  |  |  |

| СМС                       | Complement Carry Flag                         |  |  |  |  |  |

| STC                       | Set Carry Flag                                |  |  |  |  |  |

| STD                       | Set Direction Flag                            |  |  |  |  |  |

| Table 2-2b. Arithmetic Instructions |                                    |  |  |  |  |  |  |

|-------------------------------------|------------------------------------|--|--|--|--|--|--|

|                                     | ADDITION                           |  |  |  |  |  |  |

| ADD                                 | Add operands                       |  |  |  |  |  |  |

| ADC                                 | Add with carry                     |  |  |  |  |  |  |

| INC                                 | Increment operand by 1             |  |  |  |  |  |  |

| AAA                                 | ASCII adjust for addition          |  |  |  |  |  |  |

| DAA                                 | Decimal adjust for addition        |  |  |  |  |  |  |

|                                     | SUBTRACTION                        |  |  |  |  |  |  |

| SUB                                 | Subtract operands                  |  |  |  |  |  |  |

| SBB                                 | Subtract with borrow               |  |  |  |  |  |  |

| DEC                                 | Decrement operand by 1             |  |  |  |  |  |  |

| NEG                                 | Negate operand                     |  |  |  |  |  |  |

| CMP                                 | Compare operands                   |  |  |  |  |  |  |

| DAS                                 | Decimal adjust for subtraction     |  |  |  |  |  |  |

| AAS                                 | ASCII Adjust for subtraction       |  |  |  |  |  |  |

|                                     | MULTIPLICATION                     |  |  |  |  |  |  |

| MUL                                 | Multiply Double/Single Precision   |  |  |  |  |  |  |

| IMUL                                | Integer multiply                   |  |  |  |  |  |  |

| AAM                                 | ASCII adjust after multiply        |  |  |  |  |  |  |

|                                     | DIVISION                           |  |  |  |  |  |  |

| DIV                                 | Divide unsigned                    |  |  |  |  |  |  |

| IDIV                                | Integer Divide                     |  |  |  |  |  |  |

| AAD                                 | ASCII adjust before division       |  |  |  |  |  |  |

|                                     | Table 2-2c. String Instructions    |  |  |  |  |  |  |

| MOVS                                | Move byte or Word, Dword string    |  |  |  |  |  |  |

| INS                                 | Input string from I/O space        |  |  |  |  |  |  |

| OUTS                                | Output string to I/O space         |  |  |  |  |  |  |

| CMPS                                | Compare byte or Word, Dword string |  |  |  |  |  |  |

| SCAS                                | Scan Byte or Word, Dword string    |  |  |  |  |  |  |

| LODS                                | Load byte or Word, Dword string    |  |  |  |  |  |  |

| STOS                                | Store byte or Word, Dword string   |  |  |  |  |  |  |

| REP                                 | Repeat                             |  |  |  |  |  |  |

| REPE/<br>REPZ                       | Repeat while equal/zero            |  |  |  |  |  |  |

| RENE/<br>REPNZ                      | Repeat while not equal/not zero    |  |  |  |  |  |  |

| Table 2-2d. Logical Instructions    |                                    |  |  |  |  |  |  |

| LOGICALS                            |                                    |  |  |  |  |  |  |

| NOT                                 | "NOT" operands                     |  |  |  |  |  |  |

| NOT  | "NOT" operands          |

|------|-------------------------|

| AND  | "AND" operands          |

| OR   | "Inclusive OR" operands |

| XOR  | "Exclusive OR" operands |

| TEST | "Test" operands         |

### Table 2-2d. Logical Instructions (Continued)

| SHIFTS        |                                |  |  |  |  |  |  |

|---------------|--------------------------------|--|--|--|--|--|--|

| SHL/SHR       | Shift logical left or right    |  |  |  |  |  |  |

| SAL/SAR       | Shift arithmetic left or right |  |  |  |  |  |  |

| SHLD/<br>SHRD | Double shift left or right     |  |  |  |  |  |  |

| ROTATES       |                                |  |  |  |  |  |  |

|               | Detete loft /right             |  |  |  |  |  |  |

ROL/ROR

Rotate left/right

RCL/RCR

Rotate through carry left/right

### Table 2-2e. Bit Manipulation Instructions

| SINGLE BIT INSTRUCTIONS |                         |  |  |

|-------------------------|-------------------------|--|--|

| вт                      | Bit Test                |  |  |

| BTS                     | Bit Test and Set        |  |  |

| BTR                     | Bit Test and Reset      |  |  |

| BTC                     | Bit Test and Complement |  |  |

| BSF                     | Bit Scan Forward        |  |  |

| BSR                     | Bit Scan Reverse        |  |  |

|                         |                         |  |  |

### Table 2-2f. Program Control Instructions

|         | CONDITIONAL TRANSFERS              |  |  |  |

|---------|------------------------------------|--|--|--|

| SETCC   | Set byte equal to condition code   |  |  |  |

| JA/JNBE | Jump if above/not below nor equal  |  |  |  |

| JAE/JNB | Jump if above or equal/not below   |  |  |  |

| JB/JNAE | Jump if below/not above nor equal  |  |  |  |

| JBE/JNA | Jump if below or equal/not above   |  |  |  |

| JC      | Jump if carry                      |  |  |  |

| JE/JZ   | Jump if equal/zero                 |  |  |  |

| JG/JNLE | Jump if greater/not less nor equal |  |  |  |

| JGE/JNL | Jump if greater or equal/not less  |  |  |  |

| JL/JNGE | Jump if less/not greater nor equal |  |  |  |

| JLE/JNG | Jump if less or equal/not greater  |  |  |  |

| JNC     | Jump if not carry                  |  |  |  |

| JNE/JNZ | Jump if not equal/not zero         |  |  |  |

| JNO     | Jump if not overflow               |  |  |  |

| JNP/JPO | Jump if not parity/parity odd      |  |  |  |

| JNS     | Jump if not sign                   |  |  |  |

| JO      | Jump if overflow                   |  |  |  |

| JP/JPE  | Jump if parity/parity even         |  |  |  |

| JS      | Jump if Sign                       |  |  |  |

### Intel386TM DX MICROPROCESSOR

| Table 2-2f. Program Control Instructions<br>(Continued) |                                                    |  |  |  |

|---------------------------------------------------------|----------------------------------------------------|--|--|--|

| U                                                       | NCONDITIONAL TRANSFERS                             |  |  |  |

| CALL                                                    | Call procedure/task                                |  |  |  |

| RET                                                     | Return from procedure                              |  |  |  |

| JMP                                                     | Jump                                               |  |  |  |

|                                                         | ITERATION CONTROLS                                 |  |  |  |

| LOOP                                                    | Loop                                               |  |  |  |

| LOOPE/<br>LOOPZ                                         | Loop if equal/zero                                 |  |  |  |

| LOOPNE/<br>LOOPNZ                                       | Loop if not equal/not zero                         |  |  |  |

| JCXZ                                                    | JUMP if register CX=0                              |  |  |  |

|                                                         | INTERRUPTS                                         |  |  |  |

| INT                                                     | Interrupt                                          |  |  |  |

| INTO                                                    | Interrupt if overflow                              |  |  |  |

| IRET                                                    | Return from Interrupt/Task                         |  |  |  |

| CLI                                                     | Clear interrupt Enable                             |  |  |  |

| STI                                                     | Set Interrupt Enable                               |  |  |  |

| Table 2-2                                               | g. High Level Language Instructions                |  |  |  |

| BOUND                                                   | Check Array Bounds                                 |  |  |  |

| ENTER                                                   | Setup Parameter Block for Entering<br>Procedure    |  |  |  |

| LEAVE                                                   | Leave Procedure                                    |  |  |  |

| Table 2-2h. Protection Model                            |                                                    |  |  |  |

| SGDT                                                    | Store Global Descriptor Table                      |  |  |  |

| SIDT                                                    | Store Interrupt Descriptor Table                   |  |  |  |

| STR                                                     | Store Task Register                                |  |  |  |

| SLDT                                                    | Store Local Descriptor Table                       |  |  |  |

| LGDT                                                    | Load Global Descriptor Table                       |  |  |  |

| LIDT                                                    | Load Interrupt Descriptor Table                    |  |  |  |

| LTR                                                     | Load Task Register                                 |  |  |  |

| LLDT                                                    | Load Local Descriptor Table                        |  |  |  |

| ARPL                                                    | Adjust Requested Privilege Level                   |  |  |  |

| LAR                                                     | Load Access Rights                                 |  |  |  |

| LSL                                                     | Load Segment Limit                                 |  |  |  |

| VERR/<br>VERW                                           | Verify Segment for Reading or Writing              |  |  |  |

| LMSW                                                    | Load Machine Status Word (lower<br>16 bits of CR0) |  |  |  |

| SMSW                                                    | Store Machine Status Word                          |  |  |  |

| Table 2                                                 | -2i. Processor Control Instructions                |  |  |  |

| HLT                                                     | Halt                                               |  |  |  |

| ω/ΔIT                                                   | Wait until BLISY # negated                         |  |  |  |

| HLT  | Halt                      |

|------|---------------------------|

| WAIT | Wait until BUSY # negated |

| ESC  | Escape                    |

| LOCK | Lock Bus                  |

|      |                           |

### 2.5 ADDRESSING MODES

### 2.5.1 Addressing Modes Overview

The Intel386 DX provides a total of 11 addressing modes for instructions to specify operands. The addressing modes are optimized to allow the efficient execution of high level languages such as C and FORTRAN, and they cover the vast majority of data references needed by high-level languages.

### 2.5.2 Register and Immediate Modes

Two of the addressing modes provide for instructions that operate on register or immediate operands:

**Register Operand Mode:** The operand is located in one of the 8-, 16- or 32-bit general registers.

**Immediate Operand Mode:** The operand is included in the instruction as part of the opcode.

### 2.5.3 32-Bit Memory Addressing Modes

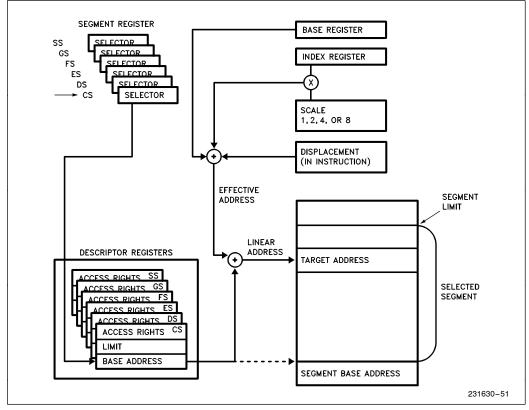

The remaining 9 modes provide a mechanism for specifying the effective address of an operand. The linear address consists of two components: the segment base address and an effective address. The effective address is calculated by using combinations of the following four address elements:

**DISPLACEMENT:** An 8-, or 32-bit immediate value, following the instruction.

**BASE:** The contents of any general purpose register. The base registers are generally used by compilers to point to the start of the local variable area.

**INDEX:** The contents of any general purpose register except for ESP. The index registers are used to access the elements of an array, or a string of characters.

**SCALE:** The index register's value can be multiplied by a scale factor, either 1, 2, 4 or 8. Scaled index mode is especially useful for accessing arrays or structures.

Combinations of these 4 components make up the 9 additional addressing modes. There is no performance penalty for using any of these addressing combinations, since the effective address calculation is pipelined with the execution of other instructions.

The one exception is the simultaneous use of Base and Index components which requires one additional clock.

As shown in Figure 2-9, the effective address (EA) of an operand is calculated according to the following formula.

EA = Base Reg + (Index Reg \* Scaling) + Displacement

Direct Mode: The operand's offset is contained as part of the instruction as an 8-, 16- or 32-bit displacement.

### EXAMPLE: INC Word PTR [500]

Register Indirect Mode: A BASE register contains the address of the operand. **EXAMPLE: MOV [ECX], EDX**

Based Mode: A BASE register's contents is added to a DISPLACEMENT to form the operands offset. **EXAMPLE: MOV ECX, [EAX** + 24]

Index Mode: An INDEX register's contents is added to a DISPLACEMENT to form the operands offset. **EXAMPLE: ADD EAX, TABLE[ESI]**

Scaled Index Mode: An INDEX register's contents is multiplied by a scaling factor which is added to a DISPLACEMENT to form the operands offset. **EXAMPLE: IMUL EBX, TABLE[ESI\*4],7**

Based Index Mode: The contents of a BASE register is added to the contents of an INDEX register to form the effective address of an operand. **EXAMPLE: MOV EAX, [ESI]** [EBX]

Based Scaled Index Mode: The contents of an IN-DEX register is multiplied by a SCALING factor and the result is added to the contents of a BASE register to obtain the operands offset. **EXAMPLE: MOV ECX, [EDX\*8] [EAX]**

Based Index Mode with Displacement: The contents of an INDEX Register and a BASE register's contents and a DISPLACEMENT are all summed together to form the operand offset.

EXAMPLE: ADD EDX, [ESI] [EBP+00FFFF0H]

Based Scaled Index Mode with Displacement: The contents of an INDEX register are multiplied by a SCALING factor, the result is added to the contents of a BASE register and a DISPLACEMENT to form the operand's offset.

EXAMPLE: MOV EAX, LOCALTABLE[EDI\*4] [EBP+80]

Figure 2-9. Addressing Mode Calculations

### 2.5.4 Differences Between 16 and 32 Bit Addresses

In order to provide software compatibility with the 80286 and the 8086, the Intel386 DX can execute 16-bit instructions in Real and Protected Modes. The processor determines the size of the instructions it is executing by examining the D bit in the CS segment Descriptor. If the D bit is 0 then all operand lengths and effective addresses are assumed to be 16 bits long. If the D bit is 1 then the default length for operands and addresses is 32 bits. In Real Mode the default size for operands and addresses is 16-bits.

Regardless of the default precision of the operands or addresses, the Intel386 DX is able to execute either 16 or 32-bit instructions. This is specified via the use of override prefixes. Two prefixes, the **Operand Size Prefix** and the **Address Length Prefix**, override the value of the D bit on an individual instruction basis. These prefixes are automatically added by Intel assemblers. Example: The processor is executing in Real Mode and the programmer needs to access the EAX registers. The assembler code for this might be MOV EAX, 32-bit MEMORYOP, ASM386 Macro Assembler automatically determines that an Operand Size Prefix is needed and generates it.

Example: The D bit is 0, and the programmer wishes to use Scaled Index addressing mode to access an array. The Address Length Prefix allows the use of MOV DX, TABLE[ESI\*2]. The assembler uses an Address Length Prefix since, with D=0, the default addressing mode is 16-bits.

Example: The D bit is 1, and the program wants to store a 16-bit quantity. The Operand Length Prefix is used to specify only a 16-bit value; MOV MEM16, DX.

### Intel386<sup>TM</sup> DX MICROPROCESSOR

|                | 16-Bit Addressing | 32-Bit Addressing                    |

|----------------|-------------------|--------------------------------------|

| BASE REGISTER  | BX,BP             | Any 32-bit GP Register               |

| INDEX REGISTER | SI,DI             | Any 32-bit GP Register<br>Except ESP |

| SCALE FACTOR   | none              | 1, 2, 4, 8                           |

| DISPLACEMENT   | 0, 8, 16 bits     | 0, 8, 32 bits                        |

#### Table 2-3. BASE and INDEX Registers for 16- and 32-Bit Addresses

The OPERAND LENGTH and Address Length Prefixes can be applied separately or in combination to any instruction. The Address Length Prefix does not allow addresses over 64K bytes to be accessed in Real Mode. A memory address which exceeds FFFFH will result in a General Protection Fault. An Address Length Prefix only allows the use of the additional Intel386 DX addressing modes.

When executing 32-bit code, the Intel386 DX uses either 8-, or 32-bit displacements, and any register can be used as base or index registers. When executing 16-bit code, the displacements are either 8, or 16 bits, and the base and index register conform to the 80286 model. Table 2-3 illustrates the differences.

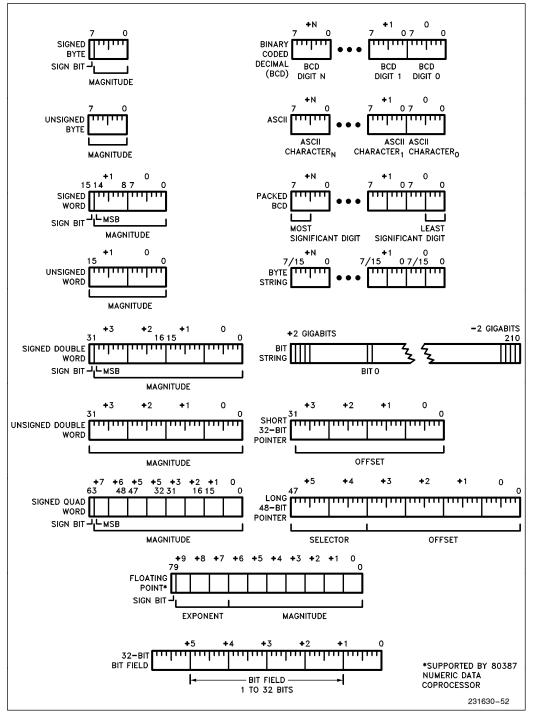

### 2.6 DATA TYPES

The Intel386 DX supports all of the data types commonly used in high level languages:

Bit: A single bit quantity.

Bit Field: A group of up to 32 contiguous bits, which spans a maximum of four bytes.

Bit String: A set of contiguous bits, on the Intel386 DX bit strings can be up to 4 gigabits long.

Byte: A signed 8-bit quantity.

Unsigned Byte: An unsigned 8-bit quantity.

Integer (Word): A signed 16-bit quantity.

Long Integer (Double Word): A signed 32-bit quantity. All operations assume a 2's complement representation.

Unsigned Integer (Word): An unsigned 16-bit quantity.

Unsigned Long Integer (Double Word): An unsigned 32-bit quantity.

Signed Quad Word: A signed 64-bit quantity.

Unsigned Quad Word: An unsigned 64-bit quanti-ty.

Offset: A 16- or 32-bit offset only quantity which indirectly references another memory location.

Pointer: A full pointer which consists of a 16-bit segment selector and either a 16- or 32-bit offset.

Char: A byte representation of an ASCII Alphanumeric or control character.

String: A contiguous sequence of bytes, words or dwords. A string may contain between 1 byte and 4 Gbytes.

BCD: A byte (unpacked) representation of decimal digits 0–9.

Packed BCD: A byte (packed) representation of two decimal digits 0–9 storing one digit in each nibble.

When the Intel386 DX is coupled with an Intel387 DX Numerics Coprocessor then the following common Floating Point types are supported.

Floating Point: A signed 32-, 64-, or 80-bit real number representation. Floating point numbers are supported by the Intel387 DX numerics co-processor.

Figure 2-10 illustrates the data types supported by the Intel386 DX and the Intel387 DX numerics co-processor.

# intel

Figure 2-10. Intel386™ DX Supported Data Types

### 2.7 MEMORY ORGANIZATION

### 2.7.1 Introduction

Memory on the Intel386 DX is divided up into 8-bit quantities (bytes), 16-bit quantities (words), and 32-bit quantities (dwords). Words are stored in two consecutive bytes in memory with the low-order byte at the lowest address, the high order byte at the high address. Dwords are stored in four consecutive bytes in memory with the low-order byte at the lowest address, the high-order byte at the highest address. The address of a word or dword is the byte address of the low-order byte.

In addition to these basic data types, the Intel386 DX supports two larger units of memory: pages and segments. Memory can be divided up into one or more variable length segments, which can be swapped to disk or shared between programs. Memory can also be organized into one or more 4K byte pages. Finally, both segmentation and paging can be combined, gaining the advantages of both systems. The Intel386 DX supports both pages and segments in order to provide maximum flexibility to the system designer. Segmentation and paging are complementary. Segmentation is useful for organizing memory in logical modules, and as such is a tool for the application programmer, while pages are useful for the system programmer for managing the physical memory of a system.

### 2.7.2 Address Spaces

The Intel386 DX has three distinct address spaces: logical, linear, and physical. A logical address

(also known as a **virtual** address) consists of a selector and an offset. A selector is the contents of a segment register. An offset is formed by summing all of the addressing components (BASE, INDEX, DIS-PLACEMENT) discussed in section 2.5.3 **Memory Addressing Modes** into an effective address. Since each task on Intel386 DX has a maximum of 16K ( $2^{14} - 1$ ) selectors, and offsets can be 4 gigabytes, ( $2^{32}$  bits) this gives a total of  $2^{46}$  bits or 64 terabytes of **logical** address space per task. The programmer sees this virtual address space.

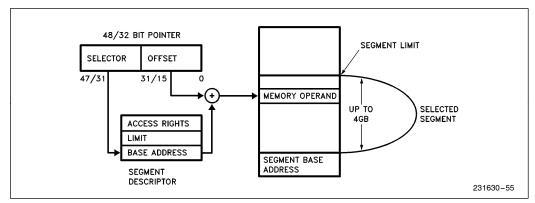

The segmentation unit translates the **logical** address space into a 32-bit **linear** address space. If the paging unit is not enabled then the 32-bit **linear** address corresponds to the **physical** address. The paging unit translates the **linear** address space into the **physical** address space. The **physical** address is what appears on the address pins.

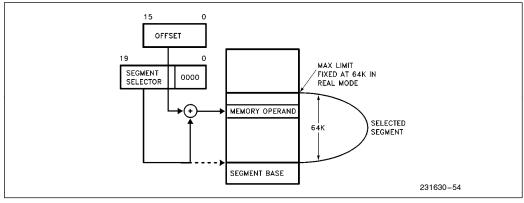

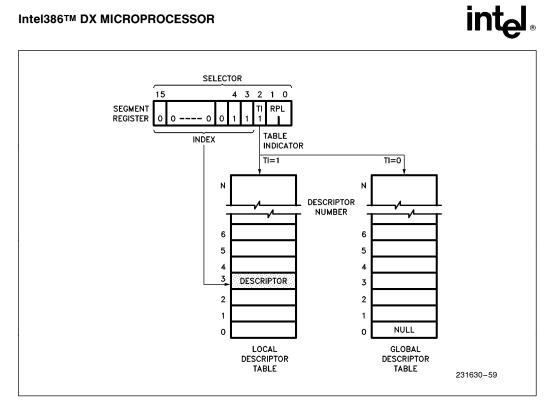

The primary difference between Real Mode and Protected Mode is how the segmentation unit performs the translation of the **logical** address into the **linear** address. In Real Mode, the segmentation unit shifts the selector left four bits and adds the result to the offset to form the **linear** address. While in Protected Mode every selector has a **linear** base address associated with it. The **linear base** address is stored in one of two operating system tables (i.e. the Local Descriptor Table or Global Descriptor Table). The selector's **linear base** address is added to the offset to form the final **linear** address.

Figure 2-11 shows the relationship between the various address spaces.

Figure 2-11. Address Translation

### 2.7.3 Segment Register Usage

The main data structure used to organize memory is the segment. On the Intel386 DX, segments are variable sized blocks of linear addresses which have certain attributes associated with them. There are two main types of segments: code and data, the segments are of variable size and can be as small as 1 byte or as large as 4 gigabytes (2<sup>32</sup> bytes).

In order to provide compact instruction encoding, and increase processor performance, instructions do not need to explicitly specify which segment register is used. A default segment register is automatically chosen according to the rules of Table 2-4 (Segment Register Selection Rules). In general, data references use the selector contained in the DS register; Stack references use the SS register and Instruction fetches use the CS register. The contents of the Instruction Pointer provides the offset. Special segment override prefixes allow the explicit use of a given segment register, and override the implicit rules listed in Table 2-4. The override prefixes also allow the use of the ES, FS and GS segment registers.

### Intel386™ DX MICROPROCESSOR

There are no restrictions regarding the overlapping of the base addresses of any segments. Thus, all 6 segments could have the base address set to zero and create a system with a four gigabyte linear address space. This creates a system where the virtual address space is the same as the linear address space. Further details of segmentation are discussed in section 4.1.

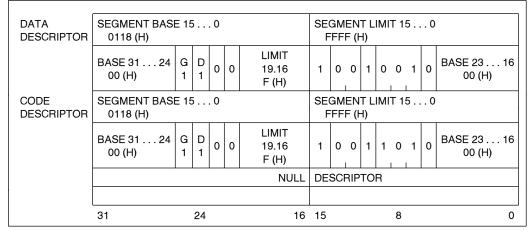

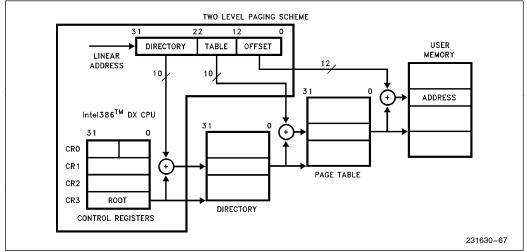

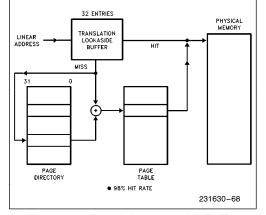

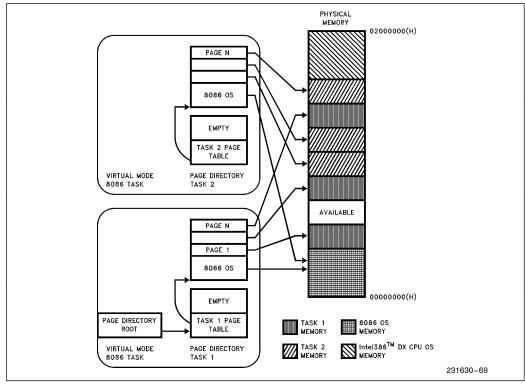

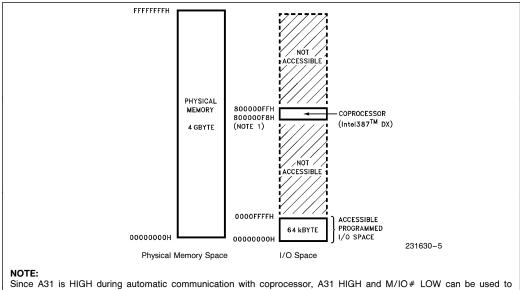

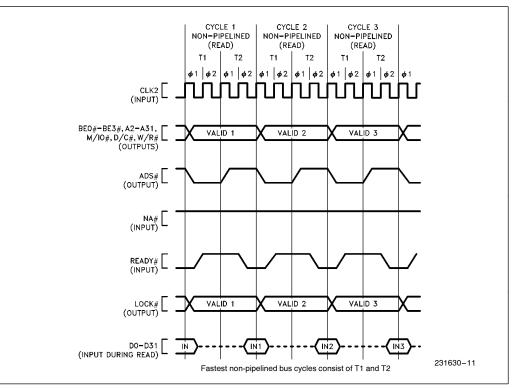

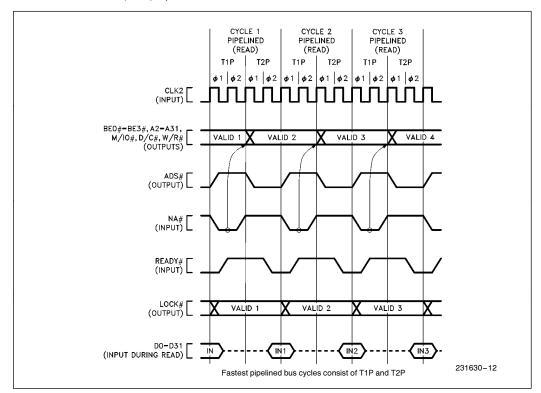

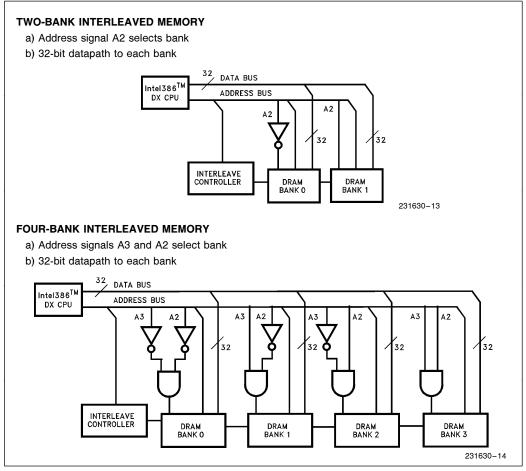

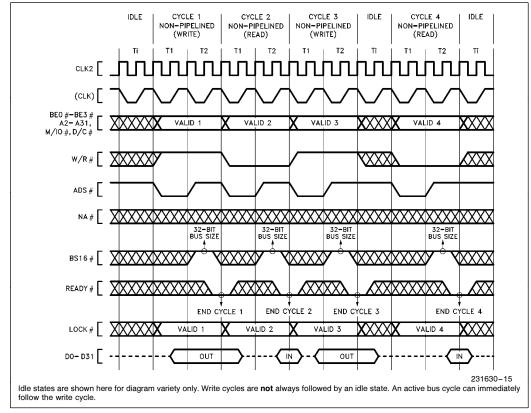

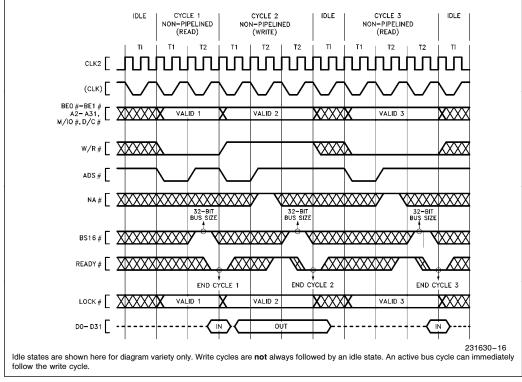

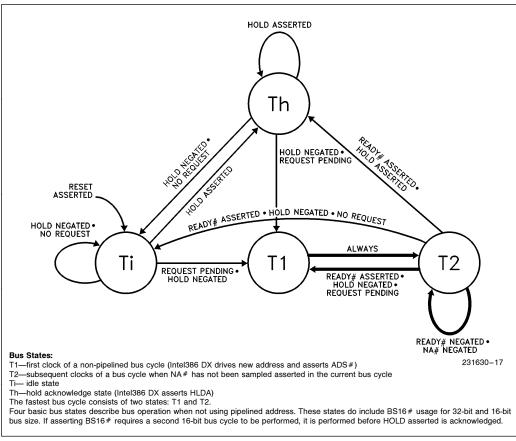

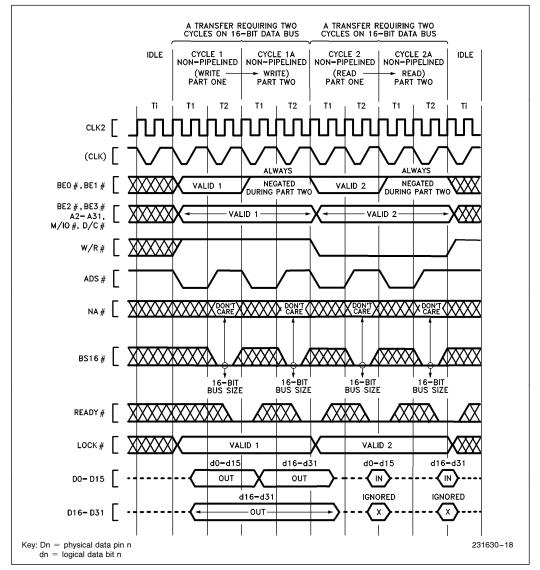

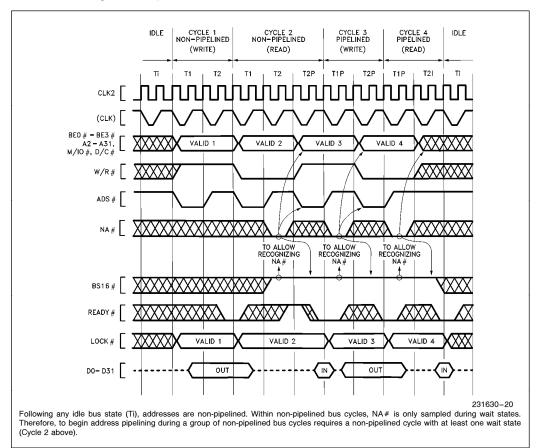

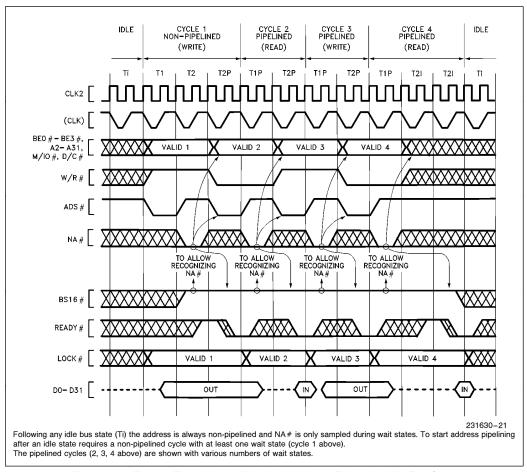

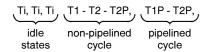

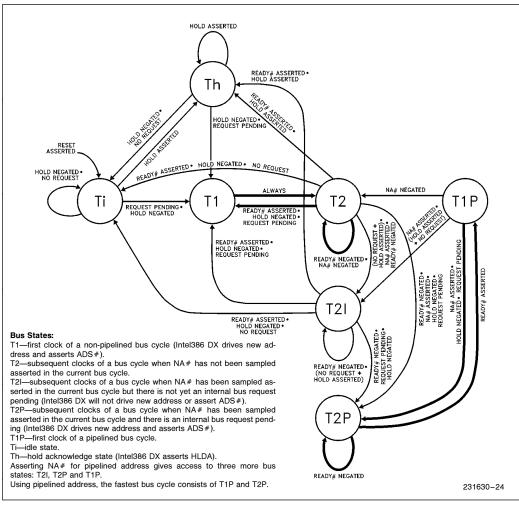

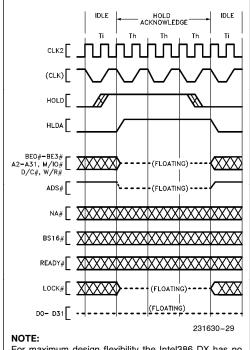

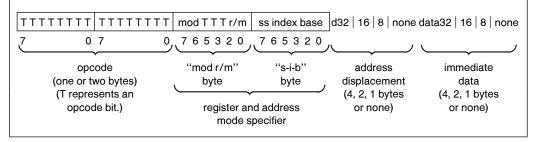

### 2.8 I/O SPACE