# High-Performance Internet Connectivity Solution

# W5300

Version 1.3.1

© 2008-2014 WIZnet Co., Ltd. All Rights Reserved.

For more information, visit our website at http://www.wiznet.co.kr

## **Document History Information**

| Version    | Date          | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ver. 1.0.0 | Mar. 11, 2008 | Release with W5300 launching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Ver. 1.1.0 | May. 15, 2008 | <ul> <li>Correct a number of typing errors</li> <li>4.4 SOCKET Register &gt;&gt; Sn_DPORTR<br/>R/W → WO, Modify the description, Refer to P.77</li> <li>4.4 SOCKET Register &gt;&gt; Sn_MSSR<br/>In the MSS Table, Modified the PPPoE MSS value of<br/>MACRAW(1502 → 1514), Refer to P.79</li> <li>5.2.1.1 TCP SERVER &gt;&gt; • ESTABLISHED : Receiving<br/>process<br/>At the <notice> phase, Modified the example code<br/>Replace 'SEND' with 'SEND_KEEP'. Refer to P.93~94</notice></li> <li>5.2.4 MACRAW &gt;&gt; • Receiving process<br/>At the <notice> phase, Modified the free size and CRC<br/>Free size 1526 → 1528, CRC(2) → CRC(4), Refer to P.111</notice></li> </ul> |

| Ver. 1.1.1 | July 4, 2008  | <ul> <li>Correct a number of typing errors</li> <li>Add PIN "BRDYn" description to "1.3 Host Interface signal"</li> <li>5.2.1.1 TCP SERVER &gt;&gt; • ESTABLISHED : Receiving process</li> <li>At the <notice> phase, Modified the example code Replace 'SEND_KEEP' with 'SEND'. Refer to P.93~94</notice></li> </ul>                                                                                                                                                                                                                                                                                                                                                                |

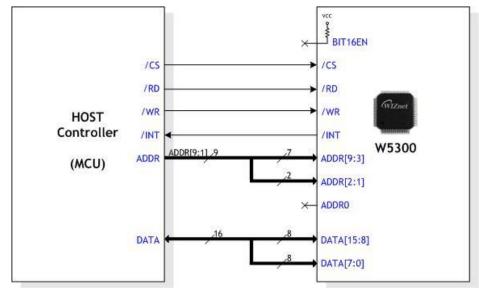

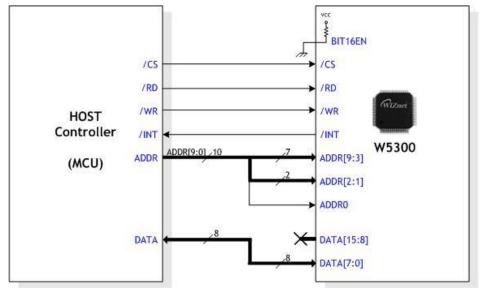

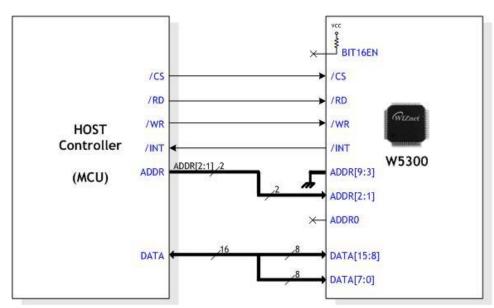

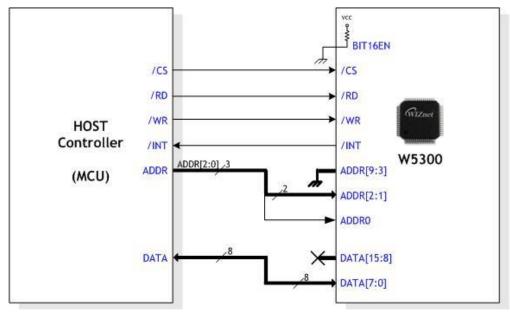

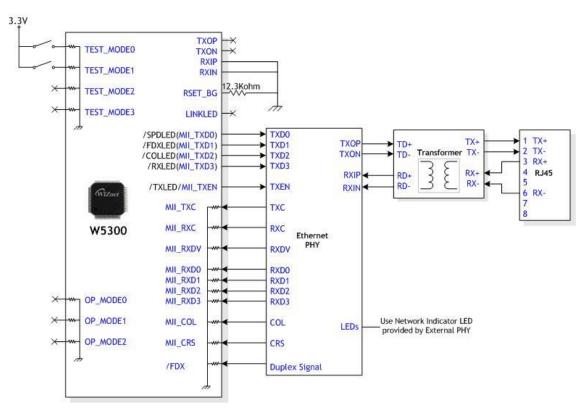

| Ver 1.2    | Dec. 30, 2008 | <ul> <li>1. PIN Description<br/>Add to '8' Symbol</li> <li>1.2 Configuration Signals<br/>Modify ADDR type (ID → I), No Internal Pulled-down<br/>Modify DATA[15:0] type (IO → IO8)</li> <li>6.2. Indirect Address Mode<br/>ADDR[9:0] has no internal pulled-down resister. So,<br/>ADDR[9:3] should be connected to ground for using indirect<br/>address mode.<br/>Modify the description &amp; figures.</li> </ul>                                                                                                                                                                                                                                                                  |

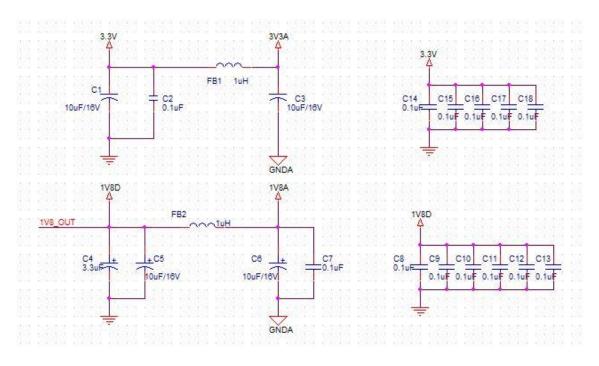

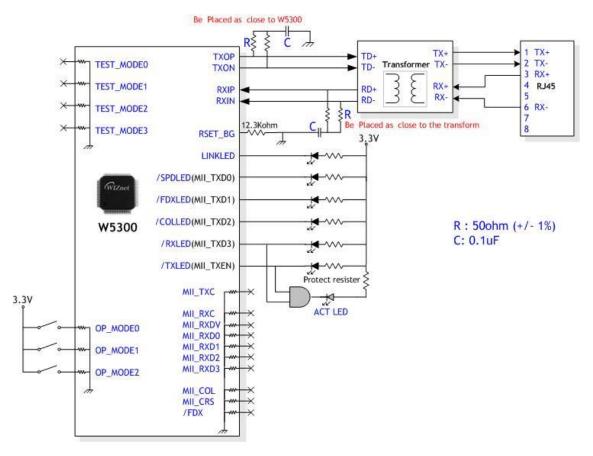

| Ver 1.2.1 | Jan. 22, 2009 | $\circ$ Modify the Figure 2.<br>Ferrite Bead 0.1uF → 1uH                                                                                                                                                                                                                                                                         |

|-----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ver 1.2.2 | Feb. 16, 2009 | <ul> <li>1.7 Clock Signals.</li> <li>Delete XTLP/XTLN Pin Type</li> <li>7. Electrical Specifications</li> <li>DC Characteristics</li> <li>Modify the Test Condition of Voн, Vo∟</li> <li>Voн - Min (2.0(2.4), Delete Typical and Max value</li> <li>Vo∟ - Delete Min and Typical value</li> </ul>                                |

| V1.2.3    | Feb.11, 2010  | <ul> <li>Change Figure 2</li> <li>Change W5300 Power Supply Signal schematic</li> </ul>                                                                                                                                                                                                                                          |

| V1.2.4    | Aug. 19, 2010 | - Change Temperature condition (p.119)                                                                                                                                                                                                                                                                                           |

| V1.2.5    | Sep. 29, 2010 | <ul> <li>Modify Table1.8 Power Supply Signal (p.21)</li> <li>1V8O: 1.8V regulator output voltage<br/>capacitor value : 0.1uF -&gt; 10uF</li> <li>Modified Figure 2 Power Design (p. 21)</li> </ul>                                                                                                                               |

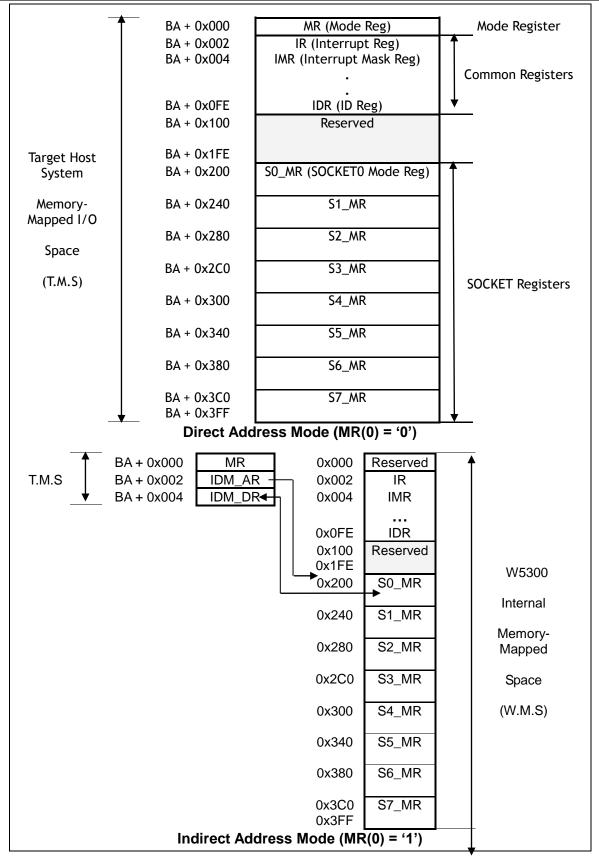

| V1.2.6    | Sep. 17, 2012 | <ul> <li>Modified Figure 3</li> <li>Modified W5300 Indirect Address Mode MR(p.23)</li> </ul>                                                                                                                                                                                                                                     |

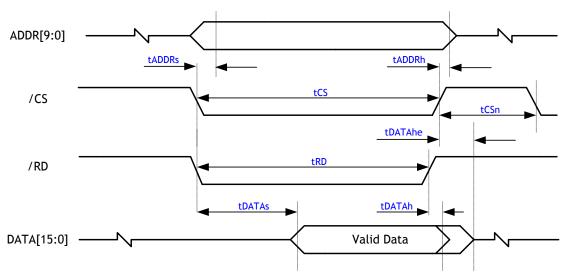

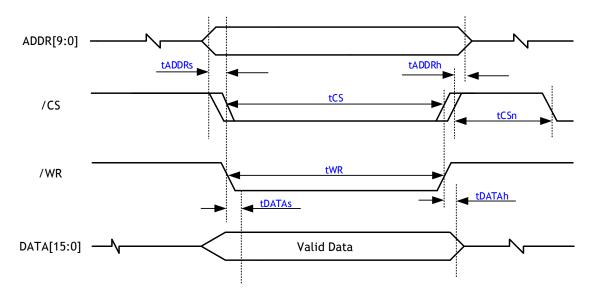

| V1.2.7    | Mar. 27, 2013 | <ul> <li>correct a number of typing error</li> <li>Modified Socket number of TMSR6,7(p.28)<br/>Socket7 -&gt; 6 ,Socket-8 -&gt; 7</li> <li>Modified range of Sn_PORTR (p.79)<br/>0x20A+0x40A -&gt; 0x20A+0x40n</li> <li>7. Electrical Specifications</li> <li>Modified Read register, Write register timing(P.123~124)</li> </ul> |

| V1.2.8    | JUN. 28, 2013 | <ul> <li>correct a number of typing error</li> <li>modified operating temperature(Top)(p.130)</li> <li>-40 to 80 -&gt; -40 to 85</li> </ul>                                                                                                                                                                                      |

| V1.2.9    | FEB. 7, 2014  | <ul> <li>Modified source code</li> <li>recved_size calculation</li> </ul>                                                                                                                                                                                                                                                        |

| V1.3.0 | JUL. 11. 2014 | Add " <notice>" information of LINKLED. (p.20)<br/>Modify the "tDATAs" of Register READ Timing (MIN -&gt; MAX)<br/>(p.124)</notice> |

|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------|

| V1.3.1 | MAR. 19. 2015 | Modify the "frequency Tolerance" of Crystal Characteristics (p.125)                                                                 |

## WIZnet's online Technical Support

If you have something to ask about WIZnet Products, write down your question on <u>Q&A Board</u> of 'Support' menu in WIZnet website (<u>www.wiznet.co.kr</u>). WIZnet Engineer will give an answer as soon as possible.

| PRODUCT                                                                              | TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SUPPORT LIBRARY                                                                                                                                      | HOW TO BUY                                                                                                                                         | OPEN HARDWAR                                                                                                                                                                                                                                          | E ABOUT                                                                                                                                                                                                                                                                                                                                     | US                                  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|                                                                                      | Click                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - FAQ - Download - Webinar                                                                                                                           | <b>*</b>                                                                                                                                           | zFi630 WIZ820io                                                                                                                                                                                                                                       | W5200                                                                                                                                                                                                                                                                                                                                       | W7200                               |

| (R)12<br>(201ama<br>923)                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |                                                                                                                                                    |                                                                                                                                                                                                                                                       | zFi630<br>h Performance 800<br>sedded WiFi Modu                                                                                                                                                                                                                                                                                             | 2.11b/g/n<br>ile                    |

| Wizard of Embed                                                                      | Ided Networking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      | Sh                                                                                                                                                 | all                                                                                                                                                                                                                                                   | WIZnet<br>Download                                                                                                                                                                                                                                                                                                                          | 1                                   |

| WIZnet NEWS                                                                          | ► MORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | APP. REFERENCE                                                                                                                                       | ► MORE                                                                                                                                             | NEWS LETTER                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                             | ► MORE                              |

| [Column] Evolving IT E                                                               | cosystem seen at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | [046] WIZ-SM10 with Energy I                                                                                                                         |                                                                                                                                                    | [Aug 2012] W5200/                                                                                                                                                                                                                                     | W7200 Application                                                                                                                                                                                                                                                                                                                           | n Note                              |

| Spinneret Web Server                                                                 | Contest Winners                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | [045] Wireless Module in Digita<br>[044] CDMA Repeater                                                                                               |                                                                                                                                                    | [July 2012] WIZnet (<br>[Jun 2012] WizFi630                                                                                                                                                                                                           | Open Hardware Pr                                                                                                                                                                                                                                                                                                                            |                                     |

| [Column] Open Source<br>WIZnet at the ESC Silic                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | [044] CDMA Repeater<br>[043] Google Power Meter                                                                                                      |                                                                                                                                                    | [Jun 2012] WizH630<br>[May 2012] WIZ820i                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                             |                                     |

| Copyright ©                                                                          | RE   MY PAGE   ONLIN<br>1998 – 2011 WIZnet Co., Ltd. Al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | l rights reserved.                                                                                                                                   | open source<br>hardware so a                                                                                                                       | Registered<br>201 2008 / ISO 14001 2004                                                                                                                                                                                                               | Mang 2017                                                                                                                                                                                                                                                                                                                                   | THRO-PART<br>PARTNER                |

|                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |                                                                                                                                                    |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                             | LOGIN   30                          |

| PRODUCT                                                                              | I WHERE TO BUY world                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | wide WIZnet distbutors GO > SUPPORT LIBRARY                                                                                                          | I SEARCH<br>HOW TO BU                                                                                                                              | GO ><br>OPEN HAR                                                                                                                                                                                                                                      | KOREA                                                                                                                                                                                                                                                                                                                                       | Login   3<br>In / Engli<br>About Us |

|                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |                                                                                                                                                    | Y OPEN HAR                                                                                                                                                                                                                                            | KOREA                                                                                                                                                                                                                                                                                                                                       | ABOUT US                            |

|                                                                                      | Carlinology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SUPPORT LIBRARY                                                                                                                                      | HOW TO BU                                                                                                                                          | Y OPEN HAR<br>Home<br>Total : 6                                                                                                                                                                                                                       | KOREA<br>DWARE  <br>-> Technical > Q&A<br>-,558 (1/438)                                                                                                                                                                                                                                                                                     | IN / ENGL                           |

| PRODUCT                                                                              | CRANOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SUPPORT LIBRARY                                                                                                                                      | HOW TO BU                                                                                                                                          | COPEN HAR                                                                                                                                                                                                                                             | KOREA<br>DWARE<br>: > Technical > Q8A                                                                                                                                                                                                                                                                                                       | ABOUT US                            |

| PRODUCT<br>UPPORT<br>and Center<br>ar                                                | CREANOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SUPPORT LIBRARY  Contents AND  Contents SUBJECT  a 9th data bit to my serial communication? In add a 9th data bit to my serial                       | HOW TO BU                                                                                                                                          | COPEN HAR                                                                                                                                                                                                                                             | KOREA           DWARE           * > Technical > Q8A           ,558 (1/438)           HIT                                                                                                                                                                                                                                                    | ABOUT US                            |

| PRODUCT UPPORT                                                                       | CREANOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SUPPORT LIBRARY                                                                                                                                      | HOW TO BU<br>SEARC<br>NAME<br>31                                                                                                                   | OPEN HAR           Home           Total : 6           DATE           2012-09-15                                                                                                                                                                       | KOREA           DWARE         -           :> Technical > Q8A         -           :,558 (1/438)         -           HIT         -           8         -                                                                                                                                                                                      | ABOUT US                            |

| PRODUCT                                                                              | CONTRACTORY CONTRA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SUPPORT LIBRARY  Contents AND  Contents AND  Contents SUBJECT  a 9th data bit to my serial communication?  I dad a 9th data bit to my serial  ation? | HOW TO BU<br>SEAR<br>NAME<br>3M<br>Wimet                                                                                                           | COPEN HAR<br>Home<br>Total : 6<br>H<br>DATE<br>2012-09-15<br>2012-09-17                                                                                                                                                                               | KOREA           DWARE                                                                                                                                                                                                                                                                                                                       | ABOUT US                            |

| UPPODUCT UPPORT ad Center ar  E-SALE wateneted-indegraam O.IMCU converses winnverses | CONTRACTORY CONTRA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SUPPORT LIBRARY                                                                                                                                      | HOW TO BU                                                                                                                                          | OPEN HAR           Home           Total : 6           DATE           2012-09-17           2012-09-14                                                                                                                                                  | KOREA           DWARE                                                                                                                                                                                                                                                                                                                       | ABOUT US                            |

| PRODUCT UPPORT add Center ar  E-SALE contrast Manuals contrast Manuals et Web Blog   | CREHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SUPPORT LIBRARY                                                                                                                                      | HOW TO BU<br>SEARC<br>NAME<br>3M<br>Waret<br>Camio Asenjo<br>Waret                                                                                 | COPEN HAR<br>Home<br>Total : 6<br>DATE<br>2012-09-17<br>2012-09-14<br>2012-09-17                                                                                                                                                                      | KOREA           DWARE         -           >> Technical > QBA         -           ,558 (1/438)         -           HIT         -           8         -           6         -           115         -           3         -                                                                                                                   | ABOUT US                            |

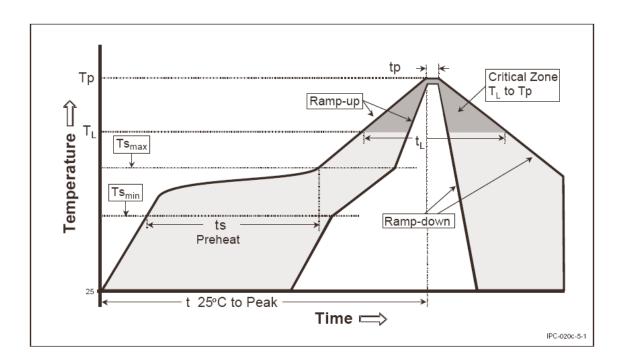

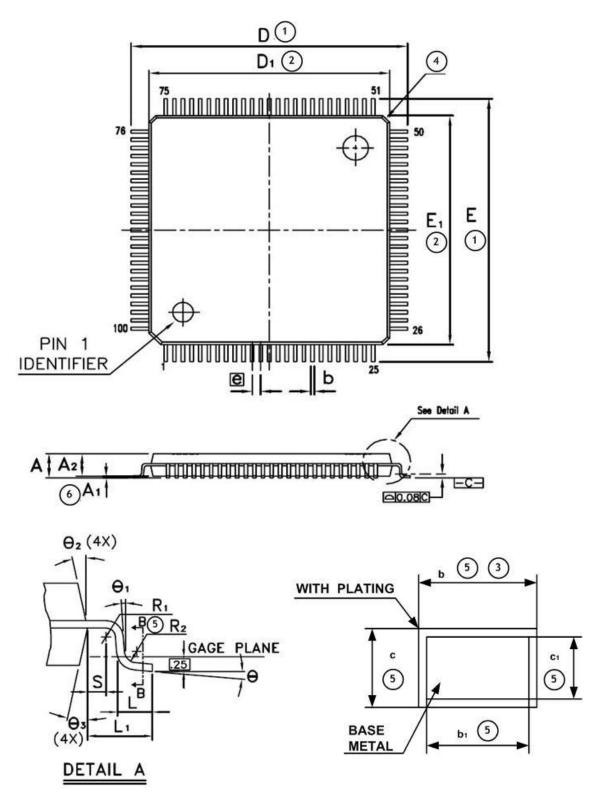

| UPPODUCT UPPORT ad Center ar  E-SALE wateneted-indegraam O.IMCU converses winnverses | CONTRACTORY<br>CORECTION<br>CORECTION<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTORY<br>CONTRACTOR | SUPPORT LIBRARY                                                                                                                                      | HOW TO BU<br>SEARC<br>NAME<br>3M<br>Wanet<br>Camio Asergio<br>Wanet<br>king<br>Wanet<br>king                                                       | COPEN HAR<br>Home<br>Total : 6<br>DATE<br>2012-09-15<br>2012-09-17<br>2012-09-17<br>2012-09-17<br>2012-09-17<br>2012-09-13<br>2012-09-13<br>2012-09-14<br>2012-09-17                                                                                  | KOREA           DWARE            2> Technical > Q&A            ,558 (1//488)            HIT            6            15         3           18            7            7                                                                                                                                                                     | ABOUT US                            |