# Compact SMART CARD Interface IC

The NCN8025 / NCN8025A is a compact and cost–effective single smart card interface IC. It is dedicated for 1.8 V / 3.0 V / 5.0 V smart card reader/writer applications. The card  $V_{CC}$  supply is provided by a built–in very low drop out and low noise LDO.

The device is fully compatible with the ISO 7816–3, EMV 4.3, UICC and related standards including NDS and other STB standards (Nagravision, Irdeto...). It satisfies the requirements specifying conditional access into Set–Top–Boxes (STB) or Conditional Access Modules (CAM and CAS).

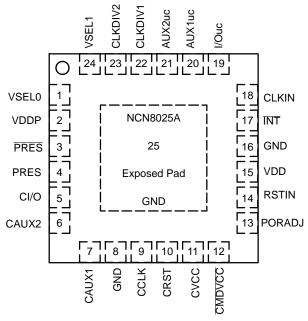

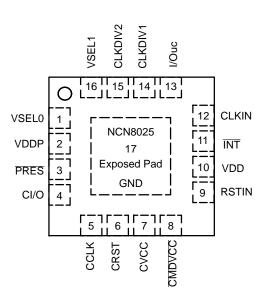

This smart card interface IC is available in a QFN-24 package (NCN8025A) providing all of the industry-standard features usually required for STB smart card interface. It is also offered in a very compact package profile, QFN-16 (NCN8025), satisfying the requirements of cost-efficiency and space-saving requested by CAM and SIM applications.

For details regarding device implementation refer to application note AND8003/D, available upon request (please contact your local ON Semiconductor sales office or representative).

#### **Features**

- Single IC Card Interface

- Fully Compatible with ISO 7816–3, EMV 4.3, UICC and Related Standards Including NDS and Other STB Standards (Nagravision, Irdeto...)

- 3 Bidirectional Buffered I/O Level Shifters (C4, C7 and C8)

(QFN-24) 1 Bidirectional I/O Level Shifter for the QFN-16 compact version

- 1.8 V, 3.0 V or 5.0 V ± 5 % Regulated Card Power Supply Generation such as ICC ≤ 70 mA

- Regulator Power Supply: V<sub>DDP</sub> = 2.7 V to 5.5 V (@ 1.8 V),

3.0 V to 5.5 V (@ 3.0 V) & 4.85 V to 5.5 V (@ 5.0 V)

- Independent Power Supply range on Controller Interface such as V<sub>DD</sub> = 2.7 V to 5.5 V

- Handles Class A, B and C Smart Cards

- Short Circuit Protection on all Card Pins

- Support up to 27 MHz input Clock with Internal Division Ratio 1/1, 1/2, 1/4 and 1/8 through CLKDIV1 and CLKDIV2

- ESD Protection on Card Pins up to +8 kV (Human Body Model)

- Activation / Deactivation Sequences (ISO7816 Sequencer)

- Fault Protection Mechanisms Enabling Automatic Device Deactivation in Case of Overload, Overheating, Card Take-off or Power Supply Drop-out (OCP, OTP, UVP)

### ON Semiconductor®

www.onsemi.com

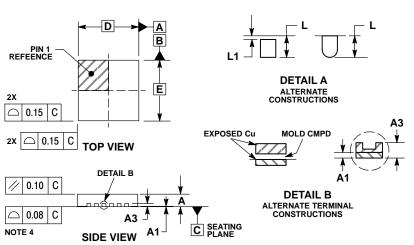

#### MARKING DIAGRAMS

QFN24 MN SUFFIX CASE 485L

QFN16 MT SUFFIX CASE 488AK

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

- Interrupt Signal INT for Card Presence and Faults

- External Under-Voltage Lockout Threshold Adjustment on VDD (PORADJ Pin) (Except QFN-16)

- Available in 2 Package Formats: QFN-24 (NCN8025A) and QFN-16 (NCN8025)

- These are Pb-Free Devices

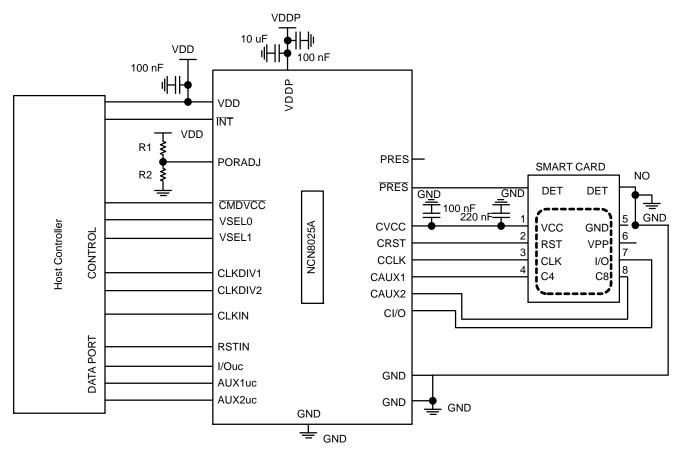

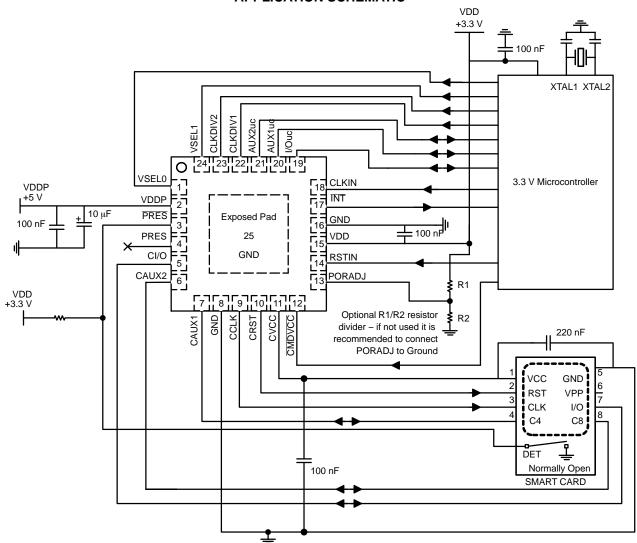

## **Typical Application**

- Pay TV, Set Top Box Decoder with Conditional Access and Pay-per-View

- Conditional Access Module (CAM / CAS)

- SIM card interface applications (UICC / USIM)

- Point Of Sales and Transaction Terminals

- Electronic Payment and Identification

Figure 1. Typical Smart Card Interface Application

Figure 2. NCN8025A – QFN–24 Pinout (Top View)

Figure 3. NCN8025 – QFN–16 Pinout (Top View)

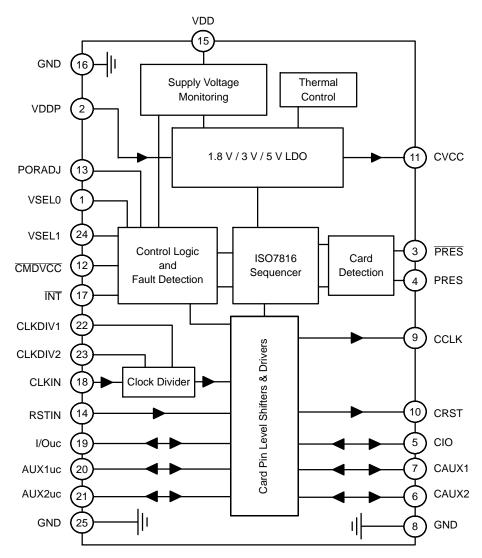

Figure 4. NCN8025A Block Diagram (QFN-24 Pin Numbering)

## **PIN FUNCTION AND DESCRIPTION**

| Pin<br>(QFN24) | Pin<br>(QFN16) | Name  | Туре             | Description                                                                                                                                                                                                                                                                                             |

|----------------|----------------|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 1              | VSEL0 | Input            | Allows selecting card $V_{CC}$ power supply voltage mode ( $5V/\overline{3V}$ or $1.8V/\overline{3V}$ ) VSEL0 = Low; CVCC = 5 V when VSEL1 = High or 3 V when VSEL1 = Low VSEL0 = High; CVCC = 1.8 V when VSEL1 = High or 3 V when VSEL1 = Low                                                          |

| 2              | 2              | VDDP  | Power            | Regulator power supply.                                                                                                                                                                                                                                                                                 |

| 3              | 3              | PRES  | Input            | Card presence pin active (card present) when PRES = Low. A built–in debounce timer of about 8 ms is activated when a card is inserted. Convenient for Normally Open (NO) Smart card connector.                                                                                                          |

| 4              | -              | PRES  | Input            | Card presence pin active (card present) when PRES = High. A built-in debounce timer of about 8 ms is activated when a card is inserted. Convenient for Normally Closed (NC) smart card connector.                                                                                                       |

| 5              | 4              | CI/O  | Input/<br>Output | This pin handles the connection to the serial I/O (C7) of the card connector. A bi–directional level translator adapts the serial I/O signal between the card and the micro controller. A 11 k $\Omega$ (typical) pull up resistor to CVCC provides a High impedance state for the smart card I/O link. |

## **PIN FUNCTION AND DESCRIPTION**

| Pin<br>(QFN24) | Pin<br>(QFN16) | Name    | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|----------------|----------------|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6              | -              | CAUX2   | Input/<br>Output  | This pin handles the connection to the chip card's serial auxiliary AUX2 I/O pin (C8). A bi–directional level translator adapts the serial I/O signal between the card and the micro controller. A 11 k $\Omega$ (typical) pull up resistor to CVCC provides a High impedance state for the smart card C8 pin.                                                                                                   |  |

| 7              | 1              | CAUX1   | Input/<br>Output  | This pin handles the connection to the chip card's serial auxiliary AUX1 I/O pin (C4). A bi–directional level translator adapts the serial I/O signal between the card and the mic controller. A 11 k $\Omega$ (typical) pull up resistor to CVCC provides a High impedance state the smart card C4 pin.                                                                                                         |  |

| 8              | -              | GND     | Ground            | Card Ground                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 9              | 5              | CCLK    | Output            | This pin is connected to the CLOCK card connector's pin (Chip card's pin C3). The Clock signal comes from the CLKIN input through clock dividers and level shifter.                                                                                                                                                                                                                                              |  |

| 10             | 6              | CRST    | Output            | This pin is connected to the chip card's RESET pin (C2) through the card connector. A level translator adapts the external Reset (RSTIN) signal to the smart card.                                                                                                                                                                                                                                               |  |

| 11             | 7              | CVCC    | Power<br>Output   | This pin is connected to the smart card power supply pin (C1). An internal low dropout regulator is programmable using the pins VSEL0 and VSEL1 to supply either 5 V or 3 V or 1.8 V output voltage. An external distributed ceramic capacitor ranging from 80 nF to 1.2 $\mu$ F recommended must be connected across CVCC and CGND. This set of capacitor (if distributed) must be low ESR (< 100 m $\Omega$ ). |  |

| 12             | 8              | CMDVCC  | Input             | Command V <sub>CC</sub> pin. Activation sequence Enable/Disable pin (active Low). The activation sequence is enabled by toggling CMDVCC High to Low and when a card is present.                                                                                                                                                                                                                                  |  |

| 13             | -              | PORADJ  | Input             | Power–on reset threshold adjustment input pin for changing the reset threshold (V <sub>DD</sub> UVLO threshold) thanks to an external resistor power divider. Needs to be connected to ground when unused.                                                                                                                                                                                                       |  |

| 14             | 9              | RSTIN   | Input             | This Reset input connected to the host and referred to VDD (microcontroller side), is connected to the smart card Reset pin through the internal level shifter which translates the level according to the CVCC programmed value.                                                                                                                                                                                |  |

| 15             | 10             | VDD     | Power<br>input    | This pin is connected to the system controller power supply. It configures the level shifted input stage to accept the signals coming from the controller. A 0.1 $\mu$ F decoupling capacitor shall be used. When V <sub>DD</sub> is below 2.30 V typical the card pins are disabled.                                                                                                                            |  |

| 16             | -              | GND     | Ground            | Ground                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 17             | 11             | INT     | Output            | The interrupt request is activated LOW on this pin. This is enabled when a card is present and the card presence is detected by $\overline{\text{PRES}}$ or PRES pins. Similarly an interrupt is generated when CVCC is overloaded. Inverter output (An open–drain output configuration with 50 k $\Omega$ pull–up resistor is available under request (metal change)).                                          |  |

| 18             | 12             | CLKIN   | Input             | Clock Input for External Clock                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 19             | 13             | I/Ouc   | Input /<br>Output | This pin is connected to an external micro–controller. A bi–directional level translator adapts the serial I/O signal between the smart card and the external controller. A built–in constant 11 k $\Omega$ (typical) resistor provides a high impedance state.                                                                                                                                                  |  |

| 20             | -              | AUX1uc  | Input /<br>Output | This pin is connected to an external micro–controller. A bi–directional level translator adapts the serial C4 signal between the smart card and the external controller. A built–in constant 11 k $\Omega$ (typical) resistor provides a high impedance state.                                                                                                                                                   |  |

| 21             | -              | AUX2uc  | Input /<br>Output | This pin is connected to an external micro–controller. A bi–directional level translator adapts the serial C8 signal between the smart card and the external controller. A built–in constant 11 k $\Omega$ (typical) resistor provides a high impedance state.                                                                                                                                                   |  |

| 22             | 14             | CLKDIV1 | Input             | This pin coupled with CLKDIV2 is used to program the clock frequency division ratio (Table 2).                                                                                                                                                                                                                                                                                                                   |  |

| 23             | 15             | CLKDIV2 | Input             | This pin coupled with CLKDIV1 is used to program the clock frequency division ratio (Table 2).                                                                                                                                                                                                                                                                                                                   |  |

| 24             | 16             | VSEL1   | Input             | Allows selecting card $V_{CC}$ power supply voltage.<br>VSEL0 = Low: CVCC = 5 V when VSEL1 = High or 3 V when VSEL1 = Low.<br>VSEL0 = High: CVCC = 1.8 V when VSEL1 = High or 3 V when VSEL1 = Low.                                                                                                                                                                                                              |  |

| 25             | 17             | GND     | Ground            | Regulator Power Supply Ground                                                                                                                                                                                                                                                                                                                                                                                    |  |

NOTE: All information below refers to QFN-24 pin numbering unless otherwise noted. This information can be transposed to the QFN-16 package according to the above "PIN FUNCTION AND DESCRIPTION" Table.

## **ATTRIBUTES**

| Characteristics                                                                                                                                                           | Values                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| ESD protection Human Body Model (HBM) (Note 1) Card Pins (card interface pins 3–11) All Other Pins Machine Model (MM) Card Pins (card interface pins 3–11) All Other Pins | 8 kV<br>2 kV<br>400 V<br>150 V |

| Moisture sensitivity (Note 2) QFN-24 and QFN-16                                                                                                                           | Level 1                        |

| Flammability Rating Oxygen Index: 28 to 34                                                                                                                                | UL 94 V-0 @ 0.125 in           |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test                                                                                                                   |                                |

- 1. Human Body Model (HBM), R = 1500  $\Omega$ , C = 100 pF.

- 2. For additional information, see Application Note AND8003/D.

## MAXIMUM RATINGS (Note 3)

| Rating                                                    | Symbol            | Value                          | Unit |

|-----------------------------------------------------------|-------------------|--------------------------------|------|

| Regulator Power Supply Voltage                            | $V_{DDP}$         | -0.3 ≤ V <sub>DDP</sub> ≤ 5.5  | V    |

| Power Supply from Microcontroller Side                    | $V_{DD}$          | $-0.3 \le V_{DD} \le 5.5$      | V    |

| External Card Power Supply                                | CVCC              | -0.3 ≤ CVCC ≤ 5.5              | V    |

| Digital Input Pins                                        | V <sub>in</sub>   | $-0.3 \le V_{in} \le V_{DD}$   | V    |

| Digital Output Pins (I/Ouc, AUX1uc, AUX2uc, ĪNT)          | V <sub>out</sub>  | $-0.3 \le V_{out} \le V_{DD}$  | V    |

| Smart card Output Pins                                    | V <sub>out</sub>  | -0.3 ≤ V <sub>out</sub> ≤ CVCC | V    |

| Thermal Resistance Junction–to–Air (Note 4) QFN–24 QFN–16 | $R_{	heta JA}$    | 37<br>48                       | °C/W |

| Operating Ambient Temperature Range                       | T <sub>A</sub>    | -40 to +85                     | °C   |

| Operating Junction Temperature Range                      | TJ                | -40 to +125                    | °C   |

| Maximum Junction Temperature                              | T <sub>Jmax</sub> | +125                           | °C   |

| Storage Temperature Range                                 | T <sub>stg</sub>  | -65 to + 150                   | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

3. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at T<sub>A</sub> = +25°C.

- 4. Exposed Pad (GND) must be connected to PCB.

## **POWER SUPPLY SECTION** ( $V_{DD} = 3.3 \text{ V}$ ; $V_{DDP} = 5 \text{ V}$ ; $T_{amb} = 25^{\circ}\text{C}$ ; $F_{CLKIN} = 10 \text{ MHz}$ )

| Symbol                  | Parameter                                                                                                                                                                                                                                                                                                                                                               | Min                          | Тур                          | Max                          | Unit        |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|-------------|

| $V_{DDP}$               | $ \begin{array}{lll} \mbox{Regulator Power Supply,} \\ \mbox{CVCC} = 5.0 \ \mbox{V,} &  \mbox{ICC}  \leq 70 \ \mbox{mA (EMV Conditions)} \\ \mbox{IICC}   \leq 70 \ \mbox{mA (NDS Conditions)} \\ \mbox{CVCC} = 3.0 \ \mbox{V,} &  \mbox{IICC}  \leq 70 \ \mbox{mA} \\ \mbox{CVCC} = 1.8 \ \mbox{V,} &  \mbox{IICC}  \leq 70 \ \mbox{mA} \\ \end{array} $               | 4.75<br>4.85<br>3.0<br>2.7   | 5.0<br>5.0                   | 5.5<br>5.5<br>5.5<br>5.5     | V           |

| I <sub>DDP</sub>        | Inactive mode (CMDVCC = High)                                                                                                                                                                                                                                                                                                                                           | -                            | _                            | 1                            | μΑ          |

| I <sub>DDP</sub>        | $\frac{\text{DC Operating supply current, F}_{\text{CLKIN}} = 10 \text{ MHz, Cout}_{\text{CCLK}} = 33 \text{ pF, }  I_{\text{CVCC}}  = 0}{(\overline{\text{CMDVCC}} = \text{Low})}$                                                                                                                                                                                     | -                            | -                            | 3.0                          | mA          |

| I <sub>DDP</sub>        | DC Operating supply current,  CVCC = 5 V, I <sub>CVCC</sub> = 70 mA  CVCC = 3 V, I <sub>CVCC</sub> = 70 mA  CVCC = 1.8 V, I <sub>CVCC</sub> = 70 mA                                                                                                                                                                                                                     | -<br>-<br>-                  | -<br>-<br>-                  | 150<br>150<br>150            | mA          |

| $V_{DD}$                | Operating Voltage                                                                                                                                                                                                                                                                                                                                                       | 2.7                          | -                            | 5.5                          | V           |

| $I_{VDD}$               | Inactive mode – standby current (CMDVCC = High)                                                                                                                                                                                                                                                                                                                         | -                            | _                            | 60                           | μΑ          |

| I <sub>VDD</sub>        | Operating Current – $F_{CLK\_IN}$ = 10 MHz , $Cout_{CCLK}$ = 33 pF $ I_{CVCC} $ = 0 ( $\overline{CMDVCC}$ = Low)                                                                                                                                                                                                                                                        | -                            | -                            | 1                            | mA          |

| UVLOV <sub>DD</sub>     | Under Voltage Lock-Out (UVLO), no external resistor at pin PORADJ (connected to GND), falling V <sub>DD</sub> level                                                                                                                                                                                                                                                     | 2.20                         | 2.30                         | 2.40                         | V           |

| UVLOHys                 | UVLO Hysteresis, no external resistor at pin PORADJ (Connected to GND)                                                                                                                                                                                                                                                                                                  | 50                           | 100                          | 180                          | mV          |

| PORADJ pin              |                                                                                                                                                                                                                                                                                                                                                                         |                              |                              |                              |             |

| V <sub>PORth+</sub>     | External Rising threshold voltage on V <sub>DD</sub> for Power On Reset – pin PORADJ                                                                                                                                                                                                                                                                                    | 1.20                         | 1.27                         | 1.34                         | V           |

| V <sub>PORth</sub>      | External Falling threshold voltage on V <sub>DD</sub> for Power On Reset – pin PORADJ                                                                                                                                                                                                                                                                                   | 1.15                         | 1.20                         | 1.28                         | V           |

| V <sub>PORHys</sub>     | Hysteresis on V <sub>PORth</sub> (pin PORADJ)                                                                                                                                                                                                                                                                                                                           | 30                           | 80                           | 100                          | mV          |

| t <sub>POR</sub>        | Width of Power–On Reset pulse (Note 5) No external resistor on PORADJ External resistor on PORADJ                                                                                                                                                                                                                                                                       | 4 4                          | 8<br>8                       | 12<br>12                     | ms<br>ms    |

| I <sub>IL</sub>         | Low level input leakage current, V <sub>IL</sub> < 0.5 V (Pull-down source current)                                                                                                                                                                                                                                                                                     |                              | 5                            |                              | μΑ          |

| Low Dropout             | Regulator                                                                                                                                                                                                                                                                                                                                                               |                              |                              |                              |             |

| C <sub>CVCC</sub>       | Output Capacitance on card power supply CVCC (Note 6)                                                                                                                                                                                                                                                                                                                   | 0.08                         | 0.32                         | 1.2                          | μF          |

| CVCC                    | Output Card Supply Voltage (including ripple)<br>$1.8 \text{ V CVCC}$ mode @ ICC $\le$ 70 mA<br>$3.0 \text{ V CVCC}$ mode @ ICC $\le$ 70 mA<br>$5.0 \text{ V CVCC}$ mode @ ICC $\le$ 70 mA with $4.85 \text{ V } \le \text{VDDP} \le 5.5 \text{ V (NDS)}$<br>$5.0 \text{ V CVCC}$ mode @ ICC $\le$ 70 mA with $4.75 \text{ V } \le \text{VDDP} \le 5.5 \text{ V (EMV)}$ | 1.70<br>2.85<br>4.75<br>4.60 | 1.80<br>3.00<br>5.00<br>5.00 | 1.90<br>3.15<br>5.25<br>5.25 | V<br>V<br>V |

| CVCC                    | Current pulses 15 nAs (t < 400 ns & $ I_{CC} $ < 100 mA peak) (Note 5) 1.8 V mode / Ripple $\leq$ 250 mV (2.7 V $\leq$ V <sub>DDP</sub> $\leq$ 5.5 V) Current pulses 40 nAs (t < 400 ns & $ I_{CC} $ < 200 mA peak)                                                                                                                                                     | 1.66                         | 1.80                         | 1.90                         | V           |

|                         | $3.0 \text{ V mode / Ripple} \le 250 \text{ mV } (2.9 \text{ V} \le \text{V}_{DDP} \le 5.5 \text{ V})$<br>Current pulses 40 nAs (t < 400 ns & $ I_{CC} $ < 200 mA peak)<br>$5.0 \text{ V mode / Ripple} \le 250 \text{ mV } (4.85 \text{ V} \le \text{V}_{DDP} \le 5.5 \text{ V})$                                                                                      | 2.70<br>4.60                 | 3.00<br>5.00                 | 3.30<br>5.30                 | V           |

| I <sub>CVCC</sub>       | Card Supply Current @ CVCC = 1.8 V @ CVCC = 3.0 V @ CVCC = 5.0 V                                                                                                                                                                                                                                                                                                        |                              |                              | 70<br>70<br>70               | mA          |

| I <sub>CVCC_SC</sub>    | Short -Circuit Current - CVCC shorted to ground                                                                                                                                                                                                                                                                                                                         |                              | 120                          | 150                          | mA          |

| $\Delta V_{	ext{CVCC}}$ | Output Card Supply Voltage Ripple peak–to–peak – $f_{ripple}$ = 100 Hz to 200 MHz (load transient frequency with 65 mA peak current and 50% Duty Cycle) (Note 5)                                                                                                                                                                                                        |                              |                              | 300                          | mV          |

| CVCC <sub>SR</sub>      | Slew Rate on CVCC turn-on / turn-off (Note 5)                                                                                                                                                                                                                                                                                                                           |                              |                              | 0.22                         | V/µs        |

<sup>5.</sup> Guaranteed by design and characterization.

6. These values take into account the tolerance of the cms capacitor used. CMS capacitor very low ESR (< 100 mΩ, X5R / X7R).</li>

$\textbf{HOST INTERFACE SECTION} \ CLKIN, \ RSTIN, \ I/Ouc, \ AUX1uc, \ AUX2uc, \ CLKDIV1, \ CLKDIV2, \ \overline{CMDVCC}, \ VSEL0, \ VSEL1 \ (V_{DD} = 1.00)$ 3.3 V;  $V_{DDP} = 5$  V;  $T_{amb} = 25^{\circ}C$ ;  $F_{CLKIN} = 10$  MHz)

| Symbol             | Parameter                                                                                                                                                                                                        | Min                    | Тур | Max                   | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----------------------|------|

| F <sub>CLKIN</sub> | Clock frequency on pin CLKIN (Note 7)                                                                                                                                                                            | -                      | -   | 27                    | MHz  |

| V <sub>IL</sub>    | Input Voltage level Low: CLKIN, RSTIN, CLKDIV1, CLKDIV2, CMDVCC, VSEL0, VSEL1                                                                                                                                    | -0.3                   | -   | 0.3 x V <sub>DD</sub> | V    |

| V <sub>IH</sub>    | Input Voltage level High: CLKIN, RSTIN, CLKDIV1, CLKDIV2, CMDVCC, VSEL0, VSEL1                                                                                                                                   | 0.7 x V <sub>DD</sub>  | -   | V <sub>DD</sub> + 0.3 | V    |

| 1112               | CLKDIV1, CLKDIV2, CMDVCC, RSTIN, CLKIN, VSEL0, VSEL1 Low Level Input Leakage Current, V <sub>IL</sub> = 0 V                                                                                                      | _                      | -   | 1                     | μΑ   |

| II <sub>IH</sub> I | CLKDIV1, CLKDIV2, CMDVCC, RSTIN, CLKIN, VSEL0, VSEL1 Low Level Input Leakage Current, V <sub>IH</sub> = V <sub>DD</sub>                                                                                          | -                      | -   | 1                     | μΑ   |

| V <sub>IL</sub>    | Input Voltage level Low: I/Ouc, AUX1uc, AUX2uc                                                                                                                                                                   | -0.3                   |     | 0.5                   | V    |

| $V_{IH}$           | Input Voltage level High: I/Ouc, AUX1uc, AUX2uc                                                                                                                                                                  | 0.7 x V <sub>DD</sub>  |     | $V_{DD} + 0.3$        | V    |

| I <sub>IL</sub>    | I/Ouc, AUX1uc, AUX2uc Low level input leakage current, V <sub>IL</sub> = 0 V                                                                                                                                     | -                      | -   | 600                   | μΑ   |

| I <sub>IH</sub>    | I/Ouc, AUX1uc, AUX2uc High level input leakage current, V <sub>IH</sub> = V <sub>DD</sub>                                                                                                                        | -                      | -   | 10                    | μΑ   |

| V <sub>OH</sub>    | l/Ouc, AUX1uc, AUX2uc data channels, @ Cs $\leq$ 30 pF High Level Output Voltage (CRD_I/O = CAUX1 = CAUX2 = CVCC) $I_{OH} = -40~\mu\text{A}$ for $V_{DD} > 2~V~(I_{OH} = -20~\mu\text{A}$ for $V_{DD} \leq 2~V)$ | 0.75 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.1 | V    |

| $V_{OL}$           | Low Level Output Voltage (CRD_I/O = CAUX1 = CAUX2 = 0 V) I <sub>OL</sub> = + 1 mA                                                                                                                                | 0                      | -   | 0.3                   | V    |

| t <sub>Ri/Fi</sub> | Input Rising/Falling times (Note 7)                                                                                                                                                                              | -                      | -   | 1.2                   | μS   |

| t <sub>Ro/Fo</sub> | Output Rising/Falling times (Note 7)                                                                                                                                                                             | -                      | -   | 0.1                   | μS   |

| R <sub>pu</sub>    | I/0uc, AUX1uc, AUX2uc Pull Up Resistor                                                                                                                                                                           | 8                      | 11  | 16                    | kΩ   |

| V <sub>OH</sub>    | Output High Voltage<br>INT @ I <sub>OH</sub> = –15 μA (source)                                                                                                                                                   | 0.75 x V <sub>DD</sub> | -   | -                     | V    |

| V <sub>OL</sub>    | Output Low Voltage INT @ I <sub>OL</sub> = 2 mA (sink)                                                                                                                                                           | 0                      | -   | 0.30                  | V    |

| R <sub>INT</sub>   | TNT Pull Up Resistor (open-drain output configuration option) (Note 8)                                                                                                                                           | 40                     | 50  | 60                    | kΩ   |

Guaranteed by design and characterization.

Option available under request (metal change). The current option is an inverter–like output.

$\begin{array}{l} \textbf{SMART CARD INTERFACE SECTION} \text{ CI/O}, \text{ CAUX1}, \text{ CAUX2}, \text{ CCLK}, \text{ CRST}, \text{ PRES}, \overline{\text{PRES}} \text{ ($V_{DD} = 3.3 V$; $V_{DDP} = 5 V$; $T_{amb} = 25^{\circ}$C$; } \\ F_{CLKIN} = 10 \text{ MHz)} \end{array}$

| Symbol                                               | Parameter                                                                                                                                                                           | Min                           | Тур         | Max                                            | Unit                     |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------|------------------------------------------------|--------------------------|

| V <sub>OH</sub><br>V <sub>OL</sub>                   | CRST @ CVCC = 1.8 V, 3.0 V, 5.0 V<br>Output RESET $V_{OH}$ @ $I_{rst}$ = $-200  \mu A$<br>Output RESET $V_{OL}$ @ $I_{rst}$ = $200  \mu A$                                          | 0.9 x CVCC<br>0               | -<br>-      | CVCC<br>0.20                                   | V<br>V                   |

| t <sub>R</sub><br>t <sub>F</sub><br>t <sub>R/F</sub> | Output RESET Rise time @ $C_{out}$ = 100 pF (Note 9)<br>Output RESET Fall time @ $C_{out}$ = 100 pF (Note 9)<br>Output Rise/Fall times @ CVCC = 1.8 V & $C_{out}$ = 100 pF (Note 9) | -<br>-<br>-                   | -<br>-<br>- | 100<br>100<br>200                              | ns<br>ns<br>ns           |

| td                                                   | RSTIN to CRST delay – Reset enabled (Note 9)                                                                                                                                        | -                             | -           | 2                                              | μs                       |

|                                                      | CCLK @ CVCC = 1.8 V, 3.0 V or 5.0 V                                                                                                                                                 |                               |             |                                                |                          |

| F <sub>CRDCLK</sub>                                  | Output Frequency (Note 9)                                                                                                                                                           | -                             | -           | 27                                             | MHz                      |

| $V_{ m OH}$ $V_{ m OL}$                              | Output CCLK $V_{OH}$ @ $I_{clk}$ = -200 $\mu A$ Output CCLK $V_{OL}$ @ $I_{clk}$ = 200 $\mu A$                                                                                      | 0.9 x CVCC<br>0               | -<br>-      | CVCC<br>+0.2                                   | V<br>V                   |

| $F_{DC}$                                             | Output Duty Cycle (Note 9)                                                                                                                                                          | 45                            | _           | 55                                             | %                        |

| t <sub>rills</sub><br>t <sub>ulsa</sub>              | Rise & Fall time Output CCLK Rise time @ C <sub>out</sub> = 33 pF (Note 9) Output CCLK Fall time @ C <sub>out</sub> = 33 pF (Note 9)                                                | -<br>-                        | -<br>-      | 16<br>16                                       | ns<br>ns                 |

| SR                                                   | Slew Rate @ C <sub>out</sub> = 33 pF (CVCC = 3.0 V or 5.0 V) (Note 9)                                                                                                               | 0.2                           | -           | _                                              | V/ns                     |

|                                                      | CAUX1, CAUX2, CI/O @ CVCC = 1.8 V, 3.0 V, 5.0 V                                                                                                                                     |                               |             |                                                |                          |

| V <sub>IH</sub>                                      | Input Voltage High Level<br>1.8 V Mode<br>3.0 V Mode<br>5.0 V Mode                                                                                                                  | 1.0<br>1.6<br>2.3             | -<br>-<br>- | CVCC + 0.3<br>CVCC + 0.3<br>CVCC + 0.3         | V<br>V<br>V              |

| $V_{IL}$                                             | Input Voltage Low Level 1.8 V mode 3.0 V mode 5.0 V mode                                                                                                                            | -0.30<br>-0.30<br>-0.30       | -<br>-<br>- | 0.50<br>0.80<br>1.00                           | V<br>V<br>V              |

| I <sub>IL</sub>  <br> I <sub>IH</sub>                | Low Level Input current $V_{IL} = 0 \text{ V}$<br>High Level Input current $V_{IH} = \text{CVCC}$                                                                                   | -<br>-                        |             | 600<br>10                                      | μ <b>Α</b><br>μ <b>Α</b> |

| V <sub>OH</sub>                                      | Output $V_{OH}$ @ $I_{OH}$ = -40 $\mu$ A for CVCC = 3.0 V and 5.0 V @ $I_{OH}$ = -20 $\mu$ A for CVCC = 1.8 V                                                                       | 0.8 x CVCC<br>0.8 x CVCC      | -<br>-      | CVCC + 0.1<br>CVCC + 0.1                       | V<br>V                   |

| V <sub>OL</sub>                                      | Output $V_{OL}$<br>@ $I_{OL} = 1$ mA, $V_{IL} = 0$ V for CVCC = 1.8 V<br>@ $I_{OL} = 1$ mA, $V_{IL} = 0$ V for CVCC = 3.0 V and 5.0 V                                               | 0<br>0                        | -<br>-      | 0.27<br>0.30                                   | V<br>V                   |

| t <sub>Ri / Fi</sub>                                 | Input Rising/Falling times (Note 9)                                                                                                                                                 | -                             | _           | 1.2                                            | μs                       |

| t <sub>Ro / Fo</sub>                                 | Output Rising/Falling times / Cout = 80 pF (Note 9)                                                                                                                                 | -                             | _           | 0.1                                            | μs                       |

| F <sub>bidi</sub>                                    | Maximum data rate through bidirectional I/O, AUX1 & AUX2 channels (Note 9)                                                                                                          | _                             | _           | 1                                              | MHz                      |

| R <sub>PU</sub>                                      | CAUX1, CAUX2, CI/O Pull- Up Resistor                                                                                                                                                | 8                             | 11          | 16                                             | kΩ                       |

| t <sub>IO</sub>                                      | Propagation delay IOuc -> CI/O and CI/O -> IOuc (falling edge) (Note 9)                                                                                                             | -                             | -           | 200                                            | ns                       |

| tpu                                                  | Active pull-up pulse width buffers I/O, AUX1 and AUX2 (Note 9)                                                                                                                      | ı                             | 1           | 200                                            | ns                       |

| C <sub>in</sub>                                      | Input Capacitance on data channels                                                                                                                                                  | ı                             | ı           | 10                                             | pF                       |

| V <sub>IH</sub><br>V <sub>IL</sub>                   | PRES, PRES  Card Presence Voltage High Level  Card Presence Voltage Low Level                                                                                                       | 0.7 x V <sub>DD</sub><br>-0.3 | -<br>-      | V <sub>DD</sub> + 0.3<br>0.3 x V <sub>DD</sub> | V                        |

**SMART CARD INTERFACE SECTION** CI/O, CAUX1, CAUX2, CCLK, CRST, PRES,  $\overline{\text{PRES}}$  (V<sub>DD</sub> = 3.3 V; V<sub>DDP</sub> = 5 V; T<sub>amb</sub> = 25°C; F<sub>CLKIN</sub> = 10 MHz)

| Symbol                | Parameter                                                                      | Min | Тур | Max     | Unit |

|-----------------------|--------------------------------------------------------------------------------|-----|-----|---------|------|

|                       | PRES, PRES High level input leakage current, V <sub>IH</sub> = V <sub>DD</sub> |     |     |         | μΑ   |

| I <sub>IH</sub>       | PRES PRES                                                                      |     | 5   | 10<br>1 |      |

| اایدا                 | Low level input leakage current, V <sub>IL</sub> = 0 V PRES PRES               |     | 5   | 1<br>10 |      |

| T <sub>debounce</sub> | Debounce time PRES and PRES (Note 9)                                           | 5   | 8   | 12      | ms   |

| I <sub>CI/O</sub>     | CI/O, CAUX1, CAUX2 current limitation                                          | -   | -   | 15      | mA   |

| ICCLK                 | CCLK current limitation                                                        | -   | -   | 70      | mA   |

| I <sub>CRST</sub>     | CRST current limitation                                                        | -   | -   | 20      | mA   |

| T <sub>act</sub>      | Activation Time (Note 9)                                                       | 30  | -   | 100     | μS   |

| T <sub>deact</sub>    | Deactivation Time (Note 9)                                                     | 30  | -   | 250     | μS   |

| Temp <sub>SD</sub>    | Shutdown temperature (Note 9)                                                  | _   | 150 | _       | °C   |

<sup>9.</sup> Guaranteed by design and characterization.

#### **POWER SUPPLY**

The NCN8025 / NCN8025A smart card interface has two power supplies:  $V_{DD}$  and  $V_{DDP}$

$V_{DD}$  is common to the system controller and the interface. The applied  $V_{DD}$  range can go from 2.7 V up to 5.5 V. If  $V_{DD}$  goes below 2.30 V typical (UVLO<sub>VDD</sub>) a power–down sequence is automatically performed. In that case the interrupt ( $\overline{INT}$ ) pin is set Low.

A Low Drop–Out (LDO) and low noise regulator is used to provide the 1.8 V, 3 V or 5 V power supply voltage (CVCC) to the card.  $V_{DDP}$  is the LDO's input voltage. CVCC is the LDO output. The typical distributed reservoir output capacitor connected to CVCC is 100~nF+220~nF. The capacitor of 100~nF is connected as close as possible to the CVCC's pin and the 220 nF one as close as possible to the card connector C1 pin. Both feature very low ESR values (lower than  $50~m\Omega$ ). The decoupling capacitors on  $V_{DD}$  and  $V_{DDP}$  respectively 100~nF and  $10~\mu F+100~nF$  have also to be connected close to the respective IC pins.

The CVCC pin can source up to 70 mA at 1.8 V, 3 V and 5 V continuously over the  $V_{DDP}$  range (see corresponding specification table), the absolute maximum current being internally limited below 150 mA (Typical at 120 mA).

The card  $V_{CC}$  voltage (CVCC) can be programmed with the pins VSEL0 and VSEL1 and according to the below table:

**Table 1. CVCC PROGRAMMING**

| VSEL0 | VSEL1 | CVCC  |

|-------|-------|-------|

| 0     | 0     | 3.0 V |

| 0     | 1     | 5.0 V |

| 1     | 0     | 3.0 V |

| 1     | 1     | 1.8 V |

VSEL0 can be used to select the CVCC programming mode which can be  $5V/\overline{3V}$  (VSEL0 connected to Ground) or  $1.8V/\overline{3V}$  (VSEL0 connected to  $V_{DD}$ ). VSEL0 and

VSEL1 are usually programmed before activating the smart card interface that is when /CMDVCC is High.

There's no specific sequence for applying  $V_{DD}$  or  $V_{DDP}$ . They can be applied to the interface in any sequence. After powering the device  $\overline{INT}$  pin remains Low until a card is inserted.

#### SUPPLY VOLTAGE MONITORING

The supply voltage monitoring block includes the Power–On Reset (POR) circuitry and the under–voltage lockout (UVLO) detection ( $V_{DD}$  voltage dropout detection). PORADJ pin allows the user, according to the considered application, to adjust the  $V_{DD}$  UVLO threshold. If not used PORADJ pin is connected to Ground (recommended even if it may be left unconnected).

The input supply voltage is continuously monitored to prevent under voltage operation. At power up, the system initializes the internal logic during POR timing and no further signal can be provided or supported during this period.

The system is ready to operate when the input voltage has reached the minimum  $V_{DD}.$  Considering this, the NCN8025 / NCN8025A will detect an Under–Voltage situation when the input supply voltage will drop below 2.30 V typical. When  $V_{DD}$  goes down below the UVLO falling threshold a deactivation sequence is performed.

The device is inactive during power—on and power—off of the  $V_{DD}$  supply (8 ms reset pulse).

PORADJ pin is used to modify the UVLO threshold according to the below relationship considering an external resistor divider R1 / R2 (see block diagram Figure 1):

$$UVLO = \frac{R1 + R2}{R2} V_{POR}$$

(eq. 1)

If PORADJ is connected to Ground the  $V_{DD}$  UVLO threshold ( $V_{DD}$  falling) is typically 2.30 V. In some cases it can be interesting to adjust this threshold at a higher value and by the way increase the  $V_{DD}$  supply dropout detection

level which enables a deactivation sequence if the  $V_{DD}$  voltage is too low.

For example, there are microcontrollers for which the minimum supply voltage insuring a correct operating is higher than 2.6 V; increasing UVLO<sub>VDD</sub> (V<sub>DD</sub> falling) is consequently necessary. Considering for instance a resistor bridge with R1 = 56 k $\Omega$ , R2 = 42 k $\Omega$  and V<sub>POR</sub> = 1.27 V typical the V<sub>DD</sub> dropout detection level can be increased up to:

UVLO =

$$\frac{56k + 42k}{42k}$$

V<sub>POR-</sub> = 2.96 V (eq. 2)

#### **CLOCK DIVIDER:**

The input clock can be divided by 1/1, 1/2, 1/4, or 1/8, depending upon the specific application, prior to be applied to the smart card driver. These division ratios are programmed using pins CLKDIV1 and CLKDIV2 (see Table 2). The input clock is provided externally to pin CLKIN.

**Table 2. CLOCK FREQUENCY PROGRAMMING**

| CLKDIV1 | CLKDIV2 | F <sub>CCLK</sub> |

|---------|---------|-------------------|

| 0       | 0       | CLKIN / 8         |

| 0       | 1       | CKLKIN / 4        |

| 1       | 0       | CLKIN             |

| 1       | 1       | CLKIN / 2         |

The clock input stage (CLKIN) can handle a 27 MHz maximum frequency signal. Of course, the ratio must be defined by the user to cope with Smart Card considered in a given application

In order to avoid any duty cycle out of the 45% / 55% range specification, the divider is synchronized by the last flip flop, thus yielding a constant 50% duty cycle, whatever be the divider ratio 1/2, 1/4 or 1/8. On the other hand, the output signal Duty Cycle cannot be guaranteed 50% if the division ratio is 1 and if the input Duty Cycle signal is not within the 46% - 56% range at the CLKIN input.

When the signal applied to CLKIN is coming from the external controller, the clock will be applied to the card under the control of the microcontroller or similar device after the activation sequence has been completed.

#### DATA I/O, AUX1 and AUX2 LEVEL SHIFTERS

The three bidirectional level shifters I/O, AUX1 and AUX2 adapt the voltage difference that might exist between the micro-controller and the smart card. These three channels are identical. The first side of the bidirectional level shifter dropping Low (falling edge) becomes the driver side until the level shifter enters again in the idle state pulling High CI/O and I/Ouc.

Passive  $11 \, k\Omega$  pull-up resistors have been internally integrated on each terminal of the bidirectional channel. In addition with these pull-up resistors, an active pull-up circuit provides a fast charge of the stray capacitance.

The current to and from the card I/O lines is limited internally to 15 mA and the maximum guaranteed frequency on these lines is 1 MHz.

#### STANDBY MODE

After a Power—on reset, the circuit enters the standby mode. A minimum number of circuits are active while waiting for the microcontroller to start a session:

- All card contacts are inactive

- Pins I/Ouc, AUX1uc and AUX2uc are in the high–impedance state (11  $k\Omega$  pull–up resistor to  $V_{DD}$ )

- Card pins are inactive and pulled Low

- Supply Voltage monitoring is active

#### POWER-UP

In the standby mode the microcontroller can check the presence of a card using the signals  $\overline{INT}$  and  $\overline{CMDVCC}$  as shown in Table 3:

**Table 3. CARD PRESENCE STATE**

| INT  | CMDVCC | State            |

|------|--------|------------------|

| HIGH | HIGH   | Card present     |

| LOW  | HIGH   | Card not present |

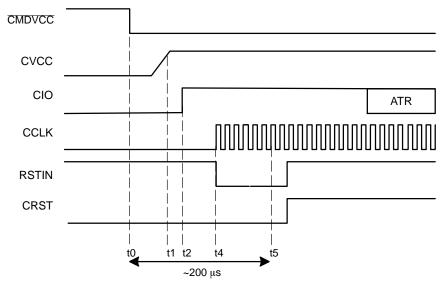

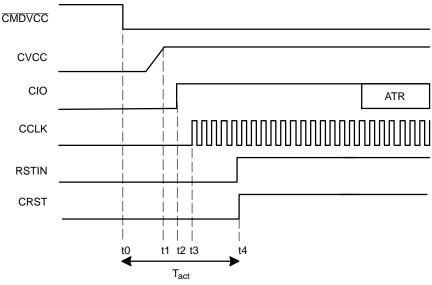

If a card is detected present (PRES or PRES active) the controller can start a card session by pulling CMDVCC Low. Card activation is run (t0, Figure 6). This Power–Up Sequence makes sure all the card related signals are LOW during the CVCC positive going slope. These lines are validated when CVCC is stable and above the minimum voltage specified. When the CVCC voltage reaches the programmed value (1.8 V, 3.0 V or 5.0 V), the circuit activates the card signals according to the following sequence (Figure 6):

- CVCC is powered-up at its nominal value (t1)

- I/O, AUX1 and AUX2 lines are activated (t2)

- Then Clock is activated and the clock signal is applied to the card (typically 500 ns after I/Os lines) (t3)

- Finally the Reset level shifter is enabled (typically 500 ns after clock channel) (t4)

The clock can also be applied to the card using a **RSTIN mode** allowing controlling the clock starting by setting RSTIN Low (Figure 5). Before running the activation sequence, that is before setting Low CMDVCC RSTIN is set High. The following sequence is applied:

- The Smart Card Interface is enable by setting CMDVCC LOW (RSTIN is High).

- Between t2 (Figure 5) and t5 = 200 μs, RSTIN is reset to LOW and CCLK will start precisely at this moment allowing a precise count of clock cycles before toggling CRST Low to High for ATR (Answer To Reset) request.

- CRST remains LOW until 200  $\mu$ s; after t5 = 200  $\mu$ s CRST is enabled and is the copy of RSTIN which has no more control on the clock.

If controlling the clock with RSTIN is not necessary (**Normal Mode**), then  $\overline{\text{CMDVCC}}$  can be set LOW with RSTIN LOW. In that case, CLK will start minimum 500 ns after the transition on I/O (Figure 6), and to obtain an ATR, CRST can be set High by RSTIN also about 500 ns after the clock channel activation ( $T_{\text{act}}$ ).

The internal activation sequence activates the different channels according to a specific hardware built-in

sequencing internally defined but at the end the actual activation sequencing is the responsibility of the application software and can be redefined by the micro-controller to comply with the different standards and the different ways the standards manage this activation (for example light differences exist between the EMV and the ISO7816 standards).

Figure 5. Activation Sequence – RSTIN Mode (RSTIN Starting High)

Figure 6. Activation Sequence - Normal Mode

#### **POWER-DOWN**

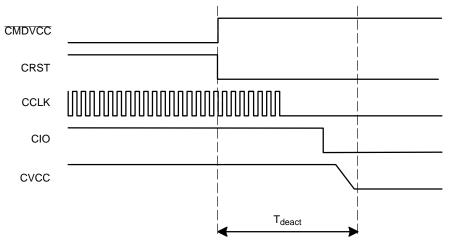

When the communication session is completed the NCN8025 / NCN8025A runs a deactivation sequence by setting High CMDVCC. The below power down sequence is executed:

- CRST is forced to Low

- CCLK is set Low 12 µs after CRST.

- CI/O, CAUX1 and CAUX2 are pulled Low

- Finally CVCC supply can be shut-off.

Figure 7. Deactivation Sequence

#### **FAULT DETECTION**

In order to protect both the interface and the external smart card, the NCN8025 / NCN8025A provides security features to prevent failures or damages as depicted here after.

- Card extraction detection

- V<sub>DD</sub> under voltage detection

- Short-circuit or overload on CVCC

- DC/DC operation: the internal circuit continuously senses the CVCC voltage (in the case of either over or under voltage situation).

- DC/DC operation: under-voltage detection on V<sub>DDP</sub>

- Overheating

- Card pin current limitation: in the case of a short circuit to ground. No feedback is provided to the external MPU.

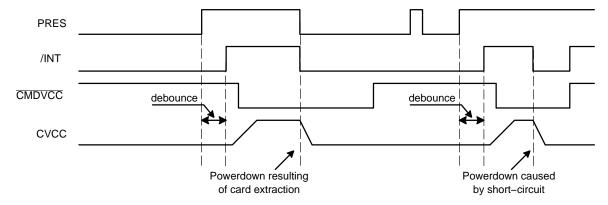

Figure 8. Fault Detection and Interrupt Management

#### **Interrupt Pin Management:**

A card session is opened by toggling  $\overline{\text{CMDVCC}}$  High to Low.

Before a card session,  $\overline{CMDVCC}$  is supposed to be in a High position.  $\overline{INT}$  is Low if no card is present in the card connector (Normally open or normally closed type).  $\overline{INT}$  is High if a card is present. If a card is inserted ( $\overline{INT}$  = High) and if  $V_{DD}$  drops below the UVLO threshold then  $\overline{INT}$  pin drops Low immediately. It switches High when  $V_{DD}$

increases again over the UVLO limit (including hysteresis), a card being still present.

During a card session,  $\overline{\text{CMDVCC}}$  is Low and  $\overline{\text{INT}}$  pin goes Low when a fault is detected. In that case a deactivation is immediately and automatically performed (see Figure 7). When the microcontroller resets  $\overline{\text{CMDVCC}}$  to High it can sense the  $\overline{\text{INT}}$  level again after having got completed the deactivation.

As illustrated by Figure 8 the device has a debounce timer of 8 ms typical duration. When a card is inserted, output  $\overline{\text{INT}}$  goes High only at the end of the debounce time. When the card is removed a deactivation sequence is automatically and immediately performed and  $\overline{\text{INT}}$  goes Low.

#### **ESD PROTECTION**

The NCN8025 / NCN8025A includes devices to protect the pins against the ESD spike voltages. To cope with the different ESD voltages developed across these pins, the built in structures have been designed to handle either 2 kV, when related to the micro controller side, or 8 kV when connected with the external contacts (HBM model). Practically, the CRST, CCLK, CI/O, CAUX1, CAUX2, PRES and  $\overline{\text{PRES}}$  pins can sustain 8 kV. The CVCC pin has the same ESD protection and can source up to 70 mA continuously, the absolute maximum current being internally limited with a max at 150 mA. The CVCC current limit depends on  $V_{DDP}$  and CVCC.

### **APPLICATION SCHEMATIC**

Figure 9. Application Schematic

## **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCN8025AMNTXG | QFN24<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCN8025MTTBG  | QFN16<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **PACKAGE DIMENSIONS**

#### QFN24, 4x4, 0.5P CASE 485L **ISSUE B**

←D2 →

<del>poolood</del>

24 | 19

**BOTTOM VIEW**

– 24X **L**

E2

24X b

0.10 C A B

0.05 C NOTE 3

DETAIL A

e/2

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION 5 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM THE TERMINAL TIP.

4. COOL ANABOTY A DEPLIES TO THE EXPOSED PAD.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |

|-----|-------------|------|

| DIM | MIN         | MAX  |

| Α   | 0.80        | 1.00 |

| A1  | 0.00        | 0.05 |

| A3  | 0.20 REF    |      |

| b   | 0.20        | 0.30 |

| D   | 4.00 BSC    |      |

| D2  | 2.70        | 2.90 |

| Е   | 4.00 BSC    |      |

| E2  | 2.70        | 2.90 |

| е   | 0.50 BSC    |      |

| L   | 0.30        | 0.50 |

| L1  | 0.05        | 0.15 |

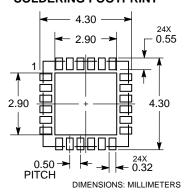

#### **RECOMMENDED SOLDERING FOOTPRINT**

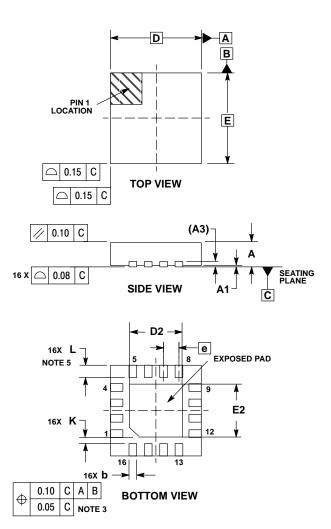

#### PACKAGE DIMENSIONS

QFN16, 3x3, 0.5 P CASE 488AK **ISSUE O**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS. DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN

0.25 AND 0.30 MM FROM TERMINAL.

COPLANARITY APPLIES TO THE EXPOSED

- PAD AS WELL AS THE TERMINALS.  $L_{\rm max}$  CONDITION CAN NOT VIOLATE 0.2 MM SPACING BETWEEN LEAD TIP AND FLAG.

|     | MILLIMETERS |      |

|-----|-------------|------|

| DIM | MIN         | MAX  |

| Α   | 0.70        | 0.80 |

| A1  | 0.00        | 0.05 |

| A3  | 0.20 REF    |      |

| b   | 0.18        | 0.30 |

| D   | 3.00 BSC    |      |

| D2  | 1.65        | 1.85 |

| Е   | 3.00 BSC    |      |

| E2  | 1.65        | 1.85 |

| е   | 0.50 BSC    |      |

| K   | 0.20        |      |

| L   | 0.30        | 0.50 |

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

Phone: 81–3–5817–1050

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

## Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А