# 1-Mbit (64K × 16) Automotive F-RAM Memory

#### **Features**

- 1-Mbit ferroelectric random access memory (F-RAM™) logically organized as 64K × 16

- □ Configurable as 128K × 8 using UB and LB

- ☐ High-endurance 100 trillion (10<sup>14</sup>) read/writes

- □ 151-year data retention (see the Data Retention and Endurance table)

- □ NoDelay™ writes

- □ Page-mode operation for 30-ns cycle time

- □ Advanced high-reliability ferroelectric process

- SRAM compatible

- □ Industry-standard 64K × 16 SRAM pinout

- □ 60-ns access time, 90-ns cycle time

- Superior to battery-backed SRAM modules

- □ No battery concerns

- □ Monolithic reliability

- ☐ True surface-mount solution, no rework steps

- Superior for moisture, shock, and vibration

- Low power consumption

- □ Active current 7 mA (typ)

- Standby current 120 μA (typ)

- Low-voltage operation: V<sub>DD</sub> = 2.0 V to 3.6 V

- Automotive-A temperature: -40 °C to +85 °C

- 44-pin thin small outline package (TSOP) Type II

- Restriction of hazardous substances (RoHS)-compliant

## **Functional Description**

The CY15B101N is a 64K × 16 nonvolatile memory that reads and writes similar to a standard SRAM. A ferroelectric random access memory or F-RAM is nonvolatile, which means that data is retained after power is removed. It provides data retention for over 151 years while eliminating the reliability concerns, functional disadvantages, and system design complexities of battery-backed SRAM (BBSRAM). Fast write-timing and high write-endurance make the F-RAM superior to other types of memory.

The CY15B101N operation is similar to that of other RAM devices, and, therefore, it can be used as a drop-in replacement for <u>a standard SRAM</u> in a system. Read cycles may be triggered by <u>CE</u> or simply <u>by changing</u> the address and write cycles may be triggered by <u>CE</u> or <u>WE</u>. The F-RAM memory is nonvolatile due to its unique ferroelectric memory process. These features make the CY15B101N ideal for nonvolatile memory applications requiring frequent or rapid writes.

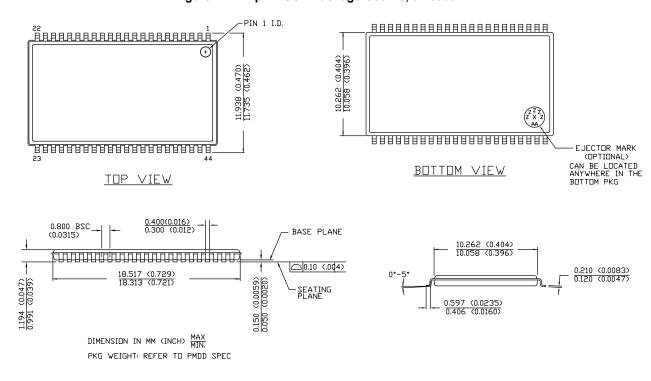

The device is available in a 400-mil, 44-pin TSOP-II surface-mount package. Device specifications are guaranteed over the Automotive-A temperature range -40 °C to +85 °C.

For a complete list of related resources, click here.

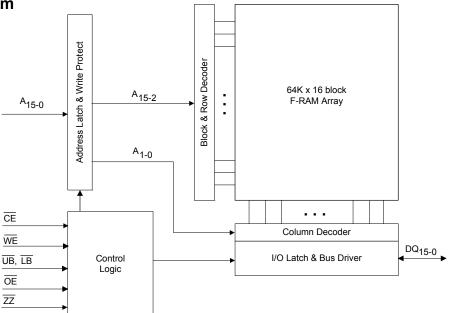

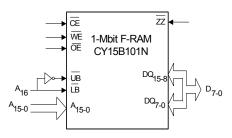

## Logic Block Diagram

## **Contents**

| Pinout                        | 3 |

|-------------------------------|---|

| Pin Definitions               | 3 |

| Device Operation              | 4 |

| Memory Operation              | 4 |

| Read Operation                | 4 |

| Write Operation               | 4 |

| Page Mode Operation           | 4 |

| Precharge Operation           | 4 |

| Sleep Mode                    | 5 |

| SRAM Drop-In Replacement      | 5 |

| Endurance                     | 5 |

| Maximum Ratings               |   |

| Operating Range               | 6 |

| DC Electrical Characteristics | 6 |

| Data Retention and Endurance  | 7 |

| Capacitance                   | 7 |

| Thermal Resistance            | 7 |

| AC Test Conditions            | 7 |

| AC Switching Characteristics            | 8  |

|-----------------------------------------|----|

| SRAM Read Cycle                         |    |

| SRAM Write Cycle                        |    |

| Power Cycle and Sleep Mode Timing       |    |

| Functional Truth Table                  |    |

| Byte Select Truth Table                 | 14 |

| Ordering Information                    | 15 |

| Ordering Code Definitions               | 15 |

| Package Diagram                         | 16 |

| Acronyms                                | 17 |

| Document Conventions                    | 17 |

| Units of Measure                        | 17 |

| Document History Page                   | 18 |

| Sales, Solutions, and Legal Information | 19 |

| Worldwide Sales and Design Support      | 19 |

| Products                                | 19 |

| PSoC® Solutions                         | 19 |

| Cypress Developer Community             | 19 |

| Technical Support                       | 10 |

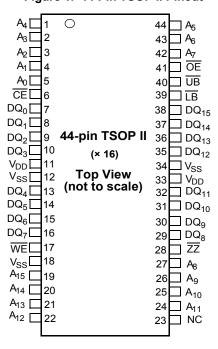

## **Pinout**

Figure 1. 44-Pin TSOP II Pinout

## **Pin Definitions**

| Pin Name                          | I/O Type     | Description                                                                                                                                                                                                                                                                                                           |

|-----------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>15</sub>   | Input        | <b>Address inputs</b> : The 16 address lines select one of 64K words in the F-RAM array. The lowest two address lines $A_1$ – $A_0$ may be used for page mode read and write operations.                                                                                                                              |

| DQ <sub>0</sub> -DQ <sub>15</sub> | Input/Output | Data I/O Lines: 16-bit bidirectional data bus for accessing the F-RAM array.                                                                                                                                                                                                                                          |

| WE                                | Input        | <b>Write Enable</b> : A write cycle begins when $\overline{WE}$ is asserted. The rising edge causes the CY15B101N to write the data on the DQ bus to the F-RAM array. The falling edge of $\overline{WE}$ latches a new column address for page mode write cycles.                                                    |

| CE                                | Input        | <b>Chip Enable</b> : The device is selected and a new memory access begins on the falling edge of $\overline{\text{CE}}$ . The entire address is latched internally at this point. Subsequent changes to the $A_1$ – $A_0$ address inputs allow page mode operation.                                                  |

| ŌĒ                                | Input        | Output Enable: When $\overline{\text{OE}}$ is LOW, the CY15B101N drives the data bus when the valid read data is available. Deasserting $\overline{\text{OE}}$ HIGH tristates the DQ pins.                                                                                                                            |

| ŪB                                | Input        | <b>Upper Byte Select</b> : Enables $DQ_{15}$ – $DQ_8$ pins during reads and writes. These pins are HI-Z if $\overline{\text{UB}}$ is HIGH. If the user does not perform byte writes and the device is not configured as a 128K × 8, the $\overline{\text{UB}}$ and $\overline{\text{LB}}$ pins may be tied to ground. |

| LB                                | Input        | <b>Lower Byte Select</b> : Enables $DQ_7$ – $DQ_0$ pins during reads and writes. These pins are HI-Z if $\overline{LB}$ is HIGH. If the user does not perform byte writes and the device is not configured as a 128 K × 8, the $\overline{UB}$ and $\overline{LB}$ pins may be tied to ground.                        |

| ZZ                                | Input        | Sleep: When $\overline{ZZ}$ is LOW, the device enters a low-power sleep mode for the lowest supply current condition. $\overline{ZZ}$ must be HIGH for a normal read/write operation. This pin must be tied to $V_{DD}$ if not used.                                                                                  |

| V <sub>SS</sub>                   | Ground       | Ground for the device. Must be connected to the ground of the system.                                                                                                                                                                                                                                                 |

| V <sub>DD</sub>                   | Power supply | Power supply input to the device.                                                                                                                                                                                                                                                                                     |

| NC                                | No connect   | No connect. This pin is not connected to the die.                                                                                                                                                                                                                                                                     |

## **Device Operation**

The CY15B101N is a word-wide F-RAM memory logically organized as  $65,536 \times 16$  and accessed using an industry-standard parallel interface. All data written to the part is immediately nonvolatile with no delay. The device offers page-mode operation, which provides high-speed access to addresses within a page (row). Access to a different page requires that either  $\overline{\text{CE}}$  transitions LOW or the upper address  $(A_{15}-A_2)$  changes. See the Functional Truth Table on page 14 for a complete description of read and write modes.

## **Memory Operation**

Users access 65,536 memory locations, each with 16 data bits through a parallel interface. The F-RAM array is organized as eight blocks, each having 2048 rows. Each row has four column locations, which allow fast access in page-mode operation. When an initial address is latched by the falling edge of  $\overline{CE}$ , subsequent column locations may be accessed without the need to toggle  $\overline{CE}$ . When  $\overline{CE}$  is deasserted (HIGH), a precharge operation begins. Writes occur immediately at the end of the access with no delay. The  $\overline{WE}$  pin must be toggled for each write operation. The write data is stored in the nonvolatile memory array immediately, which is a feature unique to F-RAM called "NoDelay" writes.

#### Read Operation

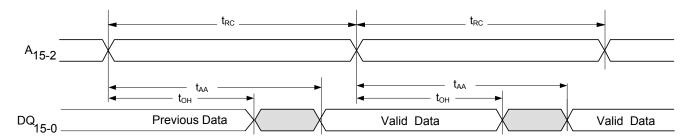

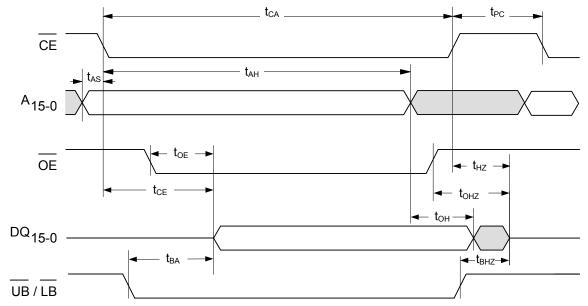

A read operation begins on the falling edge of  $\overline{\text{CE}}$ . The falling edge of  $\overline{\text{CE}}$  causes the address to be latched and starts a memory read cycle if  $\overline{\text{WE}}$  is HIGH. Data becomes available on the bus after the access time is met. When the address is latched and the access completed, a new access to a random location (different row) may begin while  $\overline{\text{CE}}$  is still LOW. The minimum cycle time for random addresses is  $t_{RC}$ . Note that unlike SRAMs, the CY15B101N's  $\overline{\text{CE}}$ -initiated access time is faster than the address access time.

The CY15B101N will drive the data bus when  $\overline{\text{OE}}$  and at least one of the byte enables  $(\overline{\text{UB}}, \overline{\text{LB}})$  is asserted LOW. The upper data byte is driven when  $\overline{\text{UB}}$  is LOW, and the lower data byte is driven when  $\overline{\text{LB}}$  is LOW. If  $\overline{\text{OE}}$  is asserted after the memory access time is met, the data bus will be driven with valid data. If  $\overline{\text{OE}}$  is asserted before completing the memory access, the data bus will not be driven until valid data is available. This feature minimizes the supply current in the system by eliminating transients caused by invalid data being driven to the bus. When  $\overline{\text{OE}}$  is deasserted HIGH, the data bus will remain in a HI-Z state.

#### Write Operation

In the CY15B101N, writes occur in the same interval as reads. The CY15B101N supports both  $\overline{\text{CE-}}$  and  $\overline{\text{WE-}}$ controlled write cycles. In both cases, the address  $A_{15}$ – $A_2$  is latched on the falling edge of  $\overline{\text{CE}}$ .

In a  $\overline{\text{CE}}$ -controlled write, the  $\overline{\text{WE}}$  signal is asserted before beginning the memory cycle. That is,  $\overline{\text{WE}}$  is LOW when  $\overline{\text{CE}}$  falls. In this case, the device begins the memory cycle as a write. The  $\overline{\text{CY}}$ 15B101N will not drive the data bus regardless of the state of  $\overline{\text{OE}}$  as long as  $\overline{\text{WE}}$  is LOW. Input data must be valid when  $\overline{\text{CE}}$  is deasserted HIGH. In a  $\overline{\text{WE}}$ -controlled write, the memory cycle begins on the falling edge of  $\overline{\text{CE}}$ . The  $\overline{\text{WE}}$  signal falls some time later. Therefore, the memory cycle begins as a read. The data bus will be driven if  $\overline{\text{OE}}$  is LOW; however, it will be HI-Z when  $\overline{\text{WE}}$  is asserted LOW. The  $\overline{\text{CE}}$ - and  $\overline{\text{WE}}$ -controlled write timing cases are shown on the page 10 and page 11.

Write access to the array begins on the falling edge of  $\overline{\text{WE}}$  after the memory cycle is initiated. The write access terminates on the rising edge of  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$ , whichever comes first. A valid write operation requires the user to meet the access time specification before deasserting  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$ . The data setup time indicates the interval during which data cannot change before the end of the write access (rising edge of  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$ ).

Unlike other nonvolatile memory technologies, there is no write delay with F-RAM. Because the read and write access times of the underlying memory are the same, the user experiences no delay through the bus. The entire memory operation occurs in a single bus cycle. Data polling, a technique used with EEPROMs to determine if a write is complete, is unnecessary.

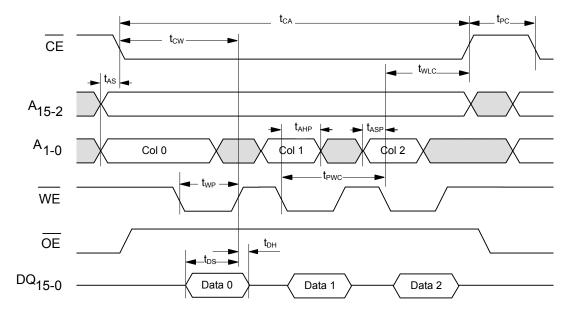

#### **Page Mode Operation**

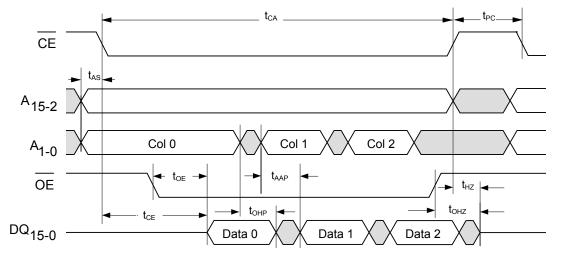

The F-RAM array is organized as eight blocks, each having 2048 rows. Each row has four column-address locations. Address inputs  $A_1\!-\!A_0$  define the column address to be accessed. An access can start on any column address, and other column locations may be accessed without the need to toggle the  $\overline{CE}$  pin. For fast access reads, after the first data byte is driven to the bus, the column address inputs  $A_1\!-\!A_0$  may be changed to a new value. A new data byte is then driven to the DQ pins no later than  $t_{AAP}$  which is less than half the initial read access time. For fast access writes, the first write pulse defines the first write access. While  $\overline{CE}$  is LOW, a subsequent write pulse along with a new column address provides a page mode write access.

### **Precharge Operation**

The precharge operation is an internal condition in which the memory state is prepared  $\underline{\text{for}}$  a new access. Precharge is user-initiated by driving the  $\overline{\text{CE}}$  signal HIGH. It must remain HIGH for at least the minimum precharge time,  $t_{\text{PC}}$ .

Precharge is also activated by changing the upper addresses,  $A_{15}$ – $A_2$ . The current row is first closed before accessing the new row. The device automatically detects an upper order address change, which starts a precharge operation. The new address is latched and the new read data is valid within the  $t_{AA}$  address access time; see Figure 5 on page 10. A similar sequence occurs for write cycles; see Figure 10 on page 11. The rate at which random addresses can be issued is  $t_{RC}$  and  $t_{WC}$ , respectively.

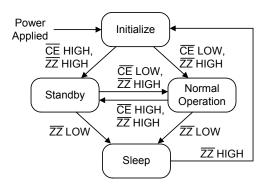

#### Sleep Mode

The device incorporates a sleep mode of operation, which allows the user to achieve the lowest-power-supply-current condition. It enters a low-power sleep mode by asserting the  $\overline{ZZ}$  pin LOW. Read and write operations must complete before the  $\overline{ZZ}$  pin going LOW. When  $\overline{ZZ}$  is LOW, all pins are ignored except the  $\overline{ZZ}$  pin. When  $\overline{ZZ}$  is deasserted HIGH, there is some time delay ( $t_{ZZFX}$ ) before the user can access the device.

If sleep mode is not used, the  $\overline{ZZ}$  pin must be tied to  $V_{DD}$ .

Figure 2. Sleep/Standby State Diagram

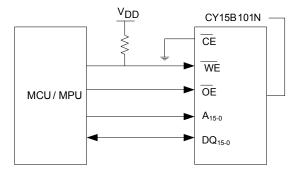

#### **SRAM Drop-In Replacement**

The CY15B101N is designed to be a drop-in replacement for standard asynchronous SRAMs. The device does not require CE to toggle for each new address.  $\overline{\mathsf{CE}}$  may remain LOW indefinitely. While CE is LOW, the device automatically detects address changes and a new access begins. This functionality allows CE to be grounded, similar to an SRAM. It also allows page mode operation at speeds up to 33 MHz. Note that if  $\overline{\text{CE}}$  is tied to ground, the user must be sure  $\overline{\text{WE}}$  is not LOW at power-up or power-down events. If  $\overline{\sf CE}$  and  $\overline{\sf WE}$  are both LOW during power cycles, data will be corrupted. Figure 3 shows a pull-up resistor on WE, which will keep the pin HIGH during power cycles, assuming the MCU/MPU pin tristates during the reset condition. The pull-up resistor value should be chosen to ensure the WE pin tracks V<sub>DD</sub> to a high enough value, so that the current drawn when  $\overline{\text{WE}}$  is LOW is not an issue. A 10-k $\Omega$  resistor draws 330  $\mu\text{A}$ when WE is LOW and  $V_{DD} = 3.3 \text{ V}$ .

Figure 3. Use of Pull-up Resistor on WE

$\overline{\text{CE}}$  applications that require the lowest power consumption, the  $\overline{\text{CE}}$  signal should be active (LOW) only during memory accesses. The CY15B101N draws supply current while  $\overline{\text{CE}}$  is LOW, even if addresses and control signals are static. While  $\overline{\text{CE}}$  is HIGH, the device draws no more than the maximum standby current,  $I_{SB}$ . The  $\overline{\text{UB}}$  and  $\overline{\text{LB}}$  byte select pins are active for both read and write cycles. They may be used to allow the device to be wired as a 128K × 8 memory. The upper and lower data bytes can be tied together and controlled with the byte selects. Individual byte enables or the next higher address line  $A_{16}$  may be available from the system processor.

Figure 4. CY15B101N Wired as 128 K x 8

#### **Endurance**

The CY15B101N is capable of being accessed at least  $10^{14}$  times – reads or writes. An F-RAM memory operates with a read and restore mechanism. Therefore, an endurance cycle is applied on a row basis. The F-RAM architecture is based on an array of rows and columns. Rows are defined by  $A_{15-2}$  and column addresses by  $A_{1-0}$ . The array is organized as 16K rows of four words each. The entire row is internally accessed once whether a single 16-bit word or all four words are read or written. Each word in the row is counted only once in an endurance calculation.

The user may choose to write CPU instructions and run them from a certain address space. Table 1 shows endurance calculations for a 256-byte repeating loop, which includes a starting address, three-page mode accesses, and a  $\overline{\text{CE}}$  precharge. The number of bus clock cycles needed to complete a four-word transaction is 4 + 1 at lower bus speeds, but 5 + 2 at 33 MHz due to initial read latency and an extra clock cycle to satisfy the device's precharge timing constraint  $t_{\text{PC}}.$  The entire loop causes each byte to experience only one endurance cycle. The F-RAM read and write endurance is virtually unlimited even at a 33-MHz system bus clock rate.

Table 1. Time to Reach 100 Trillion Cycles for Repeating 256-byte Loop

| Bus<br>Freq<br>(MHz) | Bus<br>Cycle<br>Time<br>(ns) | 256-byte<br>Transaction<br>Time (μs) | Endurance<br>Cycles/sec | Endurance<br>Cycles/year | Years to<br>Reach<br>10 <sup>14</sup><br>Cycles |

|----------------------|------------------------------|--------------------------------------|-------------------------|--------------------------|-------------------------------------------------|

| 33                   | 30                           | 10.56                                | 94,690                  | 2.98 x 10 <sup>12</sup>  | 33.5                                            |

| 25                   | 40                           | 12.8                                 | 78,125                  | 2.46 x 10 <sup>12</sup>  | 40.6                                            |

| 10                   | 100                          | 28.8                                 | 34,720                  | 1.09 x 10 <sup>12</sup>  | 91.7                                            |

| 5                    | 200                          | 57.6                                 | 17,360                  | 5.47 x 10 <sup>11</sup>  | 182.8                                           |

## **Maximum Ratings**

## **Operating Range**

| Range Ambient Temperature (T <sub>A</sub> ) |                  | V <sub>DD</sub> |  |

|---------------------------------------------|------------------|-----------------|--|

| Automotive-A                                | –40 °C to +85 °C | 2.0 V to 3.6 V  |  |

## **DC Electrical Characteristics**

Over the Operating Range

| Parameter        | Description                    | Test Conditions                                                                                                                           |                                                  | Min                   | Typ [1] | Max                   | Unit |

|------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------|---------|-----------------------|------|

| $V_{DD}$         | Power supply voltage           |                                                                                                                                           |                                                  | 2.0                   | 3.3     | 3.6                   | V    |

| I <sub>DD</sub>  | V <sub>DD</sub> supply current | $V_{DD}$ = 3.6 V, $\overline{\text{CE}}$ cycling at min. cy<br>inputs toggling at CMOS levels<br>(0.2 V or $V_{DD}$ – 0.2 V), all DQ pins | _                                                | 7                     | 12      | mA                    |      |

| I <sub>SB</sub>  | Standby current                | $V_{DD}$ = 3.6 V, $\overline{CE}$ at $V_{DD}$ ,                                                                                           | T <sub>A</sub> = 25 °C                           | -                     | 120     | 150                   | μA   |

|                  |                                | All other pins are static and at CMOS levels (0.2 V or V <sub>DD</sub> – 0.2 V), $\overline{ZZ}$ is HIGH                                  | T <sub>A</sub> = 85 °C                           | _                     | _       | 250                   | μA   |

| $I_{ZZ}$         | Sleep mode current             | All other inpute \/ or \/                                                                                                                 | T <sub>A</sub> = 25 °C                           | -                     | 3       | 5                     | μΑ   |

|                  |                                |                                                                                                                                           | T <sub>A</sub> = 85 °C                           | -                     | _       | 8                     | μA   |

| I <sub>LI</sub>  | Input leakage current          | $V_{IN}$ between $V_{DD}$ and $V_{SS}$                                                                                                    |                                                  | -                     | -       | <u>+</u> 1            | μA   |

| $I_{LO}$         | Output leakage current         | $V_{OUT}$ between $V_{DD}$ and $V_{SS}$                                                                                                   |                                                  | -                     | -       | <u>+</u> 1            | μA   |

| V <sub>IH1</sub> | Input HIGH voltage             | V <sub>DD</sub> = 2.7 V to 3.6 V                                                                                                          |                                                  | 2.2                   | _       | V <sub>DD</sub> + 0.3 | V    |

| $V_{IH2}$        | Input HIGH voltage             | V <sub>DD</sub> = 2.0 V to 2.7 V                                                                                                          |                                                  | 0.7 × V <sub>DD</sub> | -       | -                     | V    |

| V <sub>IL1</sub> | Input LOW voltage              | V <sub>DD</sub> = 2.7 V to 3.6 V                                                                                                          |                                                  | - 0.3                 | _       | 0.8                   | V    |

| V <sub>IL2</sub> | Input LOW voltage              | V <sub>DD</sub> = 2.0 V to 2.7 V                                                                                                          |                                                  | - 0.3                 | -       | 0.3 × V <sub>DD</sub> | V    |

| V <sub>OH1</sub> | Output HIGH voltage            | $I_{OH} = -1 \text{ mA}, V_{DD} > 2.7 \text{ V}$                                                                                          | I <sub>OH</sub> = -1 mA, V <sub>DD</sub> > 2.7 V |                       | _       | -                     | V    |

| V <sub>OH2</sub> | Output HIGH voltage            | I <sub>OH</sub> = -100 μA                                                                                                                 |                                                  | V <sub>DD</sub> – 0.2 | _       | _                     | V    |

| V <sub>OL1</sub> | Output LOW voltage             | <sub>OL</sub> = 2 mA, V <sub>DD</sub> > 2.7 V                                                                                             |                                                  | -                     | _       | 0.4                   | V    |

| V <sub>OL2</sub> | Output LOW voltage             | I <sub>OL</sub> = 150 μA                                                                                                                  |                                                  | -                     | _       | 0.2                   | V    |

#### Note

Document Number: 001-96058 Rev. \*E

<sup>1.</sup> Typical values are at 25 °C,  $V_{DD}$  =  $V_{DD}$  (typ). Not 100% tested.

## **Data Retention and Endurance**

| Parameter       | Description    | Test condition             | Min              | Max | Unit   |

|-----------------|----------------|----------------------------|------------------|-----|--------|

| T <sub>DR</sub> | Data retention | T <sub>A</sub> = 85 °C     | 10               | _   | Years  |

|                 |                | T <sub>A</sub> = 75 °C     | 38               | _   |        |

|                 |                | T <sub>A</sub> = 65 °C     | 151              | _   |        |

| $NV_C$          | Endurance      | Over operating temperature | 10 <sup>14</sup> | -   | Cycles |

# Capacitance

| Parameter        | Description                   | Test Conditions                                                       | Max | Unit |

|------------------|-------------------------------|-----------------------------------------------------------------------|-----|------|

| C <sub>I/O</sub> | Input/Output capacitance (DQ) | $T_A = 25 {}^{\circ}\text{C}, f = 1 \text{MHz}, V_{DD} = V_{DD(Typ)}$ | 8   | pF   |

| C <sub>IN</sub>  | Input capacitance             |                                                                       | 6   | pF   |

| $C_{ZZ}$         | Input capacitance of ZZ pin   |                                                                       | 8   | pF   |

## **Thermal Resistance**

| Parameter | Description                           | Test Conditions                                                                                 | 44-pin TSOP II | Unit |

|-----------|---------------------------------------|-------------------------------------------------------------------------------------------------|----------------|------|

| U/A       | ,                                     | Test conditions follow standard test methods and procedures for measuring thermal impedance, in |                | °C/W |

| - 30      | Thermal resistance (junction to case) | accordance with EIA/JESD51.                                                                     | 25             | °C/W |

## **AC Test Conditions**

| Input pulse levels                       | 0 V to 3 V    |

|------------------------------------------|---------------|

| Input rise and fall times (10%–90%)      | <u>≤</u> 3 ns |

| Input and output timing reference levels | 1.5 V         |

| Output load capacitance                  | 30 pF         |

Document Number: 001-96058 Rev. \*E

## **AC Switching Characteristics**

Over the Operating Range

| Param                   | neters <sup>[2]</sup> |                                              | V <sub>DD</sub> = 2.0 | V to 2.7 V | V <sub>DD</sub> = 2.7 V to 3.6 V |     |      |

|-------------------------|-----------------------|----------------------------------------------|-----------------------|------------|----------------------------------|-----|------|

| Cypress<br>Parameter    | Alt Parameter         | Description                                  | Min                   | Max        | Min                              | Max | Unit |

| SRAM Read C             | ycle                  |                                              |                       |            |                                  |     |      |

| t <sub>CE</sub>         | t <sub>ACE</sub>      | Chip enable access time                      | _                     | 70         | -                                | 60  | ns   |

| t <sub>RC</sub>         | _                     | Read cycle time                              | 105                   | -          | 90                               | _   | ns   |

| t <sub>AA</sub>         | _                     | Address access time, A <sub>15-2</sub>       | _                     | 105        | _                                | 90  | ns   |

| t <sub>OH</sub>         | t <sub>OHA</sub>      | Output hold time, A <sub>15-2</sub>          | 20                    | -          | 20                               | _   | ns   |

| t <sub>AAP</sub>        | _                     | Page mode access time, A <sub>1-0</sub>      | _                     | 40         | _                                | 30  | ns   |

| t <sub>OHP</sub>        | _                     | Page mode output hold time, A <sub>1-0</sub> | 3                     | -          | 3                                | _   | ns   |

| t <sub>CA</sub>         | _                     | Chip enable active time                      | 70                    | -          | 60                               | _   | ns   |

| t <sub>PC</sub>         | _                     | Precharge time                               | 35                    | -          | 30                               | -   | ns   |

| t <sub>BA</sub>         | t <sub>BW</sub>       | UB, LB access time                           | _                     | 25         | _                                | 15  | ns   |

| t <sub>AS</sub>         | t <sub>SA</sub>       | Address setup time (to CE LOW)               | 0                     | -          | 0                                | -   | ns   |

| t <sub>AH</sub>         | t <sub>HA</sub>       | Address hold time (CE Controlled)            | 70                    | -          | 60                               | -   | ns   |

| t <sub>OE</sub>         | t <sub>DOE</sub>      | Output enable access time                    | _                     | 25         | _                                | 15  | ns   |

| t <sub>HZ</sub> [3, 4]  | t <sub>HZCE</sub>     | Chip enable to output HI-Z                   | _                     | 15         | _                                | 10  | ns   |

| t <sub>OHZ</sub> [3, 4] | t <sub>HZOE</sub>     | Output enable HIGH to output HI-Z            | _                     | 15         | _                                | 10  | ns   |

| t <sub>BHZ</sub> [3, 4] | t <sub>HZBE</sub>     | UB, LB HIGH to output HI-Z                   | _                     | 15         | _                                | 10  | ns   |

<sup>2.</sup> Test conditions assume a signal transition time of 3 ns or less, timing reference levels of 0.5 × V<sub>DD</sub>, input pulse levels of 0 to 3 V, output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and 30-pF load capacitance shown in AC Test Conditions on page 7.

<sup>3.</sup> t<sub>HZ</sub>, t<sub>OHZ</sub> and t<sub>BHZ</sub> are specified with a load capacitance of 5 pF. Transition is measured when the outputs enter a high impedance state.

<sup>4.</sup> This parameter is characterized but not 100% tested.

## **AC Switching Characteristics** (continued)

Over the Operating Range

| Cypress Parameter Alt Parameter   |                   |                                                        | V <sub>DD</sub> = 2.0 | V <sub>DD</sub> = 2.0 V to 2.7 V |     | V <sub>DD</sub> = 2.7 V to 3.6 V |    |

|-----------------------------------|-------------------|--------------------------------------------------------|-----------------------|----------------------------------|-----|----------------------------------|----|

|                                   |                   | Description                                            |                       | Max                              | Min | Min Max                          |    |

| SRAM Write C                      | ycle              |                                                        |                       | •                                |     | •                                | •  |

| t <sub>WC</sub>                   | t <sub>WC</sub>   | Write cycle time                                       | 105                   | _                                | 90  | _                                | ns |

| t <sub>CA</sub>                   | _                 | Chip enable active time                                | 70                    | -                                | 60  | -                                | ns |

| t <sub>CW</sub>                   | t <sub>SCE</sub>  | Chip enable to write enable HIGH                       | 70                    | _                                | 60  | -                                | ns |

| t <sub>PC</sub>                   | _                 | Precharge time                                         | 35                    | _                                | 30  | -                                | ns |

| t <sub>PWC</sub>                  | _                 | Page mode write enable cycle time                      | 40                    | -                                | 30  | -                                | ns |

| t <sub>WP</sub>                   | t <sub>PWE</sub>  | Write enable pulse width                               | 22                    | -                                | 18  | _                                | ns |

| t <sub>WP2</sub>                  | t <sub>BW</sub>   | UB, LB pulse width                                     | 22                    | _                                | 18  | _                                | ns |

| t <sub>WP3</sub>                  | t <sub>PWE</sub>  | WE LOW to UB, LB HIGH                                  | 22                    | -                                | 18  | _                                | ns |

| t <sub>AS</sub>                   | t <sub>SA</sub>   | Address setup time (to CE LOW)                         | 0                     | _                                | 0   | _                                | ns |

| t <sub>AH</sub>                   | t <sub>HA</sub>   | Address hold time (CE Controlled)                      | 70                    | _                                | 60  | _                                | ns |

| t <sub>ASP</sub>                  | _                 | Page mode address setup time (to WE LOW)               | 8                     | _                                | 5   | -                                | ns |

| t <sub>AHP</sub>                  | _                 | Page mode address hold time (to WE LOW)                | 20                    | _                                | 15  | -                                | ns |

| t <sub>WLC</sub>                  | t <sub>PWE</sub>  | Write enable LOW to chip disabled                      | 30                    | _                                | 25  | _                                | ns |

| t <sub>BLC</sub>                  | t <sub>BW</sub>   | UB, LB LOW to chip disabled                            | 30                    | _                                | 25  | _                                | ns |

| t <sub>WLA</sub>                  | -                 | Write enable LOW to address change, A <sub>15-2</sub>  | 30                    | _                                | 25  | -                                | ns |

| t <sub>AWH</sub>                  | _                 | Address change to write enable HIGH, A <sub>15-2</sub> | 105                   | _                                | 90  | -                                | ns |

| t <sub>DS</sub>                   | t <sub>SD</sub>   | Data input setup time                                  | 20                    | _                                | 15  | _                                | ns |

| t <sub>DH</sub>                   | t <sub>HD</sub>   | Data input hold time                                   | 0                     | _                                | 0   | _                                | ns |

| t <sub>WZ</sub> <sup>[5, 6]</sup> | t <sub>HZWE</sub> | Write enable LOW to output HI-Z                        | _                     | 10                               | _   | 10                               | ns |

| t <sub>WX</sub> <sup>[6]</sup>    | _                 | Write enable HIGH to output driven                     | 8                     | _                                | 5   | -                                | ns |

| t <sub>BDS</sub>                  | _                 | Byte disable setup time (to WE LOW)                    | 8                     | _                                | 5   | _                                | ns |

| t <sub>BDH</sub>                  | _                 | Byte disable hold time (to WE HIGH)                    | 8                     | _                                | 5   | _                                | ns |

## Notes

<sup>5.</sup> t<sub>WZ</sub> is specified with a load capacitance of 5 pF. Transition is measured when the outputs enter a high-impedance state.

6. This parameter is characterized but not 100% tested.

Figure 5. Read Cycle Timing 1 (CE LOW, OE LOW)

Figure 6. Read Cycle Timing 2 (CE Controlled)

Figure 7. Page Mode Read Cycle Timing  $^{[7]}$

Note

7. Although sequential column addressing is shown, it is not required.

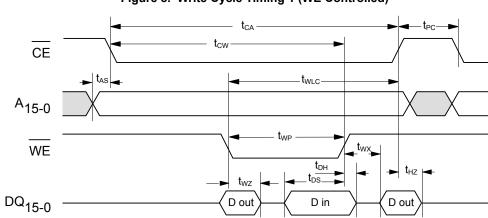

Figure 8. Write Cycle Timing 1 (WE Controlled) [8]

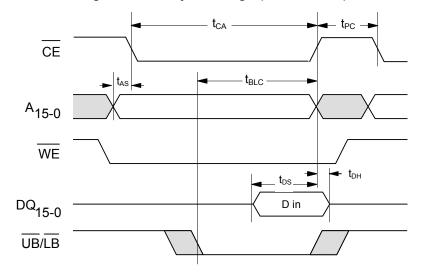

Figure 9. Write Cycle Timing 2 (CE Controlled)

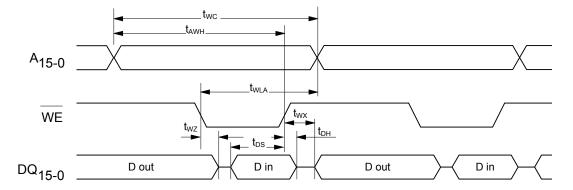

Figure 10. Write Cycle Timing 3 ( $\overline{\text{CE}}$  LOW) [8]

Note  $\underline{\phantom{a}}$  8.  $\overline{\rm OE}$  (not shown) is LOW only to show the effect of  $\overline{\rm WE}$  on DQ pins.

A<sub>15-0</sub> WE  $t_{BDS}$ UB/LB **►** t<sub>DH</sub> DQ<sub>15-0</sub> D in D in

Figure 11. Write Cycle Timing 4 (CE LOW) [9]

Figure 12. Page Mode Write Cycle Timing

Note

9. UB and LB to show byte enable and byte masking cases.

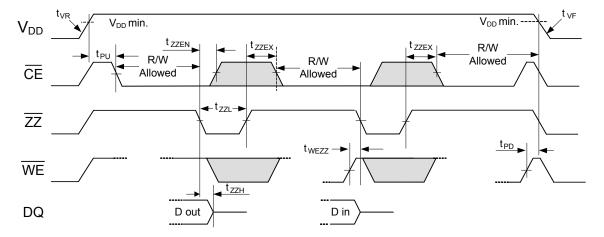

## **Power Cycle and Sleep Mode Timing**

Over the Operating Range

| Parameter                       | Description                                                           | Min | Max | Unit |

|---------------------------------|-----------------------------------------------------------------------|-----|-----|------|

| t <sub>PU</sub>                 | Power-up (after V <sub>DD</sub> min. is reached) to first access time | 1   | -   | ms   |

| t <sub>PD</sub>                 | Last write (WE HIGH) to power down time                               | 0   | _   | ms   |

| t <sub>VR</sub> <sup>[10]</sup> | V <sub>DD</sub> power-up ramp rate                                    | 50  | -   | μs/V |

| t <sub>VF</sub> <sup>[10]</sup> | V <sub>DD</sub> power-down ramp rate                                  | 100 | _   | μs/V |

| t <sub>ZZH</sub>                | ZZ active to DQ HI-Z time                                             | _   | 20  | ns   |

| t <sub>WEZZ</sub>               | Last write to sleep mode entry time                                   | 0   | -   | μs   |

| t <sub>ZZL</sub>                | ZZ active LOW time                                                    | 1   | _   | μs   |

| t <sub>ZZEN</sub>               | Sleep mode entry time (ZZ LOW to CE don't care)                       | _   | 0   | μs   |

| t <sub>ZZEX</sub>               | Sleep mode exit time (ZZ HIGH to 1st access after wakeup)             | _   | 450 | μs   |

Figure 13. Power Cycle and Sleep Mode Timing

<sup>10.</sup> Slope measured at any point on the  $\ensuremath{V_{DD}}$  waveform.

## **Functional Truth Table**

| CE           | WE           | A <sub>15-2</sub> | A <sub>1-0</sub> | ZZ | Operation [11, 12]                  |

|--------------|--------------|-------------------|------------------|----|-------------------------------------|

| Х            | X            | X                 | Χ                | L  | Sleep Mode                          |

| Н            | Х            | Х                 | Х                | Н  | Standby/Idle                        |

| $\downarrow$ | Н            | V                 | V                | Н  | Read                                |

| L            | Н            | V                 | V                | Н  |                                     |

| L            | Н            | No Change         | Change           | Ι  | Page Mode Read                      |

| L            | Н            | Change            | V                | Н  | Random Read                         |

| $\downarrow$ | L            | V                 | V                | Н  | CE-Controlled Write <sup>[12]</sup> |

| L            | L            | V                 | V                | Н  |                                     |

| L            | $\downarrow$ | V                 | V                | Н  | WE-Controlled Write [12, 13]        |

| L            | $\downarrow$ | No Change         | V                | Н  | Page Mode Write <sup>[14]</sup>     |

| 1            | Χ            | Х                 | Х                | Н  | Starts precharge                    |

| Ĺ            | Χ            | X                 | Χ                | Н  |                                     |

## **Byte Select Truth Table**

| WE | OE | LB | UB | Operation <sup>[15]</sup>          |  |

|----|----|----|----|------------------------------------|--|

| Н  | Н  | Х  | Х  | Dood: Outpute dischlod             |  |

|    | Х  | Н  | Н  | Read; Outputs disabled             |  |

| Н  | L  | Н  | L  | L Read upper byte; HI-Z lower byte |  |

|    |    | L  | Н  | Read lower byte; HI-Z upper byte   |  |

|    |    | L  | L  | Read both bytes                    |  |

| L  | Х  | Н  | L  | Write upper byte; Mask lower byte  |  |

|    |    | L  | Н  | Write lower byte; Mask upper byte  |  |

|    |    | L  | L  | Write both bytes                   |  |

<sup>11.</sup> H = Logic HIGH, L = Logic LOW, V = Valid Data, X = Don't Care, √ = toggle LOW, ↑ = toggle HIGH.

12. For write cycles, data-in is latched on the rising edge of CE or WE, whichever comes first.

13. WE-controlled write cycle begins as a Read cycle and then A<sub>15-2</sub> is latched.

<sup>14.</sup> Addresses A<sub>1-0</sub> must remain stable for at least 15 ns during page mode operation.

15. The UB and LB pins may be grounded if 1) the system does not perform byte writes and 2) the device is not configured as a 128K x 8.

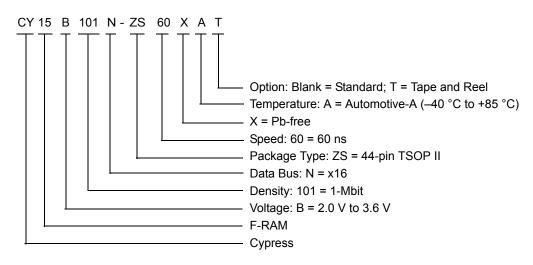

## **Ordering Information**

| Access Time (ns) | Ordering Code     | Package<br>Diagram | Package Type                     | Operating Range |

|------------------|-------------------|--------------------|----------------------------------|-----------------|

| 60               | CY15B101N-ZS60XAT | 51_85087           | 44-pin TSOP II with sleep mode   | Automotive-A    |

| 00               | CY15B101N-ZS60XA  | 31-03007           | 44-piii 130F ii witti sieep mode | Automotive-A    |

All the above parts are Pb-free.

## **Ordering Code Definitions**

## **Package Diagram**

Figure 14. 44-pin TSOP Package Outline, 51-85087

51-85087 \*E

## **Acronyms**

| Acronym                         | Description                             |  |  |  |

|---------------------------------|-----------------------------------------|--|--|--|

| UB                              | Upper Byte                              |  |  |  |

| Lower Byte                      |                                         |  |  |  |

| CE                              | Chip Enable                             |  |  |  |

| CMOS                            | Complementary Metal Oxide Semiconductor |  |  |  |

| EIA                             | Electronic Industries Alliance          |  |  |  |

| F-RAM                           | Ferroelectric Random Access Memory      |  |  |  |

| I/O Input/Output                |                                         |  |  |  |

| OE                              | Output Enable                           |  |  |  |

| RoHS                            | Restriction of Hazardous Substances     |  |  |  |

| RW                              | Read and Write                          |  |  |  |

| SRAM                            | Static Random Access Memory             |  |  |  |

| TSOP Thin Small Outline Package |                                         |  |  |  |

| WE                              | Write Enable                            |  |  |  |

## **Document Conventions**

## **Units of Measure**

| Symbol | Unit of Measure |  |  |  |

|--------|-----------------|--|--|--|

| °C     | degree Celsius  |  |  |  |

| Hz     | hertz           |  |  |  |

| kHz    | kilohertz       |  |  |  |

| kΩ     | kilohm          |  |  |  |

| MHz    | megahertz       |  |  |  |

| μΑ     | microampere     |  |  |  |

| μF     | microfarad      |  |  |  |

| μS     | microsecond     |  |  |  |

| mA     | milliampere     |  |  |  |

| ms     | millisecond     |  |  |  |

| ΜΩ     | megaohm         |  |  |  |

| ns     | nanosecond      |  |  |  |

| Ω      | ohm             |  |  |  |

| %      | percent         |  |  |  |

| pF     | picofarad       |  |  |  |

| V      | volt            |  |  |  |

| W      | watt            |  |  |  |

# **Document History Page**

|      | ocument Title: CY15B101N, 1-Mbit (64K × 16) Automotive F-RAM Memory |                    |                    |                                                                                                                                                                                                                                                                      |  |  |

|------|---------------------------------------------------------------------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rev. | ECN No.                                                             | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                |  |  |

| **   | 4630415                                                             | ZSK / LIZB         | 01/21/2015         | New data sheet.                                                                                                                                                                                                                                                      |  |  |

| *A   | 4746319                                                             | GVCH               | 04/28/2015         | Changed status from Advance to Preliminary.                                                                                                                                                                                                                          |  |  |

| *B   | 4774256                                                             | GVCH               | 06/04/2015         | Changed status from Preliminary to Final.                                                                                                                                                                                                                            |  |  |

| *C   | 4766039                                                             | GVCH               | 06/22/2015         | Updated Functional Truth Table:  Fixed typo (Included "Toggle LOW" and "Toggle HIGH" condition in "CE" and "WE" columns).                                                                                                                                            |  |  |

| *D   | 4883462                                                             | ZSK / PSR          | 09/04/2015         | Updated Functional Description: Added "For a complete list of related resources, click here." at the end. Updated Maximum Ratings: Removed "Maximum junction temperature". Added "Maximum accumulated storage time". Added "Ambient temperature with power applied". |  |  |

| *E   | 6033841                                                             | GVCH               | 01/16/2018         | Updated to the new template. Completing the Sunset review.                                                                                                                                                                                                           |  |  |

## Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### **Products**

Arm® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Memory cypress.com/memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

## PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

#### **Cypress Developer Community**

Community | Projects | Video | Blogs | Training | Components

## **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2015-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not l

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 001-96058 Rev. \*E Revised January 16, 2018 Page 19 of 19

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А