#### SINGLE-CHIP ETHERNET CONTROLLER

#### **Ethernet Controller**

- Integrated IEEE 802.3 MAC and 10 BASE-T PHY

- Fully compatible with 100/1000 BASE-T networks

- Full/Half duplex with auto-negotiation

- Automatic polarity detection and correction

- · Automatic retransmission on collision

- · Automatic padding and CRC generation

- · Supports broadcast and multi-cast MAC addressing

#### Parallel Host Interface (30 Mbps Transfer Rate)

- 8-bit multiplexed or non-multiplexed mode

- Only 11 I/O pins required in multiplexed mode

- Intel<sup>®</sup> or Motorola<sup>®</sup> Bus Format

- Interrupt on received packets and Wake-on-LAN

#### 8 kB Flash Memory

- 8192 bytes ISP non-volatile memory

- Factory pre-programmed unique 48-bit MAC Address

- No external EEPROM required

#### Other Features

- LED output drivers (Link/Activity)

- Dedicated 2 kB RAM transmit buffer and 4 kB RAM receive FIFO buffer

- Power-on Reset

- 5 V Tolerant I/O

#### **Software Support**

- Royalty-free TCP/IP stack with device drivers

- TCP/IP Stack Configuration Wizard

- · Hardware diagnostic software and example code

#### **Example Applications**

- Remote sensing and monitoring

- Inventory management

- · VoIP phone adapters

- · Point-of-sale devices

- Network clocks

- Embedded Web Server

- · Remote Ethernet-to-UART bridge

#### **Supply Voltage**

• 3.1 to 3.6 V

#### **Package**

- Pb-free 48-pin TQFP (9x9 mm footprint)

- Pb-free 28-pin QFN (5x5 mm footprint)

#### **Ordering Part Number**

- CP2200-GQ (48-pin)

- CP2201-GM (28-pin)

#### Temperature Range: -40 to +85 °C

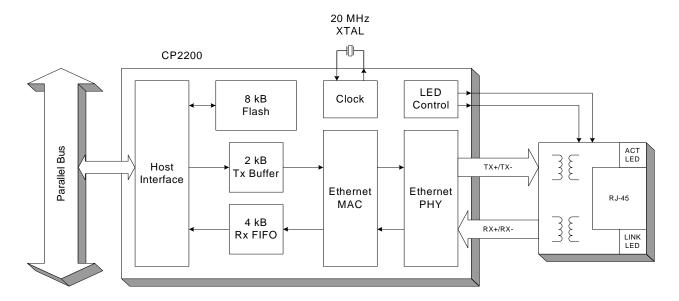

Figure 1. Example System Diagram

2

# TABLE OF CONTENTS

| <u>Section</u>                                               | <u>Page</u> |

|--------------------------------------------------------------|-------------|

| 1. System Overview                                           | 5           |

| 2. Typical Connection Diagram                                | 6           |

| 3. Absolute Maximum Ratings                                  |             |

| 4. Electrical Characteristics                                | 9           |

| 5. Pinout and Package Definitions                            | 10          |

| 6. Functional Description                                    |             |

| 6.1. Overview                                                | 18          |

| 6.2. Reset Initialization                                    | 18          |

| 6.3. Interrupt Request Signal                                |             |

| 6.4. Clocking Options                                        |             |

| 6.5. LED Control                                             |             |

| 6.6. Sending and Receiving Packets                           | 22          |

| 7. Internal Memory and Registers                             |             |

| 7.1. Random Access to RAM Transmit and Receive Buffers       |             |

| 7.2. Internal Registers                                      | 25          |

| 8. Interrupt Sources                                         |             |

| 9. Reset Sources                                             | 37          |

| 9.1. Power-On Reset                                          | 38          |

| 9.2. Power-fail                                              | 39          |

| 9.3. Oscillator-Fail Reset                                   | 39          |

| 9.4. External Pin Reset                                      | 39          |

| 9.5. Software Reset                                          | 40          |

| 9.6. Determining the Source of the Last Reset                | 41          |

| 9.7. De-Selecting Interrupt Sources                          | 42          |

| 10. Power Modes                                              | 43          |

| 10.1. Normal Mode                                            | 44          |

| 10.2. Link Detection Mode                                    | 44          |

| 10.3. Memory Mode                                            | 44          |

| 10.4. Shutdown Mode                                          | 44          |

| 10.5. Disabling Secondary Device Functions                   | 45          |

| 11. Transmit Interface                                       | 47          |

| 11.1. Overview                                               | 47          |

| 11.2. Transmitting a Packet                                  |             |

| 11.3. Overriding Transmit Configuration Options              | 48          |

| 11.4. Transmit Buffer and AutoWrite Interface                | 48          |

| 11.5. Transmit Status and Control Registers                  | 49          |

| 12. Receive Interface                                        | 58          |

| 12.1. Overview                                               | 58          |

| 12.2. Reading a Packet Using the Autoread Interface          | 58          |

| 12.3. Timing and Buffer Overflow Considerations              | 58          |

| 12.4. Initializing the Receive Buffer, Filter and Hash Table |             |

|                                                              |             |

# CP2200/1

| 12.5. Receive Status and Control Registers                     | 60  |

|----------------------------------------------------------------|-----|

| 12.6. Advanced Receive Buffer Operation                        | 66  |

| 12.7. Receive Buffer Advanced Status and Control Registers     | 67  |

| 13. Flash Memory                                               |     |

| 13.1. Programming the Flash Memory                             | 73  |

| 13.2. Reading the Flash Memory                                 | 74  |

| 13.3. Flash Access Registers                                   | 75  |

| 14. Media Access Controller (MAC)                              | 78  |

| 14.1. Initializing the MAC                                     | 78  |

| 14.2. Accessing the Indirect MAC Registers                     | 78  |

| 14.3. Indirect MAC Register Descriptions                       | 80  |

| 15. Physical Layer (PHY)                                       | 88  |

| 15.1. Auto-Negotiation and Duplex Mode                         | 88  |

| 15.2. Auto-Negotiation Synchronization                         | 88  |

| 15.3. Loopback Mode                                            | 89  |

| 15.4. Link Integrity Function                                  |     |

| 15.5. Receiver Smart Squelch and Automatic Polarity Correction |     |

| 15.6. Transmitter Jabber Function                              | 89  |

| 15.7. Initializing the Physical Layer                          | 90  |

| 16. Parallel Interface                                         |     |

| 16.1. Non-Multiplexed Intel Format                             | 96  |

| 16.2. Multiplexed Intel Format                                 |     |

| 16.3. Non-Multiplexed Motorola Format                          |     |

| 16.4. Multiplexed Motorola Format                              |     |

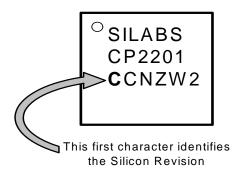

| 17. Revision-Specific Behavior                                 |     |

| 17.1. Revision Identification                                  | 104 |

| 17.2. MAC Address Filtering                                    |     |

| Document Change List                                           | 106 |

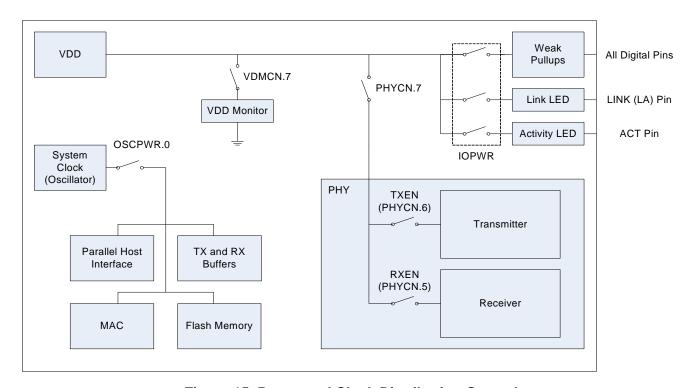

#### 1. System Overview

The CP2200/1 is a single-chip Ethernet controller containing an integrated IEEE 802.3 Ethernet Media Access Controller (MAC), 10BASE-T Physical Layer (PHY), and 8 kB Non-Volatile Flash Memory available in a compact 5 x 5 mm QFN-28 package (sometimes called "MLF" or "MLP") and a 48-pin TQFP package. The CP2200/1 can add Ethernet connectivity to any microcontroller or host processor with 11 or more Port I/O pins. The 8-bit parallel interface bus supports both Intel and Motorola bus formats in multiplexed and non-multiplexed mode. The data transfer rate in non-multiplexed mode can exceed 30 Mbps.

The on-chip Flash memory may be used to store user constants, web server content, or as general purpose non-volatile memory. The Flash is factory preprogrammed with a unique 48-bit MAC address stored in the last six memory locations. Having a unique MAC address stored in the CP2200/1 often removes the serialization step from the product manufacturing process of most embedded systems.

The CP2200/1 has four power modes with varying levels of functionality that allow the host processor to manage the overall system power consumption. The optional interrupt pin also allows the host to enter a "sleep" mode and awaken when a packet is received or when the CP2200/1 is plugged into a network. Auto-negotiation allows the device to automatically detect the most efficient duplex mode (half/full duplex) supported by the network.

The Ethernet Development Kit (Ethernet-DK) bundles a C8051F120 MCU Target Board, CP2200 Ethernet Development Board (AB4), the Silicon Laboratories IDE, all necessary debug hardware, and a TCP/IP Configuration Wizard. The Ethernet Development Kit includes all hardware, software, and examples necessary to design an embedded system using the CP2200. The CP2200 Ethernet Development Board is also compatible with the C8051F020TB and C8051F340TB. Individual target boards may be purchased online by visiting www.silabs.com.

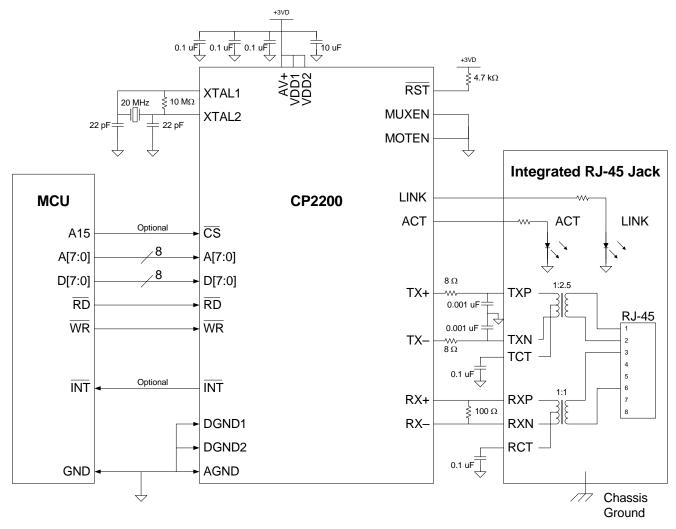

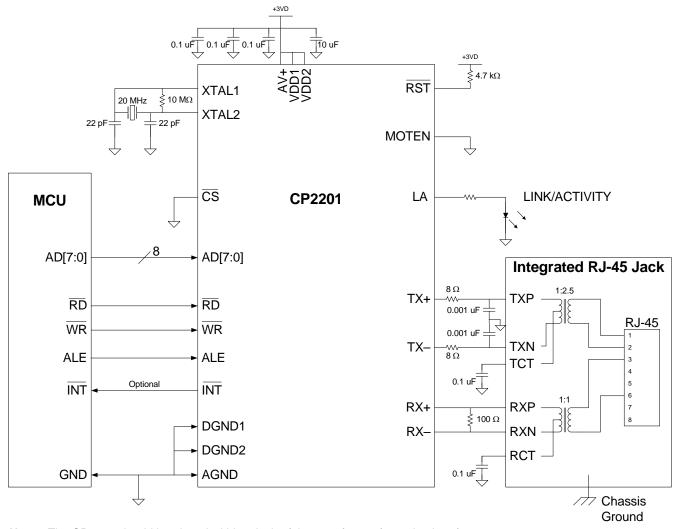

#### 2. Typical Connection Diagram

Figure 2 and Figure 3 show typical connection diagrams for the 48-pin CP2200 and 28-pin CP2201.

Note: The CP220x should be placed within 1 inch of the transformer for optimal performance.

Figure 2. Typical Connection Diagram (Non-Multiplexed)

**Note:** The CP220x should be placed within 1 inch of the transformer for optimal performance.

**Figure 3. Typical Connection Diagram (Multiplexed)**

## 3. Absolute Maximum Ratings

**Table 1. Absolute Maximum Ratings**

| Parameter                                             | Conditions | Min  | Тур | Max | Units |

|-------------------------------------------------------|------------|------|-----|-----|-------|

| Ambient temperature under bias                        |            | -55  | _   | 125 | °C    |

| Storage Temperature                                   |            | -65  | _   | 150 | °C    |

| Voltage on any I/O Pin or RST with respect to GND     |            | -0.3 | _   | 5.8 | V     |

| Voltage on V <sub>DD</sub> with respect to GND        |            | -0.3 | _   | 4.2 | V     |

| Maximum Total current through V <sub>DD</sub> and GND |            | _    | _   | 500 | mA    |

| Maximum output current sunk by RST or any I/O pin     |            | _    | _   | 100 | mA    |

**Note:** Stresses above those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the devices at or exceeding the conditions in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 4. Electrical Characteristics

**Table 2. Global DC Electrical Characteristics**

$V_{DD}$  = 3.1 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                                                           | Conditions              | Min | Тур | Max | Units |

|---------------------------------------------------------------------|-------------------------|-----|-----|-----|-------|

| Supply Voltage                                                      |                         | 3.1 | 3.3 | 3.6 | V     |

| Supply Current in Normal Mode (Transmitting)                        | V <sub>DD</sub> = 3.3 V | _   | 75  | 155 | mA    |

| Supply Current in Normal Mode (No Network Traffic)                  | V <sub>DD</sub> = 3.3 V | _   | 60  | _   | mA    |

| Supply Current with Transmitter and Receiver Disabled (Memory Mode) | V <sub>DD</sub> = 3.3 V | _   | 47  | _   | mA    |

| Supply Current in Reset                                             | V <sub>DD</sub> = 3.3 V | _   | 15  | _   | mA    |

| Supply Current in Shutdown Mode                                     | V <sub>DD</sub> = 3.3 V | _   | 6.5 | _   | mA    |

| Specified Operating Temperature Range                               |                         | -40 | _   | +85 | °C    |

# Table 3. Digital I/O DC Electrical Characteristics $V_{DD}$ = 3.1 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameters                             | Conditions                | Min                   | Тур            | Max | UNITS |

|----------------------------------------|---------------------------|-----------------------|----------------|-----|-------|

| Output High Voltage (V <sub>OH</sub> ) | $I_{OH} = -3 \text{ mA}$  | V <sub>DD</sub> - 0.7 | _              | _   | V     |

|                                        | I <sub>OH</sub> = -10 μA  | $V_{DD} - 0.1$        | _              | _   |       |

|                                        | $I_{OH} = -10 \text{ mA}$ | _                     | $V_{DD} - 0.8$ | _   |       |

| Output Low Voltage (V <sub>OL</sub> )  | I <sub>OL</sub> = 8.5 mA  | _                     | _              | 0.6 | V     |

|                                        | I <sub>OL</sub> = 10 μA   | _                     | _              | 0.1 |       |

|                                        | $I_{OL} = 25 \text{ mA}$  | _                     | 1.0            | _   |       |

| Input High Voltage (V <sub>IH</sub> )  |                           | 2.0                   | _              | _   | V     |

| Input Low Voltage (V <sub>IL</sub> )   |                           | _                     | _              | 0.8 | V     |

| Input Leakage Current                  |                           | _                     | 25             | 50  | μΑ    |

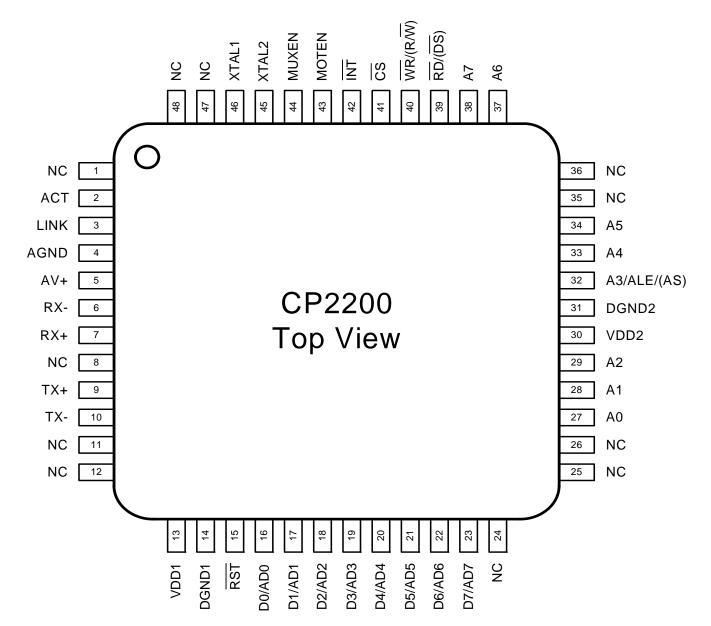

# 5. Pinout and Package Definitions

Table 4. CP2200/1 Pin Definitions

| Name Pin Numbers |        |        | Туре     | Description                                                                                                                                                                                                                                            |

|------------------|--------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 48-pin | 28-pin |          |                                                                                                                                                                                                                                                        |

| AV+              | 5      | 3      | Power In | 3.1–3.6 V Analog Power Supply Voltage Input.                                                                                                                                                                                                           |

| AGND             | 4      | 2      |          | Analog Ground                                                                                                                                                                                                                                          |

| $V_{DD1}$        | 13     | 8      | Power In | 3.1–3.6 V Digital Power Supply Voltage Input.                                                                                                                                                                                                          |

| DGND1            | 14     | 9      |          | Digital Ground                                                                                                                                                                                                                                         |

| V <sub>DD2</sub> | 30     | 19     | Power In | 3.1–3.6 V Digital Power Supply Voltage Input.                                                                                                                                                                                                          |

| DGND2            | 31     | 20     |          | Digital Ground                                                                                                                                                                                                                                         |

| RST              | 15     | 10     | D I/O    | Device Reset. Open-drain output of internal POR and $V_{DD}$ monitor. An external source can initiate a system reset by driving this pin low for at least 15 $\mu$ s.                                                                                  |

| LINK             | 3*     | _      | D Out    | Link LED. Push-pull output driven high when valid 10BASE-T link pulses are detected (Link Good) and driven low when valid 10BASE-T link pulses are not detected (Link Fail).                                                                           |

| ACT              | 2*     | _      | D Out    | Activity LED. Push-pull output driven high for 50 ms when any packet is transmitted or received and driven low all other times.                                                                                                                        |

| LA               | _      | 1*     | D Out    | Link or Activity LED. Push-pull output driven high when valid link pulses are detected (Link Good) and driven low otherwise (Link Fail). The output is toggled for each packet transmitted or received then returns to its original state after 50 ms. |

| XTAL1            | 46     | 28     | A In     | Crystal Input. This pin is the return for the external oscillator driver. This pin can be overdriven by an external CMOS clock.                                                                                                                        |

| XTAL2            | 45*    | 27*    | A Out    | Crystal Output. This pin is the excitation driver for a quartz crystal.                                                                                                                                                                                |

| TX+              | 9      | 6      | A Out    | 10BASE-T Transmit, Differential Output (Positive).                                                                                                                                                                                                     |

| TX-              | 10     | 7      | A Out    | 10BASE-T Transmit, Differential Output (Negative).                                                                                                                                                                                                     |

| RX+              | 7      | 5      | A In     | 10BASE-T Receive, Differential Input (Positive).                                                                                                                                                                                                       |

| RX-              | 6      | 4      | A In     | 10BASE-T Receive, Differential Input (Negative).                                                                                                                                                                                                       |

| MOTEN            | 43     | 26     | D In     | Motorola Bus Format Enable. This pin should be tied directly to $V_{\rm D}$ for Motorola bus format or directly to GND for Intel bus format.                                                                                                           |

| MUXEN            | 44     | _      | D In     | Multiplexed Bus Enable. This pin should be tied directly to $V_{DD}$ for multiplexed bus mode or directly to GND for non-multiplexed bus mode.                                                                                                         |

| ĪNT              | 42     | 25     | D Out    | Interrupt Service Request. This pin provides notification to the hos                                                                                                                                                                                   |

\*Note: Pins can be left unconnected when not used.

Table 4. CP2200/1 Pin Definitions (Continued)

| Name        | Pin Nu                                     | ımbers | Type  | Description                                                                                                       |

|-------------|--------------------------------------------|--------|-------|-------------------------------------------------------------------------------------------------------------------|

|             | 48-pin                                     | 28-pin |       |                                                                                                                   |

| CS          | 41                                         | 24     | D In  | Device Chip Select.                                                                                               |

| RD/(DS)     | 39                                         | 22     | D In  | Read Strobe (Intel Mode) or<br>Data Strobe (Motorola Mode)                                                        |

| WR/(R/W)    | 40                                         | 23     | D In  | Write Strobe (Intel Mode) or<br>Read/Write Strobe (Motorola Mode)                                                 |

| D0/AD0      | 16                                         | 11     | D I/O | Bit 0, Non-Multiplexed Data Bus or Multiplexed Address/Data Bus                                                   |

| D1/AD1      | 17                                         | 12     | D I/O | Bit 1, Non-Multiplexed Data Bus or Multiplexed Address/Data Bus                                                   |

| D2/AD2      | 18                                         | 13     | D I/O | Bit 2, Non-Multiplexed Data Bus or Multiplexed Address/Data Bus                                                   |

| D3/AD3      | 19                                         | 14     | D I/O | Bit 3, Non-Multiplexed Data Bus or Multiplexed Address/Data Bus                                                   |

| D4/AD4      | 20                                         | 15     | D I/O | Bit 4, Non-Multiplexed Data Bus or Multiplexed Address/Data Bus                                                   |

| D5/AD5      | 21                                         | 16     | D I/O | Bit 5, Non-Multiplexed Data Bus or Multiplexed Address/Data Bus                                                   |

| D6/AD6      | 22                                         | 17     | D I/O | Bit 6, Non-Multiplexed Data Bus or Multiplexed Address/Data Bus                                                   |

| D7/AD7      | 23                                         | 18     | D I/O | Bit 7, Non-Multiplexed Data Bus or Multiplexed Address/Data Bus                                                   |

| A0          | 27*                                        | _      | D In  | Bit 0, Non-Multiplexed Address Bus                                                                                |

| A1          | 28*                                        | _      | D In  | Bit 1, Non-Multiplexed Address Bus                                                                                |

| A2          | 29*                                        | _      | D In  | Bit 2, Non-Multiplexed Address Bus                                                                                |

| A3/ALE/(AS) | 32                                         | _      | D In  | Bit 3, Non-Multiplexed Address Bus ALE Strobe (Multiplexed Intel Mode) Address Strobe (Multiplexed Motorola Mode) |

| ALE/(AS)    | _                                          | 21     | D In  | ALE Strobe (Intel Mode) Address Strobe (Motorola Mode)                                                            |

| A4          | 33*                                        | _      | D In  | Bit 4, Parallel Interface Non-Multiplexed Address Bus                                                             |

| A5          | 34*                                        | _      | D In  | Bit 5, Parallel Interface Non-Multiplexed Address Bus                                                             |

| A6          | 37*                                        | _      | D In  | Bit 6, Parallel Interface Non-Multiplexed Address Bus                                                             |

| A7          | 38*                                        | _      | D In  | Bit 7, Parallel Interface Non-Multiplexed Address Bus                                                             |

| NC          | 1, 8,<br>11,12<br>24–26<br>35,36<br>47, 48 | _      |       | These pins should be left unconnected or tied to V <sub>DD</sub> .                                                |

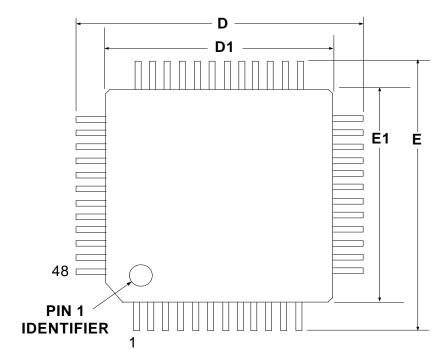

Figure 4. 48-pin TQFP Pinout Diagram

Table 5. TQFP-48 Package Dimensions

|    |      | MM   |      |  |  |  |

|----|------|------|------|--|--|--|

|    | Min  | Тур  | Max  |  |  |  |

| Α  | _    | _    | 1.20 |  |  |  |

| A1 | 0.05 | _    | 0.15 |  |  |  |

| A2 | 0.95 | 1.00 | 1.05 |  |  |  |

| b  | 0.17 | 0.22 | 0.27 |  |  |  |

| D  | _    | 9.00 | _    |  |  |  |

| D1 | _    | 7.00 | _    |  |  |  |

| Е  | _    | 9.00 | _    |  |  |  |

| е  | _    | 0.50 | _    |  |  |  |

| E1 | _    | 7.00 | _    |  |  |  |

Figure 5. 48-pin TQFP Package Dimensions

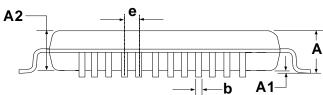

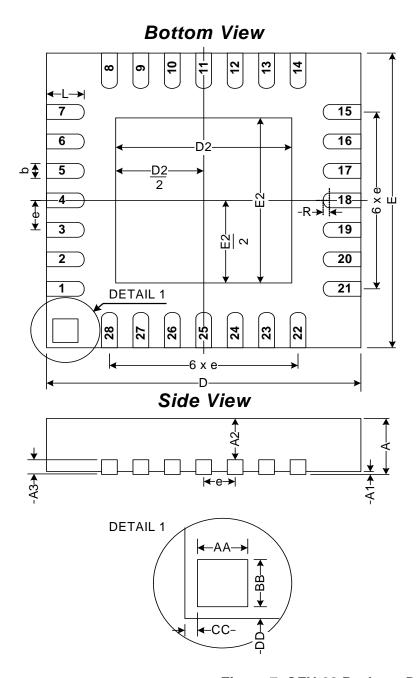

Figure 6. QFN-28 Pinout Diagram (Top View)

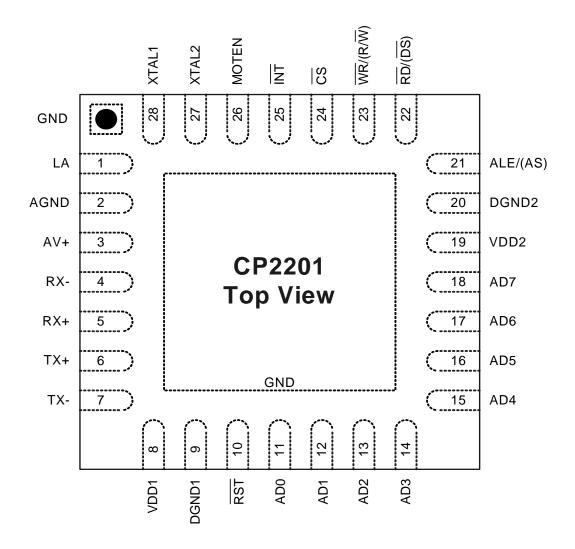

Table 6. QFN-28 Package Dimensions

|    | <u> </u> | 1010110 |      |

|----|----------|---------|------|

|    |          | MM      |      |

|    | Min      | Тур     | Max  |

| Α  | 0.80     | 0.90    | 1.00 |

| A1 | 0        | 0.02    | 0.05 |

| A2 | 0        | 0.65    | 1.00 |

| A3 | _        | 0.25    | _    |

| b  | 0.18     | 0.23    | 0.30 |

| D  | _        | 5.00    | _    |

| D2 | 2.90     | 3.15    | 3.35 |

| Е  | _        | 5.00    | _    |

| E2 | 2.90     | 3.15    | 3.35 |

| е  | _        | 0.5     | _    |

| L  | 0.45     | 0.55    | 0.65 |

| N  | _        | 28      | _    |

| ND | _        | 7       | _    |

| NE | _        | 7       | _    |

| R  | 0.09     | _       | _    |

| AA | _        | 0.435   | _    |

| BB | _        | 0.435   | _    |

| CC | _        | 0.18    | _    |

| DD |          | 0.18    | _    |

|    |          |         |      |

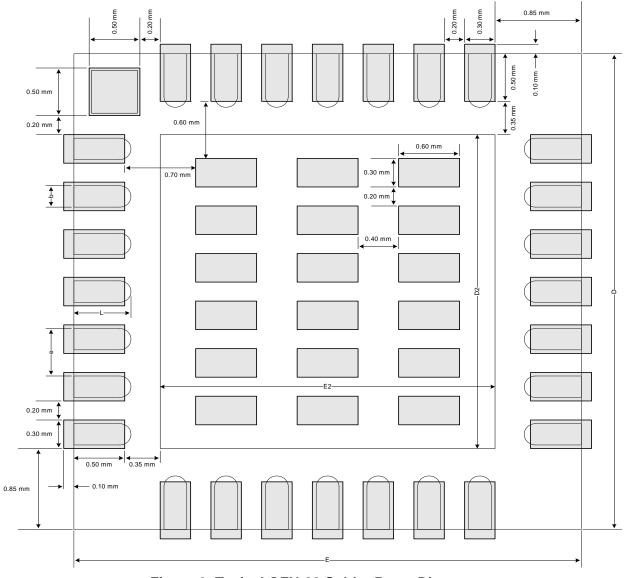

Figure 7. QFN-28 Package Drawing

# 0.50 mm Optional Output Optional Output Optional Output Ou

Top View

Figure 8. Typical QFN-28 Landing Diagram

16 Rev. 1.0

— 0.10 mm

0.85 mm

# Top View

Figure 9. Typical QFN-28 Solder Paste Diagram

#### 6. Functional Description

#### 6.1. Overview

In most systems, the CP2200/1 is used for transmitting and receiving Ethernet packets, non-volatile data storage, and controlling Link and Activity LEDs. The device is controlled using direct and indirect internal registers accessible through the parallel host interface. All digital pins on the device are 5 V tolerant.

#### 6.2. Reset Initialization

After every CP2200/1 reset, the following initialization procedure is recommended to ensure proper device operation:

- Step 1: Wait for the reset pin to rise. This step takes the longest during a power-on reset.

- Step 2: Wait for Oscillator Initialization to complete. The host processor will receive notification through the interrupt request signal once the oscillator has stabilized.

- Step 3: Wait for Self Initialization to complete. The INT0 interrupt status register on page 31 should be checked to determine when Self Initialization completes.

- Step 4: Disable interrupts (using INT0EN and INT1EN on page 33 and page 36) for events that will not be monitored or handled by the host processor. By default, all interrupts are enabled after every reset.

- Step 5: Initialize the physical layer. See "15.7. Initializing the Physical Layer" on page 90 for a detailed physical layer initialization procedure.

- Step 6: Enable the desired Activity, Link, or Activity/Link LEDs using the IOPWR register on page 45.

- Step 7: Initialize the media access controller (MAC). See "14.1. Initializing the MAC" on page 78 for a detailed MAC initialization procedure.

- Step 8: Configure the receive filter. See "12.4. Initializing the Receive Buffer, Filter and Hash Table" on page 59 for a detailed initialization procedure.

- Step 9: The CP2200/1 is ready to transmit and receive packets.

#### 6.3. Interrupt Request Signal

The CP2200/1 has an interrupt request signal (INT) that can be used to notify the host processor of pending interrupts. The INT signal is asserted upon detection of any enabled interrupt event. Host processors that cannot dedicate a port pin to the INT signal can periodically poll the interrupt status registers to see if any interrupt generating events have occurred. If the /INT signal is not used, pending interrupts such a Receive FIFO Full must still be serviced.

The 14 interrupt sources are listed below. Interrupts are enabled on reset and can be disabled by software. Pending interrupts can be cleared (allowing the INT signal to de-assert) by reading the self-clearing interrupt registers. See "8. Interrupt Sources" on page 30 for a complete description of the CP2200/1 interrupts.

- End of Packet Reached

- Receive FIFO Empty

- Receive FIFO Full

- Oscillator Initialization Complete

- Self Initialization Complete

- Flash Write/Erase Complete

- Packet Transmitted

- Packet Received

- "Wake-on-LAN" Wakeup Event

- Link Status Changed

- Jabber Detected

- Auto-Negotiation Failed

- Remote Fault Notification

- Auto-Negotiation Complete

#### 6.4. Clocking Options

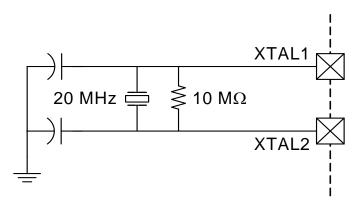

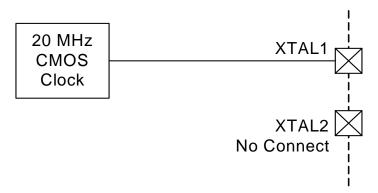

The CP2200/1 can be clocked from an external parallel-mode crystal oscillator or CMOS clock. Figure 10 and Figure 11 show typical connections for both clock source types. If a crystal oscillator is chosen to clock the device, the crystal is started once the device is released from reset and remains on until the device reenters the reset state or loses power.

Figure 10. Crystal Oscillator Example

**Important note on external crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with a ground plane from any other traces that could introduce noise or interference.

Figure 11. External CMOS Clock Example

Table 7 lists the clocking requirements of the CP2200/1 when using a crystal oscillator or CMOS clock. Table 8 shows the electrical characteristics of the XTAL1 pin. These characteristics are useful when selecting an external CMOS clock.

#### **Table 7. Clocking Requirements**

$V_{DD}$  = 3.1 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameters      | Conditions | Min | Тур | Max | UNITS |

|-----------------|------------|-----|-----|-----|-------|

| Frequency       |            | _   | 20  | _   | MHz   |

| Frequency Error |            | _   |     | ±50 | ppm   |

| Duty Cycle      |            | 45  | 50  | 55  | %     |

# Table 8. Input Clock Pin (XTAL1) DC Electrical Characteristics $V_{DD}$ = 3.1 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameters               | Conditions | Min | Тур | Max | UNITS |

|--------------------------|------------|-----|-----|-----|-------|

| XTAL1 Input Low Voltage  |            | _   | _   | 0.7 | V     |

| XTAL1 Input High Voltage |            | 2.0 | _   | _   | V     |

#### 6.5. LED Control

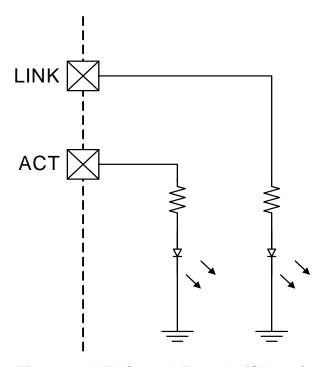

The CP2200/1 can be used to control link status and activity LEDs. The CP2200 (48-pin TQFP) has two push-pull LED drivers that can source up to 10 mA each. The CP2201 (28-pin QFN) has a single push-pull LED driver that turns the LED on or off based on the link status and blinks the LED when activity is detected on a good link. Table 9 shows the function of the LED signals available on the CP2200/1.

| Table 9 | 9. LED | Control | l Signal | ls |

|---------|--------|---------|----------|----|

|---------|--------|---------|----------|----|

| Signal | Device | Description                                                                                                 |

|--------|--------|-------------------------------------------------------------------------------------------------------------|

| LINK   | CP2200 | Asserted when valid link pulses are detected.                                                               |

| ACT    | CP2200 | Asserted for 50 ms for each packet transmitted or received.                                                 |

| LA     | CP2201 | Asserted when valid link pulses are detected and toggled for 50 ms for each packet transmitted or received. |

Figure 12 shows a typical LED connection for the CP2200. The CP2201 uses an identical connection for the LA (link/activity) pin. The LED drivers are enabled and disabled using the IOPWR register on page 45.

Figure 12. LED Control Example (CP2200)

#### CP2200/1

#### 6.6. Sending and Receiving Packets

After reset initialization is complete, the CP2200/1 is ready to send and receive packets. Packets are sent by loading data into the transmit buffer using the AutoWrite register and writing '1' to TXGO. See "11.2. Transmitting a Packet" on page 48 for detailed information on how to transmit a packet using the transmit interface. A Packet Transmitted interrupt will be generated once transmission is complete.

Packet reception occurs automatically when reception is enabled in the MAC and the receive buffer is not full. Once a packet is received, the host processor is notified by generating a Packet Received interrupt. The host may read the packet using the AutoRead interface. See "12.2. Reading a Packet Using the Autoread Interface" on page 58 and "12.4. Initializing the Receive Buffer, Filter and Hash Table" on page 59 for additional information on using and initializing the receive interface.

#### 7. Internal Memory and Registers

The CP2200/1 is controlled through direct and indirect registers accessible through the parallel host interface. The host interface provides an 8-bit address space, of which there are 114 valid direct register locations (see Table 11 on page 25). All remaining addresses in the memory space are reserved and should not be read or written. The direct registers provide access to the RAM buffers, Flash memory, indirect MAC configuration registers, and other status and control registers for various device functions.

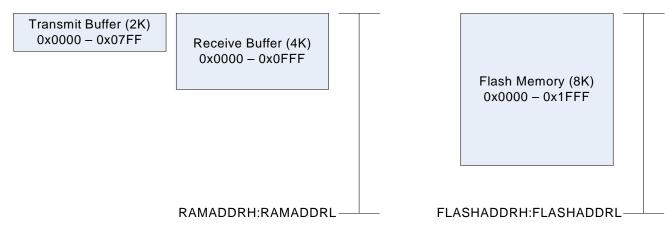

Figure 13 shows the RAM and Flash memory organization. The transmit and receive RAM buffers share the same address space and are both accessed using the RAMADDRH:RAMADDRL pointer. Each of the buffers has a dedicated data register. The Flash memory has a separate address space and a dedicated address pointer and data register. See "13. Flash Memory" on page 73 for detailed information on how to read and write to Flash.

Figure 13. RAM Buffers and Flash Memory Organization

#### 7.1. Random Access to RAM Transmit and Receive Buffers

The most common and most efficient methods for accessing the transmit and receive buffers are the AutoWrite and AutoRead interfaces. These interfaces allow entire packets to be written or read at a time. In very few cases, the transmit and receive buffers may need to be accessed randomly. An example of this is a system in which a specific byte in the packet is checked to determine whether to read the packet or discard it. The following procedure can be used to read or write data to either RAM buffer:

Step 1: Write the address of the target byte to RAMADDRH:RAMADDRL.

#### Step 2: Transmit Buffer:

Read or write 8-bit data to RAMTXDATA to read or write from the target byte in the transmit buffer.

#### Receive Buffer:

Read or write 8-bit data to RAMRXDATA to read or write from the target byte in the receive buffer.

**Note:** Reads and writes of the RAM buffers using the random access method are independent of the AutoRead and AutoWrite interfaces. Each of the interfaces has a dedicated set of address and data registers. See "11.2. Transmitting a Packet" on page 48 and "12.2. Reading a Packet Using the Autoread Interface" on page 58 for additional information about the AutoRead and AutoWrite interfaces.

#### Register 1. RAMADDRH: RAM Address Pointer High Byte

| R/W  | Reset Value |

|------|------|------|------|------|------|------|------|-------------|

|      |      |      |      |      |      |      |      | 00000000    |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | Address:    |

|      |      |      |      |      |      |      |      | 0v08        |

Bits7-0: RAMADDRH: RAM Address Register High Byte

Holds the most significant eight bits of the target RAM address.

#### Register 2. RAMADDRL: RAM Address Pointer Low Byte

|   | R/W  | Reset Value |

|---|------|------|------|------|------|------|------|------|-------------|

|   |      |      |      |      |      |      |      |      | 00000000    |

|   | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | Address:    |

| 1 |      |      |      |      |      |      |      |      | 0v $0$ a    |

Bits7-0: RAMADDRL: RAM Address Register Low Byte

Holds the least significant eight bits of the target RAM address.

#### Register 3. RAMTXDATA: RAM Transmit Buffer Data Register

| R/W  | Reset Value |

|------|------|------|------|------|------|------|------|-------------|

|      |      |      |      |      |      |      |      | 00000000    |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | Address:    |

|      |      |      |      |      |      |      |      | 0x04        |

Bits7-0: RAMTXDATA: Transmit Buffer Data Register

Read: Returns data in the transmit buffer at location RAMADDRH:RAMADDRL. Write: Writes data to the transmit buffer at location RAMADDRH:RAMADDRL.

#### Register 4. RAMRXDATA: RAM Receive Buffer Data Register

| R/W  | Reset Value |

|------|------|------|------|------|------|------|------|-------------|

|      |      |      |      |      |      |      |      | 00000000    |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | Address:    |

|      |      |      |      |      |      |      |      | 0x02        |

Bits7-0: RAMRXDATA: Receive Buffer Data Register

Read: Returns data in the receive buffer at location RAMADDRH:RAMADDRL. Write: Writes data to the receive buffer at location RAMADDRH:RAMADDRL.

#### 7.2. Internal Registers

The CP2200/1 has 114 direct internal registers and 9 indirect registers. The registers are grouped into ten categories based on function. Table 10 lists the register groups and provides links to the detailed register descriptions for each group. Table 11 lists all direct registers available on the device.

Table 10. CP2200/1 Register Groups

| RAM Access Registers                           | Section 7.1 on page 23  |

|------------------------------------------------|-------------------------|

| Interrupt Status and Control Registers         | Section 8 on page 30    |

| Reset Source Registers                         | Section 9 on page 37    |

| Power Mode Registers                           | Section 10 on page 43   |

| Transmit Status and Control Registers          | Section 11.5 on page 49 |

| Receive Interface Status and Control Registers | Section 12.5 on page 60 |

| Receive Buffer Status and Control Registers    | Section 12.7 on page 67 |

| FLASH Access Registers                         | Section 13.3 on page 75 |

| MAC Access Registers                           | Section 14.2 on page 78 |

| MAC Indirect Registers                         | Section 14.3 on page 80 |

| PHY Status and Control Registers               | Section 15 on page 88   |

**Table 11. Direct Registers**

| Register    | Address | Description                             | Page No. |

|-------------|---------|-----------------------------------------|----------|

| CPADDRH     | 0x21    | Current RX Packet Address High Byte     | page 65  |

| CPADDRL     | 0x22    | Current RX Packet Address Low Byte      | page 65  |

| CPINFOH     | 0x1D    | Current RX Packet Information High Byte | page 63  |

| CPINFOL     | 0x1E    | Current RX Packet Information Low Byte  | page 64  |

| CPLENH      | 0x1F    | Current RX Packet Length High Byte      | page 64  |

| CPLENL      | 0x20    | Current RX Packet Length Low Byte       | page 64  |

| CPTLB       | 0x1A    | Current RX Packet TLB Number            | page 67  |

| FLASHADDRH  | 0x69    | Flash Address Pointer High Byte         | page 76  |

| FLASHADDRL  | 0x68    | Flash Address Pointer Low Byte          | page 76  |

| FLASHAUTORD | 0x05    | Flash AutoRead w/ increment             | page 77  |

| FLASHDATA   | 0x06    | Flash Read/Write Data Register          | page 77  |

| FLASHERASE  | 0x6A    | Flash Erase                             | page 77  |

| FLASHKEY    | 0x67    | Flash Lock and Key                      | page 76  |

| FLASHSTA    | 0x7B    | Flash Status                            | page 75  |

**Table 11. Direct Registers**

| Register    | Address | Description                                 | Page No. |

|-------------|---------|---------------------------------------------|----------|

| INT0        | 0x63    | Interrupt Status Register 0 (Self-Clearing) | page 31  |

| INTOEN      | 0x64    | Interrupt Enable Register 0                 | page 33  |

| INT0RD      | 0x76    | Interrupt Status Register 0 (Read-Only)     | page 32  |

| INT1        | 0x7F    | Interrupt Status Register 1 (Self-Clearing) | page 34  |

| INT1EN      | 0x7D    | Interrupt Enable Register 1                 | page 36  |

| INT1RD      | 0x7E    | Interrupt Status Register 1 (Read-Only)     | page 35  |

| IOPWR       | 0x70    | Port Input/Output Power                     | page 45  |

| MACADDR     | 0x0A    | MAC Address Pointer                         | page 79  |

| MACDATAH    | 0x0B    | MAC Data Register High Byte                 | page 79  |

| MACDATAL    | 0x0C    | MAC Data Register Low Byte                  | page 79  |

| MACRW       | 0x0D    | MAC Read/Write Initiate                     | page 79  |

| OSCPWR      | 0x7C    | Oscillator Power                            | page 46  |

| PHYCF       | 0x79    | Physical Layer Configuration                | page 92  |

| PHYCN       | 0x78    | Physical Layer Control                      | page 91  |

| PHYSTA      | 0x80    | Physical Layer Status                       | page 93  |

| RAMADDRH    | 0x08    | RAM Address Pointer High Byte               | page 24  |

| RAMADDRL    | 0x09    | RAM Address Pointer Low Byte                | page 24  |

| RAMRXDATA   | 0x02    | RXFIFO RAM Data Register                    | page 24  |

| RAMTXDATA   | 0x04    | TXBUFF RAM Data Register                    | page 24  |

| RSTEN       | 0x72    | Reset Enable Register                       | page 42  |

| RSTSTA      | 0x73    | Reset Source Status Register                | page 41  |

| RXAUTORD    | 0x01    | RXFIFO AutoRead w/ increment                | page 62  |

| RXCN        | 0x11    | Receive Control                             | page 61  |

| RXFIFOHEADH | 0x17    | Receive Buffer Head Pointer High Byte       | page 71  |

| RXFIFOHEADL | 0x18    | Receive Buffer Head Pointer Low Byte        | page 71  |

| RXFIFOSTA   | 0x5B    | Receive Buffer Status                       | page 72  |

| RXFIFOTAILH | 0x15    | Receive Buffer Tail Pointer High Byte       | page 71  |

| RXFIFOTAILL | 0x16    | Receive Buffer Tail Pointer Low Byte        | page 71  |

| RXFILT      | 0x10    | Receive Filter Configuration                | page 62  |

**Table 11. Direct Registers**

| Register  | Address | Description                  | Page No. |

|-----------|---------|------------------------------|----------|

| RXHASHH   | 0x0E    | Receive Hash Table High Byte | page 62  |

| RXHASHL   | 0x0F    | Receive Hash Table Low Byte  | page 63  |

| RXSTA     | 0x12    | Receive Status               | page 61  |

| SWRST     | 0x75    | Software Reset Register      | page 40  |

| TLB0ADDRH | 0x27    | TLB0 Address High Byte       | page 70  |

| TLB0ADDRL | 0x28    | TLB0 Address Low Byte        | page 70  |

| TLB0INFOH | 0x23    | TLB0 Information High Byte   | page 68  |

| TLB0INFOL | 0x24    | TLB0 Information Low Byte    | page 69  |

| TLB0LENH  | 0x25    | TLB0 Length High Byte        | page 69  |

| TLB0LENL  | 0x26    | TLB0 Length Low Byte         | page 70  |

| TLB1ADDRH | 0x2D    | TLB1 Address High Byte       | page 70  |

| TLB1ADDRL | 0x2E    | TLB1 Address Low Byte        | page 70  |

| TLB1INFOH | 0x29    | TLB1 Information High Byte   | page 68  |

| TLB1INFOL | 0x2A    | TLB1 Information Low Byte    | page 69  |

| TLB1LENH  | 0x2b    | TLB1 Length High Byte        | page 69  |

| TLB1LENL  | 0x2C    | TLB1 Length Low Byte         | page 70  |

| TLB2ADDRH | 0x33    | TLB2 Address High Byte       | page 70  |

| TLB2ADDRL | 0x34    | TLB2 Address Low Byte        | page 70  |

| TLB2INFOH | 0x2F    | TLB2 Information High Byte   | page 68  |

| TLB2INFOL | 0x30    | TLB2 Information Low Byte    | page 69  |

| TLB2LENH  | 0x31    | TLB2 Length High Byte        | page 69  |

| TLB2LENL  | 0x32    | TLB2 Length Low Byte         | page 70  |

| TLB3ADDRH | 0x39    | TLB3 Address High Byte       | page 70  |

| TLB3ADDRL | 0x3A    | TLB3 Address Low Byte        | page 70  |

| TLB3INFOH | 0x35    | TLB3 Information High Byte   | page 68  |

| TLB3INFOL | 0x36    | TLB3 Information Low Byte    | page 69  |

| TLB3LENH  | 0x37    | TLB3 Length High Byte        | page 69  |

| TLB3LENL  | 0x38    | TLB3 Length Low Byte         | page 70  |

| TLB4ADDRH | 0x3F    | TLB4 Address High Byte       | page 70  |

**Table 11. Direct Registers**

| Register  | Address | Description                            | Page No. |

|-----------|---------|----------------------------------------|----------|

| TLB4ADDRL | 0x40    | TLB4 Address Low Byte                  | page 70  |

| TLB4INFOH | 0x3B    | TLB4 Information High Byte             | page 68  |

| TLB4INFOL | 0x3C    | TLB4 Information Low Byte              | page 69  |

| TLB4LENH  | 0x3D    | TLB4 Length High Byte                  | page 69  |

| TLB4LENL  | 0x3E    | TLB4 Length Low Byte                   | page 70  |

| TLB5ADDRH | 0x45    | TLB5 Address High Byte                 | page 70  |

| TLB5ADDRL | 0x46    | TLB5 Address Low Byte                  | page 70  |

| TLB5INFOH | 0x41    | TLB5 Information High Byte             | page 68  |

| TLB5INFOL | 0x42    | TLB5 Information Low Byte              | page 69  |

| TLB5LENH  | 0x43    | TLB5 Length High Byte                  | page 69  |

| TLB5LENL  | 0x44    | TLB5 Length Low Byte                   | page 70  |

| TLB6ADDRH | 0x4B    | TLB6 Address High Byte                 | page 70  |

| TLB6ADDRL | 0x4C    | TLB6 Address Low Byte                  | page 70  |

| TLB6INFOH | 0x47    | TLB6 Information High Byte             | page 68  |

| TLB6INFOL | 0x48    | TLB6 Information Low Byte              | page 69  |

| TLB6LENH  | 0x49    | TLB6 Length High Byte                  | page 69  |

| TLB6LENL  | 0x4A    | TLB6 Length Low Byte                   | page 70  |

| TLB7ADDRH | 0x51    | TLB7 Address High Byte                 | page 70  |

| TLB7ADDRL | 0x52    | TLB7 Address Low Byte                  | page 70  |

| TLB7INFOH | 0x4D    | TLB7 Information High Byte             | page 68  |

| TLB7INFOL | 0x4E    | TLB7 Information Low Byte              | page 69  |

| TLB7LENH  | 0x4F    | TLB7 Length High Byte                  | page 69  |

| TLB7LENL  | 0x50    | TLB7 Length Low Byte                   | page 70  |

| TLBVALID  | 0x1C    | TLB Valid Indicators                   | page 68  |

| TXAUTOWR  | 0x03    | Transmit Data AutoWrite                | page 53  |

| TXBUSY    | 0x54    | Transmit Busy Indicator                | page 51  |

| TXCN      | 0x53    | Transmit Control                       | page 51  |

| TXENDH    | 0x57    | Transmit Data Ending Address High Byte | page 53  |

| TXENDL    | 0x58    | Transmit Data Ending Address Low Byte  | page 53  |

## **Table 11. Direct Registers**

| Register | Address | Description                              | Page No. |

|----------|---------|------------------------------------------|----------|

| TXPAUSEH | 0x55    | Transmit Pause High Byte                 | page 52  |

| TXPAUSEL | 0x56    | Transmit Pause Low Byte                  | page 52  |

| TXPWR    | 0x7A    | Transmitter Power                        | page 46  |

| TXSTA0   | 0x62    | Transmit Status Vector 0                 | page 57  |

| TXSTA1   | 0x61    | Transmit Status Vector 1                 | page 56  |

| TXSTA2   | 0x60    | Transmit Status Vector 2                 | page 56  |

| TXSTA3   | 0x5F    | Transmit Status Vector 3                 | page 55  |

| TXSTA4   | 0x5E    | Transmit Status Vector 4                 | page 55  |

| TXSTA5   | 0x5D    | Transmit Status Vector 5                 | page 54  |

| TXSTA6   | 0x5C    | Transmit Status Vector 6                 | page 54  |

| TXSTARTH | 0x59    | Transmit Data Starting Address High Byte | page 52  |

| TXSTARTL | 0x5A    | Transmit Data Starting Address Low Byte  | page 52  |

| VDMCN    | 0x13    | V <sub>DD</sub> Monitor Control Register | page 39  |

#### 8. Interrupt Sources

The CP2200/1 can alert the host processor when any of the 14 interrupt source events listed in Table 12 triggers an interrupt. The CP2200/1 alerts the host by setting the appropriate flags in the interrupt status registers and driving the INT pin low. The INT pin will remain asserted until all interrupt flags for enabled interrupts have been cleared by the host. Interrupt flags are cleared by reading the self-clearing interrupt status registers, INTO and INT1. Interrupts can be disabled by clearing the corresponding bits in INT0EN and INT1EN.

If the host processor does not utilize the  $\overline{\text{INT}}$  pin, it can periodically read the interrupt status registers to determine if any interrupt-generating events have occurred. The INTORD and INT1RD read-only registers provide a method of checking for interrupts without clearing the interrupt status registers.

**Table 12. Interrupt Source Events**

| Event                              | Description                                                                                                                                                                                                                                                                                                         | Pending<br>Flag | Enable<br>Flag |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|

| End of Packet                      | The last byte of a packet has been read from the receive buffer using the AutoRead interface.                                                                                                                                                                                                                       | INT0.7          | INT0EN.7       |

| Receive FIFO Empty                 | The last packet in the receive buffer has been unloaded or discarded.                                                                                                                                                                                                                                               | INT0.6          | INT0EN.6       |

| Self Initialization Complete       | The device is ready for Reset Initialization. See "6.2. Reset Initialization" on page 18.                                                                                                                                                                                                                           | INT0.5          | INT0EN.5       |

| Oscillator Initialization Complete | The external oscillator has stabilized.                                                                                                                                                                                                                                                                             | INT0.4          | INT0EN.4       |

| Flash Write/Erase Complete         | A Flash write or erase operation has completed.                                                                                                                                                                                                                                                                     | INT0.3          | INT0EN.3       |

| Packet Transmitted                 | The transmit interface has transmitted a packet.                                                                                                                                                                                                                                                                    | INT0.2          | INT0EN.2       |

| Receive FIFO Full                  | The receive buffer is full or the maximum number of packets has been exceeded. Decode the RXFIFOSTA status register to determine the receive buffer status.                                                                                                                                                         | INT0.1          | INT0EN.1       |

| Packet Received                    | A packet has been added to the receive buffer.                                                                                                                                                                                                                                                                      | INT0.0          | INT0EN.0       |

| "Wake-on-LAN" Wakeup Event         | The device has been connected to a network.                                                                                                                                                                                                                                                                         | INT1.5          | INT1EN.5       |

| Link Status Changed                | The device has been connected or disconnected from the network.                                                                                                                                                                                                                                                     | INT1.4          | INT1EN.4       |

| Jabber Detected                    | The transmit interface has detected and responded to a jabber condition. See IEEE 802.3 for more information about jabber conditions.                                                                                                                                                                               | INT1.3          | INT1EN.3       |

| Auto-Negotiation Failed            | An auto-negotiation attempt has failed. Software should check for a valid link and re-try auto-negotiation.                                                                                                                                                                                                         | INT1.2          | INT1EN.2       |

| Reserved                           |                                                                                                                                                                                                                                                                                                                     |                 |                |

| Auto-Negotiation Complete          | An auto-negotiation attempt has completed. This interrupt only indicates completion, and not success. Occasionally, Auto-Negotiation attempts will not complete and/or fail; therefore, a 3 to 4 second timeout should be implemented. A successful auto-negotiation attempt is one that completes without failure. | INT1.0          | INT1EN.0       |

#### Register 5. INT0: Interrupt Status Register 0 (Self-Clearing)

| RC     | RC     | RC      | RC     | RC      | RC    | RC     | RC    | Reset Value |

|--------|--------|---------|--------|---------|-------|--------|-------|-------------|

| EOPINT | RXEINT | SELFINT | OSCINT | FLWEINT | TXINT | RXFINT | RXINT | 00000000    |

| Bit7   | Bit6   | Bit5    | Bit4   | Bit3    | Bit2  | Bit1   | Bit0  | Address:    |

|        |        |         |        |         |       |        |       | 0x63        |

Note: Reading this register will clear all INT0 interrupt flags.

Bit 7: EOPINT: End of Packet Interrupt Flag

0: The last byte of a packet has not been read since the last time EOPINT was cleared.

1: The last byte of a packet has been read.

Bit 6: RXEINT: Receive FIFO Empty Interrupt Flag

0: The receive FIFO has not been empty since the last time RXEINT was cleared.

1: The receive FIFO is empty.

Bit 5: SELFINT: Self Initialization Complete Interrupt Flag

0: Self Initialization has not completed since the last time SELFINT was cleared.

1: Self Initialization has completed.

Bit 4: OSCINT: Oscillator Initialization Complete Interrupt Flag

0: Oscillator Initialization has not completed since the last time OSCINT was cleared.

1: Oscillator Initialization has completed.

Bit 3: FLWEINT: Flash Write/Erase Operation Complete Interrupt Flag

0: A Flash write or erase operation has not completed since the last time FLWEINT was cleared.

1: A Flash write or erase operation has completed.

Bit 2: TXINT: Packet Transmitted Interrupt Flag

0: A packet transmission has not completed since the last time TXINT was cleared.

1: A packet has been transmitted.

Bit 1: RXFINT: Receive FIFO Full Interrupt Flag

0: The receive FIFO has not been full since the last time RXFINT was cleared.

1: The receive FIFO is full.

Bit 0: RXINT: Packet Received Interrupt Flag

0: A packet has not been added to the receive buffer since the last time RXINT was cleared.

1: A packet has been added to the receive buffer.

#### Register 6. INT0RD: Interrupt Status Register 0 (Read-Only)

|          |                                                                                                                                                             |                |            |                |              |               |             | , ,         |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|----------------|--------------|---------------|-------------|-------------|--|--|--|--|

| R        | R                                                                                                                                                           | R              | R          | R              | R            | R             | R           | Reset Value |  |  |  |  |

| EOPINT   | R RXEINTR                                                                                                                                                   | SELFINTR       | OSCINTR    | FLWEINTR       | TXINTR       | RXFINTR       | RXINTR      | 00000000    |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                        | Bit5           | Bit4       | Bit3           | Bit2         | Bit1          | Bit0        | Address:    |  |  |  |  |

|          |                                                                                                                                                             |                |            |                |              |               |             | 0x76        |  |  |  |  |

| Note: Re | ading this reg                                                                                                                                              | ister will not | clear INT0 | interrupt flac | ıs.          |               |             |             |  |  |  |  |

|          |                                                                                                                                                             |                |            |                | ,            |               |             |             |  |  |  |  |

| Bit 7:   | EOPINTR: E                                                                                                                                                  |                |            |                |              |               |             |             |  |  |  |  |

|          | 0: The last byte of a packet has not been read since the last time EOPIF was cleared.                                                                       |                |            |                |              |               |             |             |  |  |  |  |

|          | 1: The last byte of a packet has been read.                                                                                                                 |                |            |                |              |               |             |             |  |  |  |  |

| Bit 6:   | RXEINTR: Receive FIFO Empty Read-Only Interrupt Flag                                                                                                        |                |            |                |              |               |             |             |  |  |  |  |

|          | 0: The receive FIFO has not been empty since the last time RXFIFOE was cleared.                                                                             |                |            |                |              |               |             |             |  |  |  |  |

| Bit 5:   | 1: The receive FIFO is empty.                                                                                                                               |                |            |                |              |               |             |             |  |  |  |  |

| DIL O.   | SELFINTR: Self Initialization Complete Read-Only Interrupt Flag                                                                                             |                |            |                |              |               |             |             |  |  |  |  |

|          | <ul><li>0: Self Initialization has not completed since the last time SELFINT was cleared.</li><li>1: Self Initialization has completed.</li></ul>           |                |            |                |              |               |             |             |  |  |  |  |

| Bit 4:   |                                                                                                                                                             |                | •          | omplete Rea    | ad-Only Inte | errupt Flag   |             |             |  |  |  |  |

| D.(      | OSCINTR: Oscillator Initialization Complete Read-Only Interrupt Flag 0: Oscillator Initialization has not completed since the last time OSCINT was cleared. |                |            |                |              |               |             |             |  |  |  |  |

|          | 1: Oscillator                                                                                                                                               |                |            |                |              |               |             |             |  |  |  |  |

| Bit 3:   | FLWEINTR: Flash Write/Erase Operation Complete Read-Only Interrupt Flag                                                                                     |                |            |                |              |               |             |             |  |  |  |  |

|          | 0: A Flash write or erase operation has not completed since the last time FLWEINT was cleared.                                                              |                |            |                |              |               |             |             |  |  |  |  |

|          | 1: A Flash w                                                                                                                                                |                |            |                |              |               |             |             |  |  |  |  |

| Bit 2:   | TXINTR: Packet Transmitted Read-Only Interrupt Flag                                                                                                         |                |            |                |              |               |             |             |  |  |  |  |

|          | 0: A packet transmission has not completed since the last time TXINT was cleared.                                                                           |                |            |                |              |               |             |             |  |  |  |  |

| D'' 4    | 1: A packet h                                                                                                                                               |                |            | 0 1 1 1        | . =1         |               |             |             |  |  |  |  |

| Bit 1:   | RXFINTR: R                                                                                                                                                  |                |            |                |              | VEINT         | ام م م ما   |             |  |  |  |  |

|          | 0: The received: 1: The received:                                                                                                                           |                |            | JII SINCE THE  | iast time R  | AFINI Was (   | ciearea.    |             |  |  |  |  |

| Bit 0:   | RXINTR: Pa                                                                                                                                                  |                |            | aly Interrupt  | Flag         |               |             |             |  |  |  |  |

| טונ ט.   | 0: A packet h                                                                                                                                               |                |            |                |              | the last time | RXINT w     | as cleared  |  |  |  |  |

|          | 1: A packet h                                                                                                                                               |                |            |                |              | and lade anne | Z I CZNII W | ao diodiod. |  |  |  |  |

|          | paonor                                                                                                                                                      | 20011 44       |            | 223.10 24110   | ••           |               |             |             |  |  |  |  |

## Register 7. INT0EN: Interrupt Enable Register 0

| R/W    | R/W                                                        | R/W                | R/W          | R/W           | R/W         | R/W     | R/W    | Reset Value |  |  |  |

|--------|------------------------------------------------------------|--------------------|--------------|---------------|-------------|---------|--------|-------------|--|--|--|

| EEOPIN | T ERXEINT                                                  | ESELFINT E         | OSCINT       | EFLWEINT      | ETXINT      | ERXFINT | ERXINT | 00000000    |  |  |  |

| Bit7   | Bit6                                                       | Bit5               | Bit4         | Bit3          | Bit2        | Bit1    | Bit0   | Address:    |  |  |  |

|        |                                                            |                    |              |               |             |         |        | 0x64        |  |  |  |

|        |                                                            |                    |              |               |             |         |        |             |  |  |  |

| Bit 7: |                                                            | nable End of       |              | nterrupt      |             |         |        |             |  |  |  |

|        |                                                            | nd of Packet       | •            |               |             |         |        |             |  |  |  |

|        |                                                            | nd of Packet       |              |               |             |         |        |             |  |  |  |

| Bit 6: |                                                            |                    |              | mpty Interrup | t           |         |        |             |  |  |  |

|        |                                                            | eceive FIFO        |              | •             |             |         |        |             |  |  |  |

|        |                                                            | eceive FIFO        |              |               |             |         |        |             |  |  |  |

| Bit 5: |                                                            |                    |              | n Complete I  | nterrupt    |         |        |             |  |  |  |

|        |                                                            | elf Initialization | •            | •             |             |         |        |             |  |  |  |

|        |                                                            | elf Initializatio  |              |               |             |         |        |             |  |  |  |

| Bit 4: |                                                            |                    |              | zation Compl  |             | pt      |        |             |  |  |  |

|        | 0: Disable Oscillator Initialization Complete Interrupt.   |                    |              |               |             |         |        |             |  |  |  |

|        |                                                            |                    |              | omplete Inter | •           |         |        |             |  |  |  |

| Bit 3: |                                                            |                    |              | ase Operation |             |         |        |             |  |  |  |

|        | 0: Disable Flash Write/Erase Operation Complete Interrupt. |                    |              |               |             |         |        |             |  |  |  |

|        | 1: Enable Fl                                               | ash Write/Era      | ase Opera    | ition Complet | e Interrupt | ·<br>·• |        |             |  |  |  |

| Bit 2: | ETXINT: En                                                 | able Packet 1      | ransmitte    | d Interrupt   |             |         |        |             |  |  |  |

|        | 0: Disable Packet Transmitted Interrupt.                   |                    |              |               |             |         |        |             |  |  |  |

|        | 1: Enable Pa                                               | acket Transm       | itted Inter  | rupt.         |             |         |        |             |  |  |  |

| Bit 1: | ERXFINT: E                                                 | nable Receiv       | e FIFO F     | ull Interrupt |             |         |        |             |  |  |  |

|        | 0: Disable Receive FIFO Full Interrupt.                    |                    |              |               |             |         |        |             |  |  |  |

|        | 1: Enable Re                                               | eceive FIFO        | Full Interru | upt.          |             |         |        |             |  |  |  |

| Bit 0: |                                                            | able Packet I      |              |               |             |         |        |             |  |  |  |

|        | 0: Disable P                                               | acket Receiv       | ed Interru   | pt.           |             |         |        |             |  |  |  |

|        | 1: Enable Pa                                               | acket Receive      | ed Interrup  | ot.           |             |         |        |             |  |  |  |

#### Register 8. INT1: Interrupt Status Register 1 (Self-Clearing)

| R/W  | R/W  | RC      | RC      | RC     | RC       | RC    | RC     | Reset Value |

|------|------|---------|---------|--------|----------|-------|--------|-------------|

| _    | _    | WAKEINT | LINKINT | JABINT | Reserved | RFINT | ANCINT | 00000000    |

| Bit7 | Bit6 | Bit5    | Bit4    | Bit3   | Bit2     | Bit1  | Bit0   | Address:    |

Note: Reading this register will clear all INT1 interrupt flags.

Bits 7–6: UNUSED. Read = 00b, Write = don't care.

Bit 5: WAKEINT: "Wake-on-Lan" Interrupt Flag

0: The device has not been connected to a network since the last time WAKEINT was cleared.

1: The device has been connected to a network since the last time WAKEINT was cleared.

Bit 4: LINKINT: Link Status Changed Interrupt Flag

0: The link status has not changed since the last time LINKINT was cleared.

1: The link status has changed (device has been connected or removed from a network).

Bit 3: JABINT: Jabber Detected Interrupt Flag

0: A jabber condition has not been detected since the last time JABINT was cleared.

1: A jabber condition has been detected.

Bit 2: ANFINT: Auto-Negotiation Failed Interrupt Flag

0: Auto-Negotiation has not failed since the last time ANFINT was cleared.

1: Auto-Negotiation has failed.

Bit 1: Reserved: Read = 0.

Bit 0: ANCINT: Auto-Negotiation Complete Interrupt

0: Auto-Negotiation has not completed since the last time ANCINT was cleared.

1: Auto-Negotiation has completed.

#### Register 9. INT1RD: Interrupt Status Register 1 (Read-Only)

| R/W  | R/W  | R        | R        | R       | R       | R        | R       | Reset Value |

|------|------|----------|----------|---------|---------|----------|---------|-------------|

| _    | _    | WAKEINTR | LINKINTR | JABINTR | ANFINTR | Reserved | ANCINTR | 00000000    |

| Bit7 | Bit6 | Bit5     | Bit4     | Bit3    | Bit2    | Bit1     | Bit0    | Address:    |

|      |      |          |          |         |         |          |         | 0x7E        |

Note: Reading this register will not clear INT1 interrupt flags.

Bits 7-6: UNUSED. Read = 00b, Write = don't care.

Bit 5: WAKEINTR: "Wake-on-Lan" Read-Only Interrupt Flag

0: The device has not been connected to a network since the last time WAKEINT was cleared.

1: The device has been connected to a network since the last time WAKEINT was cleared.

Bit 4: LINKINTR: Link Status Changed Read-Only Interrupt Flag

0: The link status has not changed since the last time LINKINT was cleared.

1: The link status has changed (device has been connected or removed from a network).

Bit 3: JABINTR: Jabber Detected Read-Only Interrupt Flag

0: A jabber condition has not been detected since the last time JABINT was cleared.

1: A jabber condition has been detected.

Bit 2: ANFINTR: Auto-Negotiation Failed Read-Only Interrupt Flag

0: Auto-Negotiation has not failed since the last time ANFINT was cleared.

1: Auto-Negotiation has failed.

Bit 1: Reserved: Read = 0b.

Bit 0: ANCINTR: Auto-Negotiation Complete Read-Only Interrupt Flag

0: Auto-Negotiation has not completed since the last time ANCINT was cleared.

1: Auto-Negotiation has completed.

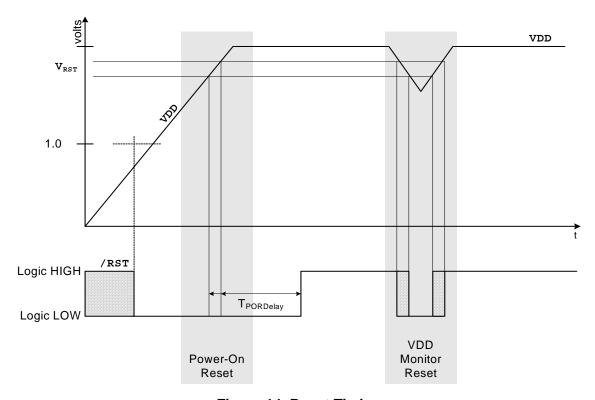

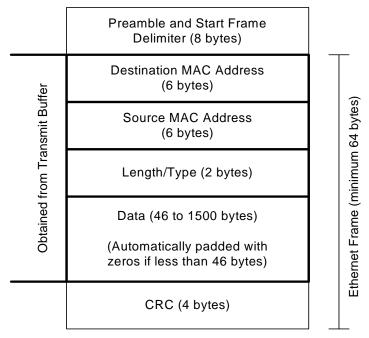

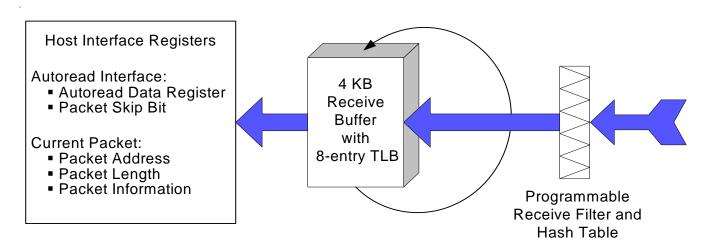

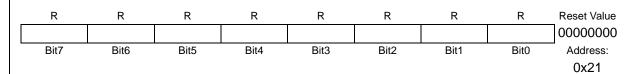

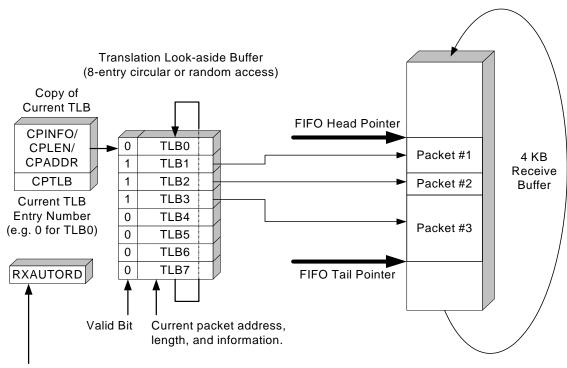

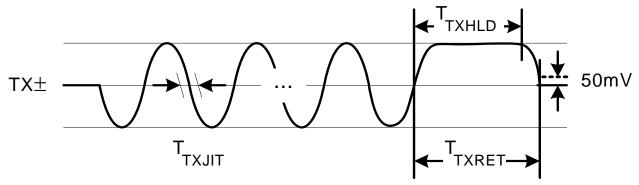

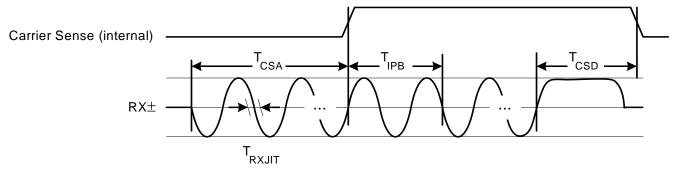

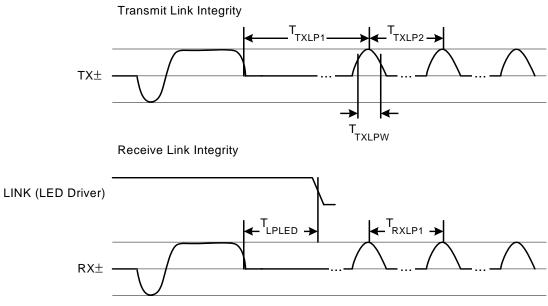

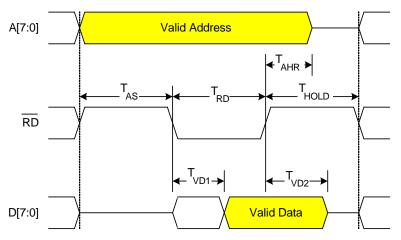

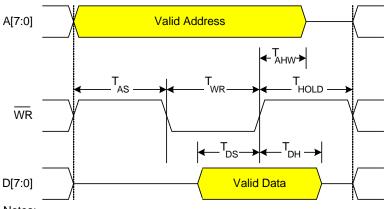

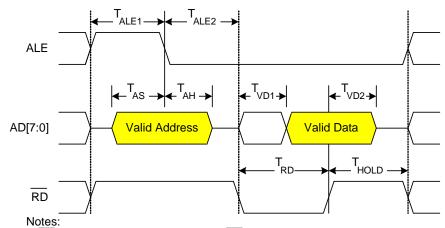

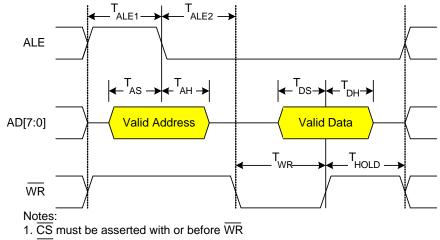

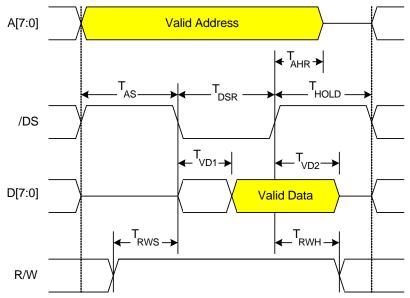

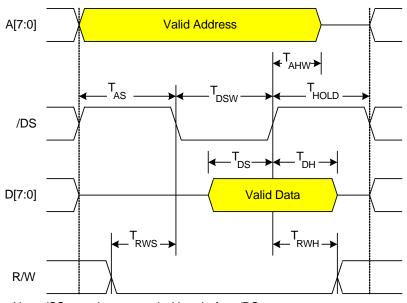

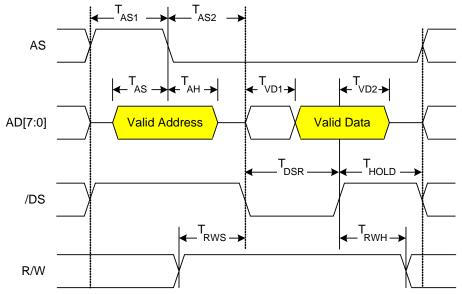

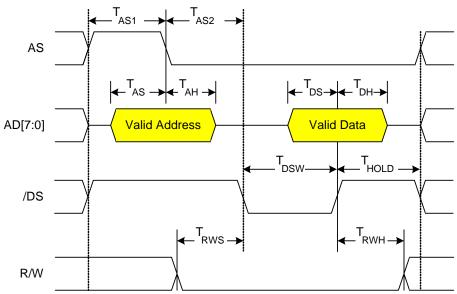

#### Register 10. INT1EN: Interrupt Enable Register 1