# Complete Low Cost 12-Bit D/A Converters

## ADDAC80/ADDAC85/ADDAC87

#### **FEATURES**

Single Chip Construction

On-Board Output Amplifier

Low Power Dissipation: 300 mW

Monotonicity Guaranteed over Temperature

Guaranteed for Operation with 12 V Supplies

Improved Replacement for Standard DAC80, DAC800

HI-5680

High Stability, High Current Output

Buried Zener Reference

Laser Trimmed to High Accuracy

1/2 LSB Max Nonlinearity

Low Cost Plastic Packaging

#### PRODUCT DESCRIPTION

The ADDAC80 Series is a family of low cost 12-bit digital-to-analog converters with both a high stability voltage reference and output amplifier combined on a single monolithic chip. The ADDAC80 Series is recommended for all low cost 12-bit D/A converter applications where reliability and cost are of paramount importance.

Advanced circuit design and precision processing techniques result in significant performance advantages over conventional DAC80 devices. Innovative circuit design reduces the total power consumption to 300 mW, which not only improves reliability, but also improves long term stability.

The ADDAC80 incorporates a fully differential, nonsaturating precision current switching cell structure which provides greatly increased immunity to supply voltage variation. This same structure also reduces nonlinearities due to thermal transients as the various bits are switched; nearly all critical components operate at constant power dissipation. High stability, SiCr thin film resistors are trimmed with a fine resolution laser, resulting in lower differential nonlinearity errors. A low noise, high stability, subsurface Zener diode is used to produce a reference voltage with excellent long term stability, high external current capability and temperature drift characteristics which challenge the best discrete Zener references.

The ADDAC80 Series is available in three performance grades and three package types. The ADDAC80 is specified for use over the 0°C to 70°C temperature range and is available in both plastic and ceramic DIP packages. The ADDAC85 and ADDAC87 are available in hermetically sealed ceramic packages and are specified for the –25°C to +85°C and –55°C to +125°C temperature ranges.

#### REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT HIGHLIGHTS

- 1. The ADDAC80 series of D/A converters directly replaces all other devices of this type with significant increases in performance.

- Single chip construction and low power consumption provides the optimum choice for applications where low cost and high reliability are major considerations.

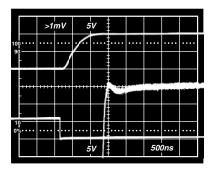

- 3. The high speed output amplifier has been designed to settle within 1/2 LSB for a 10 V full scale transition in 2.0  $\mu$ s, when properly compensated.

- 4. The precision buried Zener reference can supply up to 2.5 mA for use elsewhere in the application.

- 5. The low TC binary ladder guarantees that all units are monotonic over the specified temperature range.

- 6. System performance upgrading is possible without redesign.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

# $\label{eq:ADDAC85} \begin{tabular}{ll} ADDAC80/ADDAC85/ADDAC87-SPECIFICATIONS & (T_A=25^\circ C, rated power supplies unless otherwise noted.) \\ \end{tabular}$

| Model                                                                                                                                                                                                         | Min A              | DDAC8                                                  | 0<br>Max                                 | A<br>Min           | DDAC8              | 5<br>Max                                                | A<br>Min           | DDAC8<br>Typ       | 7<br>Max                                 | Unit                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------|------------------------------------------|--------------------|--------------------|---------------------------------------------------------|--------------------|--------------------|------------------------------------------|---------------------------------------------------------------------------|

| TECHNOLOGY                                                                                                                                                                                                    | N                  | Monolith                                               | ic                                       | Λ                  | /Ionolithi         | ic                                                      | N                  | /Ionolithi         | ic                                       |                                                                           |

| DIGITAL INPUT Binary-CBI BCD-CCD Logic Levels (TTL Compatible) V <sub>IH</sub> (Logic "1")                                                                                                                    | 2.0                |                                                        | 12<br>5.5                                | 2.0                |                    | 12<br>5.5                                               | 2.0                |                    | 12                                       | Bits<br>Digits<br>V                                                       |

| V <sub>II.</sub> (Logic "0")<br>V <sub>II.</sub> (Logic "0")<br>I <sub>IH</sub> (V <sub>IH</sub> = 5.5 V)<br>I <sub>II.</sub> (V <sub>II.</sub> = 0.8 V)                                                      | 0                  |                                                        | 0.8<br>250<br>100                        | 0                  |                    | 0.8<br>250<br>100                                       | 0                  |                    | 0.8<br>250<br>100                        | V<br>μA<br>μA                                                             |

| TRANSFER CHARACTERISTICS<br>ACCURACY<br>Linearity Error @ 25°C<br>CBI                                                                                                                                         |                    |                                                        | ±1/2                                     |                    |                    | ±1/2                                                    |                    |                    | ±1/2                                     | LSB <sup>1</sup>                                                          |

| CCD  T <sub>A</sub> @ T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                                                    |                    | ±1/4                                                   | ±1/2                                     |                    | ±1/4               | ±1/2                                                    |                    | ±1/2               | ±3/4                                     | LSB<br>LSB                                                                |

| Differential Linearity Error @ 25°C<br>CBI<br>CCD                                                                                                                                                             |                    |                                                        | ±3/4                                     |                    |                    | ±3/4                                                    |                    |                    | ±3/4                                     | LSB<br>LSB                                                                |

| $T_A @ T_{MIN}$ to $T_{MAX}$<br>Gain Error <sup>2</sup><br>Offset Error <sup>2</sup><br>Temperature Range for Guaranteed                                                                                      |                    | ±0.1<br>±0.05                                          | $\pm 3/4 \\ \pm 0.3 \\ \pm 0.15$         |                    | ±0.1<br>±0.05      | $\pm 1 \\ \pm 0.2 \\ \pm 0.1$                           |                    | ±0.1<br>±0.05      | ±1<br>±0.2<br>±0.1                       | LSB<br>%FSR <sup>3</sup><br>%FSR <sup>3</sup>                             |

| Monotonicity DRIFT ( $T_{MIN}$ to $T_{MAX}$ )                                                                                                                                                                 | 0                  |                                                        | +70                                      | -25                |                    | +85                                                     | -55                |                    | +125                                     | °C                                                                        |

| Total Bipolar Drift, max (includes gain, offset, and linearity drifts) Total Error (T <sub>MIN</sub> to T <sub>MAX</sub> ) <sup>4</sup>                                                                       |                    |                                                        | ±20                                      |                    |                    | ±20                                                     |                    |                    | ±30                                      | ppm of FSR/°C                                                             |

| Unipolar Bipolar Gain Including Internal Reference Gain Excluding Internal Reference Unipolar Offset Bipolar Offset                                                                                           |                    | $\pm 0.08$ $\pm 0.06$ $\pm 15$ $\pm 4$ $\pm 1$ $\pm 5$ | ±0.15<br>±0.10<br>±30<br>±7<br>±3<br>±10 |                    | ±0.12<br>±0.08     | $\pm 0.2$ $\pm 0.12$ $\pm 20$ $\pm 10$ $\pm 3$ $\pm 10$ |                    | ±0.18<br>±0.14     | ±0.3<br>±0.24<br>±20<br>±10<br>±3<br>±10 | % of FSR % of FSR ppm of FSR/°C ppm of FSR/°C ppm of FSR/°C ppm of FSR/°C |

| CONVERSION SPEED  Voltage Model (V) <sup>5</sup> Settling Time to $\pm 0.01\%$ of FSR for FSR Change (2 $k\Omega$  500 pF load) with 10 $k\Omega$ Feedback with 5 $k\Omega$ Feedback For LSB Change Slew Rate | 10                 | 3<br>2<br>1                                            | 4 3                                      | 10                 | 3<br>2<br>1        | 4 3                                                     | 10                 | 3<br>2<br>1        | 4 3                                      | μs<br>μs<br>μs<br>ν/μs                                                    |

| ANALOG OUTPUT<br>Voltage Models<br>Ranges-CBI                                                                                                                                                                 |                    | ±2.5, ±<br>±10, +                                      |                                          |                    | ±2.5, ±<br>±10, +  |                                                         |                    | ±2.5, ±<br>±10, +  |                                          | V<br>V                                                                    |

| -CCD Output Current Output Impedance (dc) Short Circuit Current Internal Reference Voltage (V <sub>R</sub> ) Output Impedance                                                                                 | ±5 6.23            | 0.05<br>6.3<br>1.5                                     | 40<br><b>6.3</b> 7                       | ±5 6.23            | 0.05<br>6.3<br>1.5 | 40<br><b>6.3</b> 7                                      | ±5 6.23            | 0.05<br>6.3<br>1.5 | 40<br><b>6.3</b> 7                       | V<br>V<br>mA<br>Ω<br>mA<br>V                                              |

| Max External Current <sup>6</sup> Tempco of Drift                                                                                                                                                             |                    | ±10                                                    | 2.5<br>±20                               |                    | ±10                | 2.5<br>±20                                              |                    |                    | 2.5<br>±10                               | mA<br>ppm of V <sub>R</sub> /°C                                           |

| POWER SUPPLY SENSITIVITY $\pm 15 \text{ V} \pm 10\%$ , 5 V supply when applicable $\pm 12 \text{ V} \pm 5\%$                                                                                                  |                    |                                                        | ±0.002<br>±0.002                         |                    |                    | ±0.002<br>±0.002                                        |                    |                    | ±0.002<br>±0.002                         | % of FSR/%V <sub>S</sub><br>% of FSR/%V <sub>S</sub>                      |

| POWER SUPPLY REQUIREMENTS Rated Voltages                                                                                                                                                                      |                    | ±15                                                    |                                          |                    | ±15                |                                                         |                    | ±15                |                                          | v                                                                         |

| Range Analog Supplies Logic Supplies Supply Drain                                                                                                                                                             | ±11.4 <sup>7</sup> |                                                        | ±16.5                                    | ±11.4 <sup>7</sup> |                    | ±16.5                                                   | ±11.4 <sup>7</sup> |                    | ±16.5                                    | V<br>V                                                                    |

| +12 V, +15 V<br>-12 V, -15 V                                                                                                                                                                                  |                    | 5<br>14                                                | 10<br>20                                 |                    | 5<br>14            | 10<br>20                                                |                    | 5<br>14            | 10<br>20                                 | mA<br>mA                                                                  |

|                   | ADDAC80 |     | ADDAC85 |     |     | ADDAC87 |     |     |      |      |

|-------------------|---------|-----|---------|-----|-----|---------|-----|-----|------|------|

| Model             | Min     | Typ | Max     | Min | Typ | Max     | Min | Typ | Max  | Unit |

| TEMPERATURE RANGE |         |     |         |     |     |         |     |     |      |      |

| Specifications    | 0       |     | +70     | -25 |     | +85     | -55 |     | +125 | °C   |

| Operating         | -25     |     | +85     | -55 |     | +125    | -55 |     | +125 | °C   |

| Storage           | -25     |     | +125    | -65 |     | +150    | -65 |     | +150 | °C   |

#### NOTES

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

Specifications subject to change without notice.

| Model                                                             | Min   | ADDAC8<br>Typ | 0<br>Max   | Min   | ADDAC8:    | 5<br>Max  | Min  | ADDAC8     | 37<br>Max | Unit              |

|-------------------------------------------------------------------|-------|---------------|------------|-------|------------|-----------|------|------------|-----------|-------------------|

|                                                                   | Willi |               | Max        | WIIII |            | Max       | WIII |            | Max       | Cint              |

| TECHNOLOGY                                                        |       | Hybrid        |            |       | Hybrid     |           |      | Hybrid     |           |                   |

| DIGITAL INPUT                                                     |       |               |            |       |            |           |      |            |           |                   |

| Binary-CBI                                                        |       |               | 12         |       |            | 12        |      |            | 12        | Bits              |

| BCD-CCD                                                           |       |               | 3          |       |            | 3         |      |            | 3         | Digits            |

| Logic Levels (TTL Compatible)                                     |       |               |            |       |            |           |      |            |           |                   |

| V <sub>IH</sub> (Logic "1")                                       | 2.0   |               | 5.5        | 2.0   |            | 5.5       | 2.0  |            | 5.5       | V                 |

| V <sub>IL</sub> (Logic "0")                                       | 0     |               | 0.8        | 0     |            | 0.8       | 0    | •==        | 0.8       | V                 |

| $I_{IH} (V_{IH} = 5.5 \text{ V})$                                 |       | 250           |            |       | 250        |           |      | 250        |           | μΑ                |

| $I_{IL} (V_{IL} = 0.8 \text{ V})$                                 |       | -100          |            |       | -100       |           |      | -100       |           | μΑ                |

| TRANSFER CHARACTERISTICS                                          |       |               |            |       |            |           |      |            |           |                   |

| ACCURACY                                                          |       |               |            |       |            |           |      |            |           |                   |

| Linearity Error @ 25°C                                            |       |               |            |       |            |           |      |            |           |                   |

| CBI                                                               |       | $\pm 1/4$     | $\pm 1/2$  |       |            | $\pm 1/2$ |      |            | $\pm 1/2$ | LSB <sup>1</sup>  |

| CCD                                                               |       | $\pm 1/8$     | $\pm 1/4$  |       |            | $\pm 1/4$ |      |            | $\pm 1/4$ | LSB               |

| $T_A @ T_{MIN}$ to $T_{MAX}$                                      |       | $\pm 1/4$     | $\pm 1/2$  |       | $\pm 1/4$  | $\pm 1/2$ |      | $\pm 1/2$  | $\pm 1/2$ | LSB               |

| Differential Linearity Error @ 25°C                               |       |               |            |       |            |           |      |            |           |                   |

| CBI                                                               |       | $\pm 1/2$     | $\pm 3/4$  |       | $\pm 1/2$  |           |      | $\pm 1/2$  |           | LSB               |

| CCD                                                               |       | $\pm 1/4$     | $\pm 1/2$  |       | $\pm 1/2$  |           |      | $\pm 1/2$  |           | LSB               |

| $\mathrm{T_A} \mathbin{@} \mathrm{T_{MIN}}$ to $\mathrm{T_{MAX}}$ |       |               | $\pm 1$    |       |            | ±1        |      |            | ±1        | LSB               |

| Gain Error <sup>2</sup>                                           |       | $\pm 0.1$     | $\pm 0.3$  |       | $\pm 0.1$  |           |      | $\pm 0.1$  |           | %FSR <sup>3</sup> |

| Offset Error <sup>2</sup>                                         |       | $\pm 0.05$    | $\pm 0.15$ |       | $\pm 0.05$ |           |      | $\pm 0.05$ |           | %FSR <sup>3</sup> |

| Temperature Range for Guaranteed                                  |       |               |            |       |            |           |      |            |           |                   |

| Monotonicity                                                      | 0     |               | +70        | 0     |            | +70       | -25  |            | +85       | °C                |

| DRIFT ( $T_{MIN}$ to $T_{MAX}$ )                                  |       |               |            |       |            |           |      |            |           |                   |

| Total Bipolar Drift, max (includes gain,                          |       |               |            |       |            |           |      |            |           |                   |

| offset, and linearity drifts)                                     |       |               | ±20        |       |            |           |      |            |           | ppm of FSR/°C     |

| Total Error $(T_{MIN} \text{ to } T_{MAX})^4$                     |       |               |            |       |            |           |      |            |           | 0/ 0700           |

| Unipolar                                                          |       | ±0.08         | ±0.15      |       |            |           |      |            |           | % of FSR          |

| Bipolar                                                           |       | $\pm 0.06$    | $\pm 0.10$ |       |            |           |      |            |           | % of FSR          |

| Gain                                                              |       |               |            |       |            |           |      |            |           | CECD/OC           |

| Including Internal Reference                                      |       | ±15           | ±30        |       |            | ±20       |      |            | ±20       | ppm of FSR/°C     |

| Excluding Internal Reference                                      |       | ±5            | ±7         |       |            | ±10       |      |            | ±10       | ppm of FSR/°C     |

| Unipolar Offset                                                   |       | ±1<br>±5      | ±3         |       | ±1         | 110       |      | ±1         | 110       | ppm of FSR/°C     |

| Bipolar Offset                                                    |       | Ξ)            | ±10        |       |            | ±10       |      |            | ±10       | ppm of FSR/°C     |

| CONVERSION SPEED                                                  |       |               |            |       |            |           |      |            |           |                   |

| Voltage Model (V) <sup>5</sup>                                    |       |               |            |       |            |           |      |            |           |                   |

| Settling Time to $\pm 0.01\%$ of FSR for                          |       |               |            |       |            |           |      |            |           |                   |

| FSR Change (2 $k\Omega$   500 pF load)                            |       |               |            |       |            |           |      |            |           |                   |

| with 10 kΩ Feedback                                               |       | 5             |            |       | 5          |           |      | 5          |           | μs                |

| with 5 k $\Omega$ Feedback                                        |       | 3             |            |       | 3          |           |      | 3          |           | μs                |

| For LSB Change                                                    |       | 1.5           |            |       | 1.5        |           |      | 1.5        |           | μs                |

| Slew Rate                                                         | 10    | 15            |            |       | 20         |           |      | 20         |           | V/µs              |

| Current Model (I)                                                 |       |               |            |       |            |           |      |            |           |                   |

| Settling time to $\pm 0.01\%$ of FSR for                          |       |               |            |       |            |           |      |            |           |                   |

| FSR Change                                                        |       |               |            |       |            |           |      |            |           |                   |

| 10 Ω to 100 Ω Load                                                |       | 300           |            |       | 300        |           |      | 300        |           | ns                |

| for 1 k $\Omega$                                                  |       | 1             |            |       | 1          |           |      | 1          |           | μs                |

REV. B -3-

<sup>&</sup>lt;sup>1</sup>Least Significant Bit.

<sup>&</sup>lt;sup>2</sup>Adjustable to zero with external trim potentiometer. <sup>3</sup>FSR means "Full Scale Range" and is 20 V for the  $\pm 10$  V range and 10 V for the  $\pm 5$  V range.

<sup>&</sup>lt;sup>4</sup>Gain and offset errors adjusted to zero at 25°C.

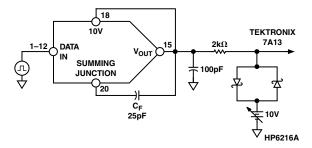

$<sup>{}^{5}</sup>C_{F} = 0$ , see Figure 3a.

<sup>&</sup>lt;sup>6</sup>Maximum with no degradation of specification, must be a constant load.

$<sup>^{7}</sup>$ A minimum of  $\pm 12.3$  V is required for a  $\pm 10$  V full scale output and  $\pm 11.4$  V is required for all other voltage ranges.

# ADDAC80/ADDAC85/ADDAC87—SPECIFICATIONS (continued)

| Model                                            | Min     | ADDAC<br>Typ | C80<br>Max | Min     | ADDAC<br>Typ | 85<br>Max | Min     | ADDAC<br>Typ | 87<br>Max | Unit                      |

|--------------------------------------------------|---------|--------------|------------|---------|--------------|-----------|---------|--------------|-----------|---------------------------|

|                                                  | IVIII   | Тур          | Max        | Willi   | Тур          | Max       | WIII    | Тур          | Max       | Cint                      |

| ANALOG OUTPUT                                    |         |              |            |         |              |           |         |              |           |                           |

| Voltage Models                                   |         |              |            |         |              |           |         |              |           |                           |

| Ranges-CBI                                       |         | ±2.5,        | -          |         | ±2.5,        | -         |         | ±2.5, =      |           |                           |

|                                                  |         | ±10, +       | -5,        |         | ±10, +       | -5,       |         | ±10, +       | .5,       | ***                       |

| D COD                                            |         | +10          |            |         | +10          |           |         | +10          |           | V                         |

| Ranges-CCD                                       | 1       | ±10          |            |         | +10          |           |         | +10          |           | V                         |

| Output Current                                   | ±5      | 0.05         |            | ±5      | 0.05         |           | ±5      | 0.05         |           | mA                        |

| Output Impedance (dc)                            |         | 0.05         |            |         | 0.05         |           | T 1 C   | 0.05         |           | Ω                         |

| Short Circuit Duration                           | Indefin | ite to Cor   | nmon       | Indefin | te to Cor    | nmon      | Indefin | ite to Cor   | nmon      |                           |

| Current Models                                   |         | 2.0          |            |         | 2.0          |           |         | 2.0          |           |                           |

| Ranges-Unipolar                                  |         | -2.0         |            |         | -2.0         |           |         | -2.0         |           | mA                        |

| Ranges-Bipolar                                   |         | $\pm 1.0$    |            |         | $\pm 1.0$    |           |         | $\pm 1.0$    |           | mA                        |

| Output Impedance                                 |         |              |            |         |              |           |         |              |           | 1.0                       |

| Bipolar                                          |         | 3.2          |            |         | 3.2          |           |         | 3.2          |           | kΩ                        |

| Unipolar                                         |         | 6.6          |            |         | 6.6          |           |         | 6.6          |           | kΩ                        |

| Compliance                                       | l       | -1.5, +      |            |         | -2.5,        |           |         | –2.5, +      |           | V                         |

| Internal Reference Voltage (V <sub>R</sub> )     | 6.17    | 6.3          | 6.43       | 6.17    | 6.3          | 6.43      | 6.17    | 6.3          | 6.43      | V                         |

| Output Impedance                                 |         | 1.5          |            |         | 1.5          |           |         | 1.5          |           | Ω                         |

| Max External Current <sup>6</sup>                |         |              | 2.5        |         |              | 2.5       |         |              | 2.5       | mA                        |

| Tempco of Drift                                  |         | ±10          | ±20        |         | ±10          | ±20       |         | ±10          | ±20       | ppm of V <sub>R</sub> /°C |

| POWER SUPPLY SENSITIVITY                         |         |              |            |         |              |           |         |              |           |                           |

| $\pm 15~V \pm 10\%$ , 5 V Supply When Applicable |         | $\pm 0.002$  | 2          |         | $\pm 0.002$  | 2         |         | $\pm 0.002$  | 2         | % of FSR/%V <sub>S</sub>  |

| POWER SUPPLY REQUIREMENTS                        |         |              |            |         |              |           |         |              |           |                           |

| Rated Voltages                                   |         | ±15, +       | -5         |         | ±15, +       | -5        |         | ±15, +       | ·5        | V                         |

| Range                                            |         |              |            |         |              |           |         |              |           |                           |

| Analog Supplies                                  | ±14     |              | ±16        | ±14.5   |              | ±15.5     | ±14.5   |              | ±15.5     | V                         |

| Logic Supplies                                   | 4.5     |              | 16         | 4.5     |              | 15.5      | 4.5     |              | 15.5      | V                         |

| Supply Drain <sup>7</sup>                        |         |              |            |         |              |           |         |              |           |                           |

| +15 V                                            |         | 10           | 20         |         | 15           | 20        |         | 15           | 20        | mA                        |

| −15 V                                            |         | 20           | 35         |         | 25           | 30        |         | 25           | 30        | mA                        |

| +5 V <sup>8</sup>                                |         | 8            | 20         |         | 15           | 20        |         | 15           | 20        | mA                        |

| TEMPERATURE RANGE                                |         |              |            |         |              |           |         |              |           |                           |

| Specifications                                   | 0       |              | +70        | 0       |              | +70       | -25     |              | +85       | °C                        |

| Operating                                        | -25     |              | +85        | -25     |              | +85       | -55     |              | +125      | l ∘c                      |

| Storage                                          | -55     |              | +130       | -65     |              | +150      | -65     |              | +150      | l ∘c                      |

Specifications subject to change without notice.

REV. B -4-

<sup>&</sup>lt;sup>1</sup>Least Significant Bit.

<sup>&</sup>lt;sup>2</sup>Adjustable to zero with external trim potentiometer.

$<sup>^3</sup>$ FSR means "Full Scale Range" and is 20 V for the  $\pm 10$  V range and 10 V for the  $\pm 5$  V range.  $^4$ Gain and offset errors adjusted to zero at 25 °C.

$<sup>{}^{5}</sup>C_{F} = 0$ , see Figure 3a.

<sup>&</sup>lt;sup>6</sup>Maximum with no degradation of specification, must be a constant load. <sup>7</sup>Including 5 mA load.

<sup>&</sup>lt;sup>8</sup>5 V supply required only for CCD versions.

| Model                                                                                         | ADDAC85LD<br>Min Typ Max     | ADDAC85MIL<br>Min Typ Max    | ADDAC87<br>Min Typ Max       | Unit                                           |

|-----------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------------------------|

| TECHNOLOGY                                                                                    | Hybrid                       | Hybrid                       | Hybrid                       |                                                |

| DIGITAL INPUT                                                                                 |                              |                              |                              |                                                |

| Binary-CBI                                                                                    | 12                           | 12                           | 12                           | Bits                                           |

| BCD-CCD                                                                                       |                              |                              |                              | Digits                                         |

| Logic Levels (TTL Compatible)                                                                 |                              |                              |                              |                                                |

| V <sub>IH</sub> (Logic "1")                                                                   | 2.0 5.5                      | 2.0 5.5                      | 2.0 5.5                      | V                                              |

| V <sub>IL</sub> (Logic "0")                                                                   | 0 0.8                        | 0 0.8                        | 0 0.8                        | V                                              |

| $I_{IH} (V_{IH} = 5.5 \text{ V})$<br>$I_{IL} (V_{IL} = 0.8 \text{ V})$                        | 250<br>-100                  | 250<br>-100                  | 250<br>-100                  | μA<br>μA                                       |

| TRANSFER CHARACTERISTICS                                                                      | 100                          | 100                          | 100                          | - Pu 1                                         |

| ACCURACY                                                                                      |                              |                              |                              |                                                |

| Linearity Error @ 25°C                                                                        |                              |                              |                              |                                                |

| CBI                                                                                           | ±1/2                         | ±1/2                         | $\pm 1/4$ $\pm 1/2$          | LSB <sup>1</sup>                               |

| CCD                                                                                           |                              |                              |                              | LSB                                            |

| $\mathrm{T_A} @ \mathrm{T_{MIN}}$ to $\mathrm{T_{MAX}}$                                       | ±1/2                         | ±3/4                         | ±3/4                         | LSB                                            |

| Differential Linearity Error @ 25°C                                                           |                              |                              |                              | T 0D                                           |

| CBI                                                                                           | ±1/2                         | ±1/2                         | ±1/2                         | LSB                                            |

| $\stackrel{	ext{CCD}}{	ext{T}_{	ext{A}} @ 	ext{T}_{	ext{MIN}} 	ext{ to } 	ext{T}_{	ext{MAX}}$ | ±1                           | ±1                           | ±1                           | LSB<br>LSB                                     |

| Gain Error <sup>2</sup>                                                                       | ±0.1                         | ±0.1                         | $\pm 0.1$ $\pm 0.2$          | %FSR <sup>3</sup>                              |

| Offset Error <sup>2</sup>                                                                     | ±0.05                        | ±0.05                        | ±0.05 ±0.1                   | %FSR <sup>3</sup>                              |

| Temperature Range for Guaranteed                                                              |                              |                              |                              |                                                |

| Monotonicity                                                                                  | -25 +85                      | -55 +125                     | -55 +125                     | °C                                             |

| DRIFT $(T_{MIN} \text{ to } T_{MAX})$                                                         |                              |                              |                              |                                                |

| Total Bipolar Drift, max (includes gain, offset, and linearity drifts)                        |                              |                              | ±15 ±20                      | ppm of FSR/°C                                  |

| Total Error $(T_{MIN} \text{ to } T_{MAX})^4$                                                 |                              |                              | ±15 ±30                      | ppin of rsk/ C                                 |

| Unipolar                                                                                      |                              |                              | ±0.13 ±0.30                  | % of FSR                                       |

| Bipolar                                                                                       |                              |                              | ±0.12 ±0.24                  | % of FSR                                       |

| Gain                                                                                          |                              |                              |                              |                                                |

| Including Internal Reference                                                                  | ±10                          | ±20                          | ±10 ±25                      | ppm of FSR/°C                                  |

| Excluding Internal Reference                                                                  |                              |                              | ±5 ±10                       | ppm of FSR/°C                                  |

| Unipolar Offset                                                                               | ±1                           | ±2                           | ±1 ±3                        | ppm of FSR/°C                                  |

| Bipolar Offset                                                                                | ±5                           | ±10                          | ±5 ±10                       | ppm of FSR/°C                                  |

| CONVERSION SPEED                                                                              |                              |                              |                              |                                                |

| Voltage Model (V) <sup>5</sup>                                                                |                              |                              |                              |                                                |

| Settling Time to $\pm 0.01\%$ of FSR for FSR change (2 k $\Omega$   500 pF load)              |                              |                              |                              |                                                |

| with 10 k $\Omega$ Feedback                                                                   | 5                            | 5                            | 5                            | 110                                            |

| with 5 kΩ Feedback                                                                            | 3                            | 3                            | 3                            | μs<br>μs                                       |

| For LSB Change                                                                                | 1.5                          | 1.5                          | 1.5                          | μs                                             |

| Slew Rate                                                                                     | 20                           | 20                           | 20                           | V/µs                                           |

| Current Model (I)                                                                             |                              |                              |                              |                                                |

| Settling Time to $\pm 0.01\%$ of FSR                                                          |                              |                              |                              |                                                |

| for FSR Change                                                                                | 200                          | 200                          | 200                          |                                                |

| 10 Ω to 100 Ω Load<br>for 1 kΩ                                                                | 300                          | 300                          | 300                          | ns<br>μs                                       |

| ·                                                                                             | •                            | + -                          | 1                            | μω                                             |

| ANALOG OUTPUT Voltage Models                                                                  |                              |                              |                              |                                                |

| Ranges-CBI                                                                                    | ±2.5, ±5,                    | $\pm 2.5, \pm 5,$            | ±2.5, ±5,                    |                                                |

| 8 0                                                                                           | ±10, +5,                     | ±10, +5,                     | ±10, +5,                     |                                                |

|                                                                                               | +10                          | +10                          | +10                          | V                                              |

| -CCD                                                                                          | l                            | 1                            |                              | V .                                            |

| Output Current                                                                                | ±5                           | ±5                           | ±5                           | mA                                             |

| Output Impedance (dc) Short Circuit Duration                                                  | 0.05<br>Indefinite to Common | 0.05<br>Indefinite to Common | 0.05<br>Indefinite to Common | Ω                                              |

| Current Models                                                                                | indennite to Common          | indefinite to Common         | midemine to Common           |                                                |

| Ranges-Unipolar                                                                               | -2.0                         | -2.0                         | -2.0                         | mA                                             |

| -Bipolar                                                                                      | ±1.0                         | ±1.0                         | ±1.0                         | mA                                             |

| Output Impedance                                                                              |                              |                              |                              |                                                |

| Bipolar                                                                                       | 3.2                          | 3.2                          | 2.5 3.2 4.1                  | kΩ                                             |

| Unipolar                                                                                      | 6.6                          | 6.6                          | 5.0 6.6 8.2                  | kΩ                                             |

| Compliance<br>Internal Reference Voltage (V <sub>R</sub> )                                    | -2.5, +10                    | -2.5, +10                    | -1.5, +10                    | V                                              |

| Output Impedance                                                                              | 6.17 6.3 6.43                | 6.17 6.3 6.43                | 6.17 6.3 6.43<br>1.5         | $\begin{array}{ c c } V \\ \Omega \end{array}$ |

| Max External Current <sup>6</sup>                                                             | 2.5                          | 2.5                          | 2.5                          | mA                                             |

| Tempco of Drift                                                                               | ±10 ±20                      | ±10 ±20                      | ±5 ±10                       | ppm of V <sub>R</sub> /°C                      |

| POWER SUPPLY SENSITIVITY                                                                      |                              |                              |                              |                                                |

| $\pm 15 \text{ V} \pm 10\%$ , 5 V supply when applicable                                      | ±0.002                       | ±0.002                       | ±0.002 ±0.003                | % of FSR/%V <sub>S</sub>                       |

|                                                                                               |                              |                              |                              |                                                |

REV. B -5-

# ADDAC80/ADDAC85/ADDAC87—SPECIFICATIONS (continued)

|                           |       | DAC85       |       |       | DAC85 |       | 1     | DDAC  |            | ** •. |

|---------------------------|-------|-------------|-------|-------|-------|-------|-------|-------|------------|-------|

| Model                     | Min   | Тур         | Max   | Min   | Тур   | Max   | Min   | Тур   | Max        | Unit  |

| POWER SUPPLY REQUIREMENTS |       |             |       |       |       |       |       |       |            |       |

| Rated Voltages            |       | $\pm 15, 5$ | ;     |       | ±15,5 | 5     |       | ±15,5 |            | V     |

| Range                     |       |             |       |       |       |       |       |       |            |       |

| Analog Supplies           | ±14.5 |             | ±15.5 | ±14.5 |       | ±15.5 | ±13.5 |       | $\pm 16.5$ | V     |

| Logic Supplies            | +4.5  |             | ±15.5 | +4.5  |       | +15.5 | +4.5  |       | $\pm 16.5$ | V     |

| Supply Drain <sup>7</sup> |       |             |       |       |       |       |       |       |            |       |

| +15 V                     |       | 15          | 20    |       | 15    | 20    |       | 10    | 20         | mA    |

| −15 V                     |       | 25          | 30    |       | 25    | 30    |       | 20    | 35         | mA    |

| +5 V <sup>8</sup>         |       | 15          | 20    |       | 15    | 20    |       | 10    | 20         | mA    |

| TEMPERATURE RANGE         |       |             |       |       |       |       |       |       |            |       |

| Specification             | -25   |             | +85   | -55   |       | +125  | -55   |       | +125       | °C    |

| Operating                 | -55   |             | +125  | -55   |       | +125  | -55   |       | +125       | °C    |

| Storage                   | -55   |             | +125  | -55   |       | +125  | -65   |       | +150       | °C    |

#### NOTES

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS

| $+V_S$ to Power Ground 0 V to +18 V                         |

|-------------------------------------------------------------|

| $-V_S$ to Power Ground 0 V to $-18$ V                       |

| Digital Inputs (Pins 1 to 12) to Power Ground               |

| 1.0 V to +7 V                                               |

| Ref In to Reference Ground $\pm 12~V$                       |

| Bipolar Offset to Reference Ground ±12 V                    |

| 10 V Span R to Reference Ground ±12 V                       |

| 20 V Span R to Reference Ground $\ \ \ \ \ \pm 24 \ V$      |

| Ref Out Indefinite Short to Power Ground or +V <sub>s</sub> |

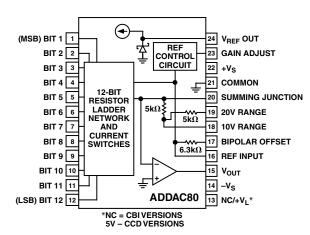

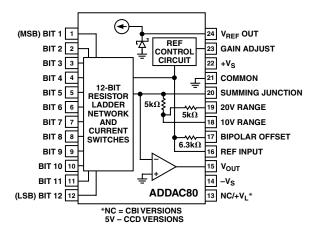

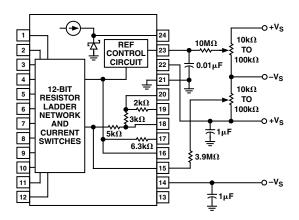

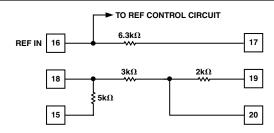

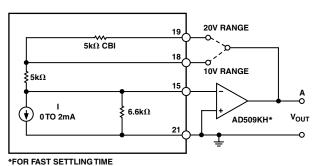

Figure 1. Voltage Model Function Diagram and Pin Configuration

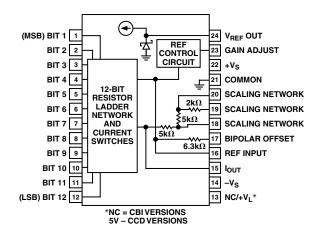

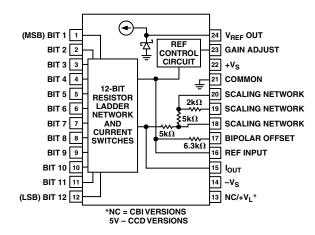

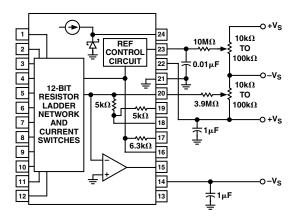

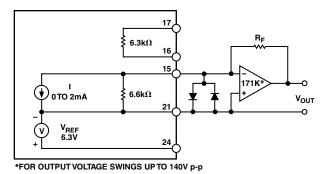

Figure 2. Current Model Functional Diagram and Pin Configuration

-6- REV. B

<sup>&</sup>lt;sup>1</sup>Least Significant Bit.

<sup>&</sup>lt;sup>2</sup>Adjustable to zero with external trim potentiometer.

$<sup>^3</sup>FSR$  means "Full-Scale Range" and is 20 V for the  $\pm 10$  V range and 10 V for the  $\pm 5$  V range.

<sup>&</sup>lt;sup>4</sup>Gain and offset errors adjusted to zero at 25°C.

$<sup>{}^5</sup>C_F = 0$ , see Figure 3a.

<sup>&</sup>lt;sup>6</sup>Maximum with no degradation of specification, must be a constant load.

<sup>&</sup>lt;sup>7</sup>Including 5 mA load.

<sup>&</sup>lt;sup>8</sup>5 V supply required only for CCD versions.

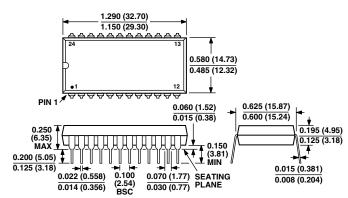

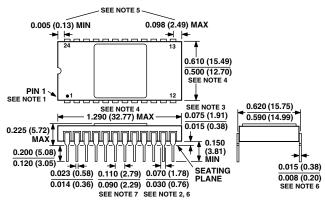

#### **ORDERING GUIDE**

| Model                         | Input<br>Code        | Output<br>Mode | Technology | Temperature<br>Range | Linearity<br>Error | Package<br>Option <sup>1</sup> |

|-------------------------------|----------------------|----------------|------------|----------------------|--------------------|--------------------------------|

| ADDAC80N-CBI-V                | Binary               | Voltage        | Monolithic | 0°C to 70°C          | ±1/2 LSB           | N-24A                          |

| ADDAC80D-CBI-V                | Binary               | Voltage        | Monolithic | 0°C to 70°C          | ±1/2 LSB           | D-24                           |

| ADDAC85D-CBI-V                | Binary               | Voltage        | Monolithic | −25°C to +85°C       | ±1/2 LSB           | D-24                           |

| ADDAC87D-CBI-V                | Binary               | Voltage        | Monolithic | −55°Cto +125°C       | ±1/2 LSB           | D-24                           |

| ADDAC80-CBI-V                 | Binary               | Voltage        | Hybrid     | 0°C to 70°C          | ±1/2 LSB           | DH-24A                         |

| ADDAC80-CBI-I                 | Binary               | Current        | Hybrid     | 0°C to 70°C          | ±1/2 LSB           | DH-24A                         |

| ADDAC80-CCD-V                 | Binary Coded Decimal | Voltage        | Hybrid     | 0°C to 70°C          | ±1/4 LSB           | DH-24A                         |

| ADDAC80-CCD-I                 | Binary Coded Decimal | Current        | Hybrid     | 0°C to 70°C          | ±1/4 LSB           | DH-24A                         |

| ADDAC80Z-CBI-V <sup>2</sup>   | Binary               | Voltage        | Hybrid     | 0°C to 70°C          | ±1/2 LSB           | DH-24A                         |

| ADDAC80Z-CBI-I <sup>2</sup>   | Binary               | Current        | Hybrid     | 0°C to 70°C          | ±1/2 LSB           | DH-24A                         |

| ADDAC80Z-CCD-V <sup>2</sup>   | Binary Coded Decimal | Voltage        | Hybrid     | 0°C to 70°C          | ±1/4 LSB           | DH-24A                         |

| ADDAC80Z-CCD-I <sup>2</sup>   | Binary Coded Decimal | Current        | Hybrid     | 0°C to 70°C          | ±1/4 LSB           | DH-24A                         |

| ADDAC85C-CBI-V <sup>3</sup>   | Binary               | Voltage        | Hybrid     | 0°C to 70°C          | ±1/2 LSB           | DH-24A                         |

| ADDAC85C-CBI-I                | Binary               | Current        | Hybrid     | 0°C to 70°C          | ±1/2 LSB           | DH-24A                         |

| ADDAC85-CBI-V <sup>3</sup>    | Binary               | Voltage        | Hybrid     | −25°C to +85°C       | ±1/2 LSB           | DH-24A                         |

| ADDAC85-CBI-I <sup>3</sup>    | Binary               | Current        | Hybrid     | −25°C to +85°C       | ±1/2 LSB           | DH-24A                         |

| ADDAC85LD-CBI-V <sup>3</sup>  | Binary               | Voltage        | Hybrid     | −25°C to +85°C       | ±1/2 LSB           | DH-24A                         |

| ADDAC85LD-CBI-I <sup>3</sup>  | Binary               | Current        | Hybrid     | −25°C to +85°C       | ±1/2 LSB           | DH-24A                         |

| ADDAC85MIL-CBI-V <sup>3</sup> | Binary               | Voltage        | Hybrid     | −55°C to +125°C      | ±1/2 LSB           | DH-24A                         |

| ADDAC85MIL-CBI-I <sup>3</sup> | Binary               | Current        | Hybrid     | −55°C to +125°C      | ±1/2 LSB           | DH-24A                         |

| ADDAC85C-CCD-V <sup>3</sup>   | Binary Coded Decimal | Voltage        | Hybrid     | 0°C to 70°C          | ±1/4 LSB           | DH-24A                         |

| ADDAC85C-CCD-I <sup>3</sup>   | Binary Coded Decimal | Current        | Hybrid     | 0°C to 70°C          | ±1/4 LSB           | DH-24A                         |

| ADDAC85-CCD-V <sup>3</sup>    | Binary Coded Decimal | Voltage        | Hybrid     | −25°C to +85°C       | ±1/4 LSB           | DH-24A                         |

| ADDAC85-CCD-I <sup>3</sup>    | Binary Coded Decimal | Current        | Hybrid     | −25°C to +85°C       | ±1/4 LSB           | DH-24A                         |

| ADDAC85MILCBII8               | Binary               | Current        | Hybrid     | −55°C to +125°C      | ±1/2 LSB           | DH-24A                         |

| ADDAC85MILCBIV8               | Binary               | Voltage        | Hybrid     | −55°C to +125°C      | ±1/2 LSB           | DH-24A                         |

| ADDAC87-CBI-V <sup>3</sup>    | Binary               | Voltage        | Hybrid     | −55°C to +125°C      | ±1/2 LSB           | DH-24A                         |

| ADDAC87-CBI-I <sup>3</sup>    | Binary               | Current        | Hybrid     | −55°C to +125°C      | ±1/2 LSB           | DH-24A                         |

| ADDAC87-CBII883               | Binary               | Current        | Hybrid     | −55°C to +125°C      | ±1/2 LSB           | DH-24A                         |

| ADDAC87-CBIV883               | Binary               | Voltage        | Hybrid     | −55°C to +125°C      | ±1/2 LSB           | DH-24A                         |

NOTES

#### PRODUCT OFFERING

Analog Devices has developed a number of technologies to support products within the data acquisition market. In serving the market new products are implemented with the technology best suited to the application. The DAC80 series of products was first implemented in hybrid form and now it is available in a single monolithic chip. We will provide both the hybrid and monolithic versions of the family so that in existing designs changes to documentation or product qualification will not have to be done. Specifications and ordering information for both versions are delineated in this data sheet.

#### **DIGITAL INPUT CODES**

The ADDAC80 Series accepts complementary digital input code in binary (CBI) format. The CBI model may be connected by the user for anyone of three complementary codes: CSB, COB or CTC.

Table I. Digital Input Codes

| Digital                                  | Input | Analog Input                                       |                                              |                                              |  |  |  |  |  |

|------------------------------------------|-------|----------------------------------------------------|----------------------------------------------|----------------------------------------------|--|--|--|--|--|

| MSB LSB                                  |       | CSB<br>Compl.<br>Straight<br>Binary                | COB<br>Compl.<br>Offset<br>Binary            | CTC* Compl. Two's Compl.                     |  |  |  |  |  |

| 0000000<br>0111111<br>1000000<br>1111111 | 11111 | +Full-Scale<br>+1/2 Full-Scale<br>Midscale<br>Zero | +Full-Scale<br>Zero<br>-1 LSB<br>-Full-Scale | -1 LSB<br>-Full-Scale<br>+Full-Scale<br>Zero |  |  |  |  |  |

<sup>\*</sup>Invert the MSB of the COB code with an external inverter to obtain CTC code.

REV. B -7-

<sup>&</sup>lt;sup>1</sup>For outline information see Package Information section.

$<sup>^2</sup>$ Z-Suffix devices guarantee performance of 0 V to +5 V and  $\pm 5$  V spans with minimum supply voltages of  $\pm 11.4$  V.

<sup>&</sup>lt;sup>3</sup>These models have been discontinued. This is for historical information only.

#### **ACCURACY**

Accuracy error of a D/A converter is the difference between the analog output that is expected when a given digital code is applied and the output that is actually measured with that code applied to the converter. Accuracy error can be caused by gain error, zero error, linearity error, or any combination of the three. Of these three specifications, the linearity error specification is the most important since it cannot be corrected. Linearity error is specified over its entire temperature range. This means that the analog output will not vary by more than its maximum specification, from an ideal straight line drawn between the end points (inputs all "1"s and all "0"s) over the specified temperature range.

Differential linearity error of a D/A converter is the deviation from an ideal 1 LSB voltage change from one adjacent output state to the next. A differential linearity error specification of  $\pm 1/2$  LSB means that the output voltage step sizes can range from 1/2 LSB to 1 1/2 LSB when the input changes from one adjacent input state to the next.

#### DRIFT Gain Drift

A measure of the change in the full scale range output over temperature expressed in parts per million of full scale range per °C (ppm of FSR/°C). Gain drift is established by: 1) testing the end point differences for each ADDAC80 model at the lowest operating temperature, 25°C and the highest operating temperature; 2) calculating the gain error with respect to the 25°C value and; 3) dividing by the temperature change.

#### Offset Drift

A measure of the actual change in output with all "1"s on the input over the specified temperature range. The maximum change in offset is referenced to the offset at 25°C and is divided by the temperature range. This drift is expressed in parts per million of full scale range per °C (ppm of FSR/°C).

#### **SETTLING TIME**

Settling time for each model is the total time (including slew time) required for the output to settle within an error band around its final value after a change in input.

#### **Voltage Output Models**

Three settling times are specified to 0.01% of full scale range (FSR); two for maximum full scale range changes of 20 V, 10 V and one for a 1 LSB change. The 1 LSB change is measured at the major carry (0 1 1 1 . . . 1 1 to 1 0 0 0 . . . 0 0), the point at which the worst case settling time occurs. The settling time characteristic depends on the compensation capacitor selected, the optimum value is 25 pF as shown in Figure 3a.

#### **Current Output Models**

Two settling times are specified to  $\pm 0.01\%$  of FSR. Each is given for current models connected with two different resistive loads:  $10~\Omega$  to  $100~\Omega$  and  $1000~\Omega$  to  $1875~\Omega$ . Internal resistors are provided for connecting nominal load resistances of approximately  $1000~\Omega$  to  $1800~\Omega$  for output voltage ranges of  $\pm 1~V$  and 0~V to -2~V.

Figure 3a. Voltage Model Settling Time Circuit

Figure 3b. Voltage Model Settling Time  $C_F = 25 pF$

#### **POWER SUPPLY SENSITIVITY**

Power supply sensitivity is a measure of the effect of a power supply change on the D/A converter output. It is defined as a percent of FSR per percent of change in either the positive or negative supplies about the nominal power supply voltages.

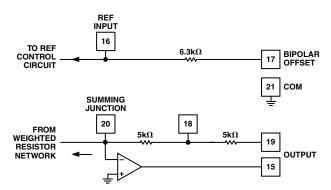

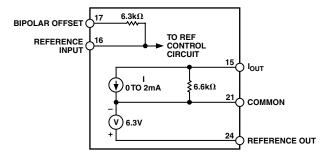

#### REFERENCE SUPPLY

All models are supplied with an internal 6.3 V reference voltage supply. This voltage (Pin 24) is accurate to  $\pm 1\%$  and must be connected to the Reference Input (Pin 16) for specified operation. This reference may also be used externally with external current drain limited to 2.5 mA. An external buffer amplifier is recommended if this reference is to be used to drive other system components. Otherwise, variations in the load driven by the reference will result in gain variations. All gain adjustments should be made under constant load conditions.

# ANALYZING DEVICE ACCURACY OVER THE TEMPERATURE RANGE

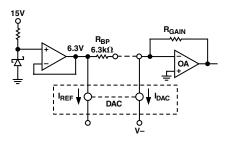

For the purposes of temperature drift analysis, the major device components are shown in Figure 4. The reference element and buffer amplifier drifts are combined to give the total reference temperature coefficient. The input reference current to the DAC,  $I_{REF}$ , is developed from the internal reference and will show the same drift rate as the reference voltage. The DAC output current,  $I_{DAC}$ , which is a function of the digital input codes, is designed to track  $I_{REF}$ ; if there is a slight mismatch in these currents over temperature, it will contribute to the gain T.C. The bipolar offset resistor,  $R_{BP}$ , and gain setting resistor,  $R_{GAIN}$ , also have temperature coefficients that contribute to system drift errors. The input offset voltage drift of the output amplifier, OA, also contributes a small error.

–8– REV. B

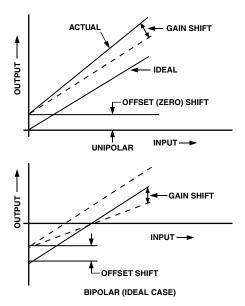

Figure 4. Bipolar Configuration

There are three types of drift errors over temperature: offset, gain, and linearity. Offset drift causes a vertical translation of the entire transfer curve; gain drift is a change in the slope of the curve; and linearity drift represents a change in the shape of the curve. The combination of these three drifts results in the complete specification for total error over temperature.

Total error is defined as the deviation from a true straight line transfer characteristic from exactly zero at a digital input that calls for zero output to a point that is defined as full-scale. A specification for total error over temperature assumes that both the zero and full-scale points have been trimmed for zero error at  $25^{\circ}C$ . Total error is normally expressed as a percentage of the full-scale range. In the bipolar situation, this means the total range from  $-V_{FS}$  to  $+V_{FS}$ .

Several new design concepts not previously used in DAC80-type devices contribute to a reduction in all the error factors over temperature. The incorporation of low temperature coefficient silicon-chromium thin-film resistors deposited on a single chip, a patented, fully differential, emitter weighted, precision current steering cell structure, and a T.C. trimmed buried Zener diode reference element results in superior wide temperature range performance. The gain setting resistors and bipolar offset resistor are also fabricated on the chip with the same SiCr material as the ladder network, resulting in low gain and offset drift.

#### MONOTONICITY AND LINEARITY

The initial linearity error of  $\pm 1/2$  LSB max and the differential linearity error of  $\pm 3/4$  LSB max guarantee monotonic performance over the specified range. It can therefore be assumed that linearity errors are insignificant in computation of total temperature errors.

#### **UNIPOLAR ERRORS**

Temperature error analysis in the unipolar mode is straightforward: there is an offset drift and a gain drift. The offset drift (which comes from leakage currents and drift in the output amplifier (OA)) causes a linear shift in the transfer curve as shown in Figure 5. The gain drift causes a change in the slope of the curve and results from reference drift, DAC drift, and drift in  $R_{\rm GAIN}$  relative to the DAC resistors.

#### **BIPOLAR RANGE ERRORS**

The analysis is slightly more complex in the bipolar mode. In this mode  $R_{BP}$  is connected to the summing node of the output amplifier (see Figure 4) to generate a current that exactly balances the current of the MSB so that the output voltage is zero with only the MSB on.

Note that if the DAC and application resistors track perfectly, the bipolar offset drift will be zero even if the reference drifts. A change in the reference voltage, which causes a shift in the bipolar offset, will also cause an equivalent change in  $I_{REF}$  and thus  $I_{DAC}$ , so that  $I_{DAC}$  will always be exactly balanced by  $I_{BP}$  with the MSB turned on. This effect is shown in Figure 5. The net effect of the reference drift then is simply to cause a rotation in the transfer around bipolar zero. However, consideration of second order effects (which are often overlooked) reveals the errors in the bipolar mode. The unipolar offset drifts previously discussed will have the same effect on the bipolar offset. A mismatch of  $R_{BP}$  to the DAC resistors is usually the largest component of bipolar drift, but in the ADDAC80 this error is held to 10 ppm/°C max. Gain drift in the DAC also contributes to bipolar offset drift, as well as full-scale drift, but again is held to 10 ppm/°C max.

Figure 5. Unipolar and Bipolar Drifts

### USING THE ADDAC80 SERIES POWER SUPPLY CONNECTIONS

For optimum performance power supply decoupling capacitors should be added as shown in the connection diagrams. These capacitors (1  $\mu F$  electrolytic recommended) should be located close to the ADDAC80. Electrolytic capacitors, if used, should be paralleled with 0.01  $\mu F$  ceramic capacitors for optimum high frequency performance.

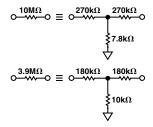

#### EXTERNAL OFFSET AND GAIN ADJUSTMENT

Offset and gain may be trimmed by installing external OFFSET and GAIN potentiometers. These potentiometers should be connected as shown in the block diagrams and adjusted as described below. TCR of the potentiometers should be 100 ppm/°C or less. The 3.9 M $\Omega$  and 10 M $\Omega$  resistors (20% carbon or better) should be located close to the ADDAC80 to prevent noise pickup. If it is not convenient to use these high-value resistors, a functionally equivalent "T" network, as shown in Figure 8 may be substituted in each case. The gain adjust (Pin 23) is a high impedance point and a 0.01  $\mu F$  ceramic capacitor should be connected from this pin to common to prevent noise pickup.

REV. B –9–

Figure 6. External Adjustment and Voltage Supply Connection Diagram, Current Model

#### Offset Adjustment

For unipolar (CSB) configurations, apply the digital input code that should produce zero potential output and adjust the OFFSET potentiometer for zero output. For bipolar (COB, CTC) configurations, apply the digital input code that should produce the maximum negative output voltage. Example: If the FULL SCALE RANGE is connected for 20 V, the maximum negative output voltage is –10 V. See Table II for corresponding codes.

#### **Gain Adjustment**

For either unipolar or bipolar configurations, apply the digital input that should give the maximum positive voltage output. Adjust the GAIN potentiometer for this positive full-scale voltage. See Table II for positive full-scale voltages.

Figure 7. External Adjustment and Voltage Supply Connection Diagram, Voltage Model

Figure 8. Equivalent Resistances

Table II. Digital Input Analog Output

| Digital Input                                         | Analog Output                                     |                                           |                                                      |                                                |  |  |  |  |

|-------------------------------------------------------|---------------------------------------------------|-------------------------------------------|------------------------------------------------------|------------------------------------------------|--|--|--|--|

| 12-Bit Resolution                                     | Voltag                                            | ge*                                       | Current                                              |                                                |  |  |  |  |

| MSB LSB<br>0 0 0 0 0 0 0 0 0 0 0 0 0<br>0 1 1 1 1 1 1 | 0 to +10 V<br>+9.9976 V<br>+5.0000 V<br>+4.9976 V | ±10 V<br>+9.9951 V<br>0.0000 V<br>4.88 mV | 0 to -2 mA<br>-1.9995 mA<br>-1.0000 mA<br>-0.9995 mA | ±1 mA<br>-0.9995 mA<br>0.0000 mA<br>+0.0005 mA |  |  |  |  |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                 | 0.0000 V<br>2.44 mV                               | -10.0000 V<br>-0.0049 V                   | 0.0000 mA<br>0.488 μA                                | -1.00 mA<br>0.488 μA                           |  |  |  |  |

<sup>\*</sup>To obtain values for other binary ranges 0 to 5 V range: divide 0 to 10 values by 2;  $\pm 5$  V range: divide  $\pm 10$  V range values by 2;  $\pm 2.5$  V range: divide  $\pm 10$  V range values by 4.

–10– REV. B

#### **VOLTAGE OUTPUT MODELS**

Internal scaling resistors provided in the ADDAC80 may be connected to produce bipolar output voltage ranges of  $\pm 10$  V,  $\pm 5$  V or  $\pm 2.5$  V or unipolar output voltage ranges of 0 V to  $\pm 5$  V or 0 V to  $\pm 10$  V (see Figure 9).

Figure 9. Output Amplifier Voltage Range Scaling Circuit

Gain and offset drift are minimized in the ADDAC80 because of the thermal tracking of the scaling resistors with other device components. Connections for various output voltage ranges are shown in Table III. Settling time is specified for a full-scale range change: 4  $\mu s$  for a 10  $k\Omega$  feedback resistor; 3  $\mu s$  for a 5  $k\Omega$  feedback resistor when using the compensation capacitor shown in Figure 3a.

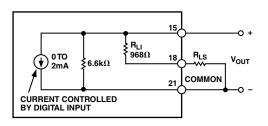

The equivalent resistive scaling network and output circuit of the current model are shown in Figures 10 and 11. External  $R_{LS}$  resistors are required to produce exactly 0 V to -2 V or  $\pm 1$  V output. TCR of these resistors should be  $\pm 100$  ppm/°C or less to maintain the ADDAC80 output specifications. If exact output ranges are not required, the external resistors are not needed.

Figure 10. Internal Scaling Resistors

Figure 11. ADDAC80 Current Model Equivalent Output Circuit

Internal resistors are provided to scale an external op amp or to configure a resistive load to offer two output voltage ranges of  $\pm 1~V$  or 0 V to –2 V. These resistors ( $R_{LI}$  TCR = 20 ppm/°C) are an integral part of the ADDAC80 and maintain gain and bipolar offset drift specifications. If the internal resistors are not used, external  $R_L$  (or  $R_F$ ) resistors should have a TCR of  $\pm 25~ppm/^\circ C$  or less to minimize drift. This will typically add  $\pm 50~ppm/^\circ C$  + the TCR of  $R_L$  (or  $R_F$ ) to the total drift.

| Table III. Output Vol | ltage Range Connections, \ | Voltage Model ADDAC80 |

|-----------------------|----------------------------|-----------------------|

|-----------------------|----------------------------|-----------------------|

| Output<br>Range | Digital<br>Input Codes | Connect<br>Pin 15 to | Connect<br>Pin 17 to | Connect<br>Pin 19 to | Connect<br>Pin 16 to |

|-----------------|------------------------|----------------------|----------------------|----------------------|----------------------|

| ±10 V           | COB or CTC             | 19                   | 20                   | 15                   | 24                   |

| ±5 V            | COB or CTC             | 18                   | 20                   | NC                   | 24                   |

| ±2.5 V          | COB or CTC             | 18                   | 20                   | 20                   | 24                   |

| 0 V to 10 V     | CSB                    | 18                   | 21                   | NC                   | 24                   |

| 0 V to 5 V      | CSB                    | 18                   | 21                   | 20                   | 24                   |

| 0 V to 10 V     | CCD                    | 19                   | NC                   | 15                   | 24                   |

NC = No Connect

#### DRIVING A RESISTIVE LOAD UNIPOLAR

A load resistance,  $R_L = R_{LI}$ , +  $R_{LS}$ , connected as shown in Figure 12 will generate a voltage range,  $V_{OUT}$ , determined by:

$$V_{OUT} = -2 \, mA \left( \frac{6.6 \, k\Omega \times R_L}{6.6 \, k\Omega + R_L} \right) \tag{1}$$

where  $R_L$  max = 1.54 k $\Omega$  and  $V_{OUT}$  max = -2.5 V

To achieve specified drift, connect the internal scaling resistor  $(R_{LI})$  as shown in Table IV to an external metal film trim resistor  $(R_{LS})$  to provide full scale output voltage range of 0 V to -2 V. With  $R_{LS} = 0$  V,  $V_{OUT} = -1.69$  V.

Figure 12. Equivalent Circuit ADDAC80-CBI-I Connected for Unipolar Voltage Output with Resistive Load

REV. B –11–

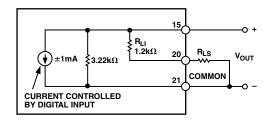

#### DRIVING A RESISTOR LOAD BIPOLAR

The equivalent output circuit for a bipolar output voltage range is shown in Figure 13,  $R_L = R_{LI} + R_{LS}$ .  $V_{OUT}$  is determined by:

$$V_{OUT} = \pm 1 \, mA \left( \frac{R_L \times 3.22 \, k\Omega}{R_L + 3.22 \, k\Omega} \right) \tag{2}$$

where  $R_L$  max = 11.18 k $\Omega$  and  $V_{OUT}$  max =  $\pm 2.5$  V