# Four-ADC, Two-DAC, Low Power Codec with Audio Processor

Data Sheet ADAU1777

#### **FEATURES**

Programmable audio processing engine

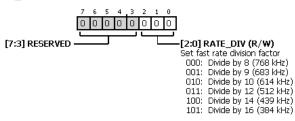

Fast (up to 768 kHz) and slow processing paths

Biquad filters, limiters, volume controls, and mixing

Low latency, 24-bit ADCs and DACs

102 dB SNR (through PGA and ADC with A weighted filter)

108 dB combined SNR (through DAC and headphone with

A weighted filter)

Serial port sampling rate from 8 kHz to 192 kHz 5 µs analog-to-analog latency

4 single-ended analog inputs, configurable as microphone or line inputs

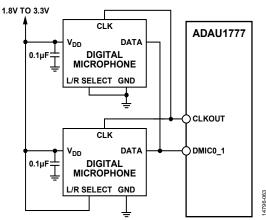

**Dual stereo digital microphone inputs**

Stereo analog audio output, single-ended or differential, configurable as either line output or headphone driver PLL supporting any input clock rate from 8 MHz to 27 MHz Full duplex, asynchronous sample rate converters (ASRCs) Power supplies

Analog and digital input/output of 1.8 V to 3.3 V

Digital signal processing (DSP) core of 1.1 V to 1.8 V

Low power

I<sup>2</sup>C and SPI control interfaces, self boot from I<sup>2</sup>C EEPROM 7 multipurpose (MPx) pins for digital controls and outputs

#### **APPLICATIONS**

Noise canceling handsets, headsets, and headphones Bluetooth® active noise canceling (ANC) handsets, headsets, and headphones

Personal navigation devices

Digital still and video cameras

#### **GENERAL DESCRIPTION**

The ADAU1777 is a codec with four inputs and two outputs that incorporates a digital processing engine to perform filtering, level control, signal level monitoring, and mixing. The path from the analog input to the DSP core to the analog output is optimized for low latency and is ideal for noise canceling headsets. With the addition of just a few passive components, a crystal, and an EEPROM for booting, the ADAU1777 provides a complete headset solution.

Note that throughout this data sheet, multifunction pins, such as SCL/SCLK, are referred to either by the entire pin name or by a single function of the pin, for example, SCLK, when only that function is relevant.

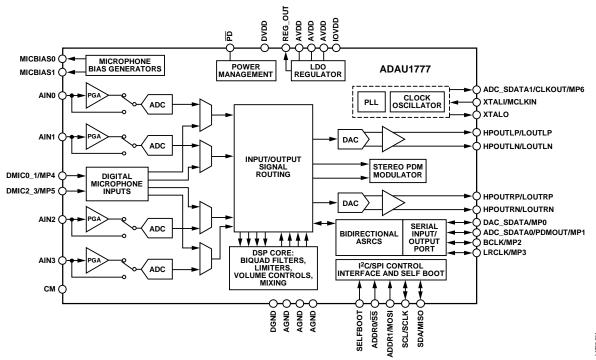

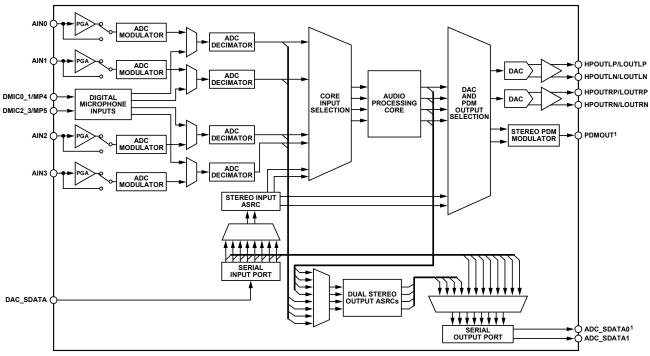

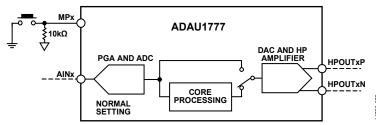

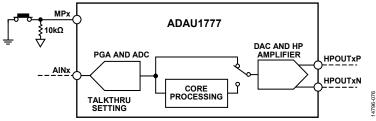

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **ADAU1777**

# **TABLE OF CONTENTS**

| Features                                    | 1  | Burst Mode Communication                            | 35 |

|---------------------------------------------|----|-----------------------------------------------------|----|

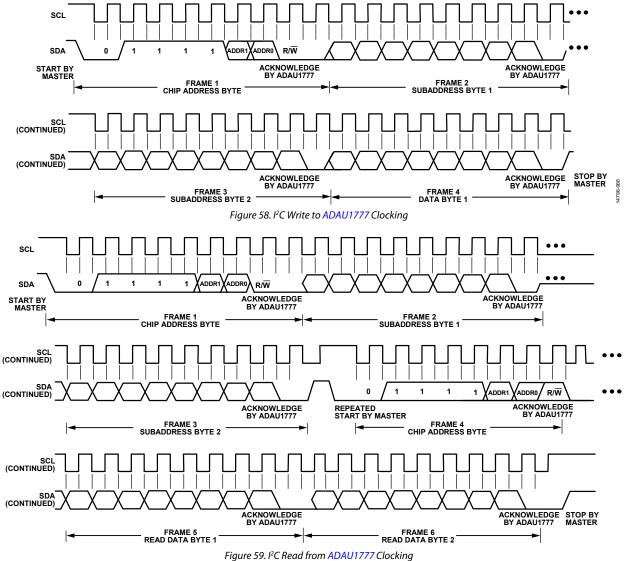

| Applications                                | 1  | I <sup>2</sup> C Port                               | 35 |

| General Description                         | 1  | SPI Port                                            | 38 |

| Functional Block Diagram                    | 1  | Self Boot                                           | 39 |

| Revision History                            | 3  | Multipurpose Pins                                   | 40 |

| Specifications                              | 4  | Push-Button Volume Controls                         | 40 |

| Analog Performance Specifications           | 4  | Limiter Compression Enable                          | 40 |

| Crystal Amplifier Specifications            | 8  | Parameter Bank Switching                            | 40 |

| Digital Input/Output Specifications         | 8  | Mute                                                | 40 |

| Power Supply Specifications                 | 8  | DSP Bypass Mode                                     | 41 |

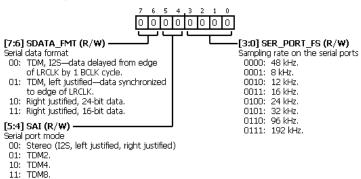

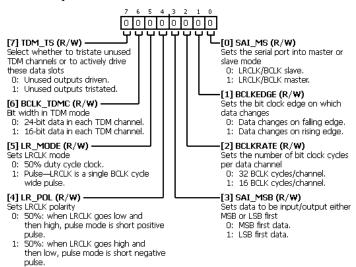

| Typical Power Management Settings           | 9  | Serial Data Input/Output Ports                      | 42 |

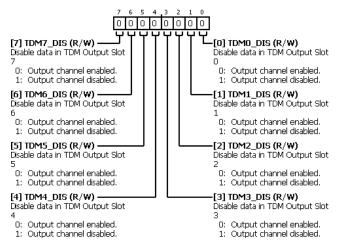

| Digital Filters Specifications              | 9  | Tristating Unused Channels                          | 42 |

| Digital Timing Specifications               | 10 | Applications Information                            | 45 |

| Absolute Maximum Ratings                    | 14 | Power Supply Bypass Capacitors                      | 45 |

| Thermal Resistance                          | 14 | Layout                                              | 45 |

| ESD Caution                                 | 14 | Grounding                                           | 45 |

| Pin Configuration and Function Descriptions | 15 | PCB Stackup                                         | 45 |

| Typical Performance Characteristics         | 17 | Low Latency Register Settings                       | 46 |

| Theory of Operation                         | 24 | Register Summary                                    | 49 |

| System Clocking and Power-Up                | 25 | Register Details                                    | 52 |

| Clock Initialization                        | 25 | Clock Control Register                              | 52 |

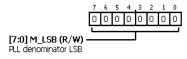

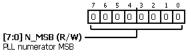

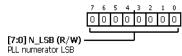

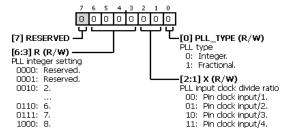

| PLL                                         | 25 | PLL Denominator MSB Register                        | 53 |

| Clock Output                                | 26 | PLL Denominator LSB Register                        | 53 |

| Power Sequencing                            | 26 | PLL Numerator MSB Register                          | 53 |

| Signal Routing                              | 27 | PLL Numerator LSB Register                          | 54 |

| Input Signal Paths                          | 28 | PLL Integer Setting Register                        | 54 |

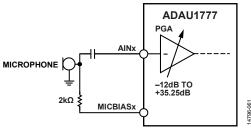

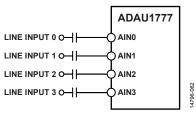

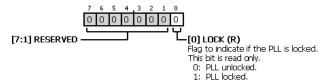

| Analog Inputs                               | 28 | PLL Lock Flag Register                              | 55 |

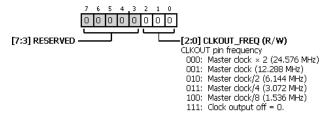

| Digital Microphone Input                    | 29 | CLKOUT Setting Selection Register                   | 55 |

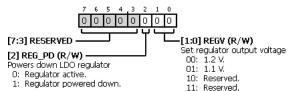

| Analog-to-Digital Converters (ADCs)         | 29 | Regulator Control Register                          | 56 |

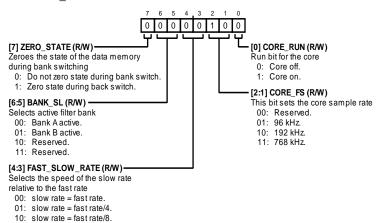

| Output Signal Paths                         | 30 | Core Control Register                               | 56 |

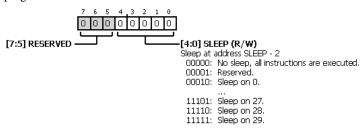

| Analog Outputs                              | 30 | Sleep on Program Address Count Register             | 57 |

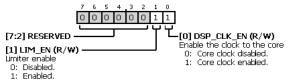

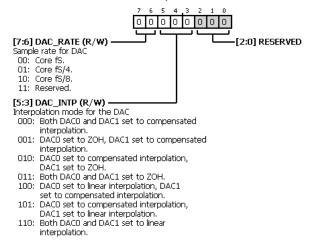

| Digital-to-Analog Converters (DACs)         | 30 | Filter Engine and Limiter Control Register          | 59 |

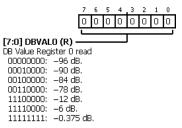

| PDM Output                                  | 30 | DB Value Register 0 Read                            | 59 |

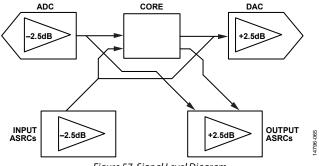

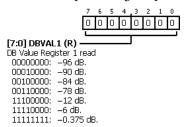

| Asynchronous Sample Rate Converters         | 31 | DB Value Register 1 Read                            | 60 |

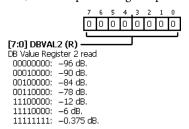

| Signal Levels                               | 31 | DB Value Register 2 Read                            | 60 |

| Signal Processing                           | 32 | Core Channel 0/Core Channel 1 Input Select Register | 61 |

| Instructions                                | 32 | Core Channel 2/Core Channel 3 Input Select Register | 62 |

| Data Memory                                 | 32 | DAC Input Select Register                           | 63 |

| Parameters                                  | 32 | PDM Modulator Input Select Register                 | 64 |

| Control Port                                | 35 |                                                     |    |

| Serial Data Output 0/Serial Data Output 1 Input Select<br>Register | 65 |

|--------------------------------------------------------------------|----|

| Serial Data Output 2/Serial Data Output 3 Input Select<br>Register | 66 |

| Serial Data Output 4/Serial Data Output 5 Input Select<br>Register | 67 |

| Serial Data Output 6/Serial Data Output 7 Input Select<br>Register | 68 |

| ADC_SDATA0/ADC_SDATA1 Channel Select Register                      | 69 |

| Output ASRC0/Output ASRC1 Source Register                          | 69 |

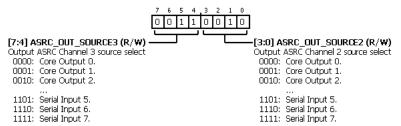

| Output ASRC2/Output ASRC3 Source Register                          | 70 |

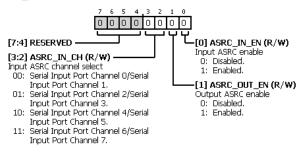

| Input ASRC Channel Select Register                                 | 71 |

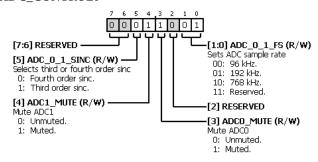

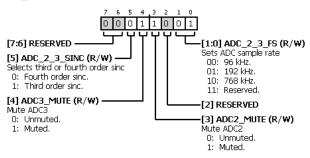

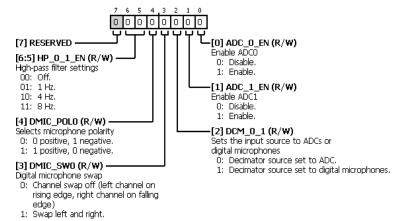

| ADC0/ADC1 Control 0 Register                                       | 72 |

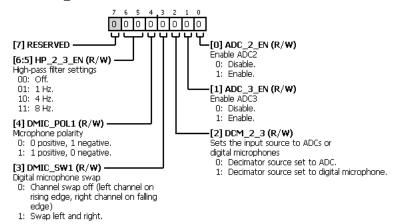

| ADC2/ADC3 Control 0 Register                                       | 73 |

| ADC0/ADC1 Control 1 Register                                       | 74 |

| ADC2/ADC3 Control 1 Register                                       | 75 |

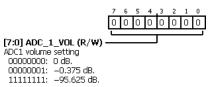

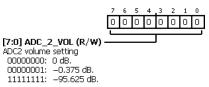

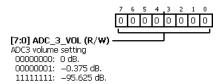

| ADC0 Volume Control Register                                       | 75 |

| ADC1 Volume Control Register                                       | 76 |

| ADC2 Volume Control Register                                       | 76 |

| ADC3 Volume Control Register                                       | 77 |

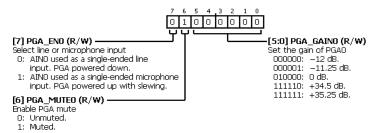

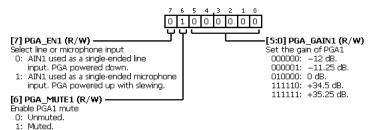

| PGA Control 0 Register                                             | 77 |

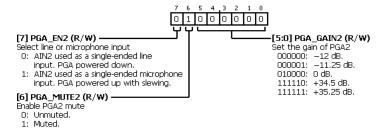

| PGA Control 1 Register                                             | 78 |

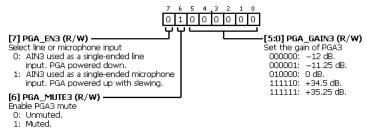

| PGA Control 2 Register                                             | 78 |

| PGA Control 3 Register                                             | 79 |

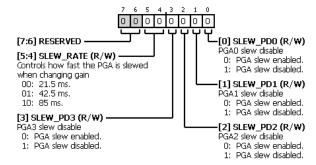

| PGA Slew Control Register                                          | 80 |

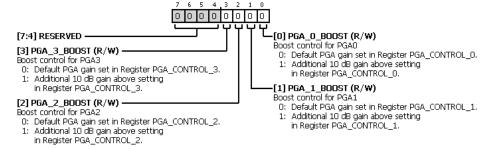

| PGA 10 dB Gain Boost Register                                      | 80 |

| Input and Output Capacitor Charging Register                       | 81 |

| DSP Bypass Path Register                                           | 82 |

| DSP Bypass Gain for PGA0 Register                                  | 82 |

| DSP Bypass Gain for PGA1 Register                                  | 82 |

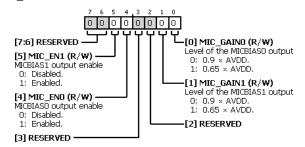

| MICBIAS0_1 Control Register                                        | 83 |

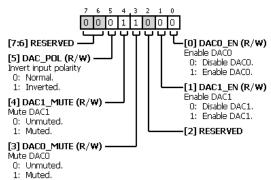

| DAC Control Register                                               | 83 |

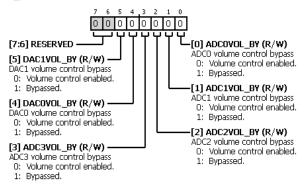

| DAC0 Volume Control Register                                       | 84 |

| DAC1 Volume Control Register                                       | 84 |

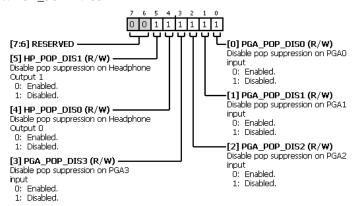

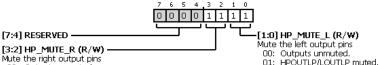

| Headphone Output Mutes Register                                    | 85 |

#### **REVISION HISTORY**

12/2016—Revision 0: Initial Version

# **SPECIFICATIONS**

Master clock = 12.288 MHz, serial input sample rate = 48 kHz, measurement bandwidth = 20 Hz to 20 kHz, word width = 24 bits,  $T_A = 25^{\circ}\text{C}$ , outputs line loaded with 10 k $\Omega$ .

#### **ANALOG PERFORMANCE SPECIFICATIONS**

AVDD = IOVDD = 1.8 V, DVDD = 1.1 V, unless otherwise noted. Phase-locked loop (PLL) disabled, direct master clock.

Table 1.

| Parameter                                   | Test Conditions/Comments                        | Min   | Тур      | Max   | Unit  |

|---------------------------------------------|-------------------------------------------------|-------|----------|-------|-------|

| ANALOG-TO-DIGITAL CONVERTERS (ADCs)         |                                                 |       |          |       |       |

| ADC Resolution                              | All ADCs                                        |       | 24       |       | Bits  |

| Digital Attenuation Step                    |                                                 |       | 0.375    |       | dB    |

| Digital Attenuation Range                   |                                                 |       | 95       |       | dB    |

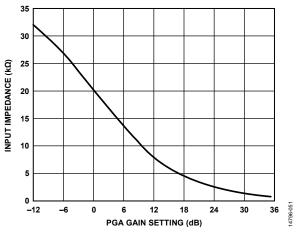

| INPUT RESISTANCE                            | Gain settings do not include 10 dB gain from    |       |          |       |       |

|                                             | PGA_x_BOOST settings; this additional gain does |       |          |       |       |

|                                             | not affect input impedance; PGA_POP_DISx = 1    |       |          |       |       |

| Single-Ended Line Input                     | 0 dB gain                                       |       | 14.3     |       | kΩ    |

| Programmable Gain Amplifier (PGA) Inputs    | –12 dB gain                                     |       | 32.0     |       | kΩ    |

|                                             | 0 dB gain                                       |       | 20       |       | kΩ    |

|                                             | +35.25 dB gain                                  |       | 0.68     |       | kΩ    |

| LINE INPUT                                  | PGA_ENx = 0, PGA_x_BOOST = 0, PGA_POP_DISx = 1  |       |          |       |       |

| Full-Scale Input Voltage                    | Scales linearly with AVDD                       |       | AVDD/3.3 |       | V rms |

|                                             | AVDD = 1.8 V                                    |       | 0.55     |       | V rms |

|                                             | AVDD = 1.8 V                                    |       | 1.54     |       | V p-p |

|                                             | AVDD = 3.3 V                                    |       | 1.00     |       | V rms |

|                                             | AVDD = 3.3 V                                    |       | 2.83     |       | V p-p |

| Dynamic Range <sup>1</sup>                  | 20 Hz to 20 kHz, -60 dB input                   |       |          |       |       |

| With A-Weighted Filter (RMS)                | AVDD = 1.8 V                                    | 95    | 97       |       | dB    |

|                                             | AVDD = 3.3 V                                    | 99    | 102      |       | dB    |

| With Flat 20 Hz to 20 kHz Filter            | AVDD = 1.8 V                                    | 92    | 94       |       | dB    |

|                                             | AVDD = 3.3 V                                    | 96    | 99       |       | dB    |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>    |                                                 |       |          |       |       |

| With A-Weighted Filter (RMS)                | AVDD = 1.8 V                                    | 96    | 98       |       | dB    |

|                                             | AVDD = 3.3 V                                    | 100   | 103      |       | dB    |

| With Flat 20 Hz to 20 kHz Filter            | AVDD = 1.8 V                                    | 92    | 96       |       | dB    |

|                                             | AVDD = 3.3 V                                    | 96    | 100      |       | dB    |

| Interchannel Gain Mismatch                  |                                                 | 0     | 40       | 200   | mdB   |

| Total Harmonic Distortion + Noise (THD + N) | 20 Hz to 20 kHz, -1 dB from full-scale input    |       |          |       |       |

|                                             | AVDD = 1.8 V                                    |       | -90      | -83   | dB    |

|                                             | AVDD = 3.3 V                                    |       | -94      | -87   | dB    |

| Offset Error                                |                                                 | -0.11 |          | +0.12 | mV    |

| Gain Error                                  |                                                 | -0.4  |          | +0.2  | dB    |

| Interchannel Isolation                      | CM capacitor = 22 μF                            |       | 95       |       | dB    |

| Power Supply Rejection Ratio (PSRR)         | CM capacitor = 22 µF, 100 mV p-p at 1 kHz       |       | 55       |       | dB    |

| PGA INPUT                                   | PGA_ENx = 1, PGA_x_BOOST = 0                    |       |          |       |       |

| Full-Scale Input Voltage                    | Scales linearly with AVDD                       |       | AVDD/3.3 |       | V rms |

|                                             | AVDD = 1.8 V                                    |       | 0.55     |       | V rms |

|                                             | AVDD = 1.8 V                                    |       | 1.54     |       | V p-p |

|                                             | AVDD = 3.3 V                                    |       | 1.00     |       | V rms |

|                                             | AVDD = 3.3 V                                    |       | 2.83     |       | V p-p |

| Dynamic Range <sup>1</sup>                  | 20 Hz to 20 kHz, –60 dB input                   |       |          |       | ' '   |

| With A-Weighted Filter (RMS)                | AVDD = 1.8 V                                    |       | 94       |       | dB    |

| <i>z</i>                                    | AVDD = 3.3 V                                    |       | 102      |       | dB    |

| With Flat 20 Hz to 20 kHz Filter            | AVDD = 1.8 V                                    |       | 92       |       | dB    |

|                                             | AVDD = 3.3 V                                    |       | 98       |       | dB    |

| Parameter                           | Test Conditions/Comments                                                       | Min   | Тур      | Max   | Unit   |

|-------------------------------------|--------------------------------------------------------------------------------|-------|----------|-------|--------|

| THD + N                             | 20 Hz to 20 kHz, -1 dB from full-scale input                                   |       |          |       |        |

|                                     | AVDD = 1.8 V                                                                   |       | -88      |       | dB     |

|                                     | AVDD = 3.3 V                                                                   |       | -90      |       | dB     |

| SNR <sup>2</sup>                    |                                                                                |       |          |       |        |

| With A-Weighted Filter (RMS)        | AVDD = 1.8 V                                                                   |       | 94       |       | dB     |

|                                     | AVDD = 3.3 V                                                                   |       | 102      |       | dB     |

| With Flat 20 Hz to 20 kHz Filter    | AVDD = 1.8 V                                                                   |       | 93       |       | dB     |

|                                     | AVDD = 3.3 V                                                                   |       | 98       |       | dB     |

| PGA Gain Variation                  | Standard deviation                                                             |       |          |       |        |

| With −12 dB Setting                 |                                                                                |       | 0.05     |       | dB     |

| With +35.25 dB Setting              |                                                                                |       | 0.15     |       | dB     |

| PGA Boost                           | PGA_x_BOOST                                                                    |       | 10       |       | dB     |

| PGA Mute Attenuation                | PGA_MUTEx                                                                      |       | -63      |       | dB     |

| Interchannel Gain Mismatch          |                                                                                |       | 0.04     |       | dB     |

| Offset Error                        |                                                                                | -0.12 |          | +0.12 | mV     |

| Gain Error                          |                                                                                | 02    | -0.05    |       | dB     |

| Interchannel Isolation              |                                                                                |       | 100      |       | dB     |

| PSRR                                | CM capacitor = 20 μF, 100 mV p-p at 1 kHz                                      |       | 63       |       | dB     |

| MICROPHONE BIAS                     | MIC_ENx = 1                                                                    |       |          |       | ub.    |

|                                     | IVIIC_EIXX = 1                                                                 |       |          |       |        |

| Bias Voltage                        | AVDD 10V MIC CAIN. 1                                                           | 1 1 4 | 1.16     | 1 17  | V      |

| 0.65 × AVDD                         | AVDD = 1.8 V, MIC_GAINx = 1                                                    | 1.14  | 1.16     | 1.17  |        |

| 0.00                                | AVDD = 3.3 V, MIC_GAINx = 1                                                    | 2.10  | 2.12     | 2.14  | V      |

| 0.90 × AVDD                         | AVDD = 1.8 V, MIC_GAINx = 0                                                    | 1.61  | 1.63     | 1.65  | V      |

|                                     | $AVDD = 3.3 \text{ V, MIC\_GAINx} = 0$                                         | 2.95  | 2.97     | 2.99  | V      |

| Bias Current Source                 |                                                                                |       | _        | 3     | mA     |

| Output Impedance                    |                                                                                |       | 1        |       | Ω      |

| MICBIASx Isolation                  | $MIC\_GAINx = 0$                                                               |       | 95       |       | dB     |

|                                     | $MIC\_GAINx = 1$                                                               |       | 99       |       | dB     |

| Noise in the Signal Bandwidth       | 20 Hz to 20 kHz, 4.7 μF decoupling capacitor, 5.0 kΩ load on the MICBIASx pins |       |          |       |        |

| AVDD = 1.8 V                        | $MIC\_GAINx = 0$                                                               |       | 27       |       | nV/√Hz |

|                                     | $MIC\_GAINx = 1$                                                               |       | 16       |       | nV/√Hz |

| AVDD = 3.3 V                        | $MIC\_GAINx = 0$                                                               |       | 35       |       | nV/√Hz |

|                                     | $MIC\_GAINx = 1$                                                               |       | 19       |       | nV/√Hz |

| DIGITAL-TO-ANALOG CONVERTERS (DACs) |                                                                                |       |          |       |        |

| Resolution                          | All DACs                                                                       |       | 24       |       | Bits   |

| Digital Attenuation Step            |                                                                                |       | 0.375    |       | dB     |

| Digital Attenuation Range           |                                                                                |       | 95       |       | dB     |

| DAC SINGLE-ENDED OUTPUT             | Single-ended operation, HPOUTLP/LOUTLP and HPOUTRP/LOUTRP pins                 |       |          |       |        |

| Full-Scale Output Voltage           | Scales linearly with AVDD                                                      |       | AVDD/3.4 |       | V rms  |

| . 5                                 | AVDD = 1.8 V                                                                   |       | 0.53     |       | V rms  |

|                                     | AVDD = 1.8 V                                                                   |       | 1.5      |       | V p-p  |

|                                     | AVDD = 3.3 V                                                                   |       | 0.97     |       | V rms  |

|                                     | AVDD = 3.3 V                                                                   |       | 2.74     |       | V p-p  |

| Mute Attenuation                    |                                                                                |       | _72      |       | dB     |

| Line Output Mode                    |                                                                                |       |          |       |        |

| Dynamic Range <sup>1</sup>          | 20 Hz to 20 kHz, –60 dB input                                                  |       |          |       |        |

| With A-Weighted Filter (RMS)        | AVDD = 1.8 V                                                                   | 97    | 100      |       | dB     |

| with A weighted ritter (miss)       | AVDD = 1.8 V<br>AVDD = 3.3 V                                                   | 102   | 104      |       | dB     |

| With Flat 20 Hz to 20 kHz Filter    | AVDD = 3.3 V<br>AVDD = 1.8 V                                                   | 95    | 97       |       | dВ     |

| WILLI FIAL ZU MZ LU ZU KMZ FIILER   |                                                                                |       |          |       |        |

|                                     | AVDD = 3.3 V                                                                   | 99    | 101      |       | dB     |

| Parameter                        | Test Conditions/Comments                                                   | Min   | Тур                | Max        | Unit  |

|----------------------------------|----------------------------------------------------------------------------|-------|--------------------|------------|-------|

| SNR <sup>2</sup>                 | 20 Hz to 20 kHz                                                            |       |                    |            |       |

| With A-Weighted Filter (RMS)     | AVDD = 1.8 V                                                               | 98    | 100                |            | dB    |

|                                  | AVDD = 3.3 V                                                               | 102   | 104                |            | dB    |

| With Flat 20 Hz to 20 kHz Filter | AVDD = 1.8 V                                                               | 96    | 98                 |            | dB    |

|                                  | AVDD = 3.3 V                                                               | 99    | 102                |            | dB    |

| Interchannel Gain Mismatch       |                                                                            | 0     | 50                 | 200        | mdB   |

| THD + N                          | 20 Hz to 20 kHz, -1 dBFS input                                             |       |                    |            | dB    |

|                                  | AVDD = 1.8 V                                                               |       | -93                | -89        | dB    |

|                                  | AVDD = 3.3 V                                                               |       | -94                | -90        | dB    |

| Gain Error                       |                                                                            | -0.13 |                    | +0.13      | dB    |

| Headphone Mode                   |                                                                            |       |                    |            |       |

| Dynamic Range <sup>1</sup>       | 20 Hz to 20 kHz, -60 dB input                                              |       |                    |            |       |

| With A-Weighted Filter (RMS)     | AVDD = 1.8 V                                                               | 97    | 100                |            | dB    |

| •                                | AVDD = 3.3 V                                                               | 102   | 104                |            | dB    |

| With Flat 20 Hz to 20 kHz Filter | AVDD = 1.8 V                                                               | 95    | 97                 |            | dB    |

|                                  | AVDD = 3.3 V                                                               | 99    | 101                |            | dB    |

| SNR <sup>2</sup>                 | 20 Hz to 20 kHz                                                            |       |                    |            |       |

| With A-Weighted Filter (RMS)     | AVDD = 1.8 V                                                               | 98    | 100                |            | dB    |

| 3 ,                              | AVDD = 3.3 V                                                               | 102   | 104                |            | dB    |

| With Flat 20 Hz to 20 kHz Filter | AVDD = 1.8 V                                                               | 96    | 98                 |            | dB    |

|                                  | AVDD = 3.3 V                                                               | 100   | 102                |            | dB    |

| Interchannel Gain Mismatch       | 7,700 3.5 7                                                                | 0     | 50                 | 230        | mdB   |

| THD + N                          | 20 Hz to 20 kHz, -1 dBFS input                                             |       | 50                 | 230        | mab   |

| 32 Ω Load                        | AVDD = 1.8 V, output power = 6.3 mW                                        |       | <b>-79</b>         | -67        | dB    |

| 32 12 LOAG                       | AVDD = 1.8 V, output power = 0.5 mW                                        |       | -84                | -67        | dB    |

| $24 \Omega$ Load                 | AVDD = 3.3 V, output power = 2.3 HW<br>AVDD = 1.8 V, output power = 8.4 mW |       | -79                | -65        | dB    |

| 24 17 LOad                       |                                                                            |       | -7 <i>9</i><br>-80 | -64        | dB    |

| 16 Ω Load                        | AVDD = 3.3 V, output power = 27 mW                                         |       | -00<br>-74         | -64<br>-61 | dB    |

| 10 17 LOdu                       | AVDD = 1.8 V, output power = 13 mW                                         |       |                    | -67        | dB    |

| Gain Error                       | AVDD = 3.3 V, output power = 30 mW                                         | 0.13  | <del>-</del> 77    |            | dB    |

|                                  |                                                                            | -0.13 |                    | +0.13      | ив    |

| Headphone Output Power           | AVDD 10V (010/ TUD ) N                                                     |       | 0.0                |            | \4/   |

| 32 Ω Load                        | AVDD = 1.8  V, < 0.1%  THD + N                                             |       | 8.0                |            | mW    |

| 24.04                            | AVDD = 3.3  V, <0.1%  THD + N                                              |       | 28.1               |            | mW    |

| 24 Ω Load                        | AVDD = 1.8  V, < 0.1%  THD + N                                             |       | 11.1               |            | mW    |

|                                  | AVDD = 3.3  V, <0.1%  THD + N                                              |       | 30.5               |            | mW    |

| 16 Ω Load                        | AVDD = 1.8  V, < 0.1%  THD + N                                             |       | 16.5               |            | mW    |

|                                  | AVDD = 3.3 V, <0.1% THD + N                                                |       | 32.7               |            | mW    |

| Offset Error                     |                                                                            | -0.11 |                    | +0.09      | mV    |

| Interchannel Isolation           | 1 kHz, 0 dBFS input signal                                                 |       | 100                |            | dB    |

| PSRR                             | CM capacitor = 22 μF, 100 mV p-p at 1 kHz                                  |       | 70                 |            | dB    |

| DAC DIFFERENTIAL OUTPUT          | Differential operation                                                     |       |                    |            |       |

| Full-Scale Output Voltage        | Scales linearly with AVDD                                                  |       | AVDD/1.7           |            | V rms |

|                                  | AVDD = 1.8 V                                                               |       | 1.06               |            | V rms |

|                                  | AVDD = 1.8 V                                                               |       | 3.00               |            | V p-p |

|                                  | AVDD = 3.3 V                                                               |       | 1.94               |            | V rms |

|                                  | AVDD = 3.3 V                                                               |       | 5.49               |            | V p-p |

| Mute Attenuation                 |                                                                            |       | -72                |            | dB    |

| Line Output Mode                 |                                                                            |       |                    |            |       |

| Dynamic Range <sup>1</sup>       | 20 Hz to 20 kHz, -60 dB input                                              |       |                    |            |       |

| With A-Weighted Filter (RMS)     | AVDD = 1.8 V                                                               | 102   | 105                |            | dB    |

| -                                | AVDD = 3.3 V                                                               | 105   | 107                |            | dB    |

| With Flat 20 Hz to 20 kHz Filter | AVDD = 1.8 V                                                               | 100   | 102                |            | dB    |

|                                  | AVDD = 3.3 V                                                               | 102   | 105                |            | dB    |

| Parameter                        | Test Conditions/Comments                     | Min   | Тур             | Max    | Unit |

|----------------------------------|----------------------------------------------|-------|-----------------|--------|------|

| SNR <sup>2</sup>                 | 20 Hz to 20 kHz                              |       |                 |        |      |

| With A-Weighted Filter (RMS)     | AVDD = 1.8 V                                 | 103   | 105             |        | dB   |

|                                  | AVDD = 3.3 V                                 | 106   | 108             |        | dB   |

| With Flat 20 Hz to 20 kHz Filter | AVDD = 1.8 V                                 | 100   | 102             |        | dB   |

|                                  | AVDD = 3.3 V                                 | 103   | 105             |        | dB   |

| Interchannel Gain Mismatch       |                                              | 0     | 50              | 200    | mdl  |

| THD + N                          | 20 Hz to 20 kHz, -1 dBFS input               |       |                 |        | dB   |

|                                  | AVDD = 1.8 V                                 |       | -96             | -90    | dB   |

|                                  | AVDD = 3.3 V                                 |       | -96             | -90    | dB   |

| Gain Error                       | 1                                            | -0.1  |                 | +0.16  | dB   |

| Headphone Mode                   |                                              |       |                 |        |      |

| Dynamic Range <sup>1</sup>       | 20 Hz to 20 kHz, -60 dB input                |       |                 |        |      |

| With A-Weighted Filter (RMS)     | AVDD = 1.8 V                                 | 102   | 105             |        | dB   |

| with A weighted their (hivis)    | AVDD = 3.3 V                                 | 105   | 107             |        | dB   |

| With Flat 20 Hz to 20 kHz Filter | AVDD = 3.5 V<br>AVDD = 1.8 V                 | 100   | 107             |        | dB   |

| WILLIT ICE 20 FIZ to 20 KHZ I HE | AVDD = 1.8 V<br>AVDD = 3.3 V                 | 100   | 102             |        | dB   |

| SNR <sup>2</sup>                 | 20 Hz to 20 kHz                              | 102   | 104             |        | ub   |

|                                  |                                              | 102   | 106             |        | dB   |

| With A-Weighted Filter (RMS)     | AVDD = 1.8 V                                 | 103   | 106             |        |      |

| With Flor 2011 to 2011 Files     | AVDD = 3.3 V                                 | 106   | 108             |        | dB   |

| With Flat 20 Hz to 20 kHz Filter | AVDD = 1.8 V                                 | 101   | 103             |        | dB   |

|                                  | AVDD = 3.3 V                                 | 104   | 106             |        | dB   |

| Interchannel Gain Mismatch       |                                              | 0     | 75              | 370    | mdl  |

| THD + N                          |                                              |       |                 |        |      |

| 32 Ω Load                        | -1 dBFS, AVDD = 1.8 V, output power = 26 mW  |       | <del>-</del> 75 | -64    | dB   |

|                                  | -1 dBFS, AVDD = 3.3 V, output power = 87 mW  |       | -83             | -75    | dB   |

| 24 Ω Load                        | -2 dBFS, AVDD = 1.8 V, output power = 27 mW  |       | <b>-75</b>      | -64    | dB   |

|                                  | -1 dBFS, AVDD = 3.3 V, output power = 115 mW |       | -82             | -75    | dB   |

| 16 Ω Load                        | -3 dBFS, AVDD = 1.8 V, output power = 32 mW  |       | <b>-75</b>      | -65    | dB   |

|                                  | −1 dBFS, AVDD = 3.3 V, output power = 168 mW |       | -77             | -68    | dB   |

| Gain Error                       | Headphone mode                               | -0.25 |                 | +0.25  | dB   |

| Headphone Output Power           |                                              |       |                 |        |      |

| 32 Ω Load                        | AVDD = 1.8 V, <0.1% THD + N                  |       | 29.1            |        | mW   |

|                                  | AVDD = 3.3 V, <0.1% THD + N                  |       | 111.8           |        | mW   |

| 24 Ω Load                        | AVDD = 1.8 V, <0.1% THD + N                  |       | 31.8            |        | mW   |

|                                  | AVDD = 3.3 V, <0.1% THD + N                  |       | 148.3           |        | mW   |

| 16 Ω Load                        | AVDD = 1.8 V, <0.1% THD + N                  |       | 32.3            |        | mW   |

|                                  | AVDD = 3.3  V, < 0.1%  THD + N               |       | 193.0           |        | mW   |

| Offset Error                     | 22 212 1, 121112 1112                        | -0.12 | 0               | +0.08  | mV   |

| Interchannel Isolation           | 1 kHz, 0 dBFS input signal                   |       | 100             | . 3.00 | dB   |

| PSRR                             | CM capacitor = 22 µF, 100 mV p-p at 1 kHz    |       | 73              |        | dB   |

| ANALOG-TO-ANALOG LATENCY         | f <sub>s</sub> = 768 kHz                     | +     | 5               |        | μs   |

| INALOG TO ANALOG LATENCT         | $f_s = 192 \text{ kHz}$                      |       | 38              |        | · ·  |

| CM REFERENCE                     |                                              |       | 50              |        | μs   |

|                                  | CM pin                                       |       | A)/DD/2         |        | V    |

| Common-Mode Reference Output     |                                              |       | AVDD/2          |        |      |

| Common-Mode Source Impedance     |                                              | -     | 5               |        | kΩ   |

| REGULATOR                        |                                              |       | _               |        |      |

| Line Regulation                  |                                              |       | 1               |        | mV/  |

| Load Regulation                  |                                              |       | 6               |        | mV/  |

<sup>&</sup>lt;sup>1</sup> Dynamic range is the ratio of the sum of the noise and harmonic power in the band of interest with a -60 dBFS signal present vs. the full-scale power level in decibels. <sup>2</sup> SNR is the ratio of the sum of all noise power in the band of interest with no signal present vs. the full-scale power level in decibels.

#### **CRYSTAL AMPLIFIER SPECIFICATIONS**

AVDD = IOVDD = 1.8 V, DVDD = 1.1 V, unless otherwise noted.

Table 2.

| Parameter         | Min | Тур | Max | Unit   |

|-------------------|-----|-----|-----|--------|

| CRYSTAL AMPLIFIER |     |     |     |        |

| Jitter            |     | 270 | 500 | ps rms |

| Frequency Range   | 8   |     | 27  | MHz    |

| Load Capacitance  |     |     | 20  | pF     |

#### **DIGITAL INPUT/OUTPUT SPECIFICATIONS**

$-40^{\circ}C$  <  $T_{A}$  < +85°C, IOVDD = 3.3 V  $\pm$  10% and 1.8 V - 5% to 1.8 V + 10%, unless otherwise noted.

Table 3.

| Parameter                              | Test Conditions/Comments                                                | Min         | Тур | Max  | Unit |

|----------------------------------------|-------------------------------------------------------------------------|-------------|-----|------|------|

| INPUT/OUTPUT                           |                                                                         |             |     |      |      |

| Input Voltage                          |                                                                         |             |     |      |      |

| High (V <sub>I</sub> H)                | IOVDD = 3.3 V                                                           | 2.0         |     |      | V    |

|                                        | IOVDD = 1.8 V                                                           | 1.1         |     |      | V    |

| Low (V <sub>IL</sub> )                 | IOVDD = 3.3 V                                                           |             |     | 0.8  | V    |

|                                        | IOVDD = 1.8 V                                                           |             |     | 0.45 | V    |

| Input Leakage                          | $IOVDD = 3.3 \text{ V, } I_{IH}^{1} \text{ at } V_{IH} = 2.0 \text{ V}$ |             |     | 10   | μΑ   |

| , ,                                    | $I_{IL}^{1}$ at $V_{IL} = 0.8 \text{ V}$                                |             |     | 10   | μΑ   |

|                                        | $IOVDD = 1.8 \text{ V}, I_{IH}^{1} \text{ at } V_{IH} = 1.1 \text{ V}$  |             |     | 10   | μΑ   |

|                                        | $I_{IL}^{1}$ at $V_{IL} = 0.45 \text{ V}$                               |             |     | 10   | μΑ   |

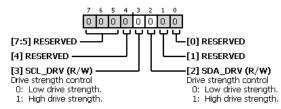

| Output Voltage High (V <sub>OH</sub> ) |                                                                         |             |     |      |      |

| Low Drive Strength                     | $I_{OH}^1 = 1 \text{ mA}$                                               | IOVDD - 0.6 |     |      | V    |

| High Drive Strength                    | $I_{OH}^{1} = 3 \text{ mA}$                                             | IOVDD - 0.6 |     |      | V    |

| Output Voltage Low (Vol)               |                                                                         |             |     |      |      |

| Low Drive Strength                     | $I_{OL}^1 = 1 \text{ mA}$                                               |             |     | 0.4  | V    |

| High Drive Strength                    | $I_{OL}^1 = 3 \text{ mA}$                                               |             |     | 0.4  | V    |

| Input Capacitance                      |                                                                         |             |     | 5    | рF   |

<sup>1</sup> lit is the current when the input is high; liL is the current when the input is low; lot is the current when the output is high; and lot is the current when the output is low.

#### **POWER SUPPLY SPECIFICATIONS**

AVDD = IOVDD = 1.8 V, DVDD = 1.1 V, unless otherwise noted.

Table 4.

| Parameter                             | Test Conditions/Comments | Min   | Тур | Max  | Unit |

|---------------------------------------|--------------------------|-------|-----|------|------|

| SUPPLIES                              |                          |       |     |      |      |

| AVDD Voltage                          |                          | 1.71  | 1.8 | 3.63 | ٧    |

| DVDD Voltage                          |                          | 1.045 | 1.1 | 1.98 | ٧    |

| IOVDD Voltage                         |                          | 1.71  | 1.8 | 3.63 | ٧    |

| Analog Current (I <sub>AVDD</sub> )   |                          |       |     |      |      |

| Normal Operation                      | See Table 5              |       |     |      |      |

| Power-Down                            |                          |       | 1.6 |      | μΑ   |

| Digital Input/Output Current (IIOVDD) |                          |       |     |      |      |

| Normal Operation                      | See Table 5              |       |     |      |      |

| Power-Down                            |                          |       | 1.3 |      | μΑ   |

| POWER CONSUMPTION                     |                          |       |     |      |      |

| All Supplies                          | See Table 5              |       |     |      |      |

| Power-Down, All Supplies              |                          |       | 1   |      | μW   |

#### TYPICAL POWER MANAGEMENT SETTINGS

Typical ANC settings, master clock = 12.288 MHz, PLL disabled, crystal oscillator enabled, core  $f_S = DAC = ADC = 768$  kHz. On-board regulator enabled. Two ADCs with PGA enabled and two ADCs configured for line input, no input signal. Two DACs are configured for differential headphone (HP) operation; DAC outputs are unloaded. Both MICBIAS0 and MICBIAS1 enabled at  $0.9 \times AVDD$ . ASRCs and pulse density modulation (PDM) modulator disabled. Core running 26 out of 32 possible instructions. Serial port set to slave. See Register 0x46 and Register 0x47 for settings.

Table 5.

| Operating Voltage    | Power Management<br>Setting | Typical AVDD<br>Current<br>Consumption (mA) | Typical IOVDD Current Consumption (mA) | Typical ADC<br>THD + N (dB) | Typical HP<br>Output<br>THD + N (dB) | Total Power<br>Consumption<br>(mW) |

|----------------------|-----------------------------|---------------------------------------------|----------------------------------------|-----------------------------|--------------------------------------|------------------------------------|

| AVDD = IOVDD = 3.3 V | Normal                      | 9.71                                        | 2.58                                   | -91                         | -97                                  | 40.56                              |

|                      | Extreme power saving        | 7.55                                        | 2.57                                   | -86                         | -96                                  | 33.40                              |

|                      | Power saving                | 7.99                                        | 2.57                                   | -87                         | -96                                  | 34.85                              |

|                      | Enhanced performance        | 10.97                                       | 2.58                                   | -91                         | -98                                  | 44.72                              |

| AVDD = IOVDD = 1.8 V | Normal                      | 7.29                                        | 0.37                                   | -87                         | -95                                  | 13.79                              |

|                      | Extreme power saving        | 5.38                                        | 0.37                                   | -81                         | -89                                  | 10.35                              |

|                      | Power saving                | 5.73                                        | 0.37                                   | -81                         | -90                                  | 10.98                              |

|                      | Enhanced Performance        | 8.62                                        | 0.37                                   | -87                         | -95                                  | 16.18                              |

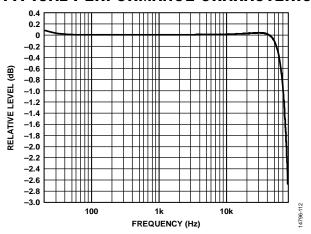

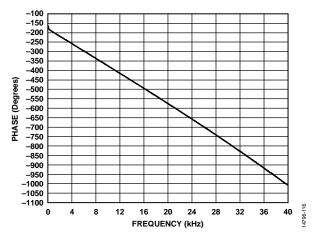

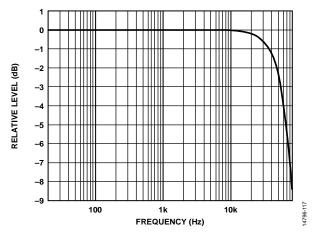

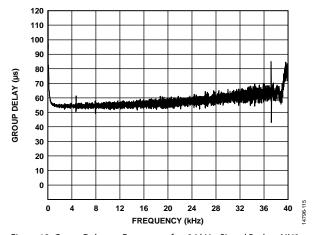

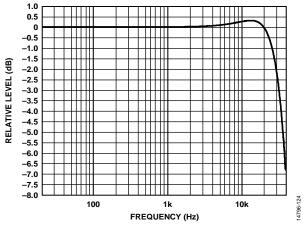

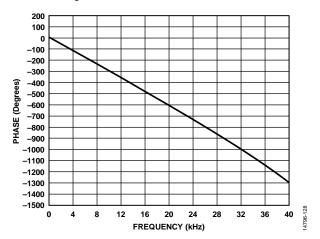

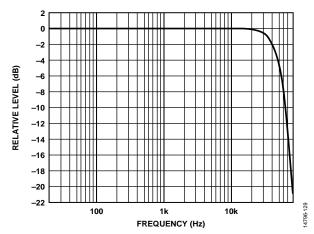

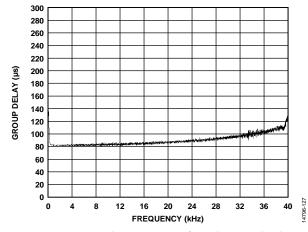

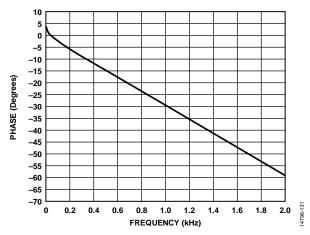

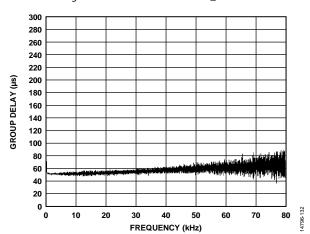

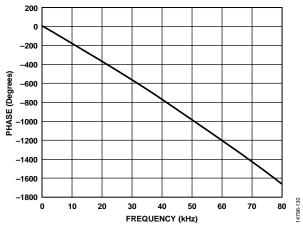

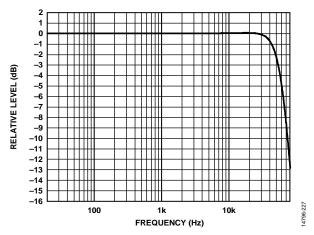

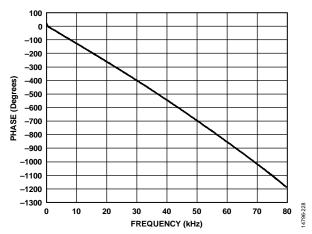

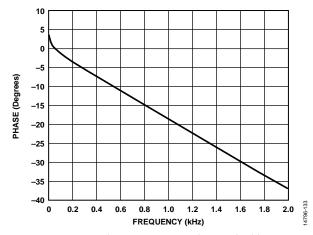

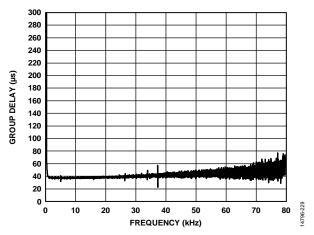

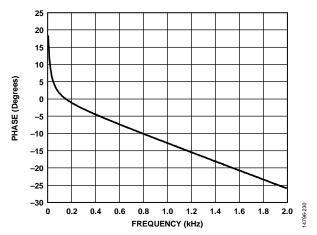

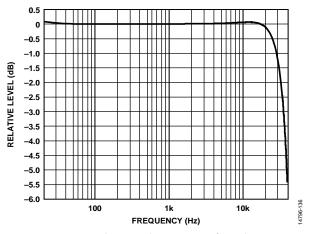

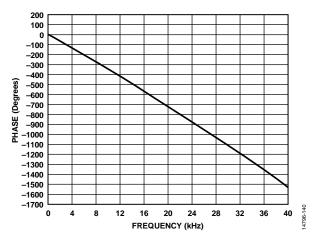

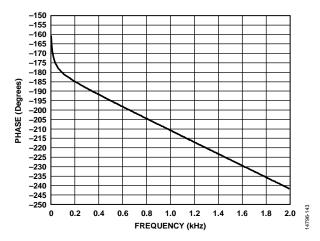

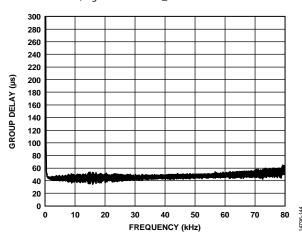

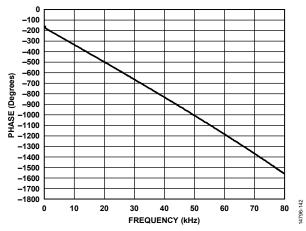

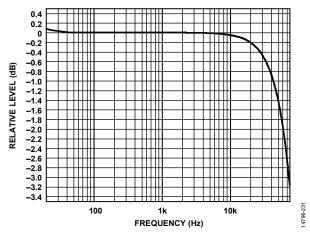

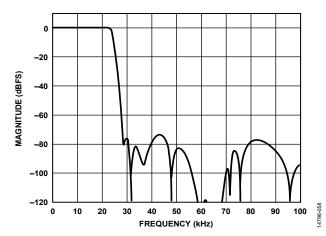

#### **DIGITAL FILTERS SPECIFICATIONS**

#### Table 6.

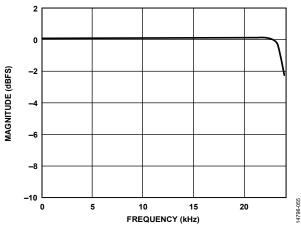

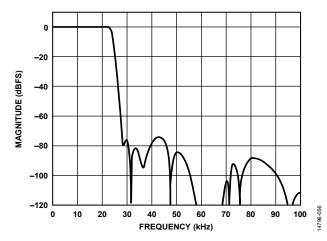

| Parameter                    | Test Conditions/Comments               | Min   | Тур | Max                 | Unit |

|------------------------------|----------------------------------------|-------|-----|---------------------|------|

| ADC INPUT TO DAC OUTPUT PATH |                                        |       |     |                     |      |

| Pass-Band Ripple             | DC to 20 kHz, f <sub>s</sub> = 768 kHz | -0.03 |     | +0.01               | dB   |

|                              | DC to 20 kHz, $f_s = 192 \text{ kHz}$  |       |     | ±0.02               | dB   |

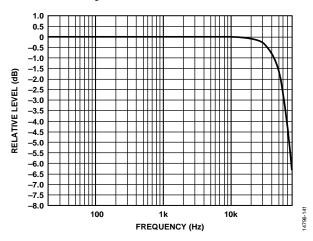

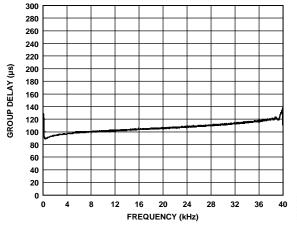

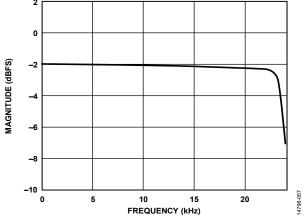

| SAMPLE RATE CONVERTER        |                                        |       |     |                     |      |

| Pass Band                    | LRCLK < 63 kHz                         | 0     |     | $0.475 \times f_S$  | kHz  |

|                              | 63 kHz < LRCLK <130 kHz                | 0     |     | $0.4286 \times f_S$ | kHz  |

|                              | LRCLK > 130 kHz                        | 0     |     | $0.4286 \times f_S$ | kHz  |

| Pass-Band Ripple             | Upsampling, 96 kHz                     | -0.27 |     | +0.05               | dB   |

|                              | Upsampling, 192 kHz                    | -0.06 |     | +0.05               | dB   |

|                              | Downsampling, 96 kHz                   | 0     |     | 0.07                | dB   |

|                              | Downsampling, 192 kHz                  | 0     |     | 0.07                | dB   |

| Input/Output Frequency Range |                                        | 8     |     | 192                 | kHz  |

| Dynamic Range                |                                        |       | 100 |                     | dB   |

| THD + N                      |                                        |       | -90 |                     | dB   |

| Start-Up Time                |                                        |       |     | 15                  | ms   |

| PDM MODULATOR                |                                        |       | •   |                     |      |

| Dynamic Range (A-Weighted)   |                                        |       | 112 |                     | dB   |

| THD + N                      |                                        |       | -92 |                     | dB   |

# **DIGITAL TIMING SPECIFICATIONS**

$-40^{\circ}\text{C} < T_{\text{A}} < +85^{\circ}\text{C}, \text{ IOVDD} = 1.71 \text{ V} \text{ to } 3.63 \text{ V}, \text{DVDD} = 1.045 \text{ V} \text{ to } 1.98 \text{ V}.$

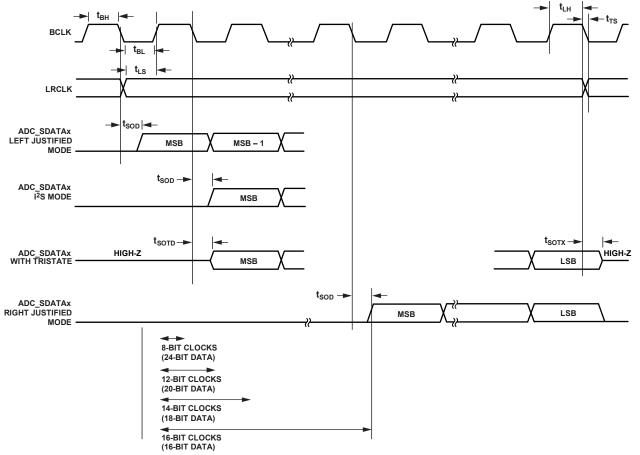

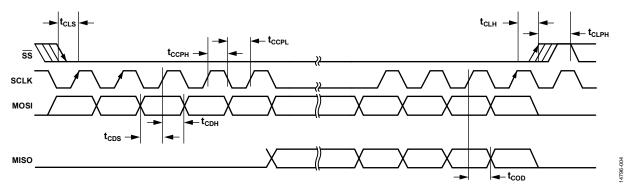

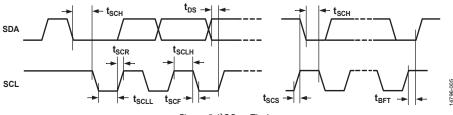

**Table 7. Digital Timing**

|                                   | Limit                   |                  |      |                                                                                                                    |

|-----------------------------------|-------------------------|------------------|------|--------------------------------------------------------------------------------------------------------------------|

| Parameter                         | t <sub>MIN</sub>        | t <sub>MAX</sub> | Unit | Description                                                                                                        |

| MASTER CLOCK (MCLK)               |                         |                  |      |                                                                                                                    |

| t <sub>MP</sub>                   | 37                      | 125              | ns   | MCLKIN period; 8 MHz to 27 MHz input clock using PLL                                                               |

| <b>t</b> mclk                     | 77                      | 82               | ns   | Internal MCLK period; direct MCLK and PLL output divided by 2                                                      |

| SERIAL PORT                       |                         |                  |      |                                                                                                                    |

| t <sub>BL</sub>                   | 40                      |                  | ns   | BCLK low pulse width (master and slave modes)                                                                      |

| t <sub>вн</sub>                   | 40                      |                  | ns   | BCLK high pulse width (master and slave modes)                                                                     |

| t <sub>LS</sub>                   | 10                      |                  | ns   | LRCLK setup; time to BCLK rising (slave mode)                                                                      |

| t <sub>LH</sub>                   | 10                      |                  | ns   | LRCLK hold; time from BCLK rising (slave mode)                                                                     |

| tss                               | 5                       |                  | ns   | DAC_SDATA setup; time to BCLK rising (master and slave modes)                                                      |

| <b>t</b> sH                       | 5                       |                  | ns   | DAC_SDATA hold; time from BCLK rising (master and slave modes)                                                     |

| t <sub>TS</sub>                   |                         | 10               | ns   | BCLK falling to LRCLK timing skew (master mode)                                                                    |

| tsod                              | 0                       | 34               | ns   | ADC_SDATAx delay; time from BCLK falling (master and slave modes)                                                  |

| t <sub>SOTD</sub>                 |                         | 30               | ns   | BCLK falling to ADC_SDATAx driven in time-division multiplexing (TDM) tristate mode                                |

| t <sub>SOTX</sub>                 |                         | 30               | ns   | BCLK falling to ADC_SDATAx tristate in TDM tristate mode                                                           |

| SERIRAL PERIPHERAL INTERFACE      |                         |                  |      |                                                                                                                    |

| (SPI) PORT                        |                         |                  |      |                                                                                                                    |

| <b>f</b> <sub>SCLK</sub>          |                         | 6.25             | MHz  | SCLK frequency                                                                                                     |

| <b>t</b> ccpl                     | 80                      |                  | ns   | SCLK pulse width low                                                                                               |

| <b>t</b> ccph                     | 80                      |                  | ns   | SCLK pulse width high                                                                                              |

| <b>t</b> cls                      | 5                       |                  | ns   | SS setup; time to SCLK rising                                                                                      |

| <b>t</b> clh                      | 100                     |                  | ns   | SS hold; time from SCLK rising                                                                                     |

| $t_CLPH$                          | 80                      |                  | ns   | SS pulse width high                                                                                                |

| t <sub>CDS</sub>                  | 10                      |                  | ns   | MOSI setup; time to SCLK rising                                                                                    |

| t <sub>CDH</sub>                  | 10                      |                  | ns   | MOSI hold; time from SCLK rising                                                                                   |

| t <sub>COD</sub>                  |                         | 101              | ns   | MISO delay; time from SCLK falling                                                                                 |

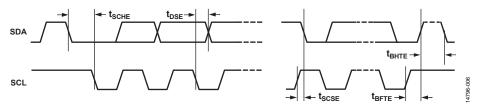

| I <sup>2</sup> C PORT             |                         |                  |      |                                                                                                                    |

| $f_{SCL}$                         |                         | 400              | kHz  | SCL frequency                                                                                                      |

| t <sub>SCLH</sub>                 | 0.6                     |                  | μs   | SCL high                                                                                                           |

| t <sub>SCLL</sub>                 | 1.3                     |                  | μs   | SCL low                                                                                                            |

| tscs                              | 0.6                     |                  | μs   | SCL rise setup time (to SDA falling), relevant for repeated start condition                                        |

| t <sub>SCR</sub>                  |                         | 250              | ns   | SCL and SDA rise time, C <sub>LOAD</sub> = 400 pF                                                                  |

| <b>t</b> <sub>SCH</sub>           | 0.6                     |                  | μs   | SCL fall hold time (from SDA falling), relevant for start condition                                                |

| t <sub>DS</sub>                   | 100                     |                  | ns   | SDA setup time (to SCL rising)                                                                                     |

| t <sub>SCF</sub>                  |                         | 250              | ns   | SCL and SDA fall time; C <sub>LOAD</sub> = 400 pF                                                                  |

| t <sub>BFT</sub>                  | 0.6                     |                  | μs   | SCL rise setup time (to SDA rising), relevant for stop condition                                                   |

| I <sup>2</sup> C EEPROM SELF BOOT |                         |                  |      |                                                                                                                    |

| t <sub>SCHE</sub>                 | $26 \times t_{MP} - 70$ |                  | ns   | SCL fall hold time (from SDA falling), relevant for start condition; $t_{MP}$ is the input clock on the MCLKIN pin |

| <b>t</b> scse                     | $38 \times t_{MP} - 70$ |                  | ns   | SCL rise setup time (to SDA falling), relevant for repeated start condition                                        |

| <b>t</b> <sub>BFTE</sub>          | $70 \times t_{MP} - 70$ |                  | ns   | SCL rise setup time (to SDA rising), relevant for stop condition                                                   |

| t <sub>DSE</sub>                  | $6 \times t_{MP} - 70$  |                  | ns   | Delay from SCL falling to SDA changing                                                                             |

| <b>t</b> внте                     | 32 × t <sub>MP</sub>    |                  | ns   | SDA rising in self boot stop condition to SDA falling edge for external master start condition                     |

|                                      |                  | Limit              |      |                                                                 |

|--------------------------------------|------------------|--------------------|------|-----------------------------------------------------------------|

| Parameter                            | t <sub>MIN</sub> | t <sub>MAX</sub>   | Unit | Description                                                     |

| MULTIPURPOSE AND POWER-<br>DOWN PINS |                  |                    |      |                                                                 |

| t <sub>GIL</sub>                     |                  | $1.5 \times 1/f_s$ | μs   | MPx input latency; time until high or low value is read by core |

| t <sub>RLPW</sub>                    | 20               |                    | ns   | PD low pulse width                                              |

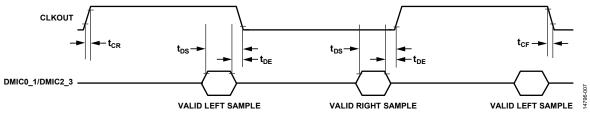

| DIGITAL MICROPHONE                   |                  |                    |      |                                                                 |

| t <sub>CF</sub>                      |                  | 20                 | ns   | Digital microphone clock fall time                              |

| <b>t</b> cr                          |                  | 20                 | ns   | Digital microphone clock rise time                              |

| t <sub>DS</sub>                      | 40               |                    |      | Digital microphone valid data start time                        |

| t <sub>DE</sub>                      |                  | 0                  | ns   | Digital microphone valid data end time                          |

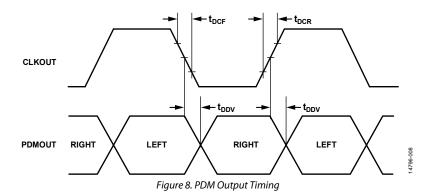

| PDM OUTPUT                           |                  |                    |      |                                                                 |

| <b>t</b> <sub>DCF</sub>              |                  | 20                 | ns   | PDM clock fall time                                             |

| t <sub>DCR</sub>                     |                  | 20                 | ns   | PDM clock rise time                                             |

| t <sub>DDV</sub>                     | 0                | 30                 | ns   | PDM delay time for valid data                                   |

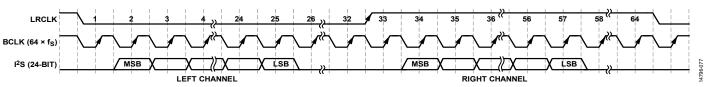

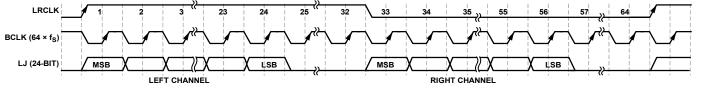

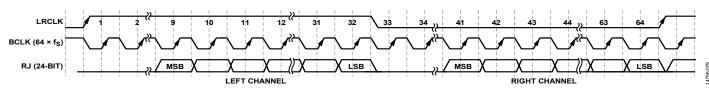

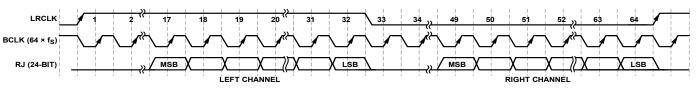

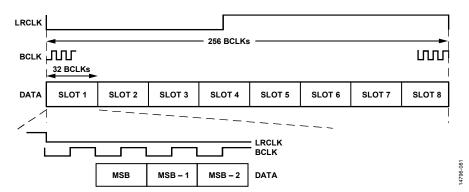

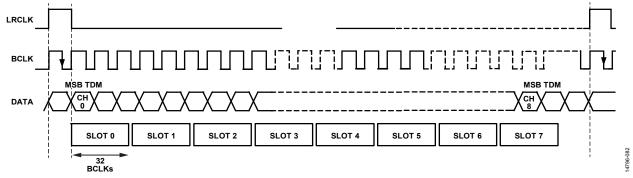

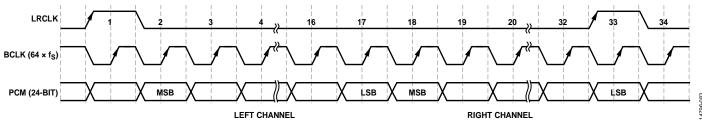

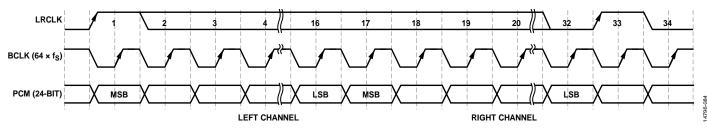

### **Digital Timing Diagrams**

Figure 2. Serial Input Port Timing

Figure 3. Serial Output Port Timing

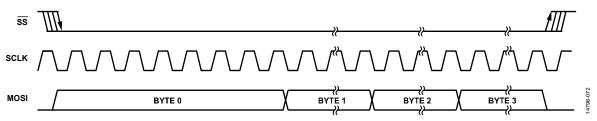

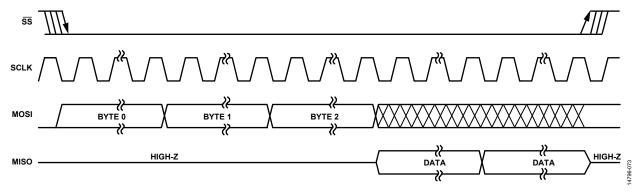

Figure 4. SPI Port Timing

Figure 5. I<sup>2</sup>C Port Timing

Figure 6. I<sup>2</sup>C EEPROM Self Boot Timing

Figure 7. Digital Microphone Timing

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 8.

| Parameter                           | Rating                 |

|-------------------------------------|------------------------|

| Power Supplies (AVDD, IOVDD)        | -0.3 V to +3.63 V      |

| Digital Supply (DVDD)               | −0.3 V to +1.98 V      |

| Input Current (Except Supply Pins)  | ±20 mA                 |

| Analog Input Voltage (Signal Pins)  | -0.3 V to AVDD + 0.3 V |

| Digital Input Voltage (Signal Pins) | -0.3 to IOVDD + 0.3 V  |

| Operating Temperature Range (Case)  | -40°C to +85°C         |

| Storage Temperature Range           | −65°C to +150°C        |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.  $\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure

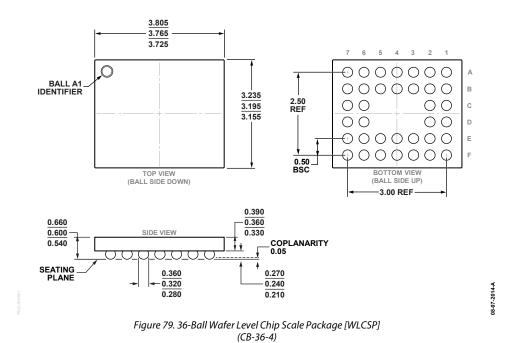

For more information, see the AN-617 Application Note, *Wafer Level Chip Scale Package*.

**Table 9. Thermal Resistance**

| Package Type         | θ <sub>JA</sub> | Unit |

|----------------------|-----------------|------|

| CB-36-4 <sup>1</sup> | 36              | °C/W |

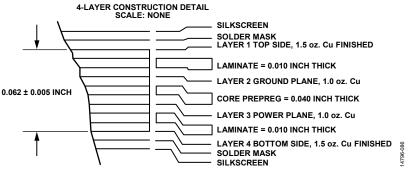

<sup>&</sup>lt;sup>1</sup> Thermal impedance simulated values are based on a 4-layer PCB with two signal layers and two power planes using natural convection cooling. See JEDEC JESD51-9.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

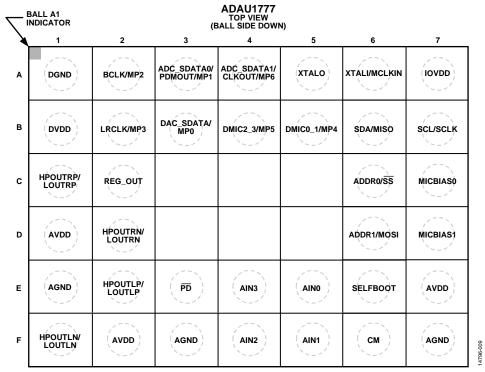

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 9. Pin Configuration

**Table 10. Pin Function Descriptions**

| Pin No. | Mnemonic              | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                |

|---------|-----------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | DGND                  | PWR               | Digital Ground. Tie the AGND and DGND pins directly together in a common ground plane.                                                                                                                                                                                                                                                                     |

| A2      | BCLK/MP2              | D_IO              | Serial Data Port Bit Clock (BCLK).                                                                                                                                                                                                                                                                                                                         |

|         |                       |                   | Multipurpose Pin (MP2).                                                                                                                                                                                                                                                                                                                                    |

| A3      | ADC_SDATA0/PDMOUT/MP1 | D_IO              | ADC Serial Data Output 0 (ADC_SDATA0).                                                                                                                                                                                                                                                                                                                     |

|         |                       |                   | Stereo PDM Output to Drive a High Efficiency Class-D Amplifier (PDMOUT).                                                                                                                                                                                                                                                                                   |

|         |                       |                   | Multipurpose Pin (MP1).                                                                                                                                                                                                                                                                                                                                    |

| A4      | ADC_SDATA1/CLKOUT/MP6 | D_IO              | Serial Data Output 1 (ADC_SDATA1).                                                                                                                                                                                                                                                                                                                         |

|         |                       |                   | Master Clock Output/Clock for the Digital Microphone Input and PDM Output (CLKOUT).                                                                                                                                                                                                                                                                        |

|         |                       |                   | Multipurpose Pin (MP6).                                                                                                                                                                                                                                                                                                                                    |

| A5      | XTALO                 | A_OUT             | Crystal Clock Output. This pin is the output of the crystal amplifier; do not use this pin to provide a clock to other ICs in the system. If a master clock output is needed, use CLKOUT (Pin A4).                                                                                                                                                         |

| A6      | XTALI/MCLKIN          | D_IN              | Crystal Clock Input (XTALI).                                                                                                                                                                                                                                                                                                                               |

|         |                       |                   | Master Clock Input (MCLKIN).                                                                                                                                                                                                                                                                                                                               |

| A7      | IOVDD                 | PWR               | Supply for Digital Input and Output Pins. The digital output pins are supplied from IOVDD; thus, the IOVDD voltage level is the highest input voltage that can be present on the digital input pins. The current draw of this pin is variable because it is dependent on the loads of the digital outputs. Decouple IOVDD to DGND with a 0.1 µF capacitor. |

| B1      | DVDD                  | PWR               | Digital Core Supply. The digital supply can be generated from an on-board regulator or supplied directly from an external supply. In each case, decouple DVDD to DGND with a 0.1 µF capacitor.                                                                                                                                                             |

| B2      | LRCLK/MP3             | D_IO              | Serial Data Port Frame Clock (LRCLK).                                                                                                                                                                                                                                                                                                                      |

|         |                       |                   | Multipurpose Pin (MP3).                                                                                                                                                                                                                                                                                                                                    |

| B3      | DAC_SDATA/MP0         | D_IO              | DAC Serial Input Data (DAC_SDATA).                                                                                                                                                                                                                                                                                                                         |

|         |                       |                   | Multipurpose Pin (MP0).                                                                                                                                                                                                                                                                                                                                    |

| B4      | DMIC2_3/MP5           | D_IN              | Digital Microphone Stereo Input 2 and Digital Microphone Stereo Input 3 (DMIC2_3).  Multipurpose Pin (MP5).                                                                                                                                                                                                                                                |

| Pin No. | Mnemonic       | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                              |

|---------|----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B5      | DMIC0_1/MP4    | D_IN              | Digital Microphone Stereo Input 0 and Digital Microphone Stereo Input 1 (DMICO_1).                                                                                                                                                                                                                                                                       |

|         |                |                   | Multipurpose Pin (MP4).                                                                                                                                                                                                                                                                                                                                  |

| B6      | SDA/MISO       | D_IO              | I <sup>2</sup> C Data (SDA). This pin is a bidirectional open-collector. The line connected to this pin                                                                                                                                                                                                                                                  |

|         |                |                   | must have a 2.0 kΩ pull-up resistor.                                                                                                                                                                                                                                                                                                                     |

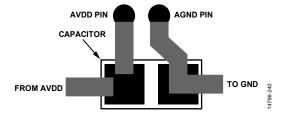

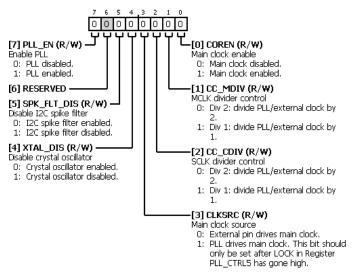

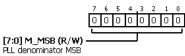

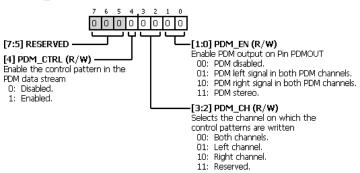

|         |                |                   | SPI Data Output (MISO). This SPI data output reads back registers and memory locations. It is tristated when an SPI read is not active.                                                                                                                                                                                                                  |