AVAILABLE

## **Gigabit Multimedia Serial Link with Spread Spectrum and Full-Duplex Control Channel**

### **General Description**

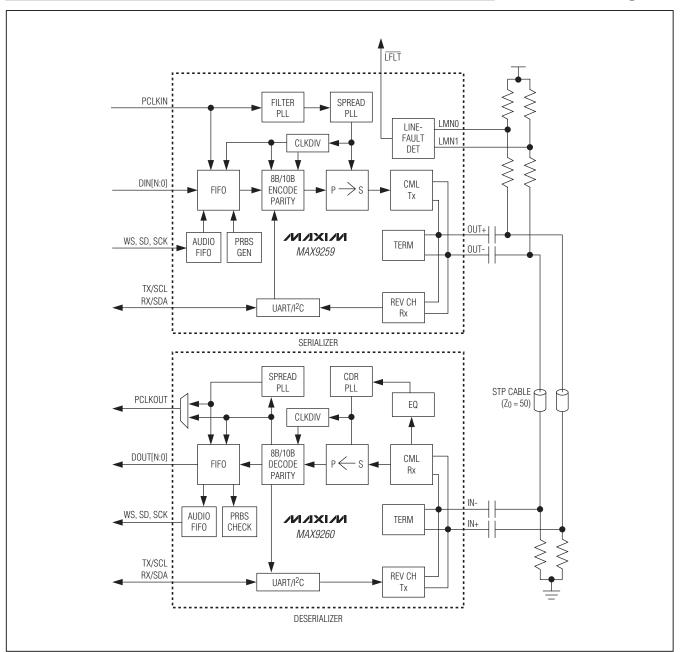

The MAX9259/MAX9260 chipset presents Maxim's

gigabit multimedia serial link (GMSL) technology. The

MAX9259 serializer pairs with the MAX9260 deserializer

to form a complete digital serial link for joint transmission

The MAX9259/MAX9260 allow a maximum serial payload data rate of 2.5Gbps for a 15m shielded twisted-pair

(STP) cable. The 24-bit or 32-bit width parallel interface operates up to a maximum bus clock of 104MHz or

78MHz, respectively. This serial link supports display

panels from QVGA (320 x 240) up to XGA (1280 x 768),

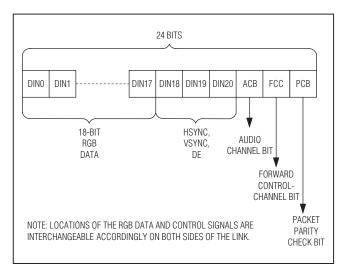

The 24-bit or 32-bit mode handles 21 or 29 bits of data,

along with an I<sup>2</sup>S input, supporting 4- to 32-bit audio

or microcontroller (µC) resides either on the MAX9259

(for video display) or on the MAX9260 (for image sens-

ing). In addition, the control channel enables ECU/µC

control of peripherals in the remote side of the serial link

through I<sup>2</sup>C (base mode) or a user-defined full-duplex

The MAX9259 serializer driver preemphasis and chan-

nel equalizer on the MAX9260 extend the link length and

enhance the link reliability. Spread spectrum is available on the MAX9259/MAX9260 to reduce EMI on the serial

and parallel output data signals. The differential link

complies with the ISO 10605 and IEC 61000-4-2 ESD-

The core supplies for the MAX9259/MAX9260 are 1.8V

and 3.3V, respectively. Both devices use an I/O sup-

of high-speed video, audio, and control data.

or dual-view WVGA (2 x 854 x 480).

UART format (bypass mode).

protection standards.

#### Features

- 2.5Gbps Payload Rate, AC-Coupled Serial Link with 8B/10B Line Coding

- ◆ 24-Bit or 32-Bit Programmable Parallel Input Bus Supports Up to XGA (1280 x 768) or Dual-View WVGA (2 x 854 x 480) Panels with 18-Bit or 24-Bit Color

- 8.33MHz to 104MHz (24-Bit Bus) or 6.25MHz to 78MHz (32-Bit Bus) Parallel Data Rate

- Support Two/Three 10-Bit Camera Links at 104MHz/78MHz Maximum Pixel Clock

- ♦ 4-Bit to 32-Bit Word Length, 8kHz to 192kHz I<sup>2</sup>S Audio Channel Supports High-Definition Audio

- Embedded Half-/Full-Duplex Bidirectional Control Channel (100kbps to 1Mbps)

- Separate Interrupt Signal Supports Touch-Screen **Functions for Display Panels**

- Remote-End I<sup>2</sup>C Master for Peripherals

- Preemphasis Line Driver (MAX9259)/Line Equalizer (MAX9260)

- Programmable Spread Spectrum on the Serial or Parallel Data Outputs Reduce EMI

- Deserializer Does Not Require an External Clock

- Auto Data-Rate Detection Allows "On-The-Fly" **Data-Rate Change**

- Ground, Battery, or Open Link

- ISO 10605 and IEC 61000-4-2 ESD Protection

- ♦ -40°C to +105°C Operating Temperature Range

#### **Ordering Information**

| PART           | TEMP RANGE      | PIN-PACKAGE |

|----------------|-----------------|-------------|

| MAX9259GCB/V+  | -40°C to +105°C | 64 TQFP-EP* |

| MAX9259GCB/V+T | -40°C to +105°C | 64 TQFP-EP* |

| MAX9259GTN/V+T | -40°C to +105°C | 56 TQFN-EP* |

| MAX9260GCB/V+  | -40°C to +105°C | 64 TQFP-EP* |

| MAX9260GCB/V+T | -40°C to +105°C | 64 TQFP-EP* |

N denotes an automotive qualified part.

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

T = Tape and reel.

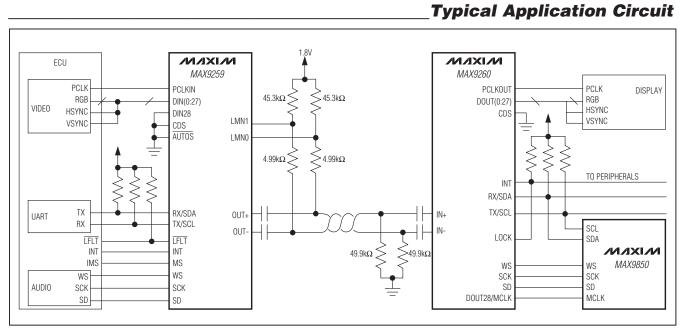

Typical Applications Circuit appears at end of data sheet.

Maxim Integrated Products 1

MAX9259/MAX9260

word lengths and an 8kHz to 192kHz sample rate. The embedded control channel forms a full-duplex, differential 100kbps to 1Mbps UART link between the serializer and deserializer. The host electronic control unit (ECU)

- Input Clock PLL Jitter Attenuator (MAX9259)

- Built-In PRBS Generator/Checker for BER Testing

- Line-Fault Detector Detects Wire Shorts to

- Patent Pending

ply from 1.8V to 3.3V. These devices are available in a 64-pin TQFP package (10mm x 10mm) and a 56-pin TQFN package (8mm x 8mm x 0.75mm) with an exposed pad. Electrical performance is guaranteed over the -40°C to +105°C automotive temperature range.

#### Applications

High-Speed Serial-Data Transmission for Display High-Speed Serial-Data Transmission for Image Sensing

Automotive Navigation, Infotainment, and Image-Sensing Systems

## MIXI/M

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

AVDD to AGND

| MAX92590.5V to +1.9V                                    |

|---------------------------------------------------------|

| MAX92600.5V to +3.9V                                    |

| DVDD to GND (MAX9259)0.5V to +1.9V                      |

| DVDD to DGND (MAX9260)0.5V to +3.9V                     |

| IOVDD to GND (MAX9259)0.5V to +3.9V                     |

| IOVDD to IOGND (MAX9260)0.5V to +3.9V                   |

| Any Ground to Any Ground0.5V to +0.5V                   |

| OUT+, OUT- to AGND (MAX9259)0.5V to +1.9V               |

| IN+, IN- to AGND (MAX9260)0.5V to +1.9V                 |

| LMN_ to GND (MAX9259)                                   |

| (60k $\Omega$ source impedance)0.5V to +3.9V            |

| All Other Pins to GND (MAX9259)0.5V to (IOVDD + 0.5V)   |

| All Other Pins to IOGND (MAX9260)0.5V to (IOVDD + 0.5V) |

| OUT+, OUT- Short Circuit to Ground or                   |

| Supply (MAX9259)Continuous                              |

| IN+, IN- Short Circuit to Ground or                     |

| Supply (MAX9260)Continuous                              |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )   |

| 64-Pin TQFP (derate 31.3mW/°C above +70°C)2508mW        |

| 56-Pin TQFN (derate 47.6mW/°C above +70°C)3809.5mW      |

|                                                         |

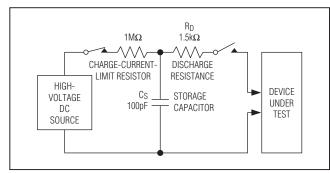

| ESD Protection                                                               |        |

|------------------------------------------------------------------------------|--------|

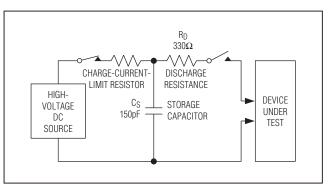

| Human Body Model (R <sub>D</sub> = $1.5k\Omega$ , C <sub>S</sub> = $100pF$ ) |        |

| (OUT+, OUT-) to AGND (MAX9259)                                               | ±8kV   |

| (IN+, IN-) to AGND (MAX9260)                                                 |        |

| All Other Pins to Any Ground (MAX9259)                                       | ±4kV   |

| All Other Pins to Any Ground (MAX9260)                                       |        |

| IEC 61000-4-2 ( $R_D = 330\Omega$ , $C_S = 150pF$ )                          |        |

| Contact Discharge                                                            |        |

| (OUT+, OUT-) to AGND (MAX9259)                                               | ±10kV  |

| (IN+, IN-) to AGND (MAX9260)                                                 | ±8kV   |

| Air Discharge                                                                |        |

| (OUT+, OUT-) to AGND (MAX9259)                                               | ±12kV  |

| (IN+, IN-) to AGND (MAX9260)                                                 | ±10kV  |

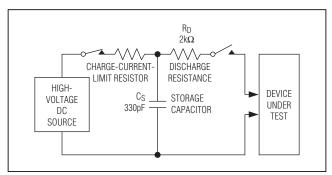

| ISO 10605 (R <sub>D</sub> = $2k\Omega$ , C <sub>S</sub> = $330pF$ )          |        |

| Contact Discharge                                                            |        |

| (OUT+, OUT-) to AGND (MAX9259)                                               |        |

| (IN+, IN-) to AGND (MAX9260)                                                 | ±8kV   |

| Air Discharge                                                                |        |

| (OUT+, OUT-) to AGND (MAX9259)                                               |        |

| (IN+, IN-) to AGND (MAX9260)                                                 |        |

| Operating Temperature Range40                                                |        |

| Junction Temperature                                                         |        |

| Storage Temperature Range65                                                  |        |

| Lead Temperature (soldering, 10s)                                            |        |

| Soldering Temperature (reflow)                                               | +260°C |

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

64 TQFP

Junction-to-Ambient Thermal Resistance  $(\theta_{JA})$ ......31.9°C/W Junction-to-Case Thermal Resistance  $(\theta_{JC})$ ......1°C/W

56 TQFN

| Junction-to-Ambient Thermal Resistance (0JA)          | 21°C/W |

|-------------------------------------------------------|--------|

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 1°C/W  |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## MAX9259 DC ELECTRICAL CHARACTERISTICS

$(VDVDD = VAVDD = 1.7V \text{ to } 1.9V, VIOVDD = 1.7V \text{ to } 3.6V, R_L = 100\Omega \pm 1\%$  (differential), T<sub>A</sub> = -40°C to +105°C, unless otherwise noted. Typical values are at V<sub>DVDD</sub> = V<sub>AVDD</sub> = V<sub>IOVDD</sub> = 1.8V, T<sub>A</sub> = +25°C.)

| PARAMETER                                                                                 | SYMBOL |                          | MIN                          | TYP              | MAX | UNITS            |    |  |  |

|-------------------------------------------------------------------------------------------|--------|--------------------------|------------------------------|------------------|-----|------------------|----|--|--|

| SINGLE-ENDED INPUTS (DIN_, PCLKIN, PWDN, SSEN, BWS, ES, DRS, MS, CDS, AUTOS, SD, SCK, WS) |        |                          |                              |                  |     |                  |    |  |  |

| High-Level Input Voltage                                                                  | VIH1   |                          |                              | 0.65 x<br>Viovdd |     |                  | V  |  |  |

| Low-Level Input Voltage                                                                   | VIL1   |                          |                              |                  |     | 0.35 x<br>Viovdd | V  |  |  |

| Input Current                                                                             | liN1   | $V_{IN} = 0$ to $V_{IO}$ | -10                          |                  | +10 | μA               |    |  |  |

| Input Clamp Voltage                                                                       | VCL    | I <sub>CL</sub> = -18mA  |                              |                  |     | -1.5             | V  |  |  |

| SINGLE-ENDED OUTPUT (INT)                                                                 |        |                          |                              |                  |     |                  |    |  |  |

| High-Level Output Voltage                                                                 | VOH1   | IOH = -2mA               |                              | VIOVDD<br>- 0.2  |     |                  | V  |  |  |

| Low-Level Output Voltage                                                                  | VOL1   | $I_{OL} = 2mA$           |                              |                  |     | 0.2              | V  |  |  |

| Output Short Circuit Ourront                                                              | 100    |                          | VIOVDD = 3.0V to 3.6V        | 16               | 35  | 64               |    |  |  |

| Output Short-Circuit Current                                                              | los    | VO = 0V                  | $V_{IOVDD} = 1.7V$ to $1.9V$ | 3                | 12  | 21               | mA |  |  |

### MAX9259 DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{DVDD} = V_{AVDD} = 1.7V \text{ to } 1.9V, V_{IOVDD} = 1.7V \text{ to } 3.6V, R_L = 100\Omega \pm 1\%$  (differential),  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{DVDD} = V_{AVDD} = V_{IOVDD} = 1.8V$ ,  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                        | SYMBOL           | CONDITIONS                      |                                                                            | MIN             | TYP | MAX             | UNITS  |

|------------------------------------------------------------------|------------------|---------------------------------|----------------------------------------------------------------------------|-----------------|-----|-----------------|--------|

| I <sup>2</sup> C AND UART I/O, OPEN-DRAI                         | N OUTPUTS        | (RX/SDA, TX/S                   | CL, LFLT)                                                                  |                 |     |                 |        |

| High-Level Input Voltage                                         | VIH2             |                                 |                                                                            | 0.7 x<br>VIOVDD |     |                 | V      |

| Low-Level Input Voltage                                          | VIL2             |                                 |                                                                            |                 |     | 0.3 x<br>Viovdd | V      |

| Input Current                                                    | lin2             | VIN = 0 to VIO                  | /DD (Note 2)                                                               | -110            |     | +5              | μA     |

| Low-Level Open-Drain Output<br>Voltage                           | V <sub>OL2</sub> | I <sub>OL</sub> = 3mA           | $V_{IOVDD} = 1.7V \text{ to } 1.9V$<br>$V_{IOVDD} = 3.0V \text{ to } 3.6V$ |                 |     | 0.4<br>0.3      | V      |

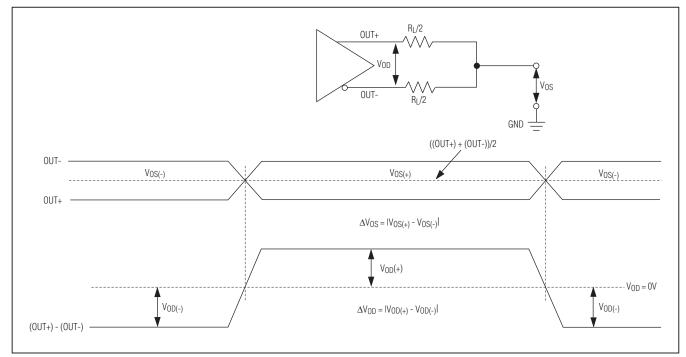

| DIFFERENTIAL OUTPUT (OUT+                                        | , OUT-)          | 1                               |                                                                            | I               |     |                 |        |

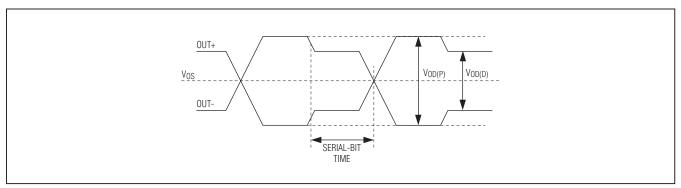

| î                                                                |                  | Preemphasis of                  | off (Figure 1)                                                             | 300             | 400 | 500             |        |

| Differential Output Voltage                                      | Vod              | 3.3dB preemp<br>(Figure 2)      | hasis setting, V <sub>OD(P)</sub>                                          | 350             |     | 610             | mVp-I  |

|                                                                  |                  | 3.3dB deempt<br>(Figure 2)      | nasis setting, V <sub>OD(D)</sub>                                          | 240             |     | 425             |        |

| Change in VOD Between<br>Complementary Output States             | ΔV <sub>OD</sub> |                                 |                                                                            |                 |     | 15              | mV     |

| Output Offset Voltage,<br>(Vout+ + Vout-)/2 = Vos                | Vos              | Preemphasis of                  | off                                                                        | 1.1             | 1.4 | 1.56            | V      |

| Change in V <sub>OS</sub> Between<br>Complementary Output States | ΔV <sub>OS</sub> |                                 |                                                                            |                 |     | 15              | mV     |

| Output Short-Circuit Current                                     | los              | Vout+ or Vou                    |                                                                            | -60             |     |                 | mA     |

|                                                                  | 103              | $V_{OUT+}$ or $V_{OUT-} = 1.9V$ |                                                                            |                 |     | 25              | 111/ \ |

| Magnitude of Differential Output<br>Short-Circuit Current        | IOSD             | V <sub>OD</sub> = 0V            |                                                                            |                 |     | 25              | mA     |

| Output Termination Resistance (Internal)                         | Ro               | From OUT+, C                    | OUT- to VAVDD                                                              | 45              | 54  | 63              | Ω      |

| REVERSE CONTROL-CHANNE                                           | 1                | (OUT+, OUT-)                    |                                                                            |                 |     |                 |        |

| High Switching Threshold                                         | VCHR             |                                 |                                                                            |                 |     | 27              | mV     |

| Low Switching Threshold                                          | VCLR             |                                 |                                                                            | -27             |     |                 | mV     |

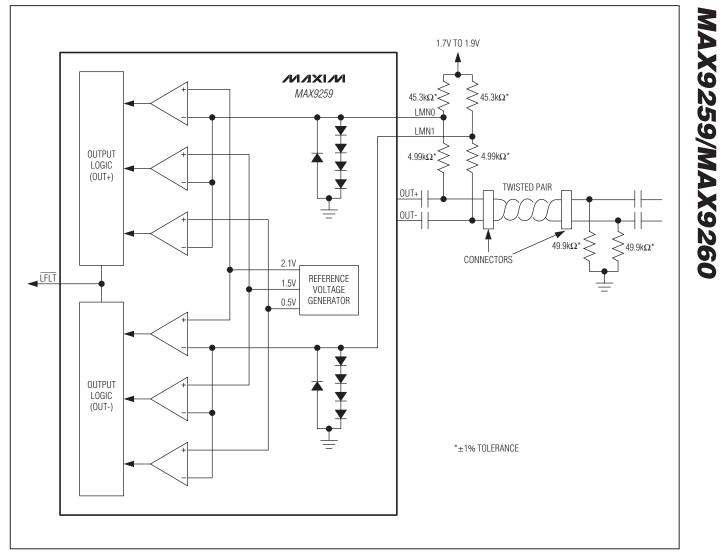

| LINE-FAULT-DETECTION INPU                                        |                  |                                 |                                                                            |                 |     |                 |        |

| Short-to-GND Threshold                                           | VTG              | Figure 3                        |                                                                            |                 |     | 0.3             | V      |

| Normal Thresholds                                                | VTN              | Figure 3                        |                                                                            | 0.57            |     | 1.07            | V      |

| Open Thresholds                                                  | V <sub>TO</sub>  | Figure 3                        |                                                                            | 1.45            |     | VIO+<br>0.06    | V      |

| Open Input Voltage                                               | VIO              | Figure 3                        |                                                                            | 1.47            |     | 1.75            | V      |

| Short-to-Battery Threshold                                       | VTE              | Figure 3                        |                                                                            | 2.47            |     |                 | V      |

| POWER SUPPLY                                                     | 1                | 1                               |                                                                            |                 |     |                 |        |

|                                                                  |                  |                                 | fPCLKIN = 16.6MHz                                                          |                 | 100 | 125             |        |

| Worst-Case Supply Current                                        | Iwcs             | BWS = GND                       | fPCLKIN = 33.3MHz                                                          |                 | 105 | 145             | mA     |

| (Figure 4)                                                       |                  |                                 | fPCLKIN = 66.6MHz                                                          |                 | 116 | 155             | 11174  |

|                                                                  |                  |                                 | fPCLKIN = 104MHz                                                           |                 | 135 | 175             |        |

| Sleep-Mode Supply Current                                        | Iccs             |                                 |                                                                            |                 | 40  | 110             | μΑ     |

| Power-Down Supply Current                                        | Iccz             | PWDN = GND                      |                                                                            |                 | 5   | 70              | μA     |

## MAX9259 AC ELECTRICAL CHARACTERISTICS

$(V_{DVDD} = V_{AVDD} = 1.7V \text{ to } 1.9V, V_{IOVDD} = 1.7V \text{ to } 3.6V, R_L = 100\Omega \pm 1\%$  (differential), TA = -40°C to +105°C, unless otherwise noted. Typical values are at V<sub>DVDD</sub> = V<sub>AVDD</sub> = V<sub>IOVDD</sub> = 1.8V, TA = +25°C.)

| PARAMETER                                 | SYMBOL              |                                                                                                       | CONDITIONS                                 | MIN            | TYP  | MAX               | UNITS   |

|-------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------|------|-------------------|---------|

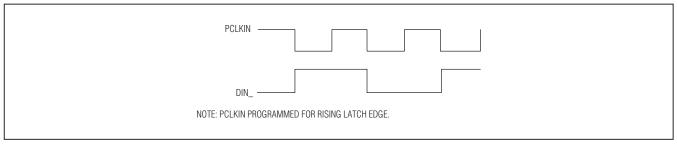

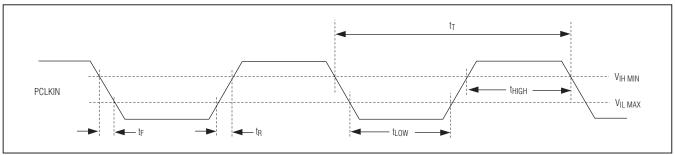

| PARALLEL CLOCK INPUT (PCL                 | KIN)                | •                                                                                                     |                                            |                |      |                   |         |

|                                           |                     | VBWS = VGN                                                                                            | id, Vdrs = Viovdd                          | 8.33           |      | 16.66             |         |

|                                           | £                   | VBWS = VGN                                                                                            | id, Vdrs = Vgnd                            | 16.66          |      | 104               |         |

| Clock Frequency                           | <sup>f</sup> PCLKIN | VBWS = VION                                                                                           | /DD, VDRS = VIOVDD                         | 6.25           |      | 12.5              | MHz     |

|                                           |                     | VBWS = VION                                                                                           | /dd, Vdrs = Vgnd                           | 12.5           |      | 78                |         |

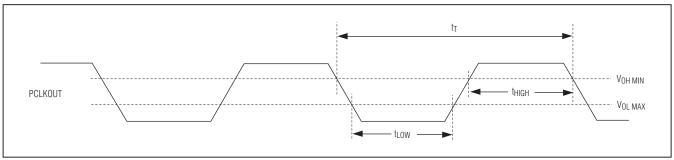

| Clock Duty Cycle                          | DC                  | thigh/tt or t                                                                                         | _OW/tT (Figure 5)                          | 35             | 50   | 65                | %       |

| Clock Transition Time                     | tR, tF              | (Figure 5)                                                                                            |                                            |                |      | 4                 | ns      |

| Clock Jitter                              | tj                  | 3.125Gbps,                                                                                            | 300kHz sinusoidal jitter                   |                |      | 800               | PS(P-P) |

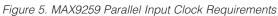

| I <sup>2</sup> C/UART PORT TIMING (Note 3 | )                   | -                                                                                                     |                                            |                |      |                   |         |

| Output Rise Time                          | t <sub>R</sub>      | 30% to 70%,<br>pullup to IO\                                                                          | $C_L = 10$ pF to 100pF, 1k $\Omega$<br>/DD | 20             |      | 150               | ns      |

| Output Fall Time                          | tF                  | 70% to 30%,<br>pullup to IO\                                                                          | $C_L = 10$ pF to 100pF, 1k $\Omega$        | 20             |      | 150               | ns      |

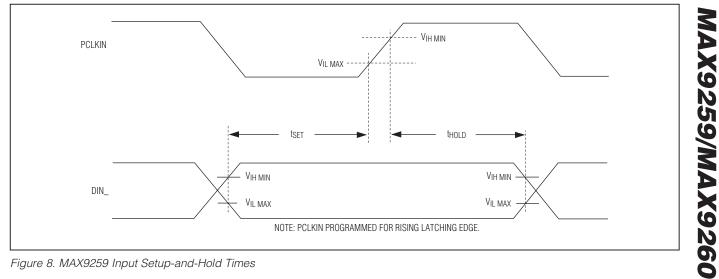

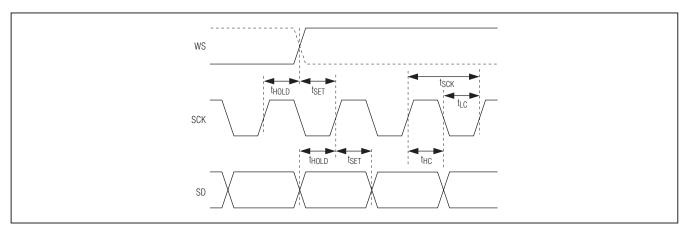

| Input Setup Time                          | tSET                | I <sup>2</sup> C only (Fig                                                                            | ure 6)                                     | 100            |      |                   | ns      |

| Input Hold Time                           | thold               | I <sup>2</sup> C only (Fig                                                                            | ure 6)                                     | 0              |      |                   | ns      |

| SWITCHING CHARACTERISTICS                 | 6 (Note 3)          |                                                                                                       |                                            |                |      |                   |         |

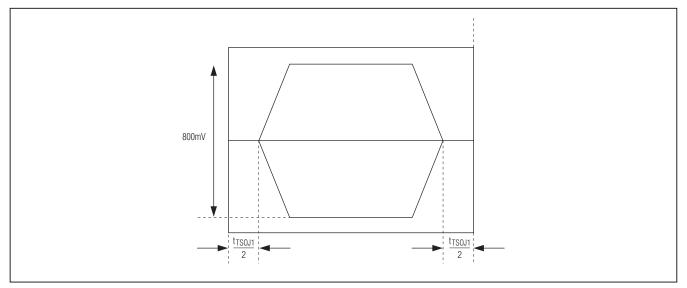

| Differential Output Rise-and-Fall<br>Time | tR, tF              | 20% to 80%, $V_{OD} \ge 400 \text{mV}$ , $R_L = 100\Omega$ , serial-data rate = 3.125Gbps             |                                            |                | 90   | 150               | ps      |

| Total Serial Output Jitter                | ttsoj1              | 3.125Gbps PRBS signal, measured at V <sub>OD</sub> = 0V differential, preemphasis disabled (Figure 7) |                                            |                | 0.25 |                   | UI      |

| Deterministic Serial Output Jitter        | tDSOJ2              | 3.125Gbps F                                                                                           | PRBS signal                                |                | 0.15 |                   | UI      |

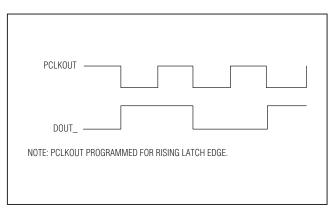

| Parallel Data Input Setup Time            | tSET                | (Figure 8)                                                                                            |                                            | 1              |      |                   | ns      |

| Parallel Data Input Hold Time             | thold               | (Figure 8)                                                                                            |                                            | 1.5            |      |                   | ns      |

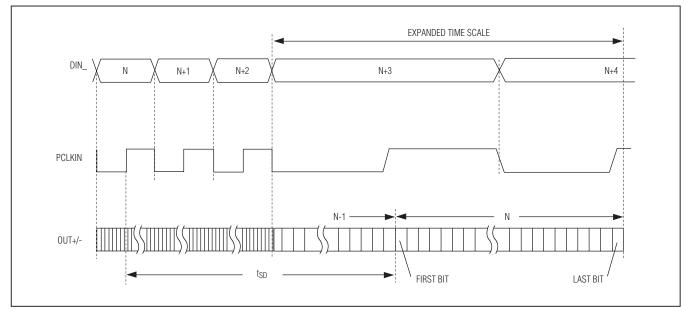

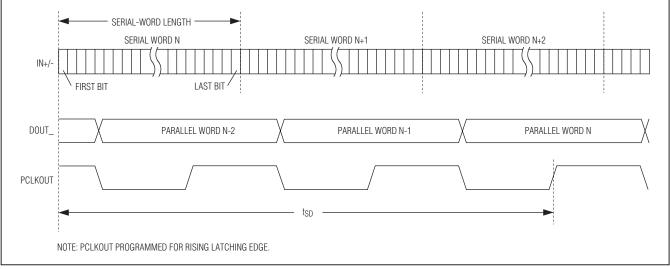

|                                           |                     |                                                                                                       | Spread spectrum enabled                    |                |      | 2830              | D'1     |

| Serializer Delay (Note 4)                 | tsD                 | (Figure 9)                                                                                            | Spread spectrum disabled                   |                |      | 270               | Bits    |

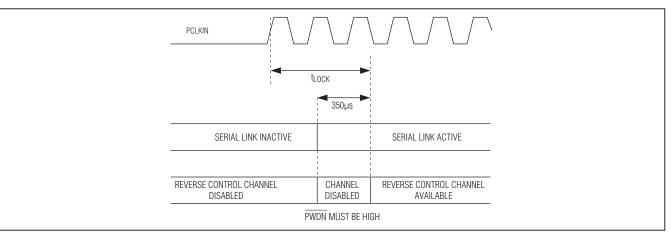

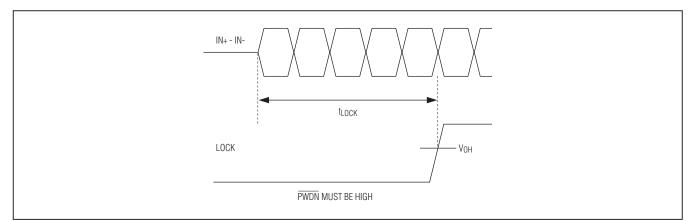

| Link Start Time                           | <b>t</b> LOCK       | (Figure 10)                                                                                           | 1                                          |                |      | 3.5               | ms      |

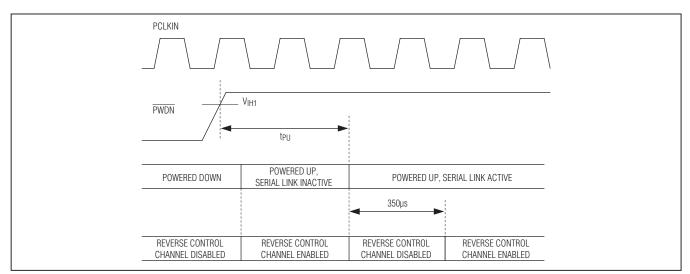

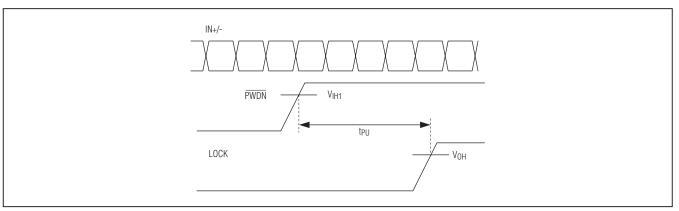

| Power-Up Time                             | tPU                 | (Figure 11)                                                                                           |                                            |                |      | 3.5               | ms      |

| I <sup>2</sup> S INPUT TIMING             |                     |                                                                                                       |                                            |                |      |                   |         |

| WS Frequency                              | fws                 | (Table 4)                                                                                             |                                            | 8              |      | 192               | kHz     |

| Sample Word Length                        | nws                 | (Table 4)                                                                                             |                                            | 4              |      | 32                | Bits    |

| SCK Frequency                             | fSCK                | fSCK = fws x nws x 2                                                                                  |                                            | (8 x 4)<br>x 2 |      | (192 x<br>32) x 2 | kHz     |

| SCK Clock High Time (Note 3)              | tHC                 | $V_{SCK} \ge V_{IH}, t_{SCK} = 1/f_{SCK}$                                                             |                                            | 0.35 x<br>tsck |      |                   | ns      |

| SCK Clock Low Time (Note 3)               | tLC                 | $V_{SCK} \le V_{IL}$ , tSCK = 1/fSCK                                                                  |                                            | 0.35 x<br>tsck |      |                   | ns      |

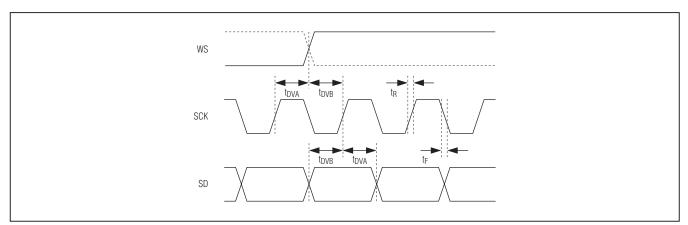

| SD, WS Setup Time                         | tSET                | (Figure 12, N                                                                                         | lote 3)                                    | 2              |      |                   | ns      |

| SD, WS Hold Time                          | thold               | (Figure 12, N                                                                                         | Jote 3)                                    | 2              |      |                   | ns      |

## MAX9260 DC ELECTRICAL CHARACTERISTICS

$(V_{DVDD} = V_{AVDD} = 3.0V \text{ to } 3.6V, V_{IOVDD} = 1.7V \text{ to } 3.6V, R_L = 100\Omega \pm 1\%$  (differential),  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{DVDD} = V_{AVDD} = V_{IOVDD} = 3.3V$ ,  $T_A = +25^{\circ}C$ .)

| PARAMETER                               | SYMBOL       |                          | CO                       | NDITIONS    |                                      | MIN              | TYP                      | MAX              | UNITS                         |                          |               |                          |    |    |

|-----------------------------------------|--------------|--------------------------|--------------------------|-------------|--------------------------------------|------------------|--------------------------|------------------|-------------------------------|--------------------------|---------------|--------------------------|----|----|

| SINGLE-ENDED INPUTS (ENA                | BLE, INT, PW | DN, SSEN, E              | BWS, E                   | S, DRS, MS  | S, CDS, EQS, I                       | DCS)             |                          |                  |                               |                          |               |                          |    |    |

| High-Level Input Voltage                | VIH1         |                          |                          |             |                                      | 0.65 x<br>Viovdd |                          |                  | V                             |                          |               |                          |    |    |

| Low-Level Input Voltage                 | VIL1         |                          |                          |             |                                      |                  |                          | 0.35 x<br>Viovdd | V                             |                          |               |                          |    |    |

| Input Current                           | liN1         | $V_{IN} = 0$ to $V_{IN}$ | /IOVDD                   |             |                                      | -10              |                          | +10              | μΑ                            |                          |               |                          |    |    |

| Input Clamp Voltage                     | VCL          | ICL = -18m               | A                        |             |                                      |                  |                          | -1.5             | V                             |                          |               |                          |    |    |

| SINGLE-ENDED OUTPUTS (DC                | UT_, SD, WS  | S, SCK, PCLI             | (OUT)                    |             |                                      |                  |                          |                  |                               |                          |               |                          |    |    |

| High Lough Output Valtage               | Mou          |                          |                          | OCS = VIOG  | ND                                   | VIOVDD<br>- 0.3  |                          |                  | V                             |                          |               |                          |    |    |

| High-Level Output Voltage               | Voh          | IOH = -2mA               |                          | OCS = VIOVI | DD                                   | VIOVDD<br>- 0.2  |                          |                  | V                             |                          |               |                          |    |    |

| Low Lovel Output Valtage                |              |                          | VD                       | CS = VIOG   | ND                                   |                  |                          | 0.3              | 17                            |                          |               |                          |    |    |

| Low-Level Output Voltage                | VOL1         | $I_{OL} = 2mA$           |                          | CS = VIOVI  |                                      |                  |                          | 0.2              | V                             |                          |               |                          |    |    |

|                                         |              | DOUT_,<br>SD, WS,<br>SCK | DOUT_,<br>SD, WS,<br>SCK | SD, WS,     | $V_{\rm O} = 0$                      | DV,              | VIOVDD =<br>3.0V to 3.6V | 15               | 25                            | 39                       |               |                          |    |    |

|                                         |              |                          |                          |             | SD, WS,                              | SD, WS,          | SD, WS,                  | VDCS             | = VIOGND                      | VIOVDD =<br>1.7V to 1.9V | 3             | 7                        | 13 |    |

|                                         |              |                          |                          |             |                                      |                  |                          |                  |                               | SCK                      | $V_{O} = OV,$ | VIOVDD =<br>3.0V to 3.6V | 20 | 35 |

|                                         |              |                          | VDCS :                   | = VIOVDD    | VIOVDD =<br>1.7V to 1.9V             | 5                | 10                       | 21               |                               |                          |               |                          |    |    |

| Output Short-Circuit Current            | IOS          |                          | $V_{O} = 0$              | DV,         | $V_{IOVDD} =$<br>3.0V to 3.6V        | 15               | 33                       | 50               | mA                            |                          |               |                          |    |    |

|                                         |              |                          |                          | = VIOGND    | VIOVDD =<br>1.7V to 1.9V             | 5                | 10                       | 17               |                               |                          |               |                          |    |    |

|                                         |              | PCLKOUT                  | FULNUUI                  | FULNUUI     | PULKUUT                              | PULKUUT          | Vo = 0                   | DV,              | $V_{IOVDD} =$<br>3.0V to 3.6V | 30                       | 54            | 97                       |    |    |

|                                         |              |                          | VDCS                     | = Viovdd    | V <sub>IOVDD</sub> =<br>1.7V to 1.9V | 9                | 16                       | 32               |                               |                          |               |                          |    |    |

| I <sup>2</sup> C AND UART I/O, OPEN-DRA | IN OUTPUTS   | (RX/SDA, T               | X/SCL,                   | ERR, GPIC   | D_, LOCK)                            |                  |                          |                  |                               |                          |               |                          |    |    |

| High-Level Input Voltage                | VIH2         |                          | _                        |             |                                      | 0.7 x<br>Viovdd  | _                        |                  | V                             |                          |               |                          |    |    |

| Low-Level Input Voltage                 | VIL2         |                          |                          |             |                                      |                  |                          | 0.3 x<br>Viovdd  | V                             |                          |               |                          |    |    |

| Input Ourront                           | luno         | $V_{IN} = 0$ to $V_{IN}$ | lovdd                    | RX/SDA,     | TX/SCL                               | -110             |                          | +1               |                               |                          |               |                          |    |    |

| Input Current                           | lin2         | (Note 2)                 |                          | GPIO, El    | RR, LOCK                             | -80              |                          | +1               | μA                            |                          |               |                          |    |    |

| Low-Level Open-Drain Output             | VOL2         | IOL = 3mA                |                          |             | = 1.7V to 1.9V                       |                  |                          | 0.4              | V                             |                          |               |                          |    |    |

| Voltage                                 | VUL2         |                          |                          | VIOVDD :    | = 3.0V to 3.6V                       |                  |                          | 0.3              | V                             |                          |               |                          |    |    |

## MAX9260 DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{DVDD} = V_{AVDD} = 3.0V \text{ to } 3.6V, V_{IOVDD} = 1.7V \text{ to } 3.6V, R_L = 100\Omega \pm 1\%$  (differential),  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{DVDD} = V_{AVDD} = V_{IOVDD} = 3.3V$ ,  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                                           | SYMBOL    | CONDI                                 | MIN                          | TYP | MAX | UNITS |    |

|-------------------------------------------------------------------------------------|-----------|---------------------------------------|------------------------------|-----|-----|-------|----|

| DIFFERENTIAL OUTPUTS FOR                                                            | REVERSE C | ONTROL CHANNEL (IN                    | N+, IN-)                     |     |     |       |    |

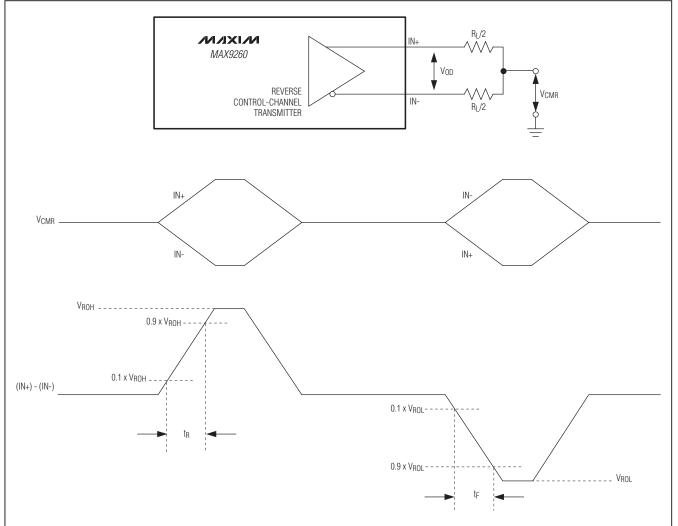

| Differential High Output Peak<br>Voltage, (V <sub>IN</sub> +) - (V <sub>IN</sub> -) | VROH      | No high-speed data tra<br>(Figure 13) | ansmission                   | 30  |     | 60    | mV |

| Differential Low Output Peak<br>Voltage, (V <sub>IN</sub> +) - (V <sub>IN</sub> -)  | VROL      | No high-speed data tra<br>(Figure 13) | ansmission                   | -60 |     | -30   | mV |

| DIFFERENTIAL INPUTS (IN+, IN-                                                       | -)        |                                       |                              |     |     |       |    |

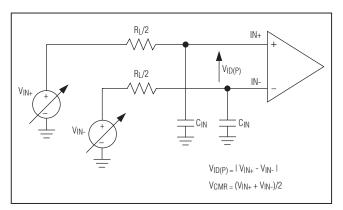

| Differential High Input Threshold<br>(Peak), (VIN+) - (VIN-)                        | VIDH(P)   | (Figure 14)                           |                              |     | 40  | 90    | mV |

| Differential Low Input Threshold<br>(Peak), (VIN+) - (VIN-)                         | VIDL(P)   | (Figure 14)                           |                              | -90 | -40 |       | mV |

| Input Common-Mode Voltage,<br>((VIN+) + (VIN-))/2                                   | VCMR      |                                       |                              | 1   | 1.3 | 1.6   | V  |

| Differential Input Resistance<br>(Internal)                                         | RI        |                                       |                              | 80  | 100 | 130   | Ω  |

| POWER SUPPLY                                                                        |           | _                                     |                              |     |     |       |    |

|                                                                                     |           | VBWS = VIOGND,<br>fpclkout = 16.6MHz  | 2% spread<br>spectrum active |     | 113 | 166   |    |

|                                                                                     |           |                                       | Spread spectrum disabled     |     | 105 | 155   |    |

|                                                                                     |           | VBWS = VIOGND,<br>fpclkout = 33.3MHz  | 2% spread<br>spectrum active |     | 122 | 181   |    |

| Worst-Case Supply Current                                                           |           |                                       | Spread spectrum disabled     |     | 110 | 165   |    |

| (Figure 15)                                                                         | Iwcs      | VBWS = VIOGND,                        | 2% spread<br>spectrum active |     | 137 | 211   | mA |

|                                                                                     |           | fPCLKOUT = 66.6MHz                    | Spread spectrum disabled     |     | 120 | 188   |    |

|                                                                                     |           | VBWS = VIOGND,                        | 2% spread<br>spectrum active |     | 159 | 247   |    |

|                                                                                     |           | fPCLKOUT = 104MHz                     | Spread spectrum disabled     |     | 135 | 214   |    |

| Sleep-Mode Supply Current                                                           | Iccs      |                                       | ·                            |     | 80  | 130   | μA |

| Power-Down Supply Current                                                           | ICCZ      | VPWDN = VIOGND                        |                              |     | 19  | 70    | μA |

## MAX9260 AC ELECTRICAL CHARACTERISTICS

$(V_{DVDD} = V_{AVDD} = 3.0V \text{ to } 3.6V, V_{IOVDD} = 1.7V \text{ to } 3.6V, R_L = 100\Omega \pm 1\% \text{ (differential)}, T_A = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}, \text{ unless otherwise noted}.$ Typical values are at  $V_{DVDD} = V_{AVDD} = V_{IOVDD} = 3.3V$ ,  $T_A = +25^{\circ}\text{C}.$ )

| PARAMETER                                   | SYMBOL                          | CONDITI                                              | MIN                                      | TYP   | MAX  | UNITS |      |

|---------------------------------------------|---------------------------------|------------------------------------------------------|------------------------------------------|-------|------|-------|------|

| PARALLEL CLOCK OUTPUT (PO                   | CLKOUT)                         |                                                      |                                          |       |      |       |      |

|                                             |                                 | VBWS = VIOGND, VDRS                                  | = Viovdd                                 | 8.33  |      | 16.66 |      |

| Cleak Fragmanay                             | francisco                       | VBWS = VIOGND, VDRS                                  | = VIOGND                                 | 16.66 |      | 104   |      |

| Clock Frequency                             | <b>f</b> PCLKOUT                | VBWS = VIOVDD, VDRS =                                | = Viovdd                                 | 6.25  |      | 12.5  | MHz  |

|                                             |                                 | VBWS = VIOVDD, VDRS =                                | = Viognd                                 | 12.5  |      | 78    | ]    |

| Clock Duty Cycle                            | DC                              | thigh/tt or tlow/tt (Figu                            | ure 16)                                  | 40    | 50   | 60    | %    |

| Clock Jitter                                | tJ                              | Period jitter, RMS, sprea<br>PRBS pattern, UI = 1/fp |                                          |       | 0.05 |       | UI   |

| I <sup>2</sup> C/UART PORT TIMING           |                                 |                                                      |                                          |       |      |       |      |

| Output Rise Time                            | tR                              | 30% to 70%, $C_L = 10pF$<br>pullup to IOVDD          | to 100pF, 1k $\Omega$                    | 20    |      | 150   | ns   |

| Output Fall Time                            | tF                              | 70% to 30%, $C_L = 10pF$<br>pullup to IOVDD          | to 100pF, 1k $\Omega$                    | 20    |      | 150   | ns   |

| Input Setup Time                            | tSET                            | I <sup>2</sup> C only                                |                                          | 100   |      |       | ns   |

| Input Hold Time                             | thold                           | I <sup>2</sup> C only                                |                                          | 0     |      |       | ns   |

| SWITCHING CHARACTERISTICS                   | S                               |                                                      |                                          |       |      |       |      |

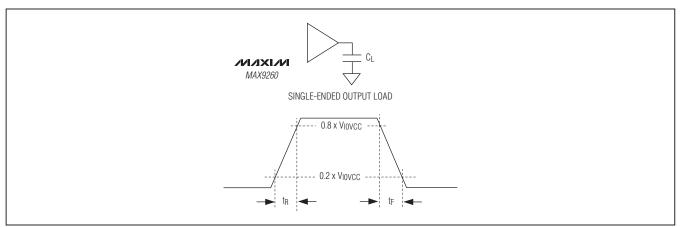

|                                             | tR, tF                          | 20% to 80%,<br>V <sub>IOVDD</sub> = 1.7V to 1.9V     | $V_{DCS} = V_{IOVDD},$<br>$C_{L} = 10pF$ | 0.4   |      | 2.2   |      |

|                                             |                                 |                                                      | $V_{DCS} = V_{IOGND},$<br>$C_L = 5pF$    | 0.5   |      | 2.8   | - ns |

| PCLKOUT Rise-and-Fall Time                  |                                 | 20% to 80%,<br>V <sub>IOVDD</sub> = 3.0V to 3.6V     | $V_{DCS} = V_{IOVDD},$<br>$C_{L} = 10pF$ | 0.25  |      | 1.7   |      |

|                                             |                                 |                                                      | $V_{DCS} = V_{IOGND},$<br>$C_{L} = 5pF$  | 0.3   |      | 2.0   |      |

|                                             |                                 | 20% to 80%,<br>VIOVDD = 1.7V to 1.9V                 | $V_{DCS} = V_{IOVDD},$<br>$C_{L} = 10pF$ | 0.5   |      | 3.1   | _    |

| Parallel Data Rise-and-Fall Time            |                                 |                                                      | $V_{DCS} = V_{IOGND},$<br>$C_{L} = 5pF$  | 0.6   |      | 3.8   |      |

| (Figure 17)                                 | t <sub>R</sub> , t <sub>F</sub> | 20% to 80%,                                          | $V_{DCS} = V_{IOVDD},$<br>$C_{L} = 10pF$ | 0.3   |      | 2.2   | ns   |

|                                             |                                 | $V_{IOVDD} = 3.0V \text{ to } 3.6V$                  | $V_{DCS} = V_{IOGND},$<br>$C_L = 5pF$    | 0.4   |      | 2.4   |      |

|                                             |                                 | Spread spectrum enabl                                | ed (Figure 18)                           |       |      | 2880  | D'I  |

| Deserializer Delay                          | tSD                             | Spread spectrum disab                                | led (Figure 18)                          |       |      | 750   | Bits |

| Look Time                                   | ti covi                         | Spread spectrum enabl                                | ed (Figure 19)                           |       |      | 1500  |      |

| Lock Time                                   | <b>t</b> LOCK                   | Spread spectrum off (Figure 19)                      |                                          |       |      | 1000  | μs   |

| Power-Up Time                               | tpu                             | (Figure 20)                                          |                                          |       |      | 2500  | μs   |

| Reverse Control-Channel Output<br>Rise Time | t <sub>R</sub>                  | No high-speed transmis                               | 180                                      |       | 400  | ns    |      |

| Reverse Control-Channel Output<br>Fall Time | tF                              | No high-speed transmis                               | sion (Figure 13)                         | 180   |      | 400   | ns   |

#### MAX9260 AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{DVDD} = V_{AVDD} = 3.0V \text{ to } 3.6V, V_{IOVDD} = 1.7V \text{ to } 3.6V, R_L = 100\Omega \pm 1\%$  (differential),  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{DVDD} = V_{AVDD} = V_{IOVDD} = 3.3V$ ,  $T_A = +25^{\circ}C$ .)

| PARAMETER                      | SYMBOL                          | CO                                                | MIN                                                              | TYP            | MAX                           | UNITS             |    |  |

|--------------------------------|---------------------------------|---------------------------------------------------|------------------------------------------------------------------|----------------|-------------------------------|-------------------|----|--|

| I <sup>2</sup> S OUTPUT TIMING |                                 |                                                   |                                                                  |                |                               |                   |    |  |

|                                |                                 | $t_{WS} = 1/f_{WS}$ , rising                      | fws = 48kHz or<br>44.1kHz                                        |                | 0.4e - 3<br>x tws             | 0.5e - 3<br>x tws |    |  |

| WS Jitter                      | taj-ws                          | (falling) edge to<br>falling (rising) edge        | f <sub>WS</sub> = 96kHz                                          |                | 0.8e - 3<br>x t <sub>WS</sub> | 1e - 3<br>x tws   | ns |  |

|                                |                                 | (Note 5)                                          | fws = 192kHz                                                     |                | 1.6e - 3<br>x tws             | 2e - 3<br>x tws   |    |  |

| SCK Jitter                     |                                 |                                                   | n <sub>WS</sub> = 16 bits,<br>f <sub>WS</sub> = 48kHz or 44.1kHz |                | 13e - 3<br>x tsck             | 16e - 3<br>x tsck |    |  |

|                                | taj-sck                         | $t_{SCK} = 1/f_{SCK}$ , risined ge to rising edge |                                                                  |                | 39e - 3<br>x tsck             | 48e - 3<br>x tsck | ns |  |

|                                |                                 |                                                   | n <sub>WS</sub> = 32 bits,<br>f <sub>WS</sub> = 192kHz           |                | 0.1<br>x tsck                 | 0.13<br>x tscк    |    |  |

| Audio Skew Relative to Video   | ASK                             | Video and audio sy                                | nchronized                                                       |                | 3 x tws                       | 4 x tws           | μs |  |

| COL CD WC Diag and Fall Time   | t- t-                           | VD(                                               | CS = VIOVDD, CL = 10pF                                           | 0.3            |                               | 3.1               | ns |  |

| SCK, SD, WS Rise-and-Fall Time | t <sub>R</sub> , t <sub>F</sub> | 20% to 80%                                        | CS = VIOGND, CL = 5pF                                            | 0.4            |                               | 3.8               | ns |  |

| SD, WS Valid Time Before SCK   | tDVB                            | tscк = 1/fscк (Figure 21)                         |                                                                  | 0.35<br>x tsck | 0.5<br>x tsck                 |                   | ns |  |

| SD, WS Valid Time After SCK    | tdva                            | tsck = 1/fsck (Figu                               | 0.35<br>x tsck                                                   | 0.5<br>x tsck  |                               | ns                |    |  |

Note 2: Minimum IIN due to voltage drop across the internal pullup resistor.

**Note 3:** Not production tested.

Note 4: Bit time =  $1/(30 \times f_{RXCLKIN})$  (BWS = 0), =  $1/(40 \times f_{RXCLKIN})$  (BWS =  $V_{IOVDD}$ ).

Note 5: Rising to rising edge jitter can be twice as large.

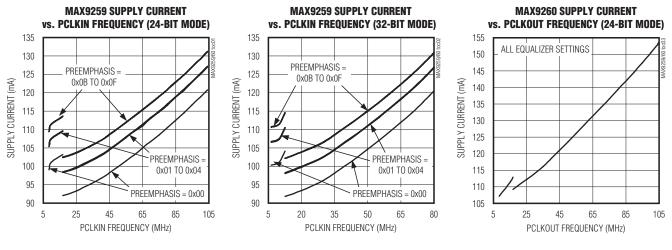

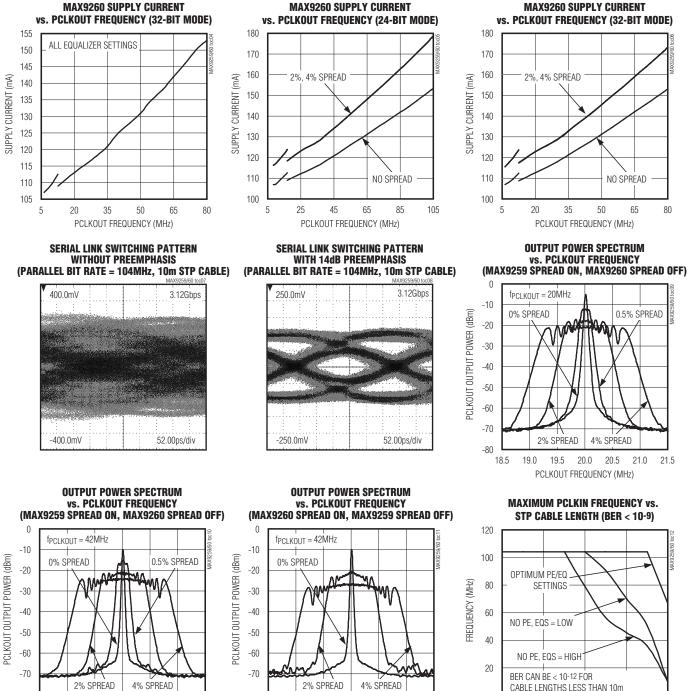

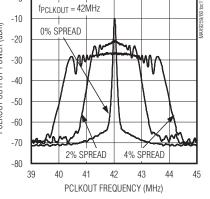

## **Typical Operating Characteristics**

(VDVDD = VAVDD = VIOVDD = 1.8V (MAX9259), VDVDD = VAVDD = VIOVDD = 3.3V (MAX9260), TA = +25°C, unless otherwise noted.)

#### **Typical Operating Characteristics (continued)**

(VDVDD = VAVDD = VIOVDD = 1.8V (MAX9259), VDVDD = VAVDD = VIOVDD = 3.3V (MAX9260), TA = +25°C, unless otherwise noted.)

CABLE LENGTH (m)

-80

PCLKOUT FREQUENCY (MHz)

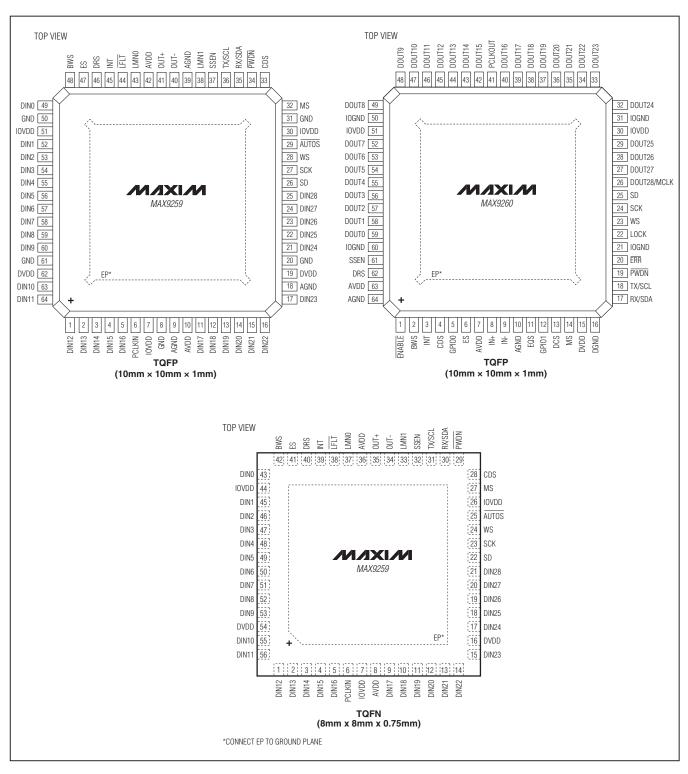

#### Pin Configurations

**WAX9259/MAX9260**

////XI///

## MAX9259 Pin Description

| PIN                                           |                                              |                |                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------|----------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFP                                          | TQFN                                         | NAME           | FUNCTION                                                                                                                                                                                                                                                                                                             |

| 1–5, 11–17,<br>21–25, 49,<br>52–60, 63,<br>64 | 1–5, 9–15,<br>17–21, 43,<br>45–53, 55,<br>56 | DINO-<br>DIN28 | Data Input[0:28]. Parallel data inputs. All pins internally pulled down to GND. Selected edge of PCLKIN latches input data. Set BWS = low (24-bit mode) to use DIN0–DIN20 (RGB and SYNC). DIN21–DIN28 are not used in 24-bit mode. Set BWS = high (32-bit mode) to use DIN0–DIN28 (RGB, SYNC, and two extra inputs). |

| 6                                             | 6                                            | PCLKIN         | Parallel Clock Input. Latches parallel data inputs and provides the PLL reference clock.                                                                                                                                                                                                                             |

| 7, 30, 51                                     | 7, 26, 44                                    | IOVDD          | I/O Supply Voltage. 1.8V to 3.3V logic I/O power supply. Bypass IOVDD to GND with $0.1\mu$ F and $0.001\mu$ F capacitors as close as possible to the device with the smaller value capacitor closest to IOVDD.                                                                                                       |

| 8, 20, 31,<br>50, 61                          | _                                            | GND            | Digital and I/O Ground                                                                                                                                                                                                                                                                                               |

| 9, 18, 39                                     | _                                            | AGND           | Analog Ground                                                                                                                                                                                                                                                                                                        |

| 10, 42                                        | 8, 36                                        | AVDD           | 1.8V Analog Power Supply. Bypass AVDD to AGND with 0.1µF and 0.001µF capacitors as close as possible to the device with the smaller value capacitor closest to AVDD.                                                                                                                                                 |

| 19, 62                                        | 16, 54                                       | DVDD           | 1.8V Digital Power Supply. Bypass DVDD to GND with 0.1µF and 0.001µF capacitors as close as possible to the device with the smaller value capacitor closest to DVDD.                                                                                                                                                 |

| 26                                            | 22                                           | SD             | I <sup>2</sup> S Serial-Data Input with Internal Pulldown to GND. Disable I <sup>2</sup> S to use SD as an additional data input latched on the selected edge of PCLKIN.                                                                                                                                             |

| 27                                            | 23                                           | SCK            | I <sup>2</sup> S Serial-Clock Input with Internal Pulldown to GND                                                                                                                                                                                                                                                    |

| 28                                            | 24                                           | WS             | I <sup>2</sup> S Word-Select Input with Internal Pulldown to GND                                                                                                                                                                                                                                                     |

| 29                                            | 25                                           | AUTOS          | Autostart Setting. Active-low power-up mode selection input requires external pulldown or pullup resistors. Set AUTOS = high to power up the device with no link active. Set AUTOS = low to have the MAX9259 power up the serial link with autorange detection (see Tables 13 and 14).                               |

| 32                                            | 27                                           | MS             | Mode Select. Control-link mode-selection input requires external pulldown or pullup resistors. Set MS = low, to select base mode. Set MS = high to select the bypass mode.                                                                                                                                           |

| 33                                            | 28                                           | CDS            | Control-Direction Selection. Control-link-direction selection input requires external pulldown or pullup resistors. Set CDS = low for $\mu$ C use on the MAX9259 side of the serial link. Set CDS = high for $\mu$ C use on the MAX9260 side of the serial link.                                                     |

| 34                                            | 29                                           | PWDN           | Power-Down. Active-low power-down input requires external pulldown or pullup resistors.                                                                                                                                                                                                                              |

| 35                                            | 30                                           | RX/SDA         | Receive/Serial Data. UART receive or I <sup>2</sup> C serial-data input/output with internal 30k $\Omega$ pullup to IOVDD. In UART mode, RX/SDA is the Rx input of the MAX9259's UART. In I <sup>2</sup> C mode, RX/SDA is the SDA input/output of the MAX9259's I <sup>2</sup> C master.                            |

## \_MAX9259 Pin Description (continued)

| PIN    |        |               |                                                                                                                                                                                                                                                                                                                                                       |  |

|--------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TQFP   | TQFN   | NAME          | FUNCTION                                                                                                                                                                                                                                                                                                                                              |  |

| 36     | 31     | TX/SCL        | Transmit/Serial Clock. UART transmit or I <sup>2</sup> C serial-clock output with internal 30k $\Omega$ pullup to IOVDD. In UART mode, TX/SCL is the Tx output of the MAX9259's UART. In I <sup>2</sup> C mode, TX/SCL is the SCL output of the MAX9259's I <sup>2</sup> C master.                                                                    |  |

| 37     | 32     | SSEN          | Spread-Spectrum Enable. Serial link spread-spectrum enable input requires external pulldown or pullup resistors. The state of SSEN latches upon power-up or when resumi from power-down mode ( $\overline{PWDN}$ = low). Set SSEN = high for ±0.5% spread spectrum on the serial link. Set SSEN = low to use the serial link without spread spectrum. |  |

| 38     | 33     | LMN1          | Line-Fault Monitor Input 1 (see Figure 3 for details)                                                                                                                                                                                                                                                                                                 |  |

| 40, 41 | 34, 35 | OUT-,<br>OUT+ | Differential CML Output -/+. Differential outputs of the serial link.                                                                                                                                                                                                                                                                                 |  |

| 43     | 37     | LMN0          | Line-Fault Monitor Input 0 (see Figure 3 for details)                                                                                                                                                                                                                                                                                                 |  |

| 44     | 38     | LFLT          | Line Fault. Active-low open-drain line-fault output with a $60k\Omega$ internal pullup resistor.<br>$\overline{\text{LFLT}} = \text{low indicates a line fault. } \overline{\text{LFLT}}$ is high impedance when $\overline{\text{PWDN}} = \text{low}$ .                                                                                              |  |

| 45     | 39     | INT           | Interrupt Output to Indicate Remote Side Requests. INT = low upon power-up and w $\overline{PWDN}$ = low. A transition on the INT input of the MAX9260 toggles the MAX9259's IN output.                                                                                                                                                               |  |

| 46     | 40     | DRS           | Data-Rate Select. Data-rate range-selection input requires external pulldown or pullup resistors. Set DRS = high for parallel input data rates of 8.33MHz to 16.66MHz (24-bit mode) or 6.25MHz to 12.5MHz (32-bit mode). Set DRS = low for parallel input data rates of 16.66MHz to 104MHz (24-bit mode) or 12.5MHz to 78MHz (32-bit mode).           |  |

| 47     | 41     | ES            | Edge Select. PCLKIN trigger edge-selection input requires external pulldown or pullup resistors. Set ES = low to trigger on the rising edge of PCLKIN. Set ES = high to trigger on the falling edge of PCLKIN.                                                                                                                                        |  |

| 48     | 42     | BWS           | Bus-Width Select. Parallel input bus-width selection input requires external pulldown or pullup resistors. Set BWS = low for 24-bit bus mode. Set BWS = high for 32-bit bus mode.                                                                                                                                                                     |  |

| _      | _      | EP            | Exposed Pad. EP internally connected to AGND (TQFP package) or AGND and GND (TQFN package). <b>MUST</b> externally connect EP to the AGND plane to maximize thermal and electrical performance.                                                                                                                                                       |  |

## MAX9260 Pin Description

| PIN    | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                          |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | ENABLE   | Enable. Active-low parallel output-enable input requires external pulldown or pullup resistors. Set ENABLE = low to enable PCLKOUT, SD, SCK, WS, and the parallel outputs, DOUT Set ENABLE = high to put PCLKOUT, SD, SCK, WS, and DOUT_ to high impedance.                                                                                                                       |

| 2      | BWS      | Bus-Width Select. Parallel output bus-width selection input requires external pulldown or pullup resistors. Set BWS = low for 24-bit bus mode. Set BWS = high for 32-bit bus mode.                                                                                                                                                                                                |

| 3      | INT      | Interrupt. Interrupt input requires external pulldown or pullup resistors. A transition on the INT input of the MAX9260 toggles the MAX9259's INT output.                                                                                                                                                                                                                         |

| 4      | CDS      | Control-Direction Selection. Control-link-direction selection input requires external pull-<br>down or pullup resistors. Set CDS = low for $\mu$ C use on the MAX9259 side of the serial<br>link. Set CDS = high for $\mu$ C use on the MAX9260 side of the serial link.                                                                                                          |

| 5      | GPI00    | GPIO0. Open-drain general-purpose input/output with internal $60k\Omega$ pullup resistors to IOVDD. GPIO0 is high impedance during power-up and when $\overline{PWDN}$ = low.                                                                                                                                                                                                     |

| 6      | ES       | Edge Select. PCLKOUT edge-selection input requires external pulldown or pullup resistors. Set ES = low for a rising-edge trigger. Set ES = high for a falling-edge trigger.                                                                                                                                                                                                       |

| 7, 63  | AVDD     | 3.3V Analog Power Supply. Bypass AVDD to AGND with $0.1\mu$ F and $0.001\mu$ F capacitors as close as possible to the device with the smallest value capacitor closest to AVDD.                                                                                                                                                                                                   |

| 8,9    | IN+, IN- | Differential CML Input +/ Differential inputs of the serial link.                                                                                                                                                                                                                                                                                                                 |

| 10, 64 | AGND     | Analog Ground                                                                                                                                                                                                                                                                                                                                                                     |

| 11     | EQS      | Equalizer Select. Deserializer equalizer-selection input requires external pulldown or pullup resistors. The state of EQS latches upon power-up or rising edge of PWDN. Set EQS = low for 10.7dB equalizer boost (EQTUNE = 1001). Set EQS = high for 5.2dB equalizer boost (EQTUNE = 0100).                                                                                       |

| 12     | GPIO1    | GPIO1. Open-drain general-purpose input/output with internal $60k\Omega$ pullup resistors to IOVDD. GPIO1 is high impedance during power-up and when $\overline{PWDN}$ = low.                                                                                                                                                                                                     |

| 13     | DCS      | Drive Current Select. Driver current-selection input requires external pulldown or pullup resistors. Set DCS = high for stronger parallel data and clock output drivers. Set DCS = low for normal parallel data and clock drivers (see the <i>MAX9260 DC Electrical Characteristics</i> table).                                                                                   |

| 14     | MS       | Mode Select. Control-link mode-selection/autostart mode selection input requires external pulldown or pullup resistors. MS sets the control-link mode when CDS = high (see the <i>Control-Channel and Register Programming</i> section). Set MS = low to select base mode. Set MS = high to select the bypass mode. MS sets autostart mode when CDS = low (see Tables 13 and 14). |

| 15     | DVDD     | 3.3V Digital Power Supply. Bypass DVDD to DGND with 0.1µF and 0.001µF capacitors as close as possible to the device with the smaller value capacitor closest to DVDD.                                                                                                                                                                                                             |

| 16     | DGND     | Digital Ground                                                                                                                                                                                                                                                                                                                                                                    |

| 17     | RX/SDA   | Receive/Serial Data. UART receive or I <sup>2</sup> C serial-data input/output with internal 30k $\Omega$ pullup to IOVDD. In UART mode, RX/SDA is the Rx input of the MAX9260's UART. In I <sup>2</sup> C mode, RX/SDA is the SDA input/output of the MAX9259's I <sup>2</sup> C master.                                                                                         |

## MAX9260 Pin Description (continued)

| PIN                           | NAME                             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18                            | TX/SCL                           | Transmit/Serial Clock. UART transmit or I <sup>2</sup> C serial-clock output with internal 30k $\Omega$ pullup to IOVDD. In UART mode, TX/SCL is the Tx output of the MAX9259's UART. In I <sup>2</sup> C mode, TX/SCL is the SCL output of the MAX9260's I <sup>2</sup> C master.                                                                                                                                                 |

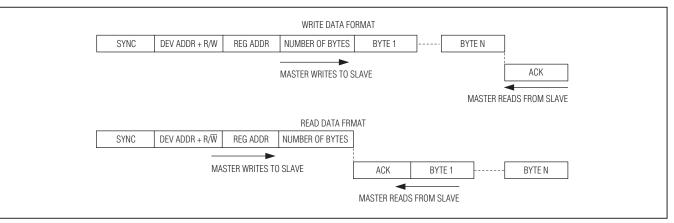

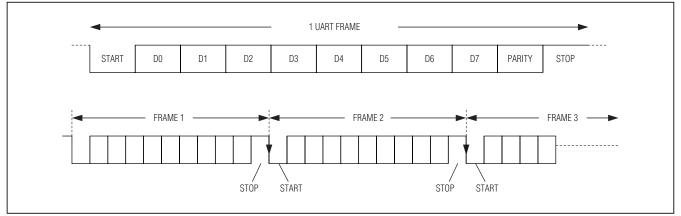

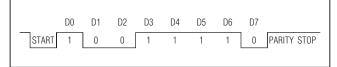

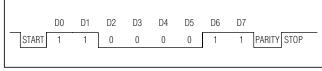

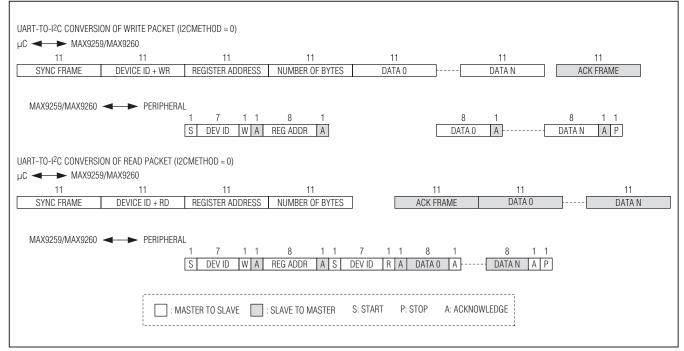

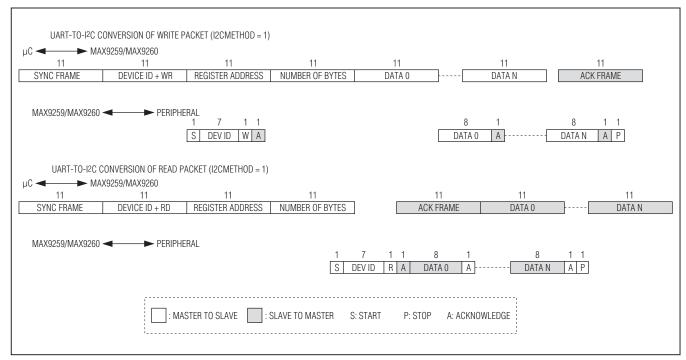

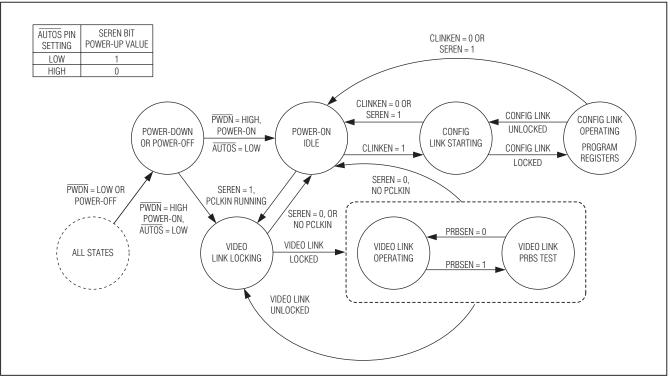

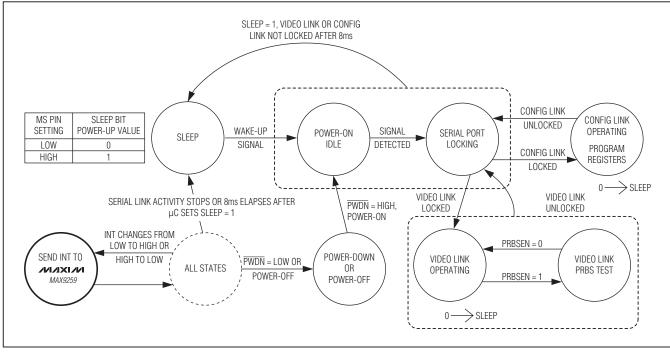

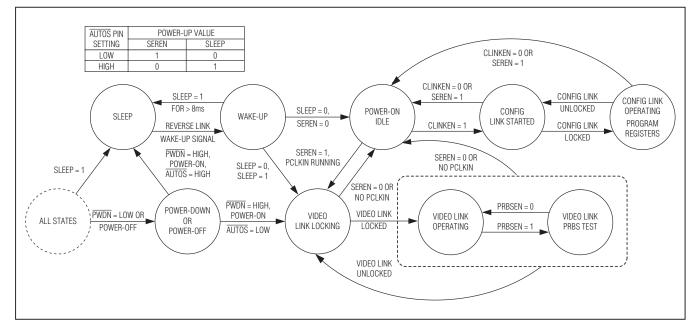

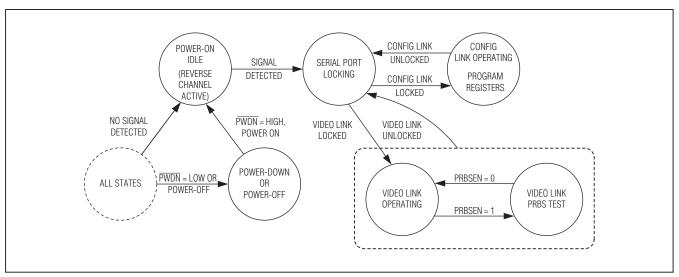

| 19                            | PWDN                             | Power-Down. Active-low power-down input requires external pulldown or pullup resistors.                                                                                                                                                                                                                                                                                                                                            |