# Integrated Optical Module for Smoke Detection

# **Data Sheet**

# ADPD188BI

### FEATURES

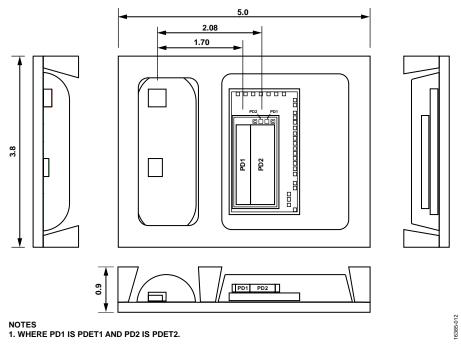

- 3.8 mm × 5.0 mm × 0.9 mm module with integrated optical components

- 1 blue LED, 1 IR LED, and 2 photodiodes

- 2 external inputs for other sensors (for example, carbon monoxide (CO) and temperature)

Three 370 mA LED drivers

20-bit burst accumulator enabling 20 bits per sample period

On-board sample to sample accumulator enabling up to

27 bits per data read

Optimized SNR for signal limited cases I<sup>2</sup>C or SPI communications

### APPLICATIONS

### **Smoke detection**

### **GENERAL DESCRIPTION**

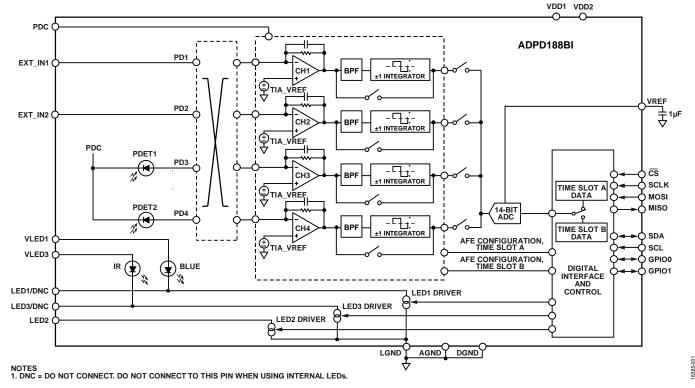

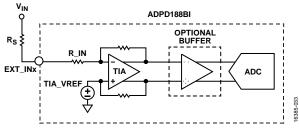

The ADPD188BI is a complete photometric system for smoke detection using optical dual wavelength technology. The module integrates a highly efficient photometric front end, two light emitting diodes (LEDs), and two photodiodes (PDs). These items are housed in a custom package that prevents light from going directly from the LED to the photodiode without first entering the smoke detection chamber.

The front end of the application specific integrated circuit (ASIC) consists of a control block, a 14-bit analog-to-digital converter (ADC) with a 20-bit burst accumulator, and three flexible, independently configurable LED drivers. The control circuitry includes flexible LED signaling and synchronous detection. The analog front end (AFE) features best-in-class rejection of signal offset and corruption due to modulated interference commonly caused by ambient light. The data output and functional configuration occur over a 1.8 V I<sup>2</sup>C interface or serial peripheral interface (SPI) port.

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

Rev. A

### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2018–2019 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features 1                                    |

|-----------------------------------------------|

| Applications1                                 |

| General Description                           |

| Functional Block Diagram1                     |

| Revision History 2                            |

| Specifications                                |

| Analog Specifications                         |

| Digital Specifications7                       |

| Timing Specifications                         |

| Absolute Maximum Ratings10                    |

| Thermal Resistance10                          |

| Recommended Soldering Profile10               |

| ESD Caution10                                 |

| Pin Configuration and Function Descriptions11 |

| Typical Performance Characteristics12         |

| Theory of Operation15                         |

| Introduction15                                |

| Optical Components15                          |

| Dual Time Slot Operation16                    |

| Time Slot Switch17                            |

| Adjustable Sampling Frequency18               |

| External Synchronization for Sampling18       |

| State Machine Operation18                     |

| Normal Mode Operation and Data Flow           |

| Communications Interface                      |

| I <sup>2</sup> C Interface                    |

| SPI Port                                      |

| Applications Information                      |

### Optional Timing Signals Available on GPIO0 and GPIO1 .. 27 LED Driver Pins and LED Supply Voltage...... 28 Recommended Configuration For Smoke Detector Using a Smoke Chamber with the ADPD188BI ...... 42 AFE Configuration Registers...... 49 Float Mode Registers ..... 53 System Registers ...... 55

### **REVISION HISTORY**

| 11/2019—Rev. 0 to Rev. A                                 |    |

|----------------------------------------------------------|----|

| Changes to Table 1                                       | 5  |

| Added Endnote 1, Table 2; Renumbered Sequentially        | 6  |

| Changed Output Voltage Level Parameter to SDA Output     |    |

| Voltage Level Parameter, Table 3                         | 7  |

| Added Endnote 1, Table 6                                 | 10 |

| Changes to Thermal Resistance Section                    | 10 |

| Changes to Figure 10 and Figure 11                       | 12 |

| Changes to Figure 12 and Figure 13                       | 13 |

| Added Figure 19 and Figure 20; Renumbered Sequentially   |    |

| Changes to Figure 21                                     | 15 |

| Changes to Dual Time Slot Operation Section and Table 11 |    |

| Changes to Time Slot Switch Section                      |    |

| Changes to Adjustable Sampling Frequency Section             |

|--------------------------------------------------------------|

| Changes to Averaging Section                                 |

| Changes to I <sup>2</sup> C Interface Section                |

| Changes to Reading Data Using the FIFO Section               |

| Changes to Calibrating the 32 kHz Clock Section 27           |

| Deleted Optimizing SNR per Watt in a Signal Limited System   |

| Section                                                      |

| Change to Determining the Average Current Section 29         |

| Added Optimizing SNR Section and Setting Optimal TIA Gain    |

| and LED Current Section                                      |

| Deleted Measuring PCB Parasitic Input Resistance Section and |

| Measuring TIA Input Shunt Resistance Section 31              |

| Changes to Tuning the Pulse Count Section 31                 |

|                                                              |

. . . . . . . .

# ADPD188BI

| Added Improving SNR Using Integrator Chopping Section       | 31 |

|-------------------------------------------------------------|----|

| Added Figure 39 and Table 18; Renumbered Sequentially       | 32 |

| Changes to Protecting Against TIA Saturation in Normal      |    |

| Operation Section                                           | 33 |

| Changes to Using the EXT_IN1 and EXT_IN2 Inputs with a      |    |

| Voltage Source Section and Table 19                         | 34 |

| Change to Float Mode Section and Table 19                   | 35 |

| Changes to Float Mode Limitations Section                   | 37 |

| Changes to Float Mode for Synchronous LED Measurements      |    |

| Section                                                     | 38 |

| Added Recommended Configuration for Smoke Detector          |    |

| Application Section, Table 26, Using a Smoke Chamber with t | he |

| ADPD188BI Section, and Figure 46                            | 42 |

|                                                             |    |

| Changed Register Listing Section to Register Details Section | 43 |

|--------------------------------------------------------------|----|

| Changes to Register Details Section and Table 27             | 43 |

| Changes to Table 28                                          | 47 |

| Changes to Table 29                                          | 49 |

| Changes to Table 30                                          | 51 |

| Changes to Table 31                                          | 52 |

| Changes to Table 33                                          | 55 |

| Changes to Table 34                                          | 60 |

| Changes to Ordering Guide                                    | 62 |

|                                                              |    |

6/2018—Revision 0: Initial Version

# **SPECIFICATIONS**

The voltage applied at the VDD1 and VDD2 pins ( $V_{DD}$ ) = 1.8 V, and  $T_A$  = full operating temperature range, unless otherwise noted.

### Table 1.

| Parameter                                            | Test Conditions/Comments                                                                                                                                                            | Min   | Тур                          | Max  | Unit |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------|------|------|

| CURRENT CONSUMPTION                                  | See the Calculating Current Consumption section for the relevant equations                                                                                                          |       |                              |      |      |

| Peak VDD Supply Current                              | Single-channel (Register 0x3C, Bits[8:3] = 0x38)                                                                                                                                    |       | 4.5                          |      | mA   |

| V <sub>DD</sub> Standby Current                      |                                                                                                                                                                                     |       | 0.3                          |      | μA   |

| Average V <sub>DD</sub> Supply Current               | 1 Hz data rate; LED offset = 25 $\mu$ s; LED pulse period (t <sub>LED_PERIOD</sub> ) = 15 $\mu$ s; LED peak current = 100 mA                                                        |       |                              |      |      |

| 1 Pulse                                              | Time Slot A only                                                                                                                                                                    |       | 0.8                          |      | μA   |

|                                                      | Time Slot B only                                                                                                                                                                    |       | 0.7                          |      | μA   |

|                                                      | Both Time Slot A and Time Slot B                                                                                                                                                    |       | 1.0                          |      | μA   |

| 16 Pulses                                            | Time Slot A only                                                                                                                                                                    |       | 1.9                          |      | μA   |

|                                                      | Time Slot B only                                                                                                                                                                    |       | 1.8                          |      | μA   |

|                                                      | Both Time Slot A and Time Slot B                                                                                                                                                    |       | 3.3                          |      | μA   |

| Average V <sub>LED</sub> <sup>1</sup> Supply Current | 1 Hz data rate; LED peak current = 100 mA and 2 $\mu$ s LED pulse                                                                                                                   |       |                              |      | '    |

| 1 Pulse                                              |                                                                                                                                                                                     |       | 0.2                          |      | μA   |

| 16 Pulses                                            |                                                                                                                                                                                     |       | 3.2                          |      | μA   |

| SATURATION ILLUMINANCE <sup>2</sup>                  | Blackbody color temperature (T = 5500 K) <sup>3</sup> , Photodetector 1<br>(PDET1) and Photodetector 2 (PDET2) multiplexed in a single<br>channel (1.2 mm <sup>2</sup> active area) |       |                              |      |      |

| Direct Illumination                                  | Transimpedance amplifier (TIA) gain = 25 k $\Omega$                                                                                                                                 |       | 13.0                         |      | kLux |

|                                                      | TIA gain = 50 k $\Omega$                                                                                                                                                            |       | 6.5                          |      | kLux |

|                                                      | TIA gain = 100 k $\Omega$                                                                                                                                                           |       | 3.25                         |      | kLux |

|                                                      | TIA gain = 200 k $\Omega$                                                                                                                                                           |       | 1.63                         |      | kLux |

| DATA ACQUISITION                                     | 5                                                                                                                                                                                   |       |                              |      |      |

| ADC Resolution                                       | Single pulse                                                                                                                                                                        |       | 14                           |      | Bits |

| Per Sample                                           | 64 pulses to 255 pulses                                                                                                                                                             |       | 20                           |      | Bits |

| Per Data Read                                        | 64 pulses to 255 pulses; 128 samples averaged                                                                                                                                       |       | 27                           |      | Bits |

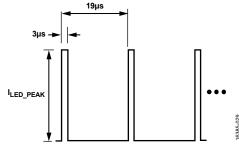

| LED PERIOD                                           | $AFE width = 4 \mu s^4$                                                                                                                                                             | 13    | 19                           |      | μs   |

|                                                      | AFE width = $3 \mu s$                                                                                                                                                               | 11    | 17                           |      | μs   |

| Sampling Frequency⁵                                  | Time Slot A or Time Slot B; normal mode; 1 pulse;<br>SLOTA_LED_OFFSET = 23 $\mu$ s; SLOTA_PERIOD = 19 $\mu$ s                                                                       | 0.122 | .,                           | 2000 | Hz   |

|                                                      | Both time slots; normal mode; 1 pulse;<br>SLOTA_LED_OFFSET = 23 $\mu$ s; SLOTA_PERIOD = 19 $\mu$ s                                                                                  | 0.122 |                              | 1600 | Hz   |

|                                                      | Time Slot A or Time Slot B; normal mode; 8 pulses;<br>SLOTA_LED_OFFSET = 23 $\mu$ s; SLOTA_PERIOD = 19 $\mu$ s                                                                      | 0.122 |                              | 1600 | Hz   |

|                                                      | Both time slots; normal mode; 8 pulses;<br>SLOTA_LED_OFFSET = 23 $\mu$ s; SLOTA_PERIOD = 19 $\mu$ s                                                                                 | 0.122 |                              | 1000 | Hz   |

| CATHODE PIN (PDC) VOLTAGE                            |                                                                                                                                                                                     |       |                              |      | İ    |

| During All Sampling Periods                          | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = $1^6$                                                                                                                            |       | 1.8                          |      | v    |

|                                                      | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 0                                                                                                                                |       | 1.3                          |      | v    |

| During Time Slot A Sampling                          | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = 0x0 <sup>6</sup>                                                                                                             |       | 1.8                          |      | v    |

|                                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = $0x1$                                                                                                                        |       | 1.3                          |      | v    |

|                                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = 0x2                                                                                                                          |       | TIA_VREF <sup>7</sup> + 0.25 |      | v    |

|                                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = $0x3^8$                                                                                                                      |       | 0                            |      | v    |

| During Time Slot B Sampling                          | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = 0x0 <sup>6</sup>                                                                                                           |       | 1.8                          |      | v    |

|                                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = $0x1$                                                                                                                      |       | 1.3                          |      | v    |

|                                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = $0x2$                                                                                                                      |       | TIA_VREF <sup>7</sup> + 0.25 |      | v    |

|                                                      | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = 0x3 <sup>8</sup>                                                                                                           |       | 0                            |      | v    |

# ADPD188BI

| Parameter                                 | Test Conditions/Comments                                                                                                                                       | Min | Тур                             | Мах | Unit            |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------|-----|-----------------|

| During Sleep Periods                      | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 1                                                                                                           |     | 1.8                             |     | V               |

|                                           | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 0                                                                                                           |     | 1.3                             |     | v               |

|                                           | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[13:12] = 0x0                                                                                                   |     | 1.8                             |     | v               |

|                                           | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[13:12] = 0x1                                                                                                   |     | 1.3                             |     | v               |

|                                           | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[13:12] = 0x2                                                                                                   |     | TIA_VREF <sup>7</sup> +<br>0.25 |     | V               |

|                                           | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[13:12] = 0x3                                                                                                   |     | 0                               |     | V               |

| LEDs                                      |                                                                                                                                                                |     |                                 |     |                 |

| LED Peak Current Setting                  | Adjustable via the Register 0x22 through Register 0x25 settings                                                                                                | 12  |                                 | 370 | mA              |

| Dominant Wavelength <sup>9</sup>          |                                                                                                                                                                |     |                                 |     |                 |

| LED1, Blue LED                            | $I_F = 20 \text{ mA}$                                                                                                                                          |     | 470                             |     | nm              |

| LED3, Infrared (IR) LED                   | $I_{F} = 100 \text{ mA}$                                                                                                                                       |     | 850                             |     |                 |

| Radiant Flux                              | $\lambda = 470 \text{ nm}, I_F = 20 \text{ mA at } 25^{\circ}\text{C}$                                                                                         | 29  |                                 | 36  | mW              |

|                                           | $\lambda = 850 \text{ nm}, I_F = 100 \text{ mA at } 25^{\circ}\text{C}$                                                                                        | 33  |                                 |     | mW              |

| PHOTODIODE                                |                                                                                                                                                                |     |                                 |     |                 |

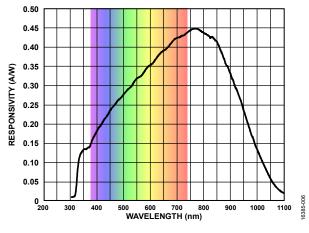

| Responsivity                              | Wavelength, $\lambda = 470$ nm                                                                                                                                 |     | 0.2                             |     | A/W             |

|                                           | Wavelength, $\lambda = 850$ nm                                                                                                                                 |     | 0.4                             |     | A/W             |

| Active Area                               |                                                                                                                                                                |     |                                 |     |                 |

| Photodiode 1                              |                                                                                                                                                                |     | 0.4                             |     | mm <sup>2</sup> |

| Photodiode 2                              |                                                                                                                                                                |     | 0.8                             |     | mm²             |

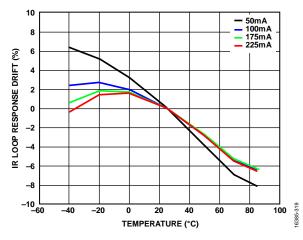

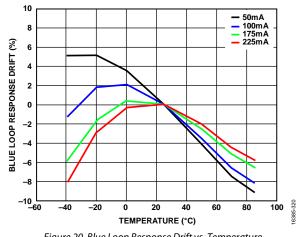

| LOOP RESPONSE DRIFT                       | Temperature drift of the full transmitter and receiver loop<br>response, Register 0x39 and Register 0x3B = 0x22F0,<br>Register 0x30 and Register 0x35 = 0x0320 |     |                                 |     |                 |

| Blue Channel                              | 25°C to 50°C, LED1 drive $\geq$ 50 mA                                                                                                                          | -8  |                                 | 0   | %               |

|                                           | +25°C to $-20$ °C, LED1 drive $\geq$ 50 mA                                                                                                                     | -15 |                                 | +15 | %               |

| IR Channel                                | 25°C to 50°C, LED3 drive ≥ 50 mA                                                                                                                               | -9  |                                 | +1  | %               |

|                                           | +25°C to $-20$ °C, LED3 drive $\geq 50$ mA                                                                                                                     | -5  |                                 | +14 | %               |

| POWER SUPPLY VOLTAGES                     | The ADPD188BI does not require a specific power-up sequence                                                                                                    |     |                                 |     |                 |

| V <sub>DD</sub>                           | Applied at the VDD1 and VDD2 pins                                                                                                                              | 1.7 | 1.8                             | 1.9 | v               |

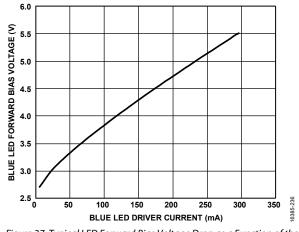

| V <sub>LED1</sub> <sup>2, 10</sup>        |                                                                                                                                                                |     | 5.0                             | 6.0 | V               |

| VLED3 <sup>2, 10</sup>                    |                                                                                                                                                                |     | 3.3                             | 4.0 | V               |

| DC Power Supply Rejection<br>Ratio (PSRR) | At 75% of full-scale input signal                                                                                                                              |     | 24                              |     | dB              |

| TEMPERATURE RANGE                         |                                                                                                                                                                |     |                                 |     |                 |

| Operating                                 |                                                                                                                                                                | -40 |                                 | +85 | °C              |

<sup>1</sup> See Figure 9 for the current limitation at the minimum VLED supply voltage, V<sub>LEDx</sub>. <sup>2</sup> Saturation illuminance refers to the amount of ambient light that saturates the ADPD188BI signal. Actual results may vary by factors of up to 2× from typical

specifications. As a point of reference, Air Mass 1.5 (AM1.5) sunlight (brightest sunlight) produces 100 kLux.

<sup>3</sup> Blackbody color temperature (T = 5800 K) closely matches the light produced by solar radiation (sunlight).

<sup>4</sup> Minimum LED period =  $(2 \times AFE \text{ width}) + 5 \mu s$ .

<sup>5</sup> The maximum values in this specification are the internal ADC sampling rates in normal mode. The I<sup>2</sup>C read rates in some configurations may limit the output data rate. <sup>6</sup> This mode may induce additional noise and is not recommended unless necessary. The 1.8 V setting uses V<sub>DD</sub>, which contains greater amounts of differential voltage noise with respect to the anode voltage. A differential voltage between the anode and cathode injects a differential current across the capacitance of the photodiode of the magnitude of  $C \times dV/dt$ , where C is the capacitance.

<sup>7</sup> TIA\_VREF is an internal reference voltage generated by the ADPD188BI.

<sup>8</sup> This setting is not recommended for photodiodes because it causes a 1.3 V forward bias of the photodiode.

<sup>9</sup> I<sub>F</sub> is the forward current of the diode.

<sup>10</sup> Set V<sub>LEDx</sub> so that the maximum desired LED current is achievable with the turn on voltage of the LEDs that are wired to the LEDx/DNC pins. The LEDx/DNC pins are connected to the LEDx driver, which can be modeled as current sinks (see Figure 1). When an appropriate VLEDx is used, the voltage at the LEDx/DNC pins adjusts automatically to accommodate the LED turn on voltage and the LED current.

### ANALOG SPECIFICATIONS

VDD1 = VDD2 = 1.8 V, and  $T_A =$  full operating temperature range, unless otherwise noted.

### Table 2.

| Parameter                                                                      | Test Conditions/Comments                                                                 | Min | Тур Мах | Unit   |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----|---------|--------|

| EXT_INx <sup>1</sup> SERIES RESISTANCE (R_IN) <sup>2</sup>                     | Measured from $-3 \mu A$ to $+3 \mu A$                                                   |     | 6.5     | kΩ     |

| PULSED SIGNAL CONVERSIONS, 3 µs                                                | $4 \mu s$ wide AFE integration; normal operation,                                        |     |         |        |

| WIDE LED PULSE <sup>3</sup>                                                    | Register $0x43$ and Register $0x45 = 0xADA5$                                             |     |         |        |

| ADC Resolution <sup>4</sup>                                                    | TIA feedback resistor                                                                    |     |         |        |

|                                                                                | 25 kΩ                                                                                    |     | 3.27    | nA/LSB |

|                                                                                | 50 kΩ                                                                                    |     | 1.64    | nA/LSB |

|                                                                                | 100 kΩ                                                                                   |     | 0.82    | nA/LSB |

|                                                                                | 200 kΩ                                                                                   |     | 0.41    | nA/LSB |

| ADC Saturation Level                                                           | TIA feedback resistor                                                                    |     |         |        |

|                                                                                | 25 kΩ                                                                                    |     | 26.8    | μA     |

|                                                                                | 50 kΩ                                                                                    |     | 13.4    | μΑ     |

|                                                                                | 100 kΩ                                                                                   |     | 6.7     | μΑ     |

|                                                                                | 200 kΩ                                                                                   |     | 3.35    | μΑ     |

| Ambient Signal Headroom on Pulsed<br>Signal                                    | TIA feedback resistor                                                                    |     |         |        |

|                                                                                | 25 kΩ                                                                                    |     | 23.6    | μΑ     |

|                                                                                | 50 kΩ                                                                                    |     | 11.8    | μΑ     |

|                                                                                | 100 kΩ                                                                                   |     | 5.9     | μΑ     |

|                                                                                | 200 kΩ                                                                                   |     | 2.95    | μΑ     |

| PULSED SIGNAL CONVERSIONS, 2 µs<br>WIDE LED PULSE <sup>3</sup>                 | 3 μs wide AFE integration; normal operation, Register 0x43<br>and Register 0x45 = 0xADA5 |     |         |        |

| ADC Resolution <sup>4</sup>                                                    | TIA feedback resistor                                                                    |     |         |        |

|                                                                                | 25 kΩ                                                                                    |     | 4.62    | nA/LSB |

|                                                                                | 50 kΩ                                                                                    |     | 2.31    | nA/LSB |

|                                                                                | 100 kΩ                                                                                   |     | 1.15    | nA/LSB |

|                                                                                | 200 kΩ                                                                                   |     | 0.58    | nA/LSB |

| ADC Saturation Level                                                           | TIA feedback resistor                                                                    |     |         |        |

|                                                                                | 25 kΩ                                                                                    |     | 37.84   | μΑ     |

|                                                                                | 50 kΩ                                                                                    |     | 18.92   | μA     |

|                                                                                | 100 kΩ                                                                                   |     | 9.46    | μΑ     |

|                                                                                | 200 kΩ                                                                                   |     | 4.73    | μA     |

| Ambient Signal Headroom on Pulsed<br>Signal                                    | TIA feedback resistor                                                                    |     |         |        |

|                                                                                | 25 kΩ                                                                                    |     | 12.56   | μA     |

|                                                                                | 50 kΩ                                                                                    |     | 6.28    | μA     |

|                                                                                | 100 kΩ                                                                                   |     | 3.14    | μA     |

|                                                                                | 200 kΩ                                                                                   |     | 1.57    | μA     |

| FULL SIGNAL CONVERSIONS <sup>5</sup><br>TIA Saturation Level Pulsed Signal and | TIA feedback resistor                                                                    |     |         |        |

| Ambient Level                                                                  | 25 40                                                                                    |     | 50.4    |        |

|                                                                                | 25 kΩ                                                                                    |     | 50.4    | μA     |

|                                                                                | 50 kΩ                                                                                    |     | 25.2    | μA     |

|                                                                                | 100 kΩ                                                                                   |     | 12.6    | μΑ     |

|                                                                                | 200 kΩ                                                                                   |     | 6.3     | μΑ     |

| TIA Linear Range                                                               | TIA feedback resistor                                                                    |     | 12.0    |        |

|                                                                                | 25 kΩ                                                                                    |     | 42.8    | μA     |

|                                                                                | 50 kΩ                                                                                    |     | 21.4    | μA     |

|                                                                                | 100 kΩ                                                                                   |     | 10.7    | μA     |

|                                                                                | 200 kΩ                                                                                   |     | 5.4     | μA     |

| Parameter                | Test Conditions/Comments                                                                 | Min | Тур  | Max | Unit    |

|--------------------------|------------------------------------------------------------------------------------------|-----|------|-----|---------|

| SYSTEM PERFORMANCE       |                                                                                          |     |      |     |         |

| Total Output Noise Floor | Normal mode; per pulse; per channel; no LED; photodiode capacitance ( $C_{PD}$ ) = 25 pF |     |      |     |         |

|                          | 25 kΩ; referred to ADC input                                                             |     | 1.0  |     | LSB rms |

|                          | 25 k $\Omega$ ; referred to peak input signal for 2 $\mu$ s LED pulse                    |     | 4.6  |     | nA rms  |

|                          | 25 k $\Omega$ ; referred to peak input signal for 3 $\mu$ s LED pulse                    |     | 3.3  |     | nA rms  |

|                          | 25 k\Omega; saturation signal-to-noise ratio (SNR) per pulse per channel^6 $$            |     | 78.3 |     | dB      |

|                          | 50 kΩ; referred to ADC input                                                             |     | 1.1  |     | LSB rms |

|                          | 50 k $\Omega$ ; referred to peak input signal for 2 $\mu$ s LED pulse                    |     | 2.5  |     | nA rms  |

|                          | 50 k $\Omega$ ; referred to peak input signal for 3 $\mu$ s LED pulse                    |     | 1.8  |     | nA rms  |

|                          | 50 kΩ; saturation SNR per pulse per channel <sup>6</sup>                                 |     | 77.4 |     | dB      |

|                          | 100 kΩ; referred to ADC input                                                            |     | 1.2  |     | LSB rms |

|                          | 100 k $\Omega$ ; referred to peak input signal for 2 $\mu$ s LED pulse                   |     | 1.4  |     | nA rms  |

|                          | 100 kΩ; referred to peak input signal for 3 µs LED pulse                                 |     | 0.98 |     | nA rms  |

|                          | 100 kΩ; saturation SNR per pulse per channel <sup>6</sup>                                |     | 76.7 |     | dB      |

|                          | 200 kΩ; referred to ADC input                                                            |     | 1.4  |     | LSB rms |

|                          | 200 k $\Omega$ ; referred to peak input signal for 2 $\mu$ s LED pulse                   |     | 0.81 |     | nA rms  |

|                          | 200 k $\Omega$ ; referred to peak input signal for 3 $\mu$ s LED pulse                   |     | 0.57 |     | nA rms  |

|                          | 200 k $\Omega$ ; saturation SNR per pulse per channel <sup>6</sup>                       |     | 75.3 |     | dB      |

<sup>1</sup> Where x is either 1 or 2.

<sup>2</sup> The R\_IN value can be ignored for current source inputs or for PD inputs. This value is important for calculating correct voltages for voltage inputs through a resistor.

<sup>4</sup> ADC resolution is listed per pulse. If using multiple pulses, divide by the number of pulses. <sup>5</sup> This saturation level applies to the full signal path and, therefore, includes both the ambient signal and the pulsed signal. <sup>6</sup> The noise term of the saturation SNR value only refers to the receive noise and does not include photon shot noise or any noise on the LED signal itself.

### **DIGITAL SPECIFICATIONS**

VDD1 = VDD2 = 1.7 V to 1.9 V, unless otherwise noted.

Table 3.

| Parameter                | Symbol           | <b>Test Conditions/Comments</b> | Min               | Тур | Max               | Unit |

|--------------------------|------------------|---------------------------------|-------------------|-----|-------------------|------|

| LOGIC INPUTS             |                  |                                 |                   |     |                   |      |

| Input Voltage Level      |                  |                                 |                   |     |                   |      |

| High                     | VIH              | GPIOx, SCLK, MOSI, CS           | $0.7 \times VDDx$ |     | VDDx              | V    |

| High                     | VIH              | SCL, SDA                        | $0.7 \times VDDx$ |     | 3.6               |      |

| Low                      | VIL              |                                 |                   |     | $0.3 \times VDDx$ | V    |

| Input Current Level      |                  |                                 |                   |     |                   |      |

| High                     | Ін               |                                 | -10               |     | +10               | μA   |

| Low                      | IIL              |                                 | -10               |     | +10               | μΑ   |

| Input Capacitance        | CIN              |                                 |                   | 10  |                   | рF   |

| LOGIC OUTPUTS            |                  |                                 |                   |     |                   |      |

| Output Voltage Level     |                  | GPIOx, MISO                     |                   |     |                   |      |

| High                     | Vон              | 2 mA high level output current  | VDDx - 0.5        |     |                   | V    |

| Low                      | Vol              | 2 mA low level output current   |                   |     | 0.5               | V    |

| SDA Output Voltage Level |                  | SDA                             |                   |     |                   |      |

| Low                      | V <sub>OL1</sub> | 2 mA low level output current   |                   |     | $0.2 \times VDDx$ | V    |

| Output Current Level     |                  | SDA                             |                   |     |                   |      |

| Low                      | lol              | $V_{OL1} = 0.6 V$               | 6                 |     |                   | mA   |

### TIMING SPECIFICATIONS

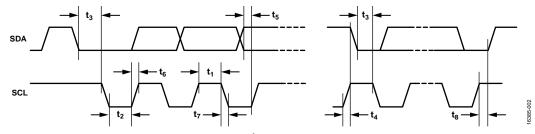

### **I<sup>2</sup>C Timing Specifications**

Table 4.

| Parameter           | Symbol         | Min | Тур | Max | Unit |

|---------------------|----------------|-----|-----|-----|------|

| SCL                 |                |     |     |     |      |

| Frequency           |                |     | 1   |     | Mbps |

| Minimum Pulse Width |                |     |     |     |      |

| High                | t1             | 370 |     |     | ns   |

| Low                 | t <sub>2</sub> | 530 |     |     | ns   |

| START CONDITION     |                |     |     |     |      |

| Hold Time           | t <sub>3</sub> | 260 |     |     | ns   |

| Setup Time          | t4             | 260 |     |     | ns   |

| SDA SETUP TIME      | t₅             | 50  |     |     | ns   |

| SCL AND SDA         |                |     |     |     |      |

| Rise Time           | t <sub>6</sub> |     |     | 120 | ns   |

| Fall Time           | t <sub>7</sub> |     |     | 120 | ns   |

| STOP CONDITION      |                |     |     |     |      |

| Setup Time          | t <sub>8</sub> | 260 |     |     | ns   |

Figure 2. I<sup>2</sup>C Timing Diagram

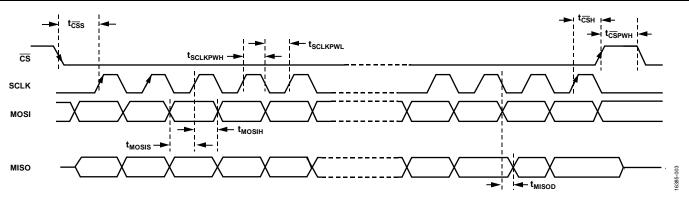

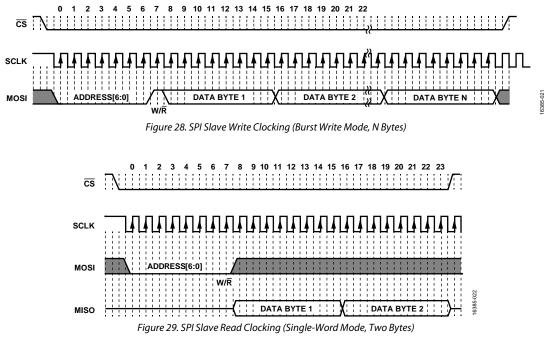

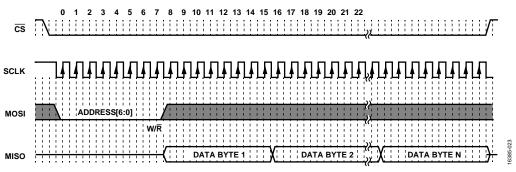

### SPI Timing Specifications

### Table 5.

| Parameter           | Symbol                      | Test Conditions/Comments                       | Min | Тур | Мах | Unit |

|---------------------|-----------------------------|------------------------------------------------|-----|-----|-----|------|

| SCLK                |                             |                                                |     |     |     |      |

| Frequency           | <b>f</b> sclk               |                                                |     |     | 10  | MHz  |

| Minimum Pulse Width |                             |                                                |     |     |     |      |

| High                | <b>t</b> sclkpwh            |                                                | 20  |     |     | ns   |

| Low                 | <b>t</b> <sub>SCLKPWL</sub> |                                                | 20  |     |     | ns   |

| <u>cs</u>           |                             |                                                |     |     |     |      |

| Setup Time          | t <sub>css</sub>            | CS setup to SCLK rising edge                   | 10  |     |     | ns   |

| Hold Time           | t <sub>csh</sub>            | CS hold from SCLK rising edge                  | 10  |     |     | ns   |

| Pulse Width High    | t <sub>cspwh</sub>          | CS pulse width high                            | 10  |     |     | ns   |

| MOSI                |                             |                                                |     |     |     | ns   |

| Setup Time          | t <sub>MOSIS</sub>          | MOSI setup to SCLK rising edge                 | 10  |     |     | ns   |

| Hold Time           | t <sub>MOSIH</sub>          | MOSI hold from SCLK rising edge                | 10  |     |     |      |

| MISO OUTPUT DELAY   | t <sub>MISOD</sub>          | MISO valid output delay from SCLK falling edge |     |     | 21  | ns   |

# ADPD188BI

Figure 3. SPI Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

### Table 6.

| Parameter                     | Rating             |  |  |  |

|-------------------------------|--------------------|--|--|--|

| VDD1, VDD2 to AGND            | -0.3 V to +2.2 V   |  |  |  |

| VDD1, VDD2 to DGND            | -0.3 V to $+2.2$ V |  |  |  |

| EXT_IN1/EXT_IN2               | -0.3 V to $+2.2$ V |  |  |  |

| GPIO0/GPIO1 to DGND           | -0.3 V to $+2.2$ V |  |  |  |

| MISO/MOSI/SCLK/CS to DGND     | -0.3 V to +2.2 V   |  |  |  |

| LEDx/DNC <sup>1</sup> to LGND | -0.3 V to +3.6 V   |  |  |  |

|                               |                    |  |  |  |

| SCL/SDA to DGND               | –0.3 V to +3.6 V   |  |  |  |

| VLED1 to LGND <sup>2</sup>    | –0.3 V to +6.0 V   |  |  |  |

| VLED3 to LGND <sup>2</sup>    | –0.3 V to +4.0 V   |  |  |  |

| Electrostatic Discharge (ESD) |                    |  |  |  |

| Human Body Model (HBM)        | 3000 V             |  |  |  |

| Charged Device Model (CDM)    | 1250 V             |  |  |  |

| Solder Reflow (Pb-Free)       |                    |  |  |  |

| Peak Temperature              | 260 (+0/-5)°C      |  |  |  |

| Time at Peak Temperature      | <30 sec            |  |  |  |

| Temperature Range             |                    |  |  |  |

| Powered                       | -40°C to +85°C     |  |  |  |

| Storage                       | -40°C to +105°C    |  |  |  |

| Junction Temperature          | 105°C              |  |  |  |

<sup>1</sup> Where x is either 1, 2, or 3.

<sup>2</sup> The absolute maximum voltage allowable between VLEDx and LGND is the voltage that causes the LEDx/DNC pins to reach or exceed their absolute maximum voltage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

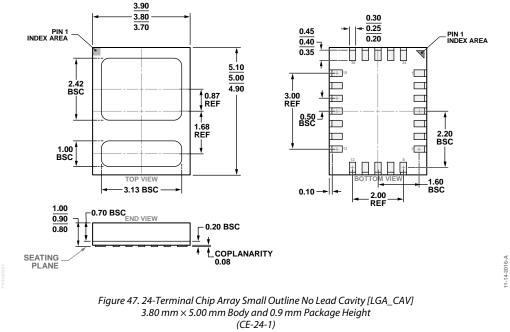

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{\text{JA}}$  is the junction to ambient thermal resistance value.

### Table 7. Thermal Resistance

| Package Type <sup>1</sup> | Supply Pins  | θιΑ | Unit |

|---------------------------|--------------|-----|------|

| CE-24-1                   |              |     |      |

| ASIC                      | VDD1, VDD2   | 67  | °C/W |

| LED1, LED3                | VLED1, VLED3 | 156 | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on JEDEC 2s2p and two thermal vias. See JEDEC JESD-51.

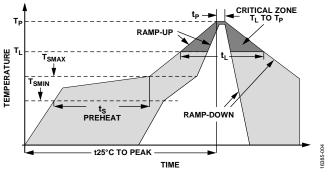

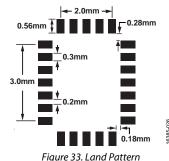

### **RECOMMENDED SOLDERING PROFILE**

Figure 4 and Table 8 provide details about the recommended soldering profile.

Figure 4. Recommended Soldering Profile

### **Table 8. Recommended Soldering Profile**

| Tuble 6. Recommended boldering Frome                           |                     |  |  |  |  |  |  |

|----------------------------------------------------------------|---------------------|--|--|--|--|--|--|

| Profile Feature                                                | Condition (Pb-Free) |  |  |  |  |  |  |

| Average Ramp Rate ( $T_L$ to $T_P$ )                           | 2°C/sec max         |  |  |  |  |  |  |

| Preheat                                                        |                     |  |  |  |  |  |  |

| Minimum Temperature (T <sub>SMIN</sub> )                       | 150°C               |  |  |  |  |  |  |

| Maximum Temperature (T <sub>SMAX</sub> )                       | 200°C               |  |  |  |  |  |  |

| Time, T <sub>SMIN</sub> to T <sub>SMAX</sub> (t <sub>s</sub> ) | 60 sec to 120 sec   |  |  |  |  |  |  |

| T <sub>SMAX</sub> to T <sub>L</sub> Ramp-Up Rate               | 2°C/sec max         |  |  |  |  |  |  |

| Time Maintained Above Liquidous                                |                     |  |  |  |  |  |  |

| Temperature                                                    |                     |  |  |  |  |  |  |

| Liquidous Temperature (T∟)                                     | 217°C               |  |  |  |  |  |  |

| Time (t <sub>L</sub> )                                         | 60 sec to 150 sec   |  |  |  |  |  |  |

| Peak Temperature (T <sub>P</sub> )                             | 260 (+0/-5)°C       |  |  |  |  |  |  |

| Time Within 5°C of Actual Peak                                 | <30 sec             |  |  |  |  |  |  |

| Temperature (t <sub>P</sub> )                                  |                     |  |  |  |  |  |  |

| Ramp-Down Rate                                                 | 3°C/sec max         |  |  |  |  |  |  |

| Time 25°C to Peak Temperature                                  | 8 minutes max       |  |  |  |  |  |  |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

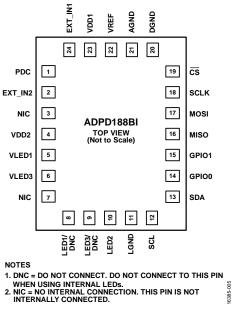

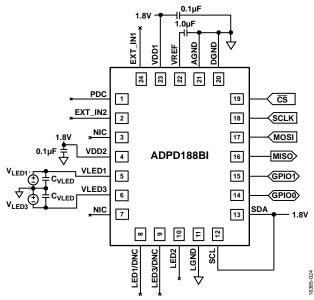

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 5. Pin Configuration

### **Table 9. Pin Function Descriptions**

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                                            |  |  |  |  |  |

|---------|----------|-------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | PDC      | AO                | Photodiode Common Cathode Bias.                                                                        |  |  |  |  |  |

| 2       | EXT_IN2  | AI                | EXT_IN2 Current Input.                                                                                 |  |  |  |  |  |

| 3       | NIC      | NIC               | lo Internal Connection (NIC). This pin is not internally connected.                                    |  |  |  |  |  |

| 4       | VDD2     | S                 | 1.8 V Supply.                                                                                          |  |  |  |  |  |

| 5       | VLED1    | S                 | Blue LED Anode Supply Voltage.                                                                         |  |  |  |  |  |

| 6       | VLED3    | S                 | IR LED Anode Supply Voltage.                                                                           |  |  |  |  |  |

| 7       | NIC      | NIC               | No Internal Connection (NIC). This pin is not internally connected.                                    |  |  |  |  |  |

| 8       | LED1/DNC | AO/DNC            | LED1 Driver Current Sink/Do Not Connect (DNC). Do not connect to this pin when using internal LEDs.    |  |  |  |  |  |

| 9       | LED3/DNC | AO/DNC            | LED3 Driver Current Sink/Do Not Connect (DNC). Do not connect to this pin when using internal LEDs.    |  |  |  |  |  |

| 10      | LED2     | AO                | LED2 Driver Current Sink. If not in use, leave this pin floating.                                      |  |  |  |  |  |

| 11      | LGND     | S                 | LED Driver Ground.                                                                                     |  |  |  |  |  |

| 12      | SCL      | DI                | I <sup>2</sup> C Clock Input.                                                                          |  |  |  |  |  |

| 13      | SDA      | DO                | I <sup>2</sup> C Data Output.                                                                          |  |  |  |  |  |

| 14      | GPIO0    | DIO               | General-Purpose Input/Output 0.                                                                        |  |  |  |  |  |

| 15      | GPIO1    | DIO               | General-Purpose Input/Output 1.                                                                        |  |  |  |  |  |

| 16      | MISO     | DO                | SPI Master Input, Slave Output.                                                                        |  |  |  |  |  |

| 17      | MOSI     | DI                | SPI Master Output, Slave Input.                                                                        |  |  |  |  |  |

| 18      | SCLK     | DI                | SPI Clock Input.                                                                                       |  |  |  |  |  |

| 19      | CS       | DI                | SPI Chip Select (Active Low).                                                                          |  |  |  |  |  |

| 20      | DGND     | S                 | Digital Ground.                                                                                        |  |  |  |  |  |

| 21      | AGND     | S                 | Analog Ground.                                                                                         |  |  |  |  |  |

| 22      | VREF     | REF               | Internally Generated ADC Voltage Reference. Connect a 1 $\mu$ F ceramic capacitor from VREF to ground. |  |  |  |  |  |

| 23      | VDD1     | S                 | 1.8 V Supply.                                                                                          |  |  |  |  |  |

| 24      | EXT_IN1  | AI                | EXT_IN1 Current Input.                                                                                 |  |  |  |  |  |

<sup>1</sup> AO is analog output, AI is analog input, NIC is not internally connected, S is supply, DNC is do not connect, DI is digital input, DO is digital output, DIO is digital input/output, and REF is analog reference.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 6. Typical Photodiode Responsivity

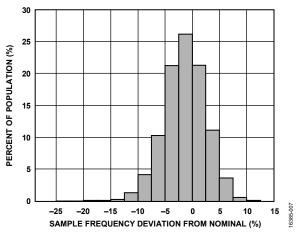

Figure 7. 32 kHz Clock Frequency Distribution; Default Settings; Before User Calibration, Register 0x4B = 0x2612

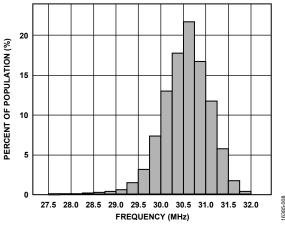

Figure 8. 32 MHz Clock Frequency Distribution; Default Settings; Before User Calibration, Register 0x4D = 0x425E

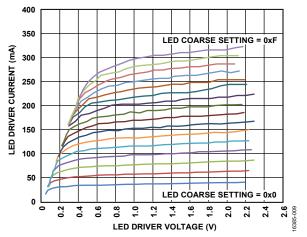

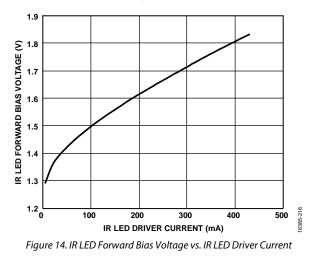

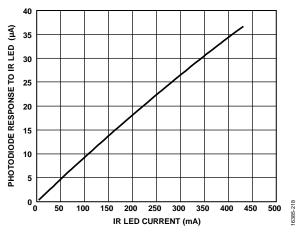

Figure 9. LED Driver Current vs. LED Driver Voltage at Various LED Coarse Settings

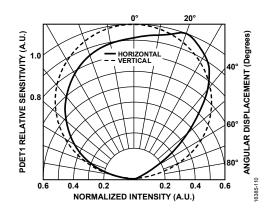

Figure 10. PDET1 Relative Sensitivity and Normalized Intensity vs. Angular Displacement

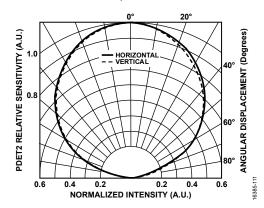

Figure 11. PDET2 Relative Sensitivity and Normalized Intensity vs. Angular Displacement

# BLUE RELATIVE INTERVISION (BUD STATUS) (BUD

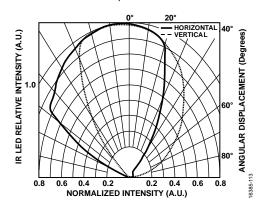

Figure 12. Blue LED Relative Intensity and Normalized Intensity vs. Angular Displacement

Figure 13. IR LED Relative Intensity and Normalized Intensity vs. Angular Displacement

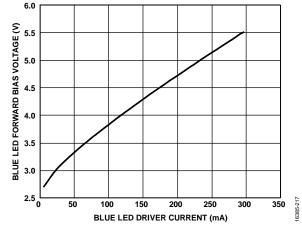

Figure 15. Blue LED Forward Bias Voltage vs. Blue LED Driver Current

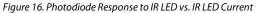

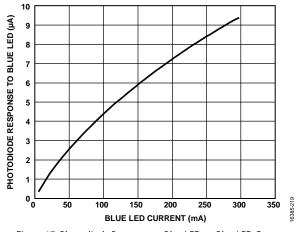

Figure 17. Photodiode Response to Blue LED vs. Blue LED Current

# ADPD188BI

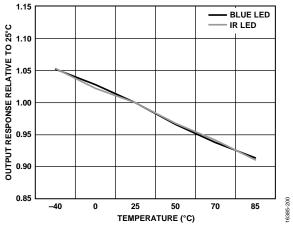

Figure 18. Output Response Relative to 25°C vs. Temperature

Figure 19. IR Loop Response Drift vs. Temperature

# THEORY OF OPERATION INTRODUCTION

The ADPD188BI is a complete, integrated optical module designed for smoke detection measurements. The module contains two optical detectors, PDET1 and PDET2. PDET1 has 0.4 mm<sup>2</sup> of active area and is connected to Channel 3 of the ASIC. PDET2 has 0.8 mm<sup>2</sup> of active area and is connected to Channel 4 of the ASIC. The two photodiodes can be combined into a single detector with 1.2 mm<sup>2</sup> of active area. The module combines the dual photodetector with two separate LEDs and a mixed-signal photometric front-end ASIC into a single compact device for optical measurements.

The dual wavelength ADPD188BI uses a 470 nm blue LED and an 850 nm IR LED. The combination of different wavelengths in a scattering measurement allows particle size discrimination between different types of smoke, dust, and water vapor. The on-board ASIC includes an analog signal processing block, an ADC, a digital signal processing block, an I<sup>2</sup>C and SPI communication interface, and three independently programmable pulsed LED current sources.

The core circuitry stimulates the LEDs and measures the corresponding optical return signals. Data can be read from

output registers directly or through a first in, first out (FIFO) buffer.

This highly integrated optical solution enables a low power, small footprint solution that reduces false smoke alarms in harsh environments due to dust, steam, and other nuisance sources.

### **OPTICAL COMPONENTS**

### Photodiode

The ADPD188BI integrates a 1.2 mm<sup>2</sup> deep junction photodiode. The optical sensing area is a dual detector connected to Channel PD3 and Channel PD4 in the ASIC. The photodiodes are accessible from Time Slot A or Time Slot B. The responsivity of the ADPD188BI photodiodes is shown in Figure 6.

### LEDs

The ADPD188BI module integrates one blue LED and one IR LED.

### Table 10. LED Dominant Wavelength

| LED Color | Driver | Typical Wavelength (nm) |

|-----------|--------|-------------------------|

| Blue      | LED1   | 470                     |

| IR        | LED3   | 850                     |

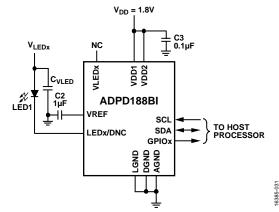

In addition to the integrated LEDs, the ADPD188BI can drive external LEDs.

Figure 21. Optical Component Locations

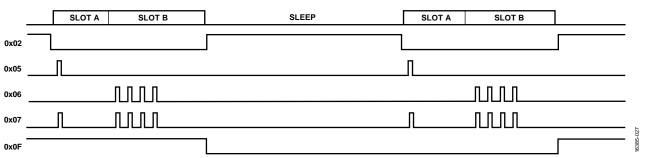

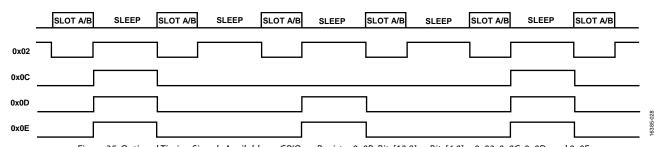

### **DUAL TIME SLOT OPERATION**

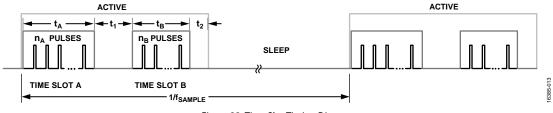

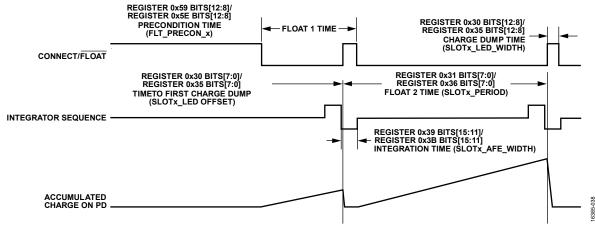

The ADPD188BI operates in two independent time slots, Time Slot A and Time Slot B, that are carried out sequentially. The signal path from LED stimulation to data capture and processing is executed during each time slot. Each time slot has a separate datapath that uses independent settings for the LED driver, AFE setup, and the resulting data. Time Slot A and Time Slot B operate in sequence for every sampling period, as shown in Figure 22. The timing parameters in Figure 22,  $t_A$ ,  $t_B$ ,  $t_1$ , and  $t_2$ , are defined with the following equations:

$$t_A$$

(µs) = SLOTA\_LED\_OFFSET +  $n_A \times$  SLOTA\_PERIOD

where  $n_A$  is the number of pulses for Time Slot A (Register 0x31, Bits[15:8]).

SLOTA\_LED\_OFFSET = 32 μs (recommended). SLOTA\_PERIOD = 15 μs (recommended).

$t_B(\mu s) = SLOTB\_LED\_OFFSET + n_B \times SLOTB\_PERIOD$

where  $n_B$  is the number of pulses for Time Slot B (Register 0x36, Bits[15:8]).

SLOTB\_LED\_OFFSET = 32 µs (recommended).

$SLOTB\_PERIOD = 15 \ \mu s \ (recommended)$

$t_1 = 68 \,\mu\text{s}$ , the processing time for Time Slot A.

$t_2 = 20 \ \mu$ s, the processing time for Time Slot B.

*f*<sub>SAMPLE</sub> is the sampling frequency (Register 0x12, Bits[15:0]).

Figure 22. Time Slot Timing Diagram

### Table 11. Recommended AFE and LED Timing Configuration

|                            | Add         | ress        |                     |

|----------------------------|-------------|-------------|---------------------|

| Register Name <sup>1</sup> | Time Slot A | Time Slot B | Recommended Setting |

| SLOTx_LED_PULSE            | 0x30        | 0x35        | 0x0320              |

| SLOTx_AFE_WINDOW           | 0x39        | 0x3B        | 0x22F0              |

<sup>1</sup> Where x is either A or B.

# ADPD188BI

6385-015

### TIME SLOT SWITCH

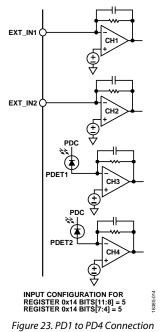

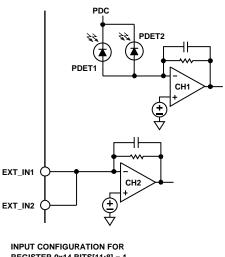

Multiple configurations of the four input channels are supported, depending on the settings of Register 0x14. The integrated photodiodes can either be routed to Channel 3 and Channel 4 or summed together into Channel 1. The recommendation for the lowest noise and lowest power is to sum PDET1 and PDET2 to Channel 1, as shown in Figure 24. The external EXT\_IN1 and EXT\_IN2 inputs can be routed to Channel 1 and Channel 2, respectively, or summed into Channel 2. See Figure 23 and Figure 24 for the supported configurations. In Figure 23 and Figure 24, PDET1 is Photodiode 1, and PDET2 is Photodiode 2.

See Table 12 for the time slot switch registers. It is important to leave any unused inputs floating to properly operate the devices. The photodiode inputs are current inputs and, as such, these pins are also considered to be voltage outputs. Tying these inputs to a voltage may saturate the analog block.

| Table 12. | Time Clot | + Switch | (Donictor | 0v14  |

|-----------|-----------|----------|-----------|-------|

|           |           | l Switch | INCEISICI | UAIH/ |

Figure 24. Current Summation

| Address | Bits   | Name         | Description                                                                                                                                                            |

|---------|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x14    | [11:8] | SLOTB_PD_SEL | These bits select the connection of input channels for Time Slot B, as shown in Figure 23 and Figure 24.                                                               |

|         |        |              | 0x0: inputs are floating in Time Slot B.                                                                                                                               |

|         |        |              | 0x1: PDET1 and PDET2 are connected to Channel 1. EXT_IN1 and EXT_IN2 are connected<br>to Channel 2 during Time Slot B.                                                 |

|         |        |              | 0x5: EXT_IN1 is connected to Channel 1, EXT_IN2 is connected to Channel 2, PDET1 is<br>connected to Channel 3, and PDET2 is connected to Channel 4 during Time Slot B. |

|         |        |              | Other: reserved.                                                                                                                                                       |

|         | [7:4]  | SLOTA_PD_SEL | These bits select the connection of input channels for Time Slot A, as shown in Figure 23 and Figure 24.                                                               |

|         |        |              | 0x0: inputs are floating in Time Slot A.                                                                                                                               |

|         |        |              | 0x1: PDET1 and PDET2 are connected to Channel 1. EXT_IN1 and EXT_IN2 are connected<br>to Channel 2 during Time Slot A.                                                 |

|         |        |              | 0x5: EXT_IN1 is connected to Channel 1, EXT_IN2 is connected to Channel 2, PDET1 is<br>connected to Channel 3, and PDET2 is connected to Channel 4 during Time Slot A. |

|         |        |              | Other: reserved.                                                                                                                                                       |

### ADJUSTABLE SAMPLING FREQUENCY

Register 0x12 controls the sampling frequency setting of the ADPD188BI and Register 0x4B, Bits[5:0] further tunes this sampling frequency clock for greater accuracy. The sampling frequency is governed by an internal 32 kHz sample rate clock that also drives the transition of the internal state machine. The maximum sampling frequencies for some sample conditions are listed in Table 1. The maximum sample frequency for all conditions, f<sub>SAMPLE\_MAX</sub>, is determined by the following equation:

$f_{SAMPLE\_MAX} = 1/(t_A + t_1 + t_B + t_2 + t_{SLEEP\_MIN})$

where  $t_{SLEEP\_MIN}$  is the minimum sleep time required between samples. See the Dual Time Slot Operation section for the definitions of  $t_A$ ,  $t_1$ ,  $t_B$ , and  $t_2$ .

If a given time slot is not in use, elements from that time slot do not factor into the calculation. For example, if Time Slot A is not in use,  $t_A$  and  $t_1$  do not add to the sampling period and the new maximum sampling frequency is calculated as follows:

$f_{SAMPLE_MAX} = 1/(t_B + t_2 + t_{SLEEP_MIN})$

### **EXTERNAL SYNCHRONIZATION FOR SAMPLING**

The ADPD188BI provides an option to use an external synchronization signal to trigger the sampling periods. This external sample synchronization signal can be provided either on the GPIO0 pin or the GPIO1 pin. This functionality is controlled by Register 0x4F, Bits[3:2]. When enabled, a rising edge on the selected input specifies when the next sample cycle occurs. When triggered, there is a delay of one to two internal sampling clock (32 kHz) cycles before the normal start-up sequence occurs. This start-up sequence is the same as when the normal sample timer provides the trigger. To enable the external synchronization signal feature, use the following procedure:

- 1. Write 0x1 to Register 0x10 to enter program mode.

- 2. Write the appropriate value to Register 0x4F, Bits[3:2] to select whether the GPIO0 pin or the GPIO1 pin specifies when the next sample cycle occurs. Enable the appropriate input buffer using Register 0x4F, Bit 1, for the GPIO0 pin, or Register 0x4F, Bit 5, for the GPIO1 pin.

- 3. Write 0x4000 to Register 0x38.

- 4. Write 0x2 to Register 0x10 to start the sampling operations.

- 5. Apply the external synchronization signal on the selected pin at the desired rate. Sampling occurs at this rate. As with normal sampling operations, read the data using the FIFO or the data registers. The maximum frequency constraints also apply in this case.

### Providing an External 32 kHZ Clock

The ADPD188BI allows the user to provide an external 32 kHz clock to the device for system synchronization, or for situations requiring a clock more accurate than the internal 32 kHz clock. The external 32 kHz clock is only provided on the GPIO1 pin. To enable the 32 kHz external clock, use the following procedure at startup:

- Drive the GPIO1 pin to a valid logic level or with the desired 32 kHz clock prior to enabling the GPIO1 pin as an input. Do not leave the pin floating prior to enabling it.

- 2. Write 0x1 to Register 0x4F, Bits[6:5] to enable the GPIO1 pin as an input.

- 3. Write 0x2 to Register 0x4B, Bits[8:7] to configure the devices to use an external 32 kHz clock. This setting disables the internal 32 kHz clock and enables the external 32 kHz clock.

- 4. Write 0x1 to Register 0x10 to enter program mode.

- 5. Write additional control registers in any order while the device is in program mode to configure the device as required.

- 6. Write 0x2 to Register 0x10 to start the normal sampling operation

### **STATE MACHINE OPERATION**

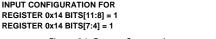

During each time slot, the ADPD188BI operates according to a state machine. The state machine operates in the sequence shown in Figure 25.

Figure 25. State Machine Operation Flowchart

The ADPD188BI operates in one of the following three modes: standby, program, or normal sampling mode.

Standby mode is a power saving mode in which data collection does not occur. All register values are retained in this mode. To place the device in standby mode, write 0x0 to Register 0x10, Bits[1:0]. The device powers up in standby mode.

Program mode is used to program registers. Always cycle the ADPD188BI through program mode when writing registers or changing modes. Because power cycling does not occur in this mode, the device can consume higher current in program mode than in normal operation. To place the device in program mode, write 0x1 to Register 0x10, Bits[1:0].

During normal operation, the ADPD188BI pulses light and collects data. Power consumption in this mode depends on the pulse count and data rate. To place the device in normal sampling mode, write 0x2 to Register 0x10, Bits[1:0].

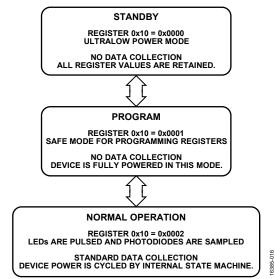

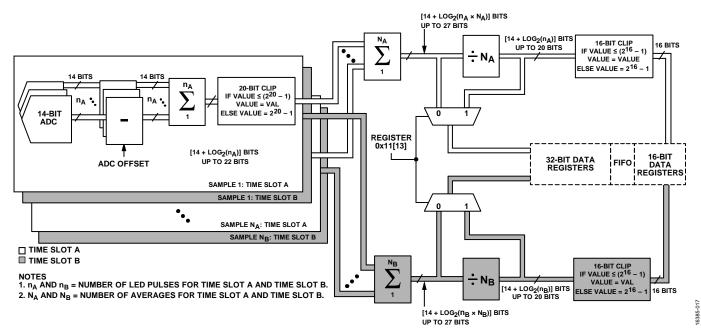

### NORMAL MODE OPERATION AND DATA FLOW

In normal mode, the ADPD188BI follows a specific pattern set up by the state machine. This pattern is shown in the corresponding data flow diagram in Figure 26. The order of the pattern is as follows:

- 1. LED pulse and sample. The ADPD188BI pulses external LEDs. The response of the photodiode to the reflected light is measured by the ADPD188BI. Each data sample is constructed from the sum of n individual pulses, where n is user configurable between 1 and 255.

- 2. Intersample averaging. If desired, the logic can average n samples, from 2 to 128 in powers of 2, to produce output data. New output data is saved to the output registers every N samples.

- 3. Data read. The host processor reads the converted results from the data register or the FIFO.

- 4. Repeat. The sequence has a few different loops that enable different types of averaging while keeping both time slots close in time relative to each other.

Figure 26. State Machine Operating Sequence (Datapath)

### LED Pulse and Sample

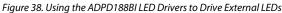

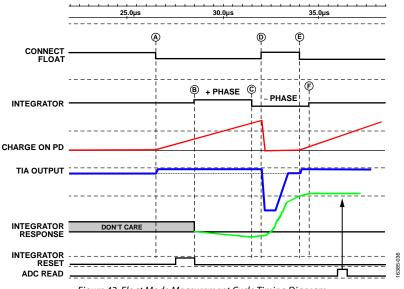

At each sampling period, the selected LED driver drives a series of LED pulses, as shown in Figure 22. The magnitude, duration, and number of pulses are programmable over the communications interface. Each LED pulse coincides with a sensing period so that the sensed value represents the total charge acquired on the photodiode in response to only the corresponding LED pulse. Charge, such as ambient light that does not correspond to the LED pulse, is rejected.

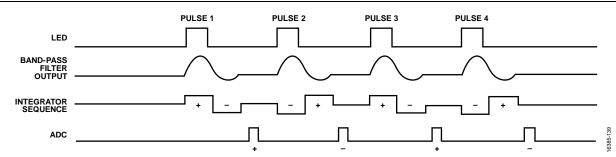

After each LED pulse, the photodiode output relating to the pulsed LED signal is sampled and converted to a digital value by the 14-bit ADC. Each subsequent conversion within a sampling period is summed with the previous result. Up to 255 pulse values from the ADC can be summed in an individual sampling period. There is a 20-bit maximum range for each sampling period.

### Averaging

The ADPD188BI offers sample accumulation and averaging functionality to increase signal resolution.

Within a sampling period, the AFE can sum up to 256 sequential pulses. As shown in Figure 26, samples acquired by the AFE are clipped to 20 bits at the output of the AFE. Up to 27 bits of additional resolution can be achieved by averaging between sampling periods. This accumulated data of N samples is stored as 27-bit values and can be read out directly by using the 32-bit output registers or the 32-bit FIFO configuration.

When using the averaging feature set up by the NUM\_AVG register, subsequent pulses can be averaged by powers of 2. The user can select from 2, 4, 8, ..., up to 128 samples to be averaged.

Pulse data is still acquired by the AFE at the sampling frequency,  $f_{SAMPLE}$  (see Register 0x12 in Table 34), but new data is written to the registers at the rate of  $f_{SAMPLE}$ /N every N<sup>th</sup> sample. This new data consists of the sum of the previous N samples. The full 32-bit sum is stored in the 32-bit registers. However, before sending this data to the FIFO, a divide by N operation occurs. This divide operation maintains bit depth to prevent clipping on the FIFO.

Use this divide operation between sample averaging to lower the noise while maintaining 16-bit resolution. If the pulse count registers are kept to 8 or less, the 16-bit width is never exceeded. Therefore, when using Register 0x15 to average subsequent pulses, many pulses can be accumulated without exceeding the 16-bit word width. This setting can reduce the number of FIFO reads required by the host processor.

### Data Read