# SANYO Semiconductors DATA SHEET

An ON Semiconductor Company

## Bi-CMOSIC For Variable Speed Control Three-Phase Brushless Motor Predriver

#### Overview

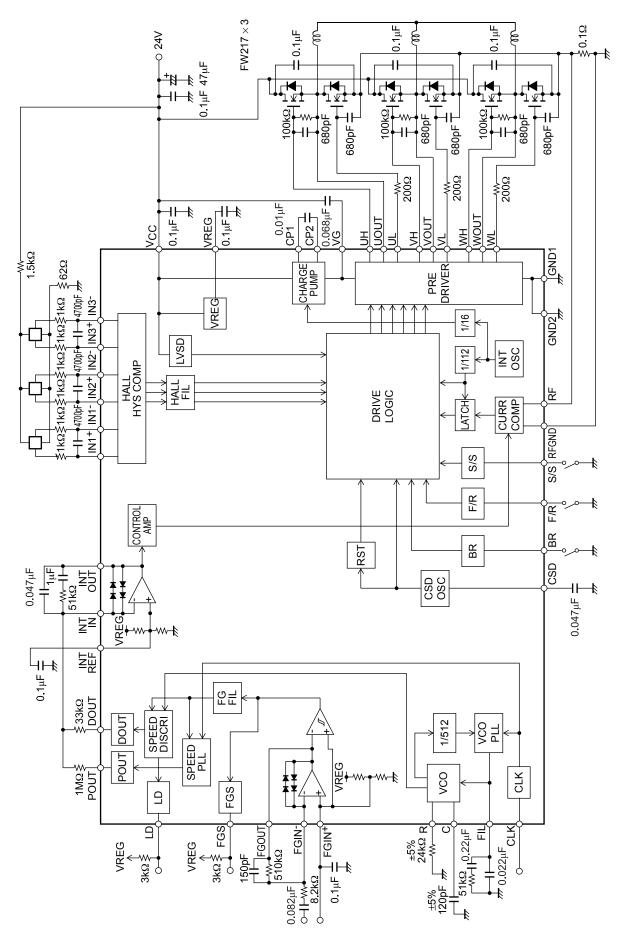

The LV8104V is a pre-driver IC designed for variable speed control of 3-phase brushless motors. It can be used to implement both upper and low output N-channel power FET drive circuit using a built-in charge pump circuit. High-efficiency drive is possible through the use of direct PWM drive and synchronous rectifyication.

#### **Functions**

- $V_{CC}$  max = VG max = 42V

- Three-phase bipolar direct PWM drive

- Built-in charge pump for the upper side gate drive voltage generation

- Speed discriminator and PLL speed control system

- High efficiency drive by synchronous rectification

- 5V regulator output

- Start/Stop switching circuit(power save state in a stop mode)

- Forward/reverse switching circuit

- Braking circuit (short braking)

- Built-in FG amplifier and integrating amplifier

- Built-in VCO circuit

- Speed lock detection output

- Current limiter

- Constaint protection circuit

- Clock disconnection protection circuit

- Thermal shutdown protection circuit

- Low-voltage protection circuit

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

SANYO Semiconductor Co., Ltd. www.semiconductor-sanyo.com/network

## Specifications

## Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions                           | Ratings     | Unit |

|-----------------------------|---------------------|--------------------------------------|-------------|------|

| Supply voltage              | V <sub>CC</sub> max | V <sub>CC</sub> = VG                 | 42          | V    |

| Charge pump output voltage  | VG max              | VG pin                               | 42          | V    |

| Output current              | I <sub>O</sub> max1 | Pins UL, VL, WL                      | -15 to 15   | mA   |

|                             | I <sub>O</sub> max2 | Pins UH, VH, WH, UOUT, VOUT and WOUT | -15 to 15   | mA   |

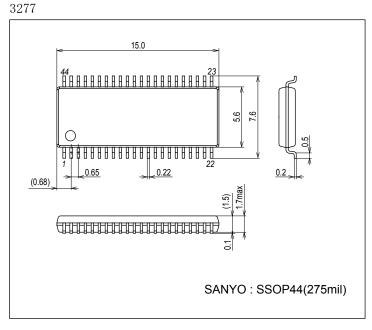

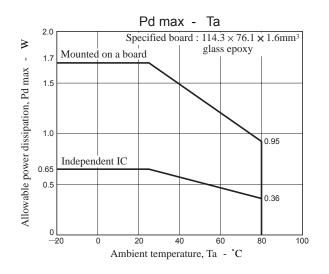

| Allowable power dissipation | Pd max1             | Independent IC                       | 0.65        | W    |

|                             | Pd max2             | Mounted on the specified board *     | 1.70        | W    |

| Operating temperature       | Topr                |                                      | -20 to +80  | °C   |

| Storage temperature         | Tstg                |                                      | -55 to +150 | °C   |

$^{\star}$  Specified board:114.3mm  $\times$  76.1mm  $\times$  1.6mm, glass epoxy board.

#### Allowable Operating range at $Ta = 25^{\circ}C$

| Parameter                          | Symbol           | Conditions | Ratings  | Unit |

|------------------------------------|------------------|------------|----------|------|

| Supply voltage range               | V <sub>CC</sub>  |            | 16 to 28 | V    |

| 5V constant voltage output current | I <sub>REG</sub> |            | 0 to -10 | mA   |

| LD pin applied voltage             | V <sub>LD</sub>  |            | 0 to 6   | V    |

| LD pin output current              | I <sub>LD</sub>  |            | 0 to 5   | mA   |

| FGS pin applied voltage            | V <sub>FGS</sub> |            | 0 to 6   | V    |

| FGS pin output current             | I <sub>FGS</sub> |            | 0 to 5   | mA   |

#### **Electrical Characteristics** at Ta = $25^{\circ}$ C, V<sub>CC</sub> = 24V

| Devenuelar                             | Oursels al            | Conditions                                   |                       | Ratings              |                       | 11-14 |

|----------------------------------------|-----------------------|----------------------------------------------|-----------------------|----------------------|-----------------------|-------|

| Parameter                              | Symbol                | Conditions                                   | min                   | typ                  | max                   | Unit  |

| Supply current 1                       | ICC1                  |                                              |                       | 6.5                  | 8.2                   | mA    |

| Supply current 2                       | I <sub>CC</sub> 2     | At stop                                      |                       | 3                    | 3.8                   | mA    |

| 5V Constant-voltage Output (VREG       | pin)                  |                                              |                       |                      |                       |       |

| Output voltage                         | VREG                  | I <sub>O</sub> = 5mA                         | 5.2                   | 5.6                  | 6.0                   | V     |

| Line regulation                        | $\Delta V$ (REG1)     | V <sub>CC</sub> = 16 to 28V                  |                       | 10                   | 50                    | mV    |

| Load regulation                        | $\Delta V$ (REG2)     | I <sub>O</sub> = -5 to -10mA                 |                       | 10                   | 50                    | mV    |

| Output block / Conditions : apply a VO | G voltage of 33V      |                                              |                       |                      |                       |       |

| High level output voltage 1            | V <sub>OH</sub> 1     | Pins UL, VL and WL I <sub>OH</sub> = -2mA    | VREG-0.48             | VREG-0.35            | VREG-0.22             | V     |

| Low level output voltage 1             | V <sub>OL</sub> 1     | Pins UL, VL and WL $I_{OL}$ = 2mA            | 0.19                  | 0.30                 | 0.41                  | V     |

| High level output voltage 2            | V <sub>OH</sub> 2     | Pins UH, VH and WH I <sub>OH</sub> = -2mA    | VG-0.65               | VG-0.5               | VG-0.35               | V     |

| Low level output voltage 2             | V <sub>OL</sub> 2     | Pins UH, VH and WH $I_{OL}$ = 2mA            | 0.45                  | 0.6                  | 0.8                   | V     |

| PWM frequency                          | f (PWM)               |                                              | 16                    | 20                   | 24                    | kHz   |

| Internal Oscillator                    |                       |                                              |                       |                      |                       |       |

| Oscillation frequency                  | f (REF)               |                                              | 1.79                  | 2.24                 | 2.69                  | MHz   |

| Charge Pump Output (VG pin)            |                       |                                              |                       |                      |                       |       |

| Output voltage                         | VGOUT                 |                                              | V <sub>CC</sub> +7.9  | V <sub>CC</sub> +9.0 | V <sub>CC</sub> +10.0 | V     |

| CP1 pin                                |                       |                                              |                       |                      |                       |       |

| High level output voltage              | V <sub>OH</sub> (CP1) | ICP1 = -2mA                                  | V <sub>CC</sub> -1.45 | V <sub>CC</sub> -1.1 | V <sub>CC</sub> -0.8  | V     |

| Low level output voltage               | V <sub>OL</sub> (CP1) | ICP1 = 2mA                                   | 0.5                   | 0.65                 | 0.8                   | V     |

| Charge pump frequency                  | f (CP1)               |                                              | 112                   | 140                  | 168                   | kHz   |

| Hall Amplifier                         |                       |                                              |                       |                      |                       |       |

| Input bias current                     | I <sub>B</sub> (HA)   |                                              | -2                    | -0.1                 |                       | μA    |

| Common-mode input voltage range 1      | VICM1                 | When using Hall elements                     | 0.3                   |                      | 3.5                   | V     |

| Common-mode input voltage range 2      | VICM2                 | At one-side input bias (Hall IC application) | 0                     |                      | VREG                  | V     |

| Hall input sensitivity                 |                       | SIN wave                                     | 50                    |                      |                       | mVp-p |

| Hysteresis width                       | ΔV <sub>IN</sub> (HA) |                                              | 5                     | 13                   | 24                    | mV    |

| Input voltage Low $\rightarrow$ High   | VSLH                  |                                              | 2                     | 7                    | 12                    | mV    |

| Input voltage High $\rightarrow$ Low   | VSHL                  |                                              | -12                   | -6                   | -2                    | mV    |

| Continued from preceding page.             |                       |                                            |           | Ratings  |           |              |

|--------------------------------------------|-----------------------|--------------------------------------------|-----------|----------|-----------|--------------|

| Parameter                                  | Symbol                | Conditions                                 | min       | typ      | max       | Unit         |

| FG Amplifier                               |                       |                                            |           |          |           |              |

| Input offset voltage                       | V <sub>IO</sub> (FG)  |                                            | -10       |          | 10        | mV           |

| Input bias current                         | IB (FG)               |                                            | -1        |          | 1         | μA           |

| Reference voltage                          | VB (FG)               |                                            | -5%       | VREG/2   | 5%        | V            |

| High level output voltage                  | V <sub>OH</sub> (FG)  | IFGI = -0.1mA, No load                     | 3.95      | 4.4      | 4.85      | V            |

| Low level output voltage                   | V <sub>OL</sub> (FG)  | IFGI = 0.1mA, No load                      | 0.75      | 1.2      | 1.65      | V            |

| FG input sensitivity                       |                       | GAIN : 100 times                           | 3         |          |           | mV           |

| Schmitt width of the next stage            |                       | One-side hysteresis comparator             | 120       | 200      | 280       | mV           |

| Operation frequency range                  |                       |                                            |           |          | 3         | kHz          |

| Open-loop gain                             |                       | f <sub>FG</sub> = 2kHz                     | 45        | 48       |           | dB           |

| FGS output                                 | 1                     | 1                                          |           |          |           |              |

| Output saturation voltage                  | V <sub>OL</sub> (FGS) | I <sub>FGS</sub> = 2mA                     |           | 0.2      | 0.4       | V            |

| Output leakage current                     | IL (FGS)              | $V_{O} = 6V$                               |           |          | 10        | μA           |

| CSD oscillator                             |                       | <u> </u>                                   |           |          |           |              |

| High level output voltage                  | V <sub>OH</sub> (CSD) |                                            | 2.9       | 3.4      | 3.9       | V            |

| Low level output voltage                   | V <sub>OL</sub> (CSD) |                                            | 1.6       | 2.0      | 2.4       | V            |

| Amplitude                                  | V (CSD)               |                                            | 1.15      | 1.4      | 1.65      | Vp-p         |

| External capacitor charge current          | ICHG1                 |                                            | -13       | -10      | -7        | μA           |

| External capacitor discharge current       | ICHG2                 |                                            | 7.5       | 10.5     | 13.5      | μA           |

| Oscillation frequency                      | f (CSD)               | C = 0.047µF                                |           | 78       |           | Hz           |

| Speed Discriminator output                 | ( )                   |                                            |           |          |           |              |

| High level output voltage                  | V <sub>OH</sub> (D)   |                                            | VREG-1.25 | VREG-1.0 | VREG-0.75 | V            |

| Low level output voltage                   | V <sub>OL</sub> (D)   |                                            | 0.65      | 0.9      | 1.15      | V            |

| Counts                                     | ·OL (2)               |                                            | 0.00      | 512      |           |              |

| LD output                                  |                       |                                            |           | 0.2      |           |              |

| Output saturation voltage                  | V <sub>OL</sub> (LD)  | I <sub>LD</sub> = 2mA                      |           | 0.2      | 0.4       | V            |

| Output leakage current                     | IL (LD)               | $V_{O} = 6V$                               |           |          | 10        | μA           |

| Lock range                                 |                       |                                            | -6.25     |          | +6.25     | μ <i>ι</i> ( |

| Speed control PLL output                   |                       |                                            | 0.20      |          | 0.20      | 70           |

| High level output voltage                  | V <sub>OH</sub> (P)   |                                            | VREG-2.0  | VREG-1.7 | VREG-1.4  | V            |

| Low level output voltage                   | V <sub>OL</sub> (P)   |                                            | 1.3       | 1.6      | 1.9       | v            |

| Current control circuit                    | VOL (1)               |                                            | 1.0       | 1.0      | 1.0       | v            |

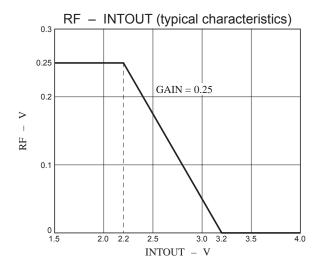

| Drive gain                                 | GDF                   |                                            | 0.20      | 0.25     | 0.32      |              |

| Current limiter operation                  | ODI                   |                                            | 0.20      | 0.25     | 0.02      |              |

| Limiter voltage                            | VRF                   | I                                          | 0.225     | 0.25     | 0.27      | V            |

| Integrator                                 | VIXI                  |                                            | 0.223     | 0.25     | 0.27      | v            |

|                                            |                       |                                            | 10        |          | 10        | m\/          |

| Input offset voltage<br>Input bias current | V <sub>IO</sub> (INT) |                                            | -10       |          | 10        | mV           |

| Reference voltage                          | I <sub>B</sub> (INT)  |                                            | -1        | VREG/2   | 5%        | μA<br>V      |

| High level output voltage                  | V <sub>B</sub> (INT)  | Intel = 0.1mA No.lood                      | -5%       |          |           | V            |

| Low level output voltage                   | V <sub>OH</sub> (INT) | $I_{INT}I = -0.1$ mA, No load              |           | 4.4      | 4.85      | V            |

| 1 5                                        | V <sub>OL</sub> (INT) | $I_{INT}I = 0.1 \text{mA}$ , No load       | 0.75      | 1.2      | 1.65      |              |

| Open-loop gain                             |                       | f <sub>INT</sub> = 2kHz                    | 45        | 48       |           | dB           |

| VCO Oscillator (C pin)                     | f(C)                  | C = 120 pc = 0.440                         | 0.45      |          | 4 F 4     | NAL 1-       |

| Oscillation frequency range                | f (C)                 | $C = 120 \text{pF}, R = 24 \text{k}\Omega$ | 0.15      |          | 1.54      | MHz          |

| High level output voltage                  | V <sub>OH</sub> (C)   | FIL = 2.5V                                 | 2.71      | 3.16     | 3.61      | V            |

| Low level output voltage                   | V <sub>OL</sub> (C)   | FIL = 2.5V                                 | 2.20      | 2.60     | 3.00      | V            |

| Amplitude                                  | V (C)                 | FIL = 2.5V                                 | 0.44      | 0.56     | 0.68      | Vp-р         |

| FIL pin                                    | 1                     | 1                                          |           | L        |           |              |

| Output source current                      | IOH (FIL)             |                                            | -15       | -11      | -6        | μA           |

| Output sink current                        | I <sub>OL</sub> (FIL) |                                            | 6         | 10       | 15        | μA           |

| Parameter                              | Symbol                | Conditions           |          | Ratings |      | Unit |

|----------------------------------------|-----------------------|----------------------|----------|---------|------|------|

| Falametei                              | Symbol                | Conditions           | min      | typ     | max  | Uni  |

| Low-voltage protection circuit         |                       |                      |          |         |      |      |

| Operation voltage                      | VLVSD                 |                      | 10.0     | 10.7    | 11.4 | V    |

| Hysteresis width                       | ∆VLVSD                |                      | 0.72     | 0.97    | 1.22 | V    |

| Thermal shutdown operation             | <u>.</u>              |                      |          |         |      |      |

| Thermal shutdown operation temperature | TSD                   | Design target value* | 150      | 175     |      | °C   |

| Hysteresis width                       | ΔTSD                  | Design target value* |          | 30      |      | °C   |

| CLK pin                                |                       |                      |          |         |      |      |

| Input frequency                        | fl (CLK)              |                      |          |         | 3    | kHz  |

| High level input voltage range         | V <sub>IH</sub> (CLK) |                      | 2.0      |         | VREG | V    |

| Low level input voltage range          | V <sub>IL</sub> (CLK) |                      | 0        |         | 1.0  | V    |

| Input open voltage                     | V <sub>IO</sub> (CLK) |                      | VREG-0.5 |         | VREG | V    |

| Hysteresis width                       | V <sub>IS</sub> (CLK) | Design target value* | 0.18     | 0.27    | 0.36 | V    |

| High level input current               | I <sub>IH</sub> (CLK) | VCLK = 5V            | -22      | -10     | -3   | μA   |

| Low level input current                | IIL (CLK)             | VCLK = 0V            | -133     | -93     | -70  | μA   |

| Pull-up resistance                     | RU (CLK)              |                      | 45       | 60      | 75   | kΩ   |

| S/S pin                                |                       |                      |          |         |      |      |

| High level input voltage range         | V <sub>IH</sub> (S/S) |                      | 2.0      |         | VREG | V    |

| Low level input voltage range          | V <sub>IL</sub> (S/S) |                      | 0        |         | 1.0  | V    |

| Input open voltage                     | V <sub>IO</sub> (S/S) |                      | VREG-0.5 |         | VREG | V    |

| Hysteresis width                       | V <sub>IS</sub> (S/S) |                      | 0.18     | 0.27    | 0.36 | V    |

| High level input current               | I <sub>IH</sub> (S/S) | VS/S = 5V            | -22      | -10     | -3   | μA   |

| Low level input current                | IIL (S/S)             | VS/S = 0V            | -133     | -93     | -70  | μA   |

| Pull-up resistance                     | RU (S/S)              |                      | 45       | 60      | 75   | kΩ   |

| F/R pin                                |                       |                      | I I      |         |      |      |

| High level input voltage range         | V <sub>IH</sub> (F/R) |                      | 2.0      |         | VREG | V    |

| Low level input voltage range          | V <sub>IL</sub> (F/R) |                      | 0        |         | 1.0  | V    |

| Input open voltage                     | V <sub>IO</sub> (F/R) |                      | VREG-0.5 |         | VREG | V    |

| Hysteresis width                       | V <sub>IS</sub> (F/R) |                      | 0.18     | 0.27    | 0.36 | V    |

| High level input current               | I <sub>IH</sub> (F/R) | VF/R = 5V            | -22      | -10     | -3   | μA   |

| Low level input current                | I <sub>IL</sub> (F/R) | VF/R = 0V            | -133     | -93     | -70  | μA   |

| Pull-up resistance                     | RU (F/R)              |                      | 45       | 60      | 75   | kΩ   |

| BR pin                                 |                       |                      | •        |         |      |      |

| High level input voltage range         | V <sub>IH</sub> (BR)  |                      | 2.0      |         | VREG | V    |

| Low level input voltage range          | V <sub>IL</sub> (BR)  |                      | 0        |         | 1.0  | V    |

| Input open voltage                     | V <sub>IO</sub> (BR)  |                      | VREG-0.5 |         | VREG | V    |

| Hysteresis width                       | V <sub>IS</sub> (BR)  |                      | 0.18     | 0.27    | 0.36 | V    |

| High level input current               | I <sub>IH</sub> (BR)  | VBR = 5V             | -22      | -10     | -3   | μA   |

| Low level input current                | I <sub>IL</sub> (BR)  | VBR = 0V             | -133     | -93     | -70  | μA   |

| Pull-up resistance                     | RU (BR)               |                      | 45       | 60      | 75   | kΩ   |

Note : \* These items are design target values and are not tested.

### **Package Dimensions**

unit : mm (typ)

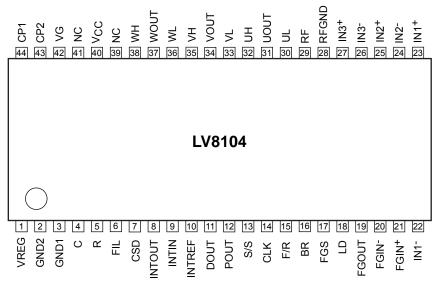

## **Pin Assignment**

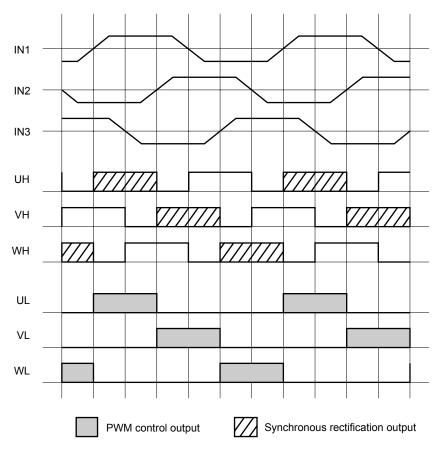

|   |     | F/R = "L" |     |     | F/R = "H" |     | Drive      | output     |

|---|-----|-----------|-----|-----|-----------|-----|------------|------------|

|   | IN1 | IN2       | IN3 | IN1 | IN2       | IN3 | Upper gate | Lower gate |

| 1 | Н   | L         | Н   | L   | Н         | L   | VH         | UL         |

| 2 | Н   | L         | L   | L   | Н         | Н   | WH         | UL         |

| 3 | Н   | Н         | L   | L   | L         | Н   | WH         | VL         |

| 4 | L   | Н         | L   | Н   | L         | Н   | UH         | VL         |

| 5 | L   | Н         | Н   | Н   | L         | L   | UH         | WL         |

| 6 | L   | L         | Н   | Н   | Н         | L   | VH         | WL         |

S/S Input

| Input        | Mode  |

|--------------|-------|

| High or Open | Stop  |

| Low          | Start |

| Dix iliput | BR | Input |

|------------|----|-------|

|------------|----|-------|

| Input        | Mode    |

|--------------|---------|

| High or Open | Brake   |

| Low          | Release |

#### **Current Control Characteristics**

#### **Block Diagram**

(Referance constants)

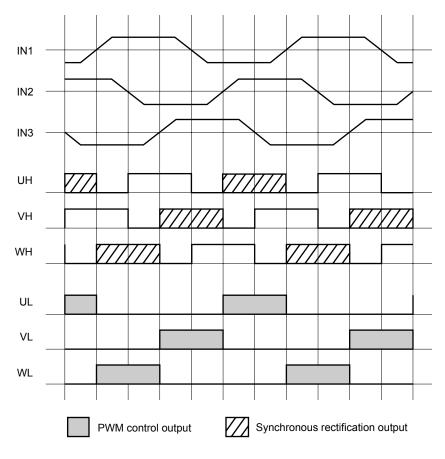

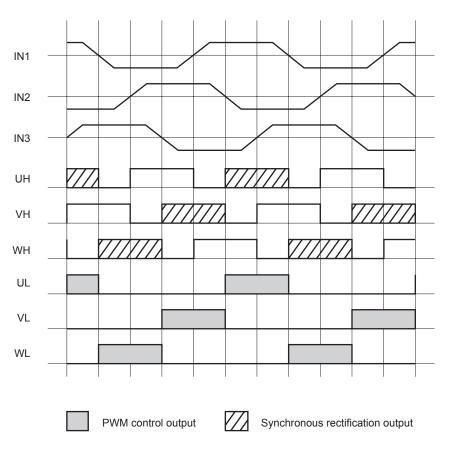

## **Relations Hall input with Drive output**

(1) When F/R = "L"

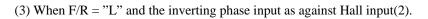

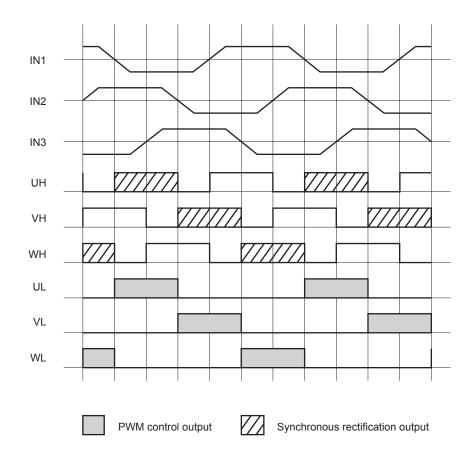

(4) When F/R="H" and the inverting phase input as against Hall input(1).

## LV8104V

| Pin Fu  | Inctions  | 6                                                                                                                |                                                                                                 |

|---------|-----------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Pin No. | Pin name  | Pin function                                                                                                     | Equivalent circuit                                                                              |

| 1       | VREG      | 5V constant voltage output pin(5.6V).<br>Connect a capacitor between this pin and GND.                           |                                                                                                 |

| 2       | GND2      | GND pins.                                                                                                        |                                                                                                 |

| 3 4     | GND1<br>C | GND1 and GND2 are connected in the IC.<br>VCO oscillation pin.<br>Connect a capacitor between this pin and GND.  | VREG                                                                                            |

| 5       | R         | Pin to set the charge / discharge current of the VCO<br>circuit.<br>Connect a resistor between this pin and GND. | VREG                                                                                            |

| 6       | FIL       | VCO PLL output filter pin.                                                                                       | VREG<br>6<br>500Ω<br>6<br>500Ω<br>m<br>m<br>m<br>m<br>m<br>m<br>m<br>m<br>m<br>m<br>m<br>m<br>m |

## LV8104V

| Continued | from precedi | ng page.                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.   | Pin name     | Pin function                                                                                                                                                                                         | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7         | CSD          | Pin to set the operating time of the constraint<br>protection.<br>Connect a capacitor between this pin and GND.<br>This pin combines also functions as the logic circuit<br>block initial reset pin. | VREG Reset circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8         | INTOUT       | Integrating amplifier output pin.                                                                                                                                                                    | VREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9         | INTIN        | Integrating amplifier inverting input pin.                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10        | INTREF       | Integrating amplifier non-inverting input pin.<br>1/2 VREG potential.<br>Connect a capacitor between this pin and GND.                                                                               | $(10) \xrightarrow{VREG} (10) \xrightarrow{VREG} (10$ |

| 11        | DOUT         | Speed discriminator output pin. Acceleration $\rightarrow$ high, deceleration $\rightarrow$ low.                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12        | POUT         | Speed control PLL output pin.<br>Outputs the phase comparison result for CLK and<br>FG.                                                                                                              | VREG<br>VREG<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)<br>(12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Continued | from precedi | ng page.                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.   | Pin name     | Pin function                                                                                                                                                                                  | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13        | S/S          | Start / Stop control pin.<br>Low : 0V to 1.0V<br>High : 2.0V to VREG<br>Goes high when left open.<br>Low for start.<br>The hysteresis width is about 0.27V.                                   | VREG<br>$55k\Omega \leq 5k\Omega$ (13)<br>m $m$ $m$ $m$ $m$ $m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14        | CLK          | External clock signal input pin.<br>Low : 0V to 1.0V<br>High : 2.0V to VREG<br>Goes high when left open.<br>The hysteresis width is about 0.27V.<br>f = 3kHz, maximum.                        | VREG<br>55kΩ \$<br>55kΩ \$<br>5kΩ (14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15        | F/R          | Forward / reverse control pin.<br>Low : 0V to 1.0V<br>High : 2.0V to VREG<br>Goes high when left open.<br>Low for forward.<br>The hysteresis width is about 0.27V.                            | VREG<br>55kΩ \$<br>55kΩ \$<br>55k |