# UNIPOLAR STEPPER MOTOR DRIVER

#### **+ GENERAL DESCRIPTION**

The NJW4350 is a high efficiency DMOS unipolar stepper motor driver IC.

Low Ron DMOS driver realizes high power efficiency and low heat generation of a stepper motor application. The motor can be controlled by step and direction pulse input which makes the programming task of a micro controller simple and easy.

Enhanced control feature, Motor Origin output, INH and RESET, make the NJW4350 applicable for a wide range of stepper motor applications.

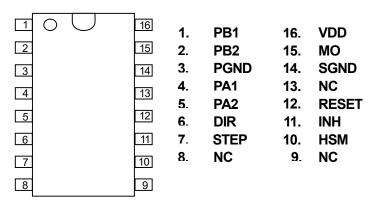

#### ◆ PACKAGE OUTLINE

#### **♦ FEATURES**

- Wide Voltage Range

5 to 50V

- Low  $R_{ON}$ =0.9 $\Omega$  typ.@lo= $\pm$ 500mA(U&L)

- STEP & DIR input Operation

- Half / Full Step Operation

- RESET Function

- Output Power Save Function (INH)

- Motor Origin Monitor Output (MO)

- Thermal Shutdown Circuit

- BCD Process Technology

- Package Outline DIP16

#### **PIN CONNECTION**

Fig.1 Pin Configuration

## **♦ BLOCK DIAGLAM** $\mathbf{I}_{\mathrm{DD}}$ VDD NJW4350 POWER ON RESET $I_{PLEAK}$ $I_{O}$ PB1 $I_{IH}\ I_{IL}$ PB2 STEP PA1 DIR PA2 HSM PHASE LOGIC CIRCUIT $V_P$ $V_{DD}$ RESE INH $I_{\text{MOLEAK}}$ $V_{\mathsf{IL}}$ МО Thermal Shut Down PGND SGND

Fig.2 Brock Diagram

## **♦ PIN DESCRIPTION**

| Pin | Pin name | Description                                                             |

|-----|----------|-------------------------------------------------------------------------|

| 1   | PB1      | B1 phase output with a maximum 1500 mA sinking open collector output    |

| 2   | PB2      | B2 phase output with a maximum 1500 mA sinking open collector output    |

| 3   | PGND     | Power ground terminal of motor supply VMM                               |

| 4   | PA1      | A1 phase output with a maximum of 1500 mA sinking open collector        |

| 5   | PA2      | A2 phase output with a maximum of 1500 mA sinking open collector        |

| 6   | DIR      | Direction command input for determining motor turning direction         |

| 7   | STEP     | Motor stepping pulse input, phase logic operation triggered by negative |

|     |          | edge of STEP signal                                                     |

| 8   | NC       | Not connected                                                           |

| 9   | NC       | Not connected                                                           |

| 10  | HSM      | Half/full step mode switching input                                     |

|     |          | H level in full step mode and L level in half step mode                 |

| 11  | INH      | Phase output off input, all phase output is off at H level              |

| 12  | RESET    | External reset signal input terminal                                    |

| 13  | NC       | Not connected                                                           |

| 14  | SGND     | Logic ground terminal of logic supply VDD                               |

| 15  | MO       | Phase output initial status detection output                            |

| 16  | VDD      | Logic unit power supply voltage terminal                                |

# **\*ABSOLUTE MAXIMUM RATINGS**

(Ta=25°C)

| PARAMETER               | RATINGS                     | SYMBOL (unit)                     | NOTE |

|-------------------------|-----------------------------|-----------------------------------|------|

| Phase output voltage    | 55                          | V <sub>P</sub> (V)                |      |

| Logic supply voltage    | 7.0                         | V <sub>DD</sub> (V)               |      |

| Output current          | 0.7                         | I <sub>o</sub> (A)                |      |

| Peak output current     | 1.5                         | I <sub>o</sub> (A)                |      |

| Logic input voltage     | -0.3 ~ V <sub>DD</sub> +0.3 | V <sub>ID</sub> (V)               |      |

| MO output current       | -20                         | I <sub>MO</sub> ( <sub>m</sub> A) |      |

| Operating temperature   | -40 ~ +85                   | Topr (°C)                         |      |

| Storage temperature     | -50 ~ <b>+</b> 150          | Tstg (°C)                         | _    |

| Total power dissipation | 1.6(DIP)                    | P <sub>D</sub> (W)                |      |

## **♦ RECOMMENDED OPERATING CONDITIONS**

(Ta=25°C)

| PARAMETER                  | SYMBOL         | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|----------------------------|----------------|----------------|------|------|------|------|

| Logic supply voltage       | $V_{DD}$       |                | 4.5  | 5.0  | 5.5  | V    |

| Phase output voltage       | $V_P$          |                | 5    | -    | 50   | V    |

| Junction temperature range | T <sub>j</sub> |                | -40  | -    | 125  | °C   |

| Output current             | Io             |                | -    | -    | 0.5  | Α    |

| Setup time                 | t <sub>s</sub> |                | -    | 0.5  | -    | μS   |

| Step pulse hold time       | t <sub>p</sub> |                | -    | 1.0  | -    | μS   |

## **◆ ERECTRICAL CHARACTERISTICS**

| (Ta=25°C, | $V_s=15V$ |

|-----------|-----------|

|-----------|-----------|

| PARAMETER                    | SYMBOL               | TEST CONDITION                               | MIN. | TYP. | MAX. | UNIT |

|------------------------------|----------------------|----------------------------------------------|------|------|------|------|

| ♦ GENERAL                    | •                    |                                              |      |      |      |      |

| Quiescent current            | I <sub>DD</sub>      | STEP, DIR, HSM, RESET,<br>INH Terminal High- | -    | 2.0  | 3.0  | mA   |

| Thermal shutdown             | T <sub>SD</sub>      |                                              | -    | 180  | -    | °C   |

| Thermal shutdown hysteresis  | T <sub>HYS</sub>     |                                              | -    | 50   | -    | °C   |

| ♦LOGIC                       |                      |                                              |      |      |      |      |

| Input H voltage              | V <sub>IH</sub>      |                                              | 3.5  | -    | -    | ٧    |

| Input L voltage              | V <sub>IL</sub>      |                                              | -    | -    | 1.5  | V    |

| Input current (High)         | I <sub>IH</sub>      | V <sub>IN</sub> =High                        | -    | 0.1  | 0.5  | μΑ   |

| Input current (Low)          | I <sub>IL</sub>      | V <sub>IN</sub> =Low                         | 50   | 100  | 200  | μΑ   |

| MO output saturation voltage | $V_{MO}$             | I <sub>MO</sub> =10mA                        | -    | 0.3  | 0.5  | V    |

| MO output leak current       | I <sub>MO LEAK</sub> | V <sub>MO</sub> =7V                          | -    | 0.1  | 0.5  | μΑ   |

| ♦ OUTPUT                     | •                    |                                              |      |      |      |      |

| Output resistance            | R <sub>ONL</sub>     | lo=500mA                                     | -    | 0.9  | -    | Ω    |

| Output leak current          | I <sub>PLEAK</sub>   | V <sub>P</sub> =50V                          | -    | 1.0  | 5.0  | μΑ   |

| Output turn ON time          | T <sub>ON</sub>      | lo= 500mA,L=1mH                              | -    | 100  | -    | ns   |

| Output turn OFF time         | T <sub>OFF</sub>     | lo= 500mA,L=1mH                              |      | 100  |      | ns   |

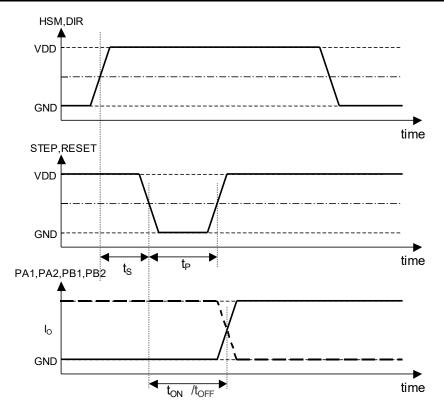

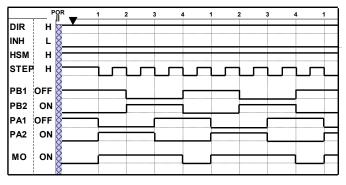

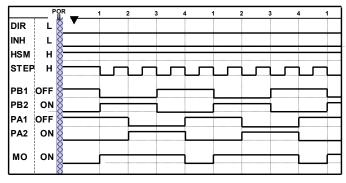

**Fig.3 Timing Chart**

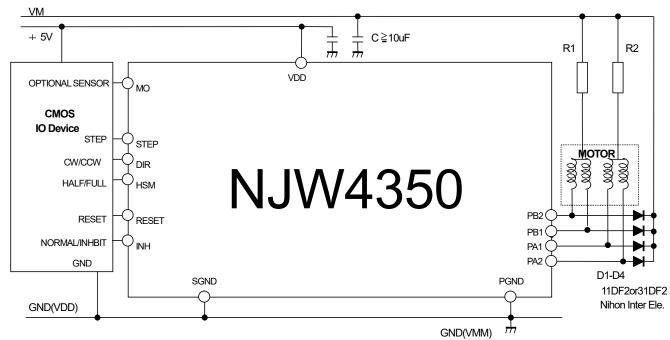

## ◆ Typical Application

**Fig.4 Application Circuit**

#### **♦ Function description**

The NJW4350 is a high-performance low-voltage driver system for driving stepping motors with unipolar winding. Employing a general-purpose STEP&DIR motion controller, it can easily control a stepping motor when combined with a pulse generator. The phase output is as high as 55V max. This prevents the phase output voltage margin of the motor from being exceeded, which is a common problem with unipolar winding systems and also simplifies the design of power control circuits during phase turn off.

#### **♦ Logic input**

All inputs are LS-TTL compatible. When the logic input is open, the circuit recognizes any open logic inputs as H level. The NJW4350 has built-in phase logic for optimum control of the stepping motor.

#### • STEP - Stepping pulse

The built-in phase logic sequencer goes UP on every negative edge of the STEP signal (pulse). In full step mode, the pulse turns the stepping motor at the basic step angle. In half step mode, two pulses are required to turn the motor at the basic step angle.

The DIR (direction) signal and HSM (half/full mode) are latched to the STEP negative edge and must therefore be established before the start of the negative edge. Note the setup time ts in Figure 3.

#### • DIR - direction

The DIR signal determines the step direction. The direction of the stepping motor depends on how the NJW4350 is connected to the motor. Although DIR can be modified this should be avoided since a misstep of 1 pulse increment may occur if it is set simultaneous with the negative edge. See the timing chart in Figure 3.

#### HSM – half/full step mode switching

This signal determines whether the stepping motor turns at half step or full step mode. The built-in phase logic is set to the half step mode when HSM is low level. Although HSM can be modified this should be avoided since a misstep of 1 pulse increment may occur if it is set simultaneous with the negative edge. See the timing chart in Figure 3.

#### • INH - phase output off

All phase output is turned off when INH goes high reducing power consumption (consumption current).

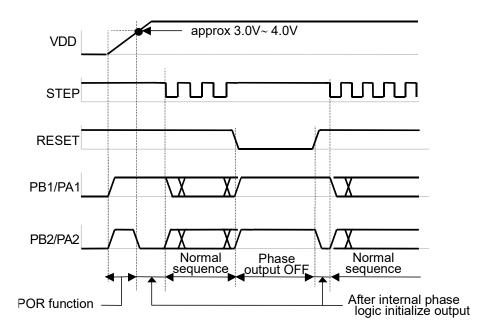

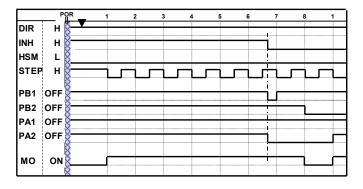

#### RESET

A two-phase stepping motor repeats the same winding energizing sequence every angle that is a multiple of four of the basic step. The phase logic sequence is repeated every four pulses in the full step mode and every eight pulses in the half step mode.

RESET forces to initialize the phase logic to sequence start mode.

When RESET is at L level, the phase logic is initialized and the phase output is turned off.

When RESET recovers to H level, the phase output resumes the energizing pattern output at sequence start of phase logic. Refer to Figure 5 for a reset timing chart.

#### ♦ POR – power on and reset function

The internal power-on and reset circuit, which is connected to VDD, resets the phase logic and turns off phase output when the power is supplied to prevent missteps.

Each time the power is turned on, the energizing pattern of phase logic at sequence start is output.

#### ♦ Phase output unit

The phase output unit is composed of four open collector transistors that are directly connected to the stepping motor as shown in Figure 4.

#### ♦MO – origin monitor

At sequence start of the phase logic or after POR or external RESET, an L level output is made to indicate to external devices that the energizing sequence is in initial status.

Fig.5 POR and external reset timing

| STEP | After  | 1   | 2   | 3   | 4   |

|------|--------|-----|-----|-----|-----|

|      | RESAET |     |     |     |     |

| PB1  | OFF    | OFF | ON  | ON  | OFF |

| PB2  | ON     | ON  | OFF | OFF | ON  |

| PA1  | OFF    | ON  | ON  | OFF | OFF |

| PA2  | ON     | OFF | OFF | ON  | ON  |

Fig.6 Full step mode / Forward Direction sequence

| STEP | After  | 1   | 2   | 3   | 4   |

|------|--------|-----|-----|-----|-----|

|      | RESAET |     |     |     |     |

| PB1  | OFF    | ON  | ON  | OFF | OFF |

| PB2  | ON     | OFF | OFF | ON  | ON  |

| PA1  | OFF    | OFF | ON  | ON  | OFF |

| PA2  | ON     | ON  | OFF | OFF | ON  |

Fig.7 Full step mode / Reverse Direction sequence

|         | POR _    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 1 |

|---------|----------|---|---|---|---|---|---|---|---|---|

| DIR L   |          |   |   |   |   |   |   |   |   |   |

| INH L   | 8        |   |   |   |   |   |   |   |   |   |

| HSM L   | ×        |   |   |   |   |   |   |   |   |   |

| STEP H  | <u> </u> |   | ட | Т | ய | ௶ | Ш | ш |   |   |

| PB1 OFF |          |   |   |   |   |   |   |   |   |   |

| PB2 ON  | 8        |   |   |   |   |   | 1 |   |   |   |

| PA1 OFF |          |   |   |   | i |   |   |   |   |   |

| PA2 ON  | <u> </u> |   |   | _ |   |   |   |   | ┪ |   |

| MO ON   | ×        |   |   |   |   |   |   |   |   |   |

| į       | 8        |   |   |   |   |   |   |   |   |   |

| After  | 1                |                       | 3                                 | 4                                                                                                                                                                                          | 5                                                                  | 6                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|------------------|-----------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESAET |                  |                       |                                   |                                                                                                                                                                                            |                                                                    |                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OFF    | OFF              | OFF                   | OFF                               | ON                                                                                                                                                                                         | ON                                                                 | ON                                                                                                                                                                                                             | OFF                                                                                                                                                                                                                                                                 | OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ON     | ON               | ON                    | OFF                               | OFF                                                                                                                                                                                        | OFF                                                                | OFF                                                                                                                                                                                                            | OFF                                                                                                                                                                                                                                                                 | ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OFF    | OFF              | ON                    | ON                                | ON                                                                                                                                                                                         | OFF                                                                | OFF                                                                                                                                                                                                            | OFF                                                                                                                                                                                                                                                                 | OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ON     | OFF              | OFF                   | OFF                               | OFF                                                                                                                                                                                        | OFF                                                                | ON                                                                                                                                                                                                             | ON                                                                                                                                                                                                                                                                  | ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F      | OFF<br>ON<br>OFF | RESAET OFF ON OFF OFF | RESAET OFF OFF OFF ON ON ON ON ON | RESAET         OFF         OFF         OFF           OFF         OF         OFF         OFF           ON         ON         ON         OFF           OFF         OFF         ON         ON | RESAET         STATE OF THE OFF OFF OFF OFF OFF OFF OFF OFF OFF OF | RESAET         OFF         OFF         OFF         ON         ON           ON         ON         ON         OFF         OFF         OFF           OFF         OFF         ON         ON         ON         OFF | RESAET         STATE OFF         OFF         OFF         ON         ON         ON           OF         OF         OFF         OFF         OFF         OFF         OFF           OFF         OFF         ON         ON         ON         ON         OFF         OFF | RESAET         OFF         OFF         OFF         ON         ON         ON         OFF           ON         ON         ON         OFF         OFF |

Fig.8 Half step mode / Forward Direction sequence

|      | P   | OR       | 1 | 2        | 3 | 4 | 5 | 6        | 7 | 8 | 1 |

|------|-----|----------|---|----------|---|---|---|----------|---|---|---|

| DIR  | L   | ₹ ▼      |   |          |   |   |   |          |   |   |   |

| INH  | L   | <u> </u> |   |          |   |   |   |          |   |   |   |

| нѕм  | L   | <u> </u> |   |          |   |   |   |          |   |   |   |

| STEP | н   | <u> </u> |   | ட        | ௶ | ய | ட | ட        | ய | ௶ | 辶 |

| PB1  | OFF | <u>X</u> |   | <u> </u> |   |   |   |          |   |   |   |

| PB2  | ON  | <u> </u> |   |          |   |   |   | <u> </u> |   |   |   |

| PA1  | OFF | <u> </u> |   |          |   | 1 |   |          |   |   |   |

| PA2  | ON  | <u> </u> |   |          |   |   |   |          |   | 1 |   |

| мо   | ON  | <u> </u> |   |          |   |   |   |          |   |   |   |

|      |     | Ŷ        |   |          |   |   |   |          |   |   |   |

| Ī | STEP | After  | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   |

|---|------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|   |      | RESAET |     |     |     |     |     |     |     |     |

|   | PB1  | OFF    | OFF | ON  | ON  | ON  | OFF | OFF | OFF | OFF |

|   | PB2  | ON     | OFF | OFF | OFF | OFF | OFF | ON  | ON  | ON  |

|   | PA1  | OFF    | OFF | OFF | OFF | ON  | ON  | ON  | OFF | OFF |

|   | PA2  | ON     | ON  | ON  | OFF | OFF | OFF | OFF | OFF | ON  |

Fig.9 Half step mode / Reverse Direction sequence

Fig.10 Half step mode / INH sequence

# NJW4350

#### ◆ Application examples

#### • Logic input unit

The circuit handles an open state in the logic input unit as an H level input. Unused input units should be fixed at  $V_{DD}$  level to maximize noise resistance characteristics.

#### Phase output unit

The phase output unit is provided with a power sink to enable unipolar drive of stepping motor windings. The resistor connected to the common line of the winding determines the maximum motor power.

To protect output transistors from kickback power, a high-speed free wheeling diode is required.

#### ♦ I/O signal sequence in each drive mode

Timing charts for I/O signals in each drive mode are shown in Figures 6 to 10. The left side shows input and output signals after POR.

#### ♦ Precautions

- 1. Do not remove ICs or PCBs when power is supplied.

- 2. Note that some stepping motors may generate excessive voltages even when free wheeling diode is used.

- 3. Select a stepping motor with the required power rating to obtain the required torque. Generally, the higher the input voltage of the stepping motor, the higher rpm it will produce. When the supply voltage is higher than stepping motor rated voltage, a current limit resistor must be used to connect the common winding to the power supply. Use the L/R time constant of the resistor to obtain optimum high-speed rpm characteristics from the stepping motor.

- 4. Do not use motor power supplies (without an output capacitor) with a serial diode. Nor use ground lines with common impedance with VDD, instead make a one point ground connection using the PGND terminal (pin3) and SGND terminal (pin14) of the IC.

- 5. To reverse motor rotation, reverse PA and PA2 (or PB1 and PB2) stepping motor connections.

- 6. Drive circuit

High-performance stepping motor operation requires that the windings are energized speedily at phase turn on, and that energizing is quickly turned off at turn off.

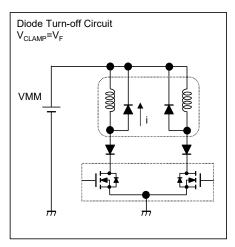

## 7. Phase turnoff problems

The drive circuit may be damaged if the kickback voltage induced when the energizing of the windings is turned off (when winding current is turned off) is not adequately suppressed.

Refer to the description of turn-off circuit as follow.

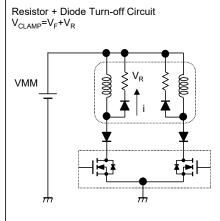

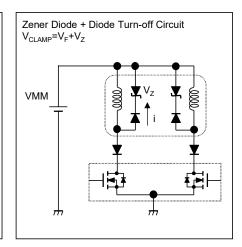

#### < About the turn-off circuit >

There are various turn-off circuit methods for the purpose of extracting the speed performance of the motor.

The turn-off time of motor current depends on the clamp voltage of the turn-off circuit.

Therefore, it is necessary to select an appropriate turn-off method according to the motor speed.

However, the larger the clamp voltage of the turn-off circuit, the negative voltage is generated by electromagnetic induction to the other winding.

| Method                 | Diode Turn-off | Resistor + Diode Turn-off | Zener Diode + Diode Turn-off |  |  |

|------------------------|----------------|---------------------------|------------------------------|--|--|

| External parts scale   | Small          | Medium                    | Large                        |  |  |

| Motor Speed            | Low            | High                      |                              |  |  |

| Negative voltage value | Low            | Middle                    | to High                      |  |  |

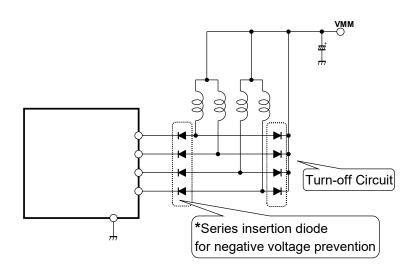

#### < Prevention of Malfunction for Negative Voltage >

In unipolar motor drive, when switching the winding current electromagnetically coupled, the output pin may become below the GND potential due to long wiring of the motor, routing of the GND wiring of the mounting board, turn-off circuit type, and so on.

Due to the nature of the monolithically structured IC, when a large negative voltage is applied to the output pin, the inside of the IC may cause unexpected operation, which may cause circuit malfunction (miss step).

Therefore, in order to reliably prevent circuit malfunction due to negative voltage, it is recommended to insert a diode in series at the output pin and take countermeasures.

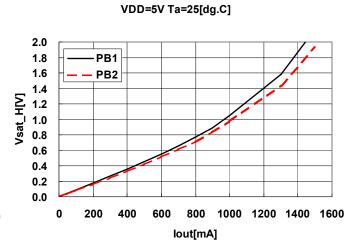

## **TYIPICAL CHARACTERISTICS**

INPUT=H ta=25[dg.C] 3.0 2.5 2.0 1.5 1.0 0.5 0.0 2 5 7 0 3 4 6 VCC[V]

VDD VS. IDD1

VDD VS. IDD2 INPUT=L Ta=25[dg.C] 3.0 2.5 2.0 1.5 1.0 0.5 0.0 0 2 3 5 6 vcc[v]

IMO VS. VMO VDD=5V Ta=25[dg.C] 1.0 0.8 0.6 0.4 0.2 0.0 0 20 40 60 80 100 IMO[mA]

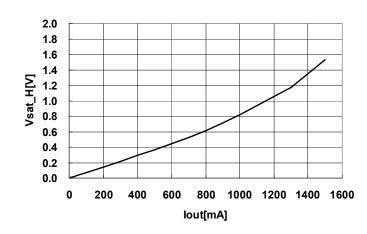

**lout VS. Vout**

lout VS. Vout VDD=7V Ta=25[dg.C]

[CAUTION]

The specifications on this datasheets are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this datasheets are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NJR:

NJW4350D

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А