ISO-CMOS ST-BUS<sup>™</sup> Family

MT8980D Digital Switch

Data Sheet

February 2005

# Features

- · Zarlink ST-BUS compatible

- 8-line x 32-channel inputs

- 8-line x 32-channel outputs

- 256 ports non-blocking switch

- Single power supply (+5 V)

- Low power consumption: 30 mW Typ.

- Microprocessor-control interface

- · Three-state serial outputs

| Ordering Information                                                      |                                                                                           |                                                                |  |  |  |  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| MT8980DE<br>MT8980DP<br>MT8980DPR<br>MT8980DP1<br>MT8980DE1<br>MT8980DPR1 | 40 Pin PDIP<br>44 Pin PLCC<br>44 Pin PLCC<br>44 Pin PLCC*<br>40 Pin PDIP*<br>44 Pin PLCC* | Tubes<br>Tubes<br>Tape & Reel<br>Tubes<br>Tubes<br>Tape & Reel |  |  |  |  |

|                                                                           | *Pb Free Matte Tin<br>-40°C to +85°C                                                      |                                                                |  |  |  |  |

# Description

This VLSI ISO-CMOS device is designed for switching PCM-encoded voice or data, under microprocessor control, in a modern digital exchange, PBX or Central Office. It provides simultaneous connections for up to 256 64 kbit/s channels. Each of the eight serial inputs and outputs consist of 32 64 kbit/s channels multiplexed to form a 2048 kbit/s ST-BUS stream. In addition, the MT8980 provides microprocessor read and write access to individual ST-BUS channels.

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 1997-2005, Zarlink Semiconductor Inc. All Rights Reserved.

1

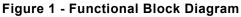

## Figure 2 - Pin Connections

#### **Pin Description**

| Pi        | n #        |               |                                                                                                                                                                                                                                                                  |

|-----------|------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40<br>DIP | 44<br>PLCC | Name          | Description                                                                                                                                                                                                                                                      |

| 1         | 2          | DTA           | <b>Data Acknowledgement (Open Drain Output).</b> This is the data acknowledgement on the microprocessor interface. This pin is pulled low to signal that the chip has processed the data. A 909 $\Omega$ , 1/4W, resistor is recommended to be used as a pullup. |

| 2-4       | 3-5        | STi0-<br>STi2 | <b>ST-BUS Input 0 to 2 (Inputs).</b> These are the inputs for the 2048 kbit/s ST-BUS input streams.                                                                                                                                                              |

| 5-9       | 7-11       | STi3-<br>STi7 | ST-BUS Input 3 to 7 (Inputs). These are the inputs for the 2048 kbit/s ST-BUS input streams.                                                                                                                                                                     |

| 10        | 12         | $V_{DD}$      | Power Input. Positive Supply.                                                                                                                                                                                                                                    |

| 11        | 13         | F0i           | <b>Framing 0-Type (Input).</b> This is the input for the frame synchronization pulse for the 2048 kbit/s ST-BUS streams. A low on this input causes the internal counter to reset on the next negative transition of $\overline{C4i}$ .                          |

| 12        | 14         | C4i           | 4.096 MHz Clock (Input). ST-BUS bit cell boundaries lie on the alternate falling edges of this clock.                                                                                                                                                            |

| 13-15     | 15-17      | A0-A2         | Address 0 to 2 (Inputs). These are the inputs for the address lines on the microprocessor interface.                                                                                                                                                             |

| 16-18     | 19-21      | A3-A5         | Address 3 to 5 (Inputs). These are the inputs for the address lines on the microprocessor interface.                                                                                                                                                             |

| 19        | 22         | DS            | Data Strobe (Input). This is the input for the active high data strobe on the microprocessor interface.                                                                                                                                                          |

| 20        | 23         | R/W           | <b>Read or Write (Input).</b> This is the input for the read/write signal on the microprocessor interface - high for read, low for write.                                                                                                                        |

| 21        | 24         | CS            | Chip Select (Input). This is the input for the active low chip select on the microprocessor interface                                                                                                                                                            |

#### **Pin Description (continued)**

| Pi        | n #              |                 |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|-----------|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 40<br>DIP | 44<br>PLCC       | Name            | Description                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 22-24     | 25-27            | D7-D5           | Data 7 to 5 (Three-state I/O Pins). These are the bidirectional data pins on the microprocessor interface.                                                                                                                                                                                                               |  |  |  |  |  |  |

| 25-29     | 29-33            | D4-D0           | Data 4 to 0 (Three-state I/O Pins). These are the bidirectional data pins on the microprocessor interface.                                                                                                                                                                                                               |  |  |  |  |  |  |

| 30        | 34               | V <sub>ss</sub> | Power Input. Negative Supply (Ground).                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 31-35     | 35-39            | STo7-<br>STo3   | <b>ST-BUS Output 7 to 3 (Three-state Outputs).</b> These are the pins for the eight 2048 kbit/s ST-BUS output streams.                                                                                                                                                                                                   |  |  |  |  |  |  |

| 36-38     | 41-43            | STo2-<br>STo0   | <b>ST-BUS Output 2 to 0 (Three-state Outputs).</b> These are the pins for the eight 2048 kbit/s ST-BUS output streams.                                                                                                                                                                                                   |  |  |  |  |  |  |

| 39        | 44               | ODE             | <b>Output Drive Enable (Input).</b> If this input is held high, the STo0-STo7 output drivers function normally. If this input is low, the STo0-STo7 output drivers go into their high impedance state. <b>NB:</b> Even when ODE is high, channels on the STo0-STo7 outputs can go high impedance under software control. |  |  |  |  |  |  |

| 40        | 1                | CSTo            | <b>Control ST-BUS Output (Complementary Output).</b> Each frame of 256 bits on this ST-BUS output contains the values of bit 1 in the 256 locations of the Connection Memory High.                                                                                                                                       |  |  |  |  |  |  |

|           | 6, 18,<br>28, 40 | NC              | No Connection.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

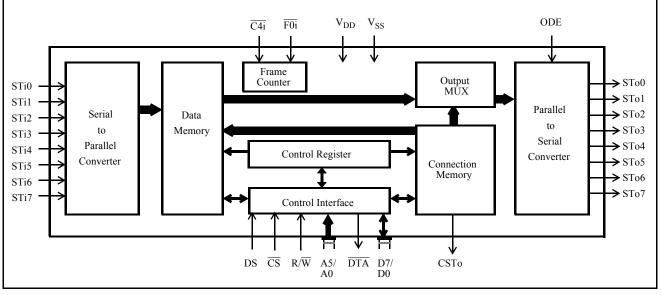

# **Functional Description**

In recent years, there has been a trend in telephony towards digital switching, particularly in association with software control. Simultaneously, there has been a trend in system architectures towards distributed processing or multi-processor systems.

In accordance with these trends, Zarlink has devised the ST-BUS (Serial Telecom Bus). This bus architecture can be used both in software-controlled digital voice and data switching, and for interprocessor communications. The uses in switching and in interprocessor communications are completely integrated to allow for a simple general purpose architecture appropriate for the systems of the future.

The serial streams of the ST-BUS operate continuously at 2048 kbit/s and are arranged in 125  $\mu$ s wide frames which contain 32 8-bit channels. Zarlink manufactures a number of devices which interface to the ST-BUS; a key device being the MT8980 chip.

The MT8980 can switch data from channels on ST-BUS inputs to channels on ST-BUS outputs, and simultaneously allows its controlling microprocessor to read channels on ST-BUS inputs or write to channels on ST-BUS outputs (Message Mode). To the microprocessor, the MT8980 looks like a memory peripheral. The microprocessor can write to the MT8980 to establish switched connections between input ST-BUS channels and output ST-BUS channels, or to transmit messages on output ST-BUS channels. By reading from the MT8980, the microprocessor can receive messages from ST-BUS input channels or check which switched connections have already been established.

By integrating both switching and interprocessor communications, the MT8980 allows systems to use distributed processing and to switch voice or data in an ST-BUS architecture.

#### Hardware Description

Serial data at 2048 kbit/s is received at the eight ST-BUS inputs (STi0 to STi7), and serial data is transmitted at the eight ST-BUS outputs (STo0 to STo7). Each serial input accepts 32 channels of digital data, each channel containing an 8-bit word which may represent a PCM-encoded analog/voice sample as provided by a codec (e.g., Zarlink's MT8964).

This serial input word is converted into parallel data and stored in the 256 X 8 Data Memory. Locations in the Data Memory are associated with particular channels on particular ST-BUS input streams. These locations can be read by the microprocessor which controls the chip.

Locations in the Connection Memory, which is split into high and low parts, are associated with particular ST-BUS output streams. When a channel is due to be transmitted on an ST-BUS output, the data for the channel can either be switched from an ST-BUS input or it can originate from the microprocessor. If the data is switched from an input, then the contents of the Connection Memory Low location associated with the output channel is used to address the Data Memory. This Data Memory address corresponds to the channel on the input ST-BUS stream on which the data for switching arrived. If the data for the output channel originates from the microprocessor (Message Mode), then the contents of the Connection Memory Low location associated with the output channel are output directly, and this data is output repetitively on the channel once every frame until the microprocessor intervenes.

The Connection Memory data is received, via the Control Interface, at D7 to D0. The Control Interface also receives address information at A5 to A0 and handles the microprocessor control signals CS, DTA, R/W and DS. There are two parts to any address in the Data Memory or Connection Memory. The higher order bits come from the Control Register, which may be written to or read from via the Control Interface. The lower order bits come from the address lines directly.

The Control Register also allows the chip to broadcast messages on all ST-BUS outputs (i.e., to put every channel into Message Mode), or to split the memory so that reads are from the Data Memory and writes are to the Connection Memory Low. The Connection Memory High determines whether individual output channels are in Message Mode, and allows individual output channels to go into a high-impedance state, which enables arrays of MT8980s to be constructed. It also controls the CSTo pin.

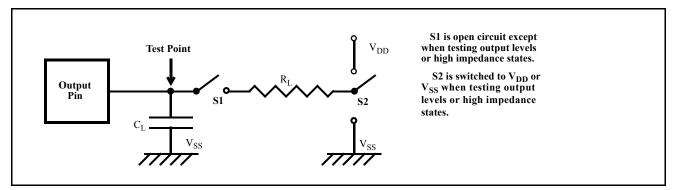

All ST-BUS timing is derived from the two signals  $\overline{C4i}$  and  $\overline{F0i}$ .

| A5      | A4        | A3        | A2         | A1         | A0          | HEX ADDRESS | LOCATION                |

|---------|-----------|-----------|------------|------------|-------------|-------------|-------------------------|

| 0       | Х         | Х         | Х          | Х          | Х           | 00 - 1F     | Control Register *      |

| 1       | 0         | 0         | 0          | 0          | 0           | 20          | Channel 0 <sup>†</sup>  |

| 1       | 0         | 0         | 0          | 0          | 1           | 21          | Channel 1 <sup>†</sup>  |

| •       | •         | •         | •          | •          | •           | •           | •                       |

| •       | •         | •         | •          | •          | •           | •           | •                       |

| •       | •         | •         | •          | •          | •           | •           | •                       |

| 1       | 1         | 1         | 1          | 1          | 1           | 3F          | Channel 31 <sup>†</sup> |

| * Writi | ng to the | Control I | Register i | s the only | v fast trar | saction     |                         |

\* Writing to the Control Register is the only fast transaction.

<sup>†</sup> Memory and stream are specified by the contents of the Control Register.

#### Figure 3 - Address Memory Map

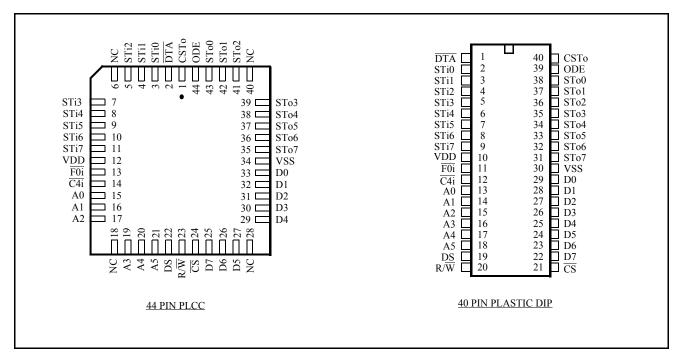

#### Software Control

The address lines on the Control Interface give access to the Control Register directly or, depending on the contents of the Control Register, to the High or Low sections of the Connection Memory or to the Data Memory.

If address line A5 is low, then the Control Register is addressed regardless of the other address lines (see Fig. 3). If A5 is high, then the address lines A4-A0 select the memory location corresponding to channel 0-31 for the memory and stream selected in the Control Register.

The data in the Control Register consists of mode control bits, memory select bits, and stream address bits (see Fig. 4). The memory select bits allow the Connection Memory High or Low or the Data Memory to be chosen, and the stream address bits define one of the ST-BUS input or output streams.

|     |                        | (unused)<br>Mode<br>Control<br>Bits<br>7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-----|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BIT | NAME                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 7   | Split Memory           | When 1, all subsequent reads are from the Data Memory and writes are to the Connection Memory<br>Low, except when the Control Register is accessed again. When 0, the Memory Select bits specify<br>the memory for subsequent operations. In either case, the Stream Address Bits select the subsection<br>of the memory which is made available. |  |  |  |  |  |

| 6   | Message<br>Mode        | When 1, the contents of the Connection Memory Low are output on the Serial Output streams except when the ODE pin is low. When 0, the Connection Memory bits for each channel determine what is output.                                                                                                                                           |  |  |  |  |  |

| 5   | (unused)               |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 4-3 | Memory<br>Select Bits  | -0 - Not to be used<br>-1 - Data Memory (read only from the microprocessor port)<br>-0 - Connection Memory Low<br>-1 - Connection Memory High                                                                                                                                                                                                     |  |  |  |  |  |

| 2-0 | Stream<br>Address Bits | The number expressed in binary notation on these bits refers to the input or output ST-BUS stream which corresponds to the subsection of memory made accessible for subsequent operations.                                                                                                                                                        |  |  |  |  |  |

#### Figure 4 - Control Register Bits

Bit 7 of the Control Register allows split memory operation - reads are from the Data Memory and writes are to the Connection Memory Low.

The other mode control bit, bit 6, puts every output channel on every output stream into active Message Mode; i.e., the contents of the Connection Memory Low are output on the ST-BUS output streams once every frame unless the ODE pin is low. In this mode the chip behaves as if bits 2 and 0 of every Connection Memory High location were 1, regardless of the actual values.

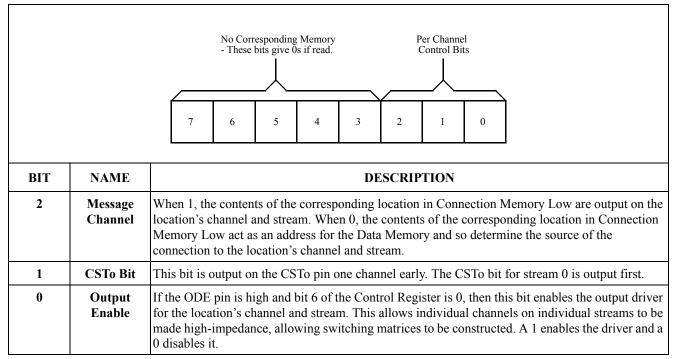

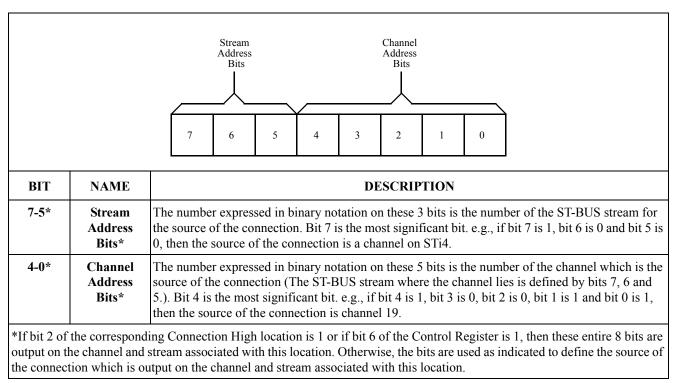

If bit 6 of the Control Register is 0, then bits 2 and 0 of each Connection Memory High location function normally (see Fig. 5). If bit 2 is 1, the associated ST-BUS output channel is in Message Mode; i.e., the byte in the corresponding Connection Memory Low location is transmitted on the stream at that channel. Otherwise, one of the bytes received on the serial inputs is transmitted and the contents of the Connection Memory Low define the ST-BUS input stream and channel where the byte is to be found (see Fig. 6).

If the ODE pin is low, then all serial outputs are high-impedance. If it is high and bit 6 in the Control Register is 1, then all outputs are active. If the ODE pin is high and bit 6 in the Control Register is 0, then the bit 0 in the Connection Memory High location enables the output drivers for the corresponding individual ST-BUS output stream and channel. Bit 0=1 enables the driver and bit 0=0 disables it (see Fig. 5).

Bit 1 of each Connection Memory High location (see Fig. 5) is output on the CSTo pin once every frame. To allow for delay in any external control circuitry the bit is output one channel before the corresponding channel on the ST-BUS streams, and the bit for stream 0 is output first in the channel; e.g., bit 1's for channel 9 of streams 0-7 are output synchronously with ST-BUS channel 8 bits 7-0.

Figure 5 - Connection Memory High Bits

## Figure 6 - Connection Memory Low Bits

# Applications

## Use in a Simple Digital Switching System

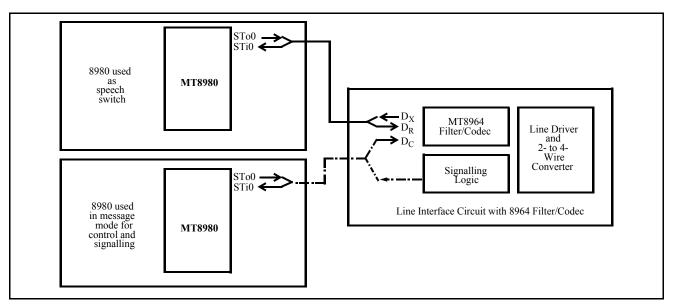

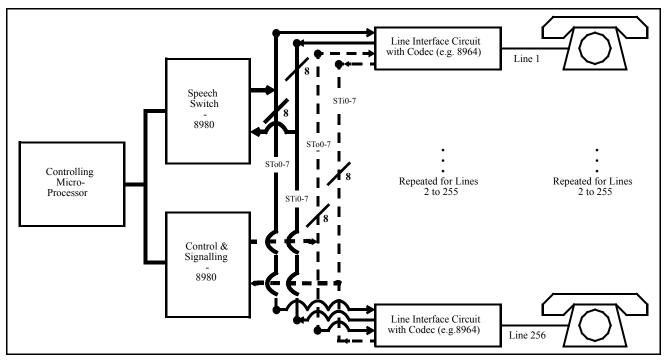

Figs. 7 and 8 show how MT8980s can be used with MT8964s to form a simple digital switching system. Fig. 7 shows the interface between the MT8980s and the filter/codecs. Fig. 8 shows the position of these components in an example architecture.

The MT8964 filter/codec in Fig. 7 receives and transmits digitized voice signals on the ST-BUS input  $D_R$ , and ST-BUS output  $D_X$ , respectively. These signals are routed to the ST-BUS inputs and outputs on the top MT8980, which is used as a digital speech switch.

The MT8964 is controlled by the ST-BUS input  $D_c$  originating from the bottom MT8980, which generates the appropriate signals from an output channel in Message Mode. This architecture optimizes the messaging capability of the line circuit by building signalling logic, e.g., for on-off hook detection, which communicates on an ST-BUS output. This signalling ST-BUS output is monitored by a microprocessor (not shown) through an ST-BUS input on the bottom MT8980.

Fig. 8 shows how a simple digital switching system may be designed using the ST-BUS architecture. This is a private telephone network with 256 extensions which uses a single MT8980 as a speech switch and a second MT8980 for communication with the line interface circuits.

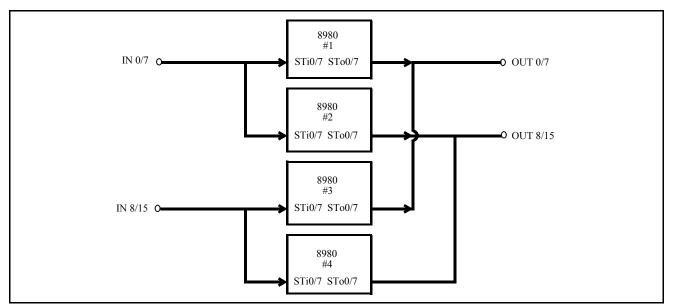

A larger digital switching system may be designed by cascading a number of MT8980s. Fig. 9 shows how four MT8980s may be arranged in a non-blocking configuration which can switch any channel on any of the ST-BUS inputs to any channel on the ST-BUS outputs.

Figure 7 - Example of Typical Interface between 8980s and 8964s for Simple Digital Switching System

Figure 8 - Example Architecture of a Simple Digital Switching System

Figure 9 - Four 8980s Arranged in a Non-Blocking 16 x 16 Configuration

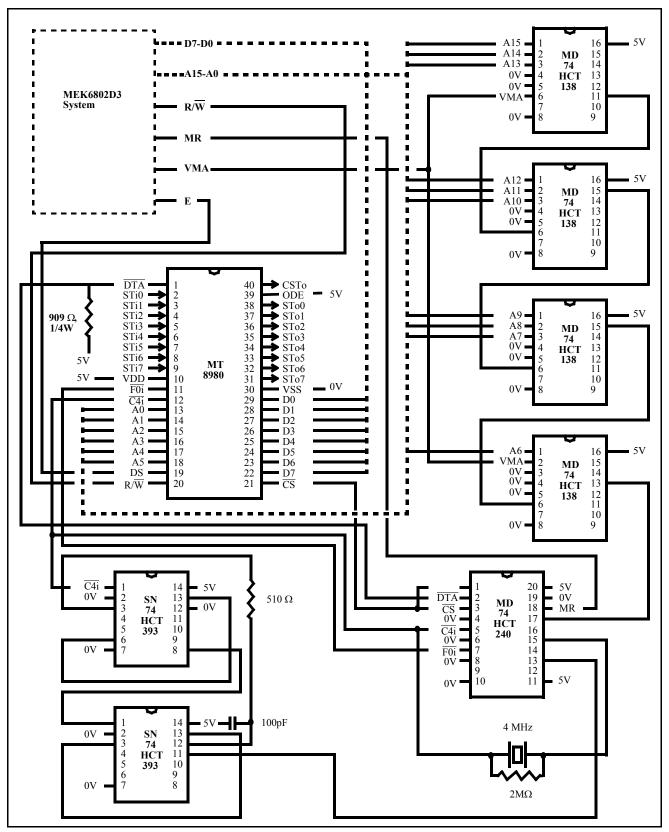

#### Application Circuit with 6802 Processor

Fig. 10 shows an example of a complete circuit which may be used to evaluate the chip.

For convenience, a 4 MHz crystal oscillator has been used rather than a 4.096 MHz clock, as both are within the limits of the chip's specifications. The RC delay used with the 393 counters ensures a sufficient hold time for the FP signal, but the values used may have to be changed if faster 393 counters become available.

The chip is shown as memory mapped into the MEK6802D3 system. Chip addresses 00-3F correspond to processor addresses 2000-203F. Delay through the address decoder requires the VMA signal to be used twice to remove glitches. The MEK6802D3 board uses a 10 K $\Omega$  pullup on the MR pin, which would have to be incorporated into the circuit if the board was replaced by a processor.

#### **Absolute Maximum Ratings\***

|   | Parameter                         | Symbol         | Min.                 | Max.          | Units |

|---|-----------------------------------|----------------|----------------------|---------------|-------|

| 1 | V <sub>DD</sub> - V <sub>SS</sub> |                | -0.3                 | 7             | V     |

| 2 | Voltage on Digital Inputs         | VI             | V <sub>ss</sub> -0.3 | $V_{DD}$ +0.3 | V     |

| 3 | Voltage on Digital Outputs        | Vo             | V <sub>ss</sub> -0.3 | $V_{DD}$ +0.3 | V     |

| 4 | Current at Digital Outputs        | Io             |                      | 40            | mA    |

| 5 | Storage Temperature               | Ts             | -65                  | +150          | °C    |

| 6 | Package Power Dissipation         | P <sub>D</sub> |                      | 2             | W     |

\* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

#### Recommended Operating Conditions - Voltages are with respect to ground (VSS) unless otherwise stated.

|   | Characteristics       | Sym.            | Min. | Typ.‡ | Max.            | Units | Test Conditions |

|---|-----------------------|-----------------|------|-------|-----------------|-------|-----------------|

| 1 | Operating Temperature | T <sub>OP</sub> | -40  |       | +85             | °C    |                 |

| 2 | Positive Supply       | V <sub>DD</sub> | 4.75 |       | 5.25            | V     |                 |

| 3 | Input Voltage         | VI              | 0    |       | V <sub>DD</sub> | V     |                 |

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

# DC Electrical Characteristics - Voltages are with respect to ground ( $V_{SS}$ ) unless otherwise stated.

|    |        | Characteristics        | Sym.            | Min. | Typ.‡ |     |    |                                                   |

|----|--------|------------------------|-----------------|------|-------|-----|----|---------------------------------------------------|

| 1  | T      | Supply Current         | I <sub>DD</sub> |      | 6     | 10  | mA | Outputs unloaded                                  |

| 2  | N      | Input High Voltage     | V <sub>IH</sub> | 2.0  |       |     | V  |                                                   |

| 3  | P<br>U | Input Low Voltage      | V <sub>IL</sub> |      |       | 0.8 | V  |                                                   |

| 4  | T      | Input Leakage          | I <sub>IL</sub> |      |       | 5   | μΑ | $V_{\rm I}$ between $V_{\rm SS}$ and $V_{\rm DD}$ |

| 5  | S      | Input Pin Capacitance  | CI              |      | 8     |     | pF |                                                   |

| 6  | 0      | Output High Voltage    | V <sub>OH</sub> | 2.4  |       |     | V  | $I_{OH} = 10 \text{ mA}$                          |

| 7  | O<br>U | Output High Current    | I <sub>OH</sub> | 10   | 15    |     | mA | Sourcing. V <sub>OH</sub> =2.4V                   |

| 8  | T<br>P | Output Low Voltage     | V <sub>OL</sub> |      |       | 0.4 | V  | $I_{OL} = 5 \text{ mA}$                           |

| 9  | P<br>U | Output Low Current     | I <sub>OL</sub> | 5    | 10    |     | mA | Sinking. $V_{OL} = 0.4V$                          |

| 10 | T<br>S | High Impedance Leakage | I <sub>OZ</sub> |      |       | 5   | μΑ | $V_{\rm O}$ between $V_{\rm SS}$ and $V_{\rm DD}$ |

| 11 | 3      | Output Pin Capacitance | Co              |      | 8     |     | pF |                                                   |

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

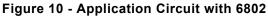

Figure 11 - Output Test Load

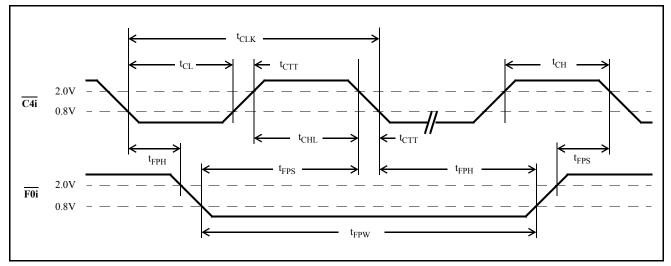

# AC Electrical Characteristics<sup>†</sup> - Clock Timing (Figures 12 and 13)

|       |          | Characteristics                                                                                                                                 | Sym.             | Min.  | Typ.‡ | Max. | Units | Test Conditions |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------|------|-------|-----------------|

| 1     |          | Clock Period*                                                                                                                                   | t <sub>CLK</sub> | 220   | 244   | 300  | ns    |                 |

| 2     | т        | Clock Width High                                                                                                                                | t <sub>CH</sub>  | 95    | 122   | 150  | ns    |                 |

| 3     | N        | Clock Width Low                                                                                                                                 | t <sub>CL</sub>  | 110   | 122   | 150  | ns    |                 |

| 4     | P<br>U   | Clock Transition Time                                                                                                                           | t <sub>CTT</sub> |       | 20    |      | ns    |                 |

| 5     | Т        | Frame Pulse SetupTime                                                                                                                           | t <sub>FPS</sub> | 20    |       | 200  | ns    |                 |

| 6     | S        | Frame Pulse Hold Time                                                                                                                           | t <sub>FPH</sub> | 0.020 |       | 50   | μs    |                 |

| 7     |          | Frame Pulse Width                                                                                                                               | t <sub>FPW</sub> |       | 244   |      | ns    |                 |

| ‡ Тур | ical fig | over recommended temperature & power suppl<br>gures are at 25°C and are for design aid only: n<br>f Connection Memory are not lost if the clock | ot guarantee     |       |       |      |       | ce state.       |

\* Contents of Connection Memory are not lost if the clock stops, however, ST-BUS outputs go into the high impedance state. **NB:** Frame Pulse is repeated every 512 cycles of  $\overline{C4i}$ .

#### Figure 12 - Frame Alignment

Figure 13 - Clock Timing

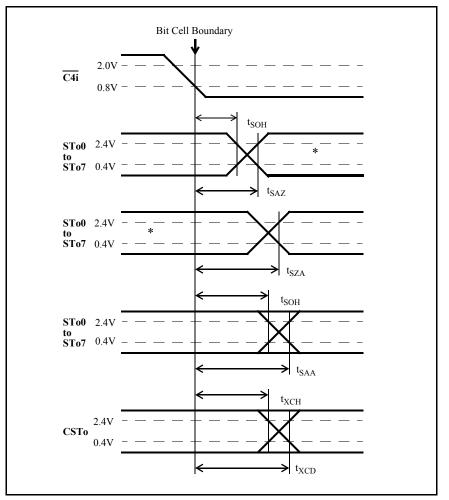

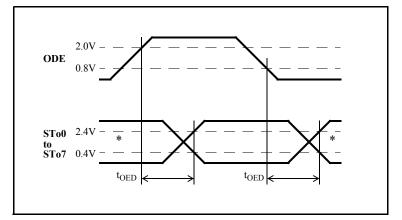

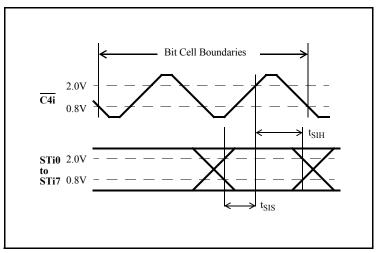

# AC Electrical Characteristics<sup>†</sup> - Serial Streams (Figures 11, 14, 15 and 16)

|   |        | Characteristics                 | Sym.             | Min. | Typ.‡ | Max. | Units | Test Conditions               |

|---|--------|---------------------------------|------------------|------|-------|------|-------|-------------------------------|

| 1 |        | STo0/7 Delay - Active to High Z | t <sub>SAZ</sub> | 20   | 50    | 80   | ns    | $R_L=1 K\Omega^*, C_L=150 pF$ |

| 2 | 0      | STo0/7 Delay - High Z to Active | t <sub>SZA</sub> | 25   | 60    | 125  | ns    | C <sub>L</sub> =150 pF        |

| 3 | U<br>T | STo0/7 Delay - Active to Active | t <sub>SAA</sub> | 30   | 65    | 125  | ns    | C <sub>L</sub> =150 pF        |

| 4 | Р      | STo0/7 Hold Time                | t <sub>SOH</sub> | 25   | 45    |      | ns    | C <sub>L</sub> =150 pF        |

| 5 | U<br>T | Output Driver Enable Delay      | t <sub>OED</sub> |      | 45    | 125  | ns    | $R_L=1 K\Omega^*, C_L=150 pF$ |

| 6 | S      | External Control Hold Time      | t <sub>XCH</sub> | 0    | 50    |      | ns    | C <sub>L</sub> =150 pF        |

| 7 |        | External Control Delay          | t <sub>XCD</sub> |      | 75    | 110  | ns    | C <sub>L</sub> =150 pF        |

| 8 | Ι      | Serial Input Setup Time         | t <sub>SIS</sub> |      | -40   | -20  | ns    |                               |

| 9 | Ν      | Serial Input Hold Time          | t <sub>SIH</sub> | 90   |       |      | ns    |                               |

† Timing is over recommended temperature & power supply voltages.

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

\* High Impedance is measured by pulling to the appropriate rail with R<sub>L</sub>, with timing corrected to cancel time taken to discharge C<sub>L</sub>.

Figure 14 - Serial Outputs and External Control

Figure 15 - Output Driver Enable

Figure 16 - Serial Inputs

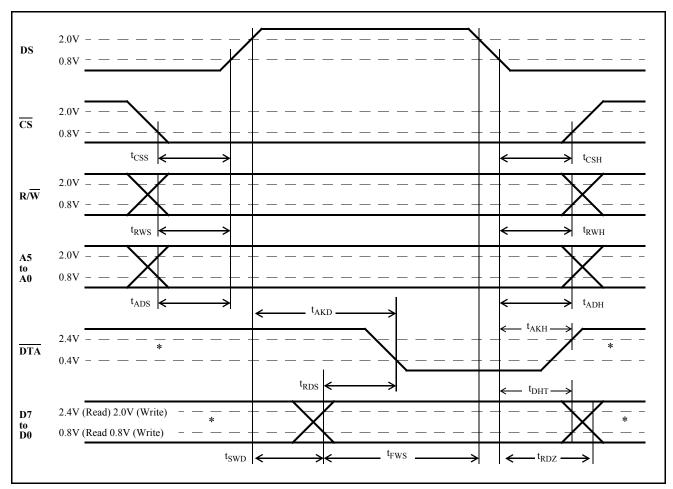

# AC Electrical Characteristics<sup>†</sup> - Processor Bus (Figures 11 and 17)

|    | Characteristics             | Sym.             | Min. | Typ.‡ | Max. | Units  | Test Conditions                                                |

|----|-----------------------------|------------------|------|-------|------|--------|----------------------------------------------------------------|

| 1  | Chip Select Setup Time      | t <sub>CSS</sub> | 20   | 0     |      | ns     |                                                                |

| 2  | Read/Write Setup Time       | t <sub>RWS</sub> | 25   | 5     |      | ns     |                                                                |

| 3  | Address Setup Time          | t <sub>ADS</sub> | 25   | 5     |      | ns     |                                                                |

| 4  | Acknowledgement Delay Fast  | t <sub>AKD</sub> |      | 40    | 100  | ns     | C <sub>L</sub> =150 pF                                         |

|    | Slow                        | t <sub>AKD</sub> | 2.7  |       | 7.2  | cycles | $\overline{C4i}$ cycles <sup>1</sup>                           |

| 5  | Fast Write Data Setup Time  | t <sub>FWS</sub> | 20   |       |      | ns     |                                                                |

| 6  | Slow Write Data Delay       | t <sub>SWD</sub> |      | 2.0   | 1.7  | cycles | $\overline{C4i}$ cycles <sup>1</sup>                           |

| 7  | Read Data Setup Time        | t <sub>RDS</sub> |      |       | 0.5  | cycles | $\overline{C4i}$ cycles <sup>1</sup> , C <sub>L</sub> = 150 pF |

| 8  | Data Hold Time Read         | t <sub>DHT</sub> | 20   |       |      | ns     | $R_{L}=1 \text{ K}\Omega^{*}, C_{L}=150 \text{ pF}$            |

|    | Write                       | t <sub>DHT</sub> | 20   | 10    |      | ns     |                                                                |

| 9  | Read Data To High Impedance | t <sub>RDZ</sub> |      | 50    | 90   | ns     | $R_L=1 \text{ K}\Omega^*, C_L=150 \text{ pF}$                  |

| 10 | Chip Select Hold Time       | t <sub>CSH</sub> | 0    |       |      | ns     |                                                                |

| 11 | Read/Write Hold Time        | t <sub>RWH</sub> | 0    |       |      | ns     |                                                                |

| 12 | Address Hold Time           | t <sub>ADH</sub> | 0    |       |      | ns     |                                                                |

| 13 | Acknowledgement Hold Time   | t <sub>AKH</sub> | 10   | 60    | 80   | ns     | $R_L=1 \text{ K}\Omega^*$ , $C_L=150 \text{ pF}$               |

\* Timing is over recommended temperature & power supply voltages.

\* Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

\* High Impedance is measured by pulling to the appropriate rail with P with time. \* High Impedance is measured by pulling to the appropriate rail with  $R_L$ , with timing corrected to cancel time taken to discharge  $C_L$ . 1. Processor accesses are dependent on the  $\overline{C4i}$  clock, and so some timings are expressed as multiples of the  $\overline{C4i}$  clock period.

Figure 17 - Processor Bus

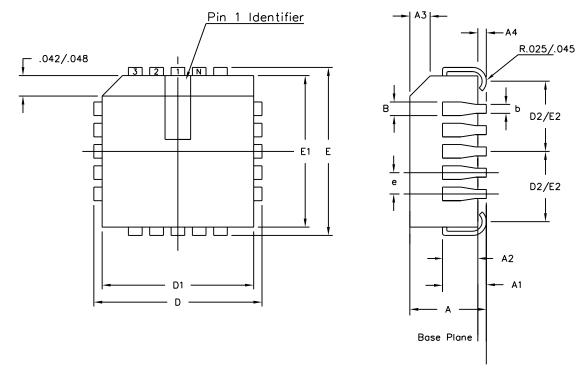

|        | Control Di | Altern. Di | mensions       |        |  |

|--------|------------|------------|----------------|--------|--|

| Symbol | in inc     | hes        | in millimetres |        |  |

|        | MIN        | MAX        | MIN            | MAX    |  |

| А      | 0.165      | 0.180      | 4.19           | 4.57   |  |

| A1     | 0.090      | 0.120      | 2.29           | 3.05   |  |

| A2     | 0.062      | 0.083      | 1.57           | 2.11   |  |

| Α3     | 0.042      | 0.056      | 1.07           | 1.42   |  |

| Α4     | 0.020      |            | 0.51           | -      |  |

| D      | 0.685      | 0.695      | 17.40          | 17.65  |  |

| D1     | 0.650      | 0.656      | 16.51          | 16.66  |  |

| D2     | 0.291      | 0.319      | 7.39           | 8.10   |  |

| Е      | 0.685      | 0.695      | 17.40          | 17.65  |  |

| E1     | 0.650      | 0.656      | 16.51          | 16.66  |  |

| E2     | 0.291      | 0.319      | 7.39           | 8.10   |  |

| В      | 0.026      | 0.032      | 0.66           | 0.81   |  |

| b      | 0.013      | 0.021      | 0.33           | 0.53   |  |

| е      | 0.050      | BSC        | 1.27           | BSC    |  |

|        |            | Pin fea    | otures         |        |  |

| ND     |            | 11         |                |        |  |

| NE     |            | 11         |                |        |  |

| Ν      |            | 44         | ł –            |        |  |

| Note   |            | Squo       | ore            |        |  |

| Confor | ms to J    | EDEC MS    |                | lss. A |  |

#### Notes:

Seating Plane

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982

- 2. Dimensions D1 and E1 do not include mould protrusions. Allowable mould protrusion is 0.010" per side. Dimensions D1 and E1 include mould protrusion mismatch and are determined at the parting line, that is D1 and E1 are measured at the extreme material condition at the upper or lower parting line.

- 3. Controlling dimensions in Inches.

- 4. "N" is the number of terminals.

- 5. Not To Scale

- 6. Dimension R required for 120° minimum bend.

| © Zarlink Semiconductor 2002 All rights reserved. |         |         |         |  |               |                        | Package Code QA     |

|---------------------------------------------------|---------|---------|---------|--|---------------|------------------------|---------------------|

| ISSUE                                             | 1       | 2       | 3       |  |               | Previous package codes | Package Outline for |

| ACN                                               | 5958    | 207470  | 213094  |  | SEMICONDUCTOR |                        | 44 lead PLCC        |

| DATE                                              | 15Aug94 | 10Sep99 | 15Jul02 |  |               | ,                      |                     |

| APPRD.                                            |         |         |         |  |               |                        | GPD00003            |

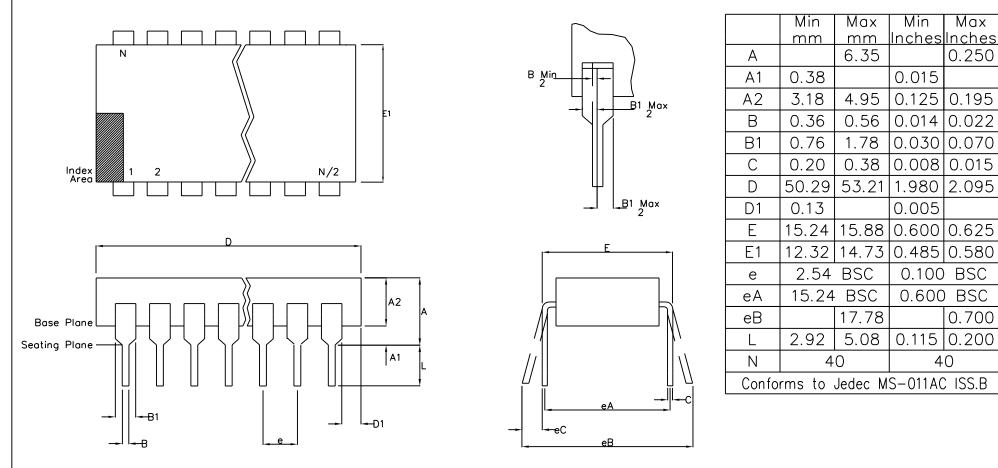

Notes:

- 1. Controlling Dimensions are in inches

- Controlling Dimensions are in increas

Dimension A, A1 and L are measured with the package seated in the Seating Plane

Dimensions D & E1 do not include mould flash or protrusions. Mould flash or protrusion shall not exceed 0.010 inch.

Dimensions E & eA are measured with leads constrained to be perpendicular to plane T.

- 5. Dimensions eB & eC are measured at the lead tips with the leads unconstrained; eC must be zero or greater.

| © Zarlink Semiconductor 2002 All rights reserved. |         |         |         |  |               |                        | Package Code DA                     |

|---------------------------------------------------|---------|---------|---------|--|---------------|------------------------|-------------------------------------|

| ISSUE                                             | 1       | 2       | 3       |  |               | Previous package codes | Backage Outline for                 |

| ACN                                               | 7010    | 203533  | 213103  |  | SEMICONDUCTOR |                        | Package Outline for<br>40 lead PDIP |

| DATE                                              | 20Apr95 | 25Nov97 | 15Jul02 |  |               |                        |                                     |

| APPRD.                                            |         |         |         |  |               |                        | GPD00073                            |

# For more information about all Zarlink products visit our Web Site at

## www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

«JONHON» (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«FORSTAR» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный) Факс: 8 (812) 320-03-32 Электронная почта: ocean@oceanchips.ru Web: http://oceanchips.ru/ Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А