### **General Description**

The MAX2769C is a next-generation Global Navigation Satellite System (GNSS) receiver covering L1/E1, B1, G1 bands for GPS, Galileo, BeiDou, and GLONASS satellite systems on a single chip. This single-conversion GNSS receiver is designed to provide high performance for industrial and wide range of consumer applications, including mobile handsets.

Designed on Maxim's advanced, low-power SiGe BiCMOS process technology, the MAX2769C offers the highest performance and integration at a low cost. Incorporated on the chip is the complete receiver chain, including a dual-input LNA and mixer, followed by the image-rejection filter, Programmable Gain Amplifier (PGA) and a multibit ADC. The total cascaded noise figure of this receiver is as low as 1.4dB. In addition, the device includes an integrated VCO, a crystal oscillator, a fractional-N frequency synthesizer to program the LO frequency using different reference frequencies.

The MAX2769C has the option to select one of the two LNAs for seperate Active and Passive Antenna inputs. LNA1 can be used with Passive Antenna input and LNA2 can be used for Active antenna input. Also, the MAX2769C completely eliminates the need for external IF filters by implementing on-chip monolithic filters and requires only a few external components to form a complete low-cost GPS RF receiver solution. Moreover, the device has the flexibility to configure the IF filter for various center frequencies and bandwidths using the SPI Interface.

The device is the most flexible receiver on the market. The integrated delta-sigma fractional-N frequency synthesizer allows programming of the IF frequency within a  $\pm 30$ Hz (When f<sub>XTAL</sub>  $\leq 32$ MHz) accuracy while operating with any reference or crystal frequencies that are available in the host system.

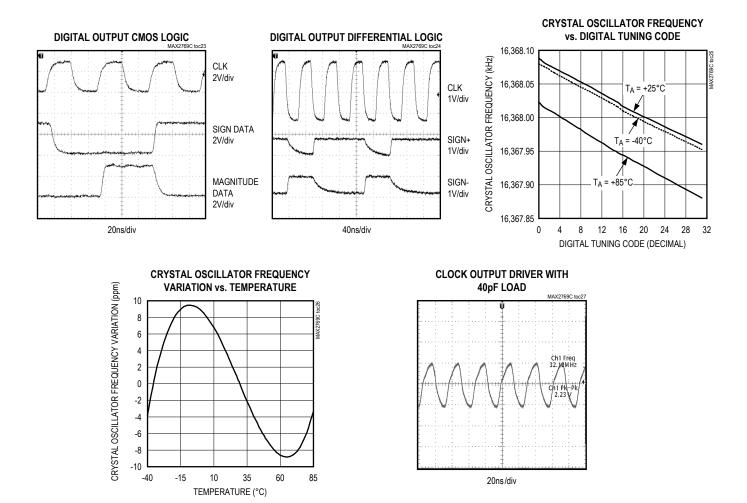

The ADC outputs CMOS logic levels with 1 or 2 quantized bits for both I and Q channels, or up to 3 quantized bits for the I channel. I and Q analog outputs are also available which will bypass the on-chip ADCs.

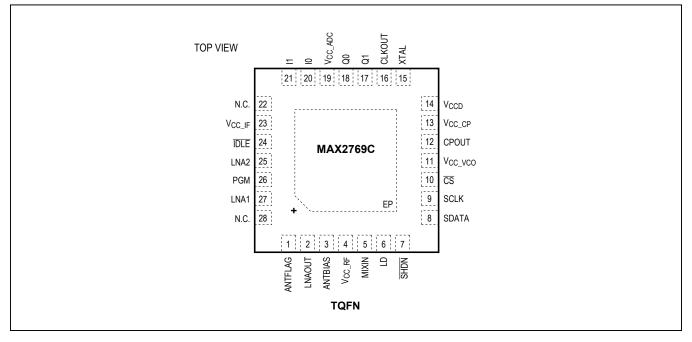

The MAX2769C is packaged in a 5mm x 5mm, 28-pin thin QFN package with an exposed paddle.

Ordering Information appears at end of data sheet.

# Universal GNSS Receiver

#### **Benefits and Features**

- GPS/GLONASS/Galileo/BeiDou Systems

- Dual-Input Selectable LNA for Separate Passive and Active Antenna Inputs

- 1.4dB Cascaded Noise Figure and 110dB of Cascaded Gain with Gain Control Range of 59dB From PGA

- Integrated Active Antenna Sensor

- Fractional-N Synthesizer with Integrated VCO

- No External IF SAW or Discrete Filters Required

- Programmable IF Frequency

- Programmable 2.5MHz, 4.2MHz, 9.66MHz IF Bandwidth and 9MHz ZIF LPF BW

- 8 Preconfigured Device States When No SPI Available

- 40pF Output Clock Drive Capability

- 28-Pin Thin QFN Package (5mm x 5mm)

- Available in AEC-Q100 Automotive-Qualified Version (MAX2769B)

### **Applications**

- Navigation Systems, Marine/Avionics Navigation

- Location-Enabled Mobile Handsets

- PNDs (Personal Navigation Devices)

- Telematics (Asset Tracking, Inventory Management)

- Software GPS

- Laptops and Netbooks

- In-Vehicle Navigation Systems

- Digital Still Cameras and Camcorders

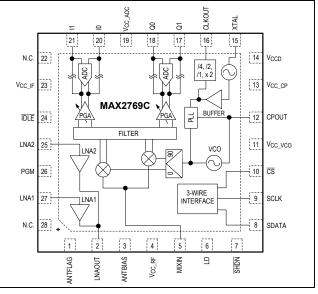

#### **Block Diagram**

# Universal GNSS Receiver

### **Absolute Maximum Ratings**

| V <sub>CC</sub> to Ground0.3V to +4.2V                |  |  |  |  |

|-------------------------------------------------------|--|--|--|--|

| Other Pins Except LNA_, MIXIN, XTAL, and LNAOUT to    |  |  |  |  |

| Ground0.3V to +(Operating V <sub>CC</sub> + 0.3V)     |  |  |  |  |

| Maximum RF Input Power+15dBm                          |  |  |  |  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |  |  |  |  |

| TQFN (derates 27mW/°C above +70°C)2500mW              |  |  |  |  |

| Operating Temperature Range       | 40°C to +85°C   |

|-----------------------------------|-----------------|

| Junction Temperature              | +150°C          |

| Storage Temperature Range         | -65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C          |

| Soldering Temperature (reflow)    | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

CAUTION! ESD SENSITIVE DEVICE

### **DC Electrical Characteristics**

(MAX2769C EV kit, V<sub>CC</sub> = 2.7V to 3.3V, T<sub>A</sub> = -40°C to +85°C, PGM = Ground. Registers are set to the default power-up states. Typical values are at V<sub>CC</sub> = 2.85V and T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                   | CONDITIONS                                                         | MIN | TYP  | MAX  | UNITS |

|---------------------------------------------|--------------------------------------------------------------------|-----|------|------|-------|

| Supply Voltage                              |                                                                    | 2.7 | 2.85 | 3.3  | V     |

|                                             | Default mode, LNA1 is active (Note 2)                              | 18  | 27   | 31   |       |

| Supply Current                              | Default mode, LNA2 is active (Note 2)                              | 15  | 25   | 30.5 | mA    |

| Supply Current                              | Idle ModeK, IDLE = low, SHDN = high                                |     | 5    |      |       |

|                                             | Shutdown mode, SHDN = low                                          |     | 200  |      | μA    |

| Voltage Drop at ANTBIAS from<br>VCC_RF      | Sourcing 20mA at ANTBIAS                                           |     | 0.2  |      | V     |

| Short-Circuit Protection Current at ANTBIAS | ANTBIAS is shorted to ground                                       |     | 57   |      | mA    |

| Active Antenna Detection Current            | tive Antenna Detection Current To assert logic-high at ANTFLAG 1.1 |     | mA   |      |       |

| DIGITAL INPUT AND OUTPUT                    |                                                                    |     |      |      | •     |

| Digital Input Logic-High                    | Measure at the SHDN pin                                            | 1.5 |      |      | V     |

| Digital Input Logic-Low                     | Measure at the SHDN pin                                            |     |      | 0.4  | V     |

Idle Mode is a trademark of Maxim Integrated Products, Inc.

### **AC Electrical Characteristics**

| PARAMETER                                             | CONDITIONS                                                       | MIN           | TYP     | MAX | UNITS |  |

|-------------------------------------------------------|------------------------------------------------------------------|---------------|---------|-----|-------|--|

| CASCADED RF PERFORMANCE                               |                                                                  | 1             |         |     | ,     |  |

| RF Frequency                                          | L1 band                                                          |               | 1575.42 |     | MHz   |  |

|                                                       | LNA1 input active, default mode (Note 3)                         | 1.4           |         |     |       |  |

| Noise Figure                                          | LNA2 input active, default mode (Note 3)                         |               | 2.7     |     | dB    |  |

|                                                       | Measured at the mixer input                                      |               | 10.3    |     | -     |  |

| Out-of-Band 3rd-Order Input<br>Intercept Point        | Measured at the mixer input (Note 4)                             |               | -7      |     | dBm   |  |

| In-Band Mixer Input Referred 1dB<br>Compression Point | Measured at the mixer input                                      |               | -85     |     | dBm   |  |

| Mixer Input Return Loss                               |                                                                  |               | 10      |     | dB    |  |

| Image Rejection                                       |                                                                  |               | 25      |     | dB    |  |

| Onum of LNA4 lanut                                    | LO leakage                                                       |               | -101    |     | - D   |  |

| Spurs at LNA1 Input                                   | Reference harmonics leakage                                      |               | -103    |     | dBm   |  |

| Maximum Voltage Gain                                  | Measured from the mixer to the baseband analog output            | 91            | 96      | 103 | dB    |  |

| Variable Gain Range                                   |                                                                  | 55            | 59      |     | dB    |  |

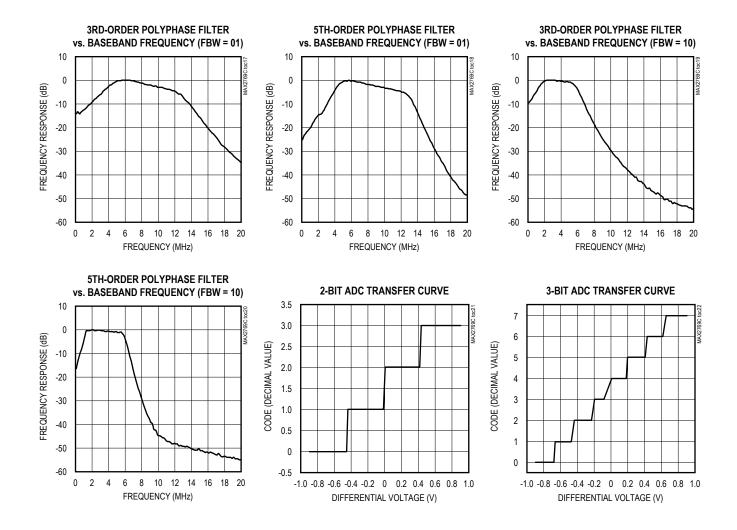

| FILTER RESPONSE                                       |                                                                  |               |         |     |       |  |

|                                                       | FCEN = 001101, FBW = 00                                          |               | 3.9     |     |       |  |

| Passband Center Frequency                             | FCEN = 001101, FBW = 10                                          |               | 7.1     |     | MHz   |  |

|                                                       | FCEN = 111101, FBW = 01                                          |               | 10.7    |     |       |  |

|                                                       | FBW = 00                                                         |               | 2.5     |     |       |  |

| Passband 3dB Bandwidth                                | FBW = 10                                                         |               | 4.2     |     | MHz   |  |

|                                                       | FBW = 01                                                         |               | 9.66    |     |       |  |

| Lowpass 3dB Bandwidth                                 | FBW = 11                                                         |               | 9       |     | MHz   |  |

| Charlend Attornation                                  | 3rd-order filter, bandwidth = 2.5MHz,<br>measured at 4MHz offset | 30<br>40 49.5 |         |     | 40    |  |

| Stopband Attenuation                                  | 5th-order filter, bandwidth = 2.5MHz,<br>measured at 4MHz offset |               |         | dB  |       |  |

| LNA                                                   |                                                                  |               |         |     |       |  |

| LNA1 INPUT                                            |                                                                  |               |         |     |       |  |

| Power Gain                                            |                                                                  |               | 19      |     | dB    |  |

| Noise Figure                                          |                                                                  |               | 0.83    |     | dB    |  |

| Input IP3                                             | (Note 5)                                                         |               | -1.1    |     | dBm   |  |

| Output Return Loss                                    |                                                                  |               | 10      |     | dB    |  |

| Intput Return Loss                                    |                                                                  |               | 8       |     | dB    |  |

### **AC Electrical Characteristics (continued)**

$(MAX2769C EV kit, V_{CC} = 2.7V to 3.3V, T_A = -40^{\circ}C to +85^{\circ}C, PGM = Ground. Registers are set to the default power-up states. LNA input is driven from a 50<math>\overline{\Omega}$  source. All RF measurements are done in the analog output mode with ADC bypassed. PGA gain is set to 51dB gain by serial-interface word GAININ = 111010. Maximum IF output load is not to exceed 10k $\Omega$ ||7.5pF on each pin. Typical values are at V<sub>CC</sub> = 2.85V and T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                  | CONDITIONS                                                  | MIN  | TYP    | MAX    | UNITS            |  |

|--------------------------------------------|-------------------------------------------------------------|------|--------|--------|------------------|--|

| LNA2 INPUT                                 | ·                                                           |      |        |        |                  |  |

| Power Gain                                 |                                                             |      | 13     |        | dB               |  |

| Noise Figure                               |                                                             |      | 1.14   |        | dB               |  |

| Input IP3                                  | (Note 5)                                                    |      | 1      |        | dBm              |  |

| Output Return Loss                         |                                                             |      | 19     |        | dB               |  |

| Input Return Loss                          |                                                             |      | 11     |        | dB               |  |

| FREQUENCY SYNTHESIZER                      |                                                             |      |        |        |                  |  |

| LO Frequency Range                         | 0.2V < V <sub>TUNE</sub> < (V <sub>CC</sub> - 0.3V)         | 1550 |        | 1610   | MHz              |  |

| LO Tuning Gain                             |                                                             |      | 57     |        | MHz/V            |  |

| Reference Input Frequency                  |                                                             | 8    |        | 32     | MHz              |  |

| Main Divider Ratio                         |                                                             | 36   |        | 32,767 | _                |  |

| Reference Divider Ratio                    |                                                             | 1    |        | 1023   | —                |  |

| Charge-Pump Current                        | ICP = 0                                                     |      | 0.5    |        |                  |  |

| Charge-Fump Current                        | ICP = 1                                                     |      | 1      |        | – mA             |  |

| TCXO INPUT BUFFER/OUTPUT                   | CLOCK BUFFER                                                |      |        |        |                  |  |

| Frequency Range                            |                                                             | 8    |        | 32     | MHz              |  |

| Output Logic-Level High (V <sub>OH</sub> ) | With respect to ground, I <sub>OH</sub> = 10µA (DC-coupled) | 2    |        |        | V                |  |

| Output Logic-Level Low (V <sub>OL</sub> )  | With respect to ground, $I_{OL}$ = 10µA (DC-coupled)        |      |        | 0.8    | V                |  |

| Capacitive Slew Current                    | Load = $10k\Omega + 40pF$ , f <sub>CLKOUT</sub> = $32MHz$   |      | 11     |        | mA               |  |

| Output Load                                |                                                             |      | 10  40 |        | kΩ  pF           |  |

| Reference Input Level                      | Sine wave                                                   | 0.5  |        |        | V <sub>P-P</sub> |  |

| Clock Output Multiply/Divide<br>Range      | /4, /2, /1<br>(x2, max input frequency of 16MHz)            | ÷4   |        | x2     |                  |  |

| ADC                                        | · ·                                                         |      |        |        |                  |  |

| ADC Differential Nonlinearity              | AGC enabled, 3-bit output                                   |      | ±0.1   |        | LSB              |  |

| ADC Integral Nonlinearity                  | AGC enabled, 3-bit output                                   |      | ±0.1   |        | LSB              |  |

Note 1: MAX2769C is production tested at T<sub>A</sub> = +25°C and +85°C. All min/max specifications are guaranteed by design and characterization from -40°C to +85°C, unless otherwise noted. Default register settings are not production tested or guaranteed. User must program the registers upon power-up.

- Note 2: Default, low-NF mode of the IC. LNA choice is gated by the ANT\_FLAG signal. In the normal mode of operation without an active antenna, LNA1 is active. If an active antenna is connected and ANT\_FLAG switches to 1, LNA1 is automatically disabled and LNA2 becomes active. PLL is in an integer-N mode with f<sub>COMP</sub> = f<sub>TCXO</sub>/16 = 1.023MHz and ICP = 0.5mA. The IF filter is configured as a 5th-order Butterworth filter with a center frequency of 4MHz and bandwidth of 2.5MHz. Output data is in a 2-bit sign/magnitude format at CMOS logic levels in the I channel only.

- Note 3: The LNA output connects to the mixer input without a SAW filter between them.

- Note 4: Two tones are located at 12MHz and 24MHz offset frequencies from the GPS center frequency of 1575.42MHz at -60dBm/ tone. Passive pole at the mixer output is programmed to be 13MHz.

- Note 5: Measured from the LNA input to the LNA output. Two tones are located at 12MHz and 24MHz offset frequencies from the GPS center frequency of 1575.42MHz at -60dBm per tone.

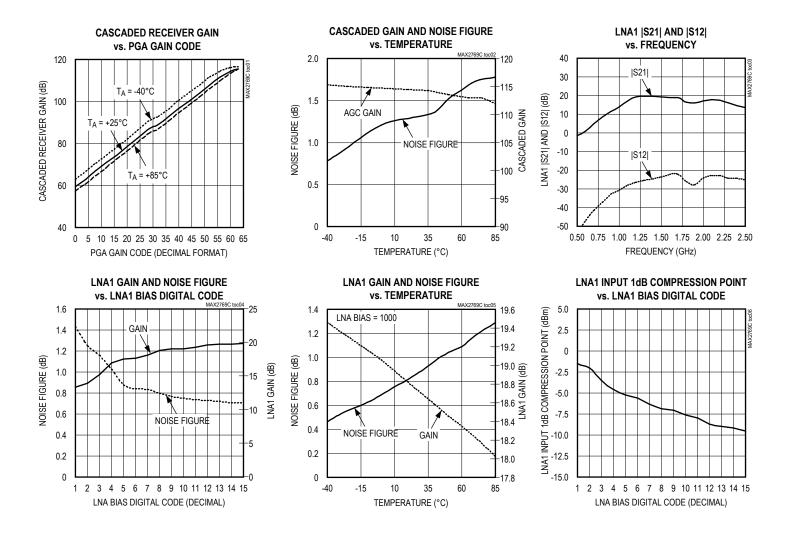

### **Typical Operating Characteristics**

### **Typical Operating Characteristics (continued)**

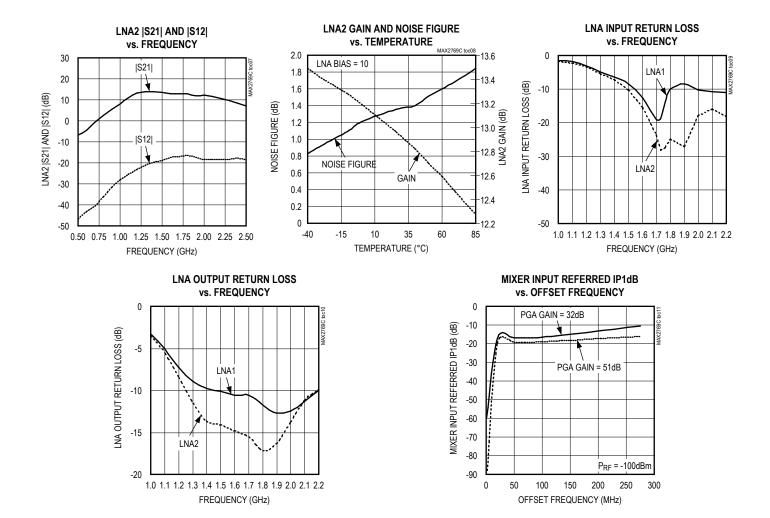

## Universal GNSS Receiver

### **Typical Operating Characteristics (continued)**

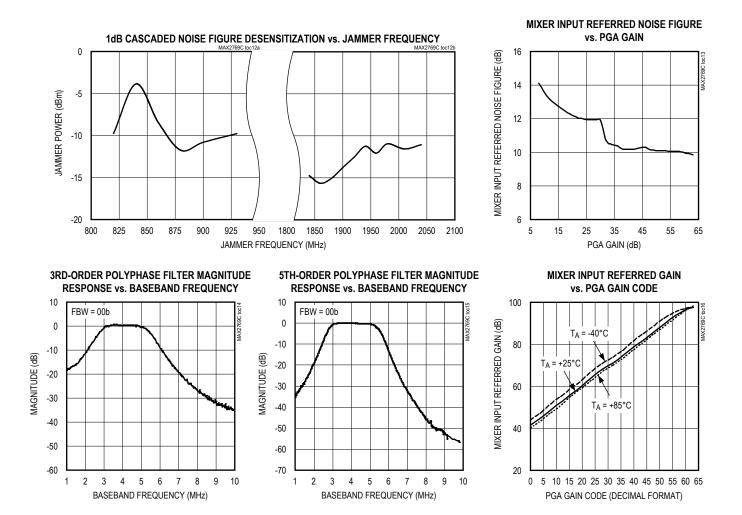

## Universal GNSS Receiver

### **Typical Operating Characteristics (continued)**

## Universal GNSS Receiver

### **Typical Operating Characteristics (continued)**

# Universal GNSS Receiver

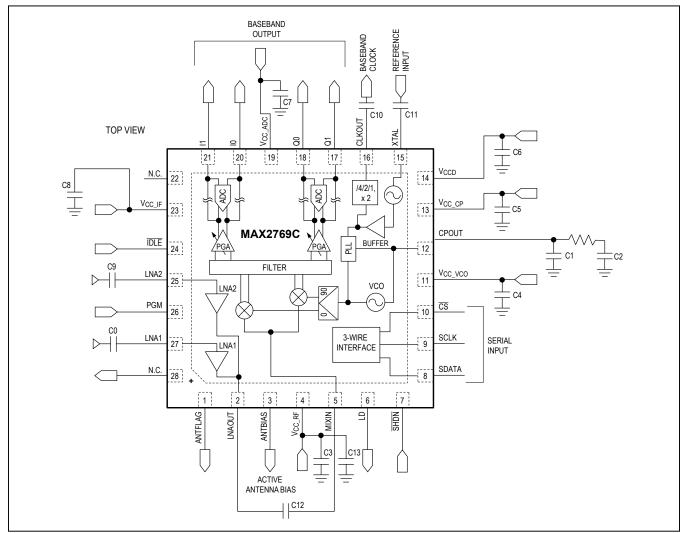

# **Typical Application Circuit**

## Table 1. Component List

| DESIGNATION | QUANTITY | DESCRIPTION                           |  |

|-------------|----------|---------------------------------------|--|

| C0, C9      | 2        | 0.47nF AC-coupling capacitors         |  |

| C1          | 1        | 27pF PLL loop filter capacitor        |  |

| C2          | 1        | 0.47nF PLL loop filter capacitor      |  |

| C3–C8       | 6        | 0.1µF supply voltage bypass capacitor |  |

| C10, C11    | 2        | 10nF AC-coupling capacitor            |  |

| C12         | 1        | 0.47nF AC-coupling capacitor          |  |

| C13         | 1        | 0.1nF supply voltage bypass capacitor |  |

| R1          | 1        | 20kΩ PLL loop filter resistor         |  |

# Universal GNSS Receiver

# **Pin Configuration**

# **Pin Description**

| PIN | NAME               | FUNCTION                                                                                                                               |  |  |  |

|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | ANTFLAG            | Active Antenna Flag Logic Output. A logic-high indicates that an active antenna is connected to the ANTBIAS pin.                       |  |  |  |

| 2   | LNAOUT             | LNA Output. The LNA output is internally matched to 50Ω.                                                                               |  |  |  |

| 3   | ANTBIAS            | Buffered Supply Voltage Output. Provides a supply voltage bias for an external active antenna.                                         |  |  |  |

| 4   | V <sub>CC_RF</sub> | RF Section Supply Voltage. Bypass to ground with 100nF and 100pF capacitors in parallel as close as possible to the pin.               |  |  |  |

| 5   | MIXIN              | Mixer Input. The mixer input is internally matched to 50Ω.                                                                             |  |  |  |

| 6   | LD                 | Lock-Detector CMOS Logic Output. A logic-high indicates the PLL is locked.                                                             |  |  |  |

| 7   | SHDN               | Operation Control Logic Input. A logic-low shuts off the entire device.                                                                |  |  |  |

| 8   | SDATA              | Data Digital Input of 3-Wire Serial Interface                                                                                          |  |  |  |

| 9   | SCLK               | Clock Digital Input of 3-Wire Serial Interface. Active when $\overline{CS}$ is low. Data is clocked in on the rising edge of the SCLK. |  |  |  |

# **Pin Description (continued)**

| PIN | NAME                | FUNCTION                                                                                                                                                                                                                 |  |

|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10  | CS                  | Chip-Select Logic Input of 3-Wire Serial Interface. Set $\overline{CS}$ low to allow serial data to shift in. Set $\overline{CS}$ high when the loading action is completed.                                             |  |

| 11  | V <sub>CC_VCO</sub> | VCO Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin.                                                                                                                             |  |

| 12  | CPOUT               | Charge-Pump Output. Connect a PLL loop filter as a shunt C and a shunt combination of series R and C (see the <i>Typical Application Circuit</i> ).                                                                      |  |

| 13  | V <sub>CC_CP</sub>  | PLL Charge-Pump Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin.                                                                                                                 |  |

| 14  | V <sub>CCD</sub>    | Digital Circuitry Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin.                                                                                                               |  |

| 15  | XTAL                | XTAL or Reference Oscillator Input. Connect to XTAL or a DC-blocking capacitor if TCXO is used.                                                                                                                          |  |

| 16  | CLKOUT              | Reference Clock Output                                                                                                                                                                                                   |  |

| 17  | Q1                  | Q-Channel Voltage Outputs. Bits 0 and 1 of the Q-channel ADC output or analog differential voltage                                                                                                                       |  |

| 18  | Q0                  | output.                                                                                                                                                                                                                  |  |

| 19  | V <sub>CC_ADC</sub> | ADC Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin.                                                                                                                             |  |

| 20  | 10                  | I-Channel Voltage Outputs. Bits 0 and 1 of the I-channel ADC output or analog differential voltage                                                                                                                       |  |

| 21  | 1                   | output.                                                                                                                                                                                                                  |  |

| 22  | N.C.                | No Connection. Leave this pin unconnected.                                                                                                                                                                               |  |

| 23  | V <sub>CC_IF</sub>  | IF Section Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin.                                                                                                                      |  |

| 24  | IDLE                | Operation Control Logic Input. A logic-low enables the idle mode, in which the XTAL oscillator is active, and all other blocks are off.                                                                                  |  |

| 25  | LNA2                | LNA Input Port 2. This port is typically used with an active antenna. Internally matched to $50\Omega$ .                                                                                                                 |  |

| 26  | PGM                 | Logic Input. Connect to ground to use the serial interface. A logic-high allows programming to 8 hard-<br>coded by device states connecting SDATA, $\overline{CS}$ , and SCLK to supply or ground according to Table 19. |  |

| 27  | LNA1                | LNA Input Port 1. This port is typically used with a passive antenna. Internally matched to $50\Omega$ (see the <i>Typical Application Circuit</i> ).                                                                    |  |

| 28  | N.C.                | No Connect.                                                                                                                                                                                                              |  |

| _   | EP                  | Exposed Pad. Ultra-low-inductance connection to ground. Place several vias to the PCB ground plane.                                                                                                                      |  |

### **Detailed Description**

#### **Integrated Active Antenna Sensor**

MAX2769C can be used either with an active antenna or a Passive antenna. Using the Active Antenna sensor feature, the antenna (either Active/ Passive) can be selcted automatically depending on the current drawn at ANTBIAS pin which enables to have a single design in both Active/Passive antenna applications. If automatic LNA selection is not desired, it can be disabled through the Config1 register <14:13>. The MAX2769C includes a low-dropout switch to bias an external active antenna. To activate the antenna switch output, set ANTEN in the Configuration 1 register to logic 1. This closes the switch that connects the antenna bias pin to  $V_{CC}$  RF to achieve a low 200mV dropout for a 20mA load current. A logic-low in ANTEN disables the antenna bias. The active antenna circuit also features short-circuit protection to prevent the output from being shorted to ground. See Table 2.

### Low-Noise Amplifier (LNA)

The MAX2769C integrates two low-noise amplifiers. LNA1 is typically used with a passive antenna and requires an AC-coupling capacitor. In the default mode, the bias current is set to 4mA, the typical Gain, noise figure and IIP3 are approximately 19dB, 0.8dB and -1.1dBm, respectively. LNA2 is typically used with an active antenna. The LNA2 is internally matched to 50 and requires a DC-blocking capacitor. The typical Gain, Noise Figure and IIP3 are approximately 13dB, 1.14dB and 1dBm, respectively.

### Table 2. Antenna Enable

| ANTEN<br>(CONFIGURATION 1 REGISTER) | ANTENNA BIAS |

|-------------------------------------|--------------|

| 0                                   | OFF          |

| 1                                   | ON           |

### Table 3. LNA Specifications

| PARAMETER    | LNA1 (PASSIVE<br>ANTENNA) | LNA2 (ACTIVE<br>ANTENNA) |

|--------------|---------------------------|--------------------------|

| Gain         | 19 dB                     | 13 dB                    |

| Noise Figure | 0.8 dB                    | 1.14 dB                  |

| IIP3         | -1.1dBm                   | 1.0 dBm                  |

See <u>Table 3</u>. Bits LNAMODE in the Configuration 1 register control the modes of the two LNAs. See Table 4.

#### Mixer

The MAX2769C includes a quadrature mixer to output low-IF or zero IF I and Q signals. The quadrature mixer is internally matched to  $50\Omega$  and requires a low-side LO injection. The output of the LNA and the input of the mixer are brought off-chip to facilitate the use of a SAW filter.

On MAX2769C, the RF signal has been made accessible between the first LNA stage output and mixer input (pins 2 and 5 respectively). If filtering is not desired, these pins can be connected through a coupling capacitor. However, filtering introduced at this point has minimal effect on the excellent sensitivity of the receiver. For example, for typical device parameters, a SAW filter with 1dB insertion loss would degrade cascaded NF (and thus GPS sensitivity) by only about 0.15dB.

While no external filtering is required for stand-alone applications, coexistence with cellular or WiLAN transmissions in close proximity may require additional filtering to prevent overdriving the GPS receiver front-end.

### IF Filter

The IF filter of the receiver can be programmed to be a lowpass filter or a bandpass filter by setting the bit FCENX either 0 for Low pass filter mode or 1 for Band pass filter mode. See <u>Table 5</u>.

### Table 4. LNA Selection

| LNAMODE<br>(CONFIGURATION 1<br>REGISTER) | MODE                                               |

|------------------------------------------|----------------------------------------------------|

| 00                                       | LNA selection gated by the<br>antenna bias circuit |

| 01                                       | LNA2 is active                                     |

| 10                                       | LNA1 is active                                     |

| 11                                       | Both LNA1 and LNA2 are off                         |

### Table 5. IF Filter Mode Selection

| FCENX<br>(CONFIGURATION 1 REGISTER) | FILTER MODE |

|-------------------------------------|-------------|

| 0                                   | Low Pass    |

| 1                                   | Band Pass   |

Also, the IF filter can be configured either as a 3rd-order Butterworth filter for a reduced group delay or a 5th-order Butterworth filter for a steeper out-of-band rejection by setting the bit F3OR5 either 1 or 0, respectively in the Configuration 1 register. See <u>Table 6</u>.

The two-sided 3dB corner bandwidth can be selected to be 2.5 MHz, 4.2 MHz, 9.66 MHz by programming bits FBW in the Configuration 1 register. See Table 7.

When the filter is enabled by changing bit FCENX in the Configuration 1 register to 1, the lowpass filter becomes a bandpass filter and the center frequency can be programmed by bits FCEN and FCENMSB in the Configuration 1 register. See Table 8.

The IF center frequency is adjustable in 127 steps with a 7 bit FCEN word with 6bit FCEN and 1bit FCENMSB.

Refer Applications section of this document to configure the desired IF filter center frequency

### Table 6. IF Filter Order Selection

| F3OR5<br>(CONFIGURATION 1 REGISTER) | IF FILTER ORDER          |

|-------------------------------------|--------------------------|

| 0                                   | 5th order<br>Butterworth |

| 1                                   | 3rd order<br>Butterworth |

### Table 7. IF Filter BW Selection

| FBW<br>(CONFIGURATION 1 REGISTER) | BANDWIDTH<br>(MHz) |

|-----------------------------------|--------------------|

| 00                                | 2.5                |

| 10                                | 4.2                |

| 01                                | 9.66               |

| 11 (Low-Pass Mode)                | 9 (Single-Sided)   |

### Table 8. IF Filter Center Frequency

| FBW<br>(CONFIG 1<br>REGISTER) | FCEN (CONFIG<br>1 REGISTER) | IF CENTER<br>FREQUENCY<br>(MHZ) |

|-------------------------------|-----------------------------|---------------------------------|

| 00                            | 001101                      | 3.9                             |

| 10                            | 001101                      | 7.1                             |

| 01                            | 111101                      | 10.7                            |

#### Programmable Gain Amplifier (PGA)

The MAX2769C integrates a baseband programmable gain amplifier that provides 59dB of gain control range. The PGA gain can be programmed through the serial interface by setting bits GAININ in the Configuration 3 register. Set bits 12 and 11 (AGCMODE) in the Configuration 2 register to 10 to control the gain of the PGA directly from the 3-wire interface. See Table 9.

#### Automatic Gain Control (AGC)

The MAX2769C provides a control loop that automatically programs PGA gain to provide the ADC with an input power that optimally fills the converter and establishes a desired magnitude bit density at its output. An algorithm operates by counting the number of magnitude bits over 512 ADC clock cycles and comparing the magnitude bit count to the reference value provided through a control word (GAINREF) using Configuration 2 register.

The desired magnitude bit density is expressed as a value of GAINREF in a decimal format divided by the counter length of 512. For example, to achieve the magnitude bit density of 33%, which is optimal for a 2-bit converter, program the GAINREF to 170, so that 170/512 = 33%. See Table 10.

### **Table 9. PGA Gain Settings**

| GAININ<br>(CONFIGURATION 3 REGISTER) | GAIN<br>(dB) |

|--------------------------------------|--------------|

| 000000                               | 0            |

| 101011                               | 42           |

| 101100                               | 43           |

| 101110                               | 45           |

| 111010                               | 57           |

| 111111                               | 62           |

### Table 10. Gain Ref Settings

| GAINREF<br>(CONFIGURATION 2 REGISTER) | MAGNITUDE BIT<br>DENSITY<br>REFERENCE |

|---------------------------------------|---------------------------------------|

| 10101010                              | 170                                   |

| 1010100                               | 84                                    |

| 100111010                             | 314                                   |

#### Synthesizer

The MAX2769C integrates a 20-bit sigma-delta fractional-N synthesizer allowing the device to tune to a required VCO frequency with an accuracy of approximately Q30Hz. The synthesizer includes a 10-bit reference divider with a divisor range programmable from 1 to 1023, a 15-bit integer portion main divider with a divisor range programmable from 36 to 32767, and also a 20-bit fractional portion main divider. The reference divider is programmable by bits RDIV in the PLL integer division ratio register, and can accommodate reference frequencies from 8MHz to 32MHz. The reference divider needs to be set so the comparison frequency falls between 0.05MHz to 32MHz.

The PLL loop filter is the only external block of the synthesizer. A typical PLL filter is a classic C-R-C network at the charge-pump output. The charge-pump output sink and source current is 0.5mA by default, and the LO tuning gain is 57MHz/V. As an example, see the <u>Typical Application</u> <u>Circuit</u> for the recommended loopfilter component values for f<sub>COMP</sub> = 1.023MHz and loop bandwidth = 50kHz.

To calculate the loop filter component values for different LO frequencies, please refer to the Design Resources section of the product page.

The desired integer and fractional divider ratios can be calculated by dividing the LO frequency ( $f_{LO}$ ) by  $f_{COMP}$ .  $f_{COMP}$  can be calculated by dividing the TCXO frequency ( $f_{TCXO}$ ) by the reference division ratio (RDIV). For example, let the TCXO frequency be 20MHz, RDIV be 1, and the nominal LO frequency be 1575.42MHz. The following method can be used when calculating divider ratios supporting various reference and comparison frequencies:

Comparison Frequency =  $\frac{f_{TCXO}}{RDIV} = \frac{20MHz}{1} = 20MHz$ LO Frequency Divider =  $\frac{f_{LO}}{f_{COMP}} = \frac{1575.42MHz}{20MHz} = 78.771$

Integer Divider = 78(d) = 000 0000 0100 1110 (binary)

Fractional Divider = 0.771 x 2<sup>20</sup> = 808452 (decimal) = 1100 0101 0110 0000 0100

In the fractional mode, the synthesizer should not be operated with integer division ratios greater than 251.

#### **Crystal Oscillator**

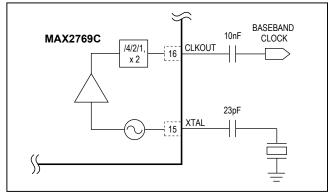

The MAX2769C includes an on-chip crystal oscillator. A parallel mode crystal is required when the crystal oscillator is being used. It is recommended that an AC-coupling capacitor be used in series with the crystal and the

XTAL pin to optimize the desired load capacitance and to center the crystal-oscillator frequency. Take the parasitic loss of interconnect traces on the PCB into account when optimizing the load capacitance. For example, the MAX2769C EV kit utilizes a 16.368MHz crystal designed for a 12pF load capacitance. A series capacitor of 23pF is used to center the crystal oscillator frequency, see Figure 1. In addition, the 5-bit serial-interface word, XTALCAP in the PLL Configuration register, can be used to vary the crystal-oscillator frequency electronically. The range of the electronic adjustment depends on how much the chosen crystal frequency can be pulled by the varying capacitor. The frequency of the crystal oscillator used on the MAX2769C EV kit has a range of approximately 200Hz.

The MAX2769C provides a reference clock output. The frequency of the clock can be adjusted to crystal-oscillator frequency, a quarter of the oscillator frequency, a half of the oscillator frequency ( $f_{XTAL} \le 32$ MHz), or twice the oscillator frequency ( $f_{XTAL} \le 16$ MHz), by programming bits REFDIV in the PLL Configuration register. See Table 11.

### **Table 11. Reference Divider Settings**

| REFDIV<br>(PLL CONFIGURATION<br>REGISTER) | CLOCK OUTPUT      |

|-------------------------------------------|-------------------|

| 00                                        | XTAL frequency x2 |

| 01                                        | XTAL frequency ÷4 |

| 10                                        | XTAL frequency ÷2 |

| 11                                        | XTAL frequency    |

Figure 1. Schematic of the Crystal Oscillator in the MAX2679B EV Kit

## Universal GNSS Receiver

#### ADC

The MAX2769C features an on-chip ADC to digitize the downconverted GPS signal. The ADC can be enabled by configuring the bits, DRVCFG to 00 in the Configuration Register 2. See Table 12.

The ADC supports the digital outputs in three different formats: the unsigned binary, the sign and magnitude, or the two's complement format by setting bits FORMAT in Configuration register 2. See Table 13.

The maximum sampling rate of the ADC is approximately 50Msps. The sampled output is provided in a 2-bit format (1-bit magnitude and 1-bit sign) by default and also can be configured as a 1-bit or 2-bit in both I and Q channels, or 1-bit, 2-bit, or 3-bit in the I channel only. This selection can be done using IQEN in configuration 2 register. See Table 14.

### Table 12. Output Driver Configuration

| DRVCFG<br>(CONFIGURATION 2 REGISTER) | OUTPUT DRIVER<br>CONFIGURATION      |

|--------------------------------------|-------------------------------------|

| 00                                   | CMOS Logic                          |

| 01                                   | Reserved                            |

| 1X                                   | Analog Outputs<br>(ADC Bypass Mode) |

#### Table 13. ADC Output Data Format

| FORMAT<br>(CONFIGURATION 2 REGISTER) | ADC OUTPUT DATA<br>FORMAT  |

|--------------------------------------|----------------------------|

| 00                                   | Unsigned Binary            |

| 01                                   | Sign and Magnitude         |

| 1X                                   | Two's Complement<br>Binary |

### Table 16. Output Data Format

MSB bits are output at I1 or Q1 pins and LSB bits are output at I0 or Q0 pins, for I or Q channel, respectively. In the case of 3-bit, output data format is selected in the I channel only, the MSB is output at I1, the second bit is at I0, and the LSB is at Q1. The number of bits of the ADC can be configured through BITS in configuration 2 register. See <u>Table 15</u>.

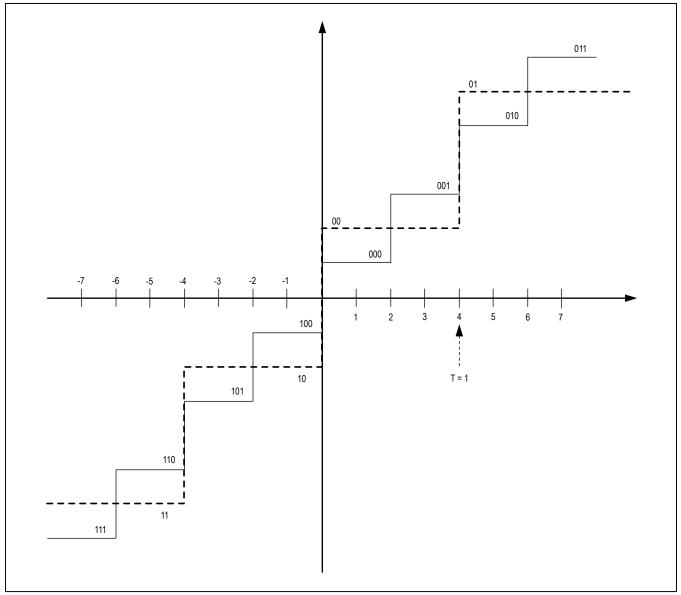

Figure 2 illustrates the ADC quantization levels for 2-bit and 3-bit cases and also describes the sign/magnitude data mapping. The variable T = 1 designates the location of the magnitude threshold for the 2-bit case.

#### **Analog Outputs**

The on-chip ADCs can be bypassed and the analog output from the PGA can be taken out directly when the bits, DRVCFG are set to 1X. See <u>Table 12</u>.

#### Table 14. IQ Channels Enable Settings

| IQEN<br>(CONFIGURATION 2 REGISTER) | ENABLED<br>CHANNEL    |

|------------------------------------|-----------------------|

| 0                                  | I channel only        |

| 1                                  | Both I and Q channels |

#### Table 15. ADC Output Bits Settings

| BITS<br>(CONFIGURATION 2 REGISTER) | NUMBER OF BITS<br>IN THE ADC |

|------------------------------------|------------------------------|

| 000                                | 1bit                         |

| 010                                | 2bits                        |

| 100                                | 3bits                        |

| INTEGER | SIC | SIGN/MAGNITUDE UNSIGNED BINARY |     | TWO'S COMPLEMENT BINARY |    |     |    |    |     |

|---------|-----|--------------------------------|-----|-------------------------|----|-----|----|----|-----|

| VALUE   | 1b  | 2b                             | 3b  | 1b                      | 2b | 3b  | 1b | 2b | 3b  |

| 7       | 0   | 01                             | 011 | 1                       | 11 | 111 | 0  | 01 | 011 |

| 5       | 0   | 01                             | 010 | 1                       | 11 | 110 | 0  | 01 | 010 |

| 3       | 0   | 00                             | 001 | 1                       | 10 | 101 | 0  | 00 | 001 |

| 1       | 0   | 00                             | 000 | 1                       | 10 | 110 | 0  | 00 | 000 |

| -1      | 1   | 10                             | 100 | 0                       | 01 | 011 | 1  | 11 | 111 |

| -3      | 1   | 10                             | 101 | 0                       | 01 | 010 | 1  | 11 | 110 |

| -5      | 1   | 11                             | 110 | 0                       | 00 | 001 | 1  | 10 | 101 |

| -7      | 1   | 11                             | 111 | 0                       | 00 | 000 | 1  | 10 | 100 |

Figure 2. ADC Quantization Levels for 2- and 3-Bit Cases

#### **ADC Fractional Clock Divider**

A 12-bit fractional clock divider is located in the clock path prior to the ADC and can be used to generate the ADC clock that is a fraction of the reference input clock. In a fractional divider mode, the instantaneous division ratio alternates between integer division ratios to achieve the required fraction. For example, if the fractional output clock is 4.5 times slower than the input clock, an average division ratio of 4.5 is achieved through an equal series of alternating divide-by-4 and divide-by-5 periods. The fractional division ratio is given by:

$f_{OUT}/f_{IN} = L_{COUNT}/(4096 - M_{COUNT} + L_{COUNT})$

where  $L_{COUNT}$  and  $M_{COUNT}$  are the 12-bit counter values programmed through the serial interface.

This divider can be enabled or bypassed by setting the bit, FCLKIN in Fractional Division Ratio Register to either 0 or 1. Also the sampling clock, ADCCLK can be taken either before or after the Reference Clock Divider/Multiplier depending on the ADCCLK bit setting.

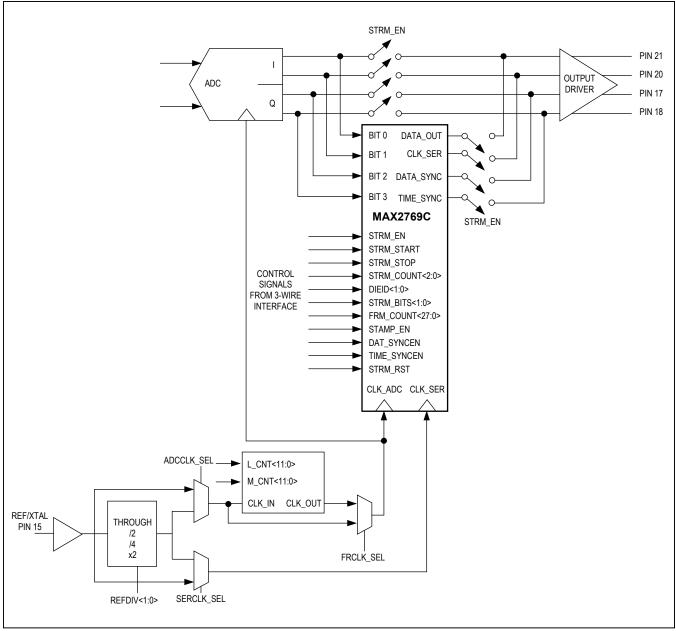

#### **DSP** Interface

GPS data is output from the ADC as the four logic signals (bit<sub>0</sub>, bit<sub>1</sub>, bit<sub>2</sub>, and bit<sub>3</sub>) that represent sign/magnitude, unsigned binary, or two's complement binary data in the I (bit<sub>0</sub> and bit<sub>1</sub>) and Q (bit<sub>2</sub> and bit<sub>3</sub>) channels. The resolution of the ADC can be set up to 3 bits per channel. For example, the 2-bit I and Q data in sign/magnitude format is mapped as follows: bit<sub>0</sub> = I<sub>SIGN</sub>, bit<sub>1</sub> = I<sub>MAG</sub>,

### Table 17. FCLKIN Mode Settings

| FCLKIN (FRACTIONAL<br>CLOCK DIVISION RATIO<br>REGISTER) | MODE (ADC INPUT<br>CLOCK)                  |

|---------------------------------------------------------|--------------------------------------------|

| 0                                                       | Comes from the Fractional<br>Clock Divider |

| 1                                                       | Bypasses the Fractional<br>Clock Divider   |

bit<sub>2</sub> =  $Q_{SIGN}$ , and bit<sub>3</sub> =  $Q_{MAG}$ . The data can be serialized in 16-bit segments of bit<sub>0</sub>, followed by bit<sub>1</sub>, bit<sub>2</sub>, and bit<sub>3</sub>. The number of bits to be serialized is controlled by the bits STRMBITS in the Configuration 3 register. This selects between bit<sub>0</sub>; bit<sub>0</sub> and bit<sub>1</sub>; bit<sub>0</sub> and bit<sub>2</sub>; and bit<sub>0</sub>, bit<sub>1</sub>, bit<sub>2</sub>, and bit<sub>3</sub> cases. If only bit<sub>0</sub> is serialized, the data stream consists of bit<sub>0</sub> data only. If a serialization of bit<sub>0</sub> and bit<sub>1</sub> (or bit<sub>2</sub>) is selected, the stream data pattern consists of 16 bits of bit<sub>0</sub> data followed by 16 bits of bit<sub>1</sub> (or bit<sub>2</sub>) data, which, in turn, is followed by 16 bits of bit<sub>0</sub> data, and so on. In this case, the serial clock must be at least twice as fast as the ADC clock. If a 4-bit serialization of bit<sub>0</sub>, bit<sub>1</sub>, bit<sub>2</sub>, and bit<sub>3</sub> is chosen, the serial clock must be at least four times faster than the ADC clock.

The ADC data is loaded in parallel into four holding registers that correspond to four ADC outputs. Holding registers are 16 bits long and are clocked by the ADC clock. At the end of the 16-bit ADC cycle, the data is transferred into four shift registers and shifted serially to the output during the next 16-bit ADC cycle. Shift registers are clocked by a serial clock that must be chosen fast enough so that all data is shifted out before the next set of data is loaded from the ADC. An all-zero pattern follows the data after all valid ADC data are streamed to the output. A DATASYNC signal is used to signal the beginning of each valid 16-bit data slice. In addition, there is a TIME\_SYNC signal that is output every 128 to 16,384 cycles of the ADC clock. see Figure 3 for details.

### Table 18. Sampling Clock Settings

| ADCCLK (SAMPLING<br>CLOCK) | SELECTION                               |

|----------------------------|-----------------------------------------|

| 0                          | Reference Divider/<br>Multiplier Output |

| 1                          | Reference clock Input                   |

# Universal GNSS Receiver

Figure 3. DSP Interface Top-Level Connectivity and Control Signals

#### **Preconfigured Device States**

When a serial interface is not available, the device can be used in preconfigured states that don't require programming through the serial interface. Connecting the PGM pin to logic-high and SCLK, SDATA, and  $\overline{CS}$  pins to either logichigh or logic-low sets the device in one of the preconfigured states according to <u>Table 19</u>.

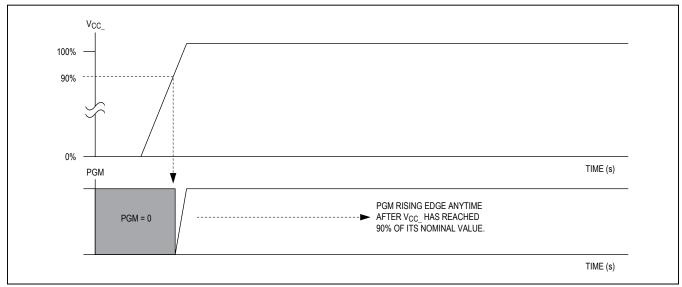

#### **Power-On Reset (POR)**

The MAX2769C incorporates power-on reset circuitry to ensure that register settings are loaded upon power-up. To ensure proper operation, the rising edge of PGM must occur no sooner than when  $V_{CC}$  reaches 90% of its final nominal value; see Figure 4 for details.

### **Table 19. Preconfigured Device States**

|              |                                 | DEVICE ELECTRICAL CHARACTERISTICS |                           |                      |                      |                        |                                 |                       |                    |      |      | L PINS    |

|--------------|---------------------------------|-----------------------------------|---------------------------|----------------------|----------------------|------------------------|---------------------------------|-----------------------|--------------------|------|------|-----------|

| DEVICE STATE | REFERENCE<br>FREQUENCY<br>(MHz) | REFERENCE<br>DIVISION<br>RATIO    | MAIN<br>DIVISION<br>RATIO | I AND Q OR I<br>ONLY | NUMBER OF<br>IQ BITS | I AND Q<br>LOGIC LEVEL | IF CENTER<br>FREQUENCY<br>(MHz) | IF FILTER<br>BW (MHz) | IF FILTER<br>ORDER | SCLK | DATA | <u>cs</u> |

| 0            | 16.368                          | 16                                | 1536                      | I                    | 1                    | Differential           | 4.092                           | 2.5                   | 5th                | 0    | 0    | 0         |

| 1            | 16.368                          | 16                                | 1536                      | I                    | 1                    | Differential           | 4.092                           | 2.5                   | 3rd                | 0    | 0    | 1         |

| 2            | 16.368                          | 16                                | 1536                      | I                    | 2                    | CMOS                   | 4.092                           | 2.5                   | 5th                | 0    | 1    | 0         |

| 3            | 32.736                          | 32                                | 1536                      | I                    | 2                    | CMOS                   | 4.092                           | 2.5                   | 5th                | 0    | 1    | 1         |

| 4            | 19.2                            | 96                                | 7857                      | I                    | 2                    | CMOS                   | 4.092                           | 2.5                   | 5th                | 1    | 0    | 0         |

| 5            | 27.456                          | 26                                | 1488                      | I                    | 3                    | CMOS                   | 4.092                           | 4.2                   | 5th                | 1    | 0    | 1         |

| 6            | 16.368                          | 16                                | 1536                      | I                    | 3                    | CMOS                   | 4.092                           | 4.2                   | 5th                | 1    | 1    | 0         |

| 7            | 27.456                          | 26                                | 1508                      | I                    | 3                    | CMOS                   | 9.27075                         | 9.66                  | 5th                | 1    | 1    | 1         |

Figure 4. V<sub>CC</sub>\_ Power-On Reset

#### Serial Interface, Address, and Bit Assignments

A serial interface is used to program the MAX2769C for configuring the different operating modes.

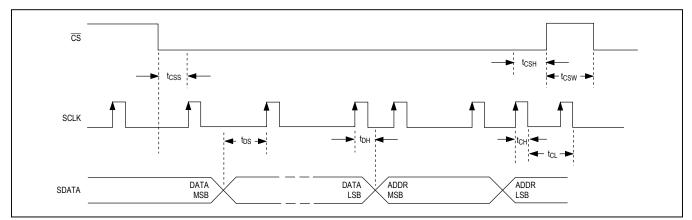

The serial interface is controlled by three signals: SCLK (serial clock),  $\overline{CS}$  (chip select), and SDATA (serial data). The control of the PLL, AGC, test, and block selection is performed through the serial-interface bus from the baseband controller. A 32-bit word, with the MSB (D27) being sent first, is clocked into a serial shift register when the chip-select signal is asserted low. The timing of the interface signals is shown in <u>Figure 5</u> and <u>Table 20</u> along with typical values for setup and hold time requirements.

Figure 5. 3-Wire Timing Diagram

### Table 20. Serial-Interface Timing Requirements

| SYMBOL           | PARAMETER                                                              | TYP VALUE | UNITS |

|------------------|------------------------------------------------------------------------|-----------|-------|

| t <sub>CSS</sub> | Falling edge of $\overline{CS}$ to rising edge of the first SCLK time. | 10        | ns    |

| t <sub>DS</sub>  | Data to serial-clock setup time.                                       | 10        | ns    |

| t <sub>DH</sub>  | Data to clock hold time.                                               | 10        | ns    |

| t <sub>CH</sub>  | Serial clock pulse-width high.                                         | 25        | ns    |

| t <sub>CL</sub>  | Clock pulse-width low.                                                 | 25        | ns    |

| t <sub>CSH</sub> | Last SCLK rising edge to rising edge of CS.                            | 10        | ns    |

| tcsw             | CS high pulse width.                                                   | 1         | clock |

### Table 21. Default Register Settings Overview

| REGISTER<br>NAME | ADDRESS<br>(A3:A0) | DATA                                                                |

|------------------|--------------------|---------------------------------------------------------------------|

| CONF1            | 0000               | Configures RX and IF sections, bias settings for individual blocks. |

| CONF2            | 0001               | Configures AGC and output sections.                                 |

| CONF3            | 0010               | Configures support and test functions for IF filter and AGC.        |

| PLLCONF          | 0011               | PLL, VCO, and CLK settings.                                         |

| DIV              | 0100               | PLL main and reference division ratios, other controls.             |

| FDIV             | 0101               | PLL fractional division ratio, other controls.                      |

| STRM             | 0110               | DSP interface number of frames to stream.                           |

| CLK              | 0111               | Fractional clock-divider values.                                    |

| TEST1            | 1000               | Reserved for test mode.                                             |

| TEST2            | 1001               | Reserved for test mode.                                             |

| REGISTER<br>NAME | ADDRESS<br>(A3:A0) | POWER-ON<br>RESET,<br>PGM = 0 |         | PR      | ECONFIGL | IRED DEVI | CE STATE, | PGM = 1 (h | ex)     |         |

|------------------|--------------------|-------------------------------|---------|---------|----------|-----------|-----------|------------|---------|---------|

|                  |                    | (hex)                         | 0       | 1       | 2        | 3         | 4         | 5          | 6       | 7       |

| CONF1            | 0000               | A2919A3                       | A2919A3 | A2919A3 | A2919A7  | A2919A3   | A2919A3   | A293573    | A293573 | A29B26B |

| CONF2            | 0001               | 055028C                       | 055121C | 055028C | 055121C  | 055028C   | 055028C   | 855030C    | 855030C | 855030C |

| CONF3            | 0010               | EAFE1DC                       | EAFE1DC | EAFE1DC | EAFE1DC  | EAFE1DC   | EAFE1DC   | EAFE1DC    | EAFE1DC | EAFE1DC |

| PLLCONF          | 0011               | 9EC0008                       | 9EC0008 | 9EC0008 | 9EC0008  | 9EC0008   | 9EC0008   | 9EC0008    | 9EC0008 | 9EC0008 |

| DIV              | 0100               | 0C00080                       | 0C00080 | 0C00080 | 0C00080  | 0C00100   | 3D62300   | 0BA00D0    | 0C00080 | 0BC80D0 |

| FDIV             | 0101               | 8000070                       | 8000070 | 8000070 | 8000070  | 8000070   | 8000070   | 8000070    | 8000070 | 8000070 |

| STRM             | 0110               | 8000000                       | 8000000 | 8000000 | 8000000  | 8000000   | 8000000   | 8000000    | 8000000 | 8000000 |

| CLK              | 0111               | 10061B2                       | 10061B2 | 10061B2 | 10061B2  | 10061B2   | 10061B2   | 10061B2    | 10061B2 | 10061B2 |

| TEST1            | 1000               | 1E0F401                       | 1E0F401 | 1E0F401 | 1E0F401  | 1E0F401   | 1E0F401   | 1E0F401    | 1E0F401 | 1E0F401 |

| TEST2            | 1001               | 28C0402                       | 28C0402 | 28C0402 | 28C0402  | 28C0402   | 28C0402   | 28C0402    | 28C0402 | 7CC0403 |

# Table 22. Default Register Settings

### **Detailed Register Definitions**

## Table 23. Configuration 1 (Address: 0000)

| DATA BIT | LOCATION | DEFAULT<br>VALUE<br>(PGM = 0) | DESCRIPTION                                                                                                                                                |

|----------|----------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHIPEN   | 27       | 1                             | Chip enable. Set 1 to enable the device and 0 to disable the entire device except the serial bus.                                                          |

| IDLE     | 26       | 0                             | Idle enable. Set 1 to put the chip in the idle mode and 0 for operating mode.                                                                              |

| RESERVED | 25:22    | 1000                          | _                                                                                                                                                          |

| RESERVED | 21:20    | 10                            | —                                                                                                                                                          |

| RESERVED | 19:18    | 10                            | _                                                                                                                                                          |

| RESERVED | 17:16    | 01                            | _                                                                                                                                                          |

| MIXPOLE  | 15       | 0                             | Mixer pole selection. Set 1 to program the passive filter pole at mixer output at 36MHz, or set 0 to program the pole at 13MHz.                            |

| LNAMODE  | 14:13    | 00                            | LNA mode selection, D14:D13 = 00: LNA selection gated by the antenna bias circuit, 01: LNA2 is active; 10: LNA1 is active; 11: both LNA1 and LNA2 are off. |

| MIXEN    | 12       | 1                             | Mixer enable. Set 1 to enable the mixer and 0 to shut down the mixer.                                                                                      |

| ANTEN    | 11       | 1                             | Antenna bias enable. Set 1 to enable the antenna bias and 0 to shut down the antenna bias.                                                                 |

| FCEN     | 10:5     | 001101                        | IF center frequency programming. Default for $f_{CENTER}$ = 3.9 MHz, BW = 2.5MHz.<br>The MSB of FCEN is located in Register Test Mode 2 (Table 32).        |

| FBW      | 4:3      | 00                            | IF filter center bandwidth selection. D4:D3 = 00: 2.5MHz; 10: 4.2MHz; 01: 9.66MHz; 11: Reserved.                                                           |

| F3OR5    | 2        | 0                             | Filter order selection. Set 0 to select the 5th-order Butterworth filter.<br>Set 1 to select the 3rd-order Butterworth filter.                             |

| FCENX    | 1        | 1                             | Polyphase filter selection. Set 1 to select bandpass filter mode. Set 0 to select lowpass filter mode.                                                     |

| FGAIN    | 0        | 1                             | IF filter gain setting. Set 0 to reduce the filter gain by 6dB.                                                                                            |

## Table 24. Configuration 2 (Address: 0001)

| DATA BIT | LOCATION | DEFAULT<br>VALUE<br>(PGM = 0) | DESCRIPTION                                                                                                                                                                                                                            |

|----------|----------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IQEN     | 27       | 0                             | I and Q channels enable. Set 1 to enable both I and Q channels and 0 to enable I channel only.                                                                                                                                         |

| GAINREF  | 26:15    | 170d                          | AGC gain reference value expressed by the number of MSB counts (magnitude bit density). 10101010 = 234 magnitude bit density reference, 1010100 = 84 magnitude bit density reference, 100111010 = 314 magnitude bit density reference. |

| RESERVED | 14:13    | 00                            | Reserved.                                                                                                                                                                                                                              |

| AGCMODE  | 12:11    | 00                            | AGC mode control. Set D12:D11 = 00: independent I and Q; 01: reserved; 10: gain is set directly from the serial interface by GAININ; 11: reserved.                                                                                     |

| FORMAT   | 10:9     | 01                            | Output data format. Set D10:D9 = 00: unsigned binary; 01: sign and magnitude; 1X: two's complement binary.                                                                                                                             |

| BITS     | 8:6      | 010                           | Number of bits in the ADC. Set D8:D6 = 000: 1 bit, 001: reserved; 010: 2 bits; 011: reserved, 100: 3 bits.                                                                                                                             |

| DRVCFG   | 5:4      | 00                            | Output driver configuration. Set D5:D4 = 00: CMOS logic, 01: reserved; 1X: analog outputs.                                                                                                                                             |

| RESERVED | 3        | 1                             | —                                                                                                                                                                                                                                      |

| RESERVED | 2        | 0                             | —                                                                                                                                                                                                                                      |

| DIEID    | 1:0      | 00                            | Identifies a version of the IC.                                                                                                                                                                                                        |

## Table 25. Configuration 3 (Address: 0010)

| DATA BIT | LOCATION | DEFAULT<br>VALUE<br>(PGM = 0) | DESCRIPTION                                                                                                                                                                                            |

|----------|----------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GAININ   | 27:22    | 111010                        | PGA gain value programming from the serial interface in steps of dB per LSB. 000000 = PGA gain set to 0dB, 101011 = 42dB, 101100 = 43dB, 101110 = 45dB, 111010 = 57dB, 111111 = 62dB.                  |

| RESERVED | 21       | 1                             | _                                                                                                                                                                                                      |

| HILOADEN | 20       | 0                             | Set 1 to enable the output driver to drive high loads.                                                                                                                                                 |

| RESERVED | 19       | 1                             | _                                                                                                                                                                                                      |

| RESERVED | 18       | 1                             | —                                                                                                                                                                                                      |

| RESERVED | 17       | 1                             | _                                                                                                                                                                                                      |

| RESERVED | 16       | 1                             | —                                                                                                                                                                                                      |

| FHIPEN   | 15       | 1                             | High-pass coupling enable. Set 1 to enable the highpass coupling between the filter and PGA, or 0 to disable the coupling.                                                                             |

| RESERVED | 14       | 1                             | —                                                                                                                                                                                                      |

| PGAIEN   | 13       | 1                             | I-Channel PGA Enable. Set 1 to enable PGA in the I channel or 0 to disable.                                                                                                                            |

| PGAQEN   | 12       | 0                             | Q-Channel PGA Enable. Set 1 to enable PGA in the Q channel or 0 to disable.                                                                                                                            |

| STRMEN   | 11       | 0                             | DSP Interface for Serial Streaming of Data Enable. This bit configures the IC such that the DSP interface is inserted in the signal path. Set 1 to enable the interface or 0 to disable the interface. |

| DATA BIT   | LOCATION | DEFAULT<br>VALUE<br>(PGM = 0) | DESCRIPTION                                                                                                                                                                                                                                                                                                    |

|------------|----------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STRMSTART  | 10       | 0                             | The positive edge of this command enables data streaming to the output. It also enables clock, data sync, and frame sync outputs.                                                                                                                                                                              |

| STRMSTOP   | 9        | 0                             | The positive edge of this command disables data streaming to the output. It also disables clock, data sync, and frame sync outputs.                                                                                                                                                                            |

| RESERVED   | 8:6      | 111                           | _                                                                                                                                                                                                                                                                                                              |

| STRMBITS   | 5:4      | 01                            | Number of Bits Streamed. D5:D4 = 00: reserved; 01: 1 MSB, 1 LSB; 10: reserved, Q<br>MSB; 11: 1 MSB, 1 LSB, Q MSB, Q LSB.                                                                                                                                                                                       |

| STAMPEN    | 3        | 1                             | The signal enables the insertion of the frame number at the beginning of each frame. If disabled, only the ADC data is streamed to the output.                                                                                                                                                                 |

| TIMESYNCEN | 2        | 1                             | This signal enables the output of the time sync pulses at all times when streaming is<br>enabled by the STRMEN command. Otherwise, the time sync pulses are available only<br>when data streaming is active at the output, for example, in the time intervals bound by<br>the STRMSTART and STRMSTOP commands. |

| DATSYNCEN  | 1        | 0                             | This control signal enables the sync pulses at the DATASYNC output. Each pulse is coincident with the beginning of the 16-bit data word that corresponds to a given output bit.                                                                                                                                |

| STRMRST    | 0        | 0                             | This command resets all the counters irrespective of the timing within the stream cycle.                                                                                                                                                                                                                       |

## Table 25. Configuration 3 (Address: 0010) (continued)

# Table 26. PLL Configuration (Address: 0011)

| DATA BIT | LOCATION | DEFAULT<br>VALUE<br>(PGM = 0) | DESCRIPTION                                                                                                                                                                                           |

|----------|----------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESERVED | 27       | 1                             | —                                                                                                                                                                                                     |

| RESERVED | 26       | 0                             | _                                                                                                                                                                                                     |

| RESERVED | 25       | 0                             | _                                                                                                                                                                                                     |

| REFOUTEN | 24       | 1                             | Clock buffer enable. Set 1 to enable the clock buffer or 0 to disable the clock buffer.                                                                                                               |

| RESERVED | 23       | 1                             | _                                                                                                                                                                                                     |

| REFDIV   | 22:21    | 11                            | Clock output divider ratio. Set D22:D21 = 00: clock frequency = XTAL frequency x 2;<br>01: clock frequency = XTAL frequency/4; 10: clock frequency = XTAL frequency/2;<br>11: clock frequency = XTAL. |

| IXTAL    | 20:19    | 01                            | Current programming for XTAL oscillator/buffer. Set D20:D19 = 00: reserved; 01: buffer normal current; 10: reserved; 11: oscillator high current.                                                     |

| RESERVED | 18:14    | 10000                         | —                                                                                                                                                                                                     |

| LDMUX    | 13:10    | 0000                          | PLL lock-detect enable.                                                                                                                                                                               |

## Table 26. PLL Configuration (Address: 0011) (continued)

| DATA BIT | LOCATION | DEFAULT<br>VALUE<br>(PGM = 0) | DESCRIPTION                                                                              |

|----------|----------|-------------------------------|------------------------------------------------------------------------------------------|

| ICP      | 9        | 0                             | Charge-pump current selection. Set 1 for 1mA and 0 for 0.5mA.                            |

| PFDEN    | 8        | 0                             | Set 0 for normal operation or 1 to disable the PLL phase frequency detector.             |

| RESERVED | 7        | 0                             | —                                                                                        |

| RESERVED | 6:4      | 000                           | -                                                                                        |

| INT_PLL  | 3        | 1                             | PLL mode control. Set 1 to enable the integer-N PLL or 0 to enable the fractional-N PLL. |

| PWRSAV   | 2        | 0                             | PLL power-save mode. Set 1 to enable the power-save mode or 0 to disable.                |

| RESERVED | 1        | 0                             | _                                                                                        |

| RESERVED | 0        | 0                             | —                                                                                        |

## Table 11. PLL Integer Division Ratio (Address 0100)

| DATA BIT | LOCATION | DEFAULT<br>VALUE<br>(PGM = 0) | DESCRIPTION                   |

|----------|----------|-------------------------------|-------------------------------|

| NDIV     | 27:13    | 1536d                         | PLL integer division ratio.   |

| RDIV     | 12:3     | 16d                           | PLL reference division ratio. |

| RESERVED | 2:0      | 000                           | —                             |