# 78P2351 Single Channel OC-3/ STM1-E/ E4 LIU

# **DATA SHEET**

#### SEPTEMBER 2006

# DESCRIPTION

The 78P2351 is Teridian's second generation Line Interface Unit (LIU) for 155 Mbps (OC-3, STS-3, or STM-1) and 140 Mbps PDH (E4) telecom interfaces. The device is a single chip solution that includes an integrated CDR in the transmit path for flexible NRZ to CMI conversion.

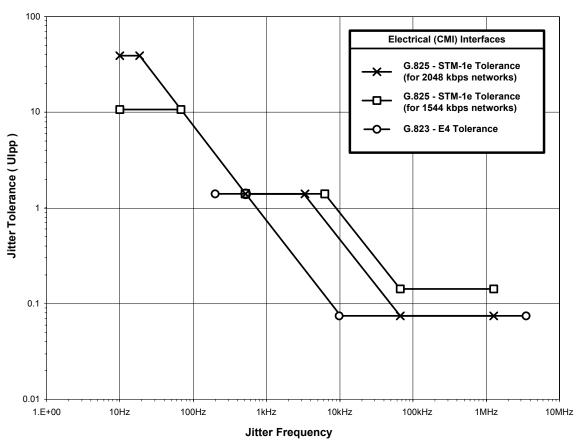

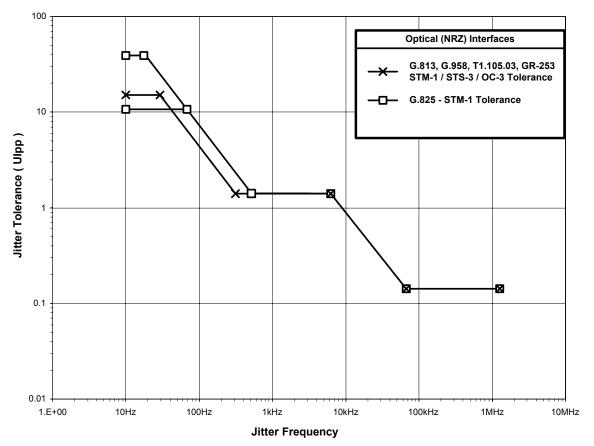

The device can interface to  $75\Omega$  coaxial cable using CMI coding or directly to a fiber optics transceiver module using NRZ coding. The 78P2351 is compliant with all respective ANSI, ITU-T, and Telcordia standards for jitter tolerance, generation, and transfer.

# **APPLICATIONS**

- Central Office Interconnects

- DSLAMs

- Add Drop Multiplexers (ADMs)

- PDH/SDH test equipment

- Multi Service Switches

- Digital Microwave Radios

# FEATURES

- ITU-T G.703 compliant cable driver for 139.264 Mbps or 155.52 Mbps CMI-coded coax transmission

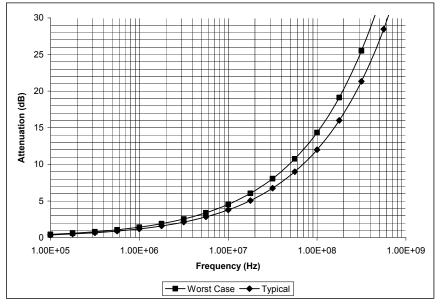

- Integrated adaptive CMI equalizer and CDR in receive path handles over 12.7dB of cable loss

- Serial, LVPECL-compatible system interface with integrated CRU in transmit path for flexible NRZ to CMI conversion.

- 4-bit parallel CMOS system interface with master and slave Tx clock modes.

- Selectable LVPECL compatible NRZ media interface for 155.52 Mbps optical transmission.

- Configurable via HW control pins or 4-wire serial interface

- Compliant with ANSI T1.105.03-1994; ITU-T G.751, G.813, G.823, G.825, G.958; and Telcordia GR-253-CORE for jitter performance.

- Receiver Loss of Signal (LOS) detection compatible with ITU-T G.783

- Operates from a single 3.3V supply

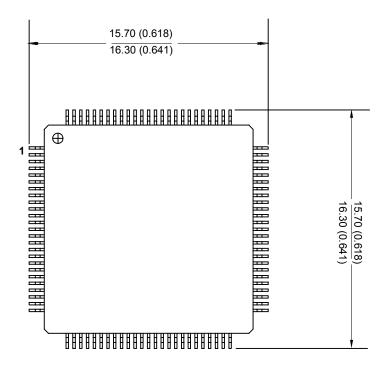

- 100-pin JEDEC LQFP

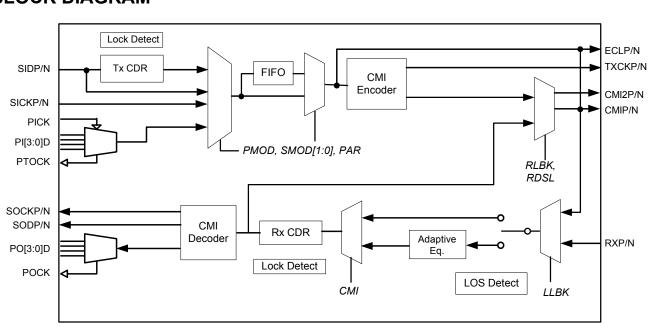

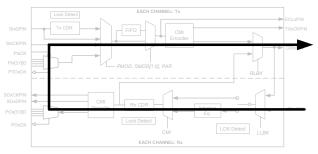

# **BLOCK DIAGRAM**

| ABLE OF CONTENTS |

|------------------|

|------------------|

| FUNCTIONAL DESCRIPTION                      | 4   |

|---------------------------------------------|-----|

| MODE SELECTION                              | 4   |

| REFERENCE CLOCK                             | 4   |

| RECEIVER OPERATION                          | 4   |

| Receiver Monitor Mode                       | 4   |

| Receive Loss of Signal                      | 5   |

| Receive Loss of Lock                        | 5   |

| TRANSMITTER OPERATION                       | -   |

| Synchronous (Re-timing) Tx Serial Modes     | 5   |

| Plesiochronous Tx Serial Modes              | 6   |

| Synchronous Parallel Modes                  | 6   |

| Transmit FIFO Description                   | 6   |

| Transmit Driver                             | 7   |

| Transmit Monitor Mode                       | 7   |

| Clock Synthesizer                           | 7   |

| Transmit Backplane Equalizer                | 7   |

| Transmit Loss of Lock                       |     |

| POWER-DOWN FUNCTION                         | 7   |

| LOOPBACK MODES                              | 8   |

| POWER-ON RESET                              |     |

| SERIAL CONTROL INTERFACE                    | 9   |

| PROGRAMMABLE INTERRUPTS                     | 9   |

| REGISTER DESCRIPTION                        | 10  |

| REGISTER ADDRESSING                         | .10 |

| REGISTER TABLE                              | .10 |

| LEGEND                                      | .11 |

| GLOBAL REGISTERS                            | .11 |

| ADDRESS 0-0: MASTER CONTROL REGISTER        | .11 |

| ADDRESS 0-1: INTERRUPT CONTROL REGISTER     | .12 |

| ADDRESS 0-2: I/O CONTROL REGISTER           | .12 |

| PORT-SPECIFIC REGISTERS                     | .13 |

| ADDRESS 1-0: MODE CONTROL REGISTER          | .13 |

| ADDRESS 1-1: SIGNAL CONTROL REGISTER        | .14 |

| ADDRESS 1-2: ADVANCED TX CONTROL REGISTER 1 | .15 |

| ADDRESS 1-3: ADVANCED TX CONTROL REGISTER 0 | .15 |

| ADDRESS 1-4: MODE CONTROL REGISTER 2        | .15 |

| ADDRESS 1-5: STATUS MONITOR REGISTER        | .16 |

|                                             |     |

# TABLE OF CONTENTS (continued)

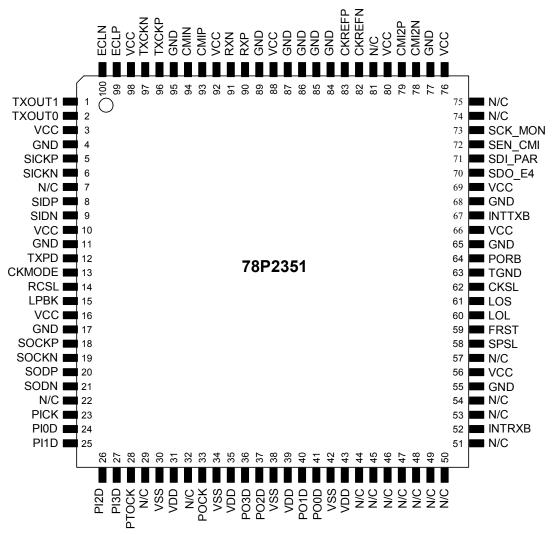

| PIN DESCRIPTION                                                 | 17 |

|-----------------------------------------------------------------|----|

| LEGEND                                                          | 17 |

| TRANSMITTER PINS                                                | 17 |

| RECEIVER PINS                                                   | 18 |

| REFERENCE AND STATUS PINS                                       | 19 |

| CONTROL PINS                                                    | 20 |

| SERIAL-PORT PINS                                                |    |

| POWER AND GROUND PINS                                           | 22 |

| ELECTRICAL SPECIFICATIONS                                       | 23 |

| ABSOLUTE MAXIMUM RATINGS                                        | 23 |

| RECOMMENDED OPERATING CONDITIONS                                | 23 |

| DC CHARACTERISTICS                                              |    |

| ANALOG PINS CHARACTERISTICS                                     |    |

| DIGITAL I/O CHARACTERISTICS                                     | 24 |

| Pins of type CI, CIU, CID                                       | 24 |

| Pins of type CIT                                                | 24 |

| Pins of type CIS                                                | 24 |

| Pins of type CO and COZ                                         |    |

| Pins of type PO                                                 | 25 |

| Pins of type PI                                                 |    |

| Pins of type OD                                                 |    |

| SERIAL-PORT TIMING CHARACTERISTICS                              | -  |

| TRANSMITTER TIMING CHARACTERISTICS                              |    |

| TIMING DIAGRAM: Transmitter Waveforms                           |    |

| REFERENCE CLOCK CHARACTERISTICS                                 |    |

| RECEIVER TIMING CHARACTERISTICS                                 |    |

| TIMING DIAGRAM: Receive Waveforms                               |    |

| TRANSMITTER SPECIFICATIONS FOR CMI INTERFACE                    | -  |

| TRANSMITTER OUTPUT JITTER                                       | -  |

| RECEIVER SPECIFICATIONS FOR CMI INTERFACE (Transformer-coupled) |    |

| RECEIVER JITTER TOLERANCE                                       |    |

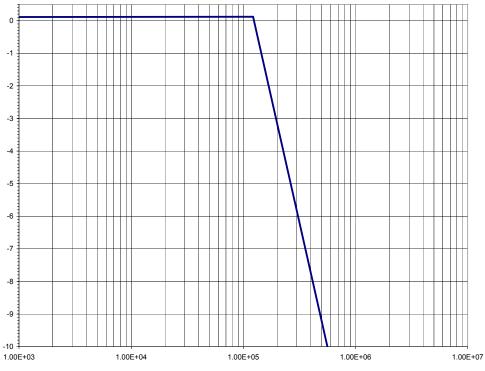

| RECEIVER JITTER TRANSFER FUNCTION                               |    |

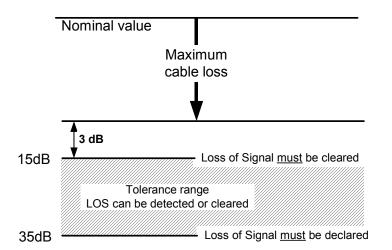

| CMI MODE LOSS OF SIGNAL CONDITION                               |    |

| APPLICATION INFORMATION                                         |    |

| EXTERNAL COMPONENTS                                             |    |

| (CMI) TRANSFORMER SPECIFICATIONS                                |    |

|                                                                 |    |

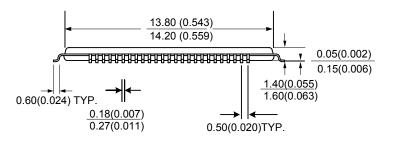

| MECHANICAL SPECIFICATIONS                                       | 40 |

| PACKAGE INFORMATION                                             | 41 |

| ORDERING INFORMATION                                            | 41 |

| Revision History                                                | 42 |

|                                                                 |    |

# FUNCTIONAL DESCRIPTION

The 78P2351 contains all the necessary transmit and receive circuitry for connection between 139.264Mbps and 155.52Mbps line interfaces and the digital universe. The chip is controllable through pins or serial port register settings.

In hardware mode (pin control) the SPSL pin must be low.

In software mode (SPSL pin high), control pins are disabled and the 78P2351 must be configured via the 4-wire serial port.

#### MODE SELECTION

The SDO\_E4 pin or E4 register bit determines which rate the device operates in according to the table below. This control combined with CKSL also selects the reference clock frequency.

| Rate               | SDO_E4 pin | E4 bit |

|--------------------|------------|--------|

| E4                 | High       | 1      |

| STM-1, STS-3, OC-3 | Low        | 0      |

The SEN\_CMI pin or CMI register bit enables the CMI encoder/decoder and selects one of two media for reception and transmission:  $75\Omega$  coaxial cable in CMI coding or optical fiber in Fiber (NRZ) mode.

| Media (coding) | SEN_CMI pin | CMI bit |

|----------------|-------------|---------|

| 75Ω Coax (CMI) | High        | 1       |

| Fiber (NRZ)    | Low         | 0       |

The SDI\_PAR pin or PAR register bit selects the interface to the framer to be 4-bit parallel CMOS or serial LVPECL. For each interface there are different transmit timing modes available. See TRANSMITTER OPERATION section for more info.

#### **REFERENCE CLOCK**

The 78P2351 requires a reference clock supplied to the CKREFP/N pins. This reference clock is used for clock recovery in the Rx DLL and Tx DLL. It is also used for transmit re-timing in the synchronous transmit modes. Refer to the TRANSMITTER OPERATION section for timing requirements during synchronous (re-timing) transmit modes.

For reference frequencies of 77.76MHz or lower, the device accepts a single ended CMOS clock at CKREFP (with CKREFN grounded). For reference frequencies of 139.264 or 155.52MHz, the device accepts a differential LVPECL clock input at CKREFP/N.

The frequency of this reference input is controlled by the rate selection and the CKSL control pin or register bit.

|                | Reference Frequency |             |  |  |  |

|----------------|---------------------|-------------|--|--|--|

| CKSL pin       | SDO_E4 low          | SDO_E4 high |  |  |  |

| Low            | 19.44MHz            | 17.408MHz   |  |  |  |

| Float          | 77.76MHz            | N/A         |  |  |  |

| High           | 155.52MHz           | 139.264MHz  |  |  |  |

| CKSL[1:0] bits | E4 bit = 0          | E4 bit = 1  |  |  |  |

| 00             | 19.44MHz            | 17.408MHz   |  |  |  |

| 10             | 77.76MHz            | N/A         |  |  |  |

| 11             | 155.52MHz           | 139.264MHz  |  |  |  |

#### **RECEIVER OPERATION**

The receiver accepts serial data, at 155.52Mbps or 139.264Mbps from the RXP/N inputs. In CMI mode, the input is differentially terminated with 75 $\Omega$  and transformer-coupled to a coaxial connector. In Fiber (NRZ) mode, the input is differentially terminated with 100 $\Omega$  and AC-coupled to an optical transceiver module. For board designs utilizing both coax and fiber media options, an analog switch or mechanical relay is required to switch between the different terminations and media paths.

The recovered CMI signal first enters an AGC and anadaptive equalizer designed to overcome intersymbol interference caused by long cable lengths. The variable gain differential amplifier automatically controls the gain to maintain a constant voltage level output regardless of the input voltage level. Note that in Fiber (NRZ) mode, the input signals bypass the adaptive equalizer.

The outputs of the data comparators are connected to the clock recovery circuits. The clock recovery system employs a Delay Locked Loop (DLL), which uses a reference frequency derived from the clock applied to the CKREFP/N pins.

In serial mode, the clock and data are decoded and transmitted through the LVPECL drivers. In parallel mode, the data is decoded and converted into four bit parallel segments before being transmitted through the CMOS drivers. Note that in Fiber (NRZ) mode, the CMI decoder is bypassed.

#### **Receiver Monitor Mode**

In CMI mode, the SCK\_MON pin or MON register bit enables the receiver's monitor mode which adds approximately 20dB of **flat gain** to the receive signal before equalization. Rx Monitor Mode can handle 20dB of flat loss typical of monitoring points with up to 6dB of cable loss. Note that Loss of Signal detection is disabled during Rx Monitor Mode.

# 78P2351 Single Channel OC-3/ STM1-E/ E4 LIU

#### Receive Loss of Signal

The 78P2351 includes a Loss of Signal (LOS) detector. When the peak value of the received signal is less than approximately 19dB below nominal for approximately 110 UI, Receive Loss of Signal is asserted. The Rx LOS signal is cleared when the received signal is greater than approximately 18dB below nominal for 110 UI.

In ECL mode, the LOS signal will be asserted when there are no transitions for longer than  $2.3\mu$ s. The signal is cleared when there are more than 4 transitions in 32 UI. It is generally recommended to use the LOS status signal from the optical transceiver module.

During Rx LOS conditions, the receive clock will remain on the last phase tap of the Rx DLL outputting a stable clock while the receive data outputs are squelched and held at logic '0'.

**<u>Note</u>**: Rx Loss of Signal detection is disabled during Local Loopback and Receive Monitor Modes.

#### **Receive Loss of Lock**

The 78P2351 includes an optional Receiver Loss of Lock detector that will flag if the recovered Rx clock frequency differs from the reference clock by more than  $\pm 100$ ppm in an interval greater than 420µs. This condition is cleared when the frequencies are less than  $\pm 100$ ppm off for more than 500µs.

#### Notes:

- 1. During Rx Loss of Signal (RLOS), the Rx Loss of Lock indicator is undefined and may report either status.

- 2. For reliable operation, the LOLOR bit in the Signal Control register should be toggled upon power-up and configuration.

### TRANSMITTER OPERATION

At the media interface, the transmit driver generates an analog signal for transmission through either a transformer and  $75\Omega$  coaxial cable or directly to a fiber optics transceiver for electrical to optical conversion.

At the host interface, the 78P2351 provides a number interface options for compatibility with most off-the-shelf framers and custom ASICs. A selectable 4-bit parallel or nibble interface is available with both slave or master timing options as well a serial LVPECL interface with various timing recovery modes.

Each of the serial NRZ transmit timing modes can be configured in HW mode or SW mode as shown in the table below.

| Serial                      | HW Con   | trol Pins | SW Control Bit |           |  |

|-----------------------------|----------|-----------|----------------|-----------|--|

| Mode                        | SDI_PAR  | CKMODE    | PAR            | SMOD[1:0] |  |

| Synchronous<br>clock + data | Low      | Low       | 0              | 0 0       |  |

| Synchronous data only       | Low      | Floating  | 0              | 1 0       |  |

| Plesiochronous data only    | Low High |           | 0              | 0 1       |  |

| Loop-timing                 | n/a      | n/a n/a   |                | 11        |  |

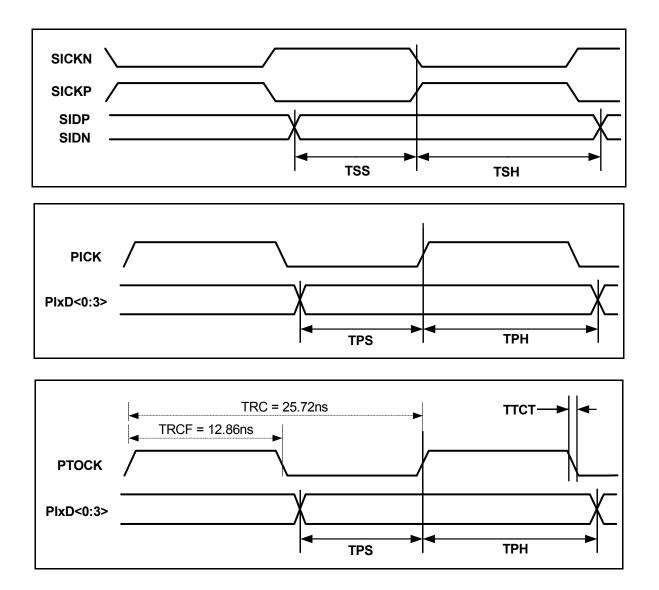

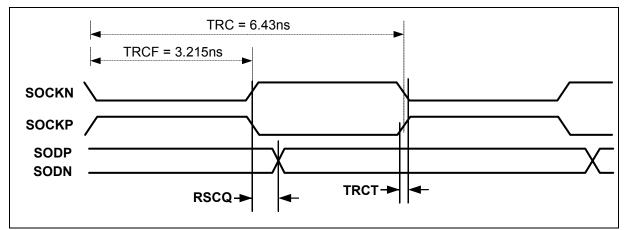

#### Synchronous (Re-timing) Tx Serial Modes

In Figure 1, serial NRZ transmit data is input to the SIDP/N pins at LVPECL levels. By default, the data is latched in on the rising edge of SICKP. An integrated FIFO decouples the on chip and off chip clocks and re-clocks the data using a clean synthesized clock generated from the provided reference clock. As such, the SICKP/N clock provided by the framer/mapper IC must be source synchronous with the provided reference clock when the FIFO is to be used.

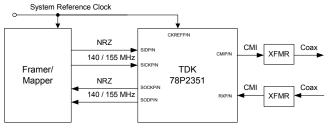

# Figure 1: Synchronous clock and data available (Tx CDR bypassed, FIFO enabled)

If an off-chip serial transmit clock is <u>not</u> available, as in Figure 2, the 78P2351 can recover a Tx clock from the serial NRZ data input and pass the data through the clock decoupling FIFO. The data is then re-clocked or re-timed using a clean synthesized clock generated from the provided reference clock. In this mode, the NRZ transmit data <u>must be source</u> <u>synchronous</u> with the reference clock applied at CKREFP/N.

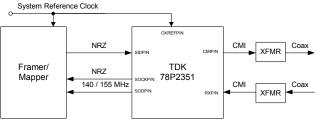

Figure 2: Synchronous data only (Tx CDR enabled, FIFO enabled)

#### Plesiochronous Tx Serial Mode

Figure 3 represents a common condition where a serial transmit clock is <u>not</u> available and/or the data is <u>not</u> source synchronous to the reference clock provided to the 78P2351. In this mode, the 78P2351 will recover a transmit clock from the serial plesiochronous data and bypass the internal FIFO and re-timing block. This mode is commonly used for mezzanine cards, modules, and any application where the reference clock can't always be synchronous to the transmit source clock/data.

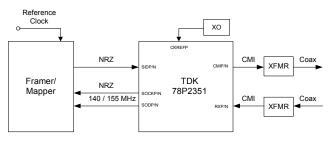

# Figure 3: Plesiochronous data only (Tx CDR enabled, FIFO bypassed)

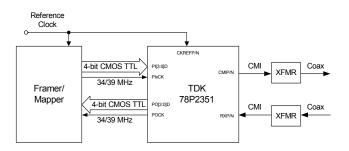

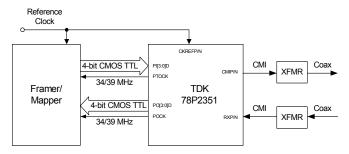

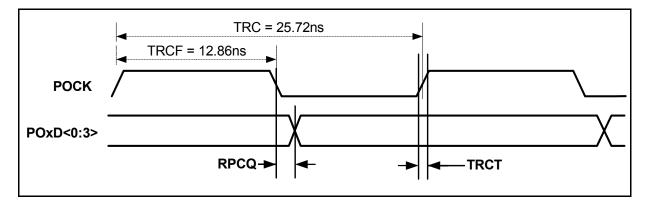

#### Synchronous Parallel Modes

In parallel modes, 4-bit CMOS data segments are input to the chip with a 34.816MHz (E4  $\div$  4) or 38.88MHz (STM1  $\div$  4) synchronous clock. These inputs are re-timed in a 4x8 clock decoupling FIFO and then to a serializer for transmission. Because the data is passed through the FIFO and re-timed using a synthesized clock, the transmit nibble clock and data <u>must be source synchronous</u> to the provided reference clock.

For maximum compatibility with legacy ASICs, the 78P2351 can operate in both slave and master clock modes as shown in Figures 4 and 5 respectively.

**Note**: A loop-timing mode is also available to allow external remote loopbacks (i.e. line loopback in framer). In this mode, the FIFO is still enabled, but the transmit data will be re-timed using the recovered receive clock.

| Parallel                | HW Con  | trol Pins      | SW Control Bits |       |  |

|-------------------------|---------|----------------|-----------------|-------|--|

| Mode                    | SDI_PAR | SDI_PAR CKMODE |                 | PMODE |  |

| Slave                   | High    | Low            | 1               | 0     |  |

| Slave +<br>*Loop-timing |         |                | 1               | 0     |  |

| Master                  | High    | High           | 1               | 1     |  |

\*To enable loop-timing in software mode, set SMOD[1:0]=11

Figure 5: Master Parallel Mode

#### Transmit FIFO Description

Since the reference clock and transmit clock/data go through different delay paths, it is inevitable that the phase relationship between the two clocks can vary in a bounded manner due to the fact that the absolute delays in the two paths can vary over time. The transmit FIFO allows long-term clock phase drift between the Tx clock and system reference clock, not exceeding +/- 25.6ns, to be handled without transmit error. If the clock wander exceeds the specified limits, the FIFO will over or under flow, and the FERR register signal will be asserted. This signal can be used to trigger an interrupt. This interrupt event is automatically cleared when a FIFO Reset (FRST) pulse is applied, and the FIFO is recentered.

#### Notes:

- External remote loopbacks (i.e. loopback within framer) are not possible in synchronous operation (FIFO enabled) unless the data is re-justified to be synchronous to the system reference clock or the 78P2351 is configured for loop-timing operation.

- 2) During IC power-up or transmit power-up, the clocks going to the FIFO may not be stable and cause the FIFO to overflow or underflow. As such, the FIFO should be manually reset using FRST anytime the transmitter is powered-up.

# 78P2351 Single Channel OC-3/ STM1-E/ E4 LIU

#### Transmit Driver

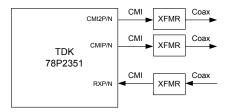

In CMI (electrical) mode, the CMIP/N pins are biased and terminated off-chip. They interface to  $75\Omega$ coaxial cable through a 1:1 wideband transformer and coaxial RF connectors. Reference application notes for schematic and layout guidelines.

The transmitter encodes the data using CMI line coding and shapes an analog signal to meet the appropriate ITU-T G.703 template. The CMI outputs are tri-stated during transmit disable and transmit power-down for redundancy applications.

**<u>Note</u>**: To avoid reflections causing unwanted board noise, it's recommended to power-down unused transmit ports that are not terminated with cable to an Rx input port.

When the CMI pin is low, the chip is in Fiber (NRZ pass-through) mode and interfaces directly to an optical transceiver module. The ECLP/N pins are internally biased and output NRZ data at LVPECL levels. The CMI driver, encoder and decoder are disabled in Fiber (NRZ) mode.

#### Transmit Monitor Mode

An optional redundant transmit output is available in CMI mode for transmit monitoring. These outputs (CMI2P/N) are enabled when the RCSL pin or RCSL register bit is activated.

Figure 6: Transmit Monitor Output

#### **Clock Synthesizer**

The transmit clock synthesizer is a low-jitter DLL that generates a 278.528/311.04 MHz clock for the CMI encoder. It is also used in both the receive and transmit sides for clock and data recovery.

**<u>Note</u>**: This 2x line rate clock is also available at the TXCKxP/N pins for downstream synchronization or system debug.

## Transmit Backplane Equalizer

An optional fixed LVPECL equalizer is integrated in the transmit path for architectures that use LIUs on active interface cards. The fixed equalizer can compensate for up to 1.5m of trace and can be enabled by the TXOUT1 pin or TXEQ bit as follows:

| TXOUT1 pin | TXEQ bit | Tx Equalizer |

|------------|----------|--------------|

| Low        | 1        | Enabled      |

| Float      | 0        | Disabled     |

#### Transmit Loss of Lock

In transmit modes using the integrated CDR, the 78P2351 will declare a loss of lock condition when there is no valid signal detected at the SIDP/N data inputs.

**<u>Note</u>**: The Tx LOL indicator is invalid and undefined when the parallel (nibble) interface is selected.

#### **POWER-DOWN FUNCTION**

Power-down control is provided to allow the 78P2351 to be shut off. Transmit and receive power-down can be set independently through SW control. Global power-down is achieved by powering down both the transmitter and receiver.

<u>Note</u>: The serial interface and configuration registers are not affected by power-down.

In HW mode, the transmitters can be powered down using the TXPD control pin.

# 78P2351 Single Channel OC-3/ STM1-E/ E4 LIU

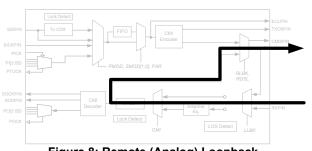

### LOOPBACK MODES

In SW mode, LLBK and RLBK bits in the Signal Control register are provided to activate the local and remote analog loopback modes respectively.

In HW mode, the LPBK pin can be used to activate local and remote analog loopback paths as shown in the table below.

| LPBK pin | Loopback Mode                                                                                                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low      | Normal operation                                                                                                                                                                                                         |

| Float    | Remote (analog) Loopback:<br>Recovered receive clock and data<br>looped back directly to the transmit<br>driver. The CMI decoder and most of<br>transmit path is bypassed (including the<br>redundant Tx monitor output) |

| High     | Local (analog) Loopback:<br>Transmit clock and data looped back to<br>receiver at the analog media interface.                                                                                                            |

Figure 7: Local (Analog) Loopback

Figure 8: Remote (Analog) Loopback

In SW mode only, a Full Remote (digital) Loopback bit FLBK is also available in the Advanced Tx Control register. This loopback exercises the entire Rx and Tx paths of the 78P2351 including the Tx clock recovery unit. As such, the user must enable either Serial Plesiochronous or Serial Loop-timing transmit modes to utilize the Full Remote (digital) Loopback.

Figure 9: Remote (Digital) Loopback

### **INTERNAL POWER-ON RESET**

Power-On Reset (POR) function is provided on chip. Roughly 50  $\mu$ s after Vcc reaches 2.4V at power up, a reset pulse is internally generated. This resets all registers to their default values as well as all state machines within the transceiver to known initial values. The reset signal is also brought out to the PORB pin. The PORB pin is a special function analog pin that allows for the following:

- Override the internal POR signal by driving in an external active low reset signal;

- Use the internally generated POR signal to trigger other resets;

- Add external capacitor to slow down the release of power-on reset (approximately 8µs per nF added).

**NOTE**: Do <u>not</u> pull-up the PORB pin to Vcc or drive this pin high during power-up. This will prevent the internal reset generator from resetting the entire chip and may result in errors.

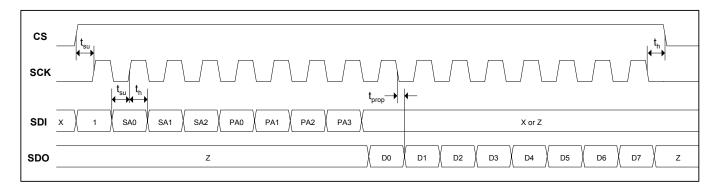

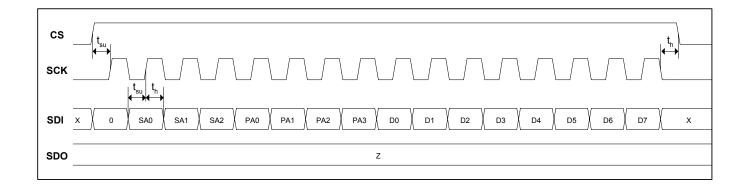

#### SERIAL CONTROL INTERFACE

The serial port controlled register allows a generic controller to interface with the 78P2351. It is used for mode settings, diagnostics and test, retrieval of status and performance information, and for on-chip fuse trimming during production test. The SPSL pin must be high in order to use the serial port.

The serial interface consists of four pins: Serial Port Enable (SEN\_CMI), Serial Clock (SCK\_MON), Serial Data In (SDI\_PAR), and Serial Data Out (SDO\_E4).

The SEN\_CMI pin initiates the read and write operations. It can also be used to select a particular device allowing SCK\_MON, SDI\_PAR and SDO\_E4 to be bussed together.

SCK\_MON is the clock input that times the data on SDI\_PAR and SDO\_E4. Data on SDI\_PAR is latched in on the rising-edge of SCK\_MON, and data on SDO\_E4 is clocked out using the falling edge of SCK\_MON.

SDI\_PAR is used to insert mode, address, and register data into the chip. Address and Data information are input least significant bit (LSB) first. The mode and address bit assignment and register table are shown in the following section.

SDO\_E4 is a tri-state capable output. It is used to output register data during a read operation. SDO\_E4 output is normally high impedance, and is enabled only during the duration when register data is being clocked out. Read data is clocked out least significant bit (LSB) first.

If SDI\_PAR coming out of the micro-controller chip is also tri-state capable, SDI\_PAR and SDO\_E4 can be connected together to simplify connections.

### PROGRAMMABLE INTERRUPTS

In addition to the receiver LOS and LOL status pins, the 78P2351 provides a programmable interrupt for the transmitter. In HW control mode, the default functions of the Tx interrupt is a transmit Loss of Lock (TXLOL) or FIFO error (FERR).

# **REGISTER DESCRIPTION**

# REGISTER ADDRESSING

| Address Bits | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3                    | Bit 2 | Bit 1 | Bit 0          |

|--------------|--------------|-------|-------|-------|--------------------------|-------|-------|----------------|

|              | Port Address |       |       |       | Port Address Sub-Address |       |       | Read/<br>Write |

| Assignment   | PA[3]        | PA[2] | PA[1] | PA[0] | SA[2]                    | SA[1] | SA[0] | R/W*           |

### **REGISTER TABLE**

### a) PA[3:0] = 0 : Global Registers

| Sub<br>Addr | Reg.<br>Name  | Description       | Bit 7        | Bit 6       | Bit 5       | Bit 4              | Bit 3              | Bit 2       | Bit 1        | Bit 0        |

|-------------|---------------|-------------------|--------------|-------------|-------------|--------------------|--------------------|-------------|--------------|--------------|

| 0           | MSCR<br>(R/W) | Master Control    | E4<br><0>    | <br><0>     | PAR<br><0>  | CKSL[1]<br><x></x> | CKSL[0]<br><x></x> | <br><x></x> | <br><x></x>  | SRST<br><0>  |

| 1           | INTC<br>(R/W) | Interrupt Control | INPOL<br><0> | <br><0>     | <br><1>     | <br><0>            | <br><0>            | <br><x></x> | MTLOL<br><1> | MFERR<br><1> |

| 2           | IOCR<br>(R/W) | I/O Control       | <br><x></x>  | <br><x></x> | <br><x></x> | <br><x></x>        | <br><x></x>        | <br><x></x> | <br><x></x>  | RCSL<br><0>  |

# b) PA[3:0] = 1 : Port-Specific Registers

| Sub<br>Addr | Reg.<br>Name | Description    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------------|--------------|----------------|---------|---------|---------|---------|---------|---------|---------|---------|

| 0           | MDCR         | Mode Control   | PDTX    | PDRX    | PMODE   | SMOD[1] | SMOD[0] | MON     |         |         |

|             | (R/W)        |                | <0>     | <0>     | <x></x> | <x></x> | <χ>     | <0>     | <0>     | <1>     |

| 1           | SGCR         | Signal Control | TCMIINV | RCMIINV | LOLOR   | RLBK    | LLBK    | RCLKP   | TCLKP   | FRST    |

|             | (R/W)        |                | <0>     | <0>     | <0>     | <0>     | <0>     | <0>     | <0>     | <0>     |

| 2           | ACR1         | Advanced Tx    |         |         |         |         |         |         | TPK     | TXEQ    |

|             | (R/W)        | Control 1      | <0>     | <0>     | <0>     | <0>     | <0>     | <0>     | <0>     | <0>     |

| 3           | ACR0         | Advanced Tx    |         |         |         |         |         | BST[1]  | BST[0]  | FLBK    |

|             | (R/W)        | Control 0      | <1>     | <0>     | <1>     | <0>     | <1>     | <0>     | <0>     | <0>     |

| 4           | MCR2         | Mada Cantral 2 | CMI     |         |         |         |         |         |         |         |

|             | (R/W)        | Mode Control 2 | <1>     | <x></x> | <x></x> | <0>     | <0>     | <0>     | <0>     | <0>     |

| 5           | STAT         | Status Monitor |         |         |         | RXLOS   | RXLOL   |         | TXLOL   | FERR    |

|             | (R/C)        |                | <x></x> |

| 6-7         |              | Reserved       |         |         |         |         |         |         |         |         |

### LEGEND

| TYPE | DESCRIPTION    | TYPE | DESCRIPTION   |

|------|----------------|------|---------------|

| R/O  | Read only      | R/W  | Read or Write |

| R/C  | Read and Clear |      |               |

### **GLOBAL REGISTERS**

### ADDRESS 0-0: MASTER CONTROL REGISTER

| BIT | NAME          | TYPE | DFLT<br>VALUE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |

|-----|---------------|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | E4            | R/W  | 0             | Line Rate Selection:<br>Selects the line rate as well as the input clock frequency at the<br>CKREFP/N pins.<br>0: OC-3, STS-3, STM-1 (155.52MHz)<br>1: E4 (139.264MHz)                                                                                                                                                                                    |

| 6   |               | R/W  | 0             | Unused                                                                                                                                                                                                                                                                                                                                                    |

| 5   | PAR           | R/W  | 0             | Serial/Parallel Interface Selection:<br>Selects the interface to the framer.<br>0: Serial LVPECL<br>1: 4-bit Parallel CMOS                                                                                                                                                                                                                                |

| 4:3 | CKSL<br>[1:0] | R/W  | XX            | Reference Clock Frequency Selection:Selects the reference clock frequency input at CKREFP/N pins.11: 155.52MHz / 139.264MHz (differential LVPECL)10: 77.76MHz / NA (single-ended CMOS)00: 19.44MHz / 17.408MHz (single-ended LVPECL)Secondary values correspond to E4 frequencies. Default values dependon the CKSL pin selection upon reset or power up. |

| 2:1 |               | R/W  | X0            | Reserved.                                                                                                                                                                                                                                                                                                                                                 |

| 0   | SRST          | R/W  | 0             | <b>Register Soft-Reset</b> :<br>When this bit is set, all registers are reset to their default values. This register bit is self-clearing.                                                                                                                                                                                                                |

#### ADDRESS 0-1: INTERRUPT CONTROL REGISTER

This register selects the events that would cause the interrupt pins to be activated. User may set as many bits as required.

| BIT | NAME  | TYPE | DFLT<br>VALUE | DESCRIPTION                                                                                                                  |

|-----|-------|------|---------------|------------------------------------------------------------------------------------------------------------------------------|

| 7   | INPOL | R/W  | 0             | Interrupt Pin Polarity Selection:<br>0 : Interrupt output is active-low (default)                                            |

| 6:2 |       | R/W  | 01000         | 1 : Interrupt output is active-high<br>Reserved for future use                                                               |

| 1   | MTLOL | R/W  | 1             | TXLOL Error Mask (active low):<br>Gates the TXLOL register bit to the INTTXB interrupt pin.<br>0: Mask<br>1: Pass            |

| 0   | MFERR | R/W  | 1             | FIERR Error Mask (active low):<br>Gates the respective FIERR register bit to the INTTXB interrupt pin.<br>0: Mask<br>1: Pass |

# ADDRESS 0-2: I/O CONTROL REGISTER

| BIT | NAME | TYPE | DFLT<br>VALUE | DESCRIPTION                                                                                               |

|-----|------|------|---------------|-----------------------------------------------------------------------------------------------------------|

| 7:1 |      | R/W  | XXXXXXX       | Unused                                                                                                    |

| 0   | RCSL | R/W  | 0             | Redundant Channel Enable:<br>Enables transmit monitor outputs at CMI2P/N pins.<br>0: Disable<br>1: Enable |

### PORT-SPECIFIC REGISTERS

For PA[3:0] = 1 only. Accessing a register with port address greater than 1 constitutes an invalid command.

### ADDRESS 1-0: MODE CONTROL REGISTER

| 5       PMODE       R/W       X       source of the transmit parallel clock, either taken from the framere externally or generated internally. Default value is determined by CKMODE pin setting upon power up or reset.         0:       Slave Timing. PICK clock input to the transmitter         1:       Master Timing. PTOCK clock output from the transmitter         1:       Master Timing. PTOCK clock output from the transmitter         1:       Master Timing. PTOCK clock output from the transmitter         2:       MOD[1]       R/W       X         3:       SMOD[0]       R/W       X         3:       SMOD[0]       R/W       X         4:       SMOD[0]       R/W       X         3:       SMOD[0]       R/W       X         4:       SMOD[0]       R/W       X         4:       SMOD[1]       R/W       X         5:       SMOD[0]       R/W       X         6:       0       1       Plesiochronous clock and data are passed through the CDR and then through the FIFO.         7:       0       1       Plesiochronous data is passed through the CDR to recover a clock. FIFO is bypassed because the data is not synchronous with the reference clock.         7:       1       1       Loop Timing Mode_Enable: The recovered receive clock is used as the reference for th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BIT | NAME    | TYPE | DFLT<br>VALUE | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Image: Section of the transmitter of the transmit plus determined by the transmit plus determined by the |     |         |      |               |                                                                                                                                                                                                                                                                                                            |

| 6         PDRX         R/W         0         Receiver Power-Down:<br>0: Normal Operation<br>1: Power-Down           5         PMODE         R/W         X         Parallel Mode Interface Selection:<br>When PAR=0, PMODE is invalid and defaults to logic '1';<br>When PAR=1, (Master Control Register: bit 5), PMODE selects the<br>source of the transmit parallel clock, either taken from the framer<br>externally or generated internally. Default value is determined by<br>CKMODE pin setting upon power up or reset.           6         SMOD[1]         R/W         X           4         SMOD[1]         R/W         X           4         SMOD[1]         R/W         X           4         SMOD[1]         R/W         X           5         Size Timing. PTCK clock input to the transmitter<br>1: Master Timing. PTCK clock output from the transmitter<br>1: Master Timing. PTCK clock output from the transmitter<br>1: Master Tohrous clock and data are passed through a<br>FIFO. The CDR is bypassed.           4         SMOD[1]         R/W         X           3         SMOD[0]         R/W         X           3         SMOD[0]         R/W         X           4         Mon         RR=PAR=1 (Master Control Register: bit 5), setting SMOD[1:0] = 11<br>will enable coop Timing Mode Enable: The recovered receive<br>clock is used as the reference for the transmit DLL<br>and FIFO.           3         SMOD[0]         R/W         X         When PAR=1 (Master Control Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7   | PDTX    | R/W  | 0             |                                                                                                                                                                                                                                                                                                            |

| 6       PDRX       R/W       0       0: Normal Operation<br>1: Power-Down         5       PMODE       R/W       X       Parallel Mode Interface Selection:<br>When PAR=0, PMODE is invalid and defaults to logic '1';<br>When PAR=1, (Master Control Register: bit 5), PMODE selects the<br>source of the transmit parallel clock, either taken from the frame<br>externally or generated intermally. Default well is determined by<br>CKMODE pin setting upon power up or reset.         6       Save Timing, PICK clock input to the transmitter         1:       Master Timing, PTOCK clock output from the transmitter         2       SMOD[1]       R/W       X         4       SMOD[0]       R/W       X         3       SMOD[1]       R/W       X         3       SMOD[0]       R/W       X         2       MON       R/W       0         2       MON       R/W       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |         |      |               |                                                                                                                                                                                                                                                                                                            |

| 1: Power-Down         1: PMODE       1: Power-Down         PMODE       R/W       X         Serial Mode Interface Selection:       When PAR=0 (Master Control Register: bit 5), SMOD[1:0] configures the transmitter's system interface. Default values determined by CKMODE pin setting upon power up or reset.         SMOD[1]       R/W       X       0       0       Synchronous clock and data are passed through a FIFO. The CDR is bypassed.         1       0       Synchronous data is passed through the CDR and then through the FIFO.       0       1         Plesiochronous data is not synchronous with the reference clock.       1       1       Loop Timing Mode Enable: The recovered receive clock is used as the reference for the t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |         |      |               |                                                                                                                                                                                                                                                                                                            |

| 5       PMODE       R/W       X       Parallel Mode Interface Selection:<br>When PAR=0, PMODE is invalid and defaults to logic '1';<br>When PAR=1, (Master Control Register: bit 5), PMODE selects the<br>source of the transmit parallel clock, either taken from the frame<br>externally or generated internally. Default value is determined by<br>CKMODE pin setting upon power up or reset.         4       SMOD[1]       R/W       X       Serial Mode Interface Selection:<br>When PAR=0 (Master Control Register: bit 5), SMOD[1:0] configures<br>the transmitter's system interface. Default values determined by<br>CKMODE pin setting upon power up or reset.         4       SMOD[1]       R/W       X       Serial Mode Interface Selection:<br>When PAR=0 (Master Control Register: bit 5), SMOD[1:0] configures<br>the transmitter's system interface. Default values determined by<br>CKMODE pin setting upon power up or reset.         3       SMOD[1]       R/W       X       0       Synchronous clock and data are passed through a<br>FIFO. The CDR is bypassed.         3       SMOD[0]       R/W       X       0       1       Plesiochronous data is passed through the CDR and<br>then through the FIFO.         3       SMOD[0]       R/W       X       When PAR=1 (Master Control Register: bit 5), setting SMOD[1:0] = 11<br>will enable Loop Timing Mode. Default values are determined by<br>CKMODE pin setting upon power up or reset as follows:<br>CKMODE Low → SMOD[1:0] default = 00 (no effect)<br>CKMODE Float → SMOD[1:0] default = 11 (loop-timing enable)<br>CKMODE Float → SMOD[1:0] default = 11 (loop-timing enable)<br>CKMODE Float → SMOD[1:0] default = 10 (no effect)         2                                                                                                                                                                                                                                                                                                                                                                         | 6   | PDRX    | R/W  | 0             |                                                                                                                                                                                                                                                                                                            |

| 5       PMODE       R/W       X       When PAR=0, PMODE is invalid and defaults to logic '1';<br>When PAR=1, (Master Control Register: bit 5), PMODE selects the<br>source of the transmit parallel clock, either taken from the framerie<br>externally or generated internally. Default value is determined by<br>CKMODE pin setting upon power up or reset.         6       Serial Mode Interface Selection:         7       When PAR=0, (Master Control Register: bit 5), SMOD[1:0] configures<br>the transmitter's system interface. Default values determined by<br>CKMODE pin setting upon power up or reset.         4       SMOD[1]       R/W       X         4       SMOD[1]       R/W       X         6       Synchronous clock and data<br>are passed through the CDR and<br>then through the FIFO.         7       0       Synchronous data is passed through the CDR and<br>then through the FIFO.         8       NOD[0]       R/W       X         9       1       Loop Timing Mode Enable: The recovered receive<br>clock is used as the reference for the transmit DLL<br>and FIFO.         3       SMOD[0]       R/W       X       When PAR=1 (Master Control Register: bit 5), setting SMOD[1:0] = 11<br>will enable Loop Timing Mode. Default values are determined by<br>CKMODE pin setting upon power up or reset as follows:<br>CKMODE in the transmit prover up or reset as follows:<br>CKMODE Fine at the target on the receive signal before equalization.<br>NOTE: Monitor Mode Enable:         2       MON       R/W       0       Receive Monitor Mode Enable:<br>CKMODE High $\rightarrow$ SMOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |         |      |               |                                                                                                                                                                                                                                                                                                            |

| 5       PMODE       R/W       X       When PAR=1, (Master Control Register: bit 5), PMODE selects the source of the transmit parallel clock, either taken from the framer externally or generated internally. Default value is determined by CKMODE pin setting upon power up or reset.         6       Slave Timing, PICK clock input to the transmitter         1       Master Timing, PTCK clock output to the transmitter         2       SMOD[1]       R/W       X         4       SMOD[1]       R/W       X         5       SMOD[1]       R/W       X         4       SMOD[1]       R/W       X         5       SMOD[1]       R/W       X         6       Signophic       Serial Mode Interface Selection:         When PAR=0 (Master Control Register: bit 5), SMOD[1:0] configures the transmitter's system interface. Default values determined by CKMODE pin setting upon power up or reset.         5       SMOD[1]       R/W       X         4       SMOD[1]       R/W       X         6       0       0       Synchronous clock and data are passed through the CDR and then through the FIFO.         7       0       1       Plesiochronous data is passed through the CDR to recover a clock. FIFO is bypassed because the data is not synchronous with the reference clock.         1       1       Loop Timing Mode Enable: The recovered receive c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |         |      |               |                                                                                                                                                                                                                                                                                                            |

| 1: Master Timing. PTOCK clock output from the transmitter         1: Master Timing. PTOCK clock output from the transmitter         1: Master Timing. PTOCK clock output from the transmitter         1: Master Timing. PTOCK clock output from the transmitter         1: Master Timing. PTOCK clock output from the transmitter         1: Master Timing. PTOCK clock output from the transmitter         1: Master Timing. PTOCK clock output from the transmitter         2: MOD[1] R/W       X         2: MON       R/W         2: MON       R/W         0: R/W       X         1: Master Timing. PTOCK clock output from the transmitter         1: Master Timing. PTOCK clock output from the transmitter         2: MON       R/W         2: MON       R/W         2: MON       R/W         3: SMOD[0]       R/W         4: SMOD[1]       R/W         4: SMOD[0]       R/W         4: SMOD[0]       R/W         5: SMOD[0]       R/W         4: SMOD[0]       R/W         5: SMOD[0]       R/W         5: SMOD[0]       R/W         6: SMOD[0]       R/W         7: SMOD[0]       R/W         7: SMOD[0]       R/W         8: SMOD[0]       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5   | PMODE   | R/W  | х             | When PAR=1, (Master Control Register: bit 5), PMODE selects the source of the transmit parallel clock, either taken from the framer externally or generated internally. Default value is determined by CKMODE pin setting upon power up or reset.                                                          |

| 4       SMOD[1]       R/W       X       Serial Mode Interface Selection:<br>When PAR=0 (Master Control Register: bit 5), SMOD[1:0] configures<br>the transmitter's system interface. Default values determined by<br>CKMODE pin setting upon power up or reset.<br>SMOD[1] SMOD[0]         4       SMOD[1]       R/W       X       0       0       Synchronous clock and data are passed through a<br>FIFO. The CDR is bypassed.         1       0       Synchronous data is passed through the CDR and<br>then through the FIFO.         0       1       Plesiochronous data is passed through the CDR to<br>recover a clock. FIFO is bypassed because the<br>data is not synchronous with the reference clock.         1       1       Loop Timing Mode Enable: The recovered receive<br>clock is used as the reference for the transmit DLL<br>and FIFO.         3       SMOD[0]       R/W       X         2       MON       R/W       0         2       MON       R/W       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |         |      |               | <b>o</b>                                                                                                                                                                                                                                                                                                   |

| 4       SMOD[1]       R/W       X       When PAR=0 (Master Control Register: bit 5), SMOD[1:0] configures the transmitter's system interface. Default values determined by CKMODE pin setting upon power up or reset.         4       SMOD[1]       R/W       X       0       0       Synchronous clock and data are passed through a FIFO. The CDR is bypassed.         1       0       Synchronous data is passed through the CDR and then through the FIFO.       0       1       Plesiochronous data is passed through the CDR to recover a clock. FIFO is bypassed because the data is not synchronous with the reference clock.         3       SMOD[0]       R/W       X       When PAR=1 (Master Control Register: bit 5), setting SMOD[1:0] = 11 will enable Loop Timing Mode. Default values are determined by CKMODE pin setting upon power up or reset as follows: CKMODE pin setting upon power up or reset as follows: CKMODE Low $\rightarrow$ SMOD[1:0] default = 10 (no effect)         2       MON       R/W       0       Receive Monitor Mode Enable:       01 (no effect)         2       MON       R/W       0       Receive Monitor Mode Enable:       01 (no effect)         2       MON       R/W       0       Receive Monitor Mode Enable:       01 (no effect)         2       MON       R/W       0       Normal Operation       1: Adds 20dB of flat gain to the receive signal before equalization. NOTE: Monitor mode is only available in CMI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |         |      |               |                                                                                                                                                                                                                                                                                                            |

| 2       MON       R/W       0       1       Plesiochronous data is passed through the CDR to recover a clock. FIFO is bypassed because the data is not synchronous with the reference clock.         3       SMOD[0]       R/W       X       When PAR=1 (Master Control Register: bit 5), setting SMOD[1:0] = 11 will enable Loop Timing Mode. Default values are determined by CKMODE pin setting upon power up or reset as follows: CKMODE Low → SMOD[1:0] default = 00 (no effect) CKMODE Float → SMOD[1:0] default = 11 (loop-timing enable) CKMODE High → SMOD[1:0] default = 01 (no effect)         2       MON       R/W       0       Receive Monitor Mode Enable: 0: Normal Operation 1: Adds 20dB of flat gain to the receive signal before equalization. NOTE: Monitor mode is only available in CMI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4   | SMOD[1] | R/W  | х             | When PAR=0 (Master Control Register: bit 5), SMOD[1:0] configures the transmitter's system interface. Default values determined by CKMODE pin setting upon power up or reset.         SMOD[1] SMOD[0]         0       0         Synchronous clock and data are passed through a FIFO. The CDR is bypassed. |

| 3       SMOD[0]       R/W       X       When PAR=1 (Master Control Register: bit 5), setting SMOD[1:0] = 11 will enable Loop Timing Mode. Default values are determined by CKMODE pin setting upon power up or reset as follows:<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |         |      |               | then through the FIFO.                                                                                                                                                                                                                                                                                     |

| 3       SMOD[0]       R/W       X       1       1       Loop Timing Mode Enable: The recovered receive clock is used as the reference for the transmit DLL and FIFO.         3       SMOD[0]       R/W       X       When PAR=1 (Master Control Register: bit 5), setting SMOD[1:0] = 11 will enable Loop Timing Mode. Default values are determined by CKMODE pin setting upon power up or reset as follows: CKMODE Low → SMOD[1:0] default = 00 (no effect) CKMODE Float → SMOD[1:0] default = 11 (loop-timing enable) CKMODE High → SMOD[1:0] default = 01 (no effect)         2       MON       R/W       0       Receive Monitor Mode Enable:       0: Normal Operation         1:       Adds 20dB of flat gain to the receive signal before equalization. NOTE: Monitor mode is only available in CMI mode.       Not mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |         |      |               | 0 1 <u>Plesiochronous data</u> is passed through the CDR to                                                                                                                                                                                                                                                |

| 2       MON       R/W       0       Receive Monitor Mode Enable:<br>0: Normal Operation<br>1: Adds 20dB of flat gain to the receive signal before equalization.<br>NOTE: Monitor mode is only available in CMI mode.       Not an operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |         |      |               | data is not synchronous with the reference clock.111Loop Timing Mode Enable: The recovered receive<br>clock is used as the reference for the transmit DLL                                                                                                                                                  |

| 2       MON       R/W       0       0: Normal Operation         1: Adds 20dB of flat gain to the receive signal before equalization.       NOTE: Monitor mode is only available in CMI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3   | SMOD[0] | R/W  | X             | CKMODE Low $\rightarrow$ SMOD[1:0] default = 00 (no effect)<br>CKMODE Float $\rightarrow$ SMOD[1:0] default = 11 (loop-timing enable)<br>CKMODE High $\rightarrow$ SMOD[1:0] default = 01 (no effect)                                                                                                      |

| 2       MON       R/W       0       1: Adds 20dB of flat gain to the receive signal before equalization.         NOTE: Monitor mode is only available in CMI mode.       NOTE: Monitor mode is only available in CMI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |         |      |               |                                                                                                                                                                                                                                                                                                            |

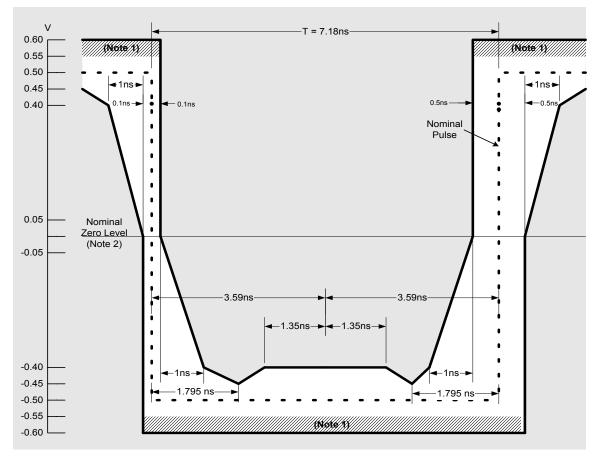

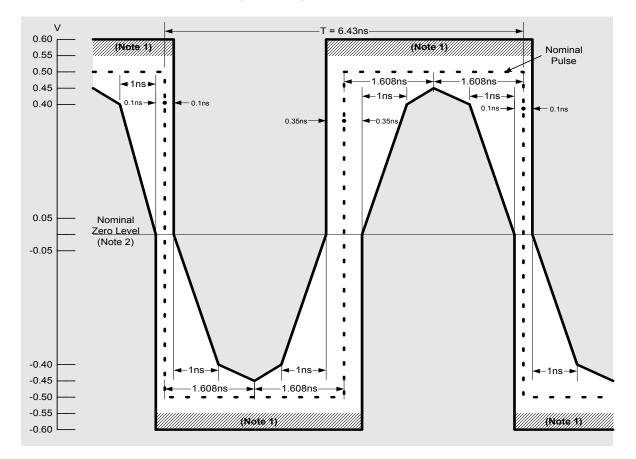

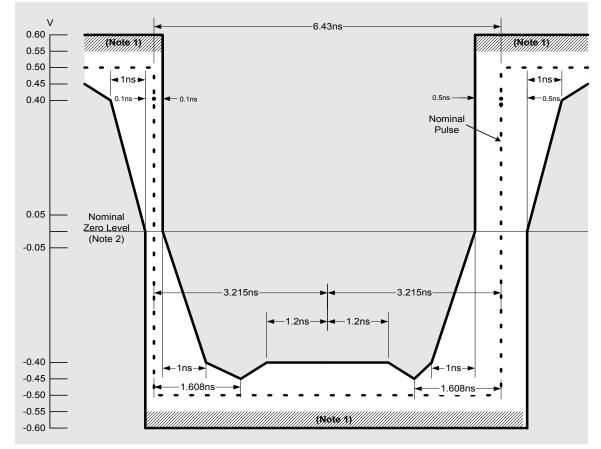

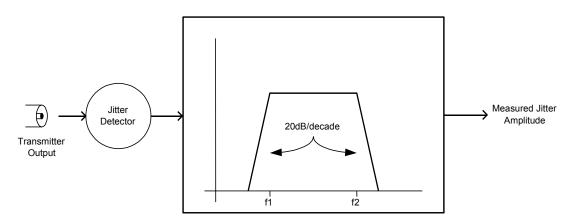

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2   | MON     | R/W  | 0             | 1: Adds 20dB of flat gain to the receive signal before equalization.                                                                                                                                                                                                                                       |