CMOS ST-BUS<sup>™</sup> Family MT89L85 Enhanced Digital Switch

Data Sheet

## Features

- 3.3 volt supply

- 5 V tolerant inputs and TTL compatible outputs

- 256 x 256 channel non-blocking switch

- Programmable frame integrity for wideband channels

- Automatic identification of ST-BUS/GCI interface backplanes

- Per channel tristate control

- Patented message mode

- Non-multiplexed microprocessor interface

- · Available in PLCC-44 and SSOP-48 packages

- Pin compatible with MT8985 device

- Low power consumption

## **Applications**

- · Medium size digital switch matrices

- Hyperchannel switching (e.g., ISDN H0)

- ST-BUS/MVIP<sup>™</sup> interface functions

- · Serial bus control and monitoring

- Centralized voice processing systems

- Data multiplexer

| Ordering Information |                |             |  |  |  |  |  |  |  |  |  |

|----------------------|----------------|-------------|--|--|--|--|--|--|--|--|--|

| MT89L85AP            | 44 Pin PLCC    | Tubes       |  |  |  |  |  |  |  |  |  |

| MT89L85AN            | 48 Pin SSOP    | Tubes       |  |  |  |  |  |  |  |  |  |

| MT89L85APR           | 44 Pin PLCC    | Tape & Reel |  |  |  |  |  |  |  |  |  |

| MT89L85ANR           | 48 Pin SSOP    | Tape & Reel |  |  |  |  |  |  |  |  |  |

| MT89L85AN1           | 48 Pin SSOP*   | Tubes       |  |  |  |  |  |  |  |  |  |

| MT89L85ANR1          | 48 Pin SSOP*   | Tape & Reel |  |  |  |  |  |  |  |  |  |

| MT89L85AP1           | 44 Pin PLCC*   | Tubes       |  |  |  |  |  |  |  |  |  |

| MT89L85APR1          | 44 Pin PLCC*   | Tape & Reel |  |  |  |  |  |  |  |  |  |

| *Pb Free Matte Tin   |                |             |  |  |  |  |  |  |  |  |  |

|                      | -40°C to +85°C |             |  |  |  |  |  |  |  |  |  |

## Description

The MT89L85 Enhanced Digital Switch device is an upgraded 3-volt version of the MT8985 Digital Switch. It is pin compatible with the MT8985 and retains all of the MT8985's functionality. The enhanced digital switch is designed for switching PCM-encoded voice or under microprocessor control, in digital data. PBXs ST-BUS/MVIP exchanges, and any environment. It provides simultaneous connections for up to 256 64 kb/s channels. Each of the eight serial inputs and outputs consist of 32 64 kbit/s channels multiplexed to form a 2048 kbit/s stream. As the main function in switching applications, the device provides per-channel selection between variable or constant throughput delays. The constant throughput delay feature allows grouped channels such as ISDN H0 to be switched through the device maintaining its sequence integrity. The MT89L85 is ideal for medium sized mixed voice/data switch and voice processing applications.

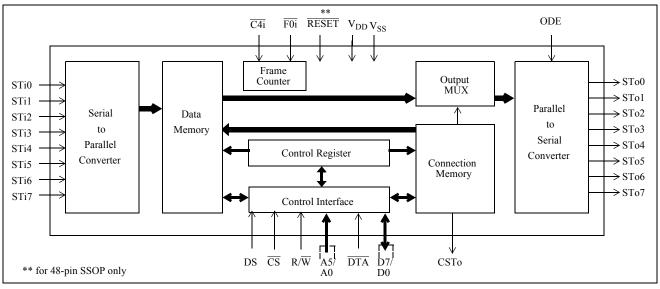

## Figure 1 - Functional Block Diagram

1

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 1999-2006, Zarlink Semiconductor Inc. All Rights Reserved.

February 2006

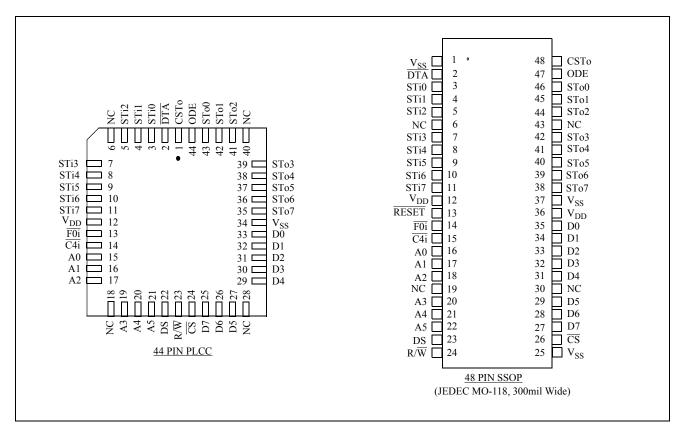

Figure 2 - Pin Connections

## **Pin Description**

| Pi             | n #            |               |                                                                                                                                                                                                                                                                                                                                                   |

|----------------|----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44<br>PLCC     | 48 SSOP        | Name          | Description                                                                                                                                                                                                                                                                                                                                       |

| 2              | 2              | DTA           | <b>Data Acknowledgment (Open Drain Output)</b> . This active low output indicates that a data bus transfer is complete. A pull-up resistor is required at this output.                                                                                                                                                                            |

| 3-5<br>7-11    | 3-5<br>7-11    | STi0-<br>STi7 | <b>ST-BUS Input 0 to 7 (Inputs).</b> Serial data input streams. These streams have 32 channels at data rates of 2.048 Mbit/s.                                                                                                                                                                                                                     |

| 12             | 12,36          | $V_{DD}$      | +3.3 Volt Power Supply.                                                                                                                                                                                                                                                                                                                           |

|                | 13             | RESET         | <b>Device Reset (5V tolerant input)</b> . This pin is only available for the 48-pin SSOP package. This active low input puts the MT89L85 in its reset state. It clears the internal counters and registers. All ST-BUS outputs are set to the high impedance state. This RESET pin must be held low for a minimum of 100nsec to reset the device. |

| 13             | 14             | F0i           | <b>Frame Pulse (Input).</b> This input accepts and automatically identifies frame synchronization signals formatted according to different backplane specifications such as ST-BUS and GCI.                                                                                                                                                       |

| 14             | 15             | C4i           | Clock (Input). 4.096 MHz serial clock for shifting data in and out of the data streams.                                                                                                                                                                                                                                                           |

| 15-17<br>19-21 | 16-18<br>20-22 | A0-A5         | Address 0 to 5 (Inputs). These lines provide the address to MT89L85 internal registers.                                                                                                                                                                                                                                                           |

| 22             | 23             | DS            | <b>Data Strobe (Input).</b> This is the input for the active high data strobe on the microprocessor interface. This input operates with $\overline{CS}$ to enable the internal read and write generation.                                                                                                                                         |

## **Pin Description**

| Pi             | Pin #          |               |                                                                                                                                                                                                                                                |

|----------------|----------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44<br>PLCC     | 48 SSOP        | Name          | Description                                                                                                                                                                                                                                    |

| 23             | 24             | R/W           | <b>Read/Write (Input).</b> This input controls the direction of the data bus lines (D0-D7) during a microprocessor access.                                                                                                                     |

| 24             | 26             | <del>CS</del> | <b>Chip Select (Input).</b> Active low input enabling a microprocessor read or write of control register or internal memories.                                                                                                                 |

| 25-27<br>29-33 | 27-29<br>31-35 | D7-D0         | <b>Data Bus 7 to 0 (Bidirectional).</b> These pins provide microprocessor access to data in the internal control register, connect memory high, connect memory low and data memory.                                                            |

| 34             | 1,25,37        | $V_{SS}$      | Ground Rail.                                                                                                                                                                                                                                   |

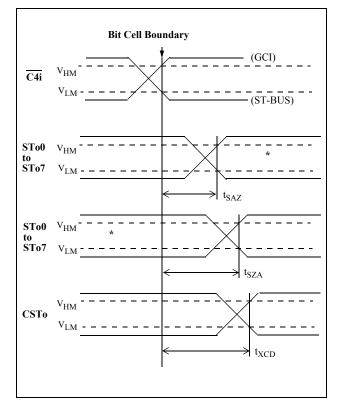

| 35-39<br>41-43 | 38-42<br>44-46 | STo7-<br>STo0 | <b>ST-BUS Outputs 7 to 0 (Three-state Outputs).</b> Serial data output streams. These streams are composed of 32 channels at data rates of 2.048 Mbit/s.                                                                                       |

| 44             | 47             | ODE           | <b>Output Drive Enable (Input).</b> This is an output enable for the STo0 to STo7 serial outputs. If this input is low STo0-7 are high impedance. If this input is high each channel may still be put into high impedance by software control. |

| 1              | 48             | CSTo          | <b>Control ST-BUS Output (Output).</b> This output is a 2.048 Mb/s line which contains 256 bits per frame. The level of each bit is controlled by the contents of the CSTo bit in the Connect Memory high locations.                           |

| 6,18,<br>28,40 | 6,19,30,4<br>3 | NC            | No Connection.                                                                                                                                                                                                                                 |

## **Functional Description**

With the integration of voice, video and data services into the same network, there has been an increasing demand for systems which ensure that data at N x 64 Kbit/s rates maintain frame sequence integrity while being transported through time slot interchange circuits. Existing requirements demand time slot interchange devices performing switching with constant throughput delay while guaranteeing minimum delay for voice channels.

The MT89L85 device provides both functions and allows existing systems based on the MT8985 to be easily upgraded to maintain the data integrity while multiple channel data are transported. The device is designed to switch 64 kbit/s PCM or N x 64 kbit/s data. The MT89L85 can provide both frame integrity for data applications and minimum throughput switching delay for voice applications on a per channel basis.

By using Zarlink Message mode capability, the microprocessor can access input and output time slots on a per channel basis to control devices such as the Zarlink MT8972, ISDN Transceivers and T1/CEPT trunk interfaces through the ST-BUS interface. Different digital backplanes can be accepted by the MT89L85 device without user's intervention. The MT89L85 device provides an internal circuit that automatically identifies the polarity and format of frame synchronization input signals compatible to ST-BUS and GCI interfaces.

## **Device Operation**

A functional block diagram of the MT89L85 device is shown in Figure 1. The serial ST-BUS streams operate continuously at 2.048 Mb/s and are arranged in 125  $\mu$ s wide frames each containing 32 8-bit channels. Eight input (STi0-7) and eight output (STo0-7) serial streams are provided in the MT89L85 device allowing a complete 256 x 256 channel non-blocking switch matrix to be constructed. The serial interface clock for the device is 4.096 MHz, as required in ST-BUS and GCI specifications.

## **Data Memory**

The received serial data is converted to parallel format by the on-chip serial to parallel converters and stored sequentially in a 256-position Data Memory. The sequential addressing of the Data Memory is generated by an internal counter that is reset by the input 8 kHz frame pulse ( $\overline{F0i}$ ) marking the frame boundaries of the incoming serial data streams.

Depending on the type of information to be switched, the MT89L85 device can be programmed to perform time slot interchange functions with different throughput delay capabilities on a per-channel basis. For voice applications, the variable delay mode can be selected ensuring minimum throughput delay between input and output data. In multiple or grouped channel data applications, the constant delay mode can be selected maintaining the integrity of the information through the switch.

Data to be output on the serial streams may come from two sources: Data Memory or Connect Memory. Locations in the Connect Memory, which is split into HIGH and LOW parts, are associated with particular ST-BUS output streams. When a channel is due to be transmitted on an ST-BUS output, the data for the channel can either be switched from an ST-BUS input (connection mode) or it can be originated from the microprocessor (message mode). If a channel is configured in connection mode, the source of the output data is the Data Memory. If a channel is configured in message mode, the source of the output data is the Connect Memory Low. Data destined for a particular channel on the serial output stream is read from the Data or Connect Memory Low during the previous channel time slot. This allows enough time for memory access and internal parallel to serial conversion.

## Connection and Message Modes

In connection mode, the addresses of input source for all output channels are stored in the Connect memory Low. The Connect Memory Low locations are mapped to each location corresponding to an output 64 kb/s channel. The contents of the Data memory at the selected address are then transferred to the parallel to serial converters. By having the output channel to specify the input channel through the connect memory, the user can route the same input channel to several output channels, allowing broadcasting facility in the switch.

In message mode the CPU writes data to the Connect Memory Low locations which correspond to the output link and channel number. The contents of the Connect Memory Low are transferred to the parallel to serial converter one channel before it is to be output. The Connect Memory Low data is transmitted each frame to the output until it is changed by the CPU.

The per-channel functions available in the MT89L85 are controlled by the Connect Memory High bits, which determine whether individual output channels are selected into specific conditions such as: message or connection mode, variable or constant throughput delay modes, output drivers enabled or in three-state condition. In addition, the Connect Memory High provides one bit to allow the user to control the state of the CSTo output pin.

If an output channel is set to three-state condition, the TDM serial stream output will be placed in high impedance during that channel time. In addition to the per-channel three-state control, all channels on the TDM outputs can be placed in high impedance at one time by pulling the ODE input pin in LOW. This overrides the individual per-channel programming on the Connect Memory High bits.

The Connect Memory data is received via the Microprocessor Interface at D0-D7 lines. The addressing of the MT89L85 internal registers, Data and Connect memories is performed through address input pins and some bits of the device's Control register. The higher order address bits come from the Control register, which may be written or read through the microprocessor interface. The lower order address bits come directly from the external address line inputs. For details on the device addressing, see Software Control and Control register description.

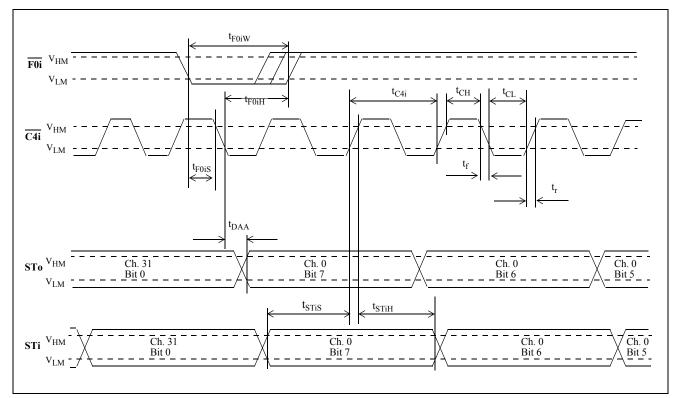

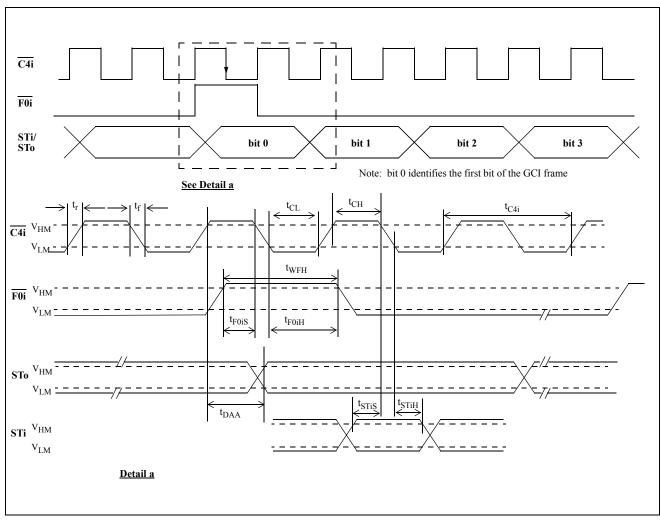

## Serial Interface Timing

The MT89L85 master clock ( $\overline{C4i}$ ) is a 4.096 MHz allowing serial data link configuration at 2.048 Mb/s to be implemented. The MT89L85 frame synchronization pulse can be formatted according to ST-BUS or GCI interface specifications; i.e., the frame pulse can be active in HIGH (GCI) or LOW (ST-BUS). The MT89L85 device automatically detects the presence of an input frame pulse and identifies the type of backplane present on the serial

interface. Upon determining the correct interface connected to the serial port, the internal timing unit establishes the appropriate serial data bit transmit and sampling edges. In ST-BUS mode, every second falling edge of the 4.096 MHz clock marks a bit boundary and the input data is clocked in by the rising edge, three quarters of the way into the bit cell. In GCI mode, every second rising edge of the 4.096 MHz clock marks the bit boundary while data sampling is performed during the falling edge, at three quarters of the bit boundaries.

#### Delay through the MT89L85

The transfer of information from the input serial streams to the output serial streams results in a delay through the MT89L85 device. The delay through the device varies according to the mode selected in the V/C bit of the connect memory high.

#### Variable Delay mode

The delay in this mode is dependent only on the combination of source and destination channels and it is not dependent on the input and output streams. The minimum delay achievable in the MT89L85 device is 3 time slots. In the MT89L85 device, the information that is to be output in the same channel position as the information is input (position n), relative to frame pulse, will be output in the following frame (channel n, frame n+1). The same occurs if the input channel has to be output in the two channels succeeding (n+1 and n+2) the channel position as the information is input.

The information switched to the third timeslot after the input has entered the device (for instance, input channel 0 to output channel 3 or input channel 30 to output channel 1), is always output three channels later.

Any switching configuration that provides three or more timeslots between input and output channels, will have a throughput delay equal to the difference between the output and input channels; i.e., the throughput delay will be less than one frame. Table 1 shows the possible delays for the MT89L85 device in Variable Delay mode:

| Input<br>Channel | Output<br>Channel                             | Throughput Delay    |  |  |  |  |

|------------------|-----------------------------------------------|---------------------|--|--|--|--|

| n                | m=n, n+1 or<br>n+2                            | m-n + 32 timeslots  |  |  |  |  |

| n                | m>n+2                                         | m-n time slots      |  |  |  |  |

| n                | m <n< td=""><td>32-(n-m) time slots</td></n<> | 32-(n-m) time slots |  |  |  |  |

Table 1 - Channel Delays for the Variable Delay Mode

## **Constant Delay Mode**

In this mode frame integrity is maintained in all switching configurations by making use of a multiple Data-Memory buffer technique where input channels written in any of the buffers during frame N will be read out during frame N+2. In the MT89L85, the minimum throughput delay achieve-able in Constant Delay mode will be 32 time slots; for example, when input time slot 32 (channel 31) is switched to output time slot 1 (channel 0). Likewise, the maximum delay is achieved when the first time slot in a frame (channel 0) is switched to the last time slot in the frame (channel 31), resulting in 94 time slots of delay.

To summarize, any input time slot from input frame N will be always switched to the destination time slot on output frame N+2. In Constant Delay mode, the device throughput delay is calculated according to the following formula:

DELAY = [32 + (32 - IN) + (OUT - 1)]; (expressed in number of time slots) Where: IN is the number of the input time slot (from 1 to 32).

OUT is the number of the output time slot (from 1 to 32).

## Microprocessor Port

The MT89L85 microprocessor port has pin compatibility with Zarlink MT8985 Digital Switch devices providing a non-multiplexed bus architecture. The parallel port consists of an 8 bit parallel data bus (D0-D7), six address input lines (A0-A5) and four control lines (CS, DS, R/W and DTA). This parallel microport allows the access to the Control registers, Connection Memory High, Connection Memory Low and the Data Memory. All locations are read/written except for the data memory which can be read only.

Accesses from the microport to the connection memory and the data memory are multiplexed with accesses from the input and output TDM ports. This can cause variable Data Acknowledge delays (DTA).

| A5 | A4     | A3     | A2     | A1     | A0     | LOCATION                      |

|----|--------|--------|--------|--------|--------|-------------------------------|

| 01 | 0<br>0 | 0<br>0 | 0<br>0 | 0<br>0 | 0<br>0 | Control Register<br>Channel 0 |

| 1  | 0      | 0      | 0      | 0      | 1      | Channel 1                     |

| 1  | •      | •      | •      | •      | •      | •                             |

| 1  | •      | •      | •      | •      | •      | •                             |

| 1  | •      | •      | •      | •      | •      | •                             |

| 1  | 1      | 1      | 1      | 1      | 1      | Channel 31                    |

Figure 3 - Address Memory Map

Note: "x" Don't care.

## Software Control

The address lines on the microprocessor interface give access to the MT89L85 internal registers and memories. If the A5,A1,A0 address line inputs are LOW, then the MT89L85 Internal Control Register is addressed (see Figure 3). If A5 input line is HIGH, then the remaining address input lines are used to select Memory subsections of 32 locations corresponding to the number of channels per input or output stream. As explained in the Control register description, the address input lines and the Stream Address bits (STA) of the Control register give the user the capability of selecting all positions of the MT89L85 Data and Connect memories.

The data in the Control register consists of Split memory and Message mode bits, Memory select and Stream Address bits (see Figure 4). The memory select bits allow the Connect Memory HIGH or LOW or the Data Memory to be chosen, and the Stream Address bits define an internal memory subsections corresponding to input or output ST-BUS streams. Bit 7 (Split Memory) of the Control register allows split memory operation whereby reads are from the Data memory and writes are to the Connect Memory LOW.

The Message Enable bit (bit 6) places every output channel on every output stream in message mode; i.e., the contents of the Connect Memory LOW (CML) are output on the ST-BUS output streams once every frame unless

the ODE input pin is LOW. If ME bit is HIGH, then the MT89L85 behaves as if bits 2 (Message Channel) and 0 (Output Enable) of every Connect Memory HIGH (CMH) locations were set to HIGH, regardless of the actual value. If ME bit is LOW, then bit 2 and 0 of each Connect Memory HIGH location operates normally. In this case, if bit 2 of the CMH is HIGH, the associated ST-BUS output channel is in Message mode. If bit 2 of the CMH is LOW, then the contents of the CML define the source information (stream and channel) of the time slot that is to be switched to an output.

If the ODE input pin is LOW, then all serial outputs are high-impedance. If ODE is HIGH, then bit 0 (Output Enable) of the CMH location enables (if HIGH) or disables (if LOW) the output drivers for the corresponding individual ST-BUS output stream and channel.

The contents of bit 1 (CSTo) of each Connection Memory High location (see Figure 5) is output on CSTo pin once every frame. The CSTo pin is a 2048 Mbit/s output which carries 256 bits. If CSTo bit is set HIGH, the corresponding bit on CSTo output is transmitted in HIGH. If CSTo bit is LOW, the corresponding bit on the CSTo output is transmitted in E256 CSTo bits of the CMH are transmitted sequentially on to the CSTo output pin and are synchronous to the ST-BUS streams. To allow for delay in any external control circuitry the contents of the CSTo bit is output one channel before the corresponding channel on the ST-BUS streams. For example, the contents of CSTo bit in position 0 (STO, CH0) of the CMH, is transmitted synchronously with ST-BUS channel 31, bit 7. The contents of CSTo bit in position 32 (ST1, CH0) of the CMH is transmitted during ST-BUS channel 31 bit 6.

Bit V/C (Variable/Constant Delay) on the Connect Memory High locations allow per-channel selection between Variable and Constant throughput delay capabilities.

#### Initialization of the MT89L85

On initialization or power up, the contents of the Connection Memory High can be in any state. This is a potentially hazardous condition when multiple MT89L85 ST-BUS outputs are tied together to form matrices, as these outputs may conflict. The ODE pin should be held low on power up to keep all outputs in the high impedance condition.

During the microprocessor initialization routine, the microprocessor should program the desired active paths through the matrices, and put all other channels into the high impedance state. Care should be taken that no two connected ST-BUS outputs drive the bus simultaneously. When this process is complete, the microprocessor controlling the matrices can bring the ODE signal high to relinquish high impedance state control to the CMH<sub>b</sub>0s.

|     |         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6           | 5       | 4       | 3   | 2    | 1    | 0    |  |  |  |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|---------|-----|------|------|------|--|--|--|

|     |         | SM                                                                                                                                                                                                                                                                                                                                                                                                                                             | ME          | X       | MS1     | MS0 | STA2 | STA1 | STA0 |  |  |  |

|     |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |         |         |     |      |      |      |  |  |  |

| Bit | Name    |                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description |         |         |     |      |      |      |  |  |  |

| 7   | SM      | <b>SM Split Memory.</b> When 1, all subsequent reads are from the Data Memory and writes are to the Connection Memory Low, except when the Control Register is accessed again. The Memory Sele bits need to be set to specify the memory for the operations. When 0, the Memory Select bits specify the memory for subsequent operations. In either case, the Stream Address Bits select the subsection of the memory which is made available. |             |         |         |     |      |      |      |  |  |  |

| 6   | ME      | Message E<br>Output streachannel det                                                                                                                                                                                                                                                                                                                                                                                                           | ams exce    | pt when | in High |     |      |      |      |  |  |  |

| 4-3 | MS1-MS0 | Memory Select Bits. The memory select bits operate as follows:<br>0-0 - Not to be used<br>0-1 - Data Memory (read only from the CPU)<br>1-0 - Connection Memory Low<br>1-1 - Connection Memory High                                                                                                                                                                                                                                            |             |         |         |     |      |      |      |  |  |  |

| 2-0 | STA2-0  | Stream Ad<br>or output S'<br>subsequent                                                                                                                                                                                                                                                                                                                                                                                                        | T-BUS st    | ream w  |         |     |      |      |      |  |  |  |

Figure 4 - Control Register Bits

x = Don't care

|     |                    |              | 7<br>X                                                                                                                                                                                                                                                                                                                                                     | 6<br>V/C | 5<br>X   | 4<br>X   | 3<br>X   | 2<br>MC | 1<br>CSTo | 0<br>OE |  |  |

|-----|--------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|---------|-----------|---------|--|--|

| Bit | t Name Description |              |                                                                                                                                                                                                                                                                                                                                                            |          |          |          |          |         |           |         |  |  |

| 6   | V/C                |              | <b>Variable/Constant Throughput Delay Mode.</b> This bit is used to select between Variable (LOW) and Constant Delay (HIGH) modes on a per-channel basis.                                                                                                                                                                                                  |          |          |          |          |         |           |         |  |  |

| 2   | МС                 | Low<br>progr | <b>Message Channel.</b> When 1, the contents of the corresponding location in Connection Memory Low are output on the corresponding channel and stream. When 0, the contents of the programmed location in Connection Memory Low act as an address for the Data Memory and so determine the source of the connection to the location's channel and stream. |          |          |          |          |         |           |         |  |  |

| 1   | СЅТо               | CSTo         | o Bit. '                                                                                                                                                                                                                                                                                                                                                   | This bit | drives a | bit time | e on the | CSTo or | utput pin | l.      |  |  |

| 0   | OE                 | chanr        | <b>Output Enable.</b> This bit enables the output drivers on a per-channel basis. This allows indi channels on individual streams to be made high-impedance, allowing switch matrices to be constructed. A HIGH enables the driver and a LOW disables it.                                                                                                  |          |          |          |          |         |           |         |  |  |

## Figure 5 - Connection Memory High Bits

x = Don't care

|      |                                                                                                                                                                                                                                                                                                                                                              |         | 7                                                                                                                                                                                                                                         | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

|      |                                                                                                                                                                                                                                                                                                                                                              | SA      | AB2                                                                                                                                                                                                                                       | SAB1 | SAB0 | CAB4 | CAB3 | CAB2 | CAB1 | CAB0 |  |  |  |

|      |                                                                                                                                                                                                                                                                                                                                                              |         |                                                                                                                                                                                                                                           |      |      |      |      |      |      |      |  |  |  |

| Bit  | Name                                                                                                                                                                                                                                                                                                                                                         |         | Description                                                                                                                                                                                                                               |      |      |      |      |      |      |      |  |  |  |

| 7-5  | SAB2-0*                                                                                                                                                                                                                                                                                                                                                      |         | <b>Source Stream Address bits.</b> These three bits are used to select eight source streams for the connection. Bit 7 of each word is the most significant bit.                                                                           |      |      |      |      |      |      |      |  |  |  |

| 4-0* | CAB4-0*                                                                                                                                                                                                                                                                                                                                                      | for the | <b>Source Channel Address bits 0-4.</b> These five bits are used to select 32 different source channels for the connection (The ST-BUS stream where the channel is present is defined by bits SAB2-0). Bit 4 is the most significant bit. |      |      |      |      |      |      |      |  |  |  |

| *    | If bit 2 of the corresponding Connection High location is 1 or if bit 6 of the Control Register is 1, then these entire 8 bits are output on the channel and stream associated with this location. Otherwise, the bits are used as indicated to define the source of the connection which is output on the channel and stream associated with this location. |         |                                                                                                                                                                                                                                           |      |      |      |      |      |      |      |  |  |  |

## Figure 6 - Connection Memory Low Bits

## Applications

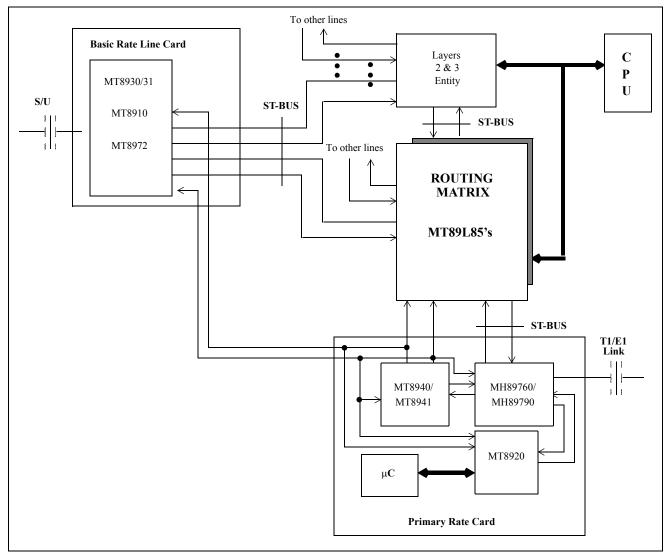

## Typical Exchange, PBX or Multiplexer

Figure 7 shows a typical implementation of line cards being interconnected through a central routing matrix that can scale up in channel capacity to accommodate different number of ports depending on the application. In a configuration where the switched services utilize concatenated or grouped time slots to carry voice, data and video (channels of 128, 256 Kb/s, ISDN H0 and others), the central routing matrix has to guarantee constant throughput delay to maintain the sequence integrity between input and output channels. Figure 7 shows an example where the MT89L85 device guarantees data integrity when data flows from the T1/E1 to the S/U interface links and vice-versa. Modern technologies available today such as Frame Relay network using dedicated fractional T1 are one of the key applications for the MT89L85 device.

Figure 7 - Typical Exchange, PBX or Multiplexer Configuration

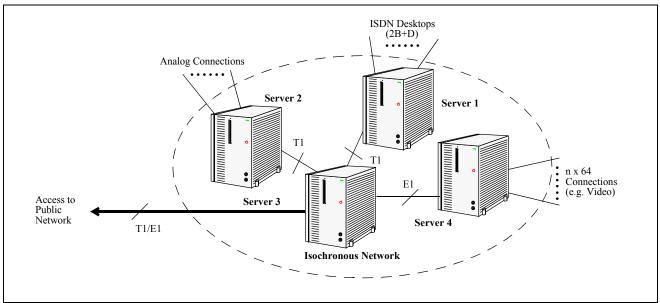

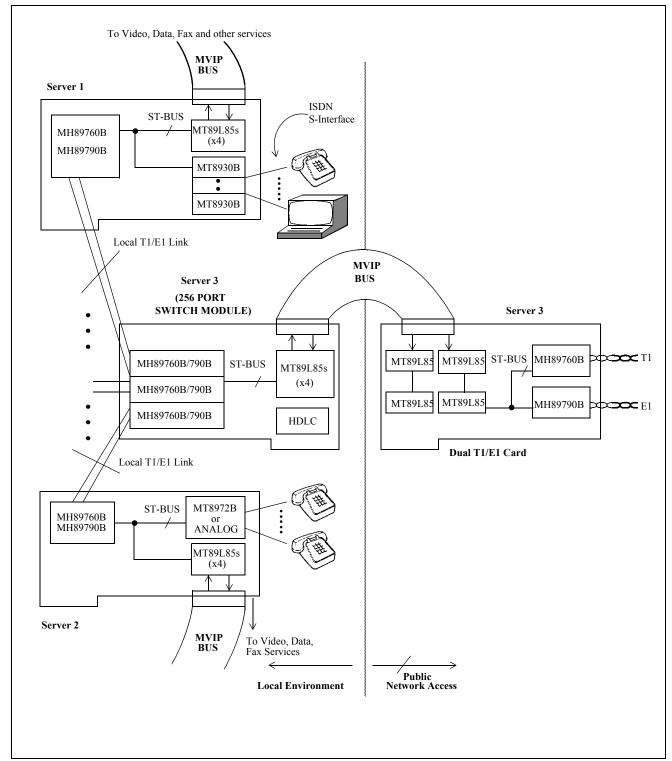

## Low Latency Isochronous Network

In today's local working group environment, there is an increasing demand for solutions on interconnection of desktop and telephone systems so that mixed voice, data and video services can be grouped together in a reliable network allowing the deployment of multimedia services. Existing multimedia applications require a network with predictable data transfer delays that can be implemented at a reasonable cost. The Low Latency Isochronous Network is one of the alternatives that system designers have chosen to accommodate this requirement (see Figure 8a). This network can be implemented using existing TDM transmission media devices such as ISDN Basic (S or U) and Primary rates trunks (T1 and CEPT) to transport mixed voice and data signals in grouped time slots; for example, 2B channels in case of ISDN S or U interfaces or up to 32 channels in case of a CEPT link.

Figure 8a - Private Isochronous Network

Figure 8b shows a more detailed configuration whereby several PCs are connected to form an Isochronous network. Several services can be interconnected within a single PC chassis through the standardized Multi Vendor Integration Protocol (MVIP). Such an interface allows the distribution and interconnection of services like voice mail, integrated voice response, voice recognition, LAN gateways, key systems, fax servers, video cards, etc.

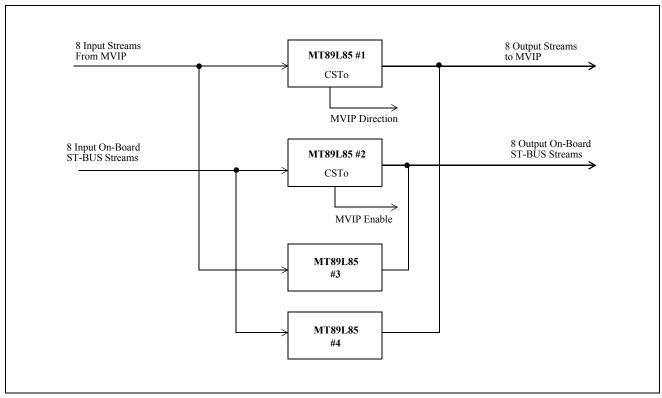

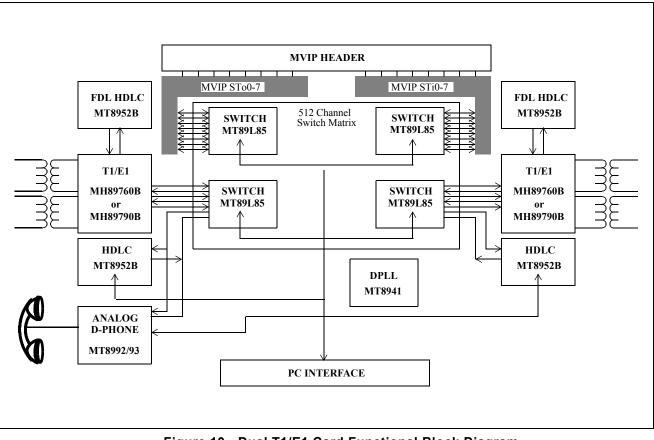

The information being exchanged between cards through the MVIP interface on every computer as well as between computers through T1 or CEPT links is, in general, of mixed type where 64 Kb/s and N\*64 Kb/s channels are grouped together. When such a mixed type of data is transferred between cards within one chassis or from one computer to another, the sequence integrity of the concatenated channels has to be maintained. The MT89L85 device suits this application and can be used to form a complete non-blocking switch matrix of 512 channels (see Figure 9). This allows 8 pairs of ST-BUS streams to be dedicated to the MVIP side whereas the remaining 8 pairs are used for local ancilliary functions in typical dual T1/E1 interface applications (Figure 10).

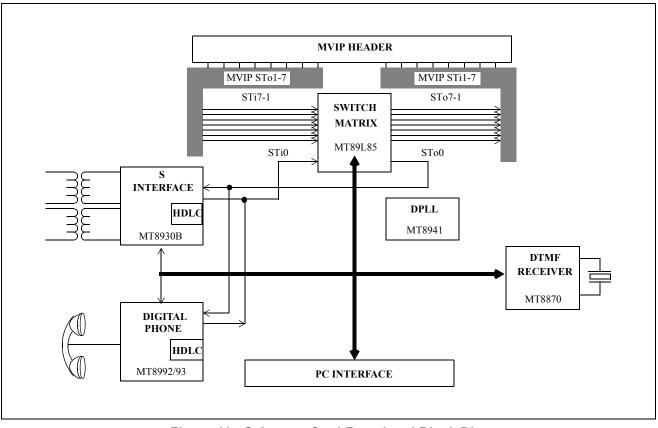

Another application of the MT89L85 in an MVIP environment is to build an ISDN S-interface card (Figure 11). In this card, 7 pairs of ST-BUS streams are connected to the MVIP interface while the remaining pair is reserved for the interconnection of Zarlink MT8930 (SNIC), MT8992 (H-PHONE) and the MVIP interface.

Figure 8b - Implementation of an Isochronous Network Using Zarlink Components

Figure 9 - 512-Channel Switch Array

Figure 10 - Dual T1/E1 Card Functional Block Diagram

Figure 11 - S-Access Card Functional Block Diagram

#### **Absolute Maximum Ratings\***

|   | Parameter                  | Symbol          | Min.                 | Max.                 | Units |

|---|----------------------------|-----------------|----------------------|----------------------|-------|

| 1 | Supply Voltage             | V <sub>DD</sub> | -0.3                 | 5.0                  | V     |

| 2 | Voltage on Digital Inputs  | VI              | V <sub>ss</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 3 | Current at Digital Outputs | Io              |                      | 20                   | mA    |

| 4 | Storage Temperature        | Ts              | -55                  | +125                 | °C    |

| 5 | Package Power Dissipation  | P <sub>D</sub>  |                      | 1                    | W     |

\* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

## Recommended Operating Conditions - Voltages are with respect to ground (V<sub>ss</sub>) unless otherwise stated.

|   | Characteristics                              | Sym.              | Min.            | Typ.‡ | Max.            | Units | Test Conditions |

|---|----------------------------------------------|-------------------|-----------------|-------|-----------------|-------|-----------------|

| 1 | Operating Temperature                        | T <sub>OP</sub>   | -40             | 25    | +85             | °C    |                 |

| 2 | Positive Supply                              | $V_{DD}$          | 3.0             | 3.3   | 3.6             | V     |                 |

| 3 | Input High Voltage                           | $V_{\mathrm{IH}}$ | $0.7 V_{DD}$    |       | V <sub>DD</sub> | V     |                 |

| 4 | Input High Voltage on 5 V Tolerant<br>Inputs | V <sub>IH</sub>   |                 |       | 5.5             | V     |                 |

| 5 | Input Low Voltage                            | $V_{IL}$          | V <sub>SS</sub> |       | $0.3 V_{DD}$    | V     |                 |

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

## DC Electrical Characteristics - Voltages are with respect to ground ( $V_{ss}$ ) unless otherwise stated.

|    |        | Characteristics        | Sym.              | Min.         | Typ.‡ | Max.        | Units | Test Conditions                                   |

|----|--------|------------------------|-------------------|--------------|-------|-------------|-------|---------------------------------------------------|

| 1  | I      | Supply Current         | I <sub>DD</sub>   |              | 4     | 7           | mA    | Outputs unloaded                                  |

| 2  | N      | Input High Voltage     | $V_{\mathrm{IH}}$ | $0.7 V_{DD}$ |       |             | V     |                                                   |

| 3  | P<br>U | Input Low Voltage      | V <sub>IL</sub>   |              |       | $0.3V_{DD}$ | V     |                                                   |

| 4  | Т      | Input Leakage          | I <sub>IL</sub>   |              |       | 5           | μΑ    | $V_{\rm I}$ between $V_{\rm SS}$ and $V_{\rm DD}$ |

| 5  | S      | Input Pin Capacitance  | CI                |              |       | 10          | pF    |                                                   |

| 6  | 0      | Output High Voltage    | V <sub>OH</sub>   | $0.8V_{DD}$  |       |             | V     | $I_{OH} = 10 \text{ mA}$                          |

| 7  | O<br>U | Output High Current    | I <sub>OH</sub>   | 10           |       |             | mA    | Sourcing. V <sub>OH</sub> =0.8V <sub>DD</sub>     |

| 8  | T<br>P | Output Low Voltage     | V <sub>OL</sub>   |              |       | 0.4         | V     | $I_{OL} = 5 \text{ mA}$                           |

| 9  | P<br>U | Output Low Current     | I <sub>OL</sub>   | 5            |       |             | mA    | Sinking. $V_{OL} = 0.4 V$                         |

| 10 | T<br>S | High Impedance Leakage | I <sub>OZ</sub>   |              |       | 5           | μΑ    | $V_{\rm O}$ between $V_{\rm SS}$ and $V_{\rm DD}$ |

| 11 | 3      | Output Pin Capacitance | Co                |              |       | 10          | pF    |                                                   |

<sup>‡</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

|   | Characteristics                       | Sym.            | Level               | Units | Test Conditions |

|---|---------------------------------------|-----------------|---------------------|-------|-----------------|

| 1 | CMOS Threshold Voltage                | $V_{\text{TT}}$ | $0.5 V_{\text{DD}}$ | V     |                 |

| 2 | CMOS Rise/Fall Threshold Voltage high | $V_{\text{HM}}$ | $0.7 V_{DD}$        | V     |                 |

| 3 | CMOS Rise/Fall Threshold Voltage low  | $V_{LM}$        | $0.3V_{\text{DD}}$  | V     |                 |

## AC Electrical Characteristics – Timing Parameter Measurement Voltage Levels

## AC Electrical Characteristics<sup>†</sup> - ST-BUS Timing Voltages are with respect to ground (VSS) unless otherwise stated.

|    | Characteristics            | Sym.              | Min. | Тур.‡ | Max. | Units | Test Conditions        |

|----|----------------------------|-------------------|------|-------|------|-------|------------------------|

| 1  | Frame Pulse width          | $t_{\rm F0iW}$    |      | 244   |      | ns    |                        |

| 2  | Frame Pulse setup time     | $t_{\rm F0iS}$    | 10   |       | 190  | ns    |                        |

| 3  | Frame Pulse hold time      | $t_{\rm F0iH}$    | 20   |       | 190  | ns    |                        |

| 4  | STo delay Active to Active | t <sub>SAA</sub>  |      |       | 55   | ns    | C <sub>L</sub> =150 pF |

| 5  | STi setup time             | t <sub>stis</sub> | 20   |       |      | ns    |                        |

| 6  | STi hold time              | t <sub>STiH</sub> | 20   |       |      | ns    |                        |

| 7  | Clock period               | $t_{C4i}$         | 200  | 244   | 300  | ns    |                        |

| 8  | CK Input Low               | $t_{\rm CL}$      | 85   | 122   | 150  | ns    |                        |

| 9  | CK Input High              | $t_{\rm CH}$      | 85   | 122   | 150  | ns    |                        |

| 10 | Clock Rise/Fall Time       | $t_{r,t_f}$       |      |       | 10   | ns    |                        |

Timing is over recommended temperature & power supply voltages (V<sub>DD</sub>=5V±5%, V<sub>SS</sub>=0V, T<sub>A</sub>=-40 to 85°C).

Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

Figure 12 - ST-BUS Timing

## AC Electrical Characteristics<sup>†</sup> - GCI Timing Voltages are with respect to ground (VSS) unless otherwise stated.

|   | Characteristics                   | Sym.                     | Min. | Тур.‡ | Max. | Units | Test Conditions        |

|---|-----------------------------------|--------------------------|------|-------|------|-------|------------------------|

| 1 | Clock Period                      | t <sub>C4i</sub>         | 150  | 244   | 300  | ns    |                        |

| 2 | Pulse Width                       | $t_{\rm CL}, t_{\rm CH}$ | 73   | 122   | 150  | ns    |                        |

| 3 | Frame Width High                  | t <sub>WFH</sub>         |      | 244   |      | ns    |                        |

| 4 | Frame Setup                       | t <sub>F0iS</sub>        | 10   |       | 190  | ns    |                        |

| 5 | Frame Hold                        | $t_{\rm F0iH}$           | 20   |       | 190  | ns    |                        |

| 6 | Data Delay/Clock Active to Active | t <sub>DAA</sub>         |      |       | 55   | ns    | C <sub>L</sub> =150 pF |

| 7 | Serial Input Setup                | t <sub>STiS</sub>        | 20   |       |      | ns    |                        |

| 8 | Serial Input Hold                 | t <sub>STiH</sub>        | 20   |       |      | ns    |                        |

| 9 | Clock Rise/Fall Time              | $t_{r,t_f}$              |      |       | 10   | ns    |                        |

† Timing is over recommended temperature & power supply voltages (V<sub>DD</sub>=3.3V±5%, V<sub>SS</sub>=0V, T<sub>A</sub>=-40 to 85°C).

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

Figure 13 - GCI Timing

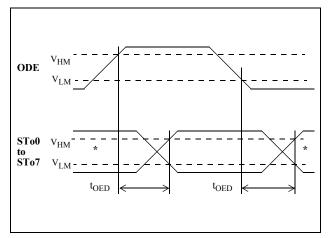

## AC Electrical Characteristics<sup>†</sup> - Serial Streams for ST-BUS and GCI Backplanes

|   |        | Characteristics                 | Sym.             | Min. | Typ.‡ | Max. | Units | Test Conditions                               |

|---|--------|---------------------------------|------------------|------|-------|------|-------|-----------------------------------------------|

| 1 | 0      | STo0/7 Delay - Active to High Z | t <sub>SAZ</sub> |      |       | 55   | ns    | $R_L=1 \text{ K}\Omega^*, C_L=150 \text{ pF}$ |

| 2 | T      | STo0/7 Delay - High Z to Active | t <sub>SZA</sub> |      |       | 55   | ns    | C <sub>L</sub> =150 pF                        |

| 3 | P<br>U | Output Driver Enable Delay      | t <sub>OED</sub> |      |       | 50   | ns    | $R_L=1 \text{ K}\Omega^*, C_L=150 \text{ pF}$ |

| 4 | T<br>S | CSTo Output Delay               | t <sub>XCD</sub> |      |       | 55   | ns    | C <sub>L</sub> =150 pF                        |

† Timing is over recommended temperature & power supply voltages.

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

\* High Impedance is measured by pulling to the appropriate rail with R<sub>L</sub>, with timing corrected to cancel time taken to discharge C<sub>L</sub>.

Figure 15 - Output Driver Enable

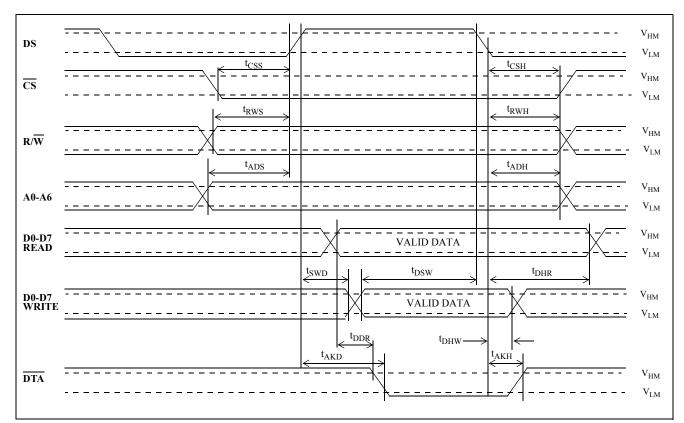

# AC Electrical Characteristics<sup>†</sup>- Microprocessor Bus Voltages are with respect to ground (VSS) unless otherwise stated .

|    | Characteristics                                                                                                                         | Sym.                        | Min. | Typ.‡                    | Max.                        | Units                | Test Conditions                                                                   |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|--------------------------|-----------------------------|----------------------|-----------------------------------------------------------------------------------|

| 1  | CS Setup from DS rising                                                                                                                 | t <sub>CSS</sub>            | 0    |                          |                             | ns                   |                                                                                   |

| 2  | $R/\overline{W}$ Setup from DS rising                                                                                                   | t <sub>RWS</sub>            | 5    |                          |                             | ns                   |                                                                                   |

| 3  | Add setup from DS rising                                                                                                                | $t_{ADS}$                   | 5    |                          |                             | ns                   |                                                                                   |

| 4  | $\overline{\text{CS}}$ hold after DS falling                                                                                            | $\mathbf{t}_{\mathrm{CSH}}$ | 0    |                          |                             | ns                   |                                                                                   |

| 5  | $R/\overline{W}$ hold after DS falling                                                                                                  | $\mathbf{t}_{\mathrm{RWH}}$ | 5    |                          |                             | ns                   |                                                                                   |

| 6  | Add hold after DS falling                                                                                                               | $\mathbf{t}_{\mathrm{ADH}}$ | 8    |                          |                             | ns                   |                                                                                   |

| 7  | Data setup from DTA Low on Read                                                                                                         | t <sub>DDR</sub>            | 0    |                          |                             | ns                   | C <sub>L</sub> =150 pF                                                            |

| 8  | Data hold on read                                                                                                                       | t <sub>DHR</sub>            | 10   |                          | 90                          | ns                   | $\begin{array}{l} R_L = 1 \text{ K}\Omega^*, \\ C_L = 150 \text{ pF} \end{array}$ |

| 9  | Data setup on write (fast write)                                                                                                        | t <sub>DSW</sub>            | 0    | 25                       |                             | ns                   |                                                                                   |

| 10 | Valid Data Delay on write<br>(slow write)                                                                                               | $t_{\rm SWD}$               |      |                          | 122                         | ns                   |                                                                                   |

| 11 | Data hold on write                                                                                                                      | t <sub>DHW</sub>            | 5    | 10                       |                             | ns                   |                                                                                   |

| 12 | Acknowledgment Delay:<br>Reading Data Memory<br>Reading/Writing Conn. Memory<br>Writing to Control Register<br>Reading Control Register | t <sub>AKD</sub>            |      | 560<br>62/30<br>25<br>52 | 1220<br>120/53<br>65<br>120 | ns<br>ns<br>ns<br>ns | C <sub>L</sub> =150 pF                                                            |

| 13 | Acknowledgment Hold Time                                                                                                                | $t_{\rm AKH}$               |      | 50                       | 80                          | ns                   | $\begin{array}{l} R_L = 1 \text{ K}\Omega^*, \\ C_L = 150 \text{ pF} \end{array}$ |

<sup>†</sup> Timing is over recommended temperature & power supply voltages.

<sup>‡</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

<sup>\*</sup> High Impedance is measured by pulling to the appropriate rail with R<sub>L</sub>, with timing corrected to cancel time taken to discharge C<sub>L</sub>.

Figure 16 - Motorola Non-Multiplexed Bus Timing

|        | Control Di | imensions | Altern. Dimensions |        |  |  |  |

|--------|------------|-----------|--------------------|--------|--|--|--|

| Symbol | in inc     | hes       | in milli           | metres |  |  |  |

|        | MIN        | MAX       | MIN                | MAX    |  |  |  |

| А      | 0.165      | 0.180     | 4.19               | 4.57   |  |  |  |

| A1     | 0.090      | 0.120     | 2.29               | 3.05   |  |  |  |

| A2     | 0.062      | 0.083     | 1.57               | 2.11   |  |  |  |

| Α3     | 0.042      | 0.056     | 1.07               | 1.42   |  |  |  |

| Α4     | 0.020      |           | 0.51               | -      |  |  |  |

| D      | 0.685      | 0.695     | 17.40              | 17.65  |  |  |  |

| D1     | 0.650      | 0.656     | 16.51              | 16.66  |  |  |  |

| D2     | 0.291      | 0.319     | 7.39               | 8.10   |  |  |  |

| Е      | 0.685      | 0.695     | 17.40              | 17.65  |  |  |  |

| E1     | 0.650      | 0.656     | 16.51              | 16.66  |  |  |  |

| E2     | 0.291      | 0.319     | 7.39               | 8.10   |  |  |  |

| В      | 0.026      | 0.032     | 0.66               | 0.81   |  |  |  |

| b      | 0.013      | 0.021     | 0.33               | 0.53   |  |  |  |

| е      | 0.050      | BSC       | 1.27 BSC           |        |  |  |  |

|        |            | Pin fea   | otures             |        |  |  |  |

| ND     |            |           |                    |        |  |  |  |

| NE     |            | 11        |                    |        |  |  |  |

| Ν      |            | 44        | t                  |        |  |  |  |

| Note   |            | Squo      | ore                |        |  |  |  |

| Confor | ms to J    | EDEC MS   |                    | lss. A |  |  |  |

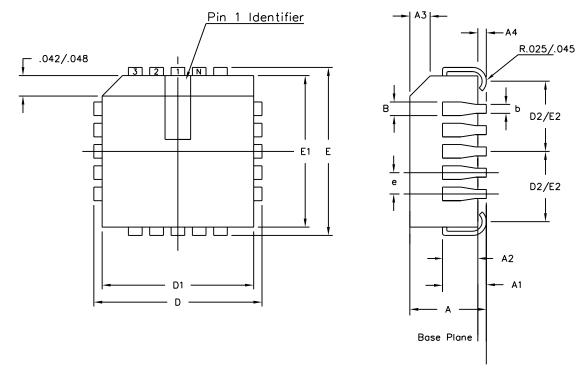

#### Notes:

Seating Plane

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982

- 2. Dimensions D1 and E1 do not include mould protrusions. Allowable mould protrusion is 0.010" per side. Dimensions D1 and E1 include mould protrusion mismatch and are determined at the parting line, that is D1 and E1 are measured at the extreme material condition at the upper or lower parting line.

- 3. Controlling dimensions in Inches.

- 4. "N" is the number of terminals.

- 5. Not To Scale

- 6. Dimension R required for 120° minimum bend.

| © Zarlink Semiconductor 2002 All rights reserved. |         |         |         |               |                        | Package Code QA     |

|---------------------------------------------------|---------|---------|---------|---------------|------------------------|---------------------|

| ISSUE                                             | 1       | 2       | 3       |               | Previous package codes | Package Outline for |

| ACN                                               | 5958    | 207470  | 213094  | SEMICONDUCTOR |                        | 44 lead PLCC        |

| DATE                                              | 15Aug94 | 10Sep99 | 15Jul02 |               | ,                      |                     |

| APPRD.                                            |         |         |         |               |                        | GPD00003            |

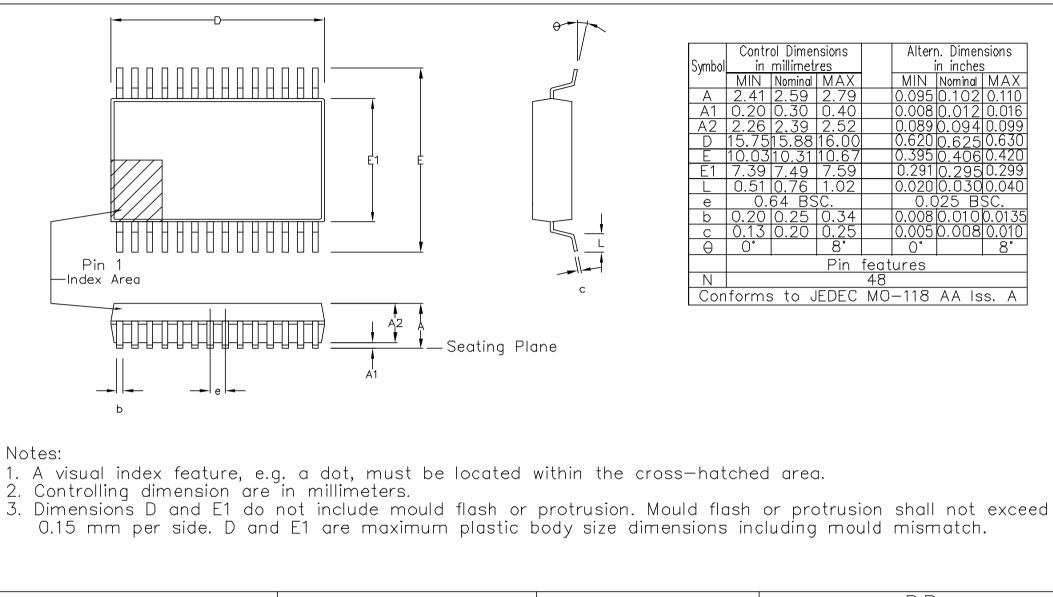

| © Zarlink Semiconductor 2003 All rights reserved. |          |  |  | <br>_            |                  |       | Package Code              |    |

|---------------------------------------------------|----------|--|--|------------------|------------------|-------|---------------------------|----|

| ISSUE                                             | 1        |  |  |                  | Previous package | codes | Package Outline for 48 le | ad |

| ACN                                               | 213915   |  |  | SEMICONDUCTOR    |                  | Ń     | SSOP (300 mil Body Width  |    |

| DATE                                              | 13-01-03 |  |  | 3E MILEOR DOCTOR |                  |       |                           |    |

| APPRD.                                            |          |  |  |                  |                  |       | GPD00816                  |    |

# For more information about all Zarlink products visit our Web Site at

## www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

«JONHON» (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«FORSTAR» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный) Факс: 8 (812) 320-03-32 Электронная почта: ocean@oceanchips.ru Web: http://oceanchips.ru/ Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А