PT7C4563

## Real-time Clock Module (I<sup>2</sup>C Bus)

## Features

- Using external 32.768kHz quartz crystal

- Supports I<sup>2</sup>C-Bus's high speed mode (400 kHz)

- Includes time (Hour/Minute/Second) and calendar (Year/Month/Date/Day) counter functions (BCD code)

- Programmable square wave output signal

- Oscillator stop flag

- Low backup current: typ. 400nA at  $V_{DD}$ =3.0V and  $T_A$ =25 °C

- Operating range: 1.3V to 5.5V

## Description

The PT7C4563 serial real-time clock is a low-power clock/calendar with a programmable square-wave output.

Address and data are transferred serially via a 2-wire bidirectional bus. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in the 24hour format indicator.

Table 1 shows the basic functions of PT7C4563. More details are shown in section: overview of functions.

| Item |              | Fun                         | ction             | PT7C4563               |

|------|--------------|-----------------------------|-------------------|------------------------|

|      |              | Source: Crystal             | : 32.768kHz       | $\checkmark$           |

| 1    | Oscillator   | Oscillator enabl            | e/disable         | -                      |

|      |              | Oscillator fail detect      |                   | √                      |

|      | Time         | Time display                | 12-hour           | -                      |

| 2    |              | Time display                | 24-hour           | √                      |

| Z    |              | Century bit                 |                   | √                      |

|      |              | Time count cha              | in enable/disable | -                      |

| 3    | Interrupt    | Alarm interrupt             |                   | √                      |

| 4    | Programmable | square wave outp            | out (Hz)          | 1, 32, 1.024k, 32.768k |

| 5    | Communicati  | 2-wire I <sup>2</sup> C bus |                   | √                      |

| 5    | on           | Burst mode                  |                   | -                      |

#### **Table 1.** Basic functions of PT7C4563

All trademarks are property of their respective owners. 2016-10-0003

PT7C4563

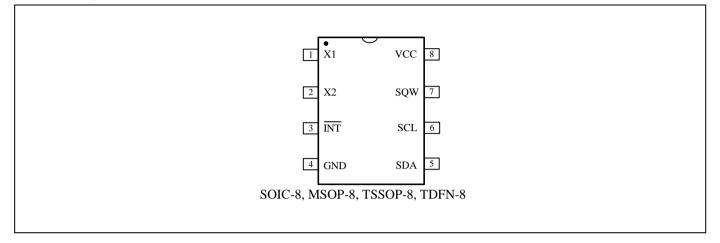

# **Pin Configuration**

# **Pin Description**

| Pin no. | Pin | Туре | Description                                                                                                                                                               |

|---------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | X1  | Ι    | Oscillator Circuit Input. Together with X2, 32.768kHz crystal is connected between them.                                                                                  |

| 2       | X2  | 0    | Oscillator Circuit Output. Together with X1, 32.768kHz crystal is connected between them.                                                                                 |

| 3       | INT | 0    | Interrupt Output. Open drain, active low.                                                                                                                                 |

| 4       | GND | Р    | Ground.                                                                                                                                                                   |

| 5       | SDA | I/O  | <b>Serial Data Input/Output.</b> SDA is the input/output pin for the 2-wire serial interface. The SDA pin is open-drain output and requires an external pull-up resistor. |

| 6       | SCL | Ι    | Serial Clock Input. SCL is used to synchronize data movement on the I <sup>2</sup> C serial interface.                                                                    |

| 7       | SQW | 0    | <b>Clock Output.</b> Open drain. Four frequencies selectable: 32.768k, 1.024k, 32, 1Hz when SQWE bit is set to 1.                                                         |

| 8       | VCC | Р    | Power.                                                                                                                                                                    |

PT7C4563

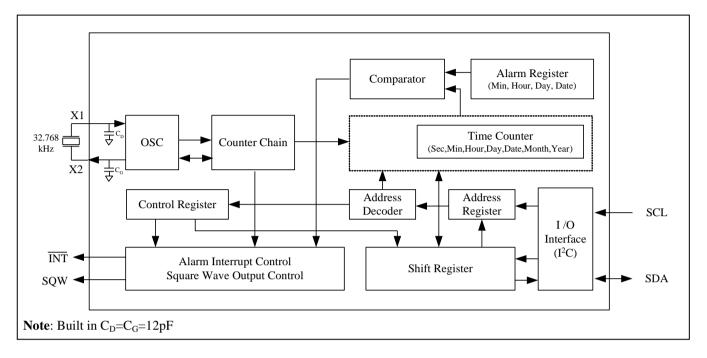

# **Function Block**

# **Maximum Ratings**

| Storage Temperature                             | 65°Cto +150°C  |

|-------------------------------------------------|----------------|

| Ambient Temperature with Power Applied          | -40°Cto +85°C  |

| Supply Voltage to Ground Potential (Vcc to GND) | -0.3V to +6.5V |

| DC Input (All Other Inputs except Vcc & GND)    |                |

| DC Output Voltage (SDA, /INTA, /INTB pins)      | -0.3V to +6.5V |

| Power Dissipation                               |                |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Recommended Operating Conditions**

| Symbol          | Description           | Min.                | Тур. | Max.                 | Unit |

|-----------------|-----------------------|---------------------|------|----------------------|------|

| V <sub>CC</sub> | Power voltage         | 1.3                 | -    | 5.5                  |      |

| V <sub>IH</sub> | Input high level      | 0.7 V <sub>CC</sub> | -    | V <sub>CC</sub> +0.3 | v    |

| V <sub>IL</sub> | Input low level       | -0.3                | -    | 0.3 V <sub>CC</sub>  |      |

| T <sub>A</sub>  | Operating temperature | -40                 | -    | 85                   | C    |

PERICOM<sup>®</sup>

# **DC Electrical Characteristics**

## Unless otherwise specified, GND =0V, $V_{CC}$ = 1.3 ~ 5.5 V, $T_A$ = -40 °C to +85 °C, $f_{OSC}$ = 32.768kHz.

| Sym.                                     | Description                             | Pin             | Conditions                                                 |                                  | Min.         | Тур. | Max.            | Unit |

|------------------------------------------|-----------------------------------------|-----------------|------------------------------------------------------------|----------------------------------|--------------|------|-----------------|------|

|                                          | C                                       | V               | Interface inactive. $T_A = 25 \ ^{\circ}C^{1)}$            |                                  | 1.1          | -    | 5.5             |      |

| V                                        | Supply voltage                          | V <sub>CC</sub> | Interface active. $f_{SCL} = 400 \text{kHz}$ ,             | $T_{\rm A} = 25 \ {\rm C}^{(1)}$ | 1.3          | -    | 5.5             | v    |

| V <sub>CC</sub>                          | Supply voltage for clock data integrity | V <sub>CC</sub> | -                                                          |                                  |              |      |                 | v    |

|                                          |                                         |                 | Interface active                                           | $f_{SCL} = 400 kHz$              | -            | -    | 35              |      |

|                                          |                                         |                 | Interface active                                           | $f_{SCL} = 100 kHz$              | -            | -    | 15              | μA   |

|                                          |                                         | V <sub>CC</sub> | Interface inactive ( $f_{SCL} = 0Hz$ ),                    | $V_{\rm CC} = 5.0 V$             | -            | 450  | 850             | nA   |

| I <sub>CC</sub>                          | Supply current                          |                 | pin 7 disabled $T_A$ =-40~85 °C                            | $V_{\rm CC} = 3.0 V$             | -            | 400  | 650             |      |

|                                          |                                         |                 | Interface inactive ( $f_{SCL} = 0Hz$ ),                    | $V_{\rm CC} = 5.0 V$             | -            | 650  | 1200            |      |

|                                          |                                         |                 | pin 7 enabled at 32kHz T <sub>A</sub> =-40~85 $^{\circ}$ C | $V_{CC} = 3.0 V$                 | -            | 600  | 850             | nA   |

| V <sub>IL1</sub>                         | Low-level input voltage                 | SCL             | -                                                          | •                                | 0            | -    | $0.3V_{CC}$     | v    |

| $V_{\rm IH1}$                            | High-level input voltage                | SCL             | -                                                          |                                  | $0.7 V_{CC}$ | -    | V <sub>CC</sub> | v    |

| т                                        | Low level output voltage                | SDA             | $V_{OL} = 0.4V, V_{CC} = 5V$                               |                                  | -3           | -    | -               | mA   |

| I <sub>OL</sub> Low-level output voltage |                                         | /INT, SQW       | $V_{OL} = 0.4 V, V_{CC} = 5 V$                             |                                  | -1           | -    | -               | ША   |

| I <sub>IL</sub>                          | Input leakage current                   | SCL             | -                                                          |                                  |              | -    | ±1              | μΑ   |

| I <sub>OZ</sub>                          | Output current when OFF                 | -               | -                                                          |                                  | -            | -    | ±1              | μΑ   |

Note: 1) For reliable oscillator start-up at power-up:  $V_{CC(min)power-up} = V_{CC(min)} + 0.3 \text{ V}.$

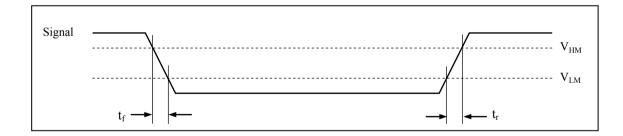

# **AC Electrical Characteristics**

| Sym             | Description                               | Value               | Unit |

|-----------------|-------------------------------------------|---------------------|------|

| V <sub>HM</sub> | Rising and falling threshold voltage high | 0.8 V <sub>CC</sub> | V    |

| V <sub>HL</sub> | Rising and falling threshold voltage low  | 0.2 V <sub>CC</sub> | V    |

PT7C4563

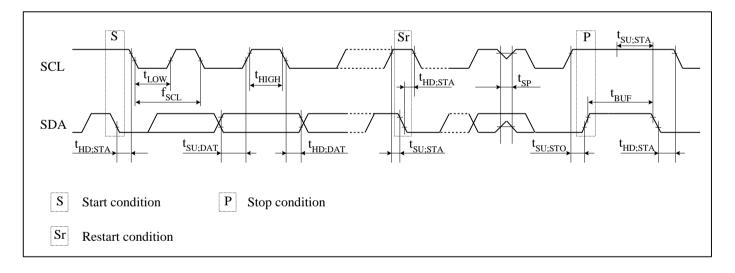

# Over the operating range

| Symbol               | Item                                             | Min. | Typ. | Max. | Unit |

|----------------------|--------------------------------------------------|------|------|------|------|

| f <sub>SCL</sub>     | SCL clock frequency                              | -    | -    | 400  | kHz  |

| t <sub>SU;STA</sub>  | START condition set-up time                      | 0.6  | -    | -    | μs   |

| t <sub>HD;STA</sub>  | START condition hold time                        | 0.6  | -    | -    | μs   |

| t <sub>SU;DAT</sub>  | Data set-up time (RTC read/write)                | 200  | -    | -    | ns   |

| t <sub>HD;DAT1</sub> | Data hold time (RTC write)                       | 35   | -    | -    | ns   |

| t <sub>HD;DAT2</sub> | Data hold time (RTC read)                        | 0    | -    | -    | μs   |

| t <sub>SU;STO</sub>  | STOP condition setup time                        | 0.6  | -    | -    | μs   |

| t <sub>BUF</sub>     | Bus idle time between a START and STOP condition | 1.3  | -    | -    | μs   |

| t <sub>LOW</sub>     | When SCL = "L"                                   | 1.3  | -    | -    | μs   |

| t <sub>HIGH</sub>    | When SCL = "H"                                   | 0.6  | -    | -    | μs   |

| t <sub>r</sub>       | Rise time for SCL and SDA                        | -    | -    | 0.3  | μs   |

| t <sub>f</sub>       | Fall time for SCL and SDA                        | -    | -    | 0.3  | μs   |

| t <sub>SP</sub> *    | Allowable spike time on bus                      | -    | -    | 50   | ns   |

| C <sub>B</sub>       | Capacitance load for each bus line               | -    | -    | 400  | pF   |

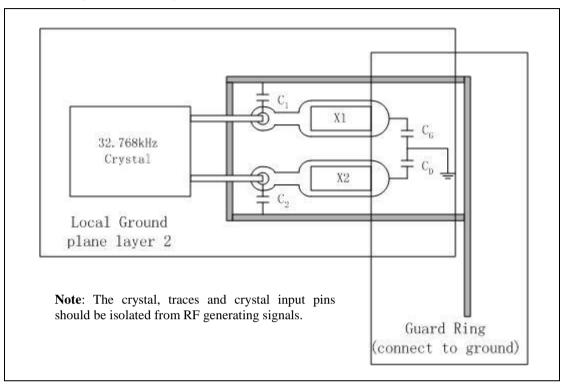

# **Recommended Layout for Crystal**

## **Built-in Capacitors Specifications and Recommended External Capacitors**

| Parameter                           |           | Symbol         | Тур | Unit |

|-------------------------------------|-----------|----------------|-----|------|

| Build-in capacitors                 | X1 to GND | C <sub>G</sub> | 12  | pF   |

| Build-III capacitors                | X2 to GND | C <sub>D</sub> | 12  | pF   |

| Recommended External capacitors for | X1 to GND | $C_1$          | 10  | pF   |

| crystal C <sub>L</sub> =12.5pF      | X2 to GND | $C_2$          | 10  | pF   |

| Recommended External capacitors for | X1 to GND | C <sub>1</sub> | 0   | pF   |

| crystal C <sub>L</sub> =6pF         | X2 to GND | $C_2$          | 0   | pF   |

Note: The frequency of crystal can be optimized by external capacitor C<sub>1</sub> and C<sub>2</sub>, for frequency=32.768Hz, C<sub>1</sub> and C<sub>2</sub> should meet the equation as below:

$Cpar + [(C_1 + C_G)^*(C_2 + C_D)] / [(C_1 + C_G) + (C_2 + C_D)] = C_L$

Cpar is all parasitical capacitor between X1 and X2.

C<sub>L</sub> is crystal's load capacitance.

## **Crystal Specifications**

| Parameter         | Symbol         | Min | Тур    | Max | Unit |

|-------------------|----------------|-----|--------|-----|------|

| Nominal Frequency | f <sub>O</sub> | -   | 32.768 | -   | kHz  |

| Series Resistance | ESR            | -   | -      | 70  | kΩ   |

| Load Capacitance  | C <sub>L</sub> | -   | 6/12.5 | -   | pF   |

# **Function Description**

### **Overview of Functions**

#### 1. Clock function

CPU can read or write data including the year (last two digits), month, date, day, hour, minute, and second. Any (two-digit) year that is a multiple of 4 is treated as a leap year and calculated automatically as such until the year 2100.

#### 2. Alarm function

These devices have one alarm system that outputs interrupt signals from INT for PT7C4563 to CPU when the date, day of the week, hour, minute or second correspond to the setting. Each of them may output interrupt signal separately at a specified time. The alarm may be selectable between on and off for matching alarm or repeating alarm.

#### 3. Programmable square wave output

A square wave output enable bit controls square wave output at pin 7. 4 frequencies are selectable: 1, 32, 1.024k, and 32.768k Hz.

#### 4. Interface with CPU

Data is read and written via the I<sup>2</sup>C bus interface using two signal lines: SCL (clock) and SDA (data).

Since the output of the I/O pin SDA is open drain, a pull-up resistor should be used on the circuit board if the CPU output I/O is also open drain.

The SCL's maximum clock frequency is 400 kHz, which supports the I<sup>2</sup>C bus's high-speed mode.

#### 5. Oscillator fail detect

When oscillator fail, OSF bit will be set.

Registers

#### 1. Allocation of registers

| Addr.    | Function (time range     | Register definition |       |       |       |           |       |                   |            |  |

|----------|--------------------------|---------------------|-------|-------|-------|-----------|-------|-------------------|------------|--|

| (hex) *1 | BCD format)              | Bit 7               | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1             | Bit 0      |  |

| 00       | Control/status 1         | ×                   | ×     | ×     | ×     | ×         | ×     | ×                 | ×          |  |

| 01       | Control/status 2         | ×                   | ×     | ×     | ×     | $AF^{*2}$ | ×     | AIE <sup>*3</sup> | ×          |  |

| 02       | Seconds (00-59)          | $OSF^{*4}$          | S40   | S20   | S10   | S8        | S4    | S2                | <b>S</b> 1 |  |

| 03       | Minutes (00-59)          | ×                   | M40   | M20   | M10   | M8        | M4    | M2                | M1         |  |

| 04       | Hours (00-23)            | ×                   | ×     | H20   | H10   | H8        | H4    | H2                | H1         |  |

| 05       | Dates (01-31)            | ×                   | ×     | D20   | D10   | D8        | D4    | D2                | D1         |  |

| 06       | Days of the week (00-06) | ×                   | ×     | ×     | ×     | ×         | W4    | W2                | W1         |  |

| 07       | Months (01-12)           | ×                   | ×     | ×     | MO10  | MO8       | MO4   | MO2               | MO1        |  |

| 08       | Years (00-99)            | Y80                 | Y40   | Y20   | Y10   | Y8        | Y4    | Y2                | Y1         |  |

| 09       | Alarm: Minutes (00-59)   | AE <sup>*5</sup>    | M40   | M20   | M10   | M8        | M4    | M2                | M1         |  |

| 0A       | Alarm: Hours (01-12)     | AE <sup>*5</sup>    | ×     | H20   | H10   | H8        | H4    | H2                | H1         |  |

| 0B       | Alarm: Dates (01-31)     | AE <sup>*5</sup>    | ×     | D20   | D10   | D8        | D4    | D2                | D1         |  |

| 0C       | Alarm: Weekday (00-06)   | AE <sup>*5</sup>    | ×     | ×     | ×     | ×         | W4    | W2                | W1         |  |

| 0D       | SQW control              | SQWE                | ×     | ×     | ×     | ×         | ×     | RS1               | RS0        |  |

Caution points:

\*1. PT7C4563 uses 8 bits for address. For excess 0FH address, PT7C4563 will not respond.

\*2. Alarm interrupt flag bits.

\*3. Alarm interrupt enable bits.

\*4. Oscillator fail indicates. Indicate clock integrity.

\*5. Alarm enable bit. Alarm will be active when related time is matching if AE = 0.

\*6. All bits marked with "×" are not implemented.

PT7C4563

#### 2. Control and status register

| Addr.<br>(hex) | Description      | D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

|----------------|------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 00             | Control/status 1 | ×         | ×         | ×         | ×         | ×         | ×         | ×         | ×         |

| 00             | (default)        | 0         | Undefined | 0         | Undefined | 1         | Undefined | Undefined | Undefined |

| 01             | Control/status 2 | ×         | ×         | ×         | ×         | AF        | ×         | AIE       | ×         |

| 01             | (default)        | Undefined | Undefined | Undefined | 0         | Undefined | Undefined | 0         | 0         |

| 0D             | SQW control      | SQWE      | ×         | ×         | ×         | ×         | ×         | RS1       | RS0       |

| 012            | (default)        | 1         | Undefined | Undefined | Undefined | Undefined | Undefined | 0         | 0         |

#### a) Alarm Interrupt

#### • **AIE:** Alarm Interrupt Enable bit.

| AIE          | Data | Description              |         |

|--------------|------|--------------------------|---------|

| Read / Write | 0    | Alarm interrupt disabled | Default |

|              | 1    | Alarm interrupt enabled  |         |

#### • **AF:** Alarm Flag

| AF    | Data | Description                  |

|-------|------|------------------------------|

| Read  | 0    | Alarm flag inactive          |

| Read  | 1    | Alarm flag active            |

| Write | 0    | Alarm flag is cleared        |

| wille | 1    | Alarm flag remains unchanged |

#### b) SQW control

#### • **SQWE:** SQW output clock enable bit.

| SQWE         | Data                                                                  | Description                 |         |  |  |  |  |

|--------------|-----------------------------------------------------------------------|-----------------------------|---------|--|--|--|--|

| Read / Write | 0 the SQW output is inhibited and SQW output is set to high-impedance |                             |         |  |  |  |  |

| Keau / Wille | 1                                                                     | the SQW output is activated | Default |  |  |  |  |

### • **RS1, RS0:** SQW output frequency select.

| RS1, RS0     | Data |         | SQW output freq. (Hz) |       |

|--------------|------|---------|-----------------------|-------|

|              | 00   | 32.768k | Def                   | fault |

| Read / Write | 01   | 1.024k  |                       |       |

| Keau / Wille | 10   | 32      |                       |       |

|              | 11   | 1       |                       |       |

PT7C4563

#### 3. Time Counter

Time digit display (in BCD code):

- Second digits: Range from 00 to 59 and carried to minute digits when incremented from 59 to 00.

- Minute digits: Range from 00 to 59 and carried to hour digits when incremented from 59 to 00.

- Hour digits: See description on the /12, 24 bit. Carried to day and day-of-the-week digits when incremented from 11 p.m. to 12 a.m. or 23 to 00.

| Addr.<br>(hex) | Description | D7                  | D6        | D5        | D4        | D3         | D2        | D1        | D0         |

|----------------|-------------|---------------------|-----------|-----------|-----------|------------|-----------|-----------|------------|

| 02             | Seconds     | $\mathrm{OSF}^{*1}$ | S40       | S20       | S10       | <b>S</b> 8 | S4        | S2        | <b>S</b> 1 |

| 02             | (default)   | 1                   | Undefined | Undefined | Undefined | Undefined  | Undefined | Undefined | Undefined  |

| 03             | Minutes     | ×                   | M40       | M20       | M10       | M8         | M4        | M2        | M1         |

| 05             | (default)   | 0                   | Undefined | Undefined | Undefined | Undefined  | Undefined | Undefined | Undefined  |

| 04             | Hours       | ×                   | ×         | H20       | H10       | H8         | H4        | H2        | H1         |

| 0.             | (default)   | 0                   | 0         | Undefined | Undefined | Undefined  | Undefined | Undefined | Undefined  |

\*1 Note: Indicate clock integrity. When the bit is 1, the clock integrity is no longer guaranteed and the time need be adjusted.

#### 4. Days of the week Counter

The day counter is a divide-by-7 counter that counts from 00 to 06 and up 06 before starting again from 00. Values that correspond to the day of week are user defined but must be sequential (i.e., if 0 equals Sunday, then 1 equals Monday, and so on). Illogical time and date entries result in undefined operation.

| Addr.<br>(hex) | Description      | D7 | D6 | D5 | D4 | D3 | D2        | D1        | D0        |

|----------------|------------------|----|----|----|----|----|-----------|-----------|-----------|

| 06             | Days of the week | ×  | ×  | ×  | ×  | ×  | W4        | W2        | W1        |

| 00             | (default)        | 0  | 0  | 0  | 0  | 0  | Undefined | Undefined | Undefined |

### 5. Calendar Counter

The data format is BCD format.

• Day digits: Range from 1 to 31 (for January, March, May, July, August, October and December).

Range from 1 to 30 (for April, June, September and November).

Range from 1 to 29 (for February in leap years).

Range from 1 to 28 (for February in ordinary years).

Carried to month digits when cycled to 1.

- Month digits: Range from 1 to 12 and carried to year digits when cycled to 1.

- Year digits: Range from 00 to 99 and 00, 04, 08, ..., 92 and 96 are counted as leap years.

| Addr.<br>(hex) | Description | D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

|----------------|-------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 05             | Dates       | ×         | ×         | D20       | D10       | D8        | D4        | D2        | D1        |

| 05             | (default)   | 0         | 0         | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

| 07             | Months      | ×         | ×         | ×         | M10       | M8        | M4        | M2        | M1        |

| 07             | (default)   | Undefined | 0         | 0         | Undefined | Undefined | Undefined | Undefined | Undefined |

| 08             | Years       | Y80       | Y40       | Y20       | Y10       | Y8        | Y4        | Y2        | Y1        |

| 50             | (default)   | Undefined |

PT7C4563

#### 6. Alarm Register

#### PT7C4563: Alarm Register

|           | 0                       |                  |           |           |           |           |           |           |           |

|-----------|-------------------------|------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Addr.     | Description             | D7               | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

| 09        | Alarm: Minutes          | $AE^{*1}$        | M40       | M20       | M10       | M8        | M4        | M2        | M1        |

| 0,7       | (default)               | Undefined        | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

| 0A        | Alarm: Hours            | $AE^{*2}$        | ×         | H20       | H10       | H8        | H4        | H2        | H1        |

| 011       | (default)               | Undefined        | 0         | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

| 0B        | Alarm: Dates            | AE <sup>*3</sup> | ×         | D20       | D10       | D8        | D4        | D2        | D1        |

| 012       | (default)               | Undefined        | 0         | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

| 0C        | Alarm: Weekday          | $AE^{*4}$        | ×         | ×         | ×         | ×         | W4        | W2        | W1        |

| ŰČ        | (default)               | Undefined        | 0         | 0         | 0         | 0         | Undefined | Undefined | Undefined |

| *1 NT / N | Minute elema enchle hit |                  |           |           |           |           |           |           |           |

\*1 Note: Minute alarm enable bit.

\*2 Note: Hour alarm enable bit.

\*3 Note: Date alarm enable bit.

\*4 Note: Weekday alarm enable bit.

## **Alarm Function**

Related register

|    | Function         |       |       |       | Register | definition |            |       |            |

|----|------------------|-------|-------|-------|----------|------------|------------|-------|------------|

|    | Function         | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3      | Bit 2      | Bit 1 | Bit 0      |

| 01 | Control/status 2 | ×     | ×     | ×     | ×        | AF         | ×          | AIE   | ×          |

| 02 | Seconds          | OSF   | S40   | S20   | S10      | <b>S</b> 8 | <b>S</b> 4 | S2    | <b>S</b> 1 |

| 03 | Minutes          | ×     | M40   | M20   | M10      | M8         | M4         | M2    | M1         |

| 04 | Hours            | ×     | ×     | H20   | H10      | H8         | H4         | H2    | H1         |

| 05 | Dates            | ×     | ×     | D20   | D10      | D8         | D4         | D2    | D1         |

| 06 | Days of the week | ×     | ×     | ×     | ×        | ×          | W4         | W2    | W1         |

| 09 | Alarm: Minutes   | AE    | M40   | M20   | M10      | M8         | M4         | M2    | M1         |

| 0A | Alarm: Hours     | AE    | ×     | H20   | H10      | H8         | H4         | H2    | H1         |

| 0B | Alarm: Dates     | AE    | ×     | D20   | D10      | D8         | D4         | D2    | D1         |

| 0C | Alarm: Weekday   | AE    | ×     | ×     | ×        | ×          | W4         | W2    | W1         |

When one or more of these registers are loaded with a valid minute, hour, day or weekday and its corresponding bit Alarm Enable (AE) is logic 0, then that information will be compared with the current minute, hour, day and weekday. When all enabled comparisons first match, the Alarm Flag (AF) is set. AF will remain set until cleared by software. Once AF has been cleared it will only be set again when the time increments to match the alarm condition once more. Alarm registers which have their bit AE at logic 1 will be ignored.

### Communication

#### 1. I<sup>2</sup>C Bus Interface

#### a) Overview of I<sup>2</sup>C-BUS

The I<sup>2</sup>C bus supports bi-directional communications via two signal lines: the SDA (data) line and SCL (clock) line. A combination of these two signals is used to transmit and receive communication start/stop signals, data signals, acknowledge signals, and so on. Both the SCL and SDA signals are held at high level whenever communications are not being performed. The starting and stopping of communications is controlled at the rising edge or falling edge of SDA while SCL is at high level. During data transfers, data changes that occur on the SDA line are performed while the SCL line is at low level, and on the receiving side the data is captured while the SCL line is at high level. In either case, the data is transferred via the SCL line at a rate of one bit per clock pulse. The I<sup>2</sup>C bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a chip select pin, slave addresses are allocated to each device and the receiving device responds to communications only when its slave address the slave address in the received data.

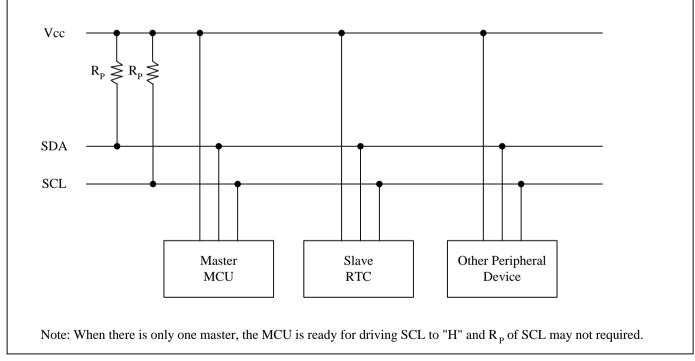

#### b) System Configuration

All ports connected to the  $I^2C$  bus must be either open drain or open collector ports in order to enable AND connections to multiple devices.

SCL and SDA are both connected to the VDD line via a pull-up resistance. Consequently, SCL and SDA are both held at high level when the bus is released (when communication is not being performed).

#### Fig.1 System configuration

PT7C4563

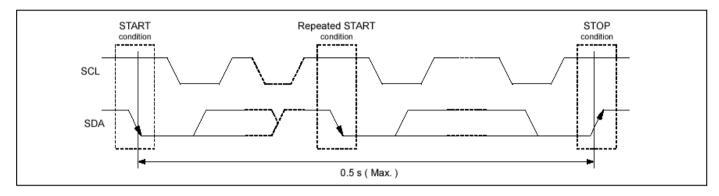

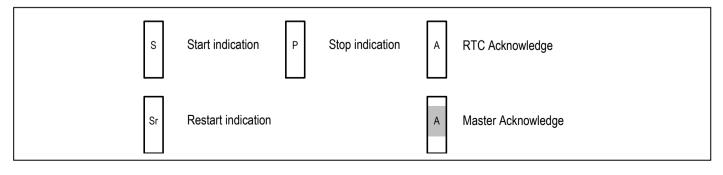

#### c) Starting and Stopping I<sup>2</sup>C Bus Communications

Fig.2 Starting and stopping on I<sup>2</sup>C bus

START condition, repeated START condition, and STOP condition

- START condition

- SDA level changes from high to low while SCL is at high level

- STOP condition

- SDA level changes from low to high while SCL is at high level

- Repeated START condition (RESTART condition)

In some cases, the START condition occurs between a previous START condition and the next STOP condition, in which case the second START condition is distinguished as a RESTART condition. Since the required status is the same as for the START condition, the SDA level changes from high to low while SCL is at high level.

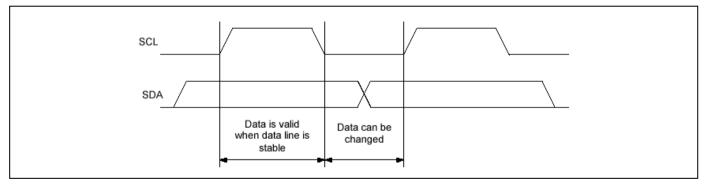

#### d) Data Transfers and Acknowledge Responses during I<sup>2</sup>C-BUS Communication

#### • Data transfers

Data transfers are performed in 8-bit (1 byte) units once the START condition has occurred. There is no limit on the amount (bytes) of data that are transferred between the START condition and STOP condition.

The address auto increment function operates during both write and read operations.

Updating of data on the transmitter (transmitting side)'s SDA line is performed while the SCL line is at low level. The receiver (receiving side) captures data while the SCL line is at high level.

\*Note with caution that if the SDA data is changed while the SCL line is at high level, it will be treated as a START, RESTART, or STOP condition.

#### • Data acknowledge response (ACK signal)

When transferring data, the receiver generates a confirmation response (ACK signal, low active) each time an 8-bit data segment is received. If there is no ACK signal from the receiver, it indicates that normal communication has not been established. (This does not include instances where the master device intentionally does not generate an ACK signal.)

Immediately after the falling edge of the clock pulse corresponding to the 8th bit of data on the SCL line, the transmitter releases the SDA line and the receiver sets the SDA line to low (= acknowledge) level.

After transmitting the ACK signal, if the Master remains the receiver for transfer of the next byte, the SDA is released at the falling edge of the clock corresponding to the 9th bit of data on the SCL line. Data transfer resumes when the Master becomes the transmitter.

When the Master is the receiver, if the Master does not send an ACK signal in response to the last byte sent from the slave, that indicates to the transmitter that data transfer has ended. At that point, the transmitter continues to release the SDA and awaits a STOP condition from the Master.

#### e) Slave Address

The  $I^2C$  bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a chip select pin, slave addresses are allocated to each device.

All communications begin with transmitting the [START condition] + [slave address (+ R/W specification)]. The receiving device responds to this communication only when the specified slave address it has received matches its own slave address. Slave addresses have a fixed length of 7 bits. See table for the details.

An  $R/\overline{W}$  bit is added to each 7-bit slave address during 8-bit transfers.

| Operation | Transfer data |       |       | SI    | ave addre | SS    |       |       | $R/\overline{W}$ bit |

|-----------|---------------|-------|-------|-------|-----------|-------|-------|-------|----------------------|

|           |               | bit 7 | bit 6 | bit 5 | bit 4     | bit 3 | bit 2 | bit 1 | bit 0                |

| Read      | A3 h          | 1     | 0     | 1     | 0         | 0     | 0     | 1     | 1 (= Read)           |

| Write     | A2 h          | 1     | 0     | 1     | 0         | 0     | 0     | 1     | 0 (= Write)          |

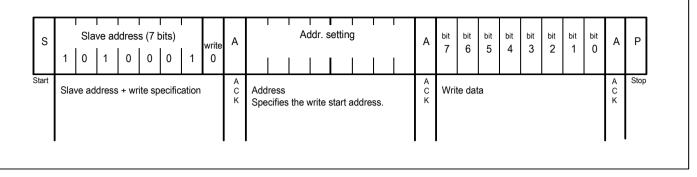

### 2. I<sup>2</sup>C Bus's Basic Transfer Format

a) Write via I<sup>2</sup>C bus

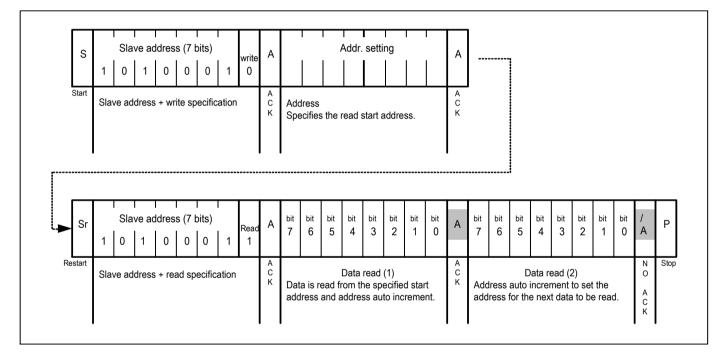

# b) Read via $I^2C$ bus

### • Standard read

#### • Simplified read

| s     | 1   | Sla                                | ve ad | ldres<br>0 | s(71 | bits) | 1           | Read<br>1 | A      | bit<br>7 | <sup>bit</sup> | <sup>bit</sup><br>5                 | bit<br>4 | <sup>bit</sup> | <sup>bit</sup> | <sup>bit</sup> | <sup>bit</sup> | А     | <sup>bit</sup> | <sup>bit</sup> | <sup>bit</sup><br>5        | bit<br>4 | bit<br>3 | <sup>bit</sup> | <sup>bit</sup>        | bit<br>0 | /<br>A | P |

|-------|-----|------------------------------------|-------|------------|------|-------|-------------|-----------|--------|----------|----------------|-------------------------------------|----------|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------------------|----------|----------|----------------|-----------------------|----------|--------|---|

| Start | Sla | Slave address + read specification |       |            |      |       | A<br>C<br>K | by t      | he int | ead fr   | om th<br>addr  | read (<br>le ado<br>ess re<br>nent. | iress    |                |                | A<br>C<br>K    |                | addre | regist         | er au          | ead (2<br>to inc<br>next o | reme     |          | set            | N<br>O<br>A<br>C<br>K | Sto      |        |   |

Note:

1. The above steps are an example of transfers of one or two bytes only. There is no limit to the number of bytes transferred during actual communications.

2. 49H, 4AH are used as test mode address. Customer should not use the addresses.

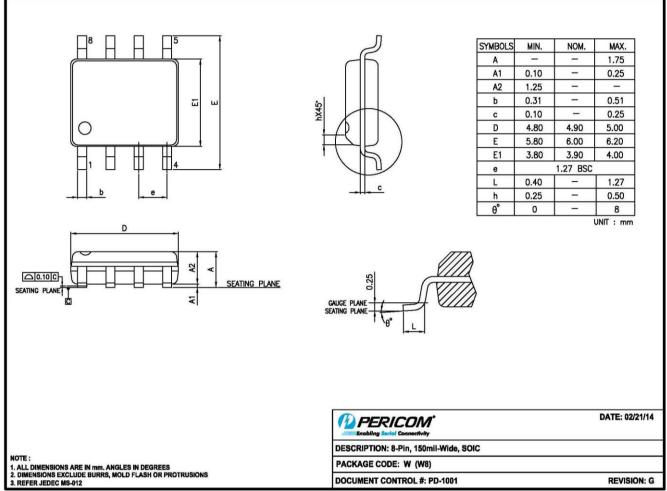

# **Mechanical Information**

W (SOIC-8)

15-0103

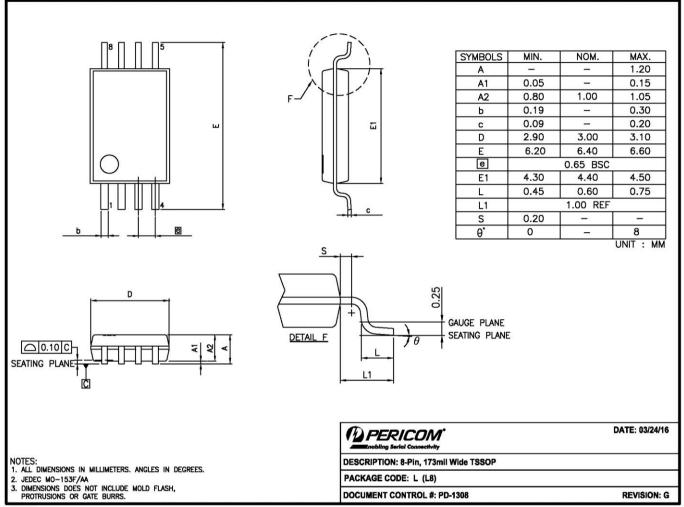

### L (TSSOP-8)

16-0062

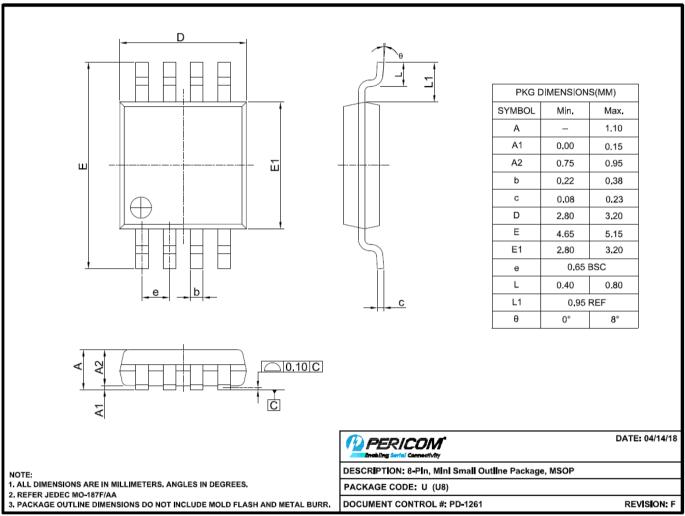

U (MSOP-8)

16-0086

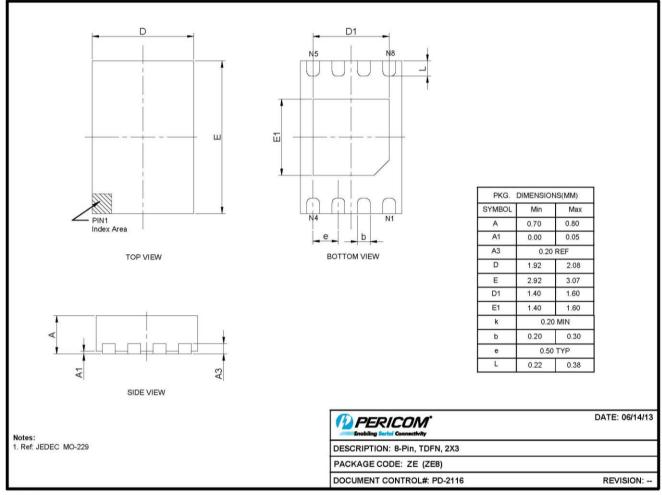

ZE (Lead free and Green 8-Pin TDFN)

13-0155

Note: For latest package info, please check: http://www.pericom.com/support/packaging/packaging-mechanicals-and-thermal-characteristics/

# **Ordering Information**

| Package Code | Package                                             |

|--------------|-----------------------------------------------------|

| W            | 8-Pin, 150mil Wide (SOIC)                           |

| W            | 8-Pin, 150mil Wide (SOIC), Tape/Reel                |

| U            | 8-Pin, Mini Small Outline Package (MSOP)            |

| U            | 8-Pin, Mini Small Outline Package (MSOP), Tape/Reel |

| L            | 8-Pin, 173mil Wide (TSSOP)                          |

| L            | 8-Pin, 173mil Wide (TSSOP), Tape/Reel               |

| ZE           | 8-Pin, 2x3 (TDFN)                                   |

| ZE           | 8-Pin, 2x3 (TDFN), Tape/Reel                        |

|              | W<br>W<br>U<br>U<br>L<br>L<br>ZE                    |

Note

• Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

• E = Pb-free and Green

• Adding X Suffix= Tape/Reel

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

«JONHON» (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«FORSTAR» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный) Факс: 8 (812) 320-03-32 Электронная почта: ocean@oceanchips.ru Web: http://oceanchips.ru/ Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А