# 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

OCTOBER 2006 REV. 1.0.4

# **GENERAL DESCRIPTION**

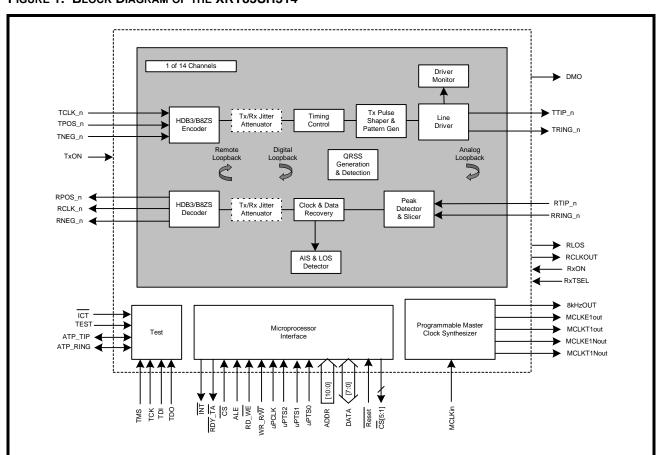

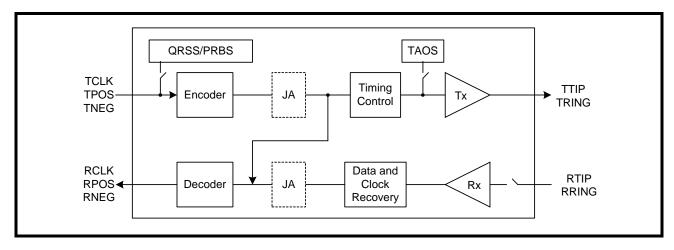

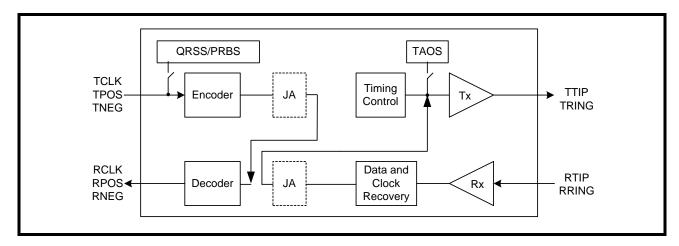

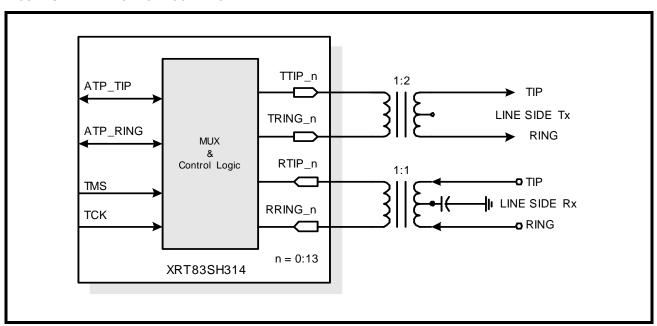

The XRT83SH314 is a fully integrated 14-channel short-haul line interface unit (LIU) that operates from a single 3.3V power supply. Using internal termination, the LIU provides one bill of materials to operate in T1, E1, or J1 mode independently on a per channel basis with minimum external components. The LIU features are programmed through a standard microprocessor interface. EXAR's LIU has patented high impedance circuits that allow the transmitter outputs and receiver inputs to be high impedance when experiencing a power failure or when the LIU is powered off. Key design features within the LIU optimize 1:1 or 1+1 redundancy and non-intrusive monitoring applications to ensure reliability without using relays.

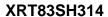

The on-chip clock synthesizer generates T1/E1/J1 clock rates from a selectable external clock frequency and has five output clock references that can be used for external timing (8kHz, 1.544Mhz, 2.048Mhz, nxT1/J1, nxE1).

Additional features include RLOS, a 16-bit LCV counter for each channel, AIS, QRSS/PRBS generation/detection, TAOS, DMO, and diagnostic loopback modes.

# **APPLICATIONS**

- T1 Digital Cross Connects (DSX-1)

- ISDN Primary Rate Interface

- CSU/DSU E1/T1/J1 Interface

- T1/E1/J1 LAN/WAN Routers

- Public Switching Systems and PBX Interfaces

- T1/E1/J1 Multiplexer and Channel Banks

- Integrated Multi-Service Access Platforms (IMAPs)

- Integrated Access Devices (IADs)

- Inverse Multiplexing for ATM (IMA)

- Wireless Base Stations

FIGURE 1. BLOCK DIAGRAM OF THE XRT83SH314

**FEATURES**

# **XRT83SH314**

# 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

- Fully integrated 14-Channel short haul transceivers for T1/J1 (1.544MHz) and E1 (2.048MHz) applications.

- T1/E1/J1 short haul and clock rate are per port selectable through software without changing components.

- Internal Impedance matching on both receive and transmit for 75Ω (E1), 100Ω (T1), 110Ω (J1), and 120Ω (E1) applications are per port selectable through software without changing components.

- Power down on a per channel basis with independent receive and transmit selection.

- Five pre-programmed transmit pulse settings for T1 short haul applications per channel.

- User programable Arbitrary Pulse mode

- On-Chip transmit short-circuit protection and limiting protects line drivers from damage on a per channel basis.

- Selectable Crystal-Less digital jitter attenuators (JA) with 32-Bit or 64-Bit FIFO for the receive or transmit

path

- On-Chip frequency multiplier generates T1 or E1 master clocks from a variety of external clock sources (8, 16, 56, 64, 128, 256kHz and 1X, 2X, 4X, 8X T1 or E1)

- Driver failure monitor output (DMO) alerts of possible system or external component problems.

- Transmit outputs and receive inputs may be "High" impedance for protection or redundancy applications on a per channel basis.

- Support for automatic protection switching.

- 1:1 and 1+1 protection without relays.

- Receive monitor mode handles 0 to 6dB resistive attenuation (flat loss) along with 0 to 6dB cable loss for both T1 and E1.

- Loss of signal (RLOS) according to ITU-T G.775/ETS300233 (E1) and ANSI T1.403 (T1/J1).

- Programmable data stream muting upon RLOS detection.

- On-Chip HDB3/B8ZS encoder/decoder with an internal 16-bit LCV counter for each channel.

- On-Chip digital clock recovery circuit for high input jitter tolerance.

- QRSS/PRBS pattern generator and detection for testing and monitoring.

- Error and bipolar violation insertion and detection.

- Transmit all ones (TAOS) Generators and Detectors

- Supports local analog, remote, digital, and dual loopback modes

- 153mW per channel Power consumption

- Single 3.3V supply operation (3V to 5V I/O tolerant)

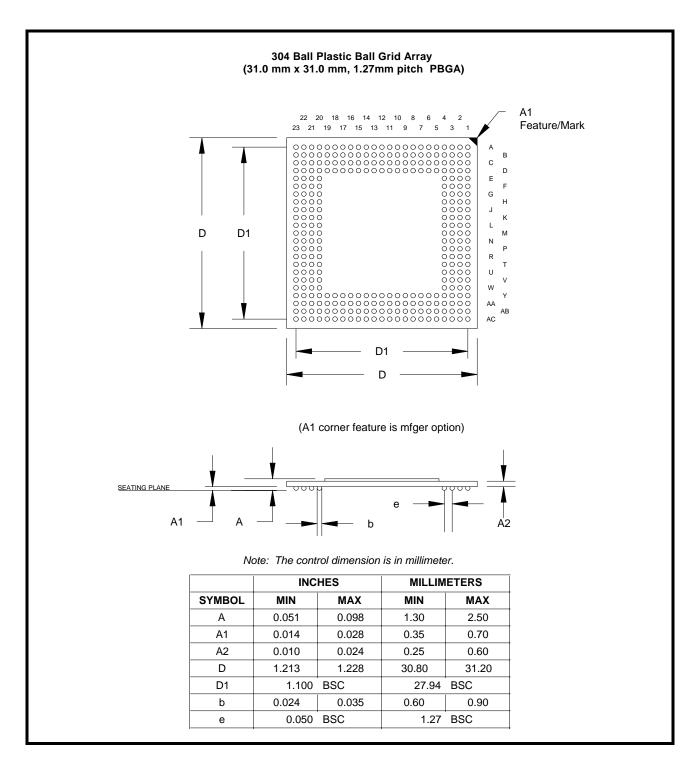

- 304-Pin TBGA package

- -40°C to +85°C Temperature Range

- Supports gapped clocks for mapper/multiplexer applications

### PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE  | OPERATING TEMPERATURE RANGE |

|----------------|---------------|-----------------------------|

| XRT83SH314IB   | 304 Lead TBGA | -40°C to +85°C              |

# PIN OUT OF THE XRT83SH314

|    | 4                          | В          | ပ                         | D                        | Ш      | ш      | Ō      | I       | ٦          | ×                  | _                 | Σ                  | z        | Д       | 8       | -        | n                            | >        | >        | <b>&gt;</b>                                    | AA             | AB              | AC                              |

|----|----------------------------|------------|---------------------------|--------------------------|--------|--------|--------|---------|------------|--------------------|-------------------|--------------------|----------|---------|---------|----------|------------------------------|----------|----------|------------------------------------------------|----------------|-----------------|---------------------------------|

| -  | TDI                        | TCK        | RGND_5                    | RRING_5                  | RTIP_5 | RVDD_4 | RTIP_4 | RRING_4 | RGND_4     | NC                 | S                 | RGND_3             | RRING_3  | RTIP_3  | RVDD_3  | RTIP_2   | RRING_2                      | RGND_2   | RRING_1  | RTIP_1                                         | NC             | RLOS            | NC                              |

| 2  | ICT                        | DGND_DRV   | TRING_5                   | TVDD_5                   | RVDD_5 | RCLK_5 | RCLK_4 | TRING_4 | DVDD_3_4_5 | NC                 | DGND_3_4_5        | TRING_3            | TVDD_3   | RCLK_3  | RCLK_2  | RVDD_2   | TRING_2                      | DVDD_1_2 | RGND_1   | RVDD_1                                         | RCLK_1         | NPCLK           | DVDD_DRV                        |

| 3  | TCLK_5                     | E          | DVDD_PRE                  | ТВО                      | TTIP_5 | RNEG_5 | RNEG_4 | TTIP_4  | TVDD_4     | OVDD_DRV           | GND_BIAS          | TIP_3              | RNEG_3   | RNEG_2  | TTIP_2  | TVDD_2   | DGND_DRV                     | TRING_1  | TIP_1    | RNEG_1                                         | RDY_TA         | D[6]            | D[5]                            |

| 4  | MCLKE1xN                   | TPOS_4     | TPOS_5                    | TEST                     | TMS    | TGND_5 | RPOS_5 | RPOS_4  | TGND_4     | AVDD_BIAS DVDD_DRV | OGND_PREAGND_BIAS | TGND_3             | RPOS_3   | RPOS_2  | TGND_2  | DGND_1_2 | TVDD_1                       | TGND_1   | RPOS_1   | ОМО                                            | [2]0           | D[2]            | D[1]                            |

| 2  | WCLKOUT_T1MCLKINMCLKOUT_E1 | TCLK_4     | TNEG_4                    | TNEG_5                   |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | DVDD_PRE                                       | D[4]           | [0]a            | TCLK_1                          |

| 9  | MCLKINN                    | TCLK_3     | TNEG_3                    | TPOS_3                   |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | D[3]                                           | TPOS_1         | TPOS_2          | TCLK_2                          |

| 7  | ACLKOUT_T1                 | TPOS_6     | TNEG_6                    | TCLK_6                   |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | TNEG_1                                         | TNEG_2         | TNEG_0          | TCLK_0                          |

| 8  | RVDD_6 N                   | MCLKT1xN   | GNDPLL_21                 | еюнт_кнz                 |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | TPOS_0                                         | DGND_DRV       | DGND_PRE        | GNDPLL_11                       |

| 6  | RTIP_6                     | RCLK_6     | RNEG_6 GNDPLL_22GNDPLL_21 | RPOS_6 DVDD_DRVEIGHT_KHZ |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | RPOS_13TGND_13DGND_13_0TGND_0 RPOS_0 GNDPIL_12 | RCLK_0         | RVDD_0          | RTIP_0                          |

| 10 | RRING_6                    | TVDD_6     | RNEG_6                    | RPOS_6                   |        |        |        |         |            |                    |                   | >                  |          |         |         |          |                              |          |          | RPOS_0                                         | RNEG_0         | TVDD_0          | RRING_0                         |

| 1  | RGND_6RRING_               | TRING_6    | TTIP_6                    | TGND_6                   |        |        |        |         |            |                    |                   | VEV                |          |         |         |          |                              |          |          | TGND_0                                         | TTIP_0         | TRING_0         | RGND_0                          |

| 12 | RGND_7                     | TRING_7    | DGND_6_7                  | _9_ddvd                  |        |        |        |         |            |                    |                   | <b>BOTTOM VIEW</b> |          |         |         |          |                              |          |          | DGND_13_0                                      | DVDD_13_0      | TRING_13        | RGND_13 RGND_0RRING_0           |

| 13 | RRING_7                    | TVDD_7     | TIP_7                     | TGND_7                   |        |        |        |         |            |                    |                   | ш                  |          |         |         |          |                              |          |          | TGND_13                                        | TTIP_13        | RCLK_13 TVDD_13 | RTIP_13 RRING_13                |

| 14 | RTIP_7                     | RCLK_7     | RNEG_7                    | RPOS_7                   |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | RPOS_13                                        | RNEG_13        | RCLK_13         | RTIP_13                         |

| 15 | RVDD_7                     | VDDPLL_21  | VDDPLL_22 RNEG_7          | DGND_PRE                 |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | RXTSEL                                         | an_aava        | DGND_UP         | RVDD_13                         |

| 16 | DGND_DRV                   | TCLK_7     | TNEG_7                    | TCLK_10                  |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | TCLK_13                                        | rpos_12TNEG_11 | POS_13VDDPLL_12 | TCLK_11TNEG_13VDDPLL_11 RVDD_13 |

| 17 | TPOS_7                     | TNEG_10    | TCLK_9                    | e_soqt                   |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | TCLK_12                                        | TNEG_11        |                 | TNEG_13                         |

| 18 | TPOS_10                    | TNEG_9     | TNEG_8                    | RD_DS                    |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | A[7]                                           | TPOS_12        | TPOS_11         |                                 |

| 19 | TCLK_8                     | TPOS_8     | ALE_AS                    | <u>cs2</u>               |        |        |        |         |            |                    |                   |                    |          |         |         |          |                              |          |          | A[1]                                           | A[6]           | RXOFF           | TNEG_12                         |

| 70 | WR_RW                      | <u>cse</u> | CS3                       | DVDD_PRE                 | A[9]   | TGND_8 | RPOS_8 | RPOS_9  | 1GND_9     | S                  | DGND_PRE          | TGND_10            | RPOS_10  | RPOS_11 | TGND_11 | TRING_11 | DGND_11_12                   | TGND_12  | RPOS_12  | DVDD_PRE                                       | A[2]           | A[5]            | TXOFF                           |

| 21 | CS4                        | <u>cs1</u> | DVDD_DRV                  | ATP_TIP                  | TVDD_8 | TTIP_8 | RNEG_8 | RNEG_9  | 6_AITT     | ATP_RING           | DGND_DRV          | TTIP_10            | RNEG_10  | RNEG_11 | TIP_11  | TVDD_11  | DVDD_DRVDVDD_11_12DGND_11_12 | TVDD_12  | TTIP_12  | RNEG_12                                        | UPTS0          | [E]Y            | A[4]                            |

| 22 | <u> S</u>                  | RESET      | A[8]                      | TRING_8                  | RVDD_8 | RCLK_8 | RCLK_9 | 6_ddVT  | TRING_9    | NC<br>C            | S<br>S            | TRING_10           | TVDD_10  | RCLK_10 | RCLK_11 | RVDD_11  | DVDD_DRV                     | TRING_12 | RGND_12  | RCLK_12                                        | N<br>N         | UPTS1           | A[0]                            |

| 23 | A[10]                      | S          | RGND_8                    | RRING_8                  | RTIP_8 | RVDD_9 | RTIP_9 | RRING_9 | RGND_9     | 0VDD_8_9_10        | OGND_8_9_10       | RGND_10            | RRING_10 | RTIP_10 | RVDD_10 | RTIP_11  | RRING_11                     | RGND_11  | RRING_12 | RTIP_12                                        | RVDD_12        | DGND_DRV        | UPTS2                           |

# **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                               | 1          |

|-----------------------------------------------------------------------------------|------------|

| APPLICATIONS                                                                      | 1          |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT83SH314                                         | 1          |

| FEATURES                                                                          |            |

| PRODUCT ORDERING INFORMATION                                                      | 2          |

| PIN OUT OF THE XRT83SH314                                                         | 3          |

| TABLE OF CONTENTS                                                                 |            |

| PIN DESCRIPTIONS (BY FUNCTION)                                                    |            |

| MICROPROCESSOR                                                                    |            |

| RECEIVER SECTION                                                                  |            |

| TRANSMITTER SECTION                                                               |            |

| CONTROL FUNCTION                                                                  |            |

| CLOCK SECTION                                                                     |            |

| JTAG Section                                                                      |            |

| POWER AND GROUND                                                                  |            |

| No Connects                                                                       |            |

| 1.0 CLOCK SYNTHESIZER                                                             |            |

| TABLE 1: INPUT CLOCK SOURCE SELECT                                                |            |

| FIGURE 2. SIMPLIFIED BLOCK DIAGRAM OF THE CLOCK SYNTHESIZER                       | 15         |

| 1.1 ALL T1/E1 MODE                                                                |            |

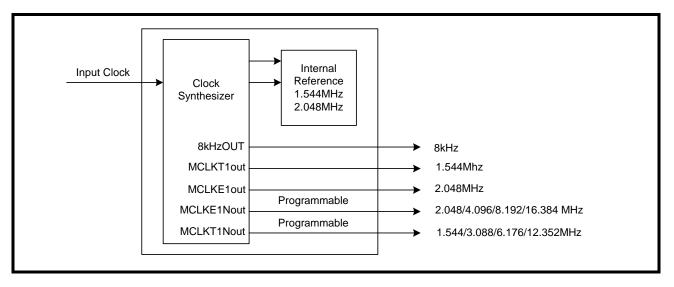

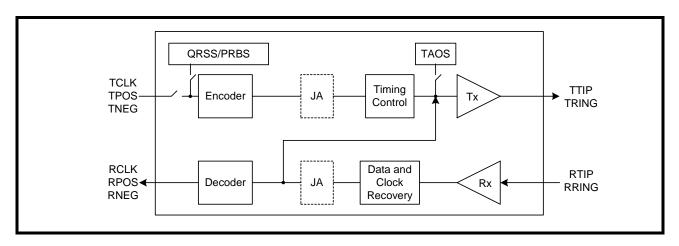

| 2.0 RECEIVE PATH LINE INTERFACE                                                   |            |

| Figure 3. Simplified Block Diagram of the Receive Path                            |            |

| 2.1 LINE TERMINATION (RTIP/RRING)                                                 |            |

| 2.1.1 CASE 1: INTERNAL TERMINATION                                                |            |

| Table 2: Selecting the Internal Impedance                                         | 1 <i>6</i> |

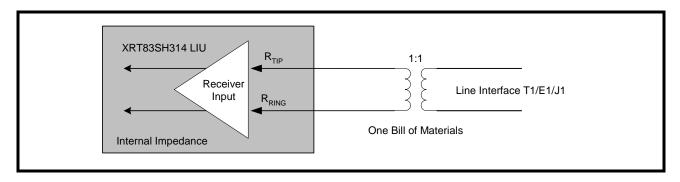

| FIGURE 4. TYPICAL CONNECTION DIAGRAM USING INTERNAL TERMINATION                   |            |

| 2.1.2 CASE 2: INTERNAL TERMINATION WITH ONE EXTERNAL FIXED RESISTOR FOR ALL MODES |            |

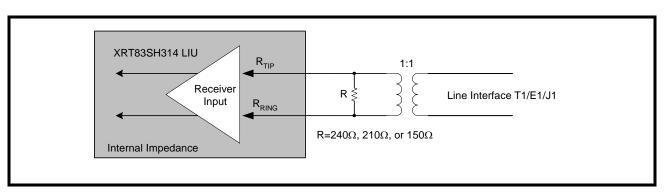

| TABLE 3: SELECTING THE VALUE OF THE EXTERNAL FIXED RESISTOR                       |            |

| Figure 5. Typical Connection Diagram Using One External Fixed Resistor            |            |

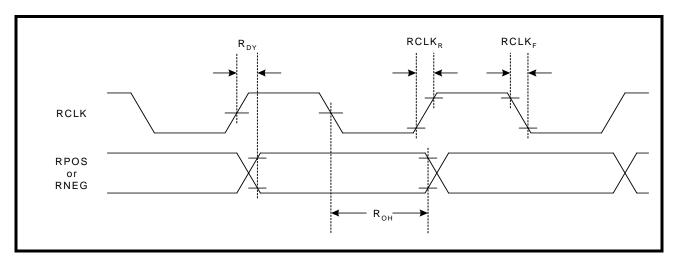

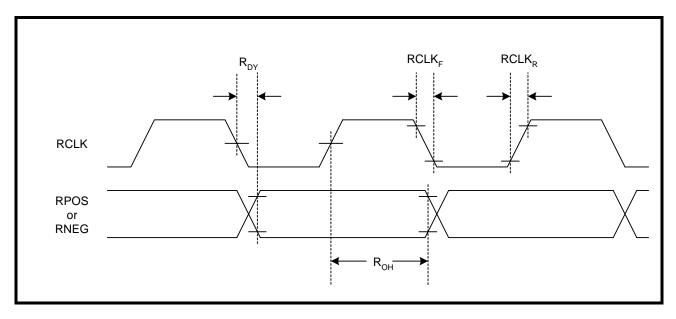

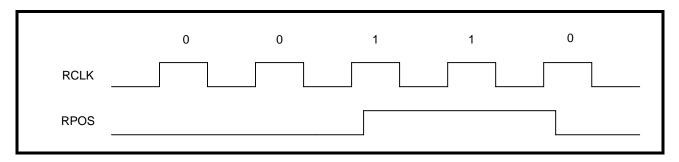

| Figure 6. Receive Data Updated on the Rising Edge of RCLK                         |            |

| FIGURE 6. RECEIVE DATA OPDATED ON THE RISING EDGE OF RCLK                         |            |

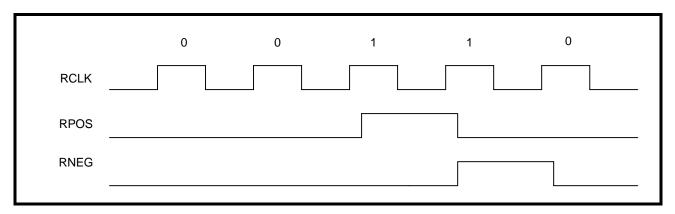

| TABLE 4: TIMING SPECIFICATIONS FOR RCLK/RPOS/RNEG                                 |            |

| 2.2.1 RECEIVE SENSITIVITY                                                         | 19         |

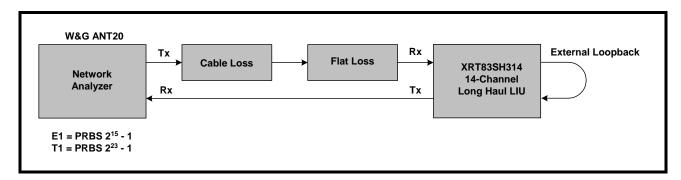

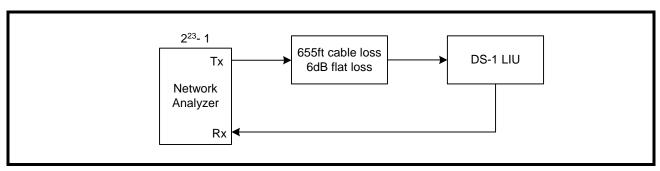

| FIGURE 8. TEST CONFIGURATION FOR MEASURING RECEIVE SENSITIVITY                    |            |

| 2.2.2 INTERFERENCE MARGIN                                                         |            |

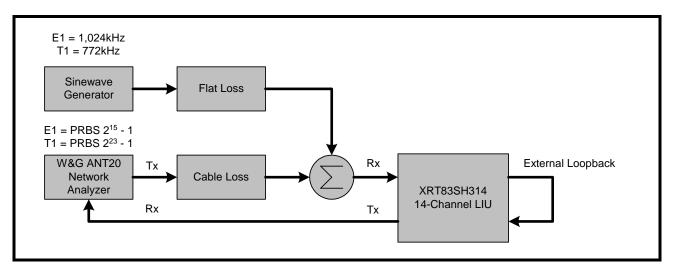

| FIGURE 9. TEST CONFIGURATION FOR MEASURING INTERFERENCE MARGIN                    |            |

| 2.2.3 GENERAL ALARM DETECTION AND INTERRUPT GENERATION                            |            |

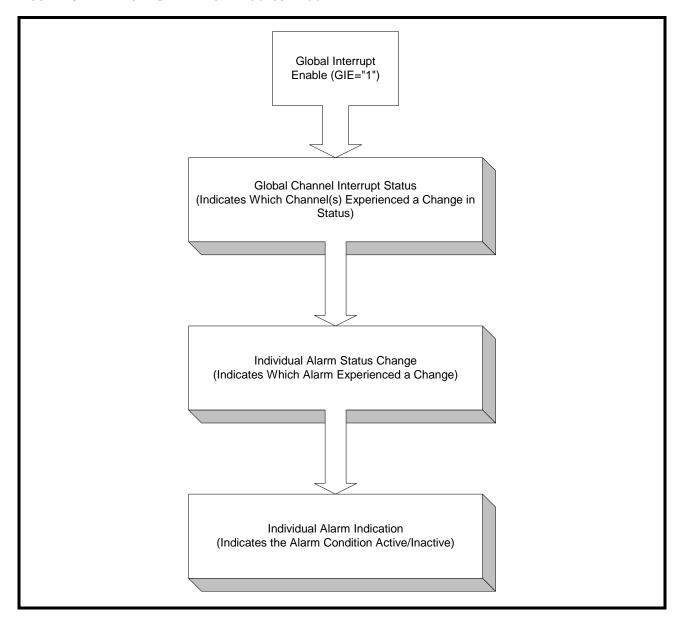

| FIGURE 10. INTERRUPT GENERATION PROCESS BLOCK                                     |            |

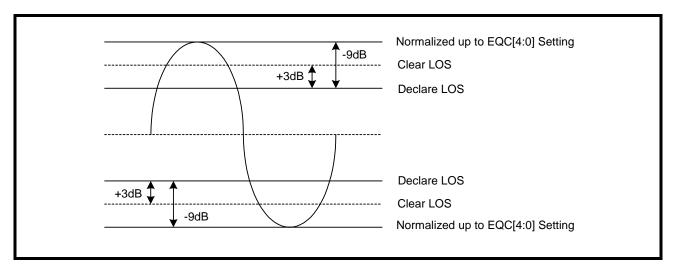

| Table 5: Analog RLOS Declare/Clear (Typical Values) for T1/E1                     |            |

| 2.3 JITTER ATTENUATOR                                                             |            |

| 2.4 HDB3/B8ZS DECODER                                                             |            |

| 2.5 RPOS/RNEG/RCLK                                                                | _          |

| Figure 12. Single Rail Mode With a Fixed Repeating "0011" Pattern                 |            |

| FIGURE 13. DUAL RAIL MODE WITH A FIXED REPEATING "0011" PATTERN                   | 24         |

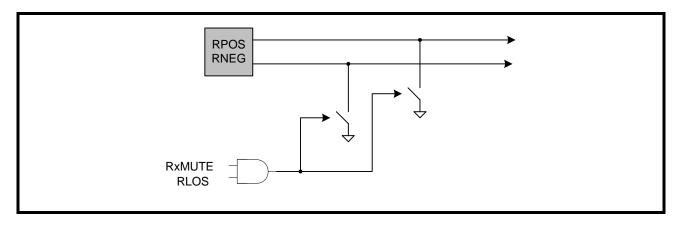

| 2.6 RXMUTE (RECEIVER LOS WITH DATA MUTING)                                        | 24         |

| FIGURE 14. SIMPLIFIED BLOCK DIAGRAM OF THE RXMUTE FUNCTION                        | 24         |

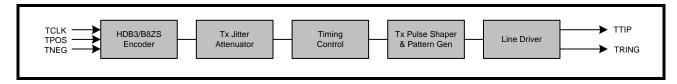

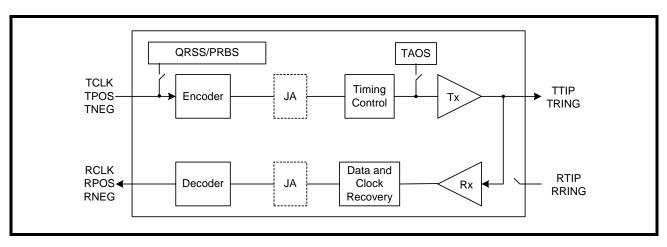

| 3.0 TRANSMIT PATH LINE INTERFACE                                                  | 25         |

| FIGURE 15. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT PATH                          |            |

| 3.1 TCLK/TPOS/TNEG DIGITAL INPUTS                                                 |            |

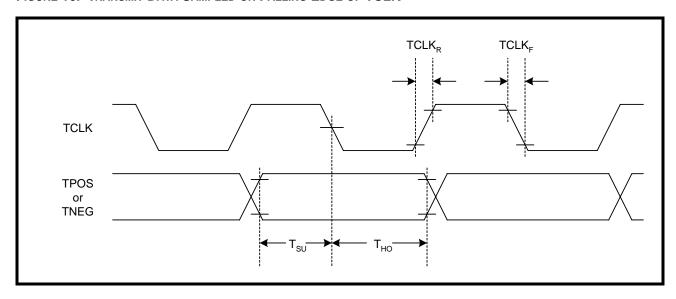

| FIGURE 16. TRANSMIT DATA SAMPLED ON FALLING EDGE OF TCLK                          |            |

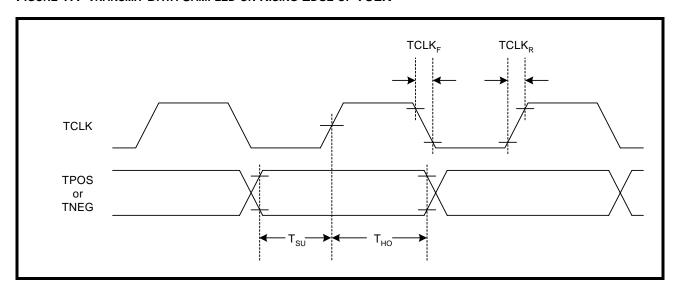

| FIGURE 17. TRANSMIT DATA SAMPLED ON RISING EDGE OF TCLK                           |            |

| TABLE 6: TIMING SPECIFICATIONS FOR TCLK/TPOS/TNEG                                 |            |

| TABLE 7: EXAMPLES OF HDB3 ENCODING                                                |            |

| TABLE 8: EXAMPLES OF BBZS ENCODING                                                |            |

| 3.3 JITTER ATTENUATOR                                                             |            |

| Table 9: Maximum Gap Width for Multiplexer/Mapper Applications                    |            |

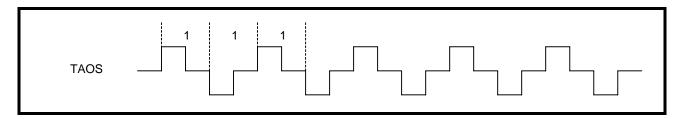

| 3.4 TAOS (TRANSMIT ALL ONES)                                                      |            |

# 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

| FIGURE 18. TAOS (TRANSMIT ALL ONES)                                                      |       |

|------------------------------------------------------------------------------------------|-------|

| 3.5 TRANSMIT DIAGNOSTIC FEATURES                                                         |       |

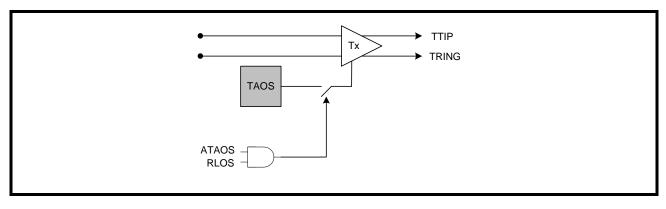

| 3.5.1 ATAOS (AUTOMATIC TRANSMIT ALL ONES)                                                |       |

| FIGURE 19. SIMPLIFIED BLOCK DIAGRAM OF THE ATAOS FUNCTION                                |       |

| 3.5.2 QRSS/PRBS GENERATION                                                               |       |

| TABLE 10: RANDOM BIT SEQUENCE POLYNOMIALS                                                |       |

| 3.6 TRANSMIT PULSE SHAPER AND FILTER                                                     |       |

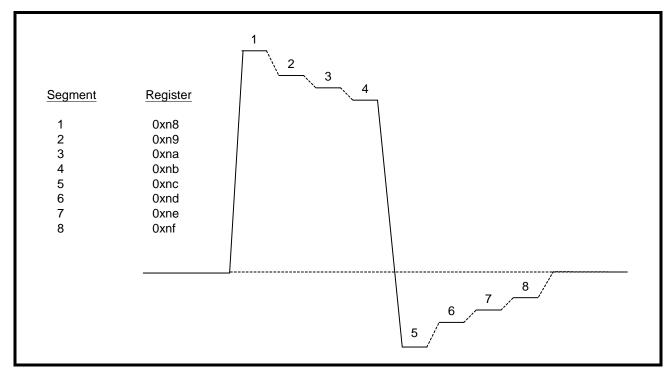

| 3.6.1 T1 SHORT HAUL LINE BUILD OUT (LBO)                                                 |       |

| TABLE 11: SHORT HAUL LINE BUILD OUT                                                      |       |

| 3.6.2 ARBITRARY PULSE GENERATOR FOR T1 AND E1                                            |       |

| 3.6.3 SETTING REGISTERS TO SELECT AN ARIBTRARY PULSE                                     |       |

|                                                                                          |       |

| TABLE 12: TYPICAL ROM VALUES                                                             |       |

|                                                                                          |       |

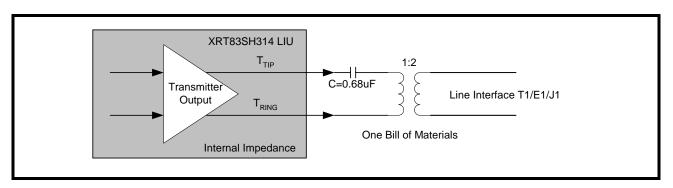

| 3.8 LINE TERMINATION (TTIP/TRING)                                                        |       |

| FIGURE 21. TYPICAL CONNECTION DIAGRAM USING INTERNAL TERMINATION                         |       |

| 4.0 T1/E1 APPLICATIONS                                                                   |       |

| 4.1 LOOPBACK DIAGNOSTICS                                                                 |       |

| 4.1.1 LOCAL ANALOG LOOPBACK                                                              |       |

| FIGURE 22. SIMPLIFIED BLOCK DIAGRAM OF LOCAL ANALOG LOOPBACK                             |       |

| 4.1.2 REMOTE LOOPBACK                                                                    |       |

| FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF REMOTE LOOPBACK                                   |       |

| 4.1.3 DIGITAL LOOPBACK                                                                   |       |

| 4.1.4 DUAL LOOPBACK                                                                      |       |

| FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF DUAL LOOPBACK                                     |       |

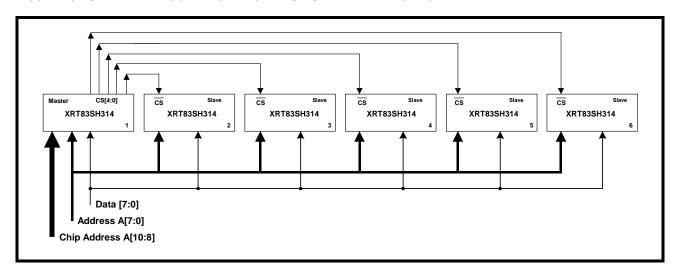

| 4.2 84-CHANNEL T1/E1 MULTIPLEXER/MAPPER APPLICATIONS                                     |       |

| FIGURE 26. SIMPLIFIED BLOCK DIAGRAM OF AN 84-CHANNEL APPLICATION                         |       |

| TABLE 13: CHIP SELECT ASSIGNMENTS                                                        |       |

| 4.3 LINE CARD REDUNDANCY                                                                 |       |

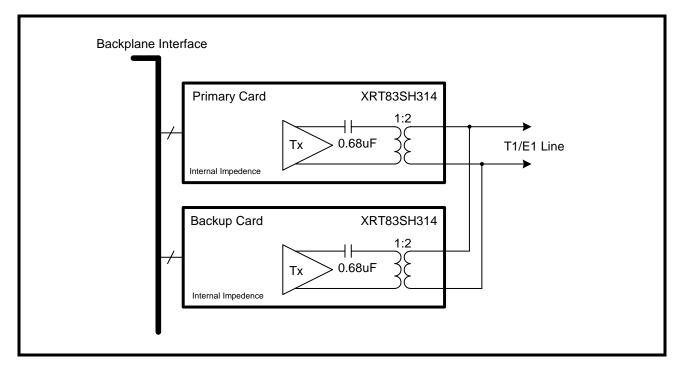

| 4.3.1 1:1 AND 1+1 REDUNDANCY WITHOUT RELAYS                                              |       |

| 4.3.2 TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY                                     |       |

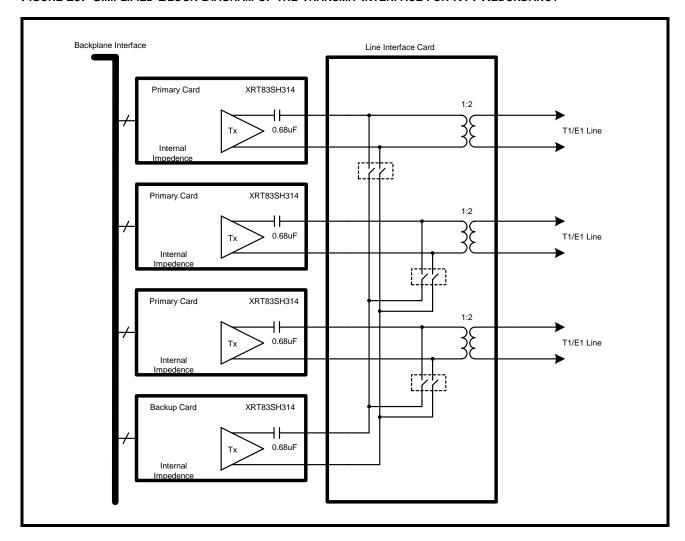

| Figure 27. Simplified Block Diagram of the Transmit Interface for 1:1 and 1+1 Redundancy |       |

| 4.3.3 RECEIVE INTERFACE WITH 1:1 AND 1+1 REDUNDANCY                                      |       |

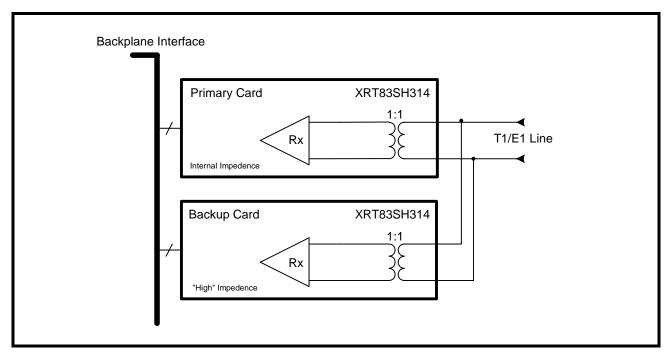

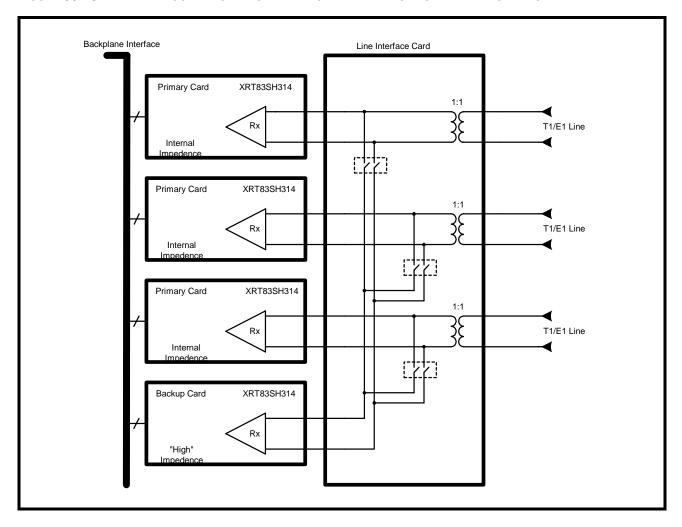

| FIGURE 28. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR 1:1 AND 1+1 REDUNDANCY  |       |

| 4.3.4 N+1 REDUNDANCY USING EXTERNAL RELAYS                                               |       |

| 4.3.5 TRANSMIT INTERFACE WITH N+1 REDUNDANCY                                             |       |

| FIGURE 29. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY         |       |

| 4.3.6 RECEIVE INTERFACE WITH N+1 REDUNDANCY                                              |       |

| FIGURE 30. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR N+1 REDUNDANCY          |       |

| 4.4 POWER FAILURE PROTECTION                                                             | 39    |

| 4.5 OVERVOLTAGE AND OVERCURRENT PROTECTION                                               | 39    |

| 4.6 NON-INTRUSIVE MONITORING                                                             |       |

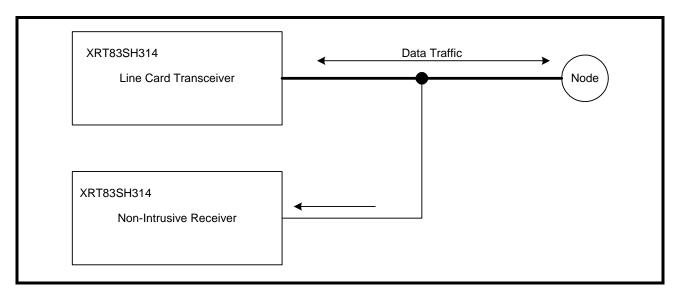

| FIGURE 31. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION            |       |

| 4.7 ANALOG BOARD CONTINUITY CHECK                                                        | 40    |

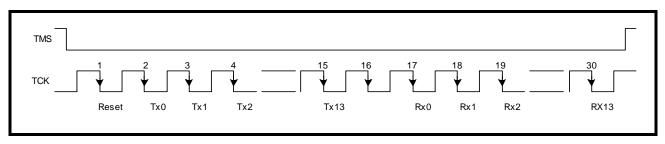

| FIGURE 32. ATP TESTING BLOCK DIAGRAM                                                     |       |

| FIGURE 33. TIMING DIAGRAM FOR ATP TESTING                                                |       |

| 4.7.1 TRANSMITTER TTIP AND TRING TESTING                                                 |       |

| 4.7.2 RECEIVER RTIP AND RRING                                                            |       |

| 4.8 XRT83SH314 JITTER CHARACTERISTICS                                                    |       |

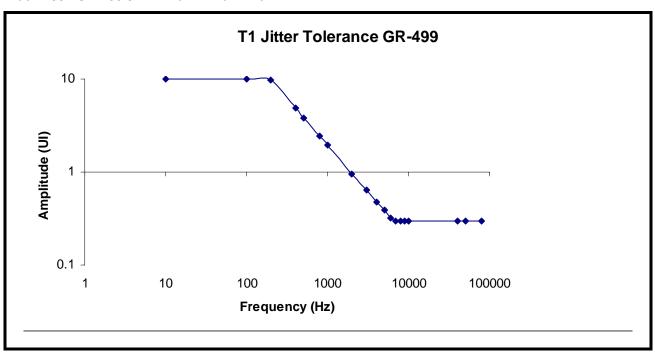

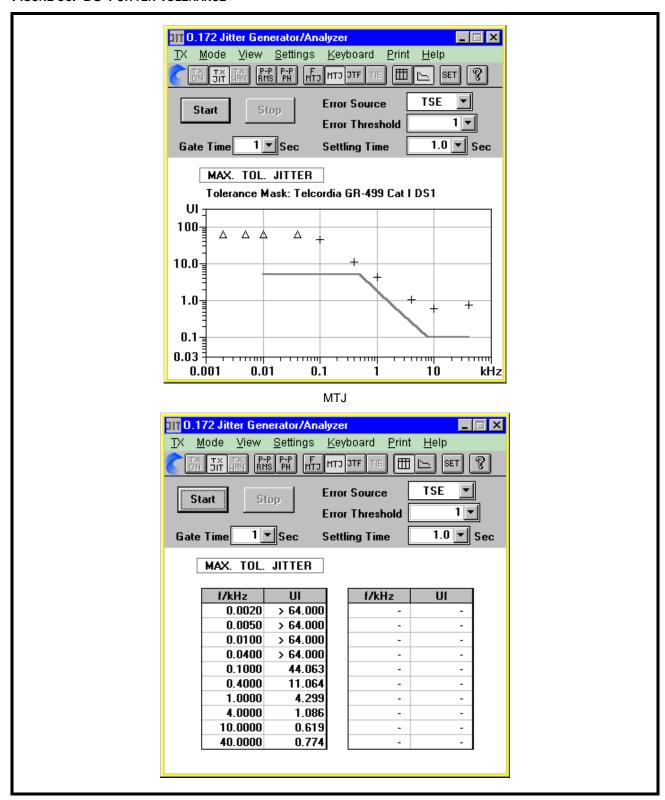

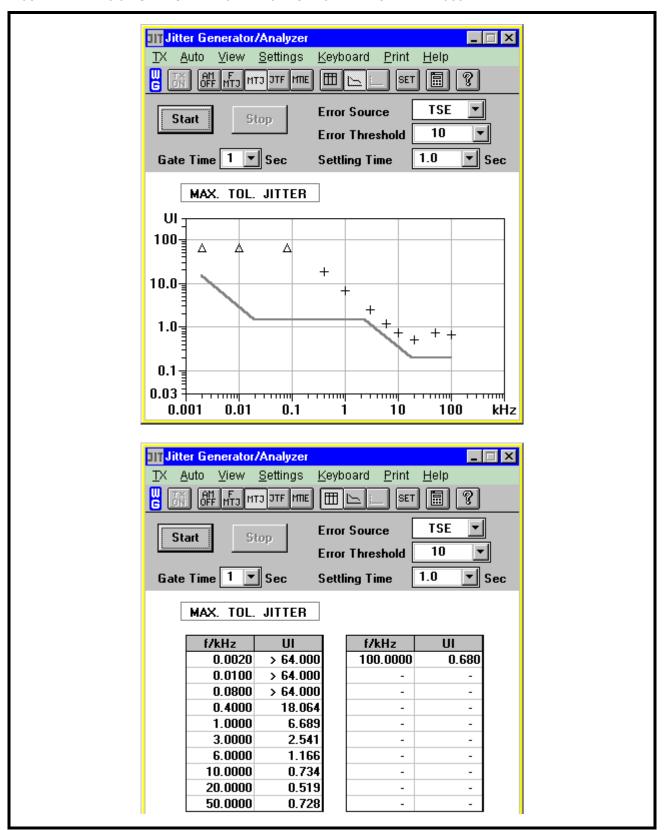

| 4.8.1 JITTER TOLERANCE                                                                   |       |

| FIGURE 34. TEST CIRCUIT FOR DS-1 JITTER TOLERANCE                                        | ····· |

| FIGURE 35. GR-499 JITTER TOLERANCE MASK                                                  |       |

| FIGURE 36. DS-1 JITTER TOLERANCE                                                         |       |

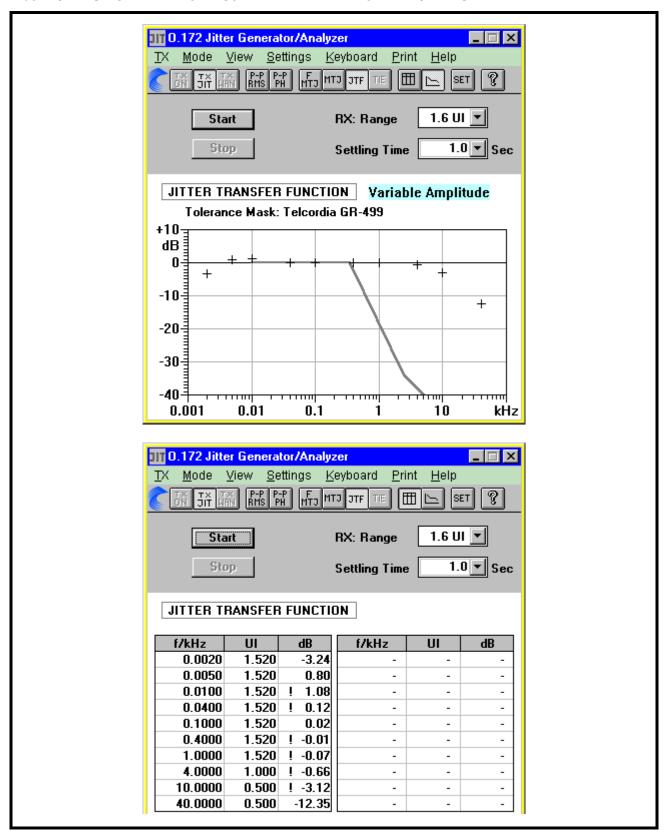

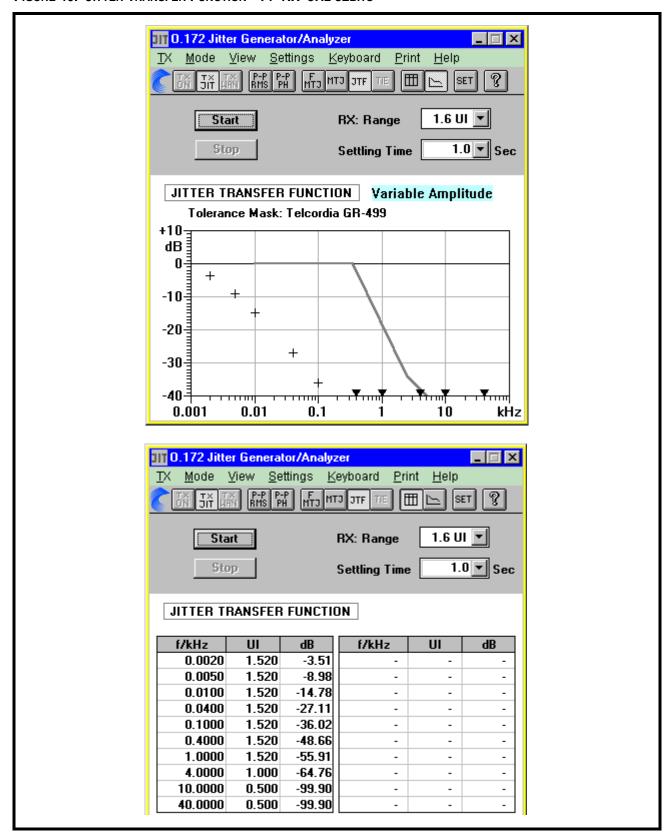

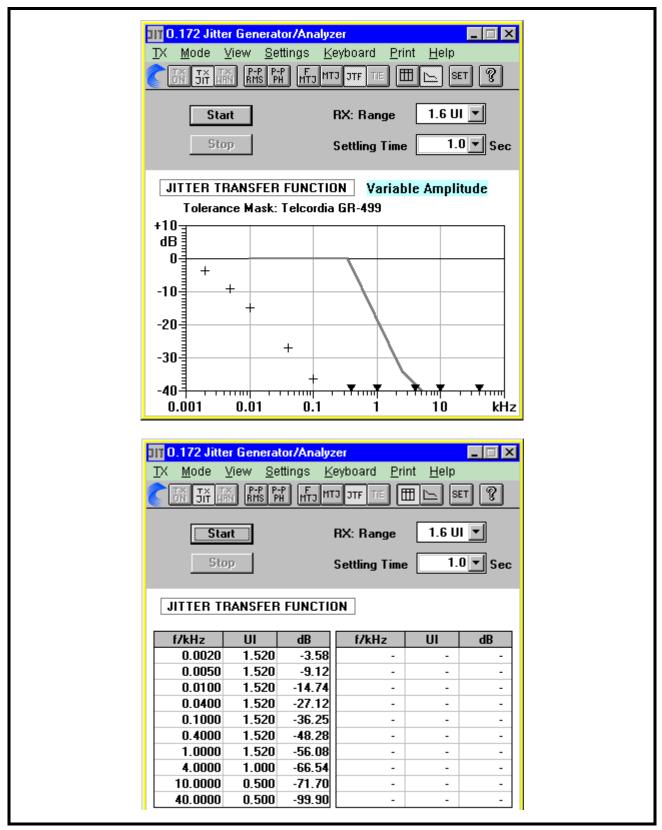

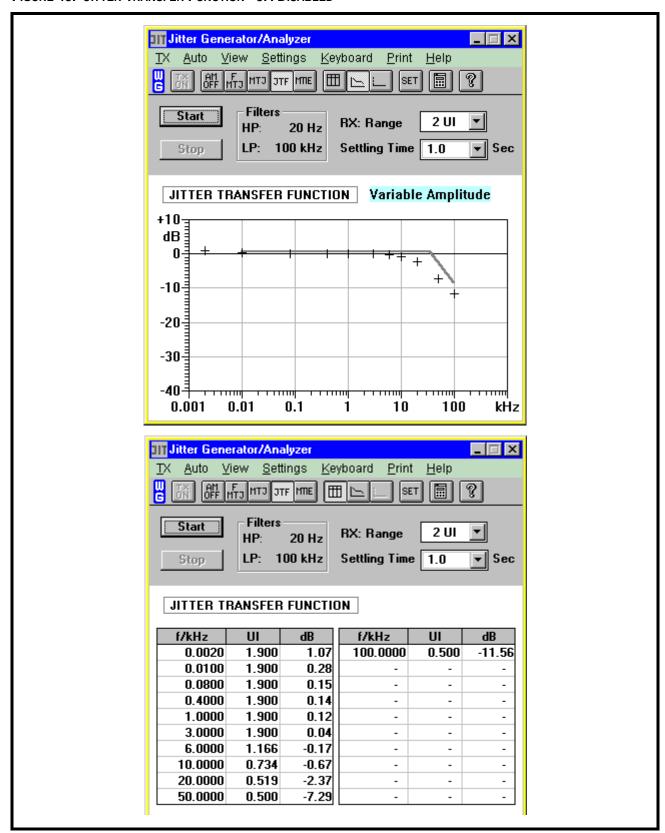

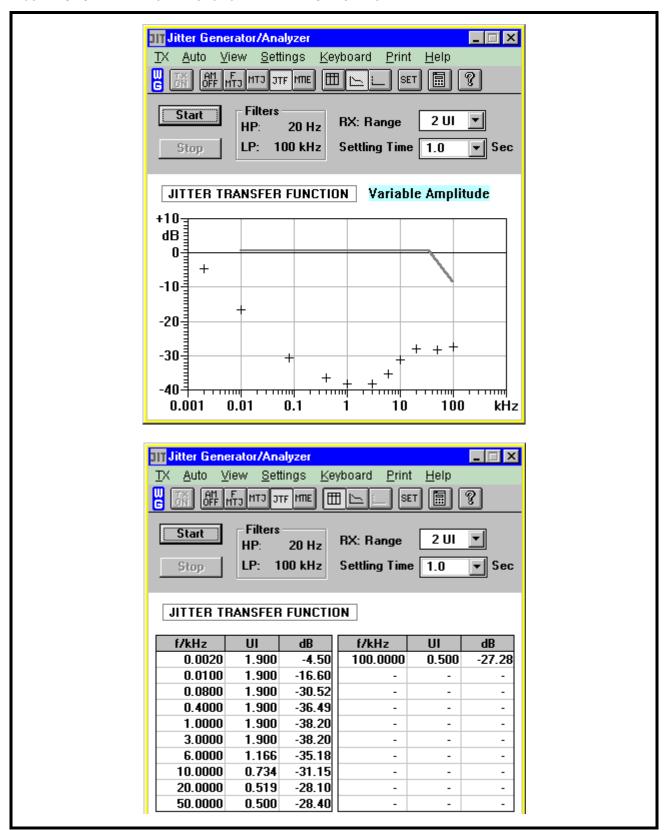

| FIGURE 37. DS-1 JITTER TRANSFER CURVE VARIABLE AMPLITUDE - T1 JA DISABLE                 |       |

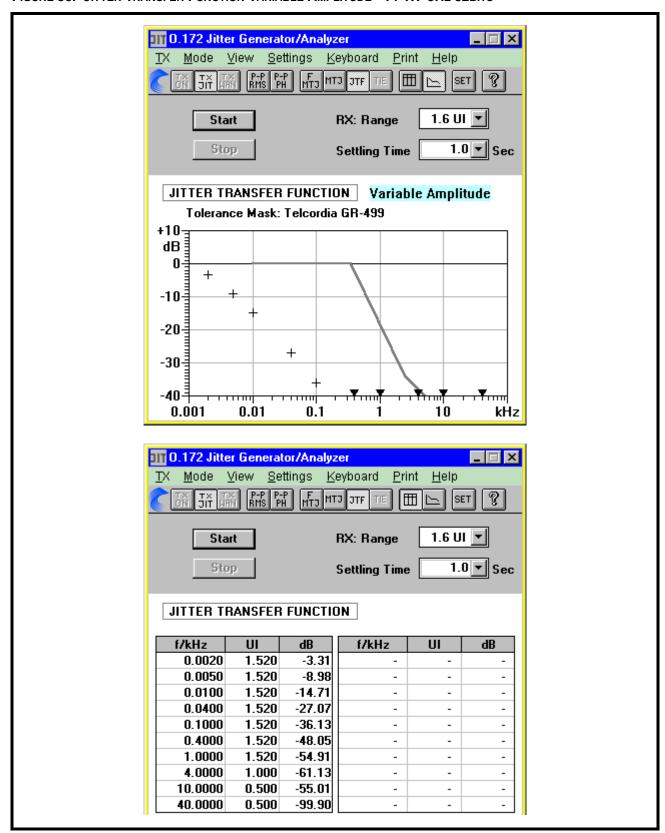

| FIGURE 38. JITTER TRANSFER FUNCTION VARIABLE AMPLITUDE - T1 TX 3Hz 32BITS                |       |

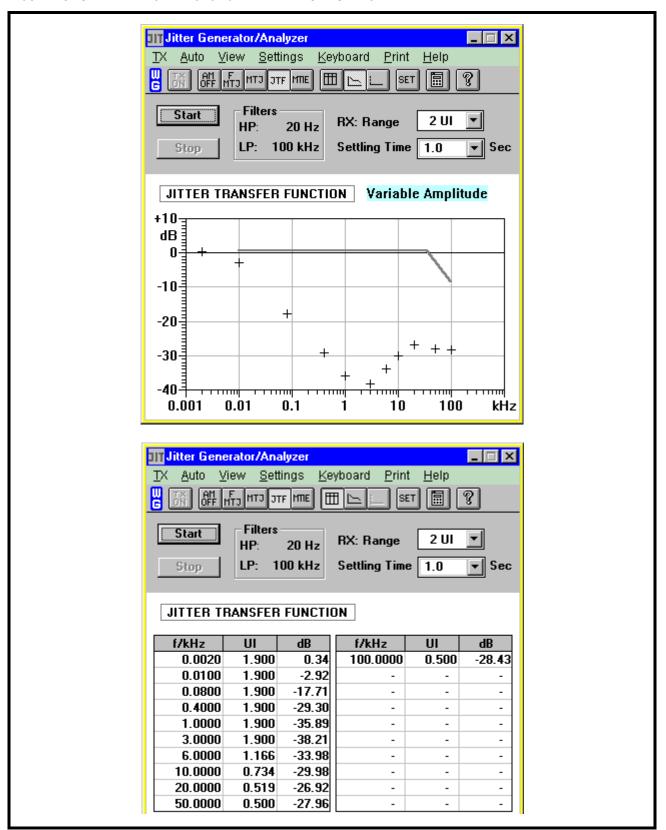

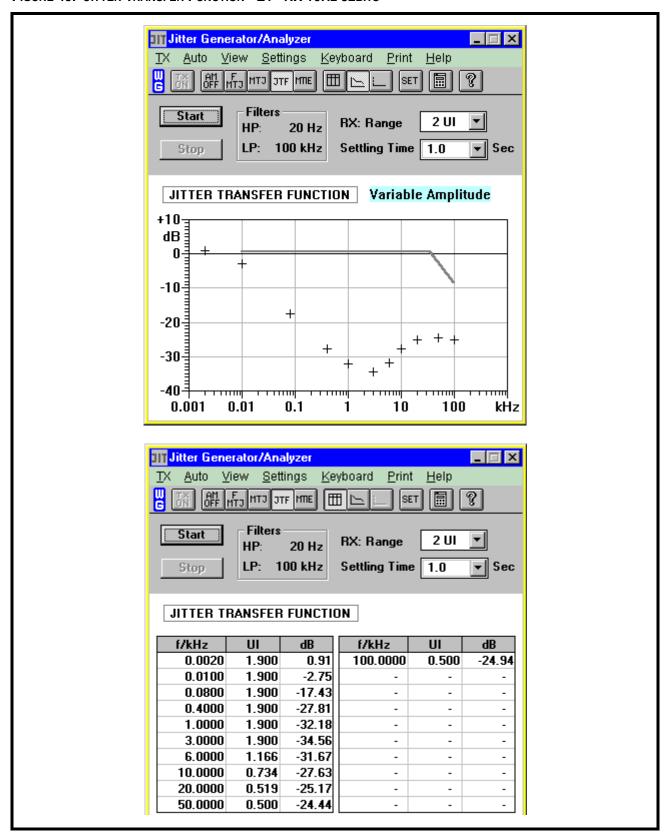

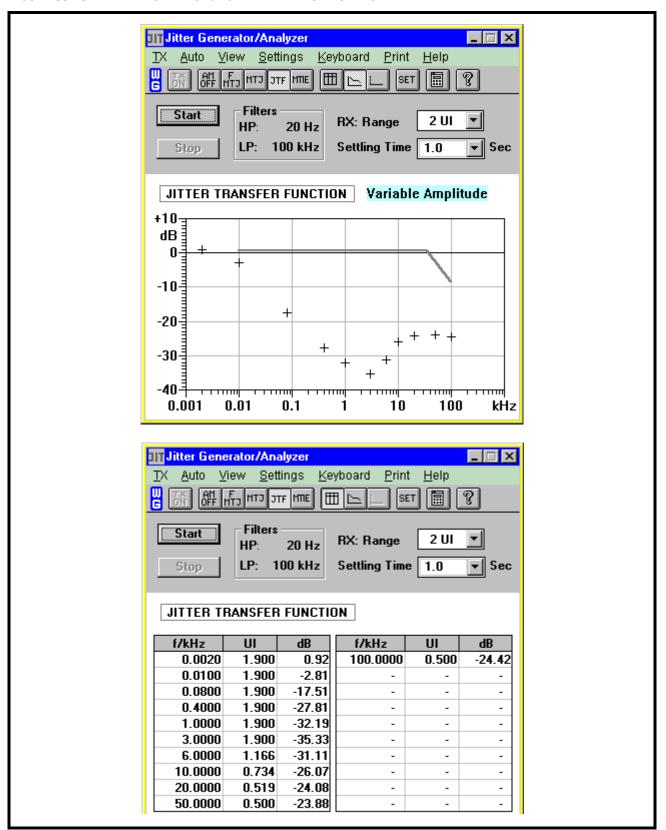

| FIGURE 39. JITTER TRANSFER FUNCTION - T1 TX 3Hz 64Bits                                   |       |

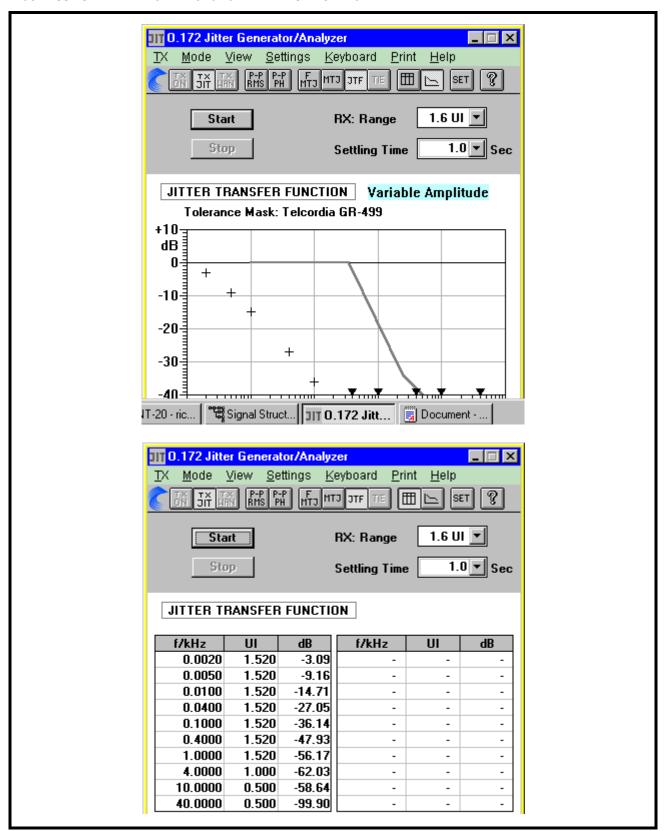

| FIGURE 40. JITTER TRANSFER FUNCTION - T1 RX 3Hz 32BITS                                   |       |

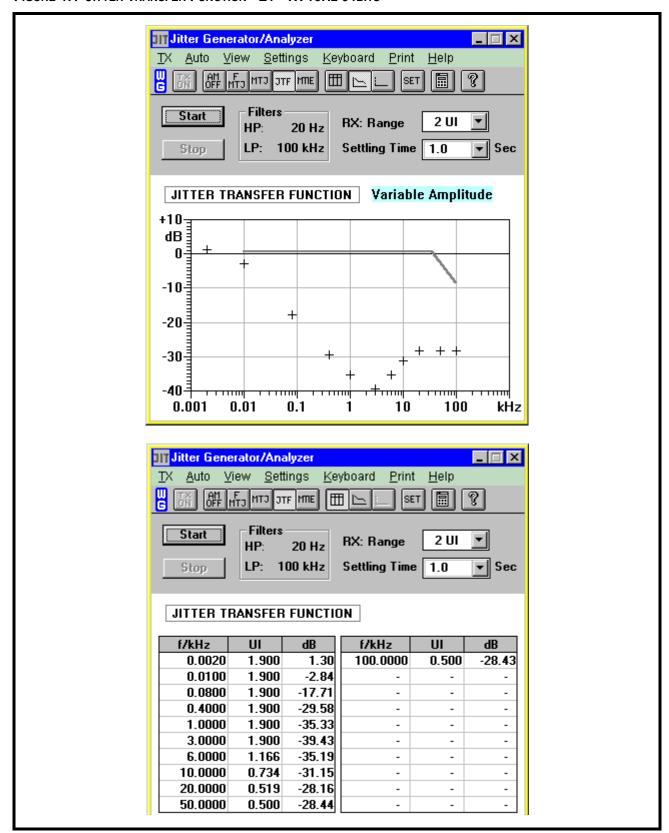

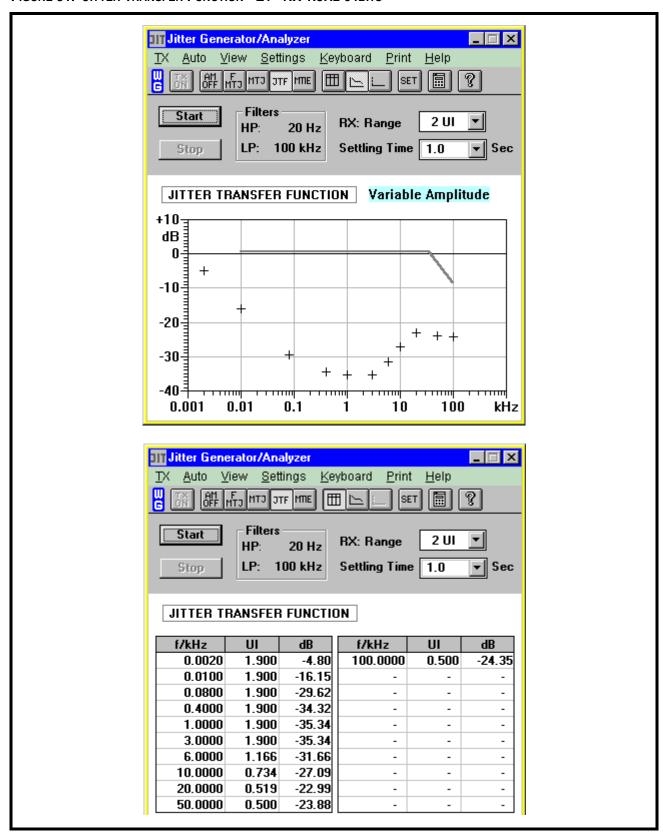

| FIGURE 41. JITTER TRANSFER FUNCTION - 11 RX 3HZ 64BITS                                   |       |

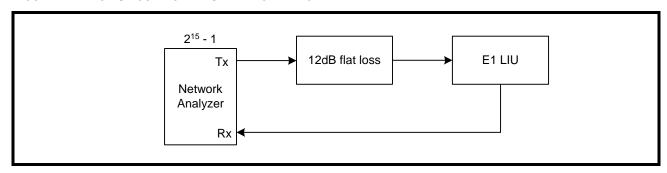

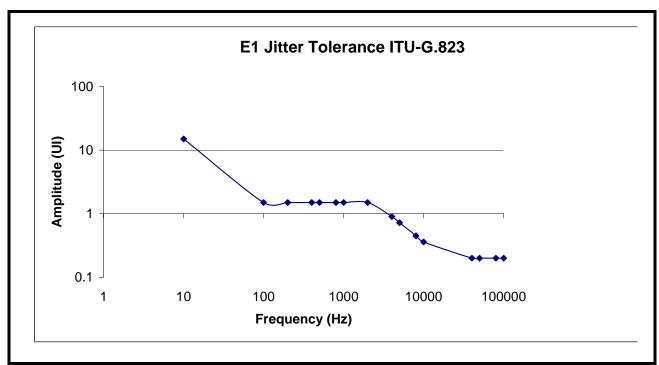

| FIGURE 43. ITU-G.823 JITTER TOLERANCE MASK                                               |       |

| FIGURE 44. REVISION C: E1 JITTER TOLERANCE - 6DB CABLE + 6DB FLAT LOSS                   |       |

| FIGURE 45. JITTER TRANSFER FUNCTION - JA DISABLED                                        |       |

| FIGURE 46. JITTER TRANSFER FUNCTION - E1 TX 10Hz 32BiTS                                  |       |

| Figure 47. Jitter Transfer Function - E1 TX 10Hz 64bits                                  |       |

|                                                                                          |       |

# XRT83SH314

# 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

| 14-CHANI  | NEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT                                                            | EV. 1.0.4 |

|-----------|--------------------------------------------------------------------------------------------------------|-----------|

| FIGURE 48 | 3. JITTER TRANSFER FUNCTION - E1 TX 1.5Hz 64BITS                                                       | 54        |

|           | D. JITTER TRANSFER FUNCTION - E1 RX 10Hz 32BiTs                                                        |           |

|           | D. JITTER TRANSFER FUNCTION - E1 RX 10Hz 64BiTs                                                        |           |

|           | JITTER TRANSFER FUNCTION - E1 RX 1.5Hz 64Bits                                                          |           |

|           | 3.2 INTRINSIC JITTER                                                                                   |           |

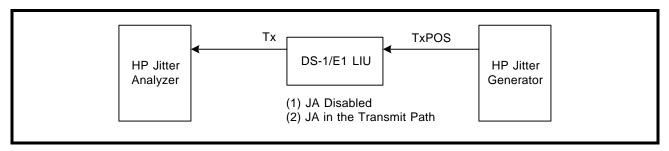

|           | 2. TEST CIRCUIT FOR INTRINSIC JITTER MEASUREMENTS                                                      |           |

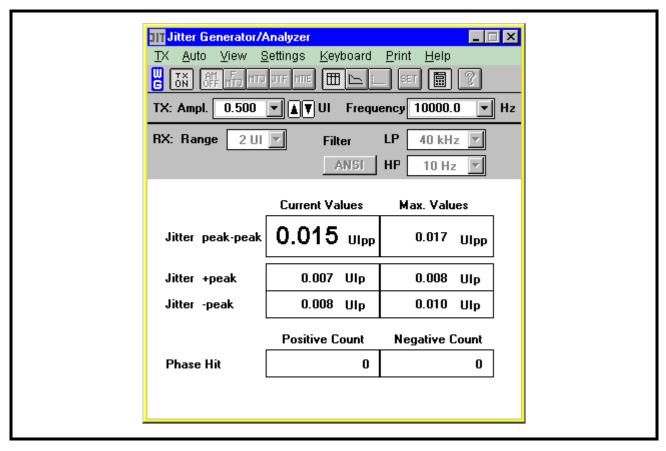

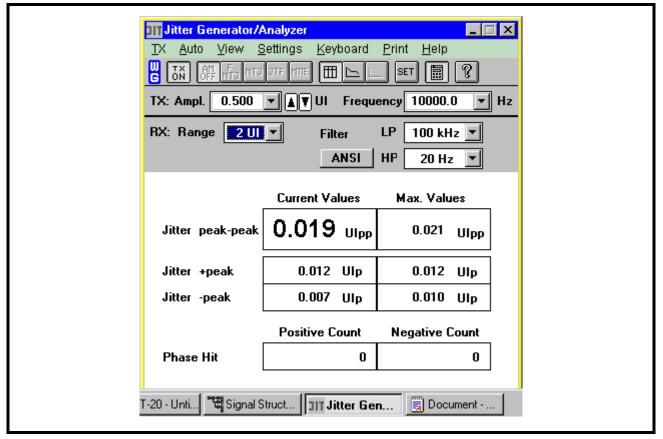

|           | 3. INTRINSIC JITTER - T1 MAX. VALUE MEASURED .019UIPP                                                  |           |

|           | 4. E1 INTRINSIC JITTER - MAX. VALUE MEASURED .023UIPP                                                  |           |

|           | 3.3 JITTER TRANSFER CURVE                                                                              |           |

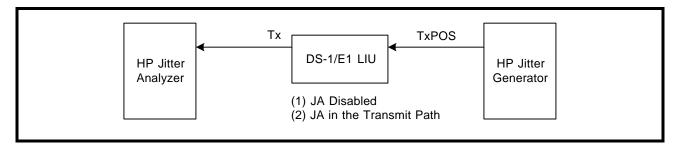

|           | 5. TEST CIRCUIT FOR JITTER TRANSFER CURVE                                                              |           |

|           | OPROCESSOR INTERFACE BLOCK                                                                             |           |

|           | SELECTING THE MICROPROCESSOR INTERFACE MODE                                                            |           |

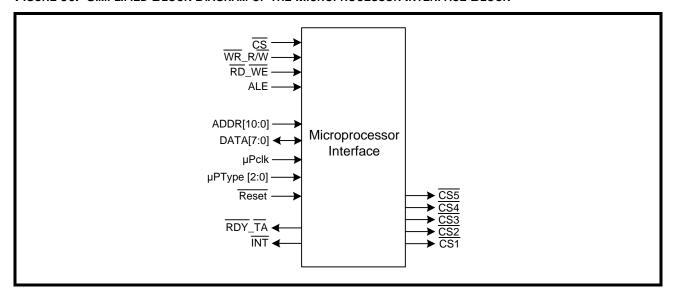

|           | S. SIMPLIFIED BLOCK DIAGRAM OF THE MICROPROCESSOR INTERFACE BLOCK                                      |           |

|           | HE MICROPROCESSOR INTERFACE BLOCK SIGNALS                                                              |           |

|           | XRT84SH314S MICROPROCESSOR INTERFACE SIGNALS COMMON TO BOTH INTEL AND MOTOROLA MODES                   |           |

|           |                                                                                                        |           |

|           | INTEL MODE: MICROPROCESSOR INTERFACE SIGNALS                                                           |           |

|           | MOTOROLA MODE: MICROPROCESSOR INTERFACE SIGNALS                                                        |           |

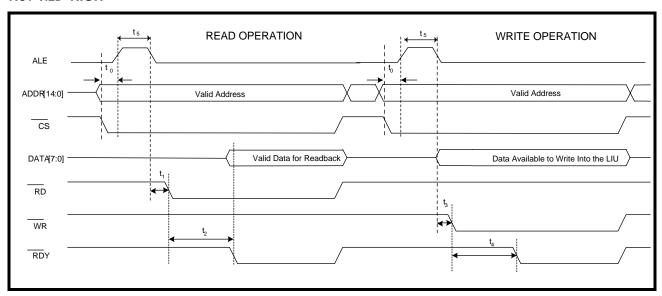

|           | ITEL MODE PROGRAMMED I/O ACCESS (ASYNCHRONOUS)                                                         |           |

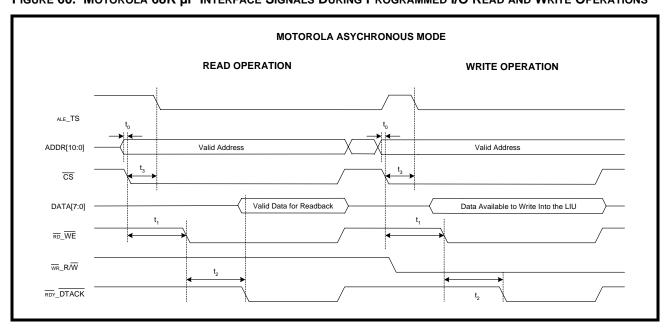

|           | 7. INTEL µP INTERFACE TIMING DURING PROGRAMMED I/O READ AND WRITE OPERATIONS WHEN ALE IS NOT TIED 'HIG |           |

| TABLE 18: | INTEL MICROPROCESSOR INTERFACE TIMING SPECIFICATIONS                                                   | 64        |

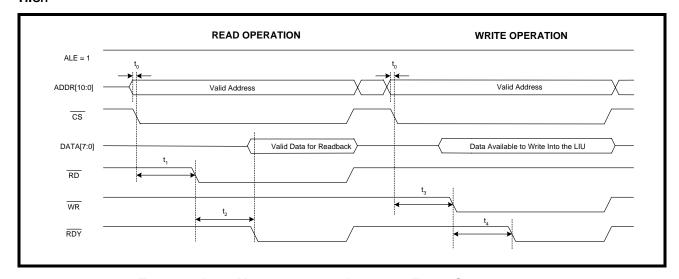

|           | 3. INTEL μP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRITE OPERATIONS WITH ALE HIGH            |           |

|           | INTEL MICROPROCESSOR INTERFACE TIMING SPECIFICATIONS                                                   |           |

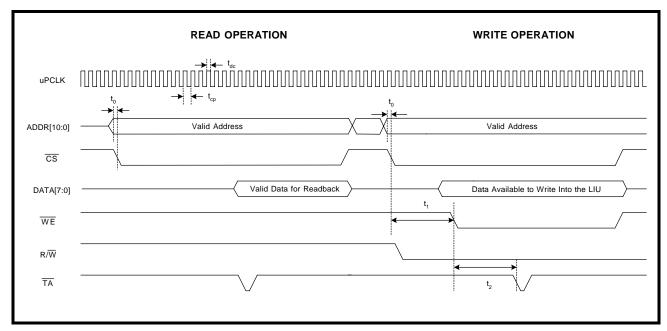

|           | PC86X MODE PROGRAMMED I/O ACCESS (SYNCHRONOUS)                                                         |           |

|           | 9. MOTOROLA MPC86X μP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRITE OPERATIONS                |           |

|           | MOTOROLA MPC86X MICROPROCESSOR INTERFACE TIMING SPECIFICATIONS                                         |           |

|           | ). MOTOROLA 68K µP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRITE OPERATIONS                   |           |

|           | MOTOROLA 68K MICROPROCESSOR INTERFACE TIMING SPECIFICATIONS                                            |           |

| 6.0 REG   | STER DESCRIPTIONS                                                                                      | 69        |

| 6.1 R     | EGISTER LISTS                                                                                          | 69        |

| TABLE 22: | MICROPROCESSOR REGISTER ADDRESS (ADDR[7:0])                                                            | 69        |

|           | MICROPROCESSOR REGISTER CHANNEL DESCRIPTION                                                            |           |

|           | MICROPROCESSOR REGISTER GLOBAL DESCRIPTION                                                             |           |

| 6.2 D     | ETAIL BIT DESCRIPTIONS                                                                                 | 71        |

|           | MICROPROCESSOR REGISTER 0x00H BIT DESCRIPTION                                                          |           |

|           | CABLE LENGTH CONTROL                                                                                   |           |

|           | MICROPROCESSOR REGISTER 0x01H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0x02H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0x03H BIT DESCRIPTION.                                                         |           |

| _         | MICROPROCESSOR REGISTER 0x04H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0x05H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0x07H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0x06H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0x08H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0x09H BIT DESCRIPTION.                                                         |           |

|           | MICROPROCESSOR REGISTER 0x0AH BIT DESCRIPTION                                                          | _         |

|           | MICROPROCESSOR REGISTER 0X0BH BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0X0CH BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0X00H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0X0EH BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0X0EH BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER OXEOH BIT DESCRIPTION                                                          |           |

|           |                                                                                                        | _         |

|           | MICROPROCESSOR REGISTER 0XE1H BIT DESCRIPTION                                                          | _         |

|           |                                                                                                        |           |

| _         | MICROPROCESSOR REGISTER OXE3H BIT DESCRIPTION                                                          |           |

| _         | MICROPROCESSOR REGISTER 0XE4H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0xE5H BIT DESCRIPTION                                                          | _         |

| _         | MICROPROCESSOR REGISTER 0xE6H BIT DESCRIPTION                                                          |           |

| _         | MICROPROCESSOR REGISTER 0xE7H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0xE8H BIT DESCRIPTION                                                          |           |

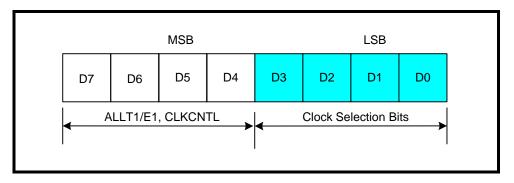

|           | 2.1 CLOCK SELECT REGISTER                                                                              |           |

|           | 1. Register 0xE9H Sub Registers                                                                        |           |

|           | MICROPROCESSOR REGISTER 0XE9H BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0XEAH BIT DESCRIPTION                                                          |           |

|           | MICROPROCESSOR REGISTER 0xEBH BIT DESCRIPTION                                                          |           |

| TABLE 54: | E1 Arbitrary Select                                                                                    | 90        |

# 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

| TABLE 55: DEVICE "ID" REGISTER (0XFEH)                           |    |

|------------------------------------------------------------------|----|

| TABLE 56: MICROPROCESSOR REGISTER 0xFFH BIT DESCRIPTION          |    |

| 7.0 ELECTRICAL CHARACTERISTICS                                   | 92 |

| TABLE 57: ABSOLUTE MAXIMUM RATINGS                               | 92 |

| TABLE 58: DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS |    |

| Table 59: AC Electrical Characteristics                          | 92 |

| Table 60: Power Consumption                                      |    |

| Table 61: E1 Receiver Electrical Characteristics                 | 93 |

| TABLE 62: T1 RECEIVER ELECTRICAL CHARACTERISTICS                 |    |

| TABLE 63: E1 TRANSMITTER ELECTRICAL CHARACTERISTICS              | 95 |

| TABLE 64: T1 TRANSMITTER ELECTRICAL CHARACTERISTICS              |    |

| Ordering Information                                             | 96 |

| PACKAGE DIMENSIONS (DIE DOWN)                                    | 96 |

| REVISION HISTORY                                                 |    |

# PIN DESCRIPTIONS (BY FUNCTION)

# MICROPROCESSOR

| NAME                                                               | Pin                                                                             | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>cs</u>                                                          | A22                                                                             | I    | Chip Select Input  Active low signal. This signal enables the microprocessor interface by pulling chip select "Low". The microprocessor interface is disabled when the chip select signal returns "High".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ALE_TS                                                             | C19                                                                             | I    | Address Latch Enable Input (Transfer Start) See the Microprocessor section of this datasheet for a description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WR_R/W                                                             | A20                                                                             | I    | Write Strobe Input (Read/Write) See the Microprocessor section of this datasheet for a description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RD_WE                                                              | D18                                                                             | I    | Read Strobe Input (Write Enable) See the Microprocessor section of this datasheet for a description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RDY_TA                                                             | AA3                                                                             | 0    | Ready Output (Transfer Acknowledge) See the Microprocessor section of this datasheet for a description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ĪNT                                                                | В3                                                                              | 0    | Interrupt Output  Active low signal. This signal is asserted "Low" when a change in alarm status occurs. Once the status registers have been read, the interrupt pin will return "High". GIE (Global Interrupt Enable) must be set "High" in the appropriate global register to enable interrupt generation.  Note: This pin is an open-drain output that requires an external 10KΩ pull-up resistor.                                                                                                                                                                                                                                                                                                                                             |

| μPCLK                                                              | AB2                                                                             | I    | Micro Processor Clock Input In a synchronous microprocessor interface, μPCLK is used as the internal timing reference for programming the LIU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ADDR10 ADDR9 ADDR8 ADDR7 ADDR6 ADDR5 ADDR4 ADDR3 ADDR2 ADDR1 ADDR0 | A23<br>E20<br>C22<br>Y18<br>AA19<br>AB20<br>AC21<br>AB21<br>AA20<br>Y19<br>AC22 |      | Address Bus Input  ADDR[10:8] is used as a chip select decoder. The LIU has 5 chip select output pins for enabling up to 5 additional devices for accessing internal registers. The LIU has the option to select itself (master device), up to 5 additional devices, or all 6 devices simultaneously by setting the ADDR[10:8] pins specified below. ADDR[7:0] is a direct address bus for permitting access to the internal registers.  ADDR[10:8]  000 = Master Device  001 = Chip Select Output 1 (Pin B21)  010 = Chip Select Output 2 (Pin D19)  011 = Chip Select Output 3 (Pin C20)  100 = Chip Select Output 4 (Pin A21)  101 = Chip Select Output 5 (Pin B20)  110 = Reserved  111 = All Chip Selects Active Including the Master Device |

# **MICROPROCESSOR**

| NAME                                            | Pin                                                 | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------|-----------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA7 DATA6 DATA5 DATA4 DATA3 DATA2 DATA1 DATA0 | AA4<br>AB3<br>AC3<br>AA5<br>Y6<br>AB4<br>AC4<br>AB5 | I/O  | Bi-directional Data Bus  DATA[7:0] is a bi-directional data bus used for read and write operations.                                                                                                                                                                                                                |

| μPTS2<br>μPTS1<br>μPTS0                         | AC23<br>AB22<br>AA21                                | I    | Microprocessor Type Select Input  μPTS[2:0] are used to select the microprocessor type interface.  000 = Intel 68HC11, 8051, 80C188 (Asynchronous)  001 = Motorola 68K (Asynchronous)  111 = Motorola MPC8260, MPC860 Power PC (Synchronous)                                                                       |

| Reset                                           | B22                                                 | I    | Hardware Reset Input Active low signal. When this pin is pulled "Low" for more than 10μS, the internal registers are set to their default state. See the register description for the default values.  Note: Internally pulled "High" with a 50ΚΩ resistor.                                                        |

| CS5<br>CS4<br>CS3<br>CS2<br>CS1                 | B20<br>A21<br>C20<br>D19<br>B21                     | 0    | Chip Select Output The XRT83SH314 can be used to provide the necessary chip selects for up to 5 additional devices by using the 3 MSBs ADDR[10:8] from the 11-Bit address bus. The LIU allows up to 84-channel applications with only using one chip select. See the ADDR[10:0] definition in the pin description. |

# **RECEIVER SECTION**

| NAME   | Pin  | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxON   | AB19 | 1    | Receive On/Off Input                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |      |      | Upon power up, the receivers are powered off. Turning the receivers On or Off can be selected through the microprocessor interface by programming the appropriate channel register if the hardware pin is pulled "High". If the hardware pin is pulled "Low", all channels are automatically turned off.  *Note: Internally pulled "Low" with a 50KΩ resistor.                                                                     |

| RxTSEL | Y15  | I    | Receive Termination Control                                                                                                                                                                                                                                                                                                                                                                                                        |

|        |      |      | Upon power up, the receivers are in "High" impedance. Switching to internal termination can be selected through the microprocessor interface by programming the appropriate channel register. However, to switch control to the hardware pin, RxTCNTL must be programmed to "1" in the appropriate global register. Once control has been granted to the hardware pin, it must be pulled "High" to switch to internal termination. |

|        |      |      | <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                  |

# **RECEIVER SECTION**

| NAME                                                                                          | Pin                                                                                       | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLOS                                                                                          | AB1                                                                                       | 0    | Receive Loss of Signal (Global Pin for All 14-Channels)  When a receive loss of signal occurs for any one of the 14-channels according to ITU-T G.775, the RLOS pin will go "High" for a minimum of one RCLK cycle. RLOS will remain "High" until the loss of signal condition clears. See the Receive Loss of Signal section of this datasheet for more details.  Note: This pin is for redundancy applications to initiate an automatic switch to the backup card. For individual channel RLOS, see the register map. |

| RCLK13 RCLK12 RCLK11 RCLK10 RCLK9 RCLK8 RCLK7 RCLK6 RCLK5 RCLK5 RCLK4 RCLK3 RCLK2 RCLK1 RCLK1 | AB14<br>Y22<br>R22<br>P22<br>G22<br>F22<br>B14<br>B9<br>F2<br>G2<br>P2<br>R2<br>AA2       | 0    | Receive Clock Output  RCLK is the recovered clock from the incoming data stream. If the incoming signal is absent or RxON is pulled "Low", RCLK maintains its timing by using an internal master clock as its reference. RPOS/RNEG data can be updated on either edge of RCLK selected by RCLKE in the appropriate global register.  Note: RCLKE is a global setting that applies to all 14 channels.                                                                                                                   |

| RPOS13 RPOS12 RPOS11 RPOS10 RPOS9 RPOS8 RPOS7 RPOS6 RPOS5 RPOS4 RPOS3 RPOS2 RPOS1 RPOS0       | Y14<br>W20<br>P20<br>N20<br>H20<br>G20<br>D14<br>D10<br>G4<br>H4<br>N4<br>P4<br>W4<br>Y10 | O    | RPOS/RDATA Output Receive digital output pin. In dual rail mode, this pin is the receive positive data output. In single rail mode, this pin is the receive non-return to zero (NRZ) data output.                                                                                                                                                                                                                                                                                                                       |

# REV. 1.0.4

# **RECEIVER SECTION**

| NAME    | Pin  | Түре | DESCRIPTION                                                                                                                                                     |

|---------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RNEG13  | AA14 | 0    | RNEG/LCV_OF Output                                                                                                                                              |

| RNEG12  | Y21  |      | In dual rail mode, this pin is the receive negative data output. In single rail                                                                                 |

| RNEG11  | P21  |      | mode, this pin is a Line Code Violation / Counter Overflow indicator. If LCV is                                                                                 |

| RNEG10  | N21  |      | selected by programming the appropriate global register and if a line code vio-                                                                                 |

| RNEG9   | H21  |      | lation, a bi-polar violation, or excessive zeros occur, the LCV pin will pull "High" for a minimum of one RCLK cycle. LCV will remain "High" until there are no |

| RNEG8   | G21  |      | more violations. However, if OF is selected the LCV pin will pull "High" if the                                                                                 |

| RNEG7   | C14  |      | internal LCV counter is saturated. The LCV pin will remain "High" until the LCV                                                                                 |

| RNEG6   | C10  |      | counter is reset.                                                                                                                                               |

| RNEG5   | F3   |      |                                                                                                                                                                 |

| RNEG4   | G3   |      |                                                                                                                                                                 |

| RNEG3   | N3   |      |                                                                                                                                                                 |

| RNEG2   | P3   |      |                                                                                                                                                                 |

| RNEG1   | Y3   |      |                                                                                                                                                                 |

| RNEG0   | AA10 |      |                                                                                                                                                                 |

| RTIP13  | AC14 | Į    | Receive Differential Tip Input                                                                                                                                  |

| RTIP12  | Y23  |      | RTIP is the positive differential input from the line interface. Along with the                                                                                 |

| RTIP11  | T23  |      | RRING signal, these pins should be coupled to a 1:1 transformer for proper                                                                                      |

| RTIP10  | P23  |      | operation.                                                                                                                                                      |

| RTIP9   | G23  |      |                                                                                                                                                                 |

| RTIP8   | E23  |      |                                                                                                                                                                 |

| RTIP7   | A14  |      |                                                                                                                                                                 |

| RTIP6   | A9   |      |                                                                                                                                                                 |

| RTIP5   | E1   |      |                                                                                                                                                                 |

| RTIP4   | G1   |      |                                                                                                                                                                 |

| RTIP3   | P1   |      |                                                                                                                                                                 |

| RTIP2   | T1   |      |                                                                                                                                                                 |

| RTIP1   | Y1   |      |                                                                                                                                                                 |

| RTIP0   | AC9  |      |                                                                                                                                                                 |

| RRING13 | AC13 | I    | Receive Differential Ring Input                                                                                                                                 |

| RRING12 | W23  |      | RRING is the negative differential input from the line interface. Along with the                                                                                |

| RRING11 | U23  |      | RTIP signal, these pins should be coupled to a 1:1 transformer for proper oper-                                                                                 |

| RRING10 | N23  |      | ation.                                                                                                                                                          |

| RRING9  | H23  |      |                                                                                                                                                                 |

| RRING8  | D23  |      |                                                                                                                                                                 |

| RRING7  | A13  |      |                                                                                                                                                                 |

| RRING6  | A10  |      |                                                                                                                                                                 |

| RRING5  | D1   |      |                                                                                                                                                                 |

| RRING4  | H1   |      |                                                                                                                                                                 |

| RRING3  | N1   |      |                                                                                                                                                                 |

| RRING2  | U1   |      |                                                                                                                                                                 |

| RRING1  | W1   |      |                                                                                                                                                                 |

| RRING0  | AC10 |      |                                                                                                                                                                 |

# TRANSMITTER SECTION

| NAME                                                                                          | Pin                                                                                          | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxON                                                                                          | AC20                                                                                         | I    | Transmit On/Off Input  Upon power up, the transmitters are powered off. Turning the transmitters On or Off is selected through the microprocessor interface by programming the appropriate channel register if this pin is pulled "High". If the TxON pin is pulled "Low", all 14 transmitters are powered off.  Notes:  1. TxON is ideal for redundancy applications. See the Redundancy Applications Section of this datasheet for more details.  2. Internally pulled "Low" with a 50KΩ resistor.                                                      |

| DMO                                                                                           | Y4                                                                                           | 0    | Digital Monitor Output (Global Pin for All 14-Channels)  When no transmit output pulse is detected for more than 128 TCLK cycles on one of the 14-channels, the DMO pin will go "High" for a minimum of one TCLK cycle. DMO will remain "High" until the transmitter sends a valid pulse.  Note: This pin is for redundancy applications to initiate an automatic switch to the backup card. For individual channel DMO, see the register map.                                                                                                            |

| TCLK13 TCLK12 TCLK11 TCLK10 TCLK9 TCLK8 TCLK7 TCLK6 TCLK5 TCLK5 TCLK4 TCLK3 TCLK2 TCLK1 TCLK1 | Y16<br>Y17<br>AC18<br>D16<br>C17<br>A19<br>B16<br>D7<br>A3<br>B5<br>B6<br>AC6<br>AC5         | I    | Transmit Clock Input TCLK is the input facility clock used to sample the incoming TPOS/TNEG data. If TCLK is absent, pulled "Low", or pulled "High", the transmitter outputs at TTIP/TRING can be selected to send an all "ones" or an all" zero" signal by programming TCLKCNL in the appropriate global register. TPOS/TNEG data can be sampled on either edge of TCLK selected by TCLKE in the appropriate global register.  **Notes:*  1. TCLKE is a global setting that applies to all 14 channels. 2. Internally pulled "Low" with a 50kΩ resistor. |

| TPOS13 TPOS12 TPOS11 TPOS10 TPOS9 TPOS8 TPOS7 TPOS6 TPOS5 TPOS4 TPOS3 TPOS2 TPOS1 TPOS0       | AB17<br>AA18<br>AB18<br>A18<br>D17<br>B19<br>A17<br>B7<br>C4<br>B4<br>D6<br>AB6<br>AA6<br>Y8 | I    | TPOS/TDATA Input  Transmit digital input pin. In dual rail mode, this pin is the transmit positive data input. In single rail mode, this pin is the transmit non-return to zero (NRZ) data input.  Note: Internally pulled "Low" with a 50ΚΩ resistor.                                                                                                                                                                                                                                                                                                    |

# TRANSMITTER SECTION

| NAME    | Pin  | Түре | DESCRIPTION                                                                     |

|---------|------|------|---------------------------------------------------------------------------------|

| TNEG13  | AC17 | I    | Transmit Negative Data Input                                                    |

| TNEG12  | AC19 |      | In dual rail mode, this pin is the transmit negative data input. In single rail |

| TNEG11  | AA17 |      | mode, this pin can be left unconnected.                                         |

| TNEG10  | B17  |      | <b>Note:</b> Internally pulled "Low" with a 50KΩ resistor.                      |

| TNEG9   | B18  |      |                                                                                 |

| TNEG8   | C18  |      |                                                                                 |

| TNEG7   | C16  |      |                                                                                 |

| TNEG6   | C7   |      |                                                                                 |

| TNEG5   | D5   |      |                                                                                 |

| TNEG4   | C5   |      |                                                                                 |

| TNEG3   | C6   |      |                                                                                 |

| TNEG2   | AA7  |      |                                                                                 |

| TNEG1   | Y7   |      |                                                                                 |

| TNEG0   | AB7  |      |                                                                                 |

| TTIP13  | AA13 | 0    | Transmit Differential Tip Output                                                |

| TTIP12  | W21  |      | TTIP is the positive differential output to the line interface. Along with the  |

| TTIP11  | R21  |      | TRING signal, these pins should be coupled to a 1:2 step up transformer for     |

| TTIP10  | M21  |      | proper operation.                                                               |

| TTIP9   | J21  |      |                                                                                 |

| TTIP8   | F21  |      |                                                                                 |

| TTIP7   | C13  |      |                                                                                 |

| TTIP6   | C11  |      |                                                                                 |

| TTIP5   | E3   |      |                                                                                 |

| TTIP4   | H3   |      |                                                                                 |

| TTIP3   | M3   |      |                                                                                 |

| TTIP2   | R3   |      |                                                                                 |

| TTIP1   | W3   |      |                                                                                 |

| TTIP0   | AA11 |      |                                                                                 |

| TRING13 | AB12 | 0    | Transmit Differential Ring Output                                               |

| TRING12 | V22  |      | TRING is the negative differential output to the line interface. Along with the |

| TRING11 | T20  |      | TTIP signal, these pins should be coupled to a 1:2 step up transformer for      |

| TRING10 | M22  |      | proper operation.                                                               |

| TRING9  | J22  |      |                                                                                 |

| TRING8  | D22  |      |                                                                                 |

| TRING7  | B12  |      |                                                                                 |

| TRING6  | B11  |      |                                                                                 |

| TRING5  | C2   |      |                                                                                 |

| TRING4  | H2   |      |                                                                                 |

| TRING3  | M2   |      |                                                                                 |

| TRING2  | U2   |      |                                                                                 |

| TRING1  | V3   |      |                                                                                 |

| TRING0  | AB11 |      |                                                                                 |

# **CONTROL FUNCTION**

| NAME | Pin | Түре | DESCRIPTION                                                                                                                                                                  |

|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST | D4  | I    | Factory Test Mode For normal operation, the TEST pin should be tied to ground.  Note: Internally pulled "Low" with a $50k\Omega$ resistor.                                   |

| ĪCT  | A2  | I    | In Circuit Testing When this pin is tied "Low", all output pins are forced to "High" impedance for in circuit testing.  Note: Internally pulled "High" with a 50ΚΩ resistor. |

# **CLOCK SECTION**

| NAME       | Pin | Түре | DESCRIPTION                                                                                                                                                          |

|------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLKin     | A6  | I    | Master Clock Input                                                                                                                                                   |

|            |     |      | The master clock input can accept a wide range of inputs that can be used to generate T1 or E1 clock rates on a per channel basis. See the register map for details. |

| 8kHzOUT    | D8  | 0    | 8kHz Output Clock                                                                                                                                                    |

| MCLKE1out  | A5  | 0    | 2.048MHz Output Clock                                                                                                                                                |

| MCLKE1Nout | A4  | 0    | 2.048MHz, 4.096MHz, 8.192MHz, or 16.384MHz Output Clock                                                                                                              |

|            |     |      | See the register map for programming details.                                                                                                                        |

| MCLKT1out  | A7  | 0    | 1.544MHz Output Clock                                                                                                                                                |

| MCLKT1Nout | B8  | 0    | 1.544MHz, 3.088MHz, 6.176MHz, or 12.352MHz Output Clock See the register map for programming details.                                                                |

# JTAG SECTION

| NAME     | Pin | Түре | DESCRIPTION                                                                                                          |

|----------|-----|------|----------------------------------------------------------------------------------------------------------------------|

| ATP_TIP  | D21 | I/O  | Analog Test Pin_TIP                                                                                                  |

| ATP_RING | K21 |      | Analog Test Pin_RING                                                                                                 |

|          |     |      | These pins are used to check continuity of the Transmit and Receive TIP and RING connections on the assembled board. |

|          |     |      | See SEE"ANALOG BOARD CONTINUITY CHECK" ON PAGE 40. for more detailed description.                                    |

| TMS      | E4  | I    | Test Mode Select                                                                                                     |

|          |     |      | This pin is used as the input mode select for the boundary scan chain.                                               |

| TCK      | B1  | I    | Test Clock Input                                                                                                     |