# +3 Volt, Serial Input Complete 12-Bit DAC

AD8300

#### **FEATURES**

Complete 12-Bit DAC

No External Components

Single +3 Volt Operation

0.5 mV/Bit with 2.0475 V Full Scale

6 µs Output Voltage Settling Time

Low Power: 3.6 mW

Compact SO-8 1.5 mm Height Package

APPLICATIONS

Portable Communications

Digitally Controlled Calibration

Servo Controls

PC Peripherals

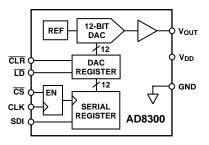

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The AD8300 is a complete 12-bit, voltage-output digital-to-analog converter designed to operate from a single +3 volt supply. Built using a CBCMOS process, this monolithic DAC offers the user low cost, and ease-of-use in single-supply +3 volt systems. Operation is guaranteed over the supply voltage range of  $\pm 2.7 \, \text{V}$  to  $\pm 5.5 \, \text{V}$  making this device ideal for battery operated applications.

The 2.0475 V full-scale voltage output is laser trimmed to maintain accuracy over the operating temperature range of the device. The binary input data format provides an easy-to-use one-half-millivolt-per-bit software programmability. The voltage outputs are capable of sourcing 5 mA.

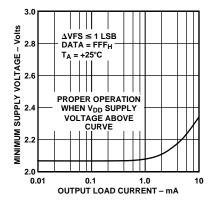

Figure 1. Minimum Supply Voltage vs. Load

A double buffered serial data interface offers high speed, threewire, DSP and microcontroller compatible inputs using data in (SDI), clock (CLK) and load strobe ( $\overline{\text{LD}}$ ) pins. A chip select ( $\overline{\text{CS}}$ ) pin simplifies connection of multiple DAC packages by enabling the clock input when active low. Additionally, a  $\overline{\text{CLR}}$  input sets the output to zero scale at power on or upon user demand.

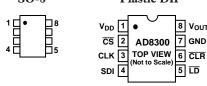

The AD8300 is specified over the extended industrial (-40°C to +85°C) temperature range. AD8300s are available in plastic DIP, and low profile 1.5 mm height SO-8 surface mount packages.

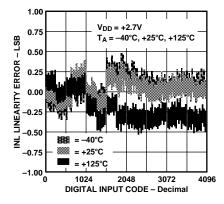

Figure 2. Linearity Error vs. Digital Code and Temperature

# AD8300-SPECIFICATIONS

## +3 V OPERATION (@ $V_{DD}$ = +5 V ± 10%, -40°C $\leq$ T<sub>A</sub> $\leq$ +85°C, unless otherwise noted)

| Parameter                                                                                                                                                                   | Symbol                                                                                                                                                                 | Condition                                                                                                                                                                                                                                                      | Min                                                | Тур                                 | Max                               | Units                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------|-----------------------------------|----------------------------------------------------|

| STATIC PERFORMANCE Resolution Relative Accuracy Differential Nonlinearity <sup>2</sup> Zero-Scale Error Full-Scale Voltage <sup>3</sup> Full-Scale Tempco                   | N<br>INL<br>DNL<br>V <sub>ZSE</sub><br>V <sub>FS</sub><br>TCV <sub>FS</sub>                                                                                            | [Note 1]  Monotonic  Data = $000_H$ Data = $FFF_H$ [Notes 3, 4]                                                                                                                                                                                                | 12<br>-2<br>-1<br>2.039                            | $\pm 1/2$ $\pm 1/2$ $+1/2$ $2.0475$ | +2<br>+1<br>+3<br>2.056           | Bits<br>LSB<br>LSB<br>mV<br>Volts<br>ppm/°C        |

| ANALOG OUTPUT Output Current (Source) Output Current (Sink) Load Regulation Output Resistance to GND Capacitive Load                                                        | $I_{OUT}$ $I_{OUT}$ $L_{REG}$ $R_{OUT}$ $C_{L}$                                                                                                                        | $\begin{array}{l} Data = 800_{H}, \Delta V_{OUT} = 5 \ LSB \\ Data = 800_{H}, \Delta V_{OUT} = 5 \ LSB \\ R_{L} = 200 \ \Omega \ to \infty, Data = 800_{H} \\ Data = 000_{H} \\ No \ Oscillation^{4} \end{array}$                                              |                                                    | 1.5<br>30<br>500                    | 5<br>2<br>5                       | mA<br>mA<br>LSB<br>Ω<br>pF                         |

| LOGIC INPUTS Logic Input Low Voltage Logic Input High Voltage Input Leakage Current Input Capacitance                                                                       | $\begin{array}{c} V_{IL} \\ V_{IH} \\ I_{IL} \\ C_{IL} \end{array}$                                                                                                    |                                                                                                                                                                                                                                                                | 2.1                                                |                                     | 0.6<br>10<br>10                   | V<br>V<br>μA<br>pF                                 |

| INTERFACE TIMING SPECIFICATIONS <sup>4, 5</sup> Clock Width High Clock Width Low Load Pulsewidth Data Setup Data Hold Clear Pulsewidth Load Setup Load Hold Select Deselect | t <sub>CH</sub> t <sub>CL</sub> t <sub>LDW</sub> t <sub>DS</sub> t <sub>DH</sub> t <sub>CLRW</sub> t <sub>LD1</sub> t <sub>LD2</sub> t <sub>CSS</sub> t <sub>CSH</sub> |                                                                                                                                                                                                                                                                | 40<br>40<br>50<br>15<br>15<br>40<br>15<br>40<br>40 |                                     |                                   | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |

| AC CHARACTERISTICS <sup>4</sup> Voltage Output Settling Time  Output Slew Rate DAC Glitch Digital Feedthrough                                                               | t <sub>S</sub> SR                                                                                                                                                      | To $\pm 0.2\%$ of Full Scale<br>To $\pm 1$ LSB of Final Value <sup>6</sup><br>Data = $000_{\rm H}$ to ${\rm FFF_H}$ to $000_{\rm H}$                                                                                                                           |                                                    | 7<br>14<br>2.0<br>15<br>15          |                                   | μs<br>μs<br>V/μs<br>nV/s<br>nV/s                   |

| SUPPLY CHARACTERISTICS Power Supply Range Positive Supply Current  Power Dissipation Power Supply Sensitivity                                                               | $V_{DD\ RANGE}$ $I_{DD}$ $P_{DISS}$ $PSS$                                                                                                                              | $\begin{array}{c} DNL < \pm 1 \; LSB \\ V_{DD} = 3 \; V, \; V_{IL} = 0 \; V, \; Data = 000_{H} \\ V_{DD} = 3.6 \; V, \; V_{IH} = 2.3 \; V, \; Data = FFF_{H} \\ V_{DD} = 3 \; V, \; V_{IL} = 0 \; V, \; Data = 000_{H} \\ \Delta V_{DD} = \pm 5\% \end{array}$ | 2.7                                                | 1.2<br>1.9<br>3.6<br>0.001          | 5.5<br>1.7<br>3.0<br>5.1<br>0.005 | V<br>mA<br>mA<br>mW<br>%/%                         |

Specifications subject to change without notice.

REV. A -2-

LSB = 0.5 mV for 0 V to +2.0475 V output range.

The first two codes (000<sub>H</sub>, 001<sub>H</sub>) are excluded from the linearity error measurement.

<sup>&</sup>lt;sup>3</sup>Includes internal voltage reference error.

<sup>&</sup>lt;sup>4</sup>These parameters are guaranteed by design and not subject to production testing.

<sup>&</sup>lt;sup>5</sup>All input control signals are specified with  $t_R = t_F = 2$  ns (10% to 90% of +3 V) and timed from a voltage level of 1.6 V. <sup>6</sup>The settling time specification does not apply for negative going transitions within the last 6 LSBs of ground. Some devices exhibit double the typical settling time in this 6 LSB region.

# $+ 5 \ V \ OPERATION \ \ (@\ V_{DD} = +5 \ V \ \pm \ 10\%, -40 \underline{\ \ } \ \underline{C \le T_A \le +85 ^{\circ}C}, \ unless \ otherwise \ noted)$

| Parameter                                                                                                                                                                   | Symbol                                                                                                                                                                 | Condition                                                                                                                                                                                                                                          | Min                                                | Тур                                            | Max                               | Units                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------|-----------------------------------|---------------------------------------------|

| STATIC PERFORMANCE Resolution Relative Accuracy Differential Nonlinearity <sup>2</sup> Zero-Scale Error Full-Scale Voltage <sup>3</sup> Full-Scale Tempco                   | N<br>INL<br>DNL<br>V <sub>ZSE</sub><br>V <sub>FS</sub><br>TCV <sub>FS</sub>                                                                                            | [Note 1]  Monotonic  Data = $000_{H}$ Data = $FFF_{H}$ [Notes 3, 4]                                                                                                                                                                                | 12<br>-2<br>-1<br>2.039                            | $\pm 1/2$ $\pm 1/2$ $+1/2$ $+0.0475$ $\pm 1/2$ | +2<br>+1<br>+3<br>2.056           | Bits<br>LSB<br>LSB<br>mV<br>Volts<br>ppm/°C |

| ANALOG OUTPUT Output Current (Source) Output Current (Sink) Load Regulation Output Resistance to GND Capacitive Load                                                        | I <sub>OUT</sub> I <sub>OUT</sub> L <sub>REG</sub> R <sub>OUT</sub> C <sub>L</sub>                                                                                     | Data = $800_{\rm H}$ , $\Delta V_{\rm OUT}$ = 5 LSB<br>Data = $800_{\rm H}$ , $\Delta V_{\rm OUT}$ = 5 LSB<br>$R_{\rm L}$ = $200~\Omega$ to $\infty$ , Data = $800_{\rm H}$<br>Data = $000_{\rm H}$<br>No Oscillation <sup>4</sup>                 |                                                    | 1.5<br>30<br>500                               | 5<br>2<br>5                       | mA<br>mA<br>LSB<br>Ω<br>pF                  |

| LOGIC INPUTS Logic Input Low Voltage Logic Input High Voltage Input Leakage Current Input Capacitance                                                                       | $\begin{array}{c} V_{IL} \\ V_{IH} \\ I_{IL} \\ C_{IL} \end{array}$                                                                                                    |                                                                                                                                                                                                                                                    | 2.4                                                |                                                | 0.8<br>10<br>10                   | V<br>V<br>μΑ<br>pF                          |

| INTERFACE TIMING SPECIFICATIONS <sup>4, 5</sup> Clock Width High Clock Width Low Load Pulsewidth Data Setup Data Hold Clear Pulsewidth Load Setup Load Hold Select Deselect | t <sub>CH</sub> t <sub>CL</sub> t <sub>LDW</sub> t <sub>DS</sub> t <sub>DH</sub> t <sub>CLWR</sub> t <sub>LD1</sub> t <sub>LD2</sub> t <sub>CSS</sub> t <sub>CSH</sub> |                                                                                                                                                                                                                                                    | 30<br>30<br>30<br>15<br>15<br>30<br>15<br>30<br>30 |                                                |                                   | ns            |

| AC CHARACTERISTICS <sup>4</sup> Voltage Output Settling Time  Output Slew Rate DAC Glitch Digital Feedthrough                                                               | t <sub>S</sub> SR                                                                                                                                                      | To $\pm 0.2\%$ of Full Scale<br>To $\pm 1$ LSB of Final Value <sup>6</sup><br>Data = $000_{\rm H}$ to ${\rm FFF_H}$ to $000_{\rm H}$                                                                                                               |                                                    | 6<br>13<br>2.2<br>15<br>15                     |                                   | μs<br>μs<br>V/μs<br>nV/s<br>nV/s            |

| SUPPLY CHARACTERISTICS Power Supply Range Positive Supply Current  Power Dissipation Power Supply Sensitivity                                                               | $V_{\mathrm{DD\ RANGE}}$ $I_{\mathrm{DD}}$ $P_{\mathrm{DISS}}$ $PSS$                                                                                                   | $\begin{array}{c} DNL < \pm 1 \ LSB \\ V_{DD} = 5 \ V, \ V_{IL} = 0 \ V, \ Data = 000_{H} \\ V_{DD} = 5.5 \ V, \ V_{IH} = 2.3 \ V, \ Data = FFF_{H} \\ V_{DD} = 5 \ V, \ V_{IL} = 0 \ V, \ Data = 000_{H} \\ \Delta V_{DD} = \pm 10\% \end{array}$ | 2.7                                                | 1.2<br>2.8<br>6<br>0.001                       | 5.5<br>1.7<br>4.0<br>5.1<br>0.006 | V<br>mA<br>mA<br>mW<br>%/%                  |

#### NOTES

Specifications subject to change without notice.

REV. A -3-

$<sup>^{1}1 \</sup>text{ LSB} = 0.5 \text{ mV}$  for 0 V to +2.0475 V output range.

$<sup>^2 \</sup>text{The first two codes } (000_{\text{H}},\,001_{\text{H}})$  are excluded from the linearity error measurement.

<sup>&</sup>lt;sup>3</sup>Includes internal voltage reference error.

<sup>&</sup>lt;sup>4</sup>These parameters are guaranteed by design and not subject to production testing. <sup>5</sup>All input control signals are specified with  $t_R = t_F = 2$  ns (10% to 90% of +5 V) and timed from a voltage level of 1.6 V.

<sup>&</sup>lt;sup>6</sup>The settling time specification does not apply for negative going transitions within the last 6 LSBs of ground. Some devices exhibit double the typical settling time in this 6 LSB region.

#### AD8300

#### ABSOLUTE MAXIMUM RATINGS\*

| $V_{DD}$ to GND                                         |

|---------------------------------------------------------|

| Logic Inputs to GND0.3 V, +7 V                          |

| $V_{OUT}$ to GND0.3 V, $V_{DD}$ + 0.3 V                 |

| I <sub>OUT</sub> Short Circuit to GND 50 mA             |

| Package Power Dissipation $(T_J Max - T_A)/\theta_{JA}$ |

| Thermal Resistance $\theta_{IA}$                        |

| 8-Lead Plastic DIP Package (N-8) 103°C/W                |

| 8-Lead SOIC Package (SO-8)                              |

| Maximum Junction Temperature (T <sub>J</sub> Max) 150°C |

| Operating Temperature Range40°C to +85°C                |

| Storage Temperature Range65°C to +150°C                 |

| Lead Temperature (Soldering, 10 secs) +300°C            |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING GUIDE**

| Model    | INL | Temp | Package<br>Description | Package<br>Options |

|----------|-----|------|------------------------|--------------------|

| AD8300AN | ±2  | XIND | 8-Lead P-DIP           | N-8                |

| AD8300AR | ±2  | XIND | 8-Lead SOIC            | SO-8               |

NOTES

XIND = -40°C to +85°C.

The AD8300 contains 630 transistors. The die size measures 72 mil  $\times$  65 mil.

#### PIN CONFIGURATIONS SO-8 Plastic DIP

#### PIN DESCRIPTIONS

| Pin# | Name              | Function                                                                                                                                                                                                     |  |

|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | $V_{\mathrm{DD}}$ | Positive power supply input. Specified range of operation +2.7 V to +5.5 V.                                                                                                                                  |  |

| 2    | CS                | Chip Select, active low input. Disables shift register loading when high. Does not affect LD operation.                                                                                                      |  |

| 3    | CLK               | Clock input, positive edge clocks data into shift register.                                                                                                                                                  |  |

| 4    | SDI               | Serial Data Input, input data loads directly into the shift register, MSB first.                                                                                                                             |  |

| 5    | LD                | Load DAC register strobes, active low.<br>Transfers shift register data to DAC register.<br>See Truth Table I for operation. Asynchronous active low input.                                                  |  |

| 6    | CLR               | Resets DAC register to zero condition.<br>Asynchronous active low input.                                                                                                                                     |  |

| 7    | GND               | Analog and Digital Ground.                                                                                                                                                                                   |  |

| 8    | V <sub>OUT</sub>  | DAC voltage output, 2.0475 V full scale with 0.5 mV per bit. An internal temperature stabilized reference maintains a fixed full-scale voltage independent of time, temperature and power supply variations. |  |

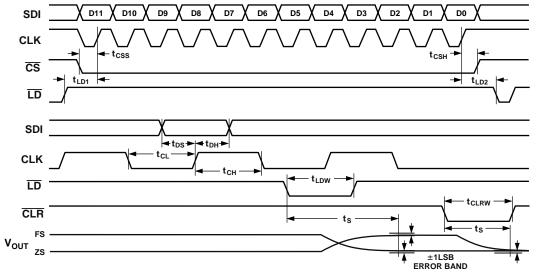

Figure 3. Timing Diagram

-4-

#### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8300 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# Typical Performance Characteristics—AD8300

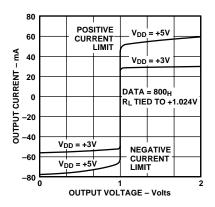

Figure 4. I<sub>OUT</sub> vs. V<sub>OUT</sub>

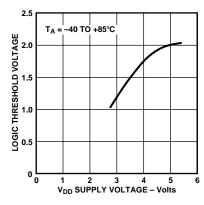

Figure 5. Logic Input Threshold Voltage vs.  $V_{DD}$

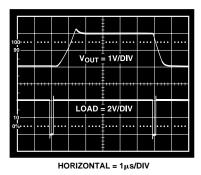

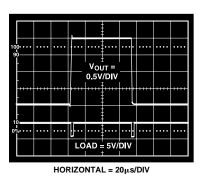

Figure 6. Detail Settling Time

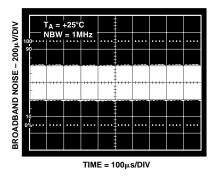

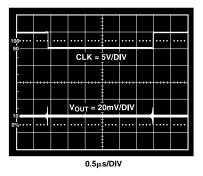

Figure 7. Broadband Noise

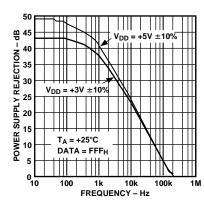

Figure 8. Power Supply Rejection vs. Frequency

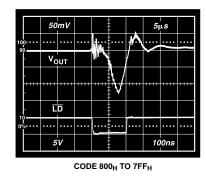

Figure 9. Large Signal Settling Time

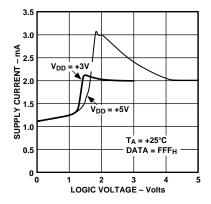

Figure 10. Supply Current vs. Logic Input Voltage

Figure 11. Midscale Transition Performance

Figure 12. Digital Feedthrough vs. Time

REV. A \_5\_

### AD8300

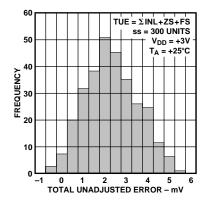

Figure 13. Total Unadjusted Error Histogram

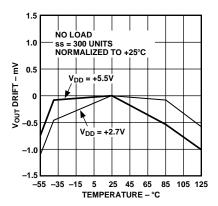

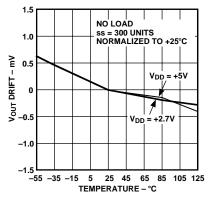

Figure 16. Full-Scale Voltage Drift vs. Temperature

Figure 14. Zero-Scale Voltage Drift vs. Temperature

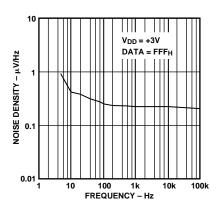

Figure 17. Output Voltage Noise Density vs. Frequency

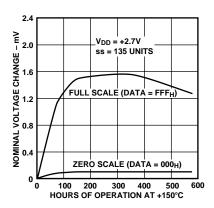

Figure 19. Long Term Drift Accelerated by Burn-In

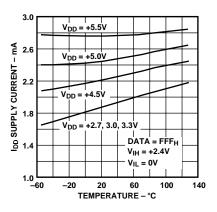

Figure 15. Supply Current vs. Temperature

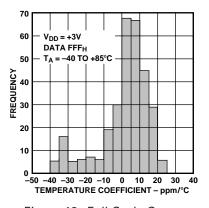

Figure 18. Full-Scale Output Tempco Histogram

-6- REV. A

| Table I. Control Logic Truth Ta |

|---------------------------------|

|---------------------------------|

| CS         | CLK | CLR      | <u>LD</u> | Serial Shift Register Function       | DAC Register Function                        |

|------------|-----|----------|-----------|--------------------------------------|----------------------------------------------|

| H          | X   | Н        | Н         | No Effect                            | Latched                                      |

| L          | L   | Н        | Н         | No Effect                            | Latched                                      |

| L          | Н   | Н        | Н         | No Effect                            | Latched                                      |

| L          | 1   | H        | Н         | Shift-Register-Data Advanced One Bit | Latched                                      |

| $\uparrow$ | L   | H        | Н         | No Effect                            | Latched                                      |

| H          | X   | H        | ↓         | No Effect                            | Updated with Current Shift Register Contents |

| H          | X   | H        | L         | No Effect                            | Transparent                                  |

| Η          | X   | L        | X         | No Effect                            | Loaded with All Zeros                        |

| H          | X   | <b>1</b> | Н         | No Effect                            | Latched All Zeros                            |

#### NOTES

- 1.  $\uparrow$  = Positive Logic Transition;  $\downarrow$  = Negative Logic Transition; X = Don't Care.

- 2. Do not clock in serial data while  $\overline{LD}$  is LOW.

- 3. Data loads MSB first.

#### **OPERATION**

The AD8300 is a complete ready to use 12-bit digital-to-analog converter. Only one +3 V power supply is necessary for operation. It contains a 12-bit laser-trimmed digital-to-analog converter, a curvature-corrected bandgap reference, rail-to-rail output op amp, serial-input register, and DAC register. The serial data interface consists of a serial-data-input (SDI) clock (CLK), and load strobe pins  $\overline{(LD)}$  with an active low  $\overline{CS}$  strobe. In addition an asynchronous  $\overline{CLR}$  pin will set all DAC register bits to zero causing the  $V_{OUT}$  to become zero volts. This function is useful for power on reset or system failure recovery to a known state.

#### D/A CONVERTER SECTION

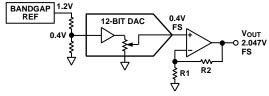

The internal DAC is a 12-bit device with an output that swings from GND potential to 0.4 volt generated from the internal bandgap voltage, see Figure 20. It uses a laser-trimmed segmented R-2R ladder which is switched by N-channel MOSFETs. The output voltage of the DAC has a constant resistance independent of digital input code. The DAC output is internally connected to the rail-to-rail output op amp.

#### **AMPLIFIER SECTION**

The internal DAC's output is buffered by a low power consumption precision amplifier. This low power amplifier contains a differential PNP pair input stage that provides low offset voltage and low noise, as well as the ability to amplify the zero-scale DAC output voltages. The rail-to-rail amplifier is configured with a gain of approximately five in order to set the 2.0475 volt full-scale output (0.5 mV/LSB). See Figure 20 for an equivalent circuit schematic of the analog section.

Figure 20. Equivalent AD8300 Schematic of Analog Portion

The op amp has a 2  $\mu s$  typical settling time to 0.4% of full scale. There are slight differences in settling time for negative slewing signals versus positive. Also negative transition settling time to within the last 6 LSB of zero volts has an extended settling time. See the oscilloscope photos in the typical performances section of this data sheet.

#### **OUTPUT SECTION**

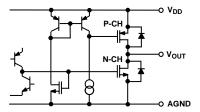

The rail-to-rail output stage of this amplifier has been designed to provide precision performance while operating near either power supply. Figure 21 shows an equivalent output schematic of the rail-to-rail amplifier with its N-channel pull-down FETs that will pull an output load directly to GND. The output sourcing current is provided by a P-channel pull-up device that can source current to GND terminated loads.

Figure 21. Equivalent Analog Output Circuit

The rail-to-rail output stage achieves the minimum operating supply voltage capability shown in Figure 2. The N-channel output pull-down MOSFET shown in Figure 21 has a 35  $\Omega$  on resistance which sets the sink current capability near ground. In addition to resistive load driving capability, the amplifier has also been carefully designed and characterized for up to 500 pF capacitive load driving capability.

#### REFERENCE SECTION

The internal curvature-corrected bandgap voltage reference is laser trimmed for both initial accuracy and low temperature coefficient. Figure 18 provides a histogram of total output performance of full-scale vs. temperature which is dominated by the reference performance.

#### **POWER SUPPLY**

The very low power consumption of the AD8300 is a direct result of a circuit design optimizing use of a CBCMOS process. By using the low power characteristics of the CMOS for the logic, and the low noise, tight matching of the complementary bipolar transistors, good analog accuracy is achieved.

For power-consumption sensitive applications it is important to note that the internal power consumption of the AD8300 is strongly dependent on the actual logic input voltage levels present on the SDI, CLK,  $\overline{\text{CS}}$ ,  $\overline{\text{LD}}$ , and  $\overline{\text{CLR}}$  pins. Since these inputs are standard CMOS logic structures, they contribute static power dissipation dependent on the actual driving logic

REV. A -7-

#### AD8300

$V_{OH}$  and  $V_{OL}$  voltage levels. Consequently, for optimum dissipation use of CMOS logic versus TTL provides minimal dissipation in the static state. A  $V_{INL}$  = 0 V on the logic input pins provides the lowest standby dissipation of 1.2 mA with a +3.3 V power supply.

As with any analog system, it is recommended that the AD8300 power supply be bypassed on the same PC card that contains the chip. Figure 8 shows the power supply rejection versus frequency performance. This should be taken into account when using higher frequency switched-mode power supplies with ripple frequencies of 100 kHz and higher.

One advantage of the rail-to-rail output amplifiers used in the AD8300 is the wide range of usable supply voltage. The part is fully specified and tested over temperature for operation from +2.7 V to +5.5 V. If reduced linearity and source current capability near full scale can be tolerated, operation of the AD8300 is possible down to +2.1 volts. The minimum operating supply voltage versus load current plot in Figure 2 provides information for operation below  $V_{\rm DD}$  = +2.7 V.

#### TIMING AND CONTROL

The AD8300 has a separate serial-input register from the 12-bit DAC register that allows preloading of a new data value MSB first into the serial register without disturbing the present DAC output voltage value. Data can only be loaded when the  $\overline{\text{CS}}$  pin is active low. After the new value is fully loaded in the serial-input register, it can be asynchronously transferred to the DAC register by strobing the  $\overline{\text{LD}}$  pin. The DAC register uses a level sensitive  $\overline{\text{LD}}$  strobe that should be returned high before any new data is loaded into the serial-input register. At any time the contents of the DAC resister can be reset to zero by strobing the  $\overline{\text{CLR}}$  pin which causes the DAC output voltage to go to zero volts. All of the timing requirements are detailed in Figure 3 along with Table I. Control Logic Truth Table.

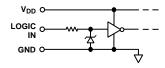

All digital inputs are protected with a Zener type ESD protection structure (Figure 22) that allows logic input voltages to exceed the  $V_{\rm DD}$  supply voltage. This feature can be useful if the user is loading one or more of the digital inputs with a 5 V CMOS logic input voltage level while operating the AD8300 on a +3.3 V power supply. If this mode of interface is used, make sure that the  $V_{\rm OL}$  of the +5 V CMOS meets the  $V_{\rm IL}$  input requirement of the AD8300 operating at 3 V. See Figure 5 for the effect on digital logic input threshold versus operating  $V_{\rm DD}$  supply voltage.

Figure 22. Equivalent Digital Input ESD Protection

#### **Unipolar Output Operation**

This is the basic mode of operation for the AD8300. The AD8300 has been designed to drive loads as low as 400  $\Omega$  in parallel with 500 pF. The code table for this operation is shown in Table II.

#### APPLICATIONS INFORMATION

See DAC8512 data sheet for additional application circuit ideas.

Table II. Unipolar Code Table

| Hexadecimal<br>Number in<br>DAC Register | Decimal<br>Number in<br>DAC Register | Analog Output<br>Voltage (V) |  |  |

|------------------------------------------|--------------------------------------|------------------------------|--|--|

| FFF                                      | 4095                                 | +2.0475                      |  |  |

| 801                                      | 2049                                 | +1.0245                      |  |  |

| 800                                      | 2048                                 | +1.0240                      |  |  |

| 7FF                                      | 2047                                 | +1.0235                      |  |  |

| 000                                      | 0                                    | +0.0000                      |  |  |

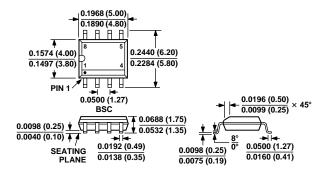

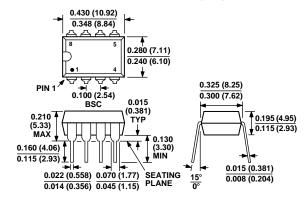

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 8-Lead SOIC (SO-8)

#### 8-Lead Plastic DIP (N-8)

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

**«FORSTAR»** (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А