# CY3677

# **Evaluation Kit User Guide**

Doc. No. 002-12185 Rev. \*D

Cypress Semiconductor 198 Champion Court San Jose, CA95134-1709 Phone (USA): 800.858.1810 Phone (Intnl): +1.408.943.2600 www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2016-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# Contents

| Safe | ety Inf | ormation                                                          | 5  |

|------|---------|-------------------------------------------------------------------|----|

| 1    | Intro   | duction                                                           | 6  |

|      | 1.1     | CY3677 EVK Contents                                               | 6  |

|      | 1.2     | Getting Started                                                   |    |

|      | 1.3     | Additional Learning Resources                                     |    |

|      | 1.4     | Technical Support                                                 |    |

|      | 1.5     | Document Conventions                                              | 8  |

|      | 1.6     | Acronyms                                                          |    |

| 2    | Soft    | ware Installation                                                 | 9  |

|      | 2.1     | Before You Begin                                                  | 9  |

|      | 2.2     | Install Software                                                  | 9  |

|      | 2.3     | Install Hardware                                                  | 12 |

|      | 2.4     | Uninstall Software                                                | 12 |

| 3    | Kit C   | Operation                                                         | 13 |

|      | 3.1     | Theory of Operation                                               | 13 |

|      | 3.2     | Functional Description                                            |    |

|      | 3.3     | CY3677 EVK USB Connection                                         |    |

|      | 3.4     | Programming the CY29430                                           |    |

|      | 3.5     | Functional Programming of the CY29430                             |    |

|      |         | 3.5.1 Generating and Programming the Device Configuration Profile |    |

|      | 3.6     | eFuse Programming of the CY29430                                  |    |

|      | 3.7     | Custom Profile Generation                                         | 20 |

| 4    | Hard    | lware                                                             | 21 |

|      | 4.1     | Board Overview                                                    | 21 |

|      | 4.2     | Board Details                                                     | 23 |

|      |         | 4.2.1 Default Jumper Settings                                     | 23 |

|      |         | 4.2.2 Power Settings                                              | 23 |

|      |         | 4.2.3 Functional Programming                                      |    |

|      |         | 4.2.4 LED Indicators                                              |    |

|      |         | 4.2.5 On-Board Crystal                                            |    |

|      |         | 4.2.6 TCXO Input Reference                                        |    |

|      |         | 4.2.7 Frequency Select (FS)                                       |    |

|      | 4.3     | Evaluating Different I/O Standards Using the CY3677 EVK           | 25 |

| 5    | Exan    | nple Projects                                                     | 27 |

|      | 5.1     | Example Project Configuration Details                             | 27 |

#### Contents

|     | 5.2   | Evaluation of VCXO Functionality                              |    |

|-----|-------|---------------------------------------------------------------|----|

| Α.  | Арре  | endix                                                         |    |

|     | A.1.  | BCP Script to Disable the Default Power-up Profile of CY29430 |    |

| в.  | Арре  | endix                                                         | 34 |

|     | B.1.  | Termination Settings of Differential Clock Outputs            |    |

|     | B.2.  | Termination Settings of LVCMOS Clock Output                   |    |

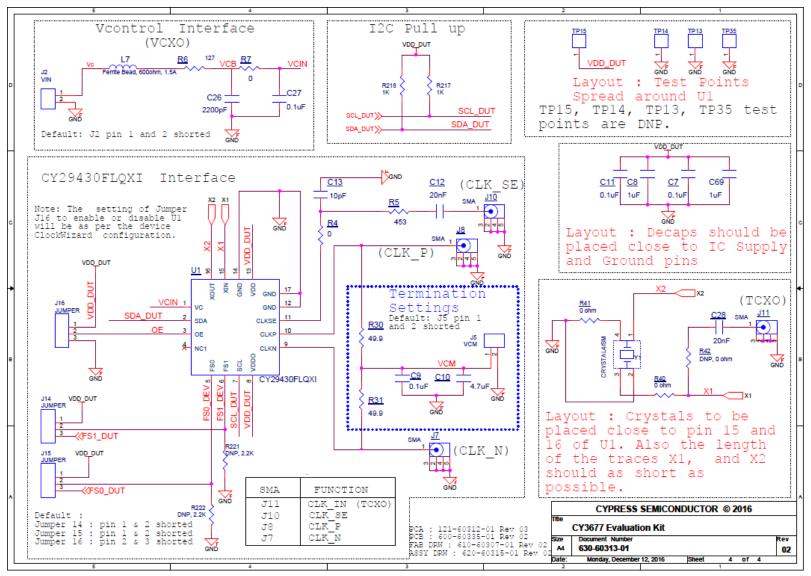

|     | B.3.  | Schematics                                                    |    |

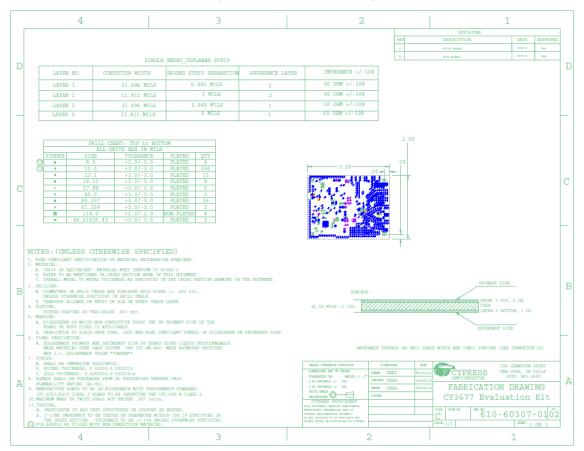

|     | B.4.  | Fabrication Drawing                                           | 40 |

|     | B.5.  | Bill of Materials                                             | 41 |

| Rev | ision | History                                                       | 44 |

|     | Docu  | ument Revision History                                        | 44 |

# Safety Information

The CY3677 Evaluation Kit is intended for use as an evaluation platform for hardware or software in a laboratory environment. The board is an open system design, which does not include a shielded enclosure, so the board may cause interference to other electrical or electronic devices in close proximity. In a domestic environment, this product may cause radio interference. In such cases, the user may be required to take adequate preventive measures. Also, this board should not be used near any medical equipment or RF devices.

Attaching additional wiring to this product or modifying the product operation from the factory default may affect its performance and cause interference with other apparatus in the immediate vicinity. If such interference is detected, suitable mitigating measures should be taken.

The CY3677 Evaluation Kit contains electrostatic discharge (ESD)-sensitive devices. Electrostatic charges readily accumulate on the human body and any equipment, and can discharge without detection. Permanent damage may occur on devices subjected to high-energy discharges. Proper ESD precautions are recommended to avoid performance degradation or loss of functionality. Store unused CY3677 Evaluation Kit boards in the protective shipping package.

#### **General Safety Instructions**

#### **ESD** Protection

ESD can damage boards and associated components. Cypress recommends that the user perform procedures only at an ESD workstation. If an ESD workstation is not available, use appropriate ESD protection by wearing an antistatic wrist strap attached to the chassis ground (any unpainted metal surface) on the board when handling parts.

#### **Handling Boards**

The CY3677 Evaluation Kit is sensitive to ESD. Hold the board only by its edges. After removing the board from its box, place it on a grounded, static-free surface. Use a conductive foam pad if available. Do not slide the board over any surface.

#### **Certification Disclaimer**

This kit is intended for demonstration, evaluation, or development purposes only and is not considered by Cypress Semiconductor to be a finished end-product fit for general consumer use. It generates and can radiate radio frequency energy and has not been specifically tested for CE certification compliance. Operation of this equipment in other environments may cause interference with radio communications, in which case users at their own expense will be required to take whatever measures may be required to correct this interference.

# 1 Introduction

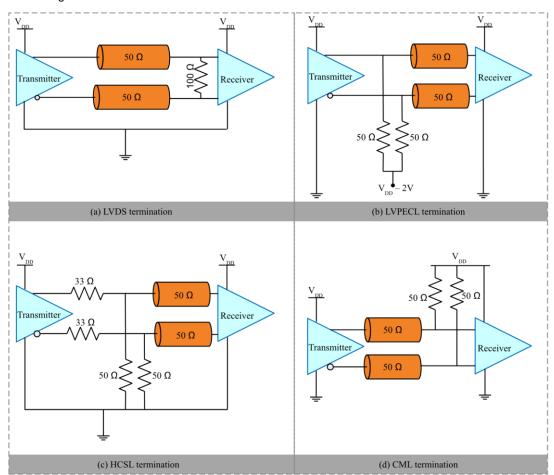

Thank you for your interest in the CY3677 Evaluation Kit (EVK). The CY3677 EVK is designed to enable you to evaluate the programmable clock device CY29430, the latest addition to the Cypress timing product portfolio. The clock device CY29430 is a high-performance programmable oscillator with one fractional PLL that generates any frequency up to 2.1 GHz with jitter as low as 110 fs. The device offers one differential output and one single-ended output. The device can be configured to generate either a single-ended output or a differential output but not both simultaneously. The device comes in a 16-pin QFN package for industrial applications. The differential I/O standards supported are LVDS, LVPECL, High-Speed Current Steering Logic (HCSL), and Current Mode Logic (CML). The single-ended signal supported is LVCMOS. The device also supports features such as a Voltage-Controlled Crystal Oscillator (VCXO), and provides the user with an I<sup>2</sup>C programming interface. The device supports four frequency profiles, which can be switched dynamically using external Frequency Select (FS0 and FS1) signals. There are two jumpers provided on the EVK to perform frequency selection on the board.

The CY3677 EVK allows you to evaluate output clock signals by making required on-board termination settings.

The CY3677 EVK is available through the Cypress Online Store or through our distributors.

#### 1.1 CY3677 EVK Contents

The CY3677 EVK includes the following:

- CY3677 Evaluation Board

- USB Standard-A to Mini-B cable

- Quick Start Guide

Inspect the contents of the kit. If you find any part missing, contact your nearest Cypress sales office for assistance: www.cypress.com/support.

### 1.2 Getting Started

To learn the solution quickly and apply it to your design, refer to the CY3677 Quick Start Guide inside the kit box or in the installation directory. The default location for the kit documents is:

<Install Directory>\CY3677 Evaluation Kit\<version>\Documentation

This guide will help you get acquainted with the CY3677 EVK:

The Software Installation chapter describes the installation of the kit software.

The Kit Operation chapter describes the major features of the CY3677 Evaluation Kit.

The Hardware chapter describes the hardware content of the CY3677 Evaluation Kit and the hardware operation.

The Example Projects chapter describes the multiple projects that will help you understand how to evaluate different supported output standards on this kit.

The Appendix captures DC/AC Measurements of Clock Outputs, Schematics, Fab Drawing, and the bill of materials (BOM).

#### 1.3 Additional Learning Resources

Visit www.cypress.com/CY3677 and www.cypress.com/HPO for additional learning resources including datasheets and application notes.

#### 1.4 Technical Support

For assistance, go to\_www.cypress.com/support, or contact our customer support at +1(800) 541-4736 Ext. 2 (in the USA), or +1 (408) 943-2600 Ext. 2 (International).

# 1.5 Document Conventions

| Table 1-1 | Document | Conventions | for | Guides |

|-----------|----------|-------------|-----|--------|

|           | Document | COnventions | 101 | Guiues |

| Convention         | Usage                                                                                                                  |

|--------------------|------------------------------------------------------------------------------------------------------------------------|

| Courier New        | Displays file locations, user entered text, and source code:<br>C:\cd\icc\                                             |

| Italics            | Displays file names and reference documentation.                                                                       |

| [Bracketed, Bold]  | Displays keyboard commands in procedures:<br>[Enter] or [Ctrl] [C]                                                     |

| File > Open        | Represents menu paths:<br>File > Open > New Project                                                                    |

| Bold               | Displays commands, menu paths and icon names in procedures:<br>Click the <b>File</b> icon and then click <b>Open</b> . |

| Times New Roman    | Displays an equation:<br>2 + 2 = 4                                                                                     |

| Text in gray boxes | Describes Cautions or unique functionality of the product.                                                             |

# 1.6 Acronyms

| Acronym                                                                     | Definition                                          |  |  |  |  |

|-----------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|

| ВОМ                                                                         | Bill of Materials                                   |  |  |  |  |

| CML                                                                         | Current Mode Logic                                  |  |  |  |  |

| DNP, DNM                                                                    | Do Not Populate, Do Not Mount                       |  |  |  |  |

| FS                                                                          | Frequency Select                                    |  |  |  |  |

| HCSL High-Speed Current Steering Logic                                      |                                                     |  |  |  |  |

| l <sup>2</sup> C                                                            | Inter-Integrated Circuit                            |  |  |  |  |

| JEDEC                                                                       | Joint Electron Device Engineering Council           |  |  |  |  |

| LDO Low-Dropout                                                             |                                                     |  |  |  |  |

| LVCMOS                                                                      | Low Voltage Complementary Metal Oxide Semiconductor |  |  |  |  |

| LVPECL Low Voltage Positive Emitter Coupled Logic                           |                                                     |  |  |  |  |

| LVPECL2 Low Voltage Positive Emitter Coupled Logic with zero Common-mode cu |                                                     |  |  |  |  |

| LVDS                                                                        | Low Voltage Differential Signaling                  |  |  |  |  |

| OE                                                                          | Output Enable                                       |  |  |  |  |

| ОТЗ                                                                         | Third Overtone Crystal                              |  |  |  |  |

| SMA                                                                         | Subminiature Version A                              |  |  |  |  |

| VCXO                                                                        | Voltage-Controlled Crystal Oscillator               |  |  |  |  |

| тсхо                                                                        | Temperature Compensated Crystal Oscillator          |  |  |  |  |

| ОТР                                                                         | One-Time Programmable                               |  |  |  |  |

# 2 Software Installation

This chapter describes the steps to install the software tools and packages on a PC for using the CY3677 Evaluation Kit.

#### 2.1 Before You Begin

All Cypress software installations require administrator privileges. Ensure that you have the required privileges on the system for successful installation. Before you install the kit software, close any other Cypress software that is currently running.

#### 2.2 Install Software

Follow these steps to install the CY3677 Evaluation Kit software:

- 1. Download the CY3677 Evaluation Kit software from www.cypress.com/CY3677. The software is available in the following formats:

- a. CY3677 Evaluation Kit Complete Setup: This installation package contains the files related to the CY3677 Evaluation Kit. However, it does not include the Windows Installer or Microsoft .NET Framework packages. If these packages are not available on your computer, the installer directs you to download and install them from the Internet.

- b. CY3677 Evaluation Kit Only: This executable file installs only the CY3677 EVK contents, which include example projects, hardware files, and user documents. This package can be used if all the software prerequisites are installed on your PC.

- c. **CY3677 Evaluation Kit ISO:** This file is a complete package, stored in a CD/DVD-ROM image format that you can use to create a CD/DVD or extract using an ISO extraction program such as WinZip or WinRAR. The file can also be mounted similar to a virtual CD/DVD using virtual drive programs such as Virtual CloneDrive and MagicISO. This file includes all the required software, utilities, drivers, hardware files, and user documents.

- 2. If you have downloaded the ISO file, mount it on a virtual drive. If you do not have a virtual drive to mount, extract the ISO contents using the appropriate ISO extractor (such as MagicISO or PowerISO). Double-click *cyautorun.exe* in the root directory of the extracted content or the mounted ISO if the "Autorun from CD/DVD" option is not enabled on the PC. The installation window will appear automatically.

**Note:** If you are using the "Kit Complete Setup" or "Kit Only" file, then go to step 4 for installation.

3. Click Install CY3677 EVK to start the installation as shown in Figure 2-1.

Figure 2-1. Installer Screen

4. Click **Change...** if you want to install the CY3677 EVK in a location other than the default, and then click **Next** as shown in Figure 2-2.

**Note:** When you click **Next**, the CY3677 EVK installer automatically installs the required software, if it is not present on your computer. The pre-requisites are ClockWizard 2.1 and PSoC Programmer 3.25.0 or later.

| CY3677 Evaluation Kit - InstallS | hield Wiz                      | ard                                                                                                                                                                                                                   | ×             |

|----------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                  | Wele<br>Eval<br>The I<br>on yo | come to the InstallShield Wizard<br>luation Kit<br>InstallShield Wizard will install CY3677 E<br>bur computer. To continue, click Next.<br>older where setup will install files.<br>Install CY3677 Evaluation Kit to: | valuation Kit |

|                                  |                                | C:\\Cypress                                                                                                                                                                                                           | Change        |

|                                  |                                | < Back Next >                                                                                                                                                                                                         | Cancel        |

Figure 2-2. InstallShield Wizard

Select the Installation Type (see Figure 2-3). The drop-down menu contains three options: Typical (installs all the required features), Custom (lets you choose the features to be installed), and Complete (installs all the contents). Click Next after you select the Installation Type.

Note: It is recommended that you choose the **Typical** Installation Type.

Figure 2-3. Product Installation Overview

| CyInstaller for CY3677 Evaluation Kit<br>roduct Installation Overview<br>Choose the install type that best suits your needs                                             | 2 <b>-</b>    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Choose the type of installation<br>Product:<br>CY3677 Evaluation Kit<br>Installation Type:<br>Typical<br>Installs the most common features of<br>CY3677 Evaluation Kit. |               |

| Contact Us                                                                                                                                                              | Next > Cancel |

6. Read and accept the End-User License Agreement, and then click Next.

When the installation begins, a list of packages appears on the Installation page. A green check mark appears next to each package after successful installation.

- 7. Enter your contact information or select the Continue Without Contact Information check box.

- 8. Click Finish to complete the CY3677 Evaluation Kit installation.

After the installation is complete, the kit contents are available at:

<Install\_Directory>\CY3677 Evaluation Kit\<version>.

Default location:

Windows 7 (64-bit): C:\Program Files (x86)\Cypress\CY3677 Evaluation Kit

Windows 7 (32-bit): C:\Program Files\Cypress\CY3677 Evaluation Kit

## 2.3 Install Hardware

No additional hardware installation is required for this kit.

### 2.4 Uninstall Software

You can uninstall the software using one of the following methods:

- Go to Start > All Programs > Cypress > Cypress Update Manager > Cypress Update Manager, and select the specific software package. Click the Uninstall button.

- Go to Start > Control Panel > Programs and Features, and select the specific software package. Click the Uninstall/Change button.

# 3 Kit Operation

The CY3677 EVK can be used to evaluate the CY29430, a high performance programmable oscillator. Connect the CY3677 kit through USB to a PC running Cypress's ClockWizard 2.1 software. The clock device CY29430 can be configured and programmed to generate frequencies with best-in-class performance.

### 3.1 Theory of Operation

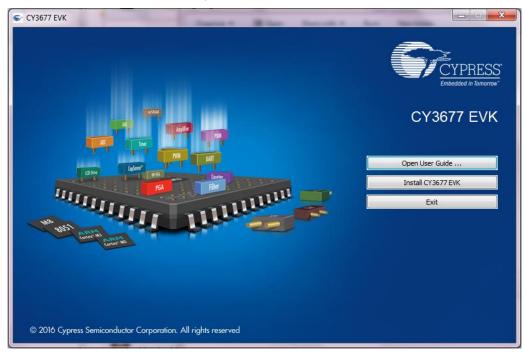

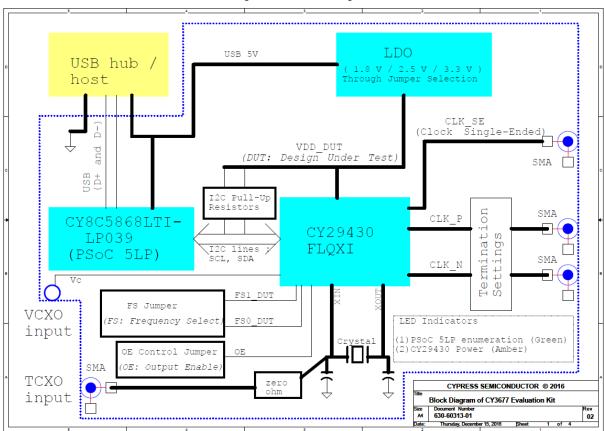

The CY3677 EVK offers one differential clock output and one single-ended clock output (only one operates at a time) for evaluation. The CY29430 device uses an on-board crystal or Temperature Compensated Crystal Oscillator (TCXO) reference input.

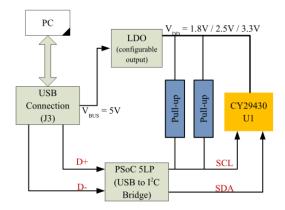

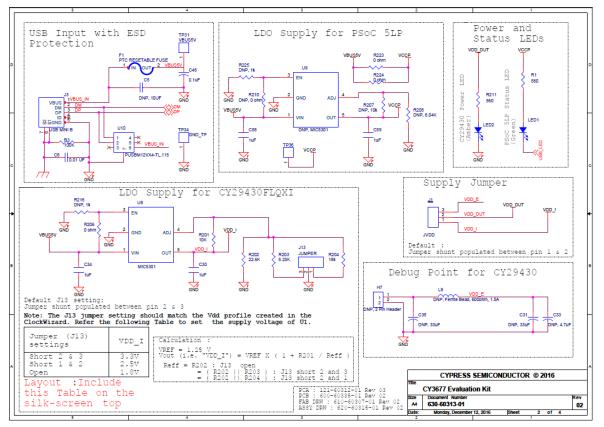

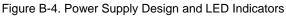

The kit is capable of generating fixed 3.3 V, 2.5 V, and 1.8 V voltages from a 5-V USB port. The on-board PSoC 5LP (U7) performs the USB-to-I<sup>2</sup>C conversion. There is one power LED (LED2) driven from the on-board LDO supply and one status LED (LED1) controlled by PSoC 5LP. The output of LDO regulator (U8) is configurable (3.3 V, 2.5 V, or 1.8 V) through jumper J13.

**Note:** An additional on-board LDO (U9 – not shown in Figure 3-1) generates a fixed 3.3-V supply for the PSoC 5LP in the **CY3677 Rev** \*\* EVK. This feature has been changed in **CY3677 Rev** \***A** EVK where the PSoC 5LP is directly powered by a 5-V USB supply. The CY3677 kit revision is printed on the label at the back of the kit box.

Figure 3-1 illustrates the block diagram of the CY3677 EVK.

Figure 3-1. CY3677 EVK Block Diagram

## 3.2 Functional Description

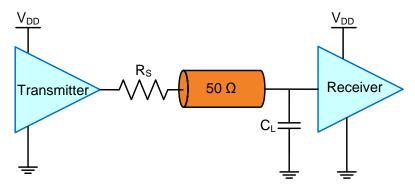

The differential clock outputs (J7, J8) and single-ended output (J10) are driven out on to SMA connectors. The EVK is populated with  $50-\Omega$  resistors (R30 and R31) for output termination. The termination options of the differential outputs on the evaluation board are listed in the Hardware chapter. These termination circuits are designed to terminate the output clocks in LVPECL, LVDS, HCSL, LVPECL2, and CML signal types by populating, or by not populating the J5 jumper shunt. The single-ended (LVCMOS) clock does not need any on-board termination settings.

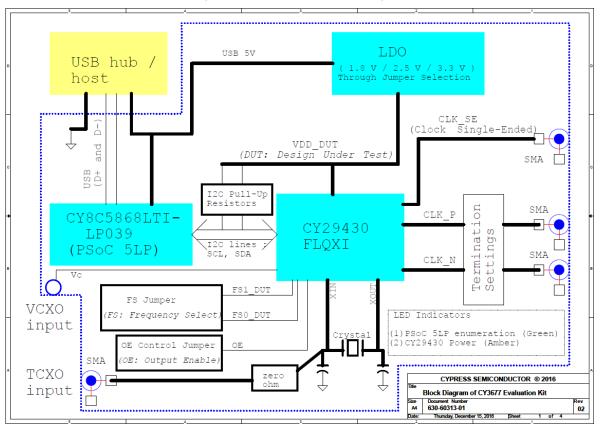

Figure 3-2 illustrates the top view and bottom view of the CY3677 EVK.

CY3677 EVK Top View

CY3677 EVK Bottom View

### 3.3 CY3677 EVK USB Connection

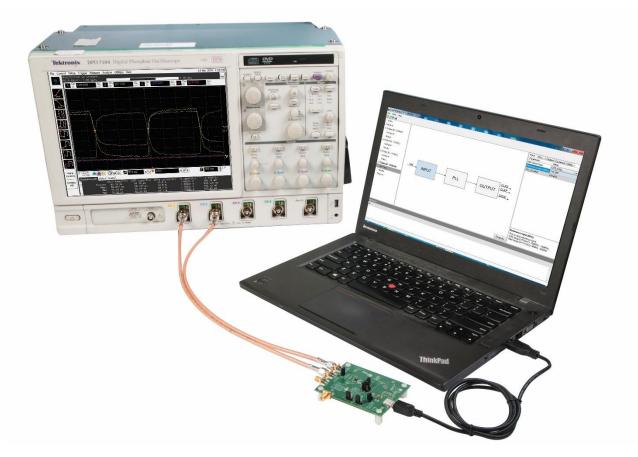

The CY29430 clock device on the kit is loaded with a default configuration. To view and evaluate other configurations on an oscilloscope (or other standard instruments), the clock device must be programmed with the desired configuration. The ClockWizard 2.1 application is required for programming any configuration. Therefore, the kit should be connected (see Figure 3-3) to a PC through a USB port for programming.

The kit enumerates as a USB Composite Device as part of the Driver Software installation on Windows.

Figure 3-4. USB Driver Installation

| Installing device driver soft       | ware                                 |  |

|-------------------------------------|--------------------------------------|--|

| USB Composite Device                | 🖌 Ready to use                       |  |

| KitProg USBUART                     | Searching Windows Update             |  |

| KitBridge                           | Searching Windows Update             |  |

| KitProg Programmer                  | Searching Windows Update             |  |

|                                     | m Windows Update might take a while. |  |

| Skip obtaining driver software from | Windows Update                       |  |

After the driver installation is complete, the device is ready to use.

| Driver Software Installation                                                              | the first                                                    | ×     |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------|

| Your device is ready to use                                                               |                                                              |       |

| USB Composite Device<br>USB Input Device<br>KitProg (1.2.3.3)<br>KitProg USB-UART (COM32) | Ready to use<br>Ready to use<br>Ready to use<br>Ready to use |       |

|                                                                                           |                                                              | Close |

#### 3.4 Programming the CY29430

The CY29430 device has an internal one-time programmable (OTP) nonvolatile memory called eFuse. The device also contains volatile memory that stores an exact copy of the eFuse at the release of reset at power-up. The output frequency depends on the configurations in the volatile memory. Writing the entire device configuration in the volatile memory section of a blank device after power-up, is called Functional Programming. The CY3677 kit is shipped with a programmed CY29430 device. This program is written to a specific internal memory location of the device. This kit can be used to check both the Functional and eFuse Programming of the device using ClockWizard 2.1. See Functional Programming of the CY29430 and eFuse Programming of the CY29430 for details.

**Kit Operation**

# 3.5 Functional Programming of the CY29430

ClockWizard 2.1 is used for functional programming of the CY29430. A configuration created in ClockWizard 2.1 can be downloaded to the volatile memory section of the device.

The example ClockWizard 2.1 projects can be found at the following location:

<Install\_Directory>\CY3677 Evaluation Kit\<version>\Firmware\Example Projects

Configuration profiles generated from these projects can be used to evaluate the CY29430 device on the CY3677 EVK. Refer to Functional Programming for the kit's hardware settings prior to programming. It is recommended that you copy the example projects to another location if you want to make any modifications to the settings so that the default project is retained in the installation directory.

#### CAUTION Before programming the CY3677 EVK through ClockWizard 2.1, it is recommended to go through CAUTION ClockWizard 2.1 configuration may cause potential damage of the EVK. Specifically, the voltage setting on the kit selected with J13 must match the voltage setting within the configuration to be programmed.

#### 3.5.1 Generating and Programming the Device Configuration Profile

The ClockWizard 2.1 is used to generate profiles and to perform functional programming of the device.

- 1. Verify that the power supply voltage jumper (J13) is set for the voltage used in the project that you intend to program. See the Hardware section for details.

- 2. Connect the CY3677 EVK to your PC through the supplied USB cable.

- 3. To launch the ClockWizard 2.1 application, go to Start > All Programs > Cypress > ClockWizard 2.1.

The workspace files are located in the Workspace folders. The four workspaces available are:

- CY3677\_LVPECL\_3p3.cpj

- CY3677\_LVDS\_2p5.cpj

- CY3677\_HCSL\_2p5.cpj

- CY3677\_LVCMOS\_1p8.cpj

- 4. Select the **File** menu in ClockWizard 2.1, select **Open workspace**, browse the required workspace file with a *.cpj* extension, and then click **Open**. Each Workspace file can contain multiple projects.

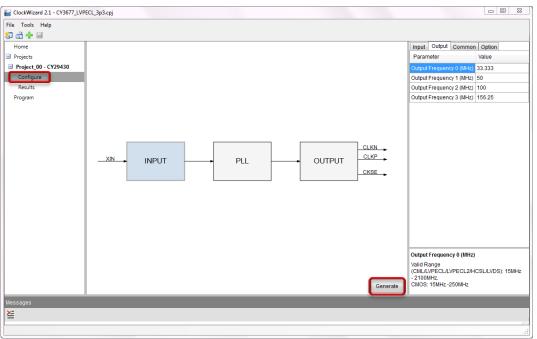

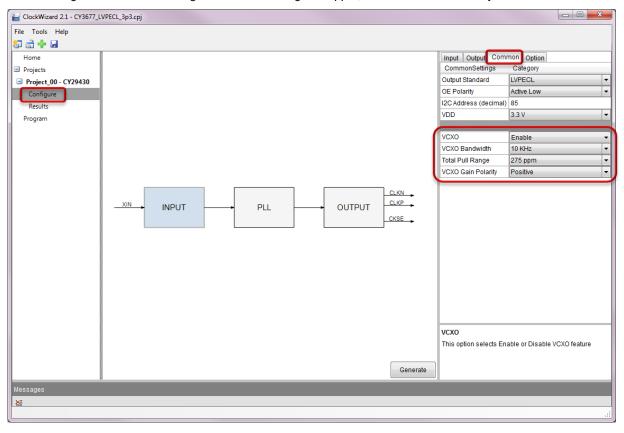

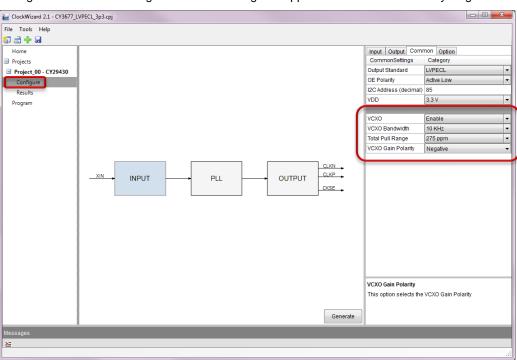

- 5. Click **Configure**, as shown in Figure 3-6. The various configuration parameters appear on the right panel of the block diagram in the tabbed interface. For more information on configuration parameters, refer to the ClockWizard 2.1 User Guide located in **Help** > **User guide** of the ClockWizard 2.1 software.

- 6. Click the **Generate** button (see Figure 3-6). This will generate the JEDEC file for the configuration selected. On completion of generation, the Results are displayed as shown in Figure 3-7.

Figure 3-6. Generating a Configuration Profile using ClockWizard 2.1

7. Click **Results** in the navigation pane to view the results at any time after a JEDEC file has been generated for a configuration, as shown in Figure 3-7.

| Home Input and output      |                    |                        |                                                             |                       | JEDEC file:                                                   | Project_   | <u>00.jed</u>            |              |              |

|----------------------------|--------------------|------------------------|-------------------------------------------------------------|-----------------------|---------------------------------------------------------------|------------|--------------------------|--------------|--------------|

| ects<br>oject_00 - CY29430 | Output Frequency   |                        | Target Frequency (MHz) Calculated Frequency (MHz) PPM Error |                       | Created on 10/24/2016 2:08 PM<br>Register programming details |            |                          |              |              |

| onfigure<br>esults         | Profile 0          |                        | 33.333 33.3329                                              | 32999970867 -0.000874 | Device slave address: 0x55                                    |            |                          |              |              |

| gram                       | Profile 1          |                        | 50                                                          | 49.9999               | 999532                                                        | -0.000936  | Register name            | Address      | Value        |

| grann                      | Profile 2          |                        | 100                                                         | 99,9999               | 999193                                                        | -0.000807  | DIVO FS0                 | 0x10         | 0xCD         |

|                            | Profile 3          |                        | 156.25                                                      | 156.249               | 999863906                                                     | -0.000871  | DIVN_FS0                 | 0x11         | 0x3C         |

|                            |                    |                        |                                                             | 1                     |                                                               |            | DIVO_MISC                | 0x12         | 0x0A         |

|                            | Common<br>Settings | Catego                 | ry                                                          |                       | Settings                                                      |            | DIVN_FRAC0<br>DIVN_FRAC1 |              | 0xF8<br>0x9B |

|                            | Input              | Ref Clo                | ck Type                                                     |                       | OT3 XTAL                                                      |            | DIVN_FRAC2               | 0x15         | 0xCA         |

|                            |                    | Referen                | ce Input (MHz)                                              |                       | 114.285                                                       |            | DIVO_FS1                 | 0x20         | 0x89         |

|                            |                    | XO Doubler             |                                                             |                       | Disable                                                       |            | DIVN_FS1                 | 0x21         | 0x3C         |

|                            | Common             | Output S               | Standard                                                    |                       | LVPECL                                                        |            | DIVO_MISC<br>DIVN_FRAC0  |              | 0x0A<br>0x8C |

|                            |                    | OE Polarity Active Low |                                                             | Active Low            |                                                               | DIVN_FRAC1 |                          | 0x8C         |              |

|                            |                    |                        |                                                             |                       | DIVN FRAC2                                                    |            | 0xF0                     |              |              |

|                            |                    | VDD                    |                                                             |                       | 3.3 V                                                         |            | DIVO_FS2                 | 0x30         | 0x45         |

|                            |                    | VCXO                   |                                                             |                       | Disable                                                       |            | DIVN_FS2                 | 0x31         | 0x3C         |

|                            |                    |                        | andwidth                                                    |                       | 10 KHz                                                        |            | DIVO_MISC                |              | 0x0A         |

|                            |                    |                        | II Range                                                    |                       | 150 ppm                                                       |            | DIVN_FRAC0               |              | 0xBA         |

|                            |                    |                        | ain Polarity                                                |                       | Positive                                                      |            | DIVN_FRAC1<br>DIVN_FRAC2 |              | 0x18<br>0x60 |

|                            | Option             |                        | DATA_1 (0xD4)                                               |                       | 0                                                             |            | DIVO FS3                 | 0x35<br>0x40 | 0x2C         |

|                            | opuon              |                        | DATA_2 (0xD5)                                               |                       | 0                                                             |            | DIVN_FS3                 | 0x41         | 0x3C         |

|                            |                    |                        | DATA 3 (0xD6)                                               |                       | 0                                                             |            | DIVO_MISC                | 0x42         | 0x0A         |

|                            |                    | 002.0                  | 5/11/ <u>-</u> 0 (0/2/0)                                    |                       |                                                               |            | DIVN_FRAC0               | 0x43         | 0xA3         |

|                            |                    |                        |                                                             |                       |                                                               |            | •                        | <b></b>      | - · · ·      |

| aes                        |                    |                        |                                                             |                       |                                                               |            |                          |              |              |

Figure 3-7. View Results Generated from the Configuration Profile using ClockWizard 2.1

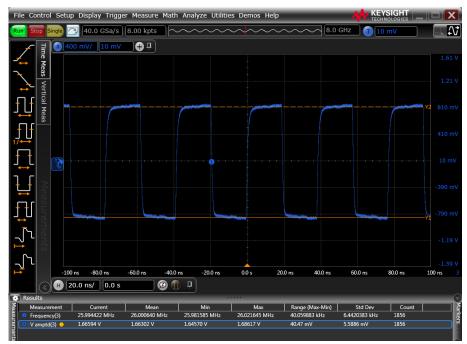

8. To program the CY29430 device, select **Program** in the left navigation pane, as shown in Figure 3-8. Choose the appropriate device in the **Select Device (I2C Master)** drop-down list prior to programming, and then click the **Functional Program** button. This will program the device directly from ClockWizard. LED1 blinks to indicate that the device is being programmed. The required output will appear on the oscilloscope.

For more information, refer to the ClockWizard 2.1 User Guide located in **Help** > **User guide** of the ClockWizard 2.1 software.

|            | Program - Project_00                                 |                         |                                   |                                  |

|------------|------------------------------------------------------|-------------------------|-----------------------------------|----------------------------------|

| - CY29430  | Device selection                                     |                         | JEDEC programm                    | ning                             |

|            | Select Device (I2C Master): KitProg/100F0D28010D5400 |                         | <ul> <li>Select JEDEC:</li> </ul> | Project_00                       |

|            |                                                      |                         |                                   | eFuse Program Functional Program |

|            | Large change programming —                           |                         |                                   | Small change programming         |

|            | Profile 0 (MHz): 33.333                              | VCXO:                   | Enable                            | ▼ Select FS profile: 00 ▼        |

|            | Profile 1 (MHz): 50                                  | Gain polarity:          | Positive                          | Small change (ppm):              |

|            | Profile 2 (MHz): 100                                 | Total pull range (ppm): | 50                                | * Small change update            |

|            | Profile 3 (MHz): 156.25                              | VCXO BW (KHz):          | 5                                 | ·                                |

|            |                                                      |                         | Large change update               |                                  |

|            | Frequency select signal                              |                         |                                   |                                  |

|            | FS1:FS0: 00                                          | - Apply                 |                                   |                                  |

|            |                                                      |                         |                                   |                                  |

|            |                                                      |                         |                                   |                                  |

|            |                                                      |                         |                                   |                                  |

| _          |                                                      |                         |                                   |                                  |

| not eFused |                                                      |                         |                                   |                                  |

Figure 3-8. Programming Configuration Profile using ClockWizard 2.1

9. The CY29430 supports the selections of four frequency profiles for a single configuration. The Frequency Select inputs of the CY29430 device (FS0 and FS1) can either be controlled by ClockWizard 2.1 or they can be hard-coded using jumpers on the board. To allow selection of a frequency profile in ClockWizard 2.1, jumpers J14 and J15 must be set to positions 2 and 3. With the jumpers in those positions, you can select any of the four available profiles in ClockWizard 2.1 and click **Apply** (see Figure 3-9). Refer to the section Frequency Select (FS) for details on the hardware settings.

Figure 3-9. Frequency Select (FS) Operation of the CY29430 device through ClockWizard 2.1

| ElockWizard 2.1 - CY3677_I                                      | LVPECL_3p3.cpj                                                                   | - C - X |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------|---------|

| File Tools Help                                                 |                                                                                  |         |

| 🗊 🗟 💠 🗟                                                         |                                                                                  |         |

| Home                                                            | Program - Project_00                                                             |         |

| Projects Project_00 - CY29430                                   | Device selection JEDEC programming                                               |         |

| Configure                                                       |                                                                                  |         |

| Results                                                         | Select Device (I2C Master): KitProg/100F0D28010D5400    Select JEDEC: Project_00 |         |

| Program                                                         | eFuse Program Functional Program                                                 |         |

|                                                                 | Large change programming                                                         |         |

|                                                                 |                                                                                  |         |

|                                                                 | Profile 0 (MHz): 33.333 VCXO: Disable v Select FS profile: 00 v                  |         |

|                                                                 | Profile 1 (MHz): 50 Gain polarity: Positive v Small change (ppm):                |         |

|                                                                 | Profile 2 (MHz): 100 Total pull range (ppm): 150 V Small change update           |         |

|                                                                 | Profile 3 (MHz): 156.25 VCXO BW (KHz): 10 v                                      |         |

|                                                                 | Large change update                                                              |         |

|                                                                 |                                                                                  |         |

|                                                                 | Frequency select signal                                                          |         |

|                                                                 | FS1:FS0: 00 • Apply                                                              |         |

|                                                                 |                                                                                  |         |

|                                                                 |                                                                                  |         |

|                                                                 |                                                                                  |         |

| Messages                                                        |                                                                                  |         |

| Info: Device is not eFused                                      |                                                                                  |         |

| Info: Programming started for<br>Info: Programming operation of | Project_00 at 12/13/2016 1:00:32 PM                                              | Ê       |

| inio. Programming operation (                                   | completed successionly                                                           |         |

|                                                                 |                                                                                  | -       |

|                                                                 |                                                                                  |         |

After functional programming, the frequency values of the current .cpj are displayed in the following fields (see Figure 3-10): Profile 0 (MHz), Profile 1 (MHz), Profile 2 (MHz), and Profile 3 (MHz). You can change any of the frequencies in these fields. To make the changes effective, click Large change update. The expected output frequency will appear on the oscilloscope.

Note: Large change programming refers to the case where the frequency is changing more than ± 500 ppm.

| Figure 3-10. | Evaluation c | of Other | Frequencies | through | Large | Change Update |  |

|--------------|--------------|----------|-------------|---------|-------|---------------|--|

|              |              |          |             |         |       |               |  |

| E ClockWizard 2.1 - CY3677_L | LVPECL_3p3.cpj                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - • <b>· ×</b> |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| File Tools Help              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| 🗊 🗟 🔶 🗟                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Home                         | Program - Project_00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

| Projects                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Project_00 - CY29430         | Device selection JEDEC programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| Configure<br>Results         | Select Device (I2C Master): KitProg/100F0D28010D5400   Select JEDEC: Project_00                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Program                      | eFuse Program Functional Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

|                              | Large change programming       Small change programming         Profile 0 (MHz):       33.333       VCXO:         Profile 1 (MHz):       50       Gain polarity:       Positive •         Profile 2 (MHz):       100       Total pull range (ppm):       150       Small change (ppm):         Profile 3 (MHz):       156.25       VCXO BW (KHz):       10       Small change update         Frequency select signal       Frequency select signal       Frequency select signal         FS1.FS0:       00       •       Apply |                |

| Messages                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| ×                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Info: Device is not eFused   | Project_00 at 12/13/2016 1:00:32 PM<br>completed successfully                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ^              |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ÷              |

11. If you want to change the frequency to less than ±500 ppm, fill in the desired ppm in the **Small change (ppm)** field, Select FS profile and click on **Small change update**. The settings are shown in Figure 3-11.

Figure 3-11. Evaluation of Other Frequencies through Small Change Update

| E ClockWizard 2.1 - CY3677_LV                                                                    | /PECL_3p3.cpj                                                                                                                                                                                                                                                                    |                                                                                                  |                                                                        |                                                                                                                                           |   |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---|

| File Tools Help                                                                                  |                                                                                                                                                                                                                                                                                  |                                                                                                  |                                                                        |                                                                                                                                           |   |

| 🗊 🚓 🔶 🖼                                                                                          |                                                                                                                                                                                                                                                                                  |                                                                                                  |                                                                        |                                                                                                                                           |   |

| G C C C C C C C C C C C C C C C C C C C                                                          | Program - Project_00           Device selection           Select Device (I2C Master):           Large change programming           Profile 0 (MHz):           33.333           Profile 1 (MHz):           50           Profile 2 (MHz):           100           Profile 3 (MHz): | KilProg/100F0D28010D5400<br>VCXO.<br>Gain polarity:<br>Total pull range (ppm):<br>VCXO BW (KHz): | JEDEC program Select JEDEC: Disable Positive 150 10 Large change updat | Project_00   eFuse Program  Functional Program  Sali change programming  Select FS profile:  Small change (ppm): 100  Small change update |   |

|                                                                                                  | Frequency select signal<br>FS1:FS0: 00                                                                                                                                                                                                                                           | - Apply                                                                                          |                                                                        |                                                                                                                                           |   |

|                                                                                                  | PS1.PS0: 00                                                                                                                                                                                                                                                                      | <ul> <li>Apply</li> </ul>                                                                        |                                                                        |                                                                                                                                           |   |

|                                                                                                  |                                                                                                                                                                                                                                                                                  |                                                                                                  |                                                                        |                                                                                                                                           |   |

| Messages                                                                                         |                                                                                                                                                                                                                                                                                  |                                                                                                  |                                                                        |                                                                                                                                           |   |

| Info: Device is not eFused<br>Info: Programming started for Pr<br>Info: Programming operation co | roject_00 at 12/13/2016 1:00:32 PM<br>mpleted successfully                                                                                                                                                                                                                       |                                                                                                  |                                                                        |                                                                                                                                           | ^ |

|                                                                                                  |                                                                                                                                                                                                                                                                                  |                                                                                                  |                                                                        |                                                                                                                                           | - |

|                                                                                                  |                                                                                                                                                                                                                                                                                  |                                                                                                  |                                                                        |                                                                                                                                           |   |

### 3.6 eFuse Programming of the CY29430

After functional programming and evaluation of different clock configurations, you may choose to write the configuration to the nonvolatile memory section of the device. The nonvolatile memory of the CY29430 is a one-time programmable (OTP) eFuse. Any configuration after functional evaluation can permanently be written to the eFuse of the device. See Figure 3-12 for the programming procedure.

Configure the device supply to 2.5 V before starting the eFuse programming. Table 4-2 provides the hardware configuration (J13 settings) of CY3677 for setting the device supply to 2.5 V.

| ElockWizard 2.1 - CY3677_I                                   | LVPECL_3p3.cpj                                                                                           |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| File Tools Help                                              |                                                                                                          |

| 💭 📩 🔶 🗐                                                      |                                                                                                          |

| Home                                                         | Program - Project 00                                                                                     |

| Projects     Projects                                        | Device selection JEDEC programming                                                                       |

| Project_00 - CY29430<br>Configure                            |                                                                                                          |

| Results                                                      | Select Device (I2C Master): KitProg/100F0D28010D5400  Select JEDEC: Project_00                           |

| Program                                                      | eFuse Program Functional Program                                                                         |

|                                                              | Large change programming Small change programming                                                        |

|                                                              | Profile 0 (MHz): 33.333 efuse programming Es profile: 00 -                                               |

|                                                              | Profile 1 (MHz): 50 change (ppm): 100                                                                    |

|                                                              | Profile 2 (MHz): 100 You are about to permanently program the device. Do you want to Small change update |

|                                                              | Profile 3 (MHz): 156.25                                                                                  |

|                                                              | Ves No                                                                                                   |

|                                                              | Frequency select signal                                                                                  |

|                                                              | FS1/FS0: 00 Y Apply                                                                                      |

|                                                              |                                                                                                          |

|                                                              |                                                                                                          |

|                                                              |                                                                                                          |

| Messages                                                     |                                                                                                          |

| ×                                                            |                                                                                                          |

| Info: Device is not eFused<br>Info: Programming started for  | Project_00 at 12/13/2016 1:00:32 PM                                                                      |

| Info: Programming operation of<br>Info: Device is not eFused | ompleted successfully                                                                                    |

|                                                              |                                                                                                          |

|                                                              |                                                                                                          |

Figure 3-12. eFuse Programming using ClockWizard 2.1

#### CAUTION CAUTION Evaluate the configuration via functional programming prior to writing a configuration to the eFuse. The configuration cannot be modified or erased once it is written to the eFuse. The CY29430 supply must be set to 2.5 V for eFuse programming. Setting the CY29430 supply to any other voltage during eFuse programming will cause potential damage to the device.

After the device is eFuse-programmed, you can only change the output frequency through the following ways. Note that these changes will revert after a power cycle.

- Large change programming: This refers to the case where the frequency is changing more than ±500 ppm. Enter the desired frequencies in the Profile 0 (MHz), Profile 1 (MHz), Profile 2 (MHz), and Profile 3 (MHz) fields, and click on Large change update. The device will recalibrate and reconfigure the internal circuit and the output will change to the desired frequencies.

- Small change programming: This refers to the case where the frequency is changing less than ±500 ppm. Select FS profile, enter the desired ppm in the small change (ppm), and click on Small change update. The device will recalibrate and reconfigure the internal circuit and the output will change to the desired frequencies.

### 3.7 Custom Profile Generation

ClockWizard 2.1 should be used to generate custom configuration profiles. For details on how to create custom profiles, refer to the ClockWizard 2.1 User Guide located in **Help** > **User guide** of the ClockWizard 2.1 software.

To understand the output termination settings of different output standards (for example, LVPECL, HCSL, or LVDS), refer to the B.1. Termination Settings of Differential Clock Outputs section.

# 4 Hardware

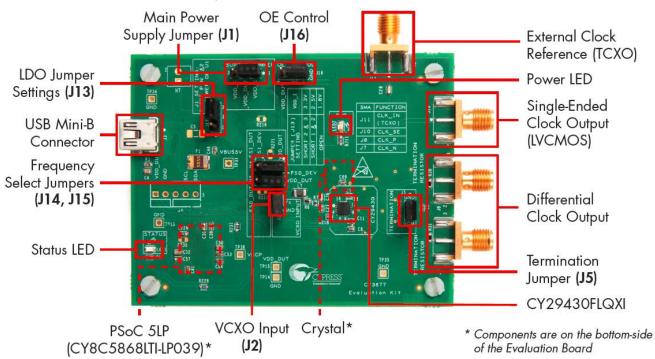

### 4.1 Board Overview

The CY3677 EVK is used for evaluating the CY29430 device.

Following are the key features of the CY3677 EVK:

- Powered from a USB port

- Jumper to configure on-board LDO output

- Jumper to short or isolate external connection for termination settings

Figure 4-1 illustrates the CY3677 EVK board with a markup of the on-board components.

Figure 4-1. CY3677 EVK On-board Components

| Table 1-1: CV3677 | EVK Onboard Com | ponents Description  |

|-------------------|-----------------|----------------------|

| Table 4-1. 0130/7 | EVR Onboard Con | iponents Description |

| Label Name                          | Description                                                                                                                                                                                                                                                                      |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CY29430FLQXI                        | CY29430FLQXI is the Cypress clock chip that is evaluated with the CY3677 EVK.                                                                                                                                                                                                    |  |  |

| Main Power Supply Jumper (J1)       | Short pin 1 and 2 of jumper J1 to power up the CY29430. The core supply and I/O supply are shorted on the board, and hence are the same for the device.                                                                                                                          |  |  |

| LDO Settings Jumper (J13)           | Set the J13 jumper per Table 4-2 to set the LDO output voltage.<br><b>Note:</b> The brightness of LED2 will vary depending on the voltage selection. It will be brightest at 3.3 V and dimmest at 1.8 V.                                                                         |  |  |

| USB Mini-B Connector                | Connect the kit to a PC using the USB Standard-A to Mini-B cable.                                                                                                                                                                                                                |  |  |

| Differential Clock Output           | Connect SMA cables to the SMA connectors (J7 and J8) on one end and to an oscilloscope on the other end.                                                                                                                                                                         |  |  |

| Single-Ended Clock Output (LVCMOS)  | Connect the SMA cable to the SMA connector (J10) on one end and to an oscilloscope on the other end.                                                                                                                                                                             |  |  |

| External Clock Reference (TCXO)     | Connect the SMA cable to the SMA connector (J11) on one end and to an external clock reference (TCXO) on the other end.                                                                                                                                                          |  |  |

| Termination Jumper (J5)             | The board has an on-board jumper (J5) to connect and disconnect output termination.                                                                                                                                                                                              |  |  |

| Status LED                          | This LED (LED1) turns ON after the USB enumeration is completed. This LED blinks during programming of the CY29430 device from a PC.                                                                                                                                             |  |  |