## GS6150 Multi-Rate 6G UHD-SDI Reclocker

### **Gennum Products** -

### **Key Features**

- SMPTE ST 2081, ST 424, ST 292, and ST 259-C compliant

- Supports retiming data at rates of 125Mb/s, 270Mb/s, 1.485 and 1.485/1.001Gb/s, 2.97 and 2.97/1.001Gb/s, 5.94 and 5.94/1.001Gb/s

- Supports retiming of DVB-ASI signals

- Automatic or Manual Rate Selection

- Detected rate indication in Auto Mode

- 4:1 input selector patented technology

- · Option of two reclocked data outputs

- Four configurable GPIO pins with ability to output device status, including:

- Lock Detect

- Loss of Signal (LOS)

- Low/High bit-rate indication for slew-rate control of SDI cable drivers

- On-chip  $100\Omega$  differential input and output termination

- Bypass support for rates up to 5940Mb/s

- Manual Bypass function

- Configurable automatic Bypass when not locked

- Option to use external reference or operate referenceless

- Cascading reference buffer supports multiple reclockers using a single reference source

- Input signal equalization and output signal de-emphasis to compensate for trace dielectric losses

- Single power supply operation at 1.8V

- 130mW typical power consumption (150mW with second output enabled)

- Pb-free and RoHS compliant

- Operating temperature range: -40°C to 85°C

### **Applications**

- SMPTE ST 2081, SMPTE ST 424,

SMPTE ST 292, SMPTE ST 259-C coaxial cable serial digital interfaces

- EN50083-9 DVB-ASI interfaces

- MADI standard

### **Description**

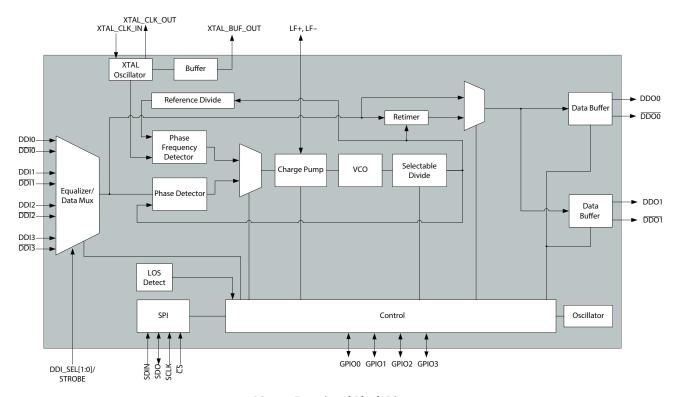

The GS6150 is a low-power, multi-rate serial digital reclocker designed to automatically recover the embedded clock from a digital video signal and re-time the incoming video data.

The GS6150 will recover the embedded clock signal and retime the data from 6G UHD-SDI signals compliant with SMPTE ST 2081. In addition, it can also re-time SMPTE ST 259-C, SMPTE ST 292, SMPTE ST 424 or DVB-ASI compliant digital video signals as well as MADI audio streams.

The GS6150 features four high-speed differential signal inputs feeding a 4:1 input selector. Input termination is on-chip for seamless matching to  $100\Omega$  differential transmission lines. The input selector is a component of a video switching system with tightly constrained timing requirements.

The GS6150 includes programmable trace equalization to compensate for high-frequency losses associated with board-level interconnect.

Two CML outputs interface seamlessly to devices with a CML input reference between 1.2V and 2.5V.

Programmable output swing and de-emphasis provide flexibility in managing signal integrity of the output signals.

The GS6150 can operate in either automatic rate detection or manual rate selection mode. In auto mode the device will automatically detect and lock onto incoming data signals at any supported rate.

The device can operate without an external 27MHz frequency reference. For applications which require rapid signal lock, an external 27MHz reference may be used to set the VCO frequency when not locked to the input signal. The presence of an external reference crystal is automatically detected by the device.

In systems that require passing of non-supported data rates, the GS6150 can be configured to either automatically or manually enter a bypass mode in order to pass the signal without reclocking.

A four-wire serial Gennum Serial Peripheral Interface (GSPI) facilitates configuration and status monitoring of the device. Multiple GS6150 devices can be daisy-chained together with a single 4-pin connection to the host system.

This device is Pb-free, and the encapsulation compound does not contain halogenated flame retardant. This component and all homogenous sub-components are RoHS compliant.

**GS6150 Functional Block Diagram**

## **Revision History**

| Version | ECO    | PCN | Date           | Changes and/or Modifications                                                                                                                     |

|---------|--------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | 024967 | _   | March 2015     | Updated Table 2-2 and Table 2-3.<br>Updated Section 4.11 and Section 5.<br>Updated to Final Data Sheet.                                          |

| 1       | 022115 | _   | September 2014 | Changed product title. Updated<br>Table 5-1 format. Updates<br>throughout Table 2-2 and Table 2-3.<br>Added Section 4.5.5. Updated<br>Table 5-1. |

| 0       | 016784 | _   | December 2013  | New Document                                                                                                                                     |

### **Contents**

| 1. Pin Out                                              | 5  |

|---------------------------------------------------------|----|

| 1.1 Pin Assignment                                      | 5  |

| 1.2 Pin Descriptions                                    | 6  |

| 2. Electrical Characteristics                           | 10 |

| 2.1 Absolute Maximum Ratings                            | 10 |

| 2.2 DC Electrical Characteristics                       | 10 |

| 2.3 AC Electrical Characteristics                       | 12 |

| 3. Input/Output Circuits                                | 15 |

| 4. Detailed Description                                 | 17 |

| 4.1 Serial Data Inputs                                  | 17 |

| 4.1.1 Input Trace Equalization                          | 17 |

| 4.1.2 Input Selection                                   | 17 |

| 4.2 Reference Clock                                     | 19 |

| 4.3 Signal Monitoring                                   | 19 |

| 4.3.1 Loss of Signal Detection                          | 19 |

| 4.3.2 Lock Detection                                    | 21 |

| 4.3.3 Rate Detection                                    | 22 |

| 4.3.4 Low/High Bit Rate Detection for Slew Rate Control | 23 |

| 4.4 Low Power Modes                                     | 23 |

| 4.5 Serial Data Output                                  | 24 |

| 4.5.1 Output Impedance                                  | 24 |

| 4.5.2 Output Signal Interface Levels                    | 24 |

| 4.5.3 Adjustable Output Swing                           | 24 |

| 4.5.4 Output De-emphasis                                | 25 |

| 4.5.5 Output Common Mode Voltage                        | 26 |

| 4.6 Output Mute, Disable, and Data Selection            | 26 |

| 4.7 Bypass Mode                                         | 27 |

| 4.8 DVB-ASI                                             | 27 |

| 4.9 Device Power Up                     | 27 |

|-----------------------------------------|----|

| 4.9.1 Power on Reset (POR)              | 27 |

| 4.9.2 Reset Pin (RST)                   | 27 |

| 4.10 GPIO Pins Configuration            | 27 |

| 4.11 GSPI Host Interface                | 29 |

| 4.11.1 CS Pin                           | 29 |

| 4.11.2 SDIN Pin                         | 29 |

| 4.11.3 SDOUT Pin                        | 29 |

| 4.11.4 SCLK Pin                         | 31 |

| 4.11.5 Command Word Description         | 31 |

| 4.11.6 GSPI Transaction Timing          | 34 |

| 4.11.7 Single Read/Write Access         | 36 |

| 4.11.8 Auto-increment Read/Write Access | 37 |

| 4.11.9 Setting a Device Unit Address    | 38 |

| 4.11.10 Default GSPI Operation          | 39 |

| 5. Host Interface Register Map          | 41 |

| 6. Typical Application Circuit          | 60 |

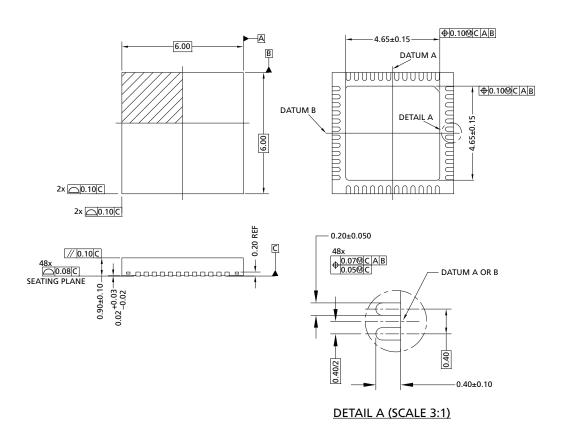

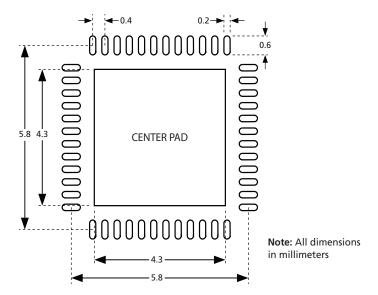

| 7. Package and Ordering Information     | 61 |

| 7.1 Package Dimensions                  | 61 |

| 7.2 Recommended PCB Footprint           | 62 |

| 7.3 Packaging Data                      | 62 |

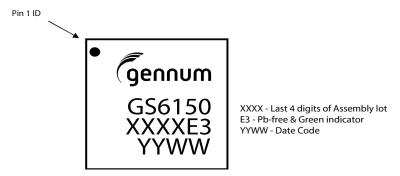

| 7.4 Marking Diagram                     | 63 |

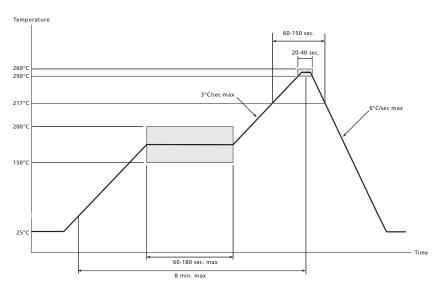

| 7.5 Solder Reflow Profile               | 63 |

| 7.6 Ordering Information                | 63 |

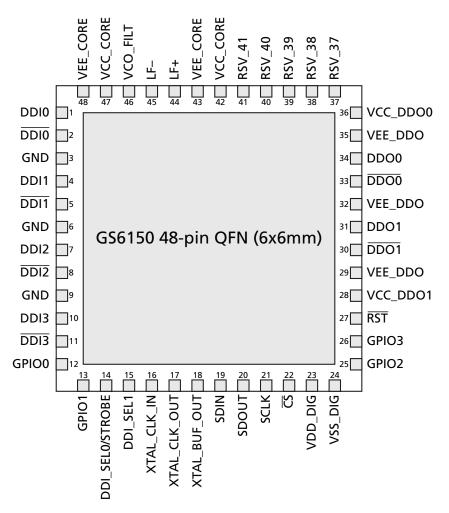

## 1. Pin Out

## 1.1 Pin Assignment

Figure 1-1: GS6150 Pin Out

Rev.2

# **1.2 Pin Descriptions**

**Table 1-1: GS6150 Pin Descriptions**

| Pin Number | Name       | Туре                    | Description                                                                                                                                                                                                                                                                                                                                                        |

|------------|------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2       | DDI0, DDI0 | Input                   | Serial Digital Differential Input 0.                                                                                                                                                                                                                                                                                                                               |

| 3, 6, 9    | GND        | Power                   | Input channel isolation. Connect to ground or leave unconnected                                                                                                                                                                                                                                                                                                    |

| 4, 5       | DDI1, DDI1 | Input                   | Serial Digital Differential Input 1.                                                                                                                                                                                                                                                                                                                               |

| 7, 8       | DDI2, DDI2 | Input                   | Serial Digital Differential Input 2.                                                                                                                                                                                                                                                                                                                               |

| 10, 11     | DDI3, DDI3 | Input                   | Serial Digital Differential Input 3.                                                                                                                                                                                                                                                                                                                               |

| 12         | GPIO0      | Digital<br>Input/Output | Multi-function Control/Status Input/Output 0.  Signal options are:  LOS (output; default)  LOCKED  LBR_HBR  RATE_DET0  RATE_DET1  RATE_DET2  LOCKED_125M  LOCKED_270M  LOCKED_1G485  LOCKED_2G97  LOCKED_5G94  RATE_CHANGE  DD00_DISABLE  DD01_DISABLE  This pin is configured using the GPIO0_SELECT and GPIO0_IO_SELECT bits in the GPIO_CONTROL_REG_0 register. |

| 13         | GPIO1      | Digital<br>Input/Output | Multi-function Control/Status Input/Output 1.  Signal options are:  LOS  LOCKED (output; default)  LBR_HBR  RATE_DET0  RATE_DET1  RATE_DET2  LOCKED_125M  LOCKED_270M  LOCKED_16485  LOCKED_2697  LOCKED_5G94  RATE_CHANGE  DDO0_DISABLE  DDO1_DISABLE  This pin is configured using the GPIO1_SELECT and GPIO1_IO_SELECT bits in the GPIO_CONTROL_REG_0 register. |

**Table 1-1: GS6150 Pin Descriptions (Continued)**

| Pin Number | Name                         | Туре              | Description                                                                                                                                                                                                                                               |

|------------|------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

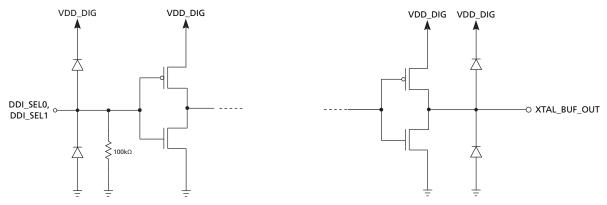

| 14, 15     | DDI_SEL0/STROBE,<br>DDI_SEL1 | Logic Input       | Input selection control.  Used to select the high-speed input for processing through the device. Refer to Table 4-1 for details on input selection.                                                                                                       |

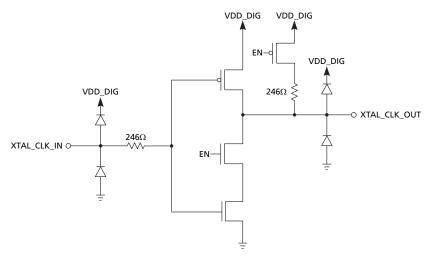

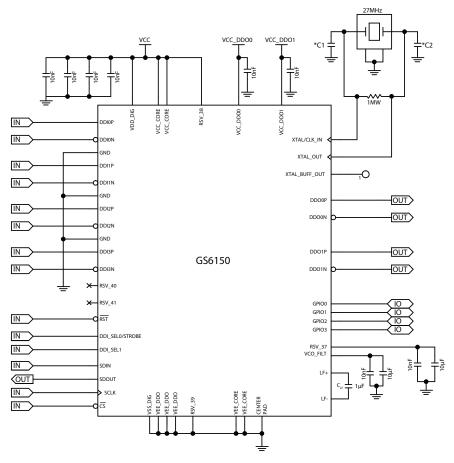

| 16         | XTAL_CLK_IN                  | Input             | Reference Crystal Pin/27MHz clock input. Connect to an external circuit as shown in Figure 6-1: GS6150 Typical Application Circuit or to a digital clock source (XTAL_BUF_OUT of another GS6150 or GS6151). Connect to ground if operating referenceless. |

| 17         | XTAL_CLK_OUT                 | Output            | Reference Crystal Pin. Connect to a external circuit as shown in Figure 6-1: GS6150 Typical Application Circuit, or leave unconnected if XTAL_CLK_IN is driven by an external clock source or if XTAL_CLK_IN is connected to ground (referenceless).      |

| 18         | XTAL_BUF_OUT                 | Output            | Buffered clock reference output. Leave unconnected if not used to drive 27MHz clock input of another device.                                                                                                                                              |

| 19         | SDIN                         | Digital Input     | Serial digital data input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.  Refer to 4.11 GSPI Host Interface for more details.                                                                                                |

| 20         | SDOUT                        | Digital<br>Output | Serial digital data output for the Gennum Serial Peripheral Interface (GSPI) host control/status port.  Refer to 4.11 GSPI Host Interface for more details.                                                                                               |

| 21         | SCLK                         | Digital Input     | Burst-mode clock input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.  Refer to 4.11 GSPI Host Interface for more details.                                                                                                   |

| 22         | CS                           | Digital Input     | Chip select input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.  Active-low input.  Refer to 4.11 GSPI Host Interface for more details.                                                                                     |

| 23         | VDD_DIG                      | Power             | Most positive power supply for the internal logic Connect to 1.8V.                                                                                                                                                                                        |

| 24         | VSS_DIG                      | Power             | Most negative power supply for the internal logic Connect to ground.                                                                                                                                                                                      |

**Table 1-1: GS6150 Pin Descriptions (Continued)**

| Pin Number | Name       | Туре                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25         | GPIO2      | Digital<br>Input/Output | Multi-function Control/Status Input/Output 2.  Signal options are:  LOS  LOCKED  LBR_HBR (output; default)  RATE_DET0  RATE_DET1  RATE_DET2  LOCKED_125M  LOCKED_270M  LOCKED_16485  LOCKED_16485  LOCKED_2697  LOCKED_5G94  RATE_CHANGE  DDO0_DISABLE  DDO1_DISABLE                                                                                                                                                                                                                        |

| 26         | GPIO3      | Digital<br>Input/Output | This pin is configured using the GPIO2_SELECT and GPIO2_IO_SELECT bits in the GPIO_CONTROL_REG_1 register.  Multi-function Control/Status Input/Output 3.  Signal options are:  LOS  LOCKED  LBR_HBR  RATE_DET0  RATE_DET1  RATE_DET2  LOCKED_125M  LOCKED_270M  LOCKED_16485  LOCKED_16485  LOCKED_2697  LOCKED_5G94  RATE_CHANGE  DDO0_DISABLE  DDO1_DISABLE (input; default)  This pin is configured using the GPIO3_SELECT and GPIO3_IO_SELECT bits in the GPIO_CONTROL_REG_1 register. |

| 27         | RST        | Digital Input           | Reset pin. If set LOW, all blocks set to default conditions and inputs/<br>outputs set to high impedance. If HIGH, normal operation of the<br>device resumes. By default, internally pulled HIGH.                                                                                                                                                                                                                                                                                           |

| 28         | VCC_DDO1   | Power                   | Most positive power supply connection for the DDO1/DDO1 output driver. Connect to any voltage between 1.2V and 2.5V.                                                                                                                                                                                                                                                                                                                                                                        |

| 29, 32, 35 | VEE_DDO    | Power                   | Most negative power supply connections for the output drivers.  Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 30, 31     | DDO1, DDO1 | Output                  | Differential serial data output 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 33, 34     | DDO0, DDO0 | Output                  | Differential serial data output 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 36         | VCC_DDO0   | Power                   | Most positive power supply connection for the DDO0/DDO0 output driver. Connect to any voltage between 1.2V and 2.5V.                                                                                                                                                                                                                                                                                                                                                                        |

**Table 1-1: GS6150 Pin Descriptions (Continued)**

| Pin Number | Name           | Туре                | Description                                                                                     |

|------------|----------------|---------------------|-------------------------------------------------------------------------------------------------|

| 37         | RSV_37         | Power<br>Decoupling | Connect through decoupling capacitor to ground.                                                 |

| 38         | RSV_38         | Power               | Connect to 1.8V.                                                                                |

| 39         | RSV_39         | Power               | Connect to ground.                                                                              |

| 40, 41     | RSV_40, RSV_41 | Input               | Leave unconnected.                                                                              |

| 42         | VCC_CORE       | Power               | Most positive power supply connection to the analog core Connect to 1.8V.                       |

| 43         | VEE_CORE       | Power               | Most negative power supply connection to the analog core Connect to ground.                     |

| 44         | LF+            | Passive             | Connect to LF– through C <sub>LF</sub> Refer to Figure 6-1: GS6150 Typical Application Circuit. |

| 45         | LF-            | Passive             | Connect to LF+ through C <sub>LF</sub> Refer to Figure 6-1: GS6150 Typical Application Circuit. |

| 46         | VCO_FILT       | Power               | External decoupling for the VCO.  Refer to Figure 6-1: GS6150 Typical Application Circuit.      |

| 47         | VCC_CORE       | Power               | Most positive power supply connection for the analog core Connect to 1.8V.                      |

| 48         | VEE_CORE       | Power               | Most negative power supply connection to the analog core Connect to ground.                     |

| _          | Center Pad     | Power               | Ground pad on bottom of package.                                                                |

## 2. Electrical Characteristics

## 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                           | Value                                               |

|-----------------------------------------------------|-----------------------------------------------------|

| Supply Voltage – Core (VCC_CORE, VDD_DIG)           | -0.5 to +2.1V <sub>DC</sub>                         |

| Supply Voltage – Output Driver (VCC_DDO0, VCC_DDO1) | -0.5 to +2.8V <sub>DC</sub>                         |

| Input ESD Voltage                                   | 4kV                                                 |

| Storage Temperature Range (T <sub>S</sub> )         | -50°C to +125°C                                     |

| Operating Temperature Range (T <sub>A</sub> )       | -40°C to +85°C                                      |

| Input Voltage Range (any input pin)                 | -0.3 to (V <sub>CC_CORE</sub> + 0.3)V <sub>DC</sub> |

| Solder Reflow Temperature                           | +260°C                                              |

**Note:** Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation outside of the ranges shown in the AC/DC electrical characteristics tables is not guaranteed.

## 2.2 DC Electrical Characteristics

**Table 2-2: DC Electrical Characteristics**

VCC\_CORE, VDD\_DIG =  $+1.8V \pm 5\%$ ,  $T_A = -40$ °C to +85°C unless otherwise specified

| Parameter                                                 | Symbol                                         | Conditions | Min   | Тур | Max   | Units | Notes |

|-----------------------------------------------------------|------------------------------------------------|------------|-------|-----|-------|-------|-------|

| Supply Voltage – Core<br>(VCC_CORE, VDD_DIG)              | V <sub>CC_CORE</sub> ,<br>V <sub>DD_DIG</sub>  | _          | 1.710 | 1.8 | 1.890 | V     |       |

| Supply Voltage – Output<br>Driver (VCC_DDO0,<br>VCC_DDO1) | V <sub>CC_DDO0</sub> ,<br>V <sub>CC_DDO1</sub> | _          | 1.140 | _   | 2.625 | V     |       |

## **Table 2-2: DC Electrical Characteristics (Continued)**

VCC\_CORE, VDD\_DIG =  $+1.8V \pm 5\%$ ,  $T_A = -40$ °C to +85°C unless otherwise specified

| Parameter                           | Symbol                                         | Conditions                                           | Min | Тур | Max                            | Units | Notes |

|-------------------------------------|------------------------------------------------|------------------------------------------------------|-----|-----|--------------------------------|-------|-------|

|                                     |                                                | Data Rate 6G,<br>DDO1/DDO1 disabled                  | _   | 140 | 185                            | mW    | 1, 2  |

|                                     |                                                | Data Rate <6G,<br>DDO1/DDO1 disabled                 | _   | 130 | 170                            | mW    | 1, 2  |

| Power                               | $P_{D}$                                        | Data Rate 6G, Default Settings, DDO1/DDO1 enabled    | _   | 210 | 280                            | mW    | 3, 4  |

|                                     | -                                              | Data Rate <6G, Default Settings, DDO1/DDO1 enabled   | _   | 190 | 255                            | mW    | 3, 4  |

|                                     |                                                | Maximum Supply and Power<br>Settings                 | _   | 280 | 360                            | mW    | 5     |

| Power (Sleep operation)             | P <sub>SLEEP</sub>                             | _                                                    | _   | 20  | 35                             | mW    |       |

| Power (Standby operation)           | P <sub>STANDBY</sub>                           | _                                                    | _   | 80  | 110                            | mW    |       |

|                                     |                                                | Output Swing Register<br>Setting = 0000 <sub>b</sub> | _   | 4.8 | 7                              | mA    | 6, 7  |

| Supply Current - Output<br>Driver   | I <sub>CC_DD00</sub> ,<br>I <sub>CC_DD01</sub> | Output Swing Register<br>Setting= 0100 <sub>b</sub>  | _   | 7.5 | 12                             | mA    | 6, 7  |

|                                     |                                                | Output Swing Register<br>Setting = 1100 <sub>b</sub> | _   | 15  | 22                             | . mA  | 6, 7  |

|                                     |                                                | Output De-emphasis<br>Disabled<br>Data Rate 6G       | _   | 82  | _                              | mA    | 8     |

| Supply Current - Core               | I <sub>CC_CORE</sub>                           | Output De-emphasis<br>Disabled<br>Data Rate 3G       | _   | 74  | _                              | mA    | 8     |

|                                     |                                                | Output De-emphasis Enabled<br>Data Rate 6G           | _   | 90  | _                              | mA    | 8     |

|                                     |                                                | Output De-emphasis Enabled<br>Data Rate 3G           | _   | 81  | _                              | mA    | 8     |

| Supply Current - Digital            | I <sub>CC_DIG</sub>                            | External Crystal Referenced                          | _   | 7   | 12                             | mA    |       |

| Serial Input Termination            |                                                | Differential                                         | 75  | 100 | 125                            | Ω     |       |

| Serial Output Termination           |                                                | Differential                                         | 75  | 100 | 125                            | Ω     |       |

| Serial Input Common<br>Mode Voltage | V <sub>CMIN</sub>                              | _                                                    | 0.9 | _   | V <sub>CC_CORE</sub><br>- 50mV | V     | 9, 10 |

GS6150 Final Data Sheet Rev.2 PDS-060127

## **Table 2-2: DC Electrical Characteristics (Continued)**

VCC\_CORE, VDD\_DIG =  $+1.8V \pm 5\%$ ,  $T_A = -40$ °C to +85°C unless otherwise specified

| Parameter                                                     | Symbol          | Conditions             | Min               | Тур | Max              | Units | Notes |

|---------------------------------------------------------------|-----------------|------------------------|-------------------|-----|------------------|-------|-------|

| Input Voltage - Digital<br>Pins<br>(CS, SDIN, CLK, GPIO[0:3]) | $V_{IH}$        | _                      | 0.65*<br>VDD_DIG  | _   | VDD_DIG          | V     |       |

|                                                               | V <sub>IL</sub> | _                      | 0                 | _   | 0.35*<br>VDD_DIG | V     |       |

| Output Voltage - Digital<br>Pins<br>(SDOUT, GPIO[0:3])        | V <sub>OH</sub> | I <sub>OH</sub> = -2mA | VDD_DIG<br>- 0.45 | _   | _                | V     |       |

|                                                               | V <sub>OL</sub> | I <sub>OL</sub> = 2mA  | _                 | _   | 0.45             | V     |       |

#### **Notes:**

PDS-060127

March 2015

- 1. Normal operation in referenceless mode, minimum output swing with de-emphasis disabled

- 2. VCC\_DDO0/1 = 1.2V

- 3. The swing is default and de-emphasis is on

- 4. VCC\_DDO0/1 = 1.8V

- 5. DD00/DD00 and DD01/DD01 set to maximum swing setting, external crystal reference used

- 6. Consumption per enabled DDO output

- 7. Refer to Table 4-3 for the exact register settings for each  $\Delta V_{DDO}$  output swing listed

- 8. For two enabled outputs

- 9. Maximum input voltage level =  $1.8V \pm 5\%$

- 10. Up to a maximum swing of 800mV

## 2.3 AC Electrical Characteristics

### **Table 2-3: AC Electrical Characteristics**

VCC\_CORE, VDD\_DIG =  $+1.8V \pm 5\%$ ,  $T_A = -40$ °C to +85°C unless otherwise specified

| Parameter                        | Symbol               | Conditions                                           | Min | Тур | Max  | Units                | Notes |

|----------------------------------|----------------------|------------------------------------------------------|-----|-----|------|----------------------|-------|

| Input Data Rate (Bypass)         | DR <sub>BYPASS</sub> | Bypass mode enabled                                  | 3   | _   | 5940 | Mb/s                 | 1     |

| Input Sensitivity                | $\Delta V_{SDI}$     | Differential                                         | 200 | _   | 800  | mV <sub>ppd</sub>    |       |

| Output Valtage Swing             | AV                   | Output Swing Register<br>Setting = 0100 <sub>b</sub> | 310 | 410 | 510  | ${\sf mV}_{\sf ppd}$ | 2     |

| Output Voltage Swing             | $\Delta V_{ m DDO}$  | Output Swing Register<br>Setting = 1100 <sub>b</sub> | 600 | 800 | 1000 | ${\sf mV}_{\sf ppd}$ | 2     |

| Serial Input Jitter<br>Tolerance | IJT                  | Square wave modulation                               | 0.8 | _   | _    | UI                   |       |

|                                  |                      | Referenceless                                        | _   | _   | 50   | ms                   |       |

| PLL Lock Time —<br>Asynchronous  | t <sub>ALOCK</sub>   | With External Reference<br>(MADI enabled)            | _   | _   | 30   | ms                   |       |

| ,                                |                      | With External Reference<br>(MADI disabled)           | _   | _   | 20   | ms                   |       |

GS6150 www.semtech.com

Final Data Sheet Rev.2

## **Table 2-3: AC Electrical Characteristics (Continued)**

VCC\_CORE, VDD\_DIG =  $+1.8V \pm 5\%$ ,  $T_A = -40$ °C to +85°C unless otherwise specified

| Parameter                                         | Symbol                      | Conditions                                         | Min | Тур  | Max  | Units             | Notes |

|---------------------------------------------------|-----------------------------|----------------------------------------------------|-----|------|------|-------------------|-------|

| PLL Lock Time —                                   | <b>+</b>                    | Referenceless                                      | _   | _    | 10   | μs                |       |

| Synchronous                                       | t <sub>SLOCK</sub>          | With External Reference                            | _   | _    | 10   | μs                |       |

| Serial Data (DDO0 and DDO1) Output Rise And       | t <sub>riseDDO</sub>        | $20\% \sim 80\%$ rising edge into $50\Omega$ load  | _   | _    | 70   | ps                |       |

| Fall Time                                         | t <sub>fallDDO</sub>        | $20\% \sim 80\%$ falling edge into $50\Omega$ load | _   | _    | 70   | ps                |       |

| Rise And Fall Time<br>Mismatch (DDO0 and<br>DDO1) | _                           | _                                                  | _   | _    | 15   | ps                |       |

| Duty Cycle Distortion                             | _                           | Data Rate 6G                                       | _   | _    | 10   | %                 |       |

| (DDO0 and DDO1)                                   | _                           | Data Rate < 6G                                     | _   | _    | 5    | %                 |       |

|                                                   | t <sub>OJ(125Mb/s)</sub>    |                                                    | _   | 0.02 | 0.03 | UI <sub>P-P</sub> | 3, 4  |

|                                                   | t <sub>OJ(270Mb/s)</sub>    |                                                    | _   | 0.02 | 0.03 | $UI_{P-P}$        | 3, 4  |

| Serial Data Output Jitter Intrinsic -             | t <sub>OJ(1485Mb/s)</sub>   | BW = Nominal                                       | _   | 0.03 | 0.06 | $UI_{P-P}$        | 3, 4  |

|                                                   | t <sub>OJ(2970Mb/s)</sub>   | PRN 2 <sup>23</sup> – 1 test pattern               | _   | 0.04 | 0.09 | UI <sub>P-P</sub> | 3, 4  |

|                                                   | t <sub>OJ(5940Mb/s)</sub>   | <del>-</del>                                       | _   | 0.07 | 0.13 | UI <sub>P-P</sub> | 3, 4  |

|                                                   | t <sub>OJ(BYPASS)</sub>     | <del>-</del>                                       | _   | 0.06 | 0.09 | UI <sub>P-P</sub> | 3, 4  |

|                                                   |                             | PLL_LOOP_BANDWIDTH<br>= 00001                      | _   | 37   | _    | kHz               |       |

|                                                   |                             | PLL_LOOP_BANDWIDTH<br>= 00010                      | _   | 74   | _    | kHz               |       |

|                                                   | BW <sub>LOOP(125Mb/s)</sub> | PLL_LOOP_BANDWIDTH<br>= 00100 (default)            | _   | 148  | _    | kHz               |       |

|                                                   |                             | PLL_LOOP_BANDWIDTH<br>= 01000                      | _   | 296  | _    | kHz               |       |

| PLL Loop Pandwidth                                |                             | PLL_LOOP_BANDWIDTH<br>= 10000                      | _   | 590  | _    | kHz               |       |

| PLL Loop Bandwidth                                |                             | PLL_LOOP_BANDWIDTH<br>= 00001                      | _   | 80   | _    | kHz               |       |

|                                                   |                             | PLL_LOOP_BANDWIDTH<br>= 00010                      | _   | 160  | _    | kHz               |       |

|                                                   | BW <sub>LOOP(270Mb/s)</sub> | PLL_LOOP_BANDWIDTH<br>= 00100 (default)            | _   | 320  | _    | kHz               |       |

|                                                   |                             | PLL_LOOP_BANDWIDTH<br>= 01000                      | _   | 640  | _    | kHz               |       |

|                                                   |                             | PLL_LOOP_BANDWIDTH<br>= 10000                      | _   | 1.28 | _    | MHz               |       |

GS6150 Final Data Sheet Rev.2 PDS-060127

March 2015

www.semtech.com

## **Table 2-3: AC Electrical Characteristics (Continued)**

VCC\_CORE, VDD\_DIG =  $+1.8V \pm 5\%$ ,  $T_A = -40$ °C to +85°C unless otherwise specified

| Parameter          | Symbol                        | Conditions                              | Min | Тур  | Max | Units | Notes |

|--------------------|-------------------------------|-----------------------------------------|-----|------|-----|-------|-------|

|                    |                               | PLL_LOOP_BANDWIDTH<br>= 00001           | _   | 438  | _   | kHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH = 00010              | _   | 875  | _   | kHz   |       |

|                    | BW <sub>LOOP(1485Mb/s)</sub>  | PLL_LOOP_BANDWIDTH<br>= 00100 (default) | _   | 1.75 | _   | MHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH<br>= 01000           | _   | 3.5  | _   | MHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH<br>= 10000           | _   | 7    | _   | MHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH<br>= 00001           | _   | 875  | _   | kHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH = 00010              | _   | 1.75 | _   | MHz   |       |

| PLL Loop Bandwidth | BW <sub>LOOP(2970Mb/s)</sub>  | PLL_LOOP_BANDWIDTH<br>= 00100 (default) | _   | 3.5  | _   | MHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH<br>= 01000           | _   | 7.0  | _   | MHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH<br>= 10000           | _   | 14.0 | _   | MHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH<br>= 00001           | _   | 1.75 | _   | MHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH<br>= 00010           | _   | 3.5  | _   | MHz   |       |

|                    | BW <sub>LOOP</sub> (5940Mb/s) | PLL_LOOP_BANDWIDTH<br>= 00100 (default) | _   | 7.0  | _   | MHz   |       |

|                    | _                             | PLL_LOOP_BANDWIDTH<br>= 01000           | _   | 14.0 | _   | MHz   |       |

|                    |                               | PLL_LOOP_BANDWIDTH<br>= 10000           | _   | 28.0 | _   | MHz   |       |

#### Note:

- 1. Edge detection method for LOS detection should be used for data rates below 20Mb/s

- 2. Refer to Table 4-3 for the exact register settings for each  $\Delta V_{DDO}$  output swing listed

- 3. Jitter measured using an oscilloscope according to SMPTE RP-184

- 4. Accumulated jitter measured peak to peak differential over 2000 hits

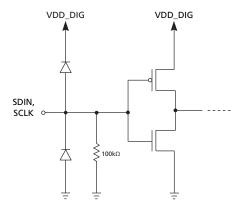

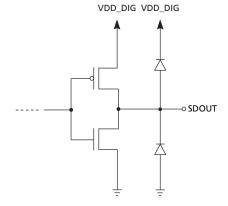

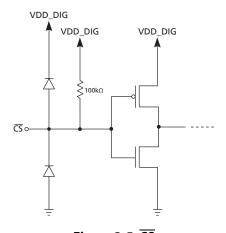

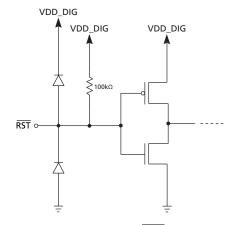

# 3. Input/Output Circuits

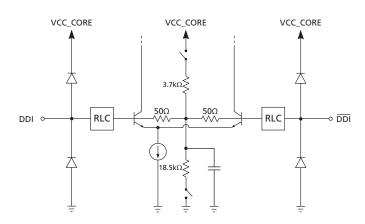

Figure 3-1: DDI0, DDI0, DDI1, DDI1, DDI2, DDI2, DDI3, DDI3 Serial Digital Differential Inputs

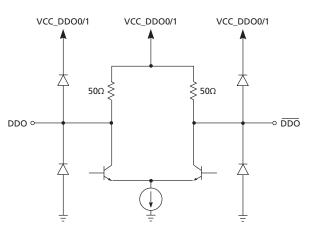

Figure 3-2: DD00, DD00, DD01, DD01 Serial Digital Differential Output

Figure 3-3: SDIN and SCLK

Figure 3-4: SDOUT

Figure 3-5: CS

Figure 3-6: RST

Figure 3-7: DDI\_SEL0/STROBE and DDI\_SEL1

Figure 3-8: XTAL\_BUF\_OUT

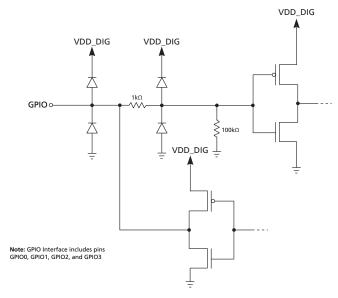

Figure 3-9: General Purpose Inputs/Outputs (GPIO)

Figure 3-10: XTAL\_CLK\_IN and XTAL\_CLK\_OUT

## 4. Detailed Description

The GS6150 is a multi-standard reclocker for serial digital SDTV SDI and DVB-ASI signals operating at 270Mb/s, HDTV SDI signals operating at 1.485Gb/s and 1.485/1.001Gb/s, 3G SDI signals operating at 2.97Gb/s and 2.97/1.001Gb/s, and 6G UHD-SDI signals operating at 5.94Gb/s and 5.94/1.001Gb/s and MADI audio streams at 125Mb/s.

## 4.1 Serial Data Inputs

The GS6150 features four  $100\Omega$  terminated differential input buffers.

A serial data input signal may be connected to any of the following input pin pairs of the device: DDI0/DDI0, DDI1/DDI1, DDI2/DDI2, and DDI3/DDI3.

By default, the self-biasing circuit at the input is enabled to allow AC coupling to upstream devices. To enable DC coupling of the inputs, the user must disable the self-biasing network by setting bits 4:4 through 5:5 to 0 in the register 7<sub>h</sub>: DDI[0:1]\_TRACE\_EQ\_DC\_TERM\_ENABLE.

In order to select DC coupling, please ensure that the output common mode of the upstream device is in range of the input common mode voltage range shown in Table 2-2.

The serial digital input buffer is capable of operation with any binary coded signal that meets the input signal level requirements defined below, with any data rate between 3Mb/s and 5.94Gb/s.

## 4.1.1 Input Trace Equalization

The GS6150 features adjustable trace equalization to compensate for PCB trace dielectric losses up to half the maximum supported data rate, or 3GHz. The equalization has three settings: the LOW (default) setting is optimized for compensating the high-frequency losses associated with 0-7dB of trace loss at 1.5GHz for data rates of 2.97Gb/s and below, and for 0-10dB of trace loss at 3GHz for 5.94Gb/s. The HIGH setting is optimized for trace loss between 7-14dB at 1.5GHz for data rates 2.97Gb/s and below. The 0dB or EQ\_BYPASS setting may be used in systems with negligible trace loss. These settings are selected using the DDI0\_TRACE\_EQ\_CONTROL, DDI1\_TRACE\_EQ\_CONTROL and DDI3\_TRACE\_EQ\_CONTROL bits in the INPUT\_CONTROL\_REG\_0 register at address 5<sub>h</sub>.

The default state of the device is input trace equalization on all inputs set to LOW.

## 4.1.2 Input Selection

The GS6150 incorporates a 4:1 input selector which allows the connection of four independent streams of video/data.

www.semtech.com

The selector is controllable in three separate ways:

- 1. The DDI\_SEL0 and DDI\_SEL1 pins can be used to select the input.

- 2. A GSPI accessible register can be used to select the input, with the state change occurring as soon as the register value changes.

- 3. A GSPI accessible register can be used to select the input, with a rising edge on the STROBE pin triggering a change to the next state.

Since these states are mutually exclusive, the DDI\_SEL0 pin is shared with the STROBE function.

In the case of using the DDI\_SEL0/STROBE and DDI\_SEL1 pins (#1 above) or the STROBE pre-select method (#3 above), the input selector will switch within 1µs of the change of state on the corresponding pin(s). This strict timing requirement is not maintained when using GSPI register selection (#2 above).

Each of the device's four inputs is selected as shown in Table 4-1.

Table 4-1: Pin and Register Settings for Input Selection

| Regist                                       | ter Settings                      |                                   | Pin S    | ettings                       | Differential                 |

|----------------------------------------------|-----------------------------------|-----------------------------------|----------|-------------------------------|------------------------------|

| INPUT_SELECTION_CONTROL 7 <sub>h</sub> [9:8] | DDI_SELECT<br>7 <sub>h</sub> [11] | DDI_SELECT<br>7 <sub>h</sub> [10] | DDI_SEL1 | DDI_SEL0/<br>STROBE           | High-speed<br>Input Selected |

| X0 (default)                                 | Х                                 | Х                                 | LOW      | LOW                           | DDI0, DDI0                   |

| X0 (default)                                 | Х                                 | Х                                 | LOW      | HIGH                          | DDI1, DDI1                   |

| X0 (default)                                 | Х                                 | Х                                 | HIGH     | LOW                           | DDI2, DDI2                   |

| X0 (default)                                 | Х                                 | Х                                 | HIGH     | HIGH                          | DDI3, DDI3                   |

| 01                                           | 0                                 | 0                                 | Х        | Х                             | DDI0, DDI0                   |

| 01                                           | 0                                 | 1                                 | Х        | Х                             | DDI1, DDI1                   |

| 01                                           | 1                                 | 0                                 | Х        | Х                             | DDI2, DDI2                   |

| 01                                           | 1                                 | 1                                 | Х        | Х                             | DDI3, DDI3                   |

| 11                                           | 0                                 | 0                                 | Х        | on LOW-to-<br>HIGH transition | DDI0, DDI0                   |

| 11                                           | 0                                 | 1                                 | Х        | on LOW-to-<br>HIGH transition | DDI1, DDI1                   |

| 11                                           | 1                                 | 0                                 | Х        | on LOW-to-<br>HIGH transition | DDI2, DDI2                   |

| 11                                           | 1                                 | 1                                 | Х        | on LOW-to-<br>HIGH transition | DDI3, DDI3                   |

Note: 'X' indicates 'Do Not Care'

The DDI\_SEL0/STROBE and DDI\_SEL1 pins include internal pull-downs, which pulls the input voltage LOW if either pin is unconnected.

When using the STROBE pre-select method (#3 above), the pre-selected input buffer and trace EQ is powered up in advance of the STROBE pulse.

March 2015

PDS-060127

## **4.2 Reference Clock**

The GS6150 can operate with or without an external frequency reference. For applications requiring rapid asynchronous locking, a 27MHz reference or crystal is required.

The PLL lock times for both referenceless and external crystal reference operation are given in Table 2-3: AC Electrical Characteristics.

If a reference is connected to the XTAL\_CLK\_IN pin or a crystal is connected to the XTAL\_CLK\_IN and XTAL\_CLK\_OUT pins of the device, it will automatically be used as the reference frequency for rapid asynchronous lock. If XTAL\_CLK\_IN is not connected to a crystal, XTAL\_CLK\_OUT must be left unconnected.

The XTAL\_CLK\_IN pin operates correctly when connected directly to the XTAL\_BUF\_OUT from another GS6150, or a 27MHz output of a different device.

## 4.3 Signal Monitoring

The GS6150 measures and reports the following signal status and quality monitoring parameters:

- Loss of Signal

- Lock Detection

- Rate Detection

- Low/High Bit Rate Detection

## 4.3.1 Loss of Signal Detection

LOS (Loss of Signal) detection is an active HIGH output available to the application on any of the GPIO[3:0] multi-function status and control pins. It is selected for output using the GPIO[3:0]\_IO\_SELECT and GPIO[3:0]\_SELECT bits accessible in the GPIO\_CONTROL\_REG\_0 and GPIO\_CONTROL\_REG\_1 registers. It is the default output of the GPIO0 pin.

LOS indicates when the serial digital signal selected by the input selector is invalid. This function is always active.

Two methods can be used to detect loss of signal: strength (default) and edge. Either method can be selected with LOS\_DETECTION\_METHOD bits of register PLL\_CONTROL.

When strength detection is used as the method of LOS detection the corresponding GPIO pin will be HIGH (signal lost) when the input signal amplitude within a predefined window falls below the threshold set by the bits DDI[0:3]\_LOS\_THRESHOLD\_CONTROL in the LOS\_CONTROL\_REG\_1 and LOS\_CONTROL\_REG\_2 registers. The LOS threshold hysteresis can be set by the LOS\_HYSTERESIS bits in the LOS\_CONTROL\_REG\_0 register at address  $\mathsf{F}_{\mathsf{h}}$ .

The corresponding GPIO pin will be LOW (signal present) when the input signal amplitude within a predefined window is above the defined threshold.

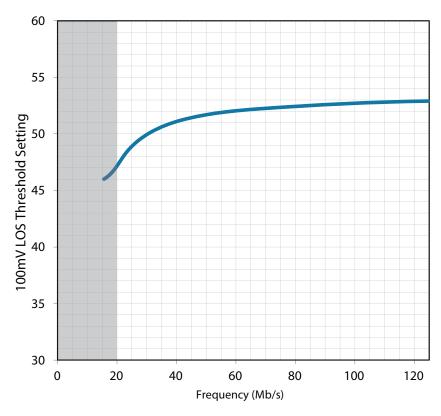

The method of strength detection is measurement of the average rectified differential voltage on the input pins. The strength detection method is therefore inherently dependent on the input signal's eye shape, particularly the rise/fall times of the input signal relative to the data rate. Additionally, the circuit has a lower bandwidth limit of operation (20Mb/s) below which it is recommended that the edge detection method is used. The absolute value of the threshold can be determined for any input swings according to Equation 4-1 below:

$$Threshold = \frac{1.9 \text{mV} \times (\text{DDI[0..3]\_LOS\_THRESHOLD\_CONTROL}) \times 53}{(\text{DEVICE\_SPECIFIC\_LOS\_THRESHOLD})}$$

Equation 4-1

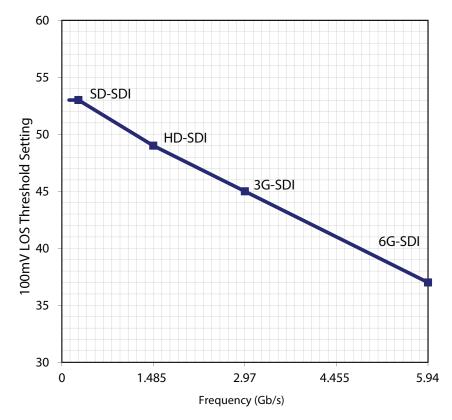

where DEVICE\_SPECIFIC\_LOS\_THRESHOLD specifies the LOS threshold value for a 100mV input swing at SD-rate specific to each device. The other rates scale according to the fractional relationship given in Figure 4-1 and Figure 4-2 below.

Figure 4-1: LOS Threshold at 100mV Input Swing vs. Low Frequency Rates for a Nominal DEVICE\_SPECIFIC\_LOS\_THRESHOLD of 53

**Note:** Edge detection method is recommended for signals in shaded areas.

GS6150 www.semtech.com 20 of 64

Final Data Sheet Rev.2

Figure 4-2: LOS Threshold at 100mV Input Swing vs. SDI Data Rates for a Nominal DEVICE\_SPECIFIC\_LOS\_THRESHOLD of 53

Strength detection is unaffected by the Trace EQ settings in INPUT\_CONTROL\_REG\_0.

When edge detection is used as the method of LOS detection the corresponding GPIO pin will be HIGH (signal lost) when no transitions are detected on the selected input. The corresponding GPIO pin will be LOW (signal present) when transitions are detected on the input. The LOS status is also available through the LOS bit in the PLL\_STATUS register, and as a sticky status through the LOS\_STICKY bit in the STICKY\_STATUS register at address 50<sub>h</sub>.

### 4.3.2 Lock Detection

The GS6150 lock detection circuitry outputs a LOCKED status signal which indicates that the CDR has achieved phase lock to the incoming data stream. The LOCKED signal is an active HIGH output available to the application on any of the GPIO[3:0] multi-function status and control pins. It is selected for output using the GPIO[3:0]\_IO\_SELECT and GPIO[3:0]\_SELECT bits accessible in the GPIO\_CONTROL\_REG\_0 and GPIO\_CONTROL\_REG\_1 registers. By default, LOCKED is output on GPIO1.

The LOCKED status is available from the LOCKED bit in the PLL\_STATUS register, and the LOCK\_LOST\_STICKY bit in the STICKY\_STATUS register indicates whether lock has been lost since the bit was last cleared.

To optimize systems with high DCD and/or high residual ISI the LOCK\_SAMPLE bit of the PD\_CONTROL register should be set to  $1_{\rm b}$  in conjunction with reducing the Loop Bandwidth.

### 4.3.2.1 Synchronous and Asynchronous Lock Time

Asynchronous lock time is defined as the time it takes the device to lock when a signal is first applied to the serial digital inputs, or when the signal rate changes.

The synchronous lock time is defined as the time it takes the device to lock to a signal which has been momentarily interrupted.

The asynchronous and synchronous lock times are defined in Table 2-3: AC Electrical Characteristics.

To qualify for synchronous lock time, the maximum interruption time of the signal is  $10\mu$ s for a 270Mb/s signal. 1.485Gb/s, 2.97Gb/s, and 5.94Gb/s signals, as well as their f/1.001 components have a maximum interruption time of  $6\mu$ s. The new signal, after interruption, must have the same frequency as the original signal but can have arbitrary phase.

### 4.3.3 Rate Detection

The GS6150 can be manually forced to lock to a specific supported data rate, or automatically search for and lock to supported rates. The selection between manual and automatic rate selection is through the FORCE\_PLL\_RATE and FORCE\_PLL\_RATE\_ENABLE bits of the PLL\_CONTROL register at address 4C<sub>h</sub>. By default the device is set to automatically search for supported SDI rates.

When set to automatically detect supported data rates, the device repeatedly cycles through each supported rate that is enabled through the RATE\_ENABLE\_5G94, RATE\_ENABLE\_1G485, RATE\_ENABLE\_270M and RATE\_ENABLE\_125M bits of the PLL\_CONTROL register, until the device phase locks to one of the enabled rates. If lock is lost the rate search resumes, continuously testing for each rate in sequence until lock is regained.

The device reports the current data rate setting of the automatic rate search state machine through the DETECTED\_RATE bits in the PLL\_STATUS register at address 4F<sub>h</sub>. Each bit of DETECTED\_RATE is also available to output through the GPIO pins, selected for output using the GPIO[3:0]\_IO\_SELECT and GPIO[3:0]\_SELECT bits accessible in the GPIO\_CONTROL\_REG\_0 register. The supported rates that the DETECTED\_RATE bits can output are shown in Table 4-2 below.

**Table 4-2: Automatic Rate Detection - Supported Data Rates**

| DETECTED_RATE | Data Rate      |

|---------------|----------------|

| 000           | 125Mb/s – MADI |

| 001           | 270Mb/s – SD   |

| 010           | 1.485Gb/s – HD |

| 011           | 2.97Gb/s – 3G  |

| 100           | 5.94Gb/s – 6G  |

## 4.3.4 Low/High Bit Rate Detection for Slew Rate Control

A status output named LBR\_HBR is provided to control the slew rate selection input of a downstream SDI cable driver. It can be connected to the SD\_EN input of drivers such as the GS6080 or GS6081 using the Semtech recommended application circuit.

When this signal is HIGH, the data rate is 270Mb/s (SD) or 125Mb/s (MADI). This signal is LOW for all other supported data rates, and when the GS6150 is operating in Bypass Mode or any time the device is not locked.

The LBR\_HBR output signal is available to the application on any of the GPIO[3:0] multifunction status and control pins. It is selected for output using the GPIO[3:0]\_IO\_SELECT and GPIO[3:0]\_SELECT bits accessible in the GPIO\_CONTROL\_REG\_0 and GPIO\_CONTROL\_REG\_1 registers. By default, LBR\_HBR is output on GPIO2.

### **4.4 Low Power Modes**

The device can be programmed via the GSPI to operate in two different low power modes. SLEEP mode has minimum power consumption at the expense of recovery time upon de-assertion of the FORCE\_PWRDN\_SLEEP bit. STANDBY mode has higher power consumption relative to SLEEP mode but minimizes time to return to operation on deassertion of the FORCE\_PWRDN\_STANDBY bit. The features affected by each mode are outlined below.

#### SLEEP mode:

- LOS detection remains functional

- The GSPI remains functional

- The reference oscillator remains functional

### STANDBY mode:

- LOS detection remains functional

- · The GSPI remains functional

- The reference oscillator remains functional

- The VCO and PLL remains functional so as to minimize the lock time when a signal is detected

- The rate detector remains set to the last valid data rate. On detection of a signal, the last valid rate is tested first by the rate detect state machine

The device can be programmed to automatically enter into SLEEP or STANDBY mode when LOS is asserted by programming the AUTO\_PWRDN\_DISABLE bit in the PWRDN\_CONTROL register at address 17<sub>h</sub>. The AUTO\_PWRDN\_MODE bit in the same register selects which mode, SLEEP or STANDBY, is entered into upon assertion of LOS.

## 4.5 Serial Data Output

The GS6150 has two current-mode differential output drivers, each capable of driving up to  $1V_{pp}$  differential into an external  $100\Omega$  differential load.

The output drivers operate with any binary coded signal with supported data rates up to 5.94Gb/s. This is applicable to both the serial data (DDO,  $\overline{DDO}$ ) and serial data (DDO1,  $\overline{DDO1}$ ) outputs of the device.

### 4.5.1 Output Impedance

Each of the GS6150's output buffers include two on-chip,  $50\Omega$  termination resistors.

## 4.5.2 Output Signal Interface Levels

The serial digital outputs operate within specification with an output CML power supply of 1.2V to 2.5V.

### 4.5.3 Adjustable Output Swing

Through the GSPI, the output swing can be set in the range from approximately  $230 \text{mV}_{ppd}$  to  $930 \text{mV}_{ppd}$  in  $45 \text{mV}_{ppd}$  increments, when the outputs are terminated with  $50\Omega$  loads. For the exact values, please see Table 4-3 below.

The output swing for each data rate is controlled using the bits in the DRIVER\_CONTROL\_REG\_3, DRIVER\_CONTROL\_REG\_4, DRIVER\_CONTROL\_REG\_5, and DRIVER\_CONTROL\_REG\_6 registers at addresses 1C<sub>h</sub> through 1F<sub>h</sub>.

The device automatically adjusts the swing setting depending on the state of the device (i.e. detected rate, bypass mode, or mute). There are separate register controls for mute, bypass and each data rate.

**Table 4-3: Serial Digital Output Swing Settings**

| Register Setting<br>(See Note 1) | Min | Тур | Max | Units |

|----------------------------------|-----|-----|-----|-------|

| 0000 <sub>b</sub>                | 175 | 230 | 290 | mV    |

| 0001 <sub>b</sub>                | 205 | 275 | 345 | mV    |

| 0010 <sub>b</sub>                | 245 | 325 | 405 | mV    |

| 0011 <sub>b</sub> (default)      | 280 | 370 | 460 | mV    |

| 0100 <sub>b</sub>                | 310 | 410 | 510 | mV    |

| 0101 <sub>b</sub>                | 345 | 460 | 575 | mV    |

| 0110 <sub>b</sub>                | 380 | 510 | 640 | mV    |

| 0111 <sub>b</sub>                | 420 | 560 | 700 | mV    |

GS6150 Final Data Sheet PDS-060127

**Table 4-3: Serial Digital Output Swing Settings (Continued)**

| Register Setting<br>(See Note 1) | Min | Тур | Max  | Units |

|----------------------------------|-----|-----|------|-------|

| 1000 <sub>b</sub>                | 455 | 605 | 760  | mV    |

| 1001 <sub>b</sub>                | 490 | 655 | 820  | mV    |

| 1010 <sub>b</sub>                | 530 | 705 | 880  | mV    |

| 1011 <sub>b</sub>                | 565 | 755 | 945  | mV    |

| 1100 <sub>b</sub>                | 600 | 800 | 1000 | mV    |

| 1101 <sub>b</sub>                | 630 | 840 | 1050 | mV    |

| 1110 <sub>b</sub>                | 670 | 890 | 1110 | mV    |

| 1111 <sub>b</sub>                | 700 | 930 | 1160 | mV    |

#### Note:

Applicable registers that can be programmed with the values shown above are DDO0\_SWING\_1G485, DDO0\_SWING\_270M, DDO0\_SWING\_125M, DDO0\_SWING\_BYPASS, DDO0\_SWING\_MUTE, DDO0\_SWING\_5G94, DDO0\_SWING\_2G97, DDO1\_SWING\_1G485, DDO1\_SWING\_270M, DDO1\_SWING\_125M, DDO1\_SWING\_BYPASS, DDO1\_SWING\_MUTE, DDO1\_SWING\_5G94, and DDO1\_SWING\_2G97

### 4.5.4 Output De-emphasis

The GS6150 features adjustable output de-emphasis to compensate for PCB dielectric trace loss. Each output can be independently set to a different de-emphasis setting for each detected rate through controls found in the DRIVER\_CONTROL\_REG\_1 and DRIVER\_CONTROL\_REG\_2 registers.

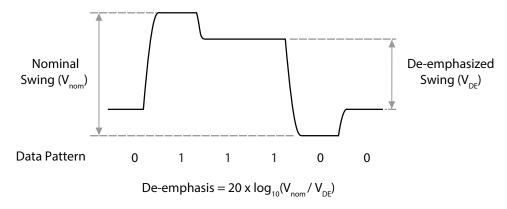

The effect of de-emphasis, illustrated in Figure 4-3, is to attenuate the swing of bits that do not follow a bit transition ( $V_{DE}$ ). The swing of bits that do follow a bit transition ( $V_{nom}$ ) is set by the output swing registers found in Section 4.5.3 and do not depend on the de-emphasis settings.

Figure 4-3: De-emphasis Waveform

The default de-emphasis settings for each rate are given in the register descriptions for DRIVER\_CONTROL\_REG\_1 and DRIVER\_CONTROL\_REG\_2 in Table 5-1. De-emphasis is disabled on both outputs in Bypass mode, when the output is muted, or when the device is not locked.

### 4.5.5 Output Common Mode Voltage

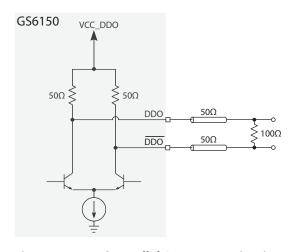

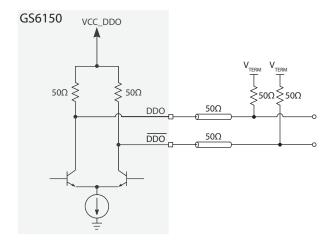

The output common mode voltage level ( $V_{CMOUT}$ ) is a function of the output voltage swing, the output driver supply voltage ( $V_{CC\_DDO}$ ) and how the transmission line is terminated. If the outputs are terminated through  $50\Omega$  resistors to a voltage  $V_{TERM}$  equal to  $V_{CC\_DDO}$ , as shown in Figure 4-5 below, the output common mode voltage is given by the following expression:

$$V_{CMOUT} = V_{CC\_DDO} - \frac{\Delta V_{DDO}}{4}$$

Equation 4-2

If the differential outputs are terminated across a  $100\Omega$  resistor, as shown in Figure 4-4 below, the output common mode voltage is given by the following expression:

$$V_{CMOUT} = V_{CC\_DDO} - \frac{\Delta V_{DDO}}{2}$$

Equation 4-3

Figure 4-4:  $100\Omega$  Parallel Output Termination

Figure 4-5:  $50\Omega$  Termination to  $V_{TERM}$

## 4.6 Output Mute, Disable, and Data Selection

The GS6150 outputs can each be individually muted using the DDO0\_MUTE and DDO1\_MUTE bits in the DRIVER\_CONTROL\_REG\_0 register at address 19<sub>h</sub>.

Each output can also be independently disabled through either register or GPIO control. When disabled each pin of the output is pulled to  $V_{CC\_DDO}$ . Register DRIVER\_CONTROL\_REG\_0 contains both register based disable bits (DDO0\_DISABLE, DDO1\_DISABLE) and bits for selection between register and GPIO control (DDO0\_DISABLE\_SELECT, DDO1\_DISABLE\_SELECT). For GPIO control refer to Section 4.10.

SS6150 www.semtech.com 26 of 64

By default DDO0, DDO0 is enabled/disabled through register control and set to enabled. DDO1, DDO1 is enabled/disabled through GPIO3 and set to output data.

## 4.7 Bypass Mode

In CDR Bypass mode, the GS6150 passes the input data to the outputs, bypassing the retiming functionality.

There are two bits in the control registers that control the bypass function: MANUAL\_BYPASS and AUTO\_BYPASS in the RECLOCKER\_BYPASS register at address 20<sub>h</sub>. The MANUAL\_BYPASS bit is inactive (set to 0) by default. The AUTO\_BYPASS bit is active (set to 1) by default, and places the GS6150 reclocker into bypass mode when the PLL is not locked to a data rate. The bypass function does not affect the trace equalization function of the device.

Note: If MANUAL\_BYPASS is active, it overrides the AUTO\_BYPASS bit setting.

### 4.8 DVB-ASI

The GS6150 has the ability to reclock DVB-ASI signals at 270Mb/s. All relevant settings and control registers that apply to SD-SDI signals at 270Mb/s are also compatible with DVB-ASI signals at 270Mb/s.

## 4.9 Device Power Up

### 4.9.1 Power on Reset (POR)

The GS6150 features an on-chip power-on-reset that places all registers and internal state machines into their known, default states when the chip is powered up.

## 4.9.2 Reset Pin (RST)

When the RST pin is set LOW, all functional blocks are set to their default conditions and high-speed data and digital functionality is suspended. When it is set HIGH, normal operation of the device resumes 0.5ms after the LOW-to-HIGH transition of the signal. This pin is not required at power up and may be left unconnected.

## 4.10 GPIO Pins Configuration

The GS6150 has four GPIO pins that can each be configured as outputs for various internal status signals, or as inputs to disable either output-driver through pin control. The bits GPIO[0:3]\_IO\_SELECT are used to configure the GPIO pins as outputs (0) or inputs (1). The signals that are output or input on the GPIO pins are selected on GPIO\_CONTROL\_REG\_0 and GPIO\_CONTROL\_REG\_1. The signals that can be output on the GPIO pins are listed in Table 4-4 below.

**Table 4-4: GPIO Status Outputs**

| GPIO[0:3]_SELECT | Parameter    | Description                                                                                                                               |

|------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0000             | LOS          | Loss of signal indication - High when there is no detected signal on the selected DDI input                                               |

| 0001             | LOCKED       | Phase lock indication - High when the CDR has phase-<br>locked to a valid input signal                                                    |

| 0010             | LBR_HBR      | Low bit-rate/High bit-rate - High when the part is locked to the SD data rate; low for all other data rates and in bypass.                |

| 0101             | RATE_DET0    | Rate Detect - Three bits used in conjunction that represent                                                                               |

| 0110             | RATE_DET1    | the data rate detected by the rate search state machine.                                                                                  |

| 0111             | RATE_DET2    | Refer to Table 4-2 for rate encoding details.                                                                                             |

| 1000             | LOCKED_125M  | High when the rate search state machine is locked to a MADI data rate (125Mb/s)                                                           |

| 1001             | LOCKED_270M  | High when the rate search state machine is locked to an SD data rate (270Mb/s)                                                            |

| 1010             | LOCKED_1G485 | High when the rate search state machine is locked to an HD data rate (1.485Gb/s)                                                          |

| 1011             | LOCKED_2G97  | High when the rate search state machine is locked to a 3G data rate (2.97Gb/s)                                                            |

| 1100             | LOCKED_5G94  | High when the rate search state machine is locked to a 6G data rate (5.94Gb/s)                                                            |

| 1101             | RATE_CHANGE  | When a change in the data rate is detected by the rate search state machine, the RATE_CHANGE signal is pulsed high for a duration of 37ns |

The signals that can be input on the GPIOs are listed in Table 4-5 below.

**Table 4-5: GPIO Signal Inputs**

| GPIO[0:3]_SELECT | Parameter    | Description                                |

|------------------|--------------|--------------------------------------------|

| 0000             | DDO0_DISABLE | Disables serial data output 0 (DDOO, DDOO) |

| 0001             | DDO1_DISABLE | Disables serial data output 1 (DDO1, DDO1) |

By default, the GPIO pins are configured to the following parameters:

GPIO0: LOS (output) GPIO1: LOCKED (output) GPIO2: LBR\_HBR (output) GPIO3: DDO1\_DISABLE (input)

## 4.11 GSPI Host Interface

The GS6150 is controlled via the Gennum Serial Peripheral Interface (GSPI).

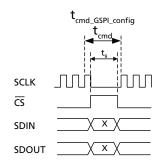

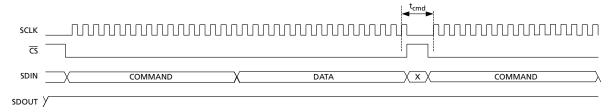

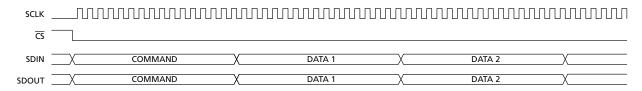

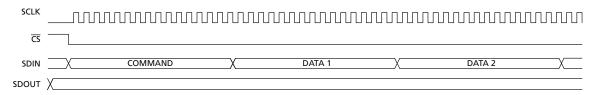

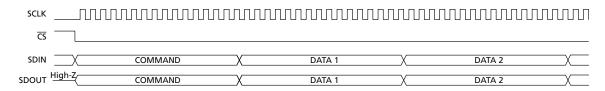

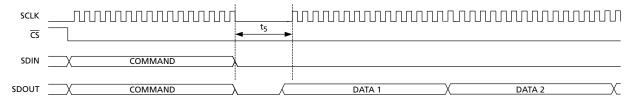

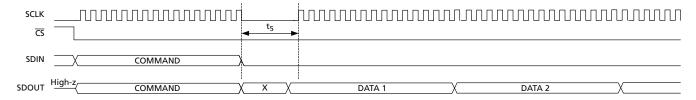

The GSPI host interface is comprised of a serial data input signal (SDIN pin), serial data output signal (SDOUT pin), an active-low chip select ( $\overline{CS}$  pin) and a burst clock (SCLK pin).

The GS6150 is a slave device, therefore the SCLK, SDIN and  $\overline{\text{CS}}$  signals must be sourced by the application host processor.

All read and write access to the device is initiated and terminated by the application host processor.

It is strongly recommended to connect the GSPI pins of the GS6150 to a host/system processor/controller or FPGA to facilitate optimization of the device to meet specific application requirements. Modification of many device settings is only facilitated through the GSPI of the GS6150, and is not available on external pins.

### 4.11.1 CS Pin

The Chip Select pin  $(\overline{CS})$  is an active-low signal provided by the host processor to the GS6150.

The high-to-low transition of this pin marks the start of serial communication to the GS6150.

The low-to-high transition of this pin marks the end of serial communication to the GS6150.

There is an option for each device to use a separate unique Chip Select signal from the host processor or for up to 32 devices to be connected to a single Chip Select when making use of the Unit Address feature.

Only those devices whose Unit Address matches the UNIT ADDRESS in the GSPI Command Word will respond to communication from the host processor (unless the B'CAST ALL bit in the GSPI Command Word is set to 1).

### 4.11.2 SDIN Pin

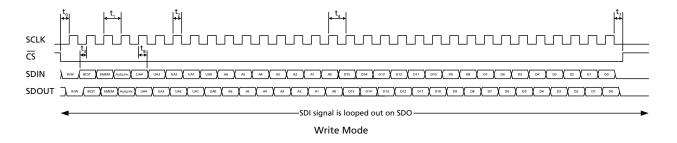

The SDIN pin is the GSPI serial data input pin of the GS6150.

The 16-bit Command and Data Words from the host processor or from the SDOUT pin of other devices are shifted into the device on the rising edge of SCLK when the  $\overline{\text{CS}}$  pin is low.

### **4.11.3 SDOUT Pin**

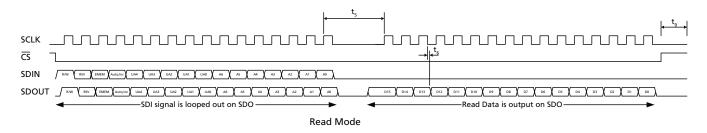

The SDOUT pin is the GSPI serial data output of the GS6150.

All data transfers out of the GS6150 to the host processor or to the SDIN pin of other connected devices occur from this pin.

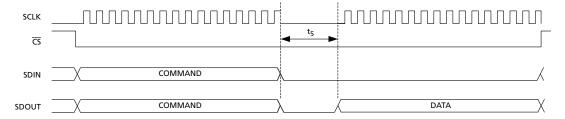

By default at power up or after system reset, the SDOUT pin provides a non-clocked path directly from the SDIN pin, regardless of the  $\overline{\text{CS}}$  pin state, except during the GSPI Data

Word portion for read operations to the device. This allows multiple devices to be connected in Loop-Through configuration.

For read operations, the SDOUT pin is used to output data read from an internal Configuration and Status Register (CSR) when  $\overline{CS}$  is LOW. Data is shifted out of the device on the falling edge of SCLK, so that it can be read by the host processor or other downstream connected device on the subsequent SCLK rising edge.

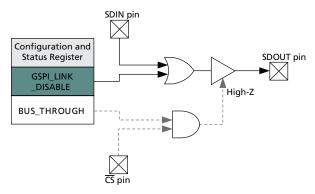

### 4.11.3.1 GSPI Link Disable Operation

It is possible to disable the direct SDIN to SDOUT (Loop-Through) connection by writing a value of 1 to the GSPI\_LINK\_DISABLE bit in REGISTER\_0. When disabled, any data appearing at the SDIN pin will not appear at the SDOUT pin and the SDOUT pin is HIGH.

**Note:** Disabling the Loop-Through operation is temporarily required when initializing the Unit Address for up to 32 connected devices.

The time required to enable/disable the Loop-Through operation from assertion of the register bit is less than the GSPI configuration command delay as defined by the parameter  $t_{cmd\_GSPI\_config}$  (5 SCLK cycles).

Table 4-6: GSPI\_LINK\_DISABLE Bit Operation

| Bit State | Description                                                             |

|-----------|-------------------------------------------------------------------------|

| 0         | SDIN pin is looped through to the SDOUT pin                             |

| 1         | Data appearing at SDIN does not appear at SDOUT, and SDOUT pin is HIGH. |

Figure 4-6: GSPI\_LINK\_DISABLE Operation

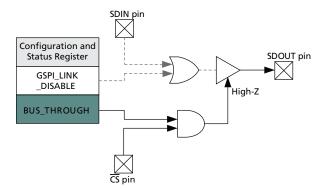

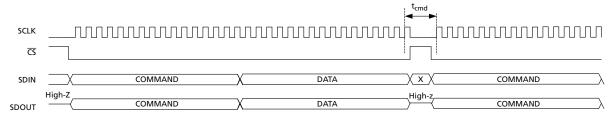

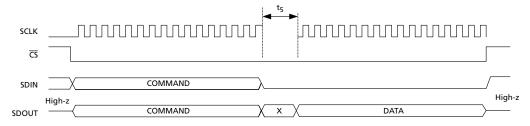

### 4.11.3.2 GSPI Bus-Through Operation

Using GSPI Bus-Through operation, the GS6150 can share a common PCB trace with other GSPI devices for SDOUT output.

When configured for Bus-Through operation, by setting GSPI\_BUS\_THROUGH\_ENABLE bit to 1, the SDOUT pin will be high-impedance when the CS pin is HIGH.

When the  $\overline{\text{CS}}$  pin is LOW, the SDOUT pin will be driven and will follow regular read and write operation as described in Section 4.11.3.

GS6150 www.semtech.com 30 of 64

Final Data Sheet Rev.2

Multiple chains of GS6150 devices can share a single SDOUT bus connection to host by configuring the devices for Bus-Through operation. In such configuration, each chain requires a separate Chip Select  $(\overline{CS})$ .

Figure 4-7: GSPI\_BUS\_THROUGH\_ENABLE Operation

### 4.11.4 SCLK Pin

The SCLK pin is the GSPI serial data shift clock input to the device, and must be provided by the host processor.

Serial data is clocked into the GS6150 SDIN pin on the rising edge of SCLK. Serial data is clocked out of the device from the SDOUT pin on the falling edge of SCLK (read operation). SCLK is ignored when  $\overline{CS}$  is HIGH.

The maximum interface clock rate is 27MHz.

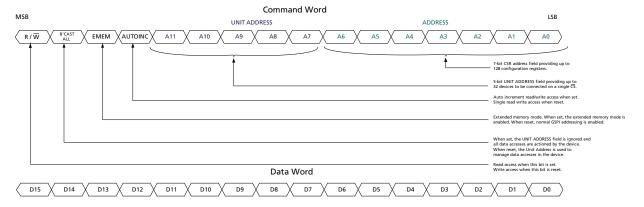

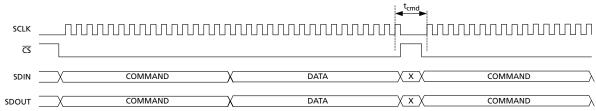

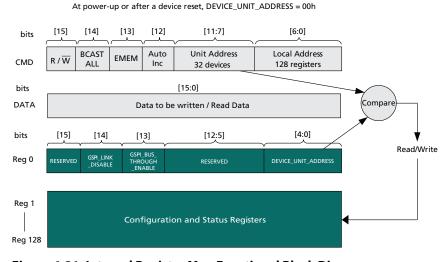

## 4.11.5 Command Word Description

All GSPI accesses are a minimum of 32 bits in length (a 16-bit Command Word followed by a 16-bit Data Word) and the start of each access is indicated by the high-to-low transition of the chip select  $(\overline{CS})$  pin of the GS6150.

The format of the Command Word and Data Words are shown in Figure 4-8.

Data received immediately following this high-to-low transition will be interpreted as a new Command Word.

### 4.11.5.1 R/W bit - B15 Command Word

This bit indicates a read or write operation.

When  $R/\overline{W}$  is set to 1, a read operation is indicated, and data is read from the register specified by the ADDRESS field of the Command Word.

When  $R/\overline{W}$  is set to 0, a write operation is indicated, and data is written to the register specified by the ADDRESS field of the Command Word.

GS6150 www.semtech.com 31 of 64 **Final Data Sheet** Rev.2 **Proprietary & Confidential**

#### 4.11.5.2 B'CAST ALL - B14 Command Word

This bit is used in write operations to configure all devices connected in Loop-Through and Bus-Through configuration with a single command.

When B'CAST ALL is set to 1, the following Data Word (AUTOINC = 0) or Data Words (AUTOINC = 1) are written to the register specified by the ADDRESS field of the Command Word (and subsequent addresses when AUTOINC = 1), regardless of the setting of the UNIT ADDRESS(es).

When B'CAST ALL is set to 0, a normal write operation is indicated. Only those devices that have a Unit Address matching the UNIT ADDRESS field of the Command Word write the Data Word to the register specified by the ADDRESS field of the Command Word.

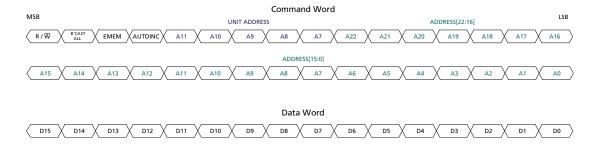

#### 4.11.5.3 EMEM - B13 Command Word

When the EMEM bit is 1 the Address Word is extended to 23 bits to allow access to registers located in the extended memory space.

When the EMEM bit is 0, the address word is limited to 7 bits.

### 4.11.5.4 AUTOINC - B12 Command Word

When AUTOINC is set to 1, Auto-Increment read or write access is enabled.

In Auto-Increment Mode, the device automatically increments the register address for each contiguous read or write access, starting from the address defined in the ADDRESS field of the Command Word.

The internal address is incremented for each 16-bit read or write access until a low-to-high transition on the  $\overline{CS}$  pin is detected.

When AUTOINC is set to 0, single read or write access is required.

Auto-Increment write must not be used to update values in HOST\_CONFIG.

### 4.11.5.5 UNIT ADDRESS - B11:B7 Command Word

The 5 bits of the UNIT ADDRESS field of the Command Word are used to select one of 32 devices connected on a single chip select in Loop-Through or Bus-Through configurations.

Read and write accesses are only accepted if the UNIT ADDRESS field matches the programmed DEVICE UNIT ADDRESS in HOST CONFIG.

By default at power-up or after a device reset, the DEVICE\_UNIT\_ADDRESS is set to 00h

#### 4.11.5.6 ADDRESS - B6:B0 Command Word

If the extended memory is not being accessed (EMEM = 0), the 7 bits of the ADDRESS field are used to select one of 128 register addresses in the device in single read or write access mode, or to set the starting address for read or write accesses in Auto-Increment Mode.

Figure 4-8: Command and Data Word Format

When EMEM is set to 1, the Address Word is extended to 23 bits. The Command and Data Word format will be extended by another 16 bits, and is shown in Figure 4-9 below.

Figure 4-9: Command and Data Word Format with EMEM set to 1