## 2x20W Stereo Single Ended Class D Audio Amplifier

# DESCRIPTION

The MP7748 is a Class D Audio Amplifier for driving stereo speakers in single-ended configuration or a mono speaker in bridge-tiedload configuration. It is fully integrated audio amplifier which dramatically reduces solution size by integrating the following:

- 250mΩ power MOSFETs

- Startup / Shutdown pop elimination

- Short circuit protection circuits

The MP7748 is capable of delivering 20W per channel into  $4\Omega$  speaker in single-ended output structure, or delivering 50W into  $6\Omega$  speaker in bridge-tied-load output structure under 24V VDD. MPS Class D Audio Amplifiers exhibit the high fidelity of a Class A/B amplifier at high efficiencies. The circuit is based on the MPS' proprietary variable frequency topology that delivers excellent linearity, fast response time and operates on a single power supply.

MP7748 features programmable VDD shutdown voltage for each channel by controlling the UVP node voltage. The default VDD shutdown (rising threshold) voltage is 8.4V if the UVP pin is NC.

### FEATURES

- Output Power at 24V VDD and 10% THD+N

- Stereo SE configuration: 20W per channel into  $4\Omega$  load

- Mono BTL configuration: 50W into  $6\Omega$  load

- THD+N = 0.02% at 1W, 8Ω(SE)

- Low Noise (103µV with SE configuration, 140µV with BTL configuration)

- Switching Frequency Up to 1MHz

- 9.5V to 36V Operation from a Single Supply

- Integrated Startup and Shutdown Pop Elimination Circuit

- Programmable UVP

- Thermal and Short Circuit Protection

- Integrated Power FETs

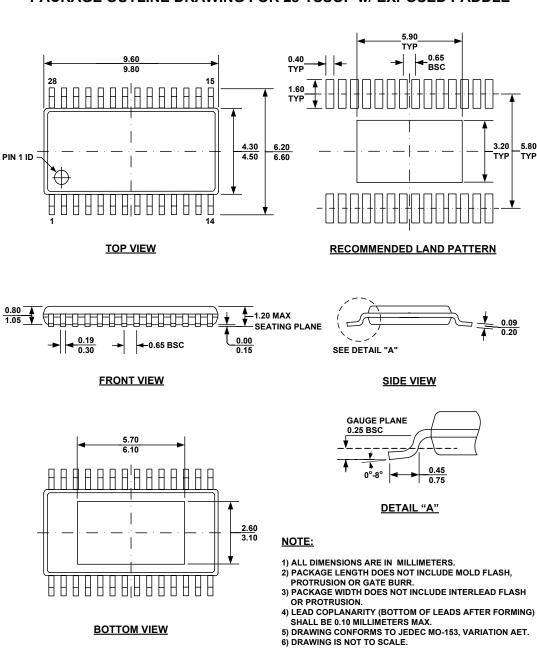

- Available in TSSOP28-Exposed Package

### **APPLICATIONS**

- Portable Docking Stations

- Surround Sound DVD Systems

- Televisions

- Flat Panel Monitors

- Multimedia Computers

- Home Stereo Systems

For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

AAM (Analog Adaptive Modulation) is a Trademark of Monolithic Power Systems, Inc.

MP7748 Rev. 1.0 1/28/2011

### **ORDERING INFORMATION**

| Part Number* | Part Number* Package |          | Free Air Temperature (T <sub>A</sub> ) |  |

|--------------|----------------------|----------|----------------------------------------|--|

| MP7748DF     | TSSOP28F             | MP7748DF | -40°C to +85°C                         |  |

\* For Tape & Reel, add suffix –Z (e.g. MP7748DF–Z). For RoHS compliant packaging, add suffix –LF (e.g. MP7748DF–LF–Z)

# ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage V <sub>DD</sub>      | 40V                                    |

|-------------------------------------|----------------------------------------|

| BS VoltageV <sub>SW</sub> – 0.3     |                                        |

| Enable Voltage V <sub>EN</sub>      | 0.3V to +6V                            |

| $V_{UVP}, V_{SW}, V_{PIN}, V_{NIN}$ | -1V to $V_{DD}$ + 1V                   |

| AGND to PGND                        | 0.3V to +0.3V                          |

| Continuous Power Dissipation (7     | Γ <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                     | 3.9W                                   |

| Junction Temperature                | 150°C                                  |

| Lead Temperature                    | 260°C                                  |

| Storage Temperature                 |                                        |

|                                     | (2)                                    |

### Recommended Operating Conditions<sup>(3)</sup>

| Supply Voltage V <sub>DD</sub>         | 9.5V to 36V |

|----------------------------------------|-------------|

| Maximum Junction Temp. (T <sub>J</sub> | ) +125°C    |

# Thermal Resistance $^{(4)}$ $\theta_{JA}$

$\theta_{\rm JC}$

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD (MAX) =  $(T_J(MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# ELECTRICAL CHARACTERISTICS (5, 6)

### $V_{DD}$ = 24V, $V_{EN}$ = 5V, $T_A$ = +25°C, unless otherwise noted.

| Parameters                                            |                | Symbol           | Condition                          | Min | Тур  | Max | Units |

|-------------------------------------------------------|----------------|------------------|------------------------------------|-----|------|-----|-------|

| Supply Currer                                         | nt             |                  |                                    |     | -    |     |       |

| Standby Curre                                         | nt             |                  | V <sub>EN</sub> = 0V,NIN=PIN=Float |     | 140  |     | μA    |

| Quiescent Curr                                        | rent           | Ι <sub>Q</sub>   | SW=Low                             |     | 3    | 6   | mA    |

| Output Drivers                                        | 5              |                  | · · · · · ·                        |     |      |     |       |

| SW On Resista                                         | ance           |                  | Sourcing and Sinking               |     | 0.25 |     | Ω     |

| Short Circuit Current                                 |                |                  | Sourcing and Sinking               |     | 4.5  |     | Α     |

| Inputs                                                |                |                  |                                    |     |      |     |       |

| EN Enable Threshold Voltage                           |                |                  | V <sub>EN</sub> Rising             |     | 1.4  | 2.0 | V     |

|                                                       | esholu voltage |                  | V <sub>EN</sub> Falling            | 0.4 | 1.0  |     | V     |

| EN Enable Inp                                         | ut Current     |                  | V <sub>EN</sub> = 5V               |     | 5    |     | μA    |

| External Undervoltage Detection                       |                | V <sub>UVP</sub> |                                    |     | 4    |     | V     |

| External Undervoltage<br>Detection Hysteresis Voltage |                | $V_{Hys}$        |                                    |     | 0.3  |     | V     |

| Thermal Shute                                         | down           |                  |                                    |     |      |     | •     |

| Thermal Shutdown Trip Point                           |                |                  | T <sub>J</sub> Rising              |     | 150  |     | °C    |

| Thermal Shutd                                         | own Hysteresis |                  |                                    |     | 30   |     | °C    |

Note:

5) The device is not guaranteed to function outside its operating rating.6) Electrical Characteristics are for the IC only with no external components except bypass capacitors.

# **OPERATING SPECIFICATIONS**

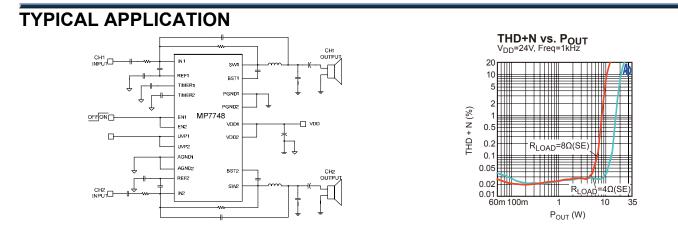

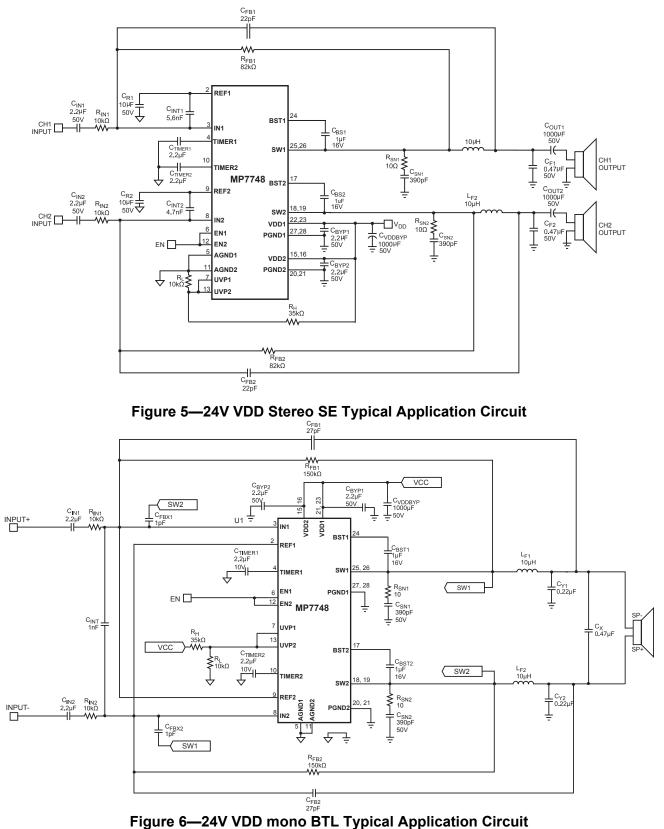

Circuit of figure 5, single-ended output configuration,  $V_{DD}$  = 24V, Gain=8.25V/V,  $V_{EN}$  = 5V,  $T_A$  = +25°C, unless otherwise noted.

| Parameters              | Symbol | Condition                                                         |              | Min  | Тур  | Max | Units |

|-------------------------|--------|-------------------------------------------------------------------|--------------|------|------|-----|-------|

| Standby Current         |        | V <sub>EN</sub> = 0V                                              |              |      | 180  |     | μA    |

| Quiescent Current       |        | Switching, no load                                                |              |      | 26   |     | mA    |

| Devuer Output           |        | f = 1kHz, THD+N =                                                 | 10%, 4Ω Load |      | 19.3 |     | W     |

| Power Output            |        | f = 1kHz, THD+N =                                                 | 10%, 8Ω Load |      | 10.6 |     | W     |

|                         |        | P <sub>OUT</sub> = 1W, f = 1kHz                                   | z, 4Ω Load   |      | 0.02 |     | %     |

| THD+ Noise              |        | P <sub>OUT</sub> = 1W, f = 1kHz                                   |              | 0.02 |      | %   |       |

| [fficiency/             |        | f = 1kHz, P <sub>OUT</sub> = 19                                   |              | 91   |      | %   |       |

| Efficiency              |        | f = 1kHz, P <sub>OUT</sub> = 10                                   |              | 96   |      | %   |       |

| Maximum Power Bandwidth |        |                                                                   |              |      | 20   |     | kHz   |

| Dynamic Range           |        |                                                                   |              |      | 97   |     | dB    |

| Noise Floor             |        | A-Weighted                                                        |              |      | 103  |     | μV    |

| Power Supply Rejection  |        | V <sub>CC</sub> =24V,<br>Gain=8.25V/V,                            | f = 1kHz     |      | -59  |     | dB    |

|                         |        | V <sub>RIPPLE</sub> =200mV <sub>PP</sub><br>C <sub>R</sub> =100µF | f = 217Hz    |      | -59  |     | dB    |

Circuit of figure 6, bridge-tied-load output configuration,  $V_{DD}$  = 24V, Gain=15V/V,  $V_{EN}$  = 5V,  $T_A$  = +25°C, unless otherwise noted.

| Parameters              | Symbol                      | Condition                            |              | Min  | Тур  | Max | Units |

|-------------------------|-----------------------------|--------------------------------------|--------------|------|------|-----|-------|

| Standby Current         |                             | VEN = 0V                             |              |      | 180  |     | μA    |

| Quiescent Current       |                             | Switching, no load                   |              |      | 26   |     | mA    |

| Dowor Output            |                             | f = 1kHz, THD+N =                    | 10%, 6Ω Load |      | 50   |     | W     |

| Power Output            |                             | f = 1kHz, THD+N =                    | 10%, 8Ω Load |      | 40   |     | W     |

|                         |                             | P <sub>OUT</sub> = 1W, f = 1kHz      | , 6Ω Load    |      | 0.04 |     | %     |

| THD+ Noise              |                             | P <sub>OUT</sub> = 1W, f = 1kHz      |              | 0.03 |      | %   |       |

| Efficiency              |                             | f = 1kHz, P <sub>OUT</sub> = 50\     |              | 91   |      | %   |       |

| Efficiency              |                             | f = 1kHz, P <sub>OUT</sub> = 40\     |              | 94   |      | %   |       |

| Maximum Power Bandwidth |                             |                                      |              |      | 20   |     | kHz   |

| Dynamic Range           |                             |                                      |              |      | 107  |     | dB    |

| Noise Floor             |                             | A-Weighted                           |              |      | 140  |     | μV    |

| Power Supply Rejection  |                             | V <sub>CC</sub> =24V,<br>Gain=15V/V, | f = 1kHz     |      | -60  |     | dB    |

|                         | $V_{RIPPLE}$ =200m $V_{PP}$ | f = 217Hz                            |              | -60  |      | dB  |       |

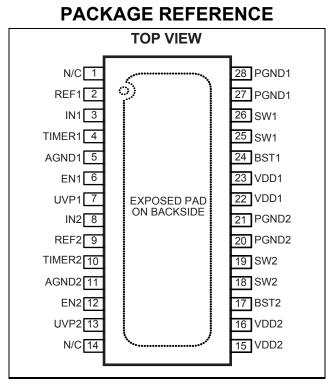

## **PIN FUNCTIONS**

| Pin #  | Name           | Description                                                                                                                                                               |

|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 14  | N/C            | Not connected internally                                                                                                                                                  |

| 2      | REF1           | Internal analog reference (VDD/2) for Amplifier 1. For SE configuration, connect a bypass capacitor from REF1 to AGND (10 $\mu$ F).                                       |

| 3      | IN1            | Inverting input for amplifier 1.                                                                                                                                          |

| 4      | TIMER1         | Internal timer input for Amplifier 1. Connect a capacitor from TIMER1 to AGND ( $2.2\mu$ F) to set the internal timer for startup pop elimination.                        |

| 5      | AGND1          | Analog ground for Amplifier 1. Connect AGND1 to AGND2. Connect PGND to AGND at a single point.                                                                            |

| 6      | EN1            | Enable input for Amplifier 1. Drive EN1 high to turn on the Amplifier 1, low to turn it off.                                                                              |

| 7      | UVP1           | Under-voltage protection reference input for Amplifier 1. Connect UVP1 to UVP2.                                                                                           |

| 8      | IN2            | Inverting input for amplifier 2.                                                                                                                                          |

| 9      | REF2           | Internal analog reference (VDD/2) for Amplifier 2. For SE configuration, connect a bypass capacitor from REF2 to AGND (10 $\mu$ F).                                       |

| 10     | TIMER2         | Internal timer input for Amplifier 2. Connect a capacitor from TIMER2 to AGND (2.2uF) to set the internal timer for startup pop elimination.                              |

| 11     | AGND2          | Analog ground for Amplifier 2. Connect AGND2 to AGND1. Connect PGND to AGND at a single point.                                                                            |

| 12     | EN2            | Enable input for Amplifier 2. Drive EN2 high to turn on the Amplifier 2, low to turn it off.                                                                              |

| 13     | UVP2           | Under-voltage protection reference input for Amplifier 2. Connect UVP2 to UVP1.                                                                                           |

| 15, 16 | VDD2           | Power supply input for Amplifier 2. Bypass VDD2 to PGND2 with a $1\mu$ F X7R capacitor (in addition to the main bulk capacitor), placed close to the VDD2 and PGND2 pins. |

| 17     | BST2           | High-side MOSFET bootstrap input for Amplifier 2. A capacitor from BST2 to SW2 supplies the gate drive current to the internal high-side MOSFET.                          |

| 18, 19 | SW2            | Switched power output for Amplifier 2.                                                                                                                                    |

| 20, 21 | PGND2          | Power ground for Amplifier 2. Connect PGND2 to PGND1. Connect PGND to AGND at a single point.                                                                             |

| 22, 23 | VDD1           | Power supply input for Amplifier 1. Bypass VDD1 to PGND1 with a $1\mu$ F X7R capacitor (in addition to the main bulk capacitor), placed close to the VDD1 and PGND1 pins. |

| 24     | BST1           | High-side MOSFET bootstrap input for Amplifier 1. A capacitor from BST1 to SW1 supplies the gate drive current to the internal high-side MOSFET.                          |

| 25, 26 | SW1            | Switched power output for Amplifier 1.                                                                                                                                    |

| 27, 28 | PGND1          | Power ground for Amplifier 1. Connect PGND1 to PGND2. Connect PGND to AGND at a single point.                                                                             |

|        | Exposed<br>Pad | Connect exposed pad to GND plane for proper thermal performance.                                                                                                          |

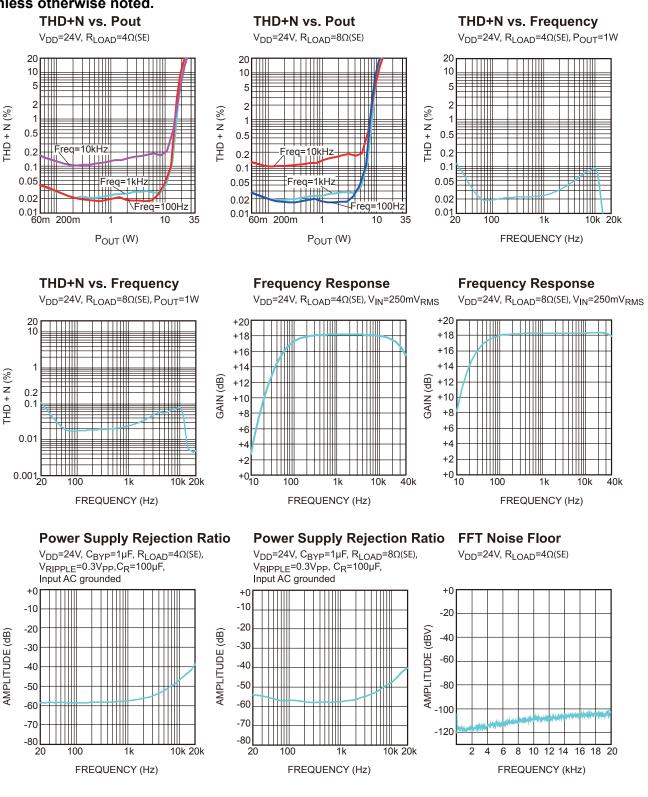

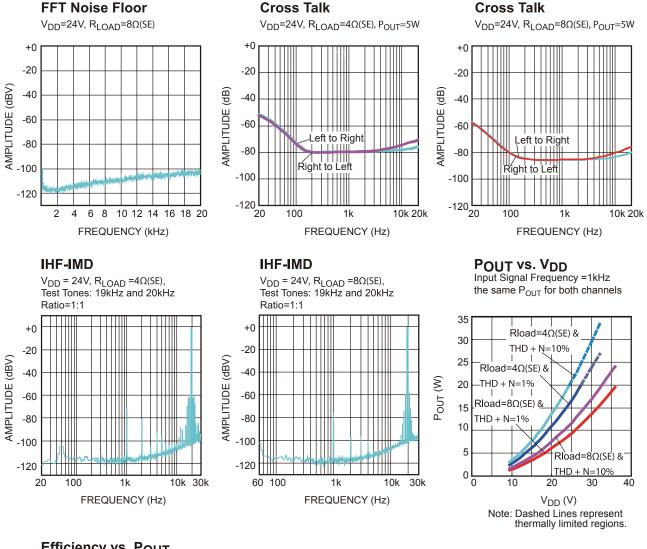

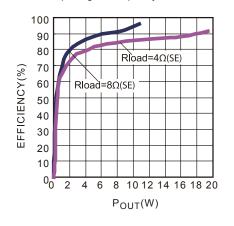

## **TYPICAL PERFORMANCE CURVES**

Circuit of Figure 5, single-ended output configuration,  $V_{DD}$ =24V,  $V_{EN}$ =5V,  $A_V$ =8.25V/V,  $T_A$  = +25°C, unless otherwise noted.

### TYPICAL PERFORMANCE CURVES (continued)

Circuit of Figure 5, single-ended output configuration,  $V_{DD}$ =24V,  $V_{EN}$ =5V,  $A_V$ =8.25V/V,  $T_A$  = +25°C, unless otherwise noted.

**Efficiency vs. POUT** V<sub>DD</sub> = 24V, Input Signal Frequency=1kHz

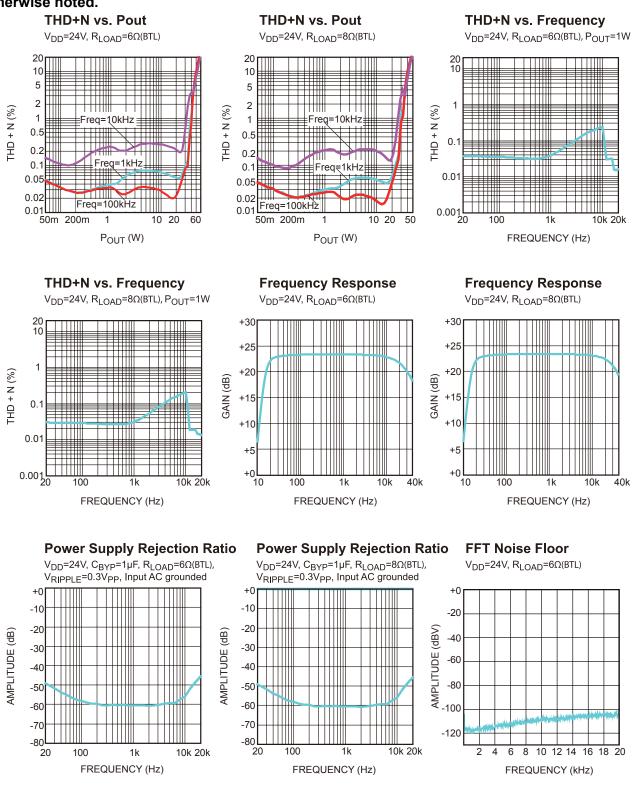

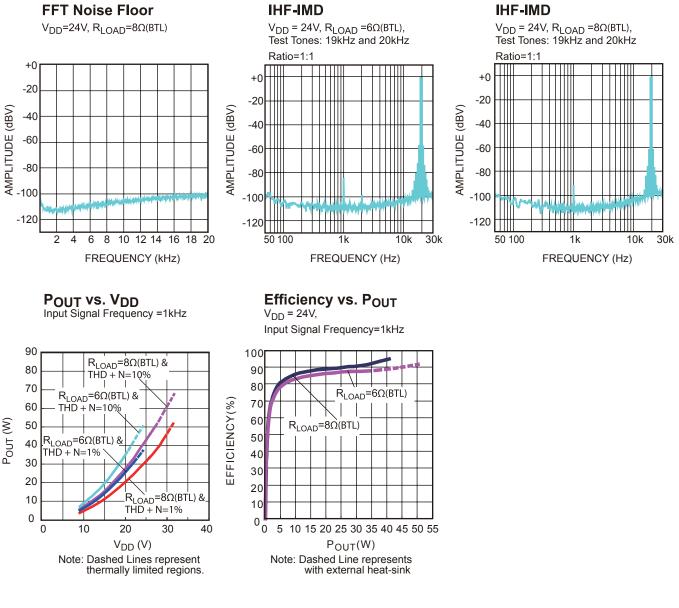

# TYPICAL PERFORMANCE CURVES (continued)

Circuit of Figure 6, BTL output configuration,  $V_{DD}$ =24V,  $V_{EN}$ =5V,  $A_V$ =15V/V,  $T_A$  = +25°C, unless otherwise noted.

## TYPICAL PERFORMANCE CURVES (continued)

Circuit of Figure 6, BTL output configuration,  $V_{DD}$ =24V,  $V_{EN}$ =5V,  $A_V$ =15V/V,  $T_A$  = +25°C, unless otherwise noted.

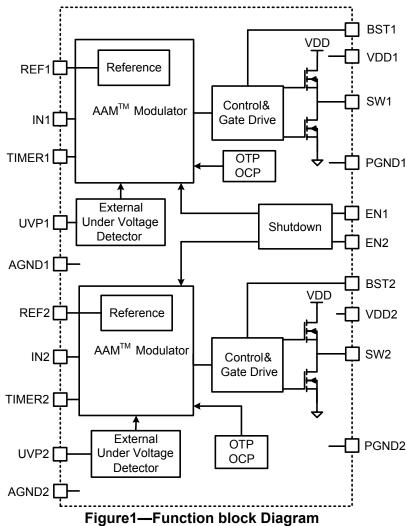

### **BLOCK DIAGRAM**

## OPERATION

The MP7748 is a Class D Audio Amplifier for driving stereo speakers in single-ended configuration or a mono speaker in bridge-tiedload configuration. It uses the Monolithic Power Systems patented Analog Adaptive Modulation<sup>™</sup> to convert the audio input signal into pulses. These pulses drive an internal highcurrent output stage and, when filtered through an external inductor-capacitor filter, reproduce the input signal across the load. Because of the switching Class D output stage, power dissipation in the amplifier is drastically reduced when compared to Class A, B or A/B amplifiers while maintaining high fidelity and low distortion.

REF1/2 are the positive inputs of the two amplifiers. They are set to half the DC power supply input voltage ( $V_{DD}/2$ ) by the internal circuit. The input capacitor  $C_{IN}$  couple the AC signal at the input.

The amplifier voltage gain is set by the combination of the input resister  $R_{IN1/2}$  and the feedback resistor  $R_{FB1/2}$  and is calculated by the equation:

$$AV = \frac{-R_{FB}}{R_{IN}}$$

The MP7748 includes four high-power MOSFETs wherein for each channel the output driver stage uses two 250m N-channel MOSFETs to deliver the pulses to the LC output filter which in turn drives the load. To fully enhance the high-side MOSFET, the gate is driven to a voltage higher than the source by the bootstrap capacitor between SW and BS. While the output is driven low, the bootstrap capacitor is charged from V<sub>DD</sub> through an internal circuit on the MP7748. The gate of the high-side MOSFET is driven high from the voltage at BS, forcing the MOSFET gate to a voltage higher than V<sub>DD</sub> and allowing the MOSFET to fully turn on, reducing power loss in the amplifier.

### **Pop Elimination**

The MP7748 integrates a source current function to charge the AC coupling capacitor  $C_{OUT1/2}$  for the SE output configuration and  $C_{IN1/2}$  at the start up moment. The start up source current slew rate is adjustable by selecting

different capacitance of timer capacitor  $C_{TIMER1/2}$ . The larger the capacitance of the timer capacitor is, the smaller the start up current slew rate is. The recommended 2.2µF timer capacitor results in a start up current slew rate of approximately 20mA/350ms which would help to minimize the turn on pop.

After driving EN pin low, output SW will be set to high impedance immediately which would help to eliminate the turn off pop.

### Short Circuit/Overload Protection

The MP7748 has internal overload and short circuit protection. The currents in both the highside and low-side MOSFETs are measured and if the current exceeds the 4.5A short circuit current limit, both MOSFETs are turned off. The MP7748 then restarts with the same power up sequence that is used for normal starting to prevent a pop from occurring after a short circuit condition is removed.

### **Enable Function**

The MP7748 EN input is an active high enable control. To enable the MP7748, drive EN with a 2.0V or higher voltage. To disable the amplifier, drive it below 0.4V. While the MP7748 is disabled, the VDD operating current is less than  $140\mu$ A and the output driver MOSFETs are turned off.

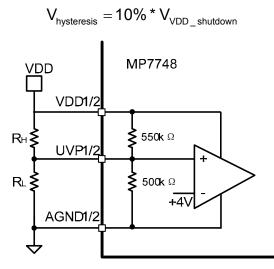

### Programmable UVP

MP7748 integrate programmable UVP function, which can be used to shutdown the MP7748 to escape the pop, by controlling the UVP node voltage. The corresponding circuit is shown in the followed figure 2. If the UVP pin is NC, the default VDD shutdown voltage (rising threshold) is 8.4V since there is internal voltage divided circuit. The VDD shutdown voltage can be flexibly adjusted by controlling UVP pin voltage The recommended VDD shutdown voltage is from 9.5V to power supply. As shown in the figure 2, if external resistor  $R_H$  and  $R_L$  is low enough (e.g.  $R_H$ ,  $R_L < 50k\Omega$ ) compared with internal 500k $\Omega$  and 550k $\Omega$  resistor, the VDD shutdown voltage (rising threshold) can be calculated by the equation:

$$V_{\text{VDD\_shutdown}} = 4 * \frac{(R_{\text{H}} + R_{\text{L}})}{R_{\text{L}}}$$

The hysteresis voltage can be calculated by the equation:

Figure 2—UVP block diagram

## **APPLICATION INFORMATION**

#### **Component Selection**

The MP7748 uses a minimum number of external components to complete a stereo SE or mono BTL Class D audio amplifier. The circuit of Figure 3 (stereo SE application circuit) and figure 4 (mono BLT application circuit) are optimized for a 24V power supply. This circuit should be suitable for most applications, and use the following sections to determine how to customize the amplifier for a particular application.

#### Setting the Voltage Gain

The maximum output voltage swing is limited by the power supply. To achieve the maximum power out of the MP7748 amplifier, set the gain such that the maximum input signal results in the maximum output voltage swing.

For single-ended (SE) output configuration, the maximum output voltage  $V_{OUT(PK)}$  is  $V_{DD}/2$ . For bridge-tied-load (BTL) output configuration, the maximum output voltage  $V_{OUT(PK)}$  is  $V_{DD}$ . For a given input signal voltage, where  $V_{IN(PK)}$  is the peak input voltage, the maximum voltage gain is:

$$A_{V}(MAX) = \frac{V_{OUT(PK)}}{V_{IN(PK)}}$$

This voltage gain setting results in the peak output voltage approaching it's maximum for the maximum input signal. In some cases the amplifier is allowed to overdrive slightly, allowing the THD to increase at high power levels, and so a higher gain than  $A_V$  (max) is required.

### **Setting the Switching Frequency**

The idle switching frequency (the switching frequency when no audio input is present) is a function of several variables: the supply voltage  $V_{\text{DD}}$ , the integral capacitor  $C_{\text{INT}}$  and the feedback resistor R<sub>FB</sub>. Lower switching frequency results in more inductor ripple, causing more guiescent output voltage ripple and increasing the output noise and distortion. Higher switching frequencies result in more power loss. The optimum quiescent switching frequency is approximately 600kHz. When used to drive stereo speakers in single-ended configuration, it is recommended to set right channel idle switching frequency larger than left channel's with 50k Hz difference by using different timing capacitor  $C_{INT}$ . For detailed please refer to the table 1 for recommended SE output configuration design, and table 2 for recommended BTL output configuration design.

| VDD | Gain  | R <sub>FB</sub> | R <sub>IN</sub> | Left<br>channel           |                           |                           | ght<br>nnel               |

|-----|-------|-----------------|-----------------|---------------------------|---------------------------|---------------------------|---------------------------|

| (V) | (V/V) | (kΩ)            | (kΩ)            | C <sub>INT1</sub><br>(nF) | F <sub>sw1</sub><br>(kHz) | C <sub>INT2</sub><br>(nF) | F <sub>sw2</sub><br>(kHz) |

| 12  | 5.6   | 56              | 10              | 4.7                       | 560                       | 3.3                       | 700                       |

| 12  | 8.2   | 39              | 4.7             | 5.6                       | 620                       | 4.7                       | 700                       |

| 12  | 12.0  | 56.4            | 4.7             | 4.7                       | 530                       | 3.3                       | 670                       |

| 12  | 17.6  | 56.4            | 3.2             | 4.7                       | 530                       | 3.3                       | 670                       |

| 12  | 25.5  | 56.4            | 2.2             | 4.7                       | 530                       | 3.3                       | 670                       |

| 12  | 30    | 60              | 2               | 4.7                       | 520                       | 3.3                       | 650                       |

| 24  | 5.6   | 56              | 10              | 10                        | 540                       | 8.2                       | 650                       |

| 24  | 8.2   | 82              | 10              | 5.6                       | 610                       | 4.7                       | 690                       |

| 24  | 12.0  | 120             | 10              | 4.7                       | 530                       | 3.3                       | 660                       |

| 24  | 17.4  | 82              | 4.7             | 5.6                       | 610                       | 4.7                       | 690                       |

| 24  | 25.5  | 120             | 4.7             | 4.7                       | 530                       | 3.3                       | 660                       |

| 24  | 30    | 120             | 4               | 4.7                       | 530                       | 3.3                       | 660                       |

Table 1—Switching Frequency Setting For SE

Output Configuration

| Table 2 - Switching Frequency Setting For |

|-------------------------------------------|

| BTL Output Configuration                  |

| V <sub>DD</sub><br>(V) | Gain<br>(V/V) | R <sub>FB</sub><br>(kΩ) | R <sub>IN</sub><br>(kΩ) | C <sub>INT1</sub><br>(nF) | F <sub>sw1</sub><br>(kHz) |

|------------------------|---------------|-------------------------|-------------------------|---------------------------|---------------------------|

| 12                     | 10            | 100                     | 10                      | 3.9                       | 400                       |

| 12                     | 20            | 100                     | 5                       | 3.3                       | 400                       |

| 12                     | 30            | 121                     | 4.02                    | 2.7                       | 400                       |

| 24                     | 10            | 100                     | 10                      | 3.9                       | 580                       |

| 24                     | 20            | 121                     | 6.04                    | 3.9                       | 480                       |

| 24                     | 30            | 121                     | 4.02                    | 3.9                       | 480                       |

| 32                     | 10            | 100                     | 10                      | 4.7                       | 580                       |

| 32                     | 20            | 121                     | 6.04                    | 3.9                       | 560                       |

| 32                     | 30            | 162                     | 5.36                    | 3.3                       | 500                       |

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2011 MPS. All Rights Reserved.

#### Choosing the Output LC Filter

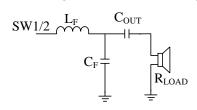

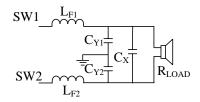

The Inductor-Capacitor (LC) filter converts the pulse train at SW to the output voltage that drives the speaker. There are two kinds of LC filter structure depending on the output configuration.

#### Figure 3—SE Filter Configuration

Figure 4—BTL Filter Configuration Where:

$$\begin{split} L_{\rm F} &= L_{\rm F1} + L_{\rm F2} \,, \\ C_{\rm F} &= C_{\rm X} + \frac{C_{\rm Y1} \times C_{\rm Y2}}{C_{\rm Y1} + C_{\rm Y2}} \\ L_{\rm F1} &= L_{\rm F2} \,; \\ C_{\rm Y1} &= C_{\rm Y2} \end{split}$$

The characteristic frequency of the LC filter needs to be high enough to allow high frequency audio to the output, yet needs to be low enough to filter out high frequency products of the pulses from SW. The characteristic frequency of the LC filter is:

$$f_0 = \frac{1}{2 \times \pi \times \sqrt{L_F \times C_F}}$$

The quality factor (Q) of the LC filter is important. If this is too low, output noise will increase, if this is too high, then peaking may occur at high signal frequencies reducing the passband flatness. The circuit Q is set by the load resistance (speaker resistance, typically  $4\Omega$  or  $8\Omega$ ). The Q is calculated as:

$$Q = \frac{R_{LOAD}}{\omega_0 \times L_F} = \frac{R_{LOAD}}{2\pi \times f_0 \times L_F}$$

$\omega_0$  is the characteristic frequency in radians per second and  $f_0$  is in Hz. Use an LC filter with Q between 0.7 and 1.

The actual output ripple and noise is greatly affected by the type of inductor and capacitor used in the LC filter. Use a film capacitor and an inductor with sufficient power handling capability to supply the output current to the load. The inductor should exhibit soft saturation characteristics. If the inductor exhibits hard saturation, it should operate well below the current. Gapped ferrite, MPP. saturation Powdered Iron, or similar type toroidal cores are recommended. If open or shielded bobbin ferrite cores are used for multi-channel designs, make sure that the start windings of each inductor line up (all starts going toward SW pin, or all starts going toward the output) to prevent crosstalk or other channel-to-channel interference.

#### **Output Coupling Capacitor For SE Output**

The output AC coupling capacitor  $C_{OUT}$  serves to block DC voltages and thus passes only the amplified AC signal from the LC filter to the load. The combination of the coupling capacitor,  $C_{OUT}$ and the load resistance results in a first-order high-pass filter. The value of  $C_{OUT}$  should be selected such that the required minimum frequency is still allowed to pass. The output corner frequency (-3dB point),  $f_{OUT}$ , can be calculated as:

$$f_{OUT} = \frac{1}{2 \times \pi \times R_{LOAD} \times C_{OUT}}$$

Set the output corner frequency  $(f_{OUT})$  at or below the minimum required frequency.

The output coupling capacitor carries the full load current, so a capacitor should be chosen such that its ripple current rating is greater than the maximum load current. Low ESR aluminum electrolytic capacitors are recommended.

#### Input Coupling Capacitor

The input coupling capacitors  $C_{IN1}$  and  $C_{IN2}$  are used to pass only the AC signal at the input. In a typical system application, the source input signal is typically centered around the circuit ground, while the MP7748 input is at half the power supply voltage (V<sub>DD</sub>/2). The input coupling capacitor transmits the AC signal from the source

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2011 MPS. All Rights Reserved. to the MP7748 while blocking the DC voltage. Choose an input coupling capacitor such that the corner frequency ( $f_{IN}$ ) is less than the passband frequency. The corner frequency is calculated as:

$$f_{IN} = \frac{1}{2 \times \pi \times R_{IN} \times C_{IN}}$$

#### **Timer capacitor**

The start up source current slew rate is adjustable by selecting different capacitance of timer capacitor  $C_{TIMER}$ . The larger the  $C_{TIMER}$  capacitance is, the smaller the start up current slew rate is. It is recommended to use the  $C_{TIMER}$  which capacitance is larger than 312nF, so the start up current slew rate would be smaller than 20mA/50ms which would help to eliminate the turn on pop. The recommended 2.2µF capacitor  $C_{TIMER}$  results in a start up current slew rate of approximately 20mA/350ms.

#### **Power Source**

For maximum output power, the amplifier circuit requires a regulated external power source to supply the power to the amplifier. The higher the power supply voltage, the more power can be delivered to a given load resistance, however if the power source voltage exceeds the maximum voltage of 36V, the MP7748 may sustain damage. The power supply rejection of the MP7748 is excellent, however noise at the power supply can get to the output, so care must be taken to minimize power supply noise within the pass-band frequencies. Bypass the power supply with a large capacitor (typically aluminum electrolytic) along with a smaller  $1\mu$ F ceramic capacitor at the MP7748 V<sub>DD</sub> supply pins.

#### PCB Layout

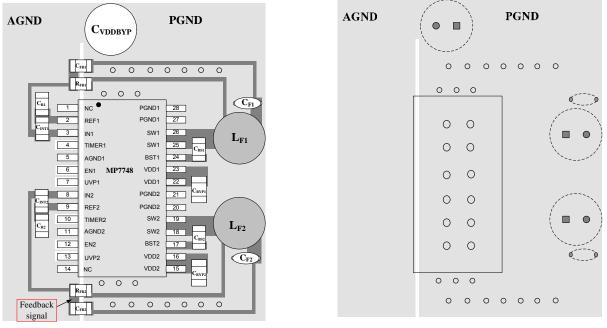

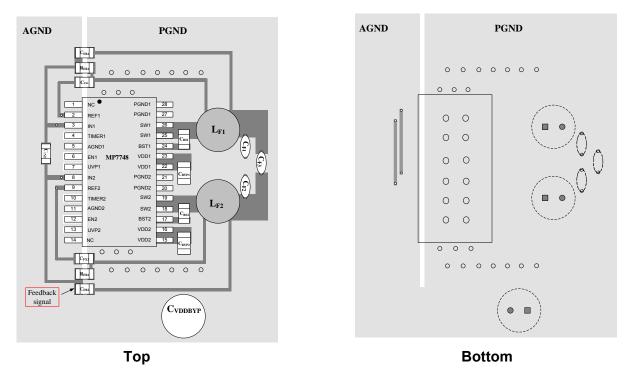

The circuit layout is critical for optimum performance and low output distortion and noise. It is highly recommended to duplicate EVB layout for optimum performance. If change is necessary, please follow these guidelines and take Figure 7 for references.

1) Place the following components as close to the MP7748 as possible:

#### Bootstrap Cap

$C_{BS1}$  and  $C_{BS2}$  are used to supply the gate drive current to the internal high-side MOSFET. Place  $C_{BS1}$  as close to BST1/2 pin and SW1/2 pin as

possible. Likewise, place  $C_{BS2}$  as close to BST2 pin and SW2 pins as possible.

#### Power Supply Bypass Cap

$C_{BYP1}$  and  $C_{BYP2}$  carry the transient current for the switching power stage. To prevent overstressing of the MP7748 and excessive noise at the output, place  $C_{BYP1}$  as close to VDD1 pins and PGND1 pins as possible and also place  $C_{BYP2}$  as close to VDD2 pins and PGND2 pins as possible.

#### Integral Capacitors

$C_{INT}$  are used to set the amplifier switching frequencies and are typically on the order of a few nF. Place the integral capacitor  $C_{INT}$  as close to the corresponding input as possible to reduce distortion and noise. For example, place  $C_{INT1}$  as close to pins 2 and 3 as possible at SE output configuration.

#### Reference Bypass Capacitors For SE Output

When used with SE output, CR1 and CR2 is needed to filter the  $\frac{1}{2}$  VDD reference voltages. Place C<sub>R1</sub> and C<sub>R2</sub> as close to the IC as possible to improve power supply rejection and reduce distortion and noise at the output.

2) The Inductor-Capacitor (LC) filter converts the pulse train at SW to the output voltage that drives the speaker. Please keep the filter capacitor close to the inductor.

3) When laying out the PCB, use two separate ground planes, analog ground (AGND) and power ground (PGND), and connect the two grounds together at a single point (usually around the bulk bypass capacitor) to prevent noise injection into the amplifier input to reduce distortion.

4) Keep the sensitive feedback signal trace on the input side and shield the trace with the AGND plane. Make sure that any traces carrying the switch node (SW) voltages are separated far from any input signal traces. If it is required to run the SW trace near the input, shield the input with a ground plane between the traces. Make sure that each channel is physically separated to prevent crosstalk. Make sure that all inductors used on a single circuit board have the same orientation.

Also, make sure that the power supply is routed from the source to each channel individually, not serially. This prevents channel-to-channel coupling through the power supply input.

#### Electro-Magnetic Interference (EMI) Considerations

Due to the switching nature of the Class D amplifier, care must be taken to minimize the effects of electromagnetic interference from the amplifier. However, with proper component selection and careful attention to circuit layout, the effects of the EMI due to the amplifier switching can be minimized.

The power inductors are a potential source of emissions. For the radiated best EMI performance, use toroidal inductors, since the magnetic field is well contained inside the core. However toroidal inductors can be expensive to wind. For a more economical solution, use shielded gapped ferrite or shielded ferrite bobbin core inductors. These inductors typically do not contain the field as well toroidal inductors, but usually can achieve a better balance of good EMI performance with low cost.

The size of high-current loops that carry rapidly changing currents needs to be minimized. To do this, make sure that the  $V_{DD}$  bypass capacitors are as close to the MP7748 as possible.

Nodes that carry rapidly changing voltage, such as SW, need to be made as small as possible. If sensitive traces run near a trace connected to SW, place a ground shield between the traces.

## **YPICAL APPLICATION CIRCUIT**

Bottom

Figure 8—Mono BTL Reference PCB Layout

## **PACKAGE INFORMATION**

TSSOP28

### PACKAGE OUTLINE DRAWING FOR 28-TSSOP w/ EXPOSED PADDLE

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

«JONHON» (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«FORSTAR» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный) Факс: 8 (812) 320-03-32 Электронная почта: ocean@oceanchips.ru Web: http://oceanchips.ru/ Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А