# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

#### **General Description**

The DS1339B serial real-time clock (RTC) is a lowpower clock/date device with two programmable timeof-day alarms and a programmable square-wave output. Address and data are transferred serially through an I<sup>2</sup>C bus. The clock/date provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator. The device has a built-in power-sense circuit that detects power failures and automatically switches to the backup supply, maintaining time, date, and alarm operation.

### **Applications**

- Handhelds (GPS, POS Terminals)

- Consumer Electronics (Set-Top Box, Digital Recording, Network Appliance)

- Office Equipment (Fax/Printers, Copier)

- Medical (Glucometer, Medicine Dispenser)

- Telecommunications (Routers, Switches, Servers)

- Other (Utility Meter, Vending Machine, Thermostat, Modem)

#### **Benefits and Features**

- Drop-In Replacement for DS1339

- Supports High-ESR Crystals Up to 100kΩ to Allow Crystals to be Optimized for Cost and Space

- Completely Manages All Timekeeping Functions

- Real-Time Clock Counts Seconds, Minutes, Hours, Date of the Month, Month, Day of the Week, and Year with Leap-Year Compensation Valid Up to 2200

- Two Time-of-Day Alarms

- Programmable Square-Wave Output Signal

- Low-Power Operation Extends Battery Backup Run Time

Automatic Power-Fail Detect and Switch Circuitry

- Simple Serial Port Interfaces to Most Microcontrollers

I<sup>2</sup>C Serial Interface

- Underwriters Laboratories (UL®) Recognized

#### Ordering Information appears at end of data sheet.

UL is a registered trademark of Underwriters Laboratories Inc.

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

### **Absolute Maximum Ratings**

Lead Temperature (soldering, 10s) .....+300°C Soldering Temperature (reflow) .....+260°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Package Thermal Characteristics(Note 1)

μSOP

Junction-to-Ambient Thermal Resistance  $(\theta_{JA})$  ...... 206.3°C/W

Junction-to- Case Thermal Resistance (0<sub>JC</sub>)...... 42°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

### **Recommended Operating Conditions**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER             | SYMBOL          | CONDITIONS | MIN             | TYP  | MAX                      | UNITS |

|-----------------------|-----------------|------------|-----------------|------|--------------------------|-------|

| Supply Voltage        | V <sub>CC</sub> |            | 1.71            | 3.3  | 5.5                      | V     |

| Paakun Sunnhu Valtaga | VBACKUP         |            | 1.3             | 3.0  | 3.7                      | v     |

| Backup Supply Voltage | VBACKMIN        |            | 1.15            | 1.3  |                          | v     |

| Logic 1               | VIH             |            | 0.7 x           |      | 5.5                      | V     |

|                       |                 |            | V <sub>CC</sub> |      |                          |       |

| Logic 0               | VIL             |            | -0.3            |      | 0.3 x<br>V <sub>CC</sub> | V     |

| Power-Fail Voltage    | V <sub>PF</sub> |            | 1.51            | 1.61 | 1.71                     | V     |

### **DC Electrical Characteristics**

(V<sub>CC</sub> = MIN to MAX,  $V_{BACKUP}$  = MIN to MAX,  $T_A$  = -40°C to +85°C.) (Note 2)

| PARAMETER                                                                                                                       | SYMBOL          | CONDITIONS | MIN  | TYP | MAX | UNITS |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|------|-----|-----|-------|

| Input Leakage                                                                                                                   | ILI             | (Note 3)   | -0.1 |     | 0.1 | μA    |

| I/O Leakage                                                                                                                     | ILO             | (Note 4)   | -0.1 |     | 0.1 | μA    |

| Logic 0 Out (SDA or SQW/ $\overline{INT}$ )<br>V <sub>OL</sub> = 0.4V,<br>V <sub>CC</sub> $\geq$ V <sub>CCMIN</sub>             | I <sub>OL</sub> | (Note 4)   |      |     | 3   | mA    |

| Logic 0 Out (SQW/ $\overline{INT}$ )<br>V <sub>OL</sub> = 0.2V, V <sub>CC</sub> = 0V,<br>V <sub>BAT</sub> ≥ V <sub>BATMIN</sub> | I <sub>OL</sub> | (Note 4)   |      |     | 250 | μA    |

| V <sub>CC</sub> Active Current                                                                                                  | ICCA            | (Note 5)   |      |     | 450 | μA    |

| V <sub>CC</sub> Standby Current                                                                                                 | Iccs            | (Note 6)   |      |     | 200 | μA    |

| Trickle-Charger Resistor Register<br>10h = A5h, $V_{CC}$ = Typ,<br>$V_{BACKUP}$ = 0V                                            | R1              | (Note 7)   |      | 200 |     | Ω     |

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

## **DC Electrical Characteristics (continued)**

(V<sub>CC</sub> = MIN to MAX,  $V_{BACKUP}$  = MIN to MAX,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                                                            | SYMBOL             | CONDITIONS | MIN  | TYP  | MAX | UNITS |

|--------------------------------------------------------------------------------------|--------------------|------------|------|------|-----|-------|

| Trickle-Charger Resistor Register<br>10h = A6h, $V_{CC}$ = Typ,<br>$V_{BACKUP}$ = 0V | R2                 |            |      | 2000 |     | Ω     |

| Trickle-Charger Resistor Register<br>10h = A7h, $V_{CC}$ = Typ,<br>$V_{BACKUP}$ = 0V | R3                 |            |      | 4000 |     | Ω     |

| VBACKUP Leakage Current                                                              | I <sub>BKLKG</sub> |            | -100 | 25   | 200 | nA    |

### **DC Electrical Characteristics**

(V<sub>CC</sub> = 0V, V<sub>BACKUP</sub> = MIN to MAX,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                        | SYMBOL            | CONDITIONS | MIN | TYP | MAX  | UNITS |

|--------------------------------------------------|-------------------|------------|-----|-----|------|-------|

| V <sub>BACKUP</sub> Current EOSC = 0,<br>SQW Off | IBKOSC            | (Note 8)   |     | 300 | 600  | nA    |

| V <sub>BACKUP</sub> Current EOSC = 0,<br>SQW On  | IBKSQW            | (Note 8)   |     | 500 | 1100 | nA    |

| V <sub>BACKUP</sub> Current EOSC = 1             | I <sub>BKDR</sub> |            |     | 10  | 200  | nA    |

### **AC Electrical Characteristics**

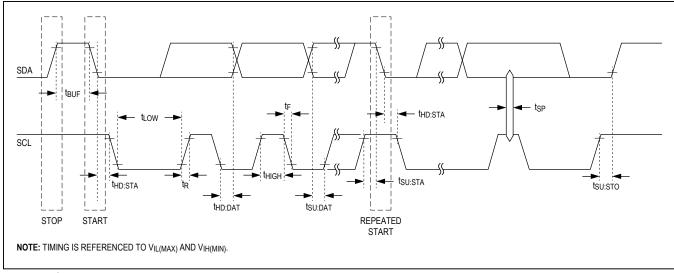

(V<sub>CC</sub> = MIN to MAX,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2, Figure 1)

| PARAMETER                                        | SYMBOL              | CONDITIONS     | MIN  | TYP | MAX | UNITS |

|--------------------------------------------------|---------------------|----------------|------|-----|-----|-------|

| SCL Clock Frequency                              | f <sub>SCL</sub>    |                | 0.03 |     | 400 | kHz   |

| Bus Free Time Between a STOP and START Condition | t <sub>BUF</sub>    |                | 1.3  |     |     | μs    |

| Hold Time (Repeated) START<br>Condition          | t <sub>HD:STA</sub> | (Note 9)       | 0.6  |     |     | μs    |

| Low Period of SCL Clock                          | tLOW                |                | 1.3  |     |     | μs    |

| High Period of SCL Clock                         | thigh               |                | 0.6  |     |     | μs    |

| Setup Time for a Repeated START Condition        | t <sub>SU:STA</sub> |                | 0.6  |     |     | μs    |

| Data Hold Time                                   | thd:dat             | (Notes 10, 11) | 0    |     | 0.9 | μs    |

| Data Setup Time                                  | t <sub>SU:DAT</sub> | (Note 12)      | 100  |     |     | ns    |

| Rise Time of Both SDA and SCL Signals            | t <sub>R</sub>      | (Note 13)      |      |     | 300 | ns    |

| Fall Time of Both SDA and SCL Signals            | t <sub>F</sub>      | (Note 13)      |      |     | 300 | ns    |

| Setup Time for STOP Condition                    | t <sub>SU:STO</sub> |                | 0.6  |     |     | μs    |

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

## **AC Electrical Characteristics (continued)**

(V<sub>CC</sub> = MIN to MAX,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2, Figure 1)

| PARAMETER                         | SYMBOL               | CONDITIONS | MIN | TYP | MAX | UNITS |

|-----------------------------------|----------------------|------------|-----|-----|-----|-------|

| Capacitive Load for Each Bus Line | CB                   | (Note 13)  |     |     | 400 | pF    |

| I/O Capacitance (SDA, SCL)        | C <sub>I/O</sub>     | (Note 14)  |     |     | 10  | pF    |

| Oscillator Stop Flag (OSF) Delay  | t <sub>OSF</sub>     | (Note 15)  |     |     | 100 | ms    |

| Timeout Interval                  | t <sub>TIMEOUT</sub> | (Note 16)  | 25  |     | 35  | ms    |

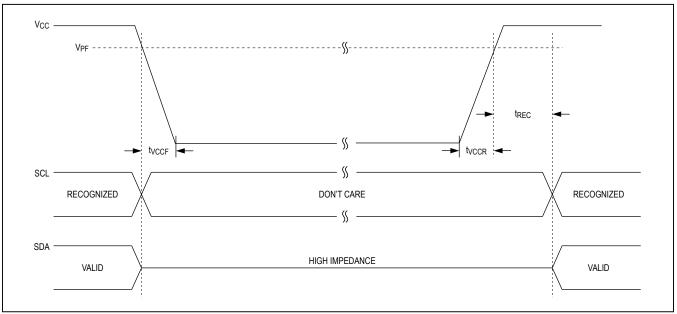

### **Power-Up/Down Characteristics**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 2, Figure 2)

| PARAMETER                                        | SYMBOL            | CONDITIONS | MIN | TYP | MAX  | UNITS |

|--------------------------------------------------|-------------------|------------|-----|-----|------|-------|

| Recovery at Power-Up                             | t <sub>REC</sub>  | (Note 17)  |     | 1   | 2    | ms    |

| V <sub>CC</sub> Slew Rate; V <sub>PF</sub> to 0V | t <sub>VCCF</sub> |            |     |     | 1/50 | V/µs  |

| $V_{CC}$ Slew Rate; 0V to $V_{PF}$               | t <sub>VCCR</sub> |            |     |     | 1/1  | V/µs  |

# WARNING: Under no circumstances are negative undershoots, of any amplitude, allowed when device is in battery-backup mode.

- **Note 2:** Limits are 100% production tested at  $T_A = +25^{\circ}C$  and  $T_A = +85^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.

- Note 3: SCL only.

- Note 4: SDA and SQW/INT.

- Note 5:  $I_{CCA}$ —SCL at  $f_{SCL}$  max,  $V_{IL}$  = 0.0V,  $V_{IH}$  =  $V_{CC}$ , trickle charger disabled.

- **Note 6:** Specified with the I<sup>2</sup>C bus inactive,  $V_{IL} = 0.0V$ ,  $V_{IH} = V_{CC}$ , trickle charger disabled.

- Note 7:  $V_{CC}$  must be less than 3.63V if the 200 $\Omega$  resistor is selected.

- Note 8: Using recommended crystal on X1 and X2.

- Note 9: After this period, the first clock pulse is generated.

- Note 10: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

Note 11: The maximum t<sub>HD:DAT</sub> need only be met if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

- Note 12: A fast-mode device can be used in a standard-mode system, but the requirement t<sub>SU:DAT</sub> ≥ to 250ns must then be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line t<sub>R(MAX)</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns before the SCL line is released.

- Note 13: C<sub>B</sub>—total capacitance of one bus line in pF.

- Note 14: Guaranteed by design; not production tested.

- Note 15: The parameter t<sub>OSF</sub> is the period of time the oscillator must be stopped for the OSF flag to be set.

- Note 16: The device can detect any single SCL clock held low longer than t<sub>TIMEOUTMIN</sub>. The device's l<sup>2</sup>C interface is in reset state and can receive a new START condition when SCL is held low for at least t<sub>TIMEOUTMAX</sub>. Once the device detects this condition, the SDA output is released. The oscillator must be running for this function to work.

- Note 17: This delay applies only if the oscillator is running. If the oscillator is disabled or stopped, no power-up delay occurs.

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

Figure 1. I<sup>2</sup>C Timing

Figure 2. Power-Up/Down Timing

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

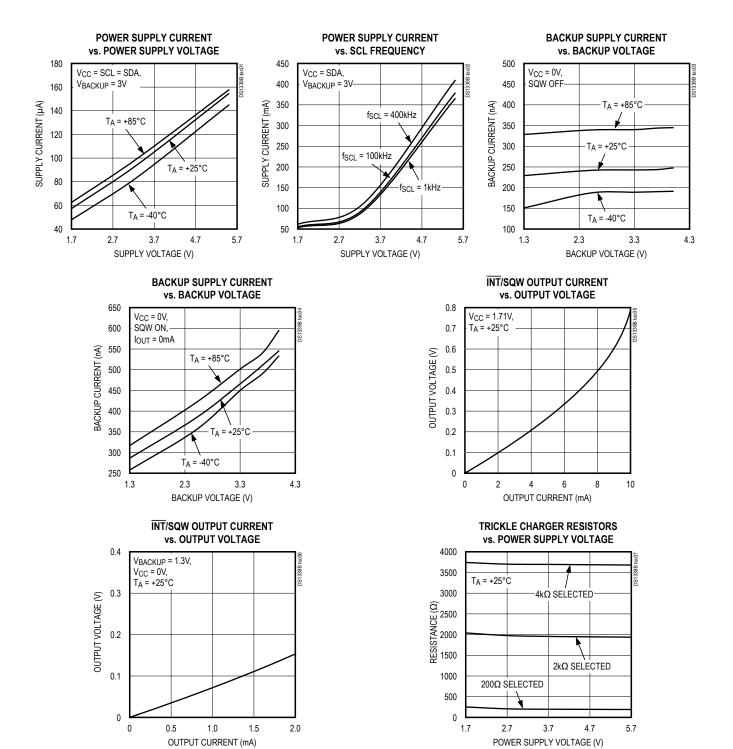

## **Typical Operating Characteristics**

(V<sub>CC</sub> = 3.3V, T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

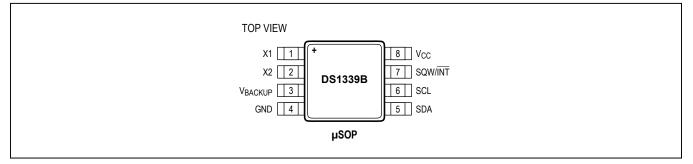

## **Pin Configuration**

## **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | X1              | Connections for Standard 32.768kHz Quartz Crystal. The internal oscillator circuitry is designed for operation with a crystal having a specified load capacitance ( $C_L$ ) of 6pF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2   | X2              | For more information about crystal selection and crystal layout considerations, see the <i>Applications Information</i> section and refer to <i>Application</i> Note 58: <i>Crystal Considerations with Dallas Real-Time Clocks</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   | VBACKUP         | Secondary Power Supply. Supply voltage must be held between 1.3V and 3.7V for proper operation.<br>This pin can be connected to a primary cell, such as a lithium coin cell. Additionally, this pin can be<br>connected to a rechargeable cell or a super cap when used in conjunction with the trickle-charge<br>feature. Diodes should not be placed in series between the backup source and the V <sub>BACKUP</sub> input,<br>or improper operation will result. If a backup supply is not required, V <sub>BACKUP</sub> must be grounded. UL<br>recognized to ensure against reverse charging current when used with a primary lithium cell. For more<br>information, visit <u>www.maximintegrated.com/qa/info/ul</u> . |

| 4   | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5   | SDA             | Serial Data Input/Output. SDA is the input/output pin for the I <sup>2</sup> C serial interface. The SDA pin is an open-<br>drain output and requires an external pullup resistor. The pull up voltage may be up to 5.5V regardless of the voltage on $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6   | SCL             | Serial Clock Input. SCL is used to synchronize data movement on the I <sup>2</sup> C serial interface. The pull up voltage may be up to 5.5V regardless of the voltage on $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7   | SQW/ĪNT         | Square-Wave/Interrupt Output. Programmable square-wave or interrupt output signal. The SQW/ $\overline{INT}$ pin is an open-drain output and requires an external pullup resistor. The pull up voltage may be up to 5.5V regardless of the voltage on V <sub>CC</sub> . If not used, this pin may be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8   | V <sub>CC</sub> | Primary Power Supply. When voltage is applied within normal limits, the device is fully accessible and data can be written and read. When a backup supply is connected and $V_{CC}$ is below $V_{PF}$ , reads and writes are inhibited. The timekeeping and alarm functions operate when the device is powered by $V_{CC}$ or $V_{BACKUP}$ .                                                                                                                                                                                                                                                                                                                                                                                |

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

### **Detailed Description**

The DS1339B serial real-time clock (RTC) is a lowpower clock/date device with two programmable timeof-day alarms and a programmable square-wave output. Address and data are transferred serially through an I<sup>2</sup>C bus. The clock/date provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator. The device has a built-in power-sense circuit that detects power failures and automatically switches to the backup supply, maintaining time, date, and alarm operation.

### **Table 1. Power Control**

| SUPPLY CONDITION                                                          | READ/<br>WRITE<br>ACCESS | POWERED<br>BY   |

|---------------------------------------------------------------------------|--------------------------|-----------------|

| V <sub>CC</sub> < V <sub>PF</sub> , V <sub>CC</sub> < V <sub>BACKUP</sub> | No                       | VBACKUP         |

| $V_{CC} < V_{PF}, V_{CC} > V_{BACKUP}$                                    | No                       | V <sub>CC</sub> |

| V <sub>CC</sub> > V <sub>PF</sub> , V <sub>CC</sub> < V <sub>BACKUP</sub> | Yes                      | V <sub>CC</sub> |

| $V_{CC} > V_{PF}, V_{CC} > V_{BACKUP}$                                    | Yes                      | V <sub>CC</sub> |

### **Table 2. Crystal Specifications\***

| PARAMETER            | SYMBOL         | MIN | TYP    | MAX | UNITS |

|----------------------|----------------|-----|--------|-----|-------|

| Nominal<br>Frequency | f <sub>O</sub> |     | 32.768 |     | kHz   |

| Series Resistance    | ESR            |     |        | 100 | kΩ    |

| Load<br>Capacitance  | CL             |     | 6      |     | pF    |

\*The crystal, traces, and crystal input pins should be isolated from RF generating signals. Refer to <u>Application Note 58:</u> <u>Crystal Considerations for Dallas Real-Time Clocks</u> for additional specifications.

### Operation

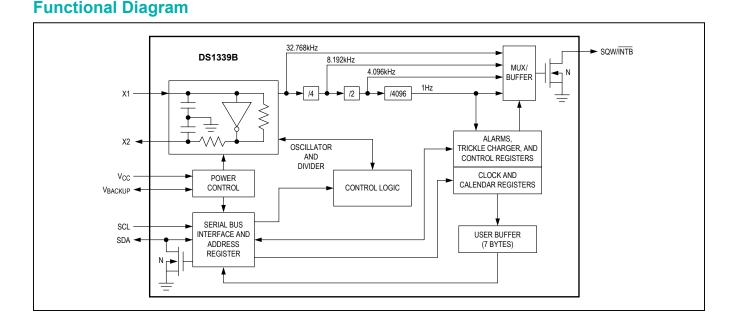

The device operates as a slave device on the serial bus. Access is obtained by implementing a START condition and providing a device identification code followed by data. Subsequent registers can be accessed sequentially until a STOP condition is executed. The device is fully accessible and data can be written and read when V<sub>CC</sub> is greater than VPF. However, when VCC falls below V<sub>PF</sub>, the internal clock registers are blocked from any access. If V<sub>PF</sub> is less than V<sub>BACKUP</sub>, the device power is switched from  $V_{CC}$  to  $V_{BACKUP}$  when  $V_{CC}$  drops below VPF. If VPF is greater than VBACKUP, the device power is switched from  $V_{CC}$  to  $V_{\text{BACKUP}}$  when  $V_{CC}$  drops below VBACKUP. The registers are maintained from the V<sub>BACKUP</sub> source until V<sub>CC</sub> is returned to nominal levels. The Functional Diagram shows the main elements of the serial real-time clock.

#### **Power Control**

The power-control function is provided by a precise, temperature-compensated voltage reference and a comparator circuit that monitors the V<sub>CC</sub> level. The device is fully accessible and data can be written and read when V<sub>CC</sub> is greater than V<sub>PF</sub>. However, when V<sub>CC</sub> falls below VPF, the internal clock registers are blocked from any access. If VPF is less than VBACKUP, the device power is switched from V<sub>CC</sub> to V<sub>BACKUP</sub> when V<sub>CC</sub> drops below VPF. If VPF is greater than VBACKUP, the device power is switched from VCC to  $V_{BACKUP}$  when VCC drops below VBACKUP. The registers are maintained from the VBACKUP source until VCC is returned to nominal levels (Table 1). After VCC returns above VPF, read and write access is allowed after t<sub>RFC</sub> (Figure 2). On the first application of power to the device the time and date registers are reset to 01/01/00 01 00:00:00 (DD/MM/YY DOW HH:MM:SS).

#### **Oscillator Circuit**

The device uses an external 32.768kHz crystal. The oscillator circuit does not require any external resistors or capacitors to operate. Table 2 specifies several crystal parameters for the external crystal. The *Functional Diagram* shows a basic schematic of the oscillator circuit. The startup time is usually less than 1 second when using a crystal with the specified characteristics.

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

#### **Clock Accuracy**

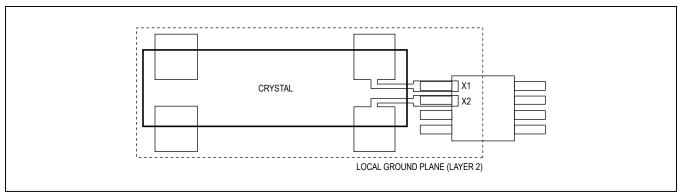

The accuracy of the clock is dependent upon the accuracy of the crystal and the accuracy of the match between the capacitive load of the oscillator circuit and the capacitive load for which the crystal was trimmed. Additional error is added by crystal frequency drift caused by temperature shifts. External circuit noise coupled into the oscillator circuit may result in the clock running fast. Figure 6 shows a typical PC board layout for isolating the crystal and oscillator from noise. Refer to <u>Application Note 58: Crystal</u> <u>Considerations with Dallas Real-Time Clocks</u> for detailed information

#### **RTC Address Map**

<u>Table 3</u> shows the address map for the device registers. During a multibyte access, when the address pointer reaches the end of the register space (10h), it wraps around to location 00h. On an I<sup>2</sup>C START or address pointer incrementing to location 00h, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to re-read the registers in case of an update of the main registers during a read.

#### **Time and Date Operation**

The time and date information is obtained by reading the appropriate register bytes. <u>Table 3</u> shows the RTC registers. The time and date are set or initialized by writing the appropriate register bytes. The contents of the time and date registers are in the BCD format. The device can be run in either 12-hour or 24-hour mode. Bit 6 of the

HOURS register is defined as the 12- or 24-hour modeselect bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the  $\overline{AM}$ /PM bit with logic high being PM. In the 24-hour mode, bit 5 is the 20-hour bit (20 to 23 hours). All hours values, including the alarms, must be re-entered whenever the  $12/\overline{24}$ -hour mode bit is changed.

The Century bit (bit 7 of the MONTH register) is toggled when the YEAR register overflows from 99 to 00. If the Century bit is logic 0, the year will be designated as a Leap Year and February will contain 29 days.

If the Century bit is logic 1, the year will not be designated as a Leap Year and February will contain 28 days.

The Day-Of-Week register increments at midnight. Values that correspond to the day of week are user-defined, but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday and so on). Illogical time and date entries result in undefined operation.

When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the internal registers on a START or when the address pointer rolls over to 00h. The countdown chain is reset whenever the seconds register is written. Write transfers occurs on the acknowledge pulse from the device. To avoid rollover issues, once the countdown chain is reset, the remaining time and date registers must be written within one second. If enabled, the 1Hz square-wave output transitions high 500ms after the seconds data transfer, provided the oscillator is already running.

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

## Table 3. Timekeeping Register Map

| ADDRESS | BIT 7   | BIT 6 | BIT 5                      | BIT 4       | BIT 3     | BIT 2 | BIT 1              | BIT 0                           | FUNCTION                        | RANGE                    |

|---------|---------|-------|----------------------------|-------------|-----------|-------|--------------------|---------------------------------|---------------------------------|--------------------------|

| 00h     | 0       |       | 10 Seconds                 |             | Seconds   |       |                    | Seconds                         | 00-59                           |                          |

| 01h     | 0       |       | 10 Minutes Minutes Minutes |             |           | 00-59 |                    |                                 |                                 |                          |

| 02h     | 0       | 12/24 | AM/PM<br>20 Hour           | 10<br>Hour  |           | ŀ     | lours              |                                 | Hours                           | 01-12<br>+AM/PM<br>00-23 |

| 03h     | 0       | 0     | 0                          | 0           | 0         |       | Day                |                                 | Day                             | 01-07                    |

| 04h     | 0       | 0     | 10 Da                      | ate         |           |       |                    |                                 | Date                            | 01-31                    |

| 05h     | Century | 0     | 0                          | 10<br>Month |           | Ν     | lonth              |                                 | Month                           | 01-12<br>+Century        |

| 06h     |         | 10 Y  | ear                        |             |           |       | Year               |                                 | Year                            | 00-99                    |

| 07h     | A1M1    |       | 10 Seconds                 |             |           | Se    | econds             |                                 | Alarm 1<br>Seconds              | 00-59                    |

| 08h     | A1M2    |       | 10 Minutes                 |             |           | М     | inutes             |                                 | Alarm 1<br>Minutes              | 00-59                    |

| 09h     | A1M3    | 12/24 | AM/PM<br>20 Hour           | 10<br>Hour  | Hours     |       |                    | Alarm 1<br>Hours                | 01-12<br>+AM/PM<br>00-23        |                          |

| 0Ah     | A1M4    | DY/DT | 10 Da                      | ate         |           | Da    | y, Date            |                                 | Alarm 1<br>Day, Alarm<br>1 Date | 01-07,<br>01-31          |

| 0Bh     | A2M2    |       | 10 Minutes Minutes         |             |           |       | Alarm 2<br>Minutes | 00-59                           |                                 |                          |

| 0Ch     | A2M3    | 12/24 | AM/PM<br>20 Hour           | 10<br>Hour  |           | ŀ     | lours              |                                 | Alarm 2<br>Hours                | 01-12<br>+AM/PM<br>00-23 |

| 0Dh     | A2M4    | DY/DT | 10 Da                      | ate         | Day, Date |       |                    | Alarm 2<br>Day, Alarm<br>2 Date | 01-07,<br>01-31                 |                          |

| 0Eh     | EOSC    | 0     | BBSQI                      | RS2         | RS1       | INTCN | A2IE               | A1IE                            | Control                         | -                        |

| 0Fh     | OSF     | 0     | 0                          | 0           | 0         | 0     | A2F                | A1F                             | Status                          | -                        |

| 10h     | TCS3    | TCS2  | TCS1                       | TCS0        | DS1       | DS0   | ROUT1              | ROUT0                           | Trickle<br>Charger              | -                        |

"0" - reads as Logic 0.

**Note:** Unless otherwise specified, the state of the registers are not defined when power is first applied or when  $V_{CC}$  and  $V_{BACKUP}$  fall below the  $V_{BACKUP(MIN)}$ .

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

#### Alarms

The device contains two time of day/date alarms. Alarm 1 can be set by writing to registers 07h to 0Ah. Alarm 2 can be set by writing to registers 0Bh to 0Dh. The alarms can be programmed (by the Alarm Enable and INTCN bits of the Control Register) to activate the SQW/INT output on an alarm match condition. Bit 7 of each of the time of day/ date alarm registers are mask bits (Table 4). When all the mask bits for each alarm are logic 0, an alarm only occurs when the values in the timekeeping registers 00h to 06h match the values stored in the time of day/date alarm registers. The alarms can also be programmed to repeat every second, minute, hour, day, or date. Table 4 shows the possible settings. Configurations not listed in the table result in illogical operation.

The DY/ $\overline{DT}$  bits (bit 6 of the alarm day/date registers) control whether the alarm value stored in bits 0 to 5 of that register reflects the day of the week or the date of the month. If DY/ $\overline{DT}$  is written to a logic 0, the alarm is the result of a match with date of the month. If DY/ $\overline{DT}$  is written to a logic 1, the alarm is the result of a match with day of the week.

The device checks for an alarm match once per second. When the RTC register values match alarm register settings, the corresponding Alarm Flag 'A1F' or 'A2F' bit is set to logic 1. If the corresponding Alarm Interrupt Enable 'A1IE' or 'A2IE' is also set to logic 1 and the INTCN bit is set to logic 1, the alarm condition activates the SQW/INT signal. If the BBSQI bit is set to 1, the INT output activates while the part is being powered by V<sub>BACKUP</sub>. The alarm output remains active until the alarm flag is cleared by the user.

#### **Table 4. Alarm Mask Bits**

|       | ALARM | 1 REGISTER | R MASK BITS | 6 (BIT 7) |                                                    |

|-------|-------|------------|-------------|-----------|----------------------------------------------------|

| DY/DT | A1M4  | A1M3       | A1M2        | A1M1      | ALARM RATE                                         |

| Х     | 1     | 1          | 1 1 A       |           | Alarm once per second                              |

| Х     | 1     | 1          | 1 0 /       |           | Alarm when seconds match                           |

| Х     | 1     | 1          | 0           | 0         | Alarm when minutes and seconds match               |

| Х     | 1     | 0          | 0           | 0         | Alarm when hours, minutes, and seconds match       |

| 0     | 0     | 0          | 0           | 0         | Alarm when date, hours, minutes, and seconds match |

| 1     | 0     | 0          | 0           | 0         | Alarm when day, hours, minutes, and seconds match  |

| DY/DT | ALARM2 R | EGISTER MASK | BITS (BIT 7) | ALARM RATE                                      |  |

|-------|----------|--------------|--------------|-------------------------------------------------|--|

|       | A2M4     | A2M3         | A2M2         |                                                 |  |

| Х     | 1        | 1            | 1            | Alarm once per minute (00 sec. of every minute) |  |

| Х     | 1        | 1            | 0            | Alarm when minutes match                        |  |

| Х     | 1        | 0            | 0            | Alarm when hours and minutes match              |  |

| 0     | 0        | 0            | 0            | Alarm when date, hours, and minutes match       |  |

| 1     | 0        | 0            | 0            | Alarm when day, hours, and minutes match        |  |

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

### **Control Register (0Eh)**

The control register controls the operation of the SQW/INT pin and provides oscillator status.

| Bit # | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name  | EOSC  | 0     | BBSQI | RS2   | RS1   | INTCN | A2IE  | A1IE  |

| POR   | 0     | 0     | 0     | 1     | 1     | 0     | 0     | 0     |

**Bit 7: Enable Oscillator** (EOSC). When the EOSC bit is 0, the oscillator is enabled. When this bit is a 1, the oscillator is disabled. This bit is cleared (0) when power is first applied.

**Bit 5: Battery-Backed Square-Wave Interrupt (BBSQI).** When set to logic 1, this bit enables the SQW/ $\overline{INT}$  output functionality while the part is powered by V<sub>BACKUP</sub>. When set to logic 0, this bit disables the SQW/ $\overline{INT}$  output while the part is powered by V<sub>BACKUP</sub>.

**Bits 4 and 3: Rate Select (RS2 and RS1).** These bits control the frequency of the SQW/INT output when the square-wave has been enabled (INTCN = 0). Table 5 lists the square-wave frequencies that can be selected with the RS bits.

**Bit 2: Interrupt Control (INTCN).** This bit controls the relationship between the two alarms and the interrupt output pin. When the INTCN bit is set to logic 1, a match between the timekeeping registers and the Alarm 1 or Alarm 2 registers activate the SQW/INT pin (provided that the alarm is enabled). When the INTCN bit is set to logic 0, a square wave is output on the SQW/INT pin. This bit is set to logic 0 when power is first applied.

**Bit 1: Alarm 2 Interrupt Enable (A2IE).** When set to a logic 1, this bit permits the Alarm 2 Flag (A2F) bit in the status register to assert SQW/INT (when INTCN = 1). When the A2IE bit is set to logic 0 or INTCN is set to logic 0, the A2F bit does not initiate an interrupt signal. The A2IE bit is disabled (logic 0) when power is first applied.

**Bit 0: Alarm 1 Interrupt Enable (A1IE).** When set to logic 1, this bit permits the Alarm 1 Flag (A1F) bit in the status register to assert SQW/INT (when INTCN = 1). When the A1IE bit is set to logic 0 or INTCN is set to logic 0, the A1F bit does not initiate an interrupt signal. The A1IE bit is disabled (logic 0) when power is first applied.

| INTCN | RS2 | RS1 | SQW/INT OUTPUT | A2IE | A1IE |

|-------|-----|-----|----------------|------|------|

| 0     | 0   | 0   | 1Hz            | Х    | X    |

| 0     | 0   | 1   | 4.096kHz       | Х    | Х    |

| 0     | 1   | 0   | 8.192kHz       | Х    | X    |

| 0     | 1   | 1   | 32.768kHz      | Х    | Х    |

| 1     | X   | X   | A1F            | 0    | 1    |

| 1     | X   | X   | A2F            | 1    | 0    |

| 1     | X   | X   | A2F + A1F      | 1    | 1    |

## Table 5. SQW/INT Output

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

### Status Register (0Fh)

The control register controls the operation of the SQW/INT pin and provides oscillator status.

| Bit # | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name  | OSF   | 0     | 0     | 0     | 0     | 0     | A2F   | A1F   |

| POR   | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

**Bit 7: Oscillator Stop Flag (OSF).** A logic 1 in this bit indicates that the oscillator has stopped or was stopped for some time period and can be used to judge the validity of the clock and calendar data. This bit is edge triggered, and is set to logic 1 when the internal circuitry senses the oscillator has transitioned from a normal run state to a stopped condition. The following are examples of conditions that may cause the OSF bit to be set:

The first time power is applied.

The voltage present on  $V_{CC}$  and  $V_{BAT}$  are insufficient to support oscillation.

The  $\overline{\text{EOSC}}$  bit is set to 1, disabling the oscillator.

External influences on the crystal (i.e., noise, leakage, etc.).

This bit remains at logic 1 until written to logic 0. This bit can only be written to logic 0. Attempting to write OSF to logic 1 leaves the value unchanged.

**Bit 1: Alarm 2 Flag (A2F).** A logic 1 in the Alarm 2 Flag bit indicates that the time matched the Alarm 2 registers. If the A2IE bit is a logic 1 and the INTCN bit is set to a logic 1, the SQW/INT pin is also asserted. A2F is cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write to logic 1 leaves the value unchanged.

**Bit 0: Alarm 1 Flag (A1F).** A logic 1 in the Alarm 1 Flag bit indicates that the time matched the Alarm 1 registers. If the A1IE bit is a logic 1 and the INTCN bit is set to a logic 1, the SQW/INT pin is also asserted. A1F is cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write to logic 1 leaves the value unchanged.

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

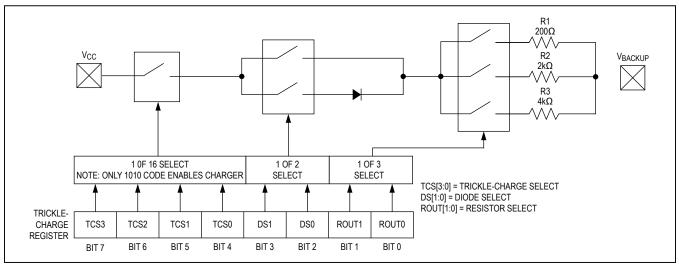

#### **Trickle Charger (10h)**

The simplified schematic in Figure 3 shows the basic components of the trickle charger. The trickle-charge select bits (TCS[3:0]) control the selection of the trickle charger. To prevent accidental enabling, only a pattern on 1010 enables the trickle charger. All other patterns disable the trickle charger. The trickle charger is disabled when power is first applied. The diode-select (DS[1:0]) bits select whether or not a diode is connected between V<sub>CC</sub> and V<sub>BACKUP</sub>. The ROUT[1:0] bits select the value of the resistor connected between V<sub>CC</sub> and V<sub>BACKUP</sub>. Table 6 shows the register settings.

Figure 3. Trickle Charger

### Table 6. Trickle Charger Register (10h)

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | FUNCTION                       |

|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------------|

| TCS3  | TCS2  | TCS1  | TCS0  | DS1   | DS0   | ROUT1 | ROUT0 | FUNCTION                       |

| Х     | Х     | Х     | Х     | 0     | 0     | Х     | Х     | Disabled                       |

| Х     | Х     | Х     | Х     | 1     | 1     | Х     | Х     | Disabled                       |

| Х     | Х     | Х     | Х     | Х     | Х     | 0     | 0     | Disabled                       |

| 1     | 0     | 1     | 0     | 0     | 1     | 0     | 1     | No diode, $200\Omega$ resistor |

| 1     | 0     | 1     | 0     | 1     | 0     | 0     | 1     | One diode, 200Ω resistor       |

| 1     | 0     | 1     | 0     | 0     | 1     | 1     | 0     | No diode, 2kΩ resistor         |

| 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | One diode, 2kΩ resistor        |

| 1     | 0     | 1     | 0     | 0     | 1     | 1     | 1     | No diode, 4kΩ resistor         |

| 1     | 0     | 1     | 0     | 1     | 0     | 1     | 1     | One diode, 4kΩ resistor        |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | Initial power-up values        |

#### Warning: The ROUT value of 200 $\Omega$ must not be selected whenever V<sub>CC</sub> is greater than 3.63V.

The user determines diode and resistor selection according to the maximum current desired for battery or super cap charging. The maximum charging current can be calculated as illustrated in the following example. Assume that a 3.3V system power supply is applied to  $V_{CC}$  and a super cap is connected to  $V_{BACKUP}$ . Also assume that the trickle charger has been enabled with a diode and resistor R2 between  $V_{CC}$  and  $V_{BACKUP}$ . The maximum current I<sub>MAX</sub> would therefore be calculated as follows:

$I_{MAX} = (3.3V - diode drop) / R2 \approx (3.3V - 0.7V) / 2k\Omega \approx 1.3mA$

As the super cap or battery charges, the voltage drop between  $V_{CC}$  and  $V_{BACKUP}$  decreases and therefore the charge current decreases.

## Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

### I<sup>2</sup>C Serial Port Operation

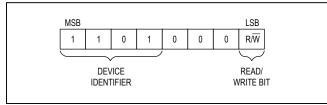

#### I<sup>2</sup>C Slave Address

The device's slave address byte is D0h. The first byte sent to the device includes the device identifier and the  $R/\overline{W}$  bit (Figure 4). The device address sent by the I<sup>2</sup>C master must match the address assigned to the device.

Figure 4. Slave Address Byte

#### I<sup>2</sup>C Definitions

The following terminology is commonly used to describe  $I^2C$  data transfers.

**Master Device:** The master device controls the slave devices on the bus. The master device generates SCL clock pulses and START and STOP conditions.

**Slave Devices:** Slave devices send and receive data at the master's request.

**Bus Idle or Not Busy:** Time between STOP and START conditions when both SDA and SCL are inactive and in their logic-high states. When the bus is idle it often initiates a low-power mode for slave devices.

**START Condition:** A START condition is generated by the master to initiate a new data transfer with a slave. Transitioning SDA from high to low while SCL remains high generates a START condition. See Figure 1 for applicable timing.

**STOP Condition:** A STOP condition is generated by the master to end a data transfer with a slave. Transitioning SDA from low to high while SCL remains high generates a STOP condition. See Figure 1 for applicable timing.

**Repeated START Condition**: The master can use a repeated START condition at the end of one data transfer to indicate that it immediately initiates a new data transfer following the current one. Repeated STARTs are commonly used during read operations to identify a specific memory address to begin a data transfer. A repeated START condition is issued identically to a

normal START condition. See Figure 1 for applicable timing.

**Bit Write:** Transitions of SDA must occur during the low state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL plus the setup and hold time requirements (see Figure 1). Data is shifted into the device during the rising edge of the SCL.

**Bit Read:** At the end a write operation, the master must release the SDA bus line for the proper amount of setup time (see Figure 1) before the next rising edge of SCL during a bit read. The device shifts out each bit of data on SDA at the falling edge of the previous SCL pulse and the data bit is valid at the rising edge of the current SCL pulse. Remember that the master generates all SCL clock pulses including when it is reading bits from the slave.

Acknowledge (ACK and NACK): An Acknowledge (ACK) or Not Acknowledge (NACK) is always the 9th bit transmitted during a byte transfer. The device receiving data (the master during a read or the slave during a write operation) performs an ACK by transmitting a zero during the 9th bit. A device performs a NACK by transmitting a one during the 9th bit. Timing for the ACK and NACK is identical to all other bit writes. An ACK is the acknowledgment that the device is properly receiving data. A NACK is used to terminate a read sequence or as an indication that the device is not receiving data.

**Byte Write:** A byte write consists of 8 bits of information transferred from the master to the slave (most significant bit first) plus a 1-bit acknowledgment from the slave to the master. The 8 bits transmitted by the master are done according to the bit write definition and the acknowledgment is read using the bit read definition.

**Byte Read:** A byte read is an 8-bit information transfer from the slave to the master plus a 1-bit ACK or NACK from the master to the slave. The 8 bits of information that are transferred (most significant bit first) from the slave to the master are read by the master using the bit read definition, and the master transmits an ACK using the bit write definition to receive additional data bytes. The master must NACK the last byte read to terminate communication so the slave returns control of SDA to the master.

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

**Slave Address Byte:** Each slave on the I<sup>2</sup>C bus responds to a slave address byte sent immediately following a START condition. The slave address byte contains the slave address in the most significant 7 bits and the R/ $\overline{W}$  bit in the least significant bit. The whatever's slave address is D0h and cannot be modified by the user. When the R/ $\overline{W}$  bit is 0 (such as in D0h), the master is indicating it writes data to the slave. If R/ $\overline{W}$  = 1, (D1h in this case), the master is indicating it wants to read from the slave. If an incorrect slave address is written, the device assumes the master is communicating with another I<sup>2</sup>C device and ignores the communication until the next START condition is sent.

**Memory Address:** During an  $I^2C$  write operation, the master must transmit a memory address to identify the memory location where the slave is to store the data. The memory address is always the second byte transmitted during a write operation following the slave address byte.

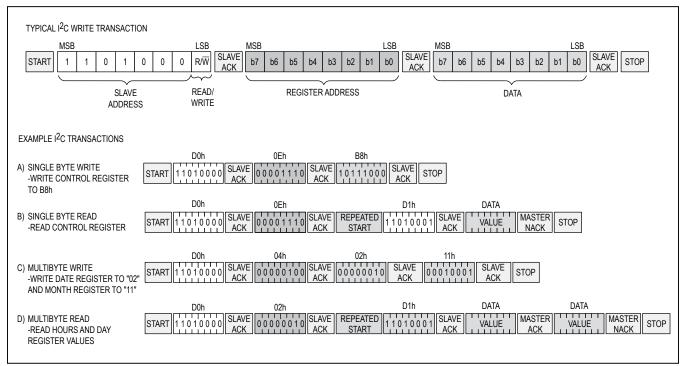

#### I<sup>2</sup>C Communication

Writing a Single Byte to a Slave: The master must generate a START condition, write the slave address

byte  $(R/\overline{W} = 0)$ , write the memory address, write the byte of data, and generate a STOP condition. Remember the master must read the slave's acknowledgment during all byte write operations.

Writing Multiple Bytes to a Slave: To write multiple bytes to a slave, the master generates a START condition, writes the slave address byte (R/W = 0), writes the starting memory address, writes multiple data bytes, and generates a STOP condition.

**Reading a Single Byte from a Slave:** Unlike the write operation that uses the specified memory address byte to define where the data is to be written, the read operation occurs at the present value of the memory address counter. To read a single byte from the slave, the master generates a START condition, writes the slave address byte with R/W = 1, reads the data byte with a NACK to indicate the end of the transfer, and generates a STOP condition. However, since requiring the master to keep track of the memory address counter is impractical, the following method should be used to perform reads from a specified memory location.

Figure 5. I<sup>2</sup>C Transactions

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

**Manipulating the Address Counter for Reads:** A dummy write cycle can be used to force the address counter to a particular value. To do this the master generates a START condition, writes the slave address byte ( $R/\overline{W} = 0$ ), writes the memory address where it desires to read, generates a repeated START condition, writes the slave address byte ( $R/\overline{W} = 1$ ), reads data with ACK or NACK as applicable, and generates a STOP condition. See Figure 5 for a read example using the repeated START condition to specify the starting memory location.

**Reading Multiple Bytes From a Slave:** The read operation can be used to read multiple bytes with a single transfer. When reading bytes from the slave, the master simply ACKs the data byte if it desires to read another byte before terminating the transaction. After the master reads the last byte it must NACK to indicate the end of the transfer and then it generates a STOP condition.

### **Applications Information**

#### **Power-Supply Decoupling**

To achieve the best results when using the device, decouple the V<sub>CC</sub> power supply with a  $0.01\mu$ F and/or  $0.1\mu$ F capacitor. Use a high-quality, ceramic, surface-mount capacitor if possible. Surface-mount components minimize lead inductance, which improves performance, and ceramic capacitors tend to have adequate high-frequency response for decoupling applications.

### Using an Open-Drain Output

The SQW/INT output is open-drain and therefore requires an external pullup resistor to realize a logic-high output level.

#### **SDA and SCL Pullup Resistors**

SDA is an open-drain output and requires an external pullup resistor to realize a logic-high output level.

Because the device does not use clock cycle stretching, a master using either an open-drain output with a pullup resistor or CMOS output driver (push-pull) could be used for SCL.

#### **Battery Charge Protection**

The device contains Maxim's redundant battery-charge protection circuit to prevent any charging of an external battery. The DS1339B is recognized by the Underwriters Laboratories (UL) under file E141114.

#### Handling, PCB Layout, and Assembly

Avoid running signal traces under the package, unless a ground plane is placed between the package and the signal line. Do not use external components to compensate for improper crystal selection.

Moisture-sensitive packages are shipped from the factory dry-packed. Handling instructions listed on the package label must be followed to prevent damage during reflow. Refer to the IPC/JEDEC J-STD-020 standard for moisture-sensitive device (MSD) classifications.

Figure 6. Typical PCB Layout for Crystal

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

## **Ordering Information**

| PART      | TEMP RANGE     | PIN-PACKAGE |

|-----------|----------------|-------------|

| DS1339BU+ | -40°C to +85°C | 8 µSOP      |

|           |                |             |

+Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

\*Future product—contact factory for availability.

### **Chip Information**

PROCESS: CMOS SUBSTRATE CONNECTED TO GROUND

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE        | LAND        |

|---------|---------|----------------|-------------|

| TYPE    | CODE    | NO.            | PATTERN NO. |

| 8 µSOP  | U8+1    | <u>21-0036</u> | 90-0092     |

# Low-Current, I<sup>2</sup>C, Serial Real-Time Clock for High-ESR Crystals

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                           | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------|------------------|

| 0                  | 5/13             | Initial release                       | —                |

| 1                  | 4/15             | Revised Benefits and Features section | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

«JONHON» (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«FORSTAR» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный) Факс: 8 (812) 320-03-32 Электронная почта: ocean@oceanchips.ru Web: http://oceanchips.ru/ Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А