# AT30TSE002A

# Atmel

## Integrated Temperature Sensor with SEEPROM

## DATASHEET

#### **Features**

- Integrated Temperature Sensor (TS) + 2Kb Serial EEPROM

- Standard voltage operation

- Optimized for voltage range: 2.7V to 3.6V

- 100khz and 400khz compatibility

- 2-wire serial interface: I<sup>2</sup>C/SMBus™ compatible

- SMBus Timeout supported

- Schmitt Trigger, filtered inputs for noise suppression

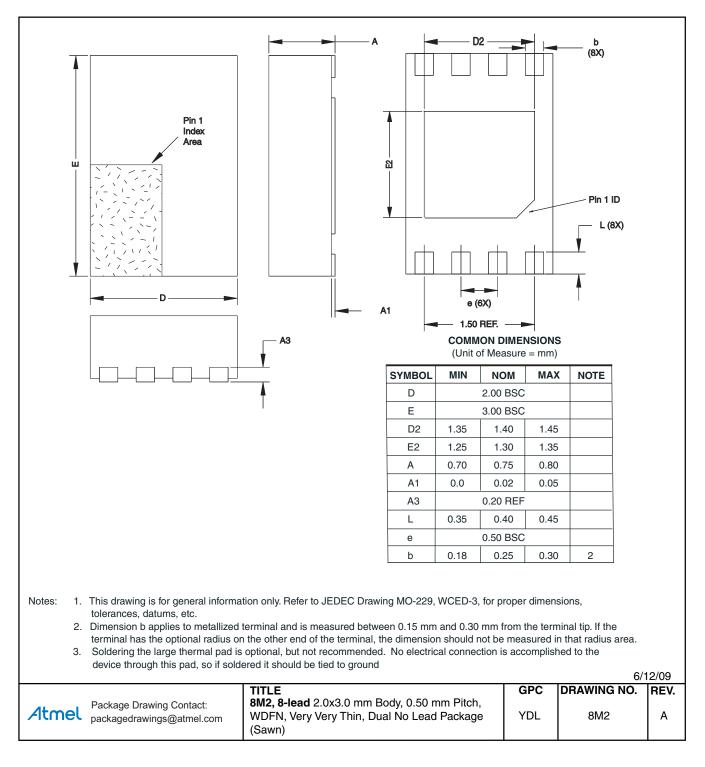

- Industry standard green (Pb/Halide-free/RoHS compliant) package options

8-lead Very Very Thin DFN (2 x 3 x 0.8mm)

#### **Serial EEPROM Features**

- Permanent and reversible software write protection for the first-half of the array

Software procedure to verify write protect status

- Internally organized as one block of 256-bytes (256 x 8)

- Supports byte and Page Write operation

- Write 1, 2, 3, and up to 16 bytes at a time

- Self-timed write cycle (5ms max)

- High-reliability

- Endurance: 1 million write cycles

- Data retention: 100 years

- Low operating current

- EEPROM write ~1.5mA (typical)

- EEPROM read ~ 0.2mA (typical)

#### **Temperature Sensor Features**

- 11-bit ADC temp-to-digital converter with 0.125°C resolution

- Programmable hysteresis threshold: off, 0°C, 1.5°C, 3°C, and 6 °C

- Accuracy

- ±0.5°C (typ.) for +75°C to +95°C

- ±1.0°C (typ.) for +20°C to +110°C

- ±2.0°C (typ.) for -20°C to +125°C

- Low operating current

- Temperature sensor active ~ 0.2mA (typical)

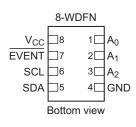

#### Figure 1. Pin Configuration

| Pin                                              | Function           |

|--------------------------------------------------|--------------------|

| A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> | Address Inputs     |

| SDA                                              | Serial Data        |

| SCL                                              | Serial Clock Input |

| Temperature Alert                                | EVENT              |

| GND                                              | Ground             |

| V <sub>CC</sub>                                  | Power Supply       |

## 1. Description

Atmel<sup>®</sup> AT30TSE002A is a combination Serial EEPROM and temperature sensor device containing 2048-bits of Serially Electrically Erasable and Programmable Read-Only Memory (EEPROM) organized as 256-bytes of eight bits each and could be used to store memory module and vendor information. The EEPROM operation is tailored specifically for DRAM Memory Modules Serial Presence Detect (SPD). The first 128-bytes of the memory incorporate a permanent and a Reversible Software Write Protection (WP) feature. Once the Permanent Software WP is enabled, by sending a special command, it cannot be reversed; however, once the reversible software WP is enabled, it can be reversed by sending a special command.

The integrated temperature sensor converts temperatures from -20°C to +125°C to a digital word and provides an accuracy of  $\pm 1.0$ °C (max.) for the temperature range +75°C to +95°C. The temperature sensor continuously monitors temperature and updates data in the temperature register at least eight times per second. Temperature data is latched internally by the device and may be read by software via a microcontroller at anytime. The AT30TSE002A has flexible user programmable internal registers to configure the temperature sensor performance and response to over temperature conditions. The device contains programmable high, low, and critical temperature limits. The device  $\overline{EVENT}$  pin is configured as active low and can be configured to operate as an interrupt or as a comparator output. Manufacturer and Device ID Registers provide the ability to confirm the identity of the device. The AT30TSE002A supports the industry standard 2-wire l<sup>2</sup>C/ SMBus serial interface to include time out feature to help prevent system lock-ups.

## 2. Absolute Maximum Ratings\*

| Temperature under Bias40°C to +125°C                                          |

|-------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                             |

| Supply voltage<br>with respect to ground0.5V to +4.3V                         |

| A <sub>0</sub> Pin0.5V to +12.0V                                              |

| All other input voltages with respect to ground0.5V to $V_{CC}$ + 0.5V        |

| $\overline{\text{EVENT}}$ Pin $\ldots$ -0.5V to $\text{V}_{\text{CC}}$ + 0.3V |

| All other output voltages with respect to ground0.5V to $V_{CC}$ + 0.5V       |

\*Notice: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these ratings or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Voltage extremes referenced in the "Absolute Maximum Ratings" are intended to accommodate short duration undershoot/overshoot conditions and does not imply or guarantee functional device operation at these levels for any extended period of time.

Pull-up voltages applied to the EVENT pin that exceed the "Absolute Maximum Ratings" may forward bias the ESD protection circuitry. Doing so may result in improper device function and may corrupt temperature measurements.

# Atmel

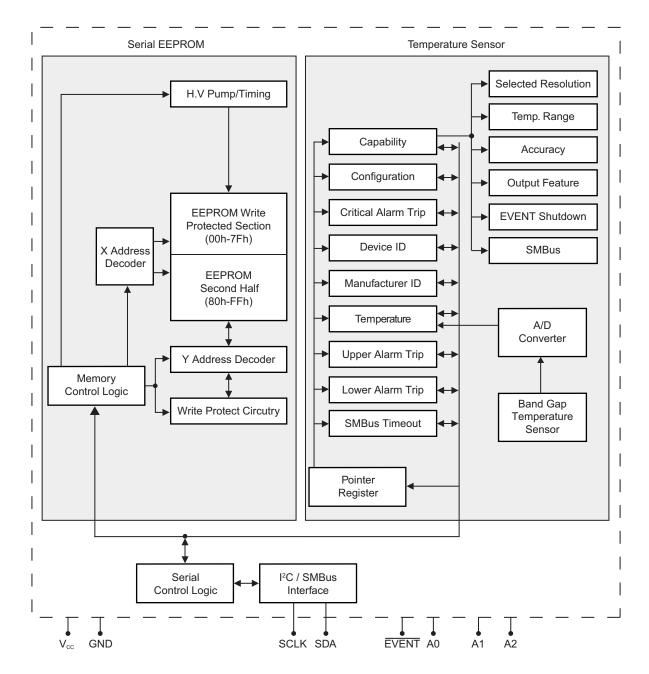

## 3. Block Diagram

## 4. Pin Description

AT30TSE002A requires no external components for operation except for pull-up resistors on SCL, SDA, and  $\overline{\text{EVENT}}$  pins. In order to provide effective noise protection and filtering, it is recommended that a decoupling capacitor of 0.1µF be used and is located as close as possible to the device between V<sub>CC</sub> and ground pins.

Serial Clock (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.

**Serial Data (SDA):** The SDA pin is bidirectional for serial data transfer. This pin is open drain driven and may be wire-ORed with any number of other open-drain or open collector devices.

**Device Addresses (A<sub>2</sub>, A<sub>1</sub>, A<sub>0</sub>):** The A<sub>2</sub>, A<sub>1</sub>, and A<sub>0</sub> pins are device address inputs that are hardwired (directly to GND or to V<sub>CC</sub>) for compatibility with 2-wire devices. When the pins are hardwired, as many as eight devices may be addressed on a single bus system. A device is selected when a corresponding hardware and software match is true. If these pins are left floating, the A<sub>2</sub>, A<sub>1</sub>, and A<sub>0</sub> pins will be internally pulled to GND; however, Atmel recommends always connecting the address pins to a known state by direct connection to ground or V<sub>CC</sub>, but if using a pull-up resistor, Atmel recommends using  $10k\Omega$  or less.

The  $A_0$  pin is also overvoltage tolerant, allowing up to 10V for software write protection functionality. (See Section 6. through Section 9.)

**Temperature Alert Output (EVENT):** The EVENT pin outputs a signal when the temperature goes beyond the user-programmed temperature limits and be configured in one of three modes; either Interrupt, Comparator, or Critical Alarm modes.

The EVENT pin is an open-drain output and requires a pull-up resistor for proper operation (see Section 10.).

#### 4.1 Pin Capacitance<sup>(1)</sup>

SymbolTest ConditionMaxUnitsConditions $C_{I/O}$ Input/output Capacitance (SDA), EVENT8pF $V_{I/O} = 0V$  $C_{IN}$ Input Capacitance (A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>, and SCL)6pF $V_{IN} = 0V$

Applicable over recommended operating range from  $T_A = 25^{\circ}C$ , f = 100 kHz,  $V_{CC} = +3.0V$ .

Note: 1. This parameter is ensured by characterization only.

## 4.2 DC Characteristics

Applicable over recommended operating range:  $T_A = -20^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{cc} = +2.7v$  to +3.6V (unless otherwise noted).

| Symbol            | Parameter                                          | Test Condition                                                                                                                          | Min                  | Тур | Max                   | Units |  |

|-------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|-----------------------|-------|--|

| V <sub>CC1</sub>  | Supply Voltage                                     |                                                                                                                                         | 2.7                  |     | 3.6                   | V     |  |

| Supply C          | urrent                                             |                                                                                                                                         |                      |     |                       |       |  |

|                   | EEPROM Read $V_{CC} = 3.6V^{(2)}$                  | 100kHz                                                                                                                                  |                      | 0.4 | 1.0                   |       |  |

|                   | EEPROM Write V <sub>CC</sub> = 3.6V <sup>(2)</sup> | 100kHz                                                                                                                                  |                      | 1.5 | 3.0                   |       |  |

| I <sub>CC</sub>   | Temp. Sensor V <sub>CC</sub> = 3.6V                | EEPROM Inactive                                                                                                                         |                      | 0.2 | 0.5                   | mA    |  |

|                   | Timeout Active $V_{CC}$ = 3.6V                     | EEPROM Inactive,<br>Temp. Sensor Shutdown                                                                                               |                      | 0.2 |                       |       |  |

| I <sub>SB</sub>   | Standby Current $V_{CC} = 3.6V^{(3)}$              | $V_{in} = V_{HV} = \text{ or } V_{SS}$                                                                                                  |                      | 1.6 | 4.0                   | μA    |  |

| I <sub>LI</sub>   | Input Leakage Current                              | $V_{in} = V_{HV} = \text{ or } V_{SS}$                                                                                                  |                      | 0.1 | 2.0                   | μA    |  |

| I <sub>LO</sub>   | Output Leakage Current                             | $V_{in} = V_{HV} = or V_{SS}$                                                                                                           |                      | 0.1 | 2.0                   | μA    |  |

| V <sub>IL</sub>   | Input Low Level <sup>(1)</sup>                     |                                                                                                                                         | -0.6                 |     | V <sub>HV</sub> x 0.3 | V     |  |

| V <sub>IH</sub>   | Input High Level <sup>(1)</sup>                    |                                                                                                                                         | V <sub>HV</sub> x0.7 |     | V <sub>HV</sub> + 0.5 | V     |  |

| V <sub>OL</sub>   | Output Low level $V_{CC}$ = 3.0V                   | I <sub>OL</sub> = 2.1mA                                                                                                                 |                      |     | 0.4                   | V     |  |

| V <sub>HV</sub>   | High Voltage Input A0                              | $\label{eq:Pin} \begin{array}{l} \mbox{Pin} = \mbox{A}_0; \\ \mbox{V}_{\mbox{HV}} - \mbox{V}_{\mbox{CC}} \geq 4.8 \mbox{V} \end{array}$ | 7.0                  |     | 10.0                  | V     |  |

| V <sub>HYST</sub> | Input Hysteresis (SDA, SCL)                        |                                                                                                                                         | $0.05 \times V_{CC}$ |     |                       | V     |  |

Notes: 1.  $V_{IL}$  min and  $V_{IH}$  max are reference only and are not tested.

2. Sensor in shutdown mode.

3. EEPROM inactive; sensor in shutdown mode.

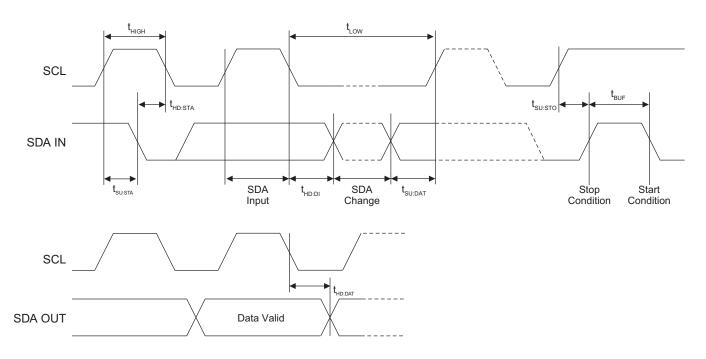

## 4.3 AC Characteristics

Applicable over recommended operating range:  $T_A = -20^{\circ}C$  to +125°C,  $V_{CC} = +2.7V$  to +3.6V, CL = 1 TTL Gate and 100µF (unless otherwise noted).

| 7.                                 |                                                                              |                   |      |                   |                 |       |

|------------------------------------|------------------------------------------------------------------------------|-------------------|------|-------------------|-----------------|-------|

| Symbol                             | Parameter                                                                    | Min               | Max  | Min               | Max             | Units |

| F <sub>SCL</sub>                   | Clock Frequency, SCL                                                         | 10 <sup>(2)</sup> | 100  | 10 <sup>(2)</sup> | 400             | kHz   |

| T <sub>LOW</sub>                   | Clock Pulse Width Low                                                        | 4.7               |      | 1.2               |                 | us    |

| T <sub>HIGH</sub>                  | Clock Pulse Width High                                                       | 4.0               |      | 0.6               |                 | us    |

| T <sub>R</sub>                     | Inputs Rise Time <sup>(1)</sup>                                              |                   | 1.0  |                   | 0.3             | us    |

| T <sub>F</sub>                     | Inputs Fall Time <sup>(1)</sup>                                              |                   | 300  |                   | 300             | ns    |

| T <sub>SU.DAT</sub>                | Data In Set-up Time                                                          | 200               |      | 100               |                 | ns    |

| T <sub>HD.DI</sub>                 | Data In Hold Time                                                            | 0.0               |      | 0.0               |                 | us    |

| T <sub>HD.DAT</sub>                | Data Out Hold Time                                                           | 200               | 3450 | 200               | 900             | ns    |

| T <sub>BUF</sub>                   | Time the bus must be free before a new transmission can start <sup>(1)</sup> | 4.7               |      | 1.2               |                 | us    |

| T <sub>SU.STA</sub>                | Start Set-up Time                                                            | 4.7               |      | 0.6               |                 | us    |

| T <sub>HD.STA</sub>                | Start Hold Time                                                              | 4.0               |      | 0.6               |                 | us    |

| T <sub>SU.STO</sub>                | Stop Set-up Time                                                             | 4.7               |      | 0.6               |                 | us    |

| TI                                 | Noise Suppression Time <sup>(1)</sup>                                        |                   | 100  |                   | 50              | ns    |

| T <sub>OUT</sub>                   | SMBus Timeout Time                                                           | 25                | 35   | 25                | 35              | ms    |

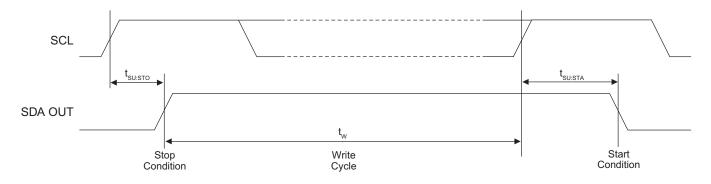

| T <sub>WR</sub>                    | Write Cycle Time                                                             |                   | 5.0  |                   | 5.0             | ms    |

| EEPROM<br>Endurance <sup>(1)</sup> | 25°C, Page Mode                                                              | 1,000,000         |      |                   | Write<br>Cycles |       |

Notes: 1. This parameter is ensured by characterization only.

2. The minimum frequency is specified at 10kHz to avoid activating the timeout feature.

## 4.4 Temperature Sensor Characteristics

Applicable over recommended operating range:  $T_A$  = -20°C to +125°C,  $V_{cc}$  = 2.7V to 3.6V (unless otherwise noted).

| Symbol            | Parameter          | Test Condition      | Min | Тур    | Max     | Units |

|-------------------|--------------------|---------------------|-----|--------|---------|-------|

|                   |                    | +75°C < Ta < +95°C  |     | ±0.500 | +1.000  |       |

| T <sub>ACC</sub>  | TS Accuracy        | +20°C < Ta < +110°C |     | ±1.000 | +2.000  | °C    |

|                   |                    | -20°C < Ta < +125°C |     | ±2.000 | +3.000  |       |

| T <sub>CONV</sub> | TS Conversion Time |                     |     | 75.000 | 125.000 | ms    |

| T <sub>RES</sub>  | TS Resolution      |                     |     | 0.125  |         | °C    |

## 5. Memory Organization

AT30TSE002A, 2K Serial EEPROM: The 2K memory is internally organized with 16 pages of 16-bytes each. Random word addressing requires an 8-bit data word address.

## 6. Device Operation

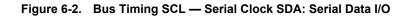

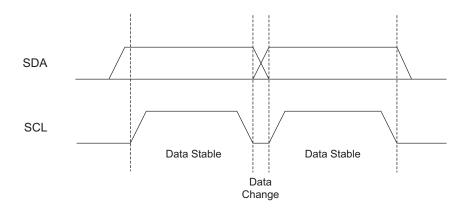

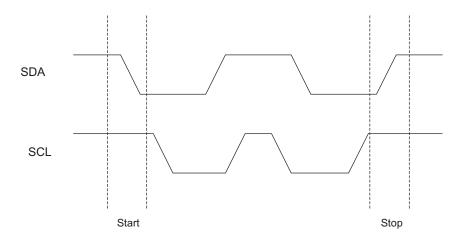

**Clock and Data Transitions:** The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods. (See Figure 6-4) Data changes during SCL high periods will indicate a Start or Stop condition as defined below.

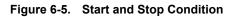

**Start Condition:** A high-to-low transition of SDA with SCL high is a Start condition which must precede any other command (see Figure 6-5).

**Stop Condition:** A low-to-high transition of SDA with SCL high is a Stop condition. After a Read sequence, the Stop command will place the device in a standby power mode (see Figure 6-5).

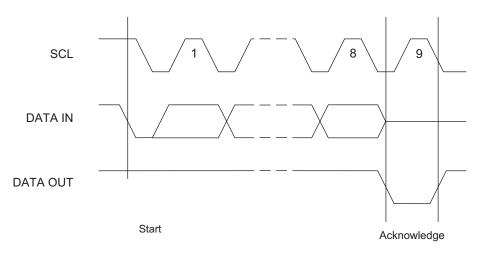

**Acknowledge:** All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The device sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle.

**Standby Mode:** The AT30TSE002A features a low-power standby mode which is enabled:

- a. Upon power-up.

- b. After the receipt of the Stop bit and the completion of any internal operations. The temperature sensor must be disabled by the user for low-power standby mode.

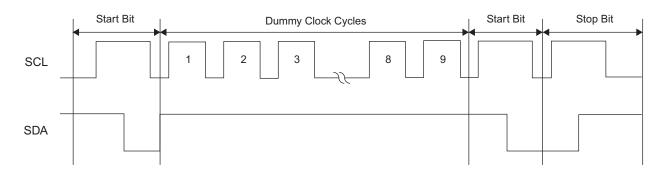

**2-wire Software Reset:** After an interruption in protocol, power loss or system reset, any 2-wire part can be reset by following these steps:

- 1. Create a Start bit condition.

- 2. Clock nine cycles.

- 3. Create another Start bit followed by Stop bit condition as shown below.

The device is ready for next communication after the above steps have been completed.

#### Figure 6-1. 2-wire Software Reset

## Atmel

#### Figure 6-3. Write Cycle Timing SCL — Serial Clock SDA: Serial Data I/O

Figure 6-4. Data Validity

Figure 6-6. Output Acknowledge

## 7. Device Addressing

AT30TSE002A device requires an 8-bit device address word following a Start condition to enable the chip to access either the Temperature Sensor or EEPROM functions (See Table 7-1).

|                         | Control / Device Address Word |    |    |    |                     |    |    |     |  |

|-------------------------|-------------------------------|----|----|----|---------------------|----|----|-----|--|

|                         | Device ID                     |    |    |    | Device Address Bits |    |    | R/W |  |

| Device                  | B7                            | B6 | B5 | B4 | A2                  | A1 | A0 | B0  |  |

| EEPROM                  | 1                             | 0  | 1  | 0  |                     |    |    |     |  |

| Temperature Sensor      | 0                             | 0  | 1  | 1  | X                   | Х  | Х  | Х   |  |

| EEPROM Write Protection | 0                             | 1  | 1  | 0  |                     |    |    |     |  |

#### Table 7-1. Control/Device Address Word

Note: 1. X = User Selectable

The EEPROM device address word consists of a mandatory one-zero sequence for the first four most significant bits ('1010') for normal Read and Write operations, a '0110' for writing to the EEPROM Write Protect Register, and '0011' for Temperature Sensor operations. The next three bits are the A2, A1, and A0 device address bits for the AT30TSE002A device. These three bits must match their corresponding hard-wired input pins. The eighth bit of the device address is the Read/Write operation select bit. A Read operation is initiated if this bit is high and an EEPROM Write operation is selected if this bit is low. Upon a compare of the device address, the device will output a zero, called an Acknowledge (ACK). If a compare is not made, the chip will not ACK and will return to a standby state. The EEPROM will not ACK if the Write Protect Register has been programmed and the control code is '0110'.

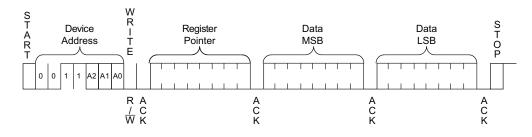

## 8. **EEPROM Write Operations**

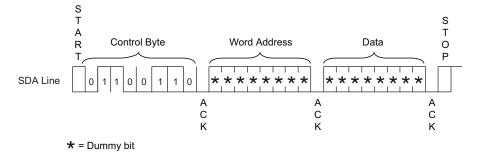

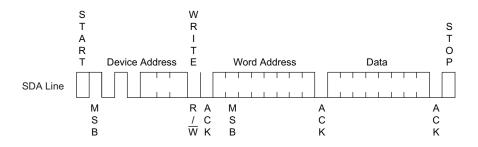

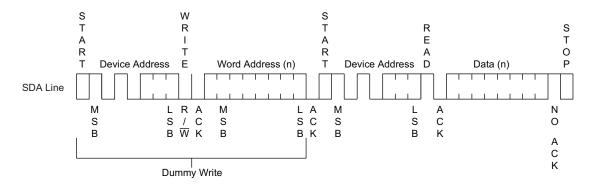

**Byte Write**: A Write operation requires an 8-bit data word address following the device address word and ACK. Upon receipt of this address, the EEPROM will again respond with an ACK and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output an ACK and the addressing device, such as a microcontroller, must terminate the Write sequence with a Stop condition. At this time the EEPROM enters an internally timed write cycle, t<sub>WR</sub>, to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 13-2 and Figure 13-3).

The device will acknowledge a Write command, but not write the data, if the Software Write Protection has been enabled. The write cycle time must be observed even when the Write Protection is enabled.

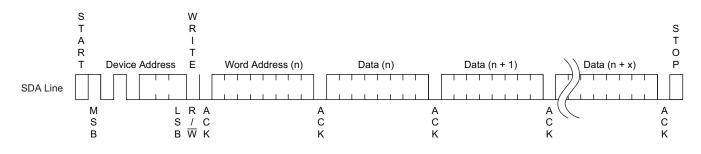

**Page Write:** The 2K EEPROM device is capable of 16-byte Page Write. A Page Write is initiated the same as a Byte Write, but the microcontroller does not send a Stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to fifteen more data words. The EEPROM will respond with a zero after each data word received. The microcontroller must terminate the Page Write Sequence with a Stop condition (see Figure 13-3). The data word address lower four bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than sixteen data words are transmitted to the EEPROM, the data word address will roll-over and previous data will be overwritten. The address roll-over during Write is from the last byte of the current page to the first byte of the same page. The device will acknowledge a Write command, but not write the data, if the Software Write Protection has been enabled. The write cycle time must be observed even when the Write Protection is enabled.

**Acknowledge (ACK) Polling:** Once the internally-timed write cycle has started and the EEPROM inputs are disabled, ACK polling can be initiated. This involves sending a Start condition followed by the device address word. The Read/Write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a zero allowing the Read or Write sequence to continue.

# Atmel

## 9. EEPROM Write Protection

The device supports Permanent and Reversible Software Write Protection and once enabled, Write protects the first-half of the array (00H – 7FH).

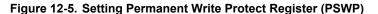

**Permanent Software Write Protection:** The Software Write Protection is enabled by sending a command similar to a normal Write command; to the device which programs the Permanent Write Protect Register. The Write Protect Register is programmed by sending a Write command with the device address of '0110' with the address and data bit being don't cares (see Figure 12-5 and Table 12-1). Once the Software Write Protection has been enabled, the device will no longer acknowledge the '0110' control byte. The Software Write Protection cannot be reversed even if the device is powered down. The write cycle time must be observed.

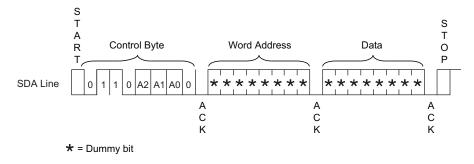

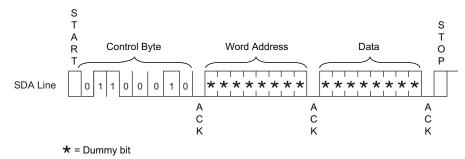

**Reversible Software Write Protection:** The Reversible Software Write Protection is enabled by sending a command, similar to a normal Write command; to the device which programs the Reversible Write Protect Register. The Write Protect Register is programmed by sending a Write command '01100010' with pins  $A_2$  and  $A_1$  tied to ground or no connect and pin  $A_0$  connected to  $V_{HV}$  (see Figure 12-6 and Table 12-1). The Reversible Write Protection can be reversed by sending a command '01100110' with pin  $A_2$  tied to ground or no connect, pin  $A_1$  tied to  $V_{CC}$ , and pin  $A_0$  tied to  $V_{HV}$  (see Figure 12-6 and Table 12-1).

## 10. Temperature Sensor Functional Description

AT30TSE002A consists of a Delta-Sigma Analog to Digital Converter (ADC) with a band gap type temperature sensor that monitors and updates its own temperature reading at least eight times per second converting the readings into digital data bits and latching them into a temperature register that can be read via 2-wire I<sup>2</sup>C/SMBus serial interface. The device communicates over a 2-wire I<sup>2</sup>C/SMBus interface with the bus master or controller consisting of a serial clock (SCL) and serial bidirectional data bus (SDA) with clock frequencies up to 400Khz. The bus master or controller generates the SCL signal and is used by the AT30TSE002A to receive and send serial data on the SDA line with the most significant bit transferred first. A pull-up resistor is required on the SDA pin since it has an open drain configuration.

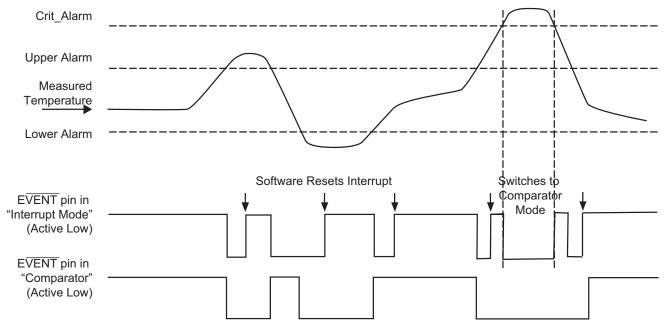

## 10.1 EVENT Output

The EVENT pin has three operating modes depending on configuration settings. They are:

- Interrupt mode

- Comparator mode

- Critical Alarm (Crit\_Alarm) mode

In the Interrupt mode, once a temperature reaches a boundary limit, the AT30TSE002A asserts the EVENT pin. The EVENT pin will remain asserted until software clears the interrupt by writing a Logic 1 to the EVTCLR bit five in the Configuration Register. When the temperature drops below specified limits, the device returns back to either interrupt or comparator mode as programmed in the Configuration Register's EVTMOD bit zero.

In the comparator mode, the EVENT pin remains asserted until the error condition that caused the pin to be asserted no longer exists and the EVENT pin will clear itself. In the Crit\_Alarm mode, when the measured temperature exceeds Crit\_Alarm trip limit, the EVENT pin will remain asserted until the temperature drops below Crit\_Alarm limit minus hysteresis (See Figure 11-1). All event thresholds use hysteresis as programmed in the Configuration Register.

#### 10.2 Alarm Window

The alarm window consists of the Upper Alarm Trip Register and Lower Alarm Trip Register. The Upper Alarm Trip Register holds the upper temperature trip point and the Lower Alarm Trip Register holds the lower temperature trip point. After the EVENT pin control is enabled, the EVENT output will be triggered upon entering and exiting from this window.

## 10.3 Temperature Sensor Power-On Default

The AT30TSE002A has an internal Power-On Reset (POR) circuit. When the supply voltage drops below the POR threshold, the device will reset to the following power-on default conditions:

- Sensor starts monitoring temperature continuously.

- Address Pointer Register = 00h.

- Upper/Lower Alarm Trip registers and Crit\_Alarm registers are set to 0°C.

- EVENT Register cleared and pulled high by external pull up resistor.

- Operational mode is comparator.

- EVENT hysteresis is 0°C.

- SMBus Register =00h.

#### 10.4 Device Initialization

The AT30TSE002A Temperature Sensor has programmable registers that, upon device power-on, are initialized to zero. Table 11-1 shows the Power-On register default values. The **EVENT** output is defaulted to deasserted state and comparator mode.

The Upper Alarm Trip, Lower Alarm Trip, Critical Alarm Trip, and Configuration Registers need to be programmed to desired values before temperature sensor can properly function.

#### 10.5 SMBus Timeout

The AT30TSE002A supports the SMBus timeout feature for temperature sensor operations if enabled via setting the SMBus Register (see Section 11.10). This feature helps prevent potential system bus hang-ups by resetting the serial interface if SCL stays low for a time specified by the  $t_{OUT}$  parameter. This requires a minimum SCL clock speed of 10kHz as specified in the SMBus specification to avoid any timeout issues.

## 11. Register Descriptions

This section describes all the temperature sensor registers that are used in AT30TSE002A. The AT30TSE002A has several registers that are user accessible and or programmable and used for latching temperature readings, storing high and low temperature limits, configuring the hysteresis threshold, and reporting status.

These registers include the Capability Register, Upper Alarm Trip Register, Lower Alarm Trip Register, Critical Alarm Trip Register, Temperature Register, Manufacturer Identification Register, Device Identification Register, and SMBus Register. The AT30TSE002A uses an 8-bit Pointer Register to access these registers and all other registers contain 16-bits.

Table 11-1 indicates the Write/Read access capability of each register. Reading from a Write-Only Register will result in reading zero data and writing to Read-Only Register will have no impact even though the Write sequence was acknowledged by the device.

|               | Register   |                             |         |                                         |  |  |  |  |

|---------------|------------|-----------------------------|---------|-----------------------------------------|--|--|--|--|

| Address (hex) | Read/Write | Register Name               | Section | Power-up Default<br>Register Data (hex) |  |  |  |  |

| N/A           | W          | Address Pointer             | 11.1    | 00h                                     |  |  |  |  |

| 00h           | R          | Capability                  | 11.2    | 00F7h                                   |  |  |  |  |

| 01h           | R/W        | Configuration               | 11.3    | 0000h                                   |  |  |  |  |

| 02h           | R/W        | Upper Alarm Trip            | 11.4    | 0000h                                   |  |  |  |  |

| 03h           | R/W        | Lower Alarm Trip            | 11.5    | 0000h                                   |  |  |  |  |

| 04h           | R/W        | Critical Alarm Trip         | 11.6    | 0000h                                   |  |  |  |  |

| 05h           | R          | Temperature Data            | 11.7    | N/A                                     |  |  |  |  |

| 06h           | R          | Manufacturer I.D.           | 11.8    | 001Fh                                   |  |  |  |  |

| 07h           | R          | Device I.D./Device Revision | 11.9    | 8201h                                   |  |  |  |  |

| 08h to 21h    | R/W        | Reserved <sup>(1)</sup>     | N/A     | 0000h                                   |  |  |  |  |

| 22h           | R/W        | SMBus Timeout               | 11.10   | 0000h                                   |  |  |  |  |

| 23h to FFh    | R/W        | Reserved <sup>(1)</sup>     | N/A     | 0000h                                   |  |  |  |  |

#### Table 11-1. Register Summary

Note: 1. Write operations to reserve registers should be avoided as it may cause undesirable results.

#### 11.1 Address Pointer Register

The AT30TSE002A uses a Pointer Register to select and access the 16-bit data registers shown in Table 11-1. The Pointer Register is an 8-bit Write-Only Register (See Table 11-2). The power-on default value is 00h which is the address location for the Capability Register.

#### Table 11-2. Address Pointer Register

| Bit           | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|---|--------------|---|---|---|---|---|---|

| Symbol        |   | Pointer Bits |   |   |   |   |   |   |

| R/W           | W | W            | W | W | W | W | W | W |

| Default Value | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |

## 11.2 Capability Register (16-bit Read Only, Address = 00h)

AT30TSE002A is capable of measuring temperature with  $\pm 1^{\circ}$ C over the active range and  $\pm 2^{\circ}$ C over the monitor range. This register is a 16-bit Read-Only Register used to specify the capabilities of the temperature sensor. The Capability Register functions are described in Table 11-3 and Table 11-4.

| Bit           | 15   | 14    | 13              | 12  | 11  | 10    | 9    | 8    |  |

|---------------|------|-------|-----------------|-----|-----|-------|------|------|--|

| Symbol        |      | RFU   |                 |     |     |       |      |      |  |

| Default Value | 0    | 0     | 0               | 0   | 0   | 0     | 0    | 0    |  |

| R/W Access    | R    | R     | R               | R   | R   | R     | R    | R    |  |

| Bit           | 7    | 6     | 5               | 4   | 3   | 2     | 1    | 0    |  |

| Symbol        | EVSD | TMOUT | V <sub>HV</sub> | TPF | RES | RANGE | SACC | ICAP |  |

| Default Value | 1    | 1     | 1               | 1   | 0   | 1     | 1    | 1    |  |

| R/W Access    | R    | R     | R               | R   | R   | R     | R    | R    |  |

Table 11-3. Capability Register Bit Distribution

#### Table 11-4. Capability Register Bit Description

| Bit  | Symbol          | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | RFU             | Reserved for Future Use. Must be zero.                                                                                                                                                                                                                                                                                                                                                                  |

| 7    | EVSD            | <ul> <li>Event Output Status during shutdown mode:</li> <li>1 = The EVENT pin output is deasserted (not driven) when entering shutdown mode and will resume status update immediately upon exiting shutdown.</li> <li>In addition, the EVTSTS bit in the Configuration Register will be cleared when entering shutdown mode and will resume status update immediately upon exiting shutdown.</li> </ul> |

| 6    | TMOUT           | Bus Timeout:<br>1 = Supported within the SMBus compatible range 25 to 35ms (power-up default).                                                                                                                                                                                                                                                                                                          |

| 5    | V <sub>HV</sub> | High Voltage Support for $A_0$ pin:<br>1 = $A_0$ pin supports a voltage up to 10V (power-up default).                                                                                                                                                                                                                                                                                                   |

| 4:3  | TPRES           | Temperature Resolution:<br>10 = Supports 0.125°C                                                                                                                                                                                                                                                                                                                                                        |

| 2    | RANGE           | 1 = Can read temperatures below 0°C and sets appropriate sign bit.                                                                                                                                                                                                                                                                                                                                      |

| 1    | SACC            | Supported Accuracy:<br>1 = Supports accuracy of ±1°C (max.) over the range (75°C to 95°C) and ±3°C (max.) over the range<br>(-20°C to 125°C).                                                                                                                                                                                                                                                           |

| 0    | ICAP            | Interrupt Capability:<br>1 = Has alarm and critical trip interrupt capability.                                                                                                                                                                                                                                                                                                                          |

## 11.3 Configuration Register (16-bit Read/Write, Address = 01h)

The AT30TSE002A contains a 16-bit Configuration Register allowing the user to set key operational features of the Temperature Sensor. The Configuration Register functions are described in Table 11-5, Table 11-6, and Figure 11-1.

| Bit           | 15      | 14      | 13     | 12      | 11     | 10      | 9      | 8      |

|---------------|---------|---------|--------|---------|--------|---------|--------|--------|

| Symbol        |         |         | RFU    | HYSTENB |        | SHTDWN  |        |        |

| Default Value | 0       | 0       | 0      | 0       | 0      | 0       | 0      | 0      |

| R/W Access    | R       | R       | R      | R       | R      | R/W     | R/W    | R/W    |

| Bit           | 7       | 6       | 5      | 4       | 3      | 2       | 1      | 0      |

| Symbol        | CRTALML | WINLOCK | EVTCLR | EVTSTS  | EVTOUT | CRITEVT | EVTPOL | EVTMOD |

| Default Value | 0       | 0       | 0      | 0       | 0      | 0       | 0      | 0      |

| R/W Access    | R/W     | R/W     | W      | R       | R/W    | R/W     | R/W    | R/W    |

Table 11-5. Configuration Register Bit Distribution

#### Table 11-6. Configuration Register Bit Description

| Bit   | Symbol  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | RFU     | Reserved for Future Use and must be zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10:9  | HYSTENB | Hysteresis Enable:         00 = 0°C Disable Hysteresis (default power-on condition)         01 = 1.5°C Enable Hysteresis         10 = 3.0°C Enable Hysteresis         11 = 6.0°C Enable Hysteresis         The purpose of these bits is to control the hysteresis applied to the alarm trip point boundaries. The above hysteresis applies to all limits when temperature drops below the user specified alarm trip points.         Note:       Hysteresis applies to decreasing temperature only. Once ambient temperature is above a given threshold, it must drop below the boundary limit minus hysteresis in order for a comparator EVENT to be cleared.         Example:       If these bits are set to '01' for 1.5°C and the Upper Alarm Trip limit is set to 85°C, as temperature rises above 85°C, bit 14 of temperature register will be set to a Logic 1. Bit 14 will remain set until the ambient temperature drops below the threshold (85°C) minus the hysteresis value or 83.5°C. |

|       |         | Note:         Hysteresis is also applied to the EVENT pin functionality. When either of the Crit_Alarm           Trip or Alarm Window lock bits is set, this bit cannot be altered until unlocked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8     | SHTDWN  | Shutdown Mode:         0 = Temperature sensor enabled for continuous conversion (power-on default).         1 = Temperature sensor disabled.         In shutdown mode, the temperature sensor is not active and will not generate interrupts or update temperature data. The EVENT pin is deasserted (not driven).         When either of the Crit_Alarm Trip or Alarm Window lock bits is set, this bit cannot be altered until unlocked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7     | CRTALML | <ul> <li>Crit_Alarm Trip Lock bit:</li> <li>Locks the Critical Alarm Trip Register from being updated.</li> <li>0 = Crit_Alarm Trip Register can be updated (power-on default).</li> <li>1 = Crit_Alarm Trip Register is locked and cannot be updated.</li> <li>Once set, it can be only be cleared to zero by internal POR which occurs when the device is powered off and then powered on.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6     | WINLOCK | <ul> <li>Alarm Window Lock bit:</li> <li>0 = Upper and Lower Alarm Trip Registers can be updated (Power-on default).</li> <li>1 = Upper and Lower Alarm Trip Registers are locked and cannot be updated.</li> <li>Once set, it can be only be cleared to zero by internal POR when device is powered off then powered on.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5     | EVTCLR  | <ul> <li>EVENT Clear: This bit is a write only bit and will read zero.</li> <li>This bit can clear the EVENT pin after it has been enabled and is self clearing.</li> <li>0 = has no effect (power-on default).</li> <li>1 = clears (releases) the active EVENT pin in interrupt mode. This bit is ignored when in comparator mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Table 11-6. | Configuration Register Bit Description | (Continued) |

|-------------|----------------------------------------|-------------|

|-------------|----------------------------------------|-------------|

| Bit | Symbol  | Description                                                                                                                 |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------|

|     |         | EVENT Pin Output Status:                                                                                                    |

|     |         | 0 = The $\overline{\text{EVENT}}$ Output is not asserted by the device (power-on default).                                  |

| 4   | EVTSTS  | 1 = The $\overline{\text{EVENT}}$ Output is asserted due to an alarm trip condition.                                        |

|     |         | Note: This bit will be cleared when entering shutdown mode and will resume status update immediately upon exiting shutdown. |

|     |         | EVENT Output Control:                                                                                                       |

|     |         | This bit, when set, prevents the EVENT pin from generating an interrupt.                                                    |

|     |         | 0 = The EVENT output is disabled and will not generate interrupts (power-on default).                                       |

| 3   | EVTOUT  | 1 = The $\overline{\text{EVENT}}$ output is enabled.                                                                        |

|     |         | When either of the Crit_Alarm Trip or Alarm Window lock bits is set, this bit cannot be altered until unlocked.             |

|     |         | Note: Please see note below for the recommended sequence for setting this bit.                                              |

|     |         | Critical Temperature Only:                                                                                                  |

|     |         | 0 = The EVENT output is asserted for the Upper, Lower, and Critical Alarms (power-on default).                              |

| 2   | CRITEVT | 1 = The EVENT output is asserted for only Critical Alarm when ambient temperature > Crit_Alarm trip boundary.               |

|     |         | When the Alarm Window lock bit is set, this bit cannot be altered until unlocked.                                           |

|     |         | Note: Please see note below for the recommended sequence for setting this bit.                                              |

|     |         | EVENT Polarity:                                                                                                             |

|     |         | 0 = Active Low (power-on default). A pull-up resistor is required on this pin to set inactive state.                        |

| 1   | EVTPOL  | 1 = Active High.                                                                                                            |

|     |         | When either of the Crit_Alarm Trip or Alarm Window lock bits is set, this bit cannot be altered until unlocked              |

|     |         | EVENT Mode:                                                                                                                 |

|     |         | 0 = The $\overline{\text{EVENT}}$ pin will operate in Comparator mode (power-on default).                                   |

| 0   | EVTMOD  | 1 = The $\overline{\text{EVENT}}$ pin will operate in Interrupt mode.                                                       |

|     |         | When either of the Crit_Alarm Trip or Alarm Window lock bits is set, this bit cannot be altered until unlocked.             |

Note: Any JEDEC TSE2002av compliant temperature sensor can be configured to report an over temperature limit condition to the Host system via its EVENT pin. These temperature sensors have the default value for all temperature alarm thresholds set at 0°C. Often, if a system designer determines to utilize only the Critical Alarm temperature threshold to trigger an Event, it is likely he/she would only setup the Critical Alarm temperature threshold to a proper value while leaving the Upper Alarm temperature threshold unchanged at the default (0°C). Due to some ambiguity in the TSE2002av specification, it is possible a temperature sensor can process bit 3 (Event Output Control) of the Configuration Register first while others process bit 2 (Critical Temperature only) first from the Configuration Register. If both bits are set to Logic 1 state concurrently and bit 3 is processed first, the Event output would be enabled before learning the Upper Alarm temperature threshold should be ignored. Since the Upper Alarm temperature threshold is often left unchanged at 0°C (if it is not used), and if the temperature sensor operates in a greater than 0°C environment, it naturally outputs an Event condition. Sometime later, after bit 2 is also processed, the temperature sensor would ignore the Upper Alarm temperature threshold and deassert the Event output if the ambient temperature has not exceeded the Critical Alarm temperature threshold; however, for a system that triggers action off this Event output, this correction has arrived too late. To remedy this ambiguity in the TSE2002av specification, one must avoid setting both bit 2 and bit 3 of the Configuration Register to a Logic 1 concurrently. Instead, Atmel recommends using a two step programming process to set bit 2 first followed by bit 3 in separate commands if the system is designed to only trigger off the Critical Alarm temperature threshold.

## 11.4 Upper Alarm Trip Register (16-bit Read/Write, Address = 02h)

The Upper Alarm Trip Register holds the user programmed upper temperature boundary trip point in 11-bit twos complement format (0.25°C resolution) that can be used to monitor ambient temperature in an operating window (See Table 11-7 and Table 11-8). When the temperature increases above this trip point, or drops below, or is equal to the trip point (minus any hysteresis set), then the EVENT pin is asserted (if enabled). This register becomes read-only if the Alarm Window Lock bit (WINLOCK) bit six in the Configuration Register is set to a Logic 1.

| Bit           | 15  | 14  | 13  | 12   | 11      | 10  | 9   | 8   |  |

|---------------|-----|-----|-----|------|---------|-----|-----|-----|--|

| Symbol        | RFU |     |     | SIGN | ALMWINH |     |     |     |  |

| Default Value | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |  |

| R/W access    | R   | R   | R   | R/W  | R/W     | R/W | R/W | R/W |  |

| Bit           | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |  |

| Symbol        |     |     | ALM | WINH |         |     | RFU |     |  |

| Default Value | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |  |

| R/W access    | R/W | R/W | R/W | R/W  | R/W     | R/W | R   | R   |  |

#### Table 11-7. Upper Alarm Trip Register Bit Distribution

#### Table 11-8. Upper Alarm Trip Register Bit Description

| Bit   | Symbol  | Description                                                                                               |

|-------|---------|-----------------------------------------------------------------------------------------------------------|

| 15:13 | RFU     | <b>Reserved</b> for <b>Future Use</b> . Read as zero.                                                     |

| 12    | SIGN    | Sign bit:0 = Ambient temperature is greater than or equal to 0°C.1= Ambient temperature is less than 0°C. |

| 11:2  | ALMWINH | Upper Alarm Trip temperature bits:<br>Represented in two's complement format.                             |

| 0:1   | RFU     | <b>Reserved</b> for <b>Future Use</b> . Read as zero.                                                     |

## 11.5 Lower Alarm Trip Register (16-bit Read/Write, Address = 03h)

The Lower Alarm Trip Register holds the user programmed lower temperature boundary trip point in 11-bit twos complement format (0.25°C resolution) that can be used to monitor ambient temperature in an operating window (See Table 11-9 and Table 11-10). When temperature decreases below this trip point minus any hysteresis set or increases to meet or exceed this trip point, then the EVENT pin is asserted (if enabled).

This register becomes read-only if the Alarm Window Lock bit (WINLOCK) bit six in the Configuration Register is set to a Logic 1.

| Bit           | 15  | 14  | 13  | 12   | 11      | 10  | 9   | 8   |  |

|---------------|-----|-----|-----|------|---------|-----|-----|-----|--|

| Symbol        |     | RFU |     | SIGN | ALMWINL |     |     |     |  |

| Default Value | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |  |

| R/W access    | R   | R   | R   | R/W  | R/W     | R/W | R/W | R/W |  |

| Bit           | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |  |

| Symbol        |     |     | ALM | WINL |         |     | RFU |     |  |

| Default Value | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |  |

| R/W access    | R/W | R/W | R/W | R/W  | R/W     | R/W | R   | R   |  |

#### Table 11-9. Lower Alarm Trip Register Bit Distribution

#### Table 11-10. Lower Alarm Trip Register Bit Description

| Bit   | Symbol  | Description                                                                                                |

|-------|---------|------------------------------------------------------------------------------------------------------------|

| 15:13 | RFU     | <b>Reserved</b> for <b>Future Use</b> . Read as zero.                                                      |

| 12    | SIGN    | Sign bit:0 = Ambient temperature is greater than or equal to 0°C.1 = Ambient temperature is less than 0°C. |

| 11:2  | ALMWINL | Lower Alarm Trip temperature bits:<br>Represented in twos complement format.                               |

| 0:1   | RFU     | Reserved for Future Use. Read as zero.                                                                     |

## 11.6 Critical Alarm Trip Register (16-bit Read/Write, Address = 04h)

The Critical Alarm Trip Register holds the user programmed Critical Alarm temperature boundary trip point in 11-bit twos complement format (0.25°C resolution) that can be used to monitor ambient temperature (See Table 11-11 and Table 11-12). When the temperature increases above this trip point, the EVENT pin will be asserted (if enabled). It will remain asserted until temperature decreases below or equal to the trip point minus any hysteresis set. This register becomes read-only if the Critical Alarm Trip Lock Bit (CRTALML) bit 7 in the Configuration Register is set to a Logic 1.

| Bit           | 15  | 14  | 13  | 12   | 11      | 10  | 9   | 8   |  |

|---------------|-----|-----|-----|------|---------|-----|-----|-----|--|

| Symbol        | RFU |     |     | SIGN | CRITEVT |     |     |     |  |

| Default Value | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |  |

| R/W access    | R   | R   | R   | R/W  | R/W     | R/W | R/W | R/W |  |

| Bit           | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |  |

| Symbol        |     |     | CRI | ΓEVT |         |     | RFU |     |  |

| Default Value | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |  |

| R/W access    | R/W | R/W | R/W | R/W  | R/W     | R/W | R   | R   |  |

#### Table 11-11. Critical Alarm Trip Register Bit Distribution

#### Table 11-12. Critical Alarm Trip Register Bit Description

| Bit   | Symbol  | Description                                                                                                |

|-------|---------|------------------------------------------------------------------------------------------------------------|

| 15:13 | RFU     | <b>Reserved</b> for <b>Future Use</b> . Read as zero.                                                      |

| 12    | SIGN    | Sign bit:0 = Ambient temperature is greater than or equal to 0°C.1 = Ambient temperature is less than 0°C. |

| 11:2  | CRITEVT | Critical Alarm Trip temperature bits:<br>Represented in two's complement format.                           |

| 0:1   | RFU     | Reserved for Future Use. Read as zero.                                                                     |

### 11.7 Temperature Register (16-bit Read-only, Address = 05h)

The Temperature Register holds the internal temperature measurement data represented in 11-bit twos complement word format allowing for resolution equal to 0.125°C (least significant bit). The upper three bits (15, 14, and 13) of the temperature register indicates the trip status of the current temperature and most important, are not affected by the status of the output of the EVENT pin (See Table 11-13 and Table 11-14).

| Bit           | 15       | 14      | 13     | 12   | 11    | 10     | 9       | 8    |

|---------------|----------|---------|--------|------|-------|--------|---------|------|

| Symbol        | CRITHIGH | ALMHIGH | ALMLOW | SIGN | 128°C | 64°C   | 32°C    | 16°C |

| Default Value | 0        | 0       | 0      | 0    | 0     | 0      | 0       | 0    |

| R/W access    | R        | R       | R      | R    | R     | R      | R       | R    |

| Bit           | 7        | 6       | 5      | 4    | 3     | 2      | 1       | 0    |

| Symbol        | 8°C      | 4°C     | 2°C    | 1°C  | 0.5°C | 0.25°C | 0.125°C | RFU  |

| Default Value | 0        | 0       | 0      | 0    | 0     | 0      | 0       | 0    |

| R/W access    | R        | R       | R      | R    | R     | R      | R       | R    |

#### Table 11-13. Temperature Register Bit Distribution

#### Table 11-14. Temperature Register Bit Description

| Bit  | Symbol   | Description                                                                                                                                                                                                                                                                                                                                                                      |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | CRITHIGH | <ul> <li>0 = Ambient temperature is less than the Critical Alarm Trip Register setting.</li> <li>1 = Ambient temperature is greater than or equal to Critical Alarm Trip Register setting.</li> <li>When this bit is set a Logic 1, it will automatically clear once the measured temperature decreases below or is equal to the trip point minus any hysteresis set.</li> </ul> |

| 14   | ALMHIGH  | <ul> <li>0 = Ambient temperature is below the Upper Alarm Trip Register setting.</li> <li>1 = Ambient temperature is above the Upper Alarm Trip Register setting.</li> <li>When the bit is set to a Logic 1, it will automatically clear once the measured temperature decreases below or is equal to the trip point minus any hysteresis set.</li> </ul>                        |

| 13   | ALMLOW   | <ul> <li>0 = Ambient temperature is above the Lower Alarm Trip Register setting.</li> <li>1 = Ambient temperature is below the Lower Alarm Trip Register setting.</li> <li>When the bit is set to a Logic 1, it will automatically clear once the measured temperature increases above or is to equal to the trip point.</li> </ul>                                              |

| 12   | SIGN     | Sign bit:0 = Ambient temperature is greater than or equal to 0°C.1 = Ambient temperature is less than 0°C.                                                                                                                                                                                                                                                                       |

| 11:1 | TEMP     | Ambient Temperature bits:Represented in twos complement format.The encoding of bits B11 through B2 is the same as in the Alarm Trip Registers.                                                                                                                                                                                                                                   |

| 0    | RFU      | Reserved for Future Use. Read as zero.                                                                                                                                                                                                                                                                                                                                           |

#### 11.7.1 Temperature Register Format

This section will clarify the temperature register format and temperature bit value assignments used for temperature for the following registers: Upper Alarm Trip, Lower Alarm Trip, Critical Alarm Trip, and Temperature Data Registers. The temperatures expressed in the Upper Alarm Trip, Lower Alarm Trip, Critical Alarm Trip, and Temperature Data Registers are indicated in twos complement format. In each of the trip registers, bits 12 through bit 2 are used for temperature settings, or in the case of the Temperature Register, holds the internal temperature measurement with bits 12 through bit one allowing 0.125°C resolution.

Table 11-15 indicates the Temperature Register's assigned bit values used for temperature. Table 11-15 below shows examples for Temperature Register bit values for various temperature readings.

| Table 11-15. | Temperature | Register | Format |

|--------------|-------------|----------|--------|

| 10010 11 101 | romporataro |          |        |

| Bit Position | 12   | 11    | 10   | 9    | 8    | 7   | 6   | 5   | 4   | 3     | 2      | 1       | 0 |

|--------------|------|-------|------|------|------|-----|-----|-----|-----|-------|--------|---------|---|

| Bit Value    | SIGN | 128°C | 64°C | 32°C | 16°C | 8°C | 4°C | 2°C | 1°C | 0.5°C | 0.25°C | 0.125°C | Х |

#### Table 11-16. Temperature Register Examples

| Temperature Re | gister Value Examples   |

|----------------|-------------------------|

| Temperature    | Binary (Bit 15 – Bit 0) |

| +125°C         | xxx0 0111 1101 00xx     |

| +99.75°C       | xxx0 0110 0011 11xx     |

| +85°C          | xxx0 0101 0101 00xx     |

| +39°C          | xxx0 0010 0111 00xx     |

| +15.75°C       | xxx0 0000 1111 11xx     |

| +0.25°C        | xxx0 0000 0000 01xx     |

| 0°C            | xxx0 0000 0000 00xx     |

## 11.8 Manufacturer ID Register (16-bit Read-only, Address = 06h)

This register is used to identity the manufacturer of the product. The Manufacturer ID for the AT30TSE002A is 001Fh (See Table 11-17).

| Bit           | 15 | 14              | 13 | 12     | 11        | 10 | 9 | 8 |  |  |  |

|---------------|----|-----------------|----|--------|-----------|----|---|---|--|--|--|

| Symbol        |    | Manufacturer ID |    |        |           |    |   |   |  |  |  |

| Default Value | 0  | 0               | 0  | 0      | 0         | 0  | 0 | 0 |  |  |  |

| R/W access    | R  | R               | R  | R      | R         | R  | R | R |  |  |  |

| Bit           | 7  | 6               | 5  | 4      | 3         | 2  | 1 | 0 |  |  |  |

| Symbol        |    |                 |    | Manufa | cturer ID |    |   |   |  |  |  |

| Default Value | 0  | 0               | 0  | 1      | 1         | 1  | 1 | 1 |  |  |  |

| R/W access    | R  | R               | R  | R      | R         | R  | R | R |  |  |  |

#### Table 11-17. Manufacturer ID Register Bit Distribution

## 11.9 Device ID Register (16-bit Read-only, Address = 07h)

The upper or high order byte is used to specify the device identification and the other byte is used to specify device revision. The Device ID for the AT30TSE002A is 8201h (See Table 11-18).

| Bit           | 15 | 14        | 13 | 12     | 11       | 10 | 9 | 8 |  |  |  |

|---------------|----|-----------|----|--------|----------|----|---|---|--|--|--|

| Symbol        |    | Device ID |    |        |          |    |   |   |  |  |  |

| Default Value | 1  | 0         | 0  | 0      | 0        | 0  | 1 | 0 |  |  |  |

| R/W access    | R  | R         | R  | R      | R        | R  | R | R |  |  |  |

| Bit           | 7  | 6         | 5  | 4      | 3        | 2  | 1 | 0 |  |  |  |

| Symbol        |    |           |    | Device | Revision |    |   |   |  |  |  |

| Default Value | 0  | 0         | 0  | 0      | 0        | 0  | 0 | 1 |  |  |  |

| R/W access    | R  | R         | R  | R      | R        | R  | R | R |  |  |  |

## 11.10 SMBus Register (16-bit Write/Read only, Address = 22h)

The SMBus Register allows the user to enable or disable the SMBus time out feature (See Table 11-19 and Table 11-20).

| Bit           | 15     | 14  | 13 | 12 | 11  | 10 | 9 | 8 |  |  |  |

|---------------|--------|-----|----|----|-----|----|---|---|--|--|--|

| Symbol        |        | RFU |    |    |     |    |   |   |  |  |  |

| Default Value | 0      | 0   | 0  | 0  | 0   | 0  | 0 | 0 |  |  |  |

| R/W access    | R      | R   | R  | R  | R   | R  | R | R |  |  |  |

| Bit           | 7      | 6   | 5  | 4  | 3   | 2  | 1 | 0 |  |  |  |

| Symbol        | SMBOUT |     |    |    | RFU |    |   |   |  |  |  |

| Default Value | 0      | 0   | 0  | 0  | 0   | 0  | 0 | 0 |  |  |  |

| R/W access    | R/W    | R   | R  | R  | R   | R  | R | R |  |  |  |

#### Table 11-19. SMBus Register Bit Distribution

#### Table 11-20. SMBus Register Bit Distribution

| Bit  | Symbol | Description                                                                                                                                                                                                                                                                                    |

|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | RFU    | <b>Reserved</b> for <b>Future Use</b> . Read as zero.                                                                                                                                                                                                                                          |

| 7    | SMBOUT | SMBus Timeout:         0 = SMBus Timeout is enabled.         1 = SMBus Timeout is disabled.         When enabled, timeout is active for temperature sensor operations.         When either of the Crit_Alarm Trip or Alarm Window lock bits is set, this bit cannot be altered until unlocked. |

| 6:0  | RFU    | <b>Reserved</b> for <b>Future Use</b> . Read as zero.                                                                                                                                                                                                                                          |

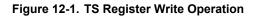

## 12. TS Write Operations

Writing to the AT30TSE002A Temperature Register set is accomplished through a modified Write operation for two data bytes. To maintain 2-Wire compatibility, the 16-bit register is accessed through a Pointer Register, requiring the Write sequence to include an address pointer in addition to the device address. This indicates the storage location for the next two bytes received. Table 12-1 shows an entire Write transaction on the bus.

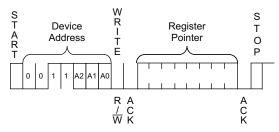

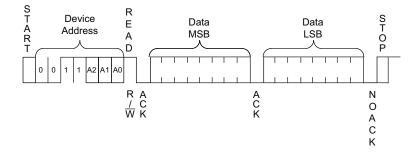

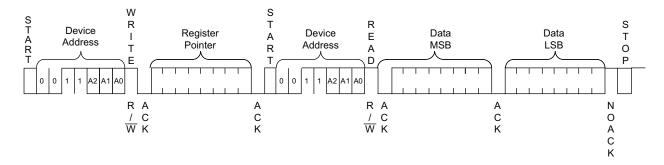

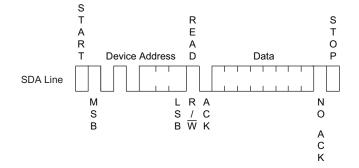

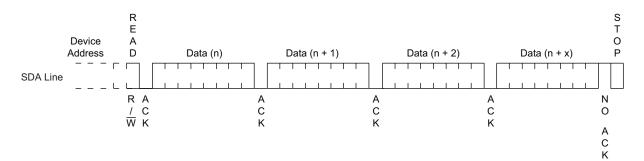

## 12.1 TS Read Operations

Reading data from the TS may be accomplished in one of two ways:

- If the location latched in the Pointer Register is correct (for normal operation it is expected the same address will be read repeatedly for temperature), the Read sequence may consist of a device address from the bus master followed by two bytes of data from the device; or

- The Pointer Register is loaded with the correct register address, and the data is read. The sequence to preset the Pointer Register is shown in Figure 12-4, and the preset Pointer Read is shown in Figure 12-3. If it is desired to read random address each cycle, the complete Pointer Write, Word Read sequence is shown in Figure 12-4.

The data byte has the most significant bit first. At the end of a Read, this device can accept either Acknowledge (ACK) or No Acknowledge (No ACK) from the Master (No Acknowledge is typically used as a signal for the slave that the Master has read its last byte).

#### Figure 12-2. Write to Pointer Register

Figure 12-3. Preset Pointer Register Word Read

Figure 12-4. 2-wire Pointer Write Register Word Read

#### Figure 12-6. Setting Reversible Write Protect Register (RSWP)

#### Table 12-1. EEPROM Write Protection

|            |    | Pin |     | Preamble |    |    |    |            |    |    | R/W |

|------------|----|-----|-----|----------|----|----|----|------------|----|----|-----|

| Command    | A2 | A1  | A0  | B7       | B6 | B5 | B4 | <b>B</b> 3 | B2 | B1 | B0  |

| Set PSWP   | A2 | A1  | A0  | 0        | 1  | 1  | 0  | A2         | A1 | A0 | 0   |

| Set RSWP   | 0  | 0   | VHV | 0        | 1  | 1  | 0  | 0          | 0  | 1  | 0   |

| Clear RSWP | 0  | 1   | VHV | 0        | 1  | 1  | 0  | 0          | 1  | 1  | 0   |

## Table 12-2. V<sub>HV</sub>

|                 | Min | Мах | Units |

|-----------------|-----|-----|-------|

| V <sub>HV</sub> | 7   | 10  | V     |

#### Table 12-3. EEPROM Software Write Protection

| Command    | R/W<br>Bit | Permanent Write<br>Protect Register<br>PSWP | Reversible Write<br>Protect Register<br>RSWP | Acknowledgement<br>from Device | Action from Device                                                   |

|------------|------------|---------------------------------------------|----------------------------------------------|--------------------------------|----------------------------------------------------------------------|

| 1010       | R          | Х                                           | х                                            | ACK                            |                                                                      |

| 1010       | W          | Programmed                                  | Х                                            | ACK                            | Can write to second Half (80H – FFH) only.                           |

| 1010       | W          | Х                                           | Programmed                                   | ACK                            | Can write to second Half (80H – FFH) only.                           |

| 1010       | W          | Not<br>Programmed                           | Not<br>Programmed                            | ACK                            | Can write to full array.                                             |

| Read PSWP  | R          | Programmed                                  | х                                            | No ACK                         | Stop – Indicates Permanent Write Protect Register is programmed.     |

| Read PSWP  | R          | Not<br>Programmed                           | Х                                            | ACK                            | Read out data don't care. Indicates PSWP Register is not programmed. |

| Set PSWP   | W          | Programmed                                  | х                                            | No ACK                         | Stop – Indicates Permanent Write Protect Register is programmed.     |

| Set PSWP   | W          | Not<br>Programmed                           | Х                                            | ACK                            | Program Permanent Write Protect Register (irreversible).             |

| Read RSWP  | R          | х                                           | Programmed                                   | No ACK                         | Stop – Indicates Reversible Write Protect Register is programmed.    |

| Read RSWP  | R          | х                                           | Not<br>Programmed                            | ACK                            | Read out data don't care. Indicates RSWP Register is not programmed. |

| Set RSWP   | W          | х                                           | Programmed                                   | No ACK                         | Stop – Indicates Reversible Write Protect Register is programmed.    |

| Set RSWP   | W          | х                                           | Not<br>Programmed                            | ACK                            | Program Reversible Write Protect Register (reversible).              |

| Clear RSWP | W          | Programmed                                  | Х                                            | No ACK                         | Stop – Indicates Permanent Write Protect Register is programmed.     |