## ITS42k5D-LD-F

Dual Channel High-Side PMOS Power Switch with Integrated Freewheeling Diodes

## **Data Sheet**

Rev 1.0, 2015-04-28

## Standard Power

# Dual Channel High-Side PMOS Power Switch with Integrated Freewheeling Diodes

ITS42k5D-LD-F

#### 1 Overview

#### **Features**

- Two channel power PMOS high-side switch

- · Integrated freewheeling diode

- Output current capability: up to 250mA per channel

- Wide operating voltage range: 4.5V to 42V

- · Very low quiescent current in OFF state

- High current limit accuracy

- 3.3V and 5V compatible logic inputs

- Optimized EMC behavior

- Overload, short circuit, open load and overtemperature diagnosis

- ESD, short circuit, safe operation area and overtemperature protection

- Undervoltage lockout (UVLO)

- Green and robust product (RoHS compliant)

The ITS42k5D-LD-F, which is available in a very small leadless PG-TSON-10 package, is a  $2.5\Omega$  dual channel high-side PMOS power switch with integrated freewheeling diodes including protection and diagnostic functions. The ITS42k5D-LD-F has two diagnostic status output pins, one for each channel.

The diagnosis can be read out from two separate open drain outputs in order to indicate overload, short circuit, open load and overtemperature conditions. The device controls the respective channel one or two by the two separate input pins i.e. IN1 and IN2. When both inputs are low the device is in OFF condition. Each channel of the device is able to drive loads up to 250mA.

### **Application range**

The ITS42k5D-LD-F is capable of switching resistive, capacitive and inductive loads (e.g. sensor units, LEDs, relays, valves) in harsh industrial environments. An integrated freewheeling diode enables driving of inductive loads. The ITS42k5D-LD-F is suitable for switching small loads such as sensors. For sensor supplies please refer to Infineon's industrial linear voltage regulator products.

The qualification of this product is based on JEDEC JESD47 and may reference existing qualification results of similar products. Such referencing is justified by the structural similarity of the products. The product is not qualified and manufactured according to the requirements of Infineon Technologies with regard to automotive and/or transportation applications.

| Туре          | Package    | Marking |

|---------------|------------|---------|

| ITS42k5D-LD-F | PG-TSON-10 | I2k5DF  |

PG-TSON-10

Overview

Infineon Technologies administrates a comprehensive quality management system according to the latest version of the ISO9001 and ISO/TS 16949.

The most updated certificates of the aforesaid ISO9001 and ISOTS 16949 are available on the Infineon Technologies web page http://www.infineon.com/cms/en/product/technology/quality/

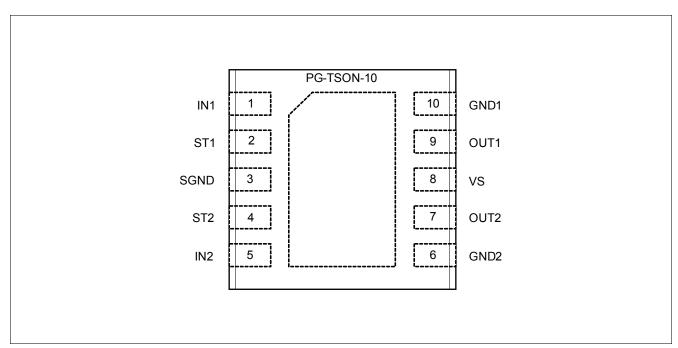

**Pin Configuration**

## 2 Pin Configuration

## 2.1 Pin Assignment

Figure 1 Pin configuration top view, PG-TSON-10

## 2.2 Pin Definitions and Functions

Table 1 Pin Definition

| Pin         | Symbol | Function                                                                            |

|-------------|--------|-------------------------------------------------------------------------------------|

| 1           | IN1    | INPUT 1; Control Input for Channel 1, Active High                                   |

| 2           | ST1    | STATUS 1; Status Flag for Channel 1; Open Drain Output                              |

| 3           | SGND   | SIGNAL GND; connect to all GNDs and to exposed GND pad                              |

| 4           | ST2    | STATUS 2; Status Flag for Channel 2; Open Drain Output                              |

| 5           | IN2    | INPUT 2; Control Input for Channel 2; Active High                                   |

| 6           | GND2   | Ground Channel 2; Connect to all GNDs and to exposed GND pad                        |

| 7           | OUT2   | <b>OUTPUT 2;</b> drain of the power-PMOS Channel 2; power freewheeling diode to GND |

| 8           | VS     | Supply Voltage; block to GND with a capacitor near the IC                           |

| 9           | OUT1   | <b>OUTPUT 1;</b> drain of the power-PMOS Channel 1; power freewheeling diode to GND |

| 10          | GND1   | Ground Channel 1; Connect to all GNDs and to exposed GND pad                        |

| Exposed pad | _      | Connect externally to all GNDs i.e. GND1, GND2 and SGND                             |

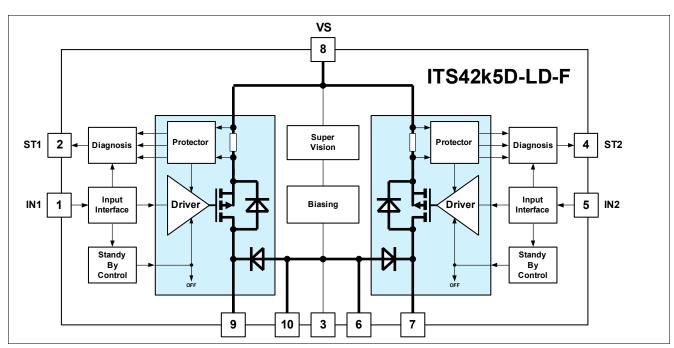

**Block Diagram**

## 3 Block Diagram

## 3.1 ITS42k5D-LD-F in the PG-TSON-10 package

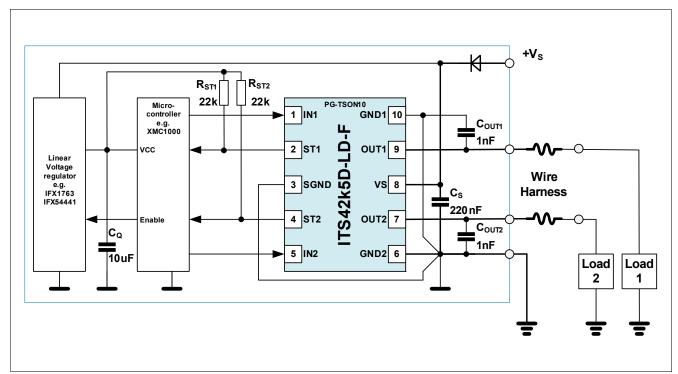

Figure 2 Block diagram ITS42k5D-LD-F

### 4 Functional Description

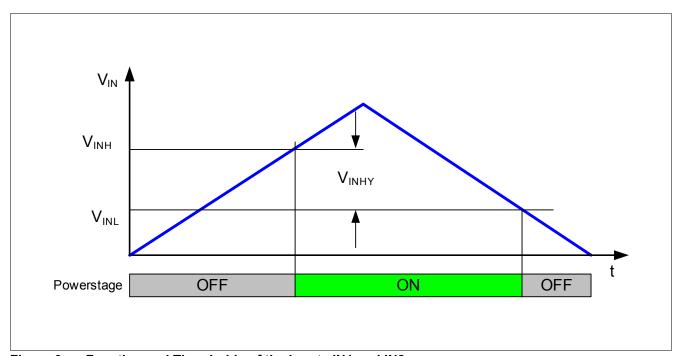

### 4.1 Input Circuit

The two inputs i.e. IN1 and IN2 control the outputs of channel 1 and channel 2 respectively.

When both inputs IN1 and IN2 are low the device is switched OFF. In OFF state, the current consumption of the device is very low. For more details on current consumption in ON and OFF states please refer to electrical characteristics. The logic input levels are compatible with 3.3V and 5V microcontrollers. To avoid switching noise all inputs have hysteresis. Logic level definitions are shown in **Figure 3**

Figure 3 Function and Thresholds of the inputs IN1 and IN2

The input pins are optimized in terms of ESD protection, withstanding overvoltage scenarios like surge pulses. Overvoltage transient levels higher than the maximum ratings of 45V must be avoided.

Note: Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" the normal operating range. Protection functions are neither designed for continuous nor repetitive operation.

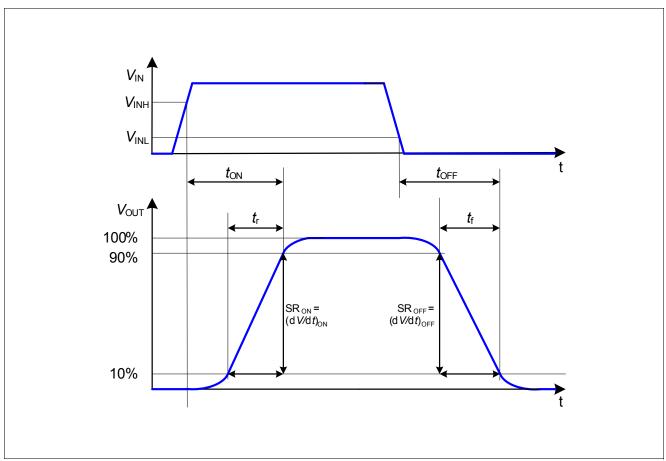

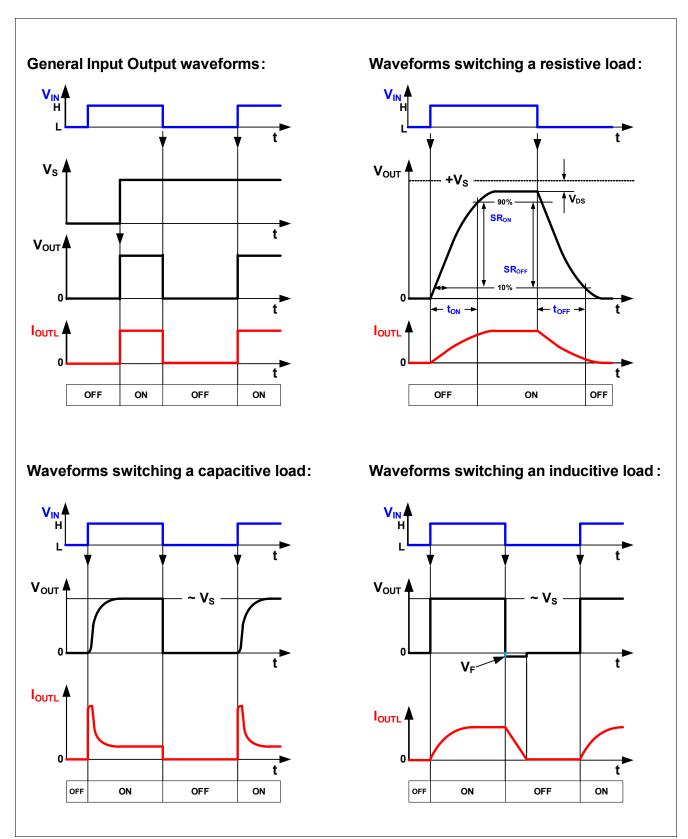

### 4.2 Powerstage

The two outputs are designed as high-side switches with integrated freewheeling diodes from OUT to GND. The high side switch is a power P-channel MOSFET. The integrated freewheeling diodes enable the device to switch inductive loads on each channel.

A built-in high accuracy current limiter ensures that the Power P-channel MOSFET is protected against overload when driving heavy capacitive loads.

Figure 4 shows the output voltage  $V_{\mathrm{OUT1}}$  and  $V_{\mathrm{OUT2}}$  controlled by the input interfaces IN1, IN2

Figure 4 Input / output timings when switching a resistive load.

### 4.3 Protection Functions

Note: Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" the normal operating range. Protection functions are neither designed for continuous nor repetitive operation.

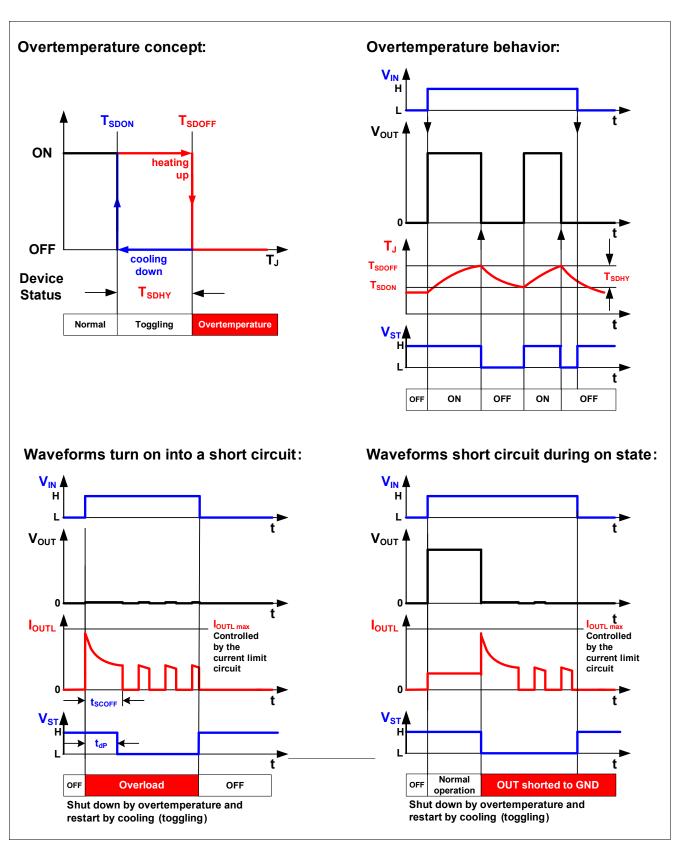

### 4.3.1 Short Circuit Protection

Short circuit is a special case of overload. The device is protected within the supply voltage range from  $V_{\rm S}$  = 4.5 V to 42 V. If the device stays in short circuit condition for a longer time the integrated temperature protection will switch the device OFF (both channels OFF). For details please look at chapter "Overtemperature Protection".

### 4.3.2 Protection by Overtemperature Shutdown

This circuit monitors the junction temperature  $T_{\rm j}$ . When the device is ON, the junction temperature  $T_{\rm j}$  increases proportional to the power loss. The temperature protector is equipped with two temperature sensors, one for each one of the powerstages. When the thermal shutdown trip point  $T_{\rm SDOFF}$  is reached, the in-built protector switches OFF the respective channel. This overtemperature shutdown is reported via diagnosis to the respective status flag i.e. either ST1 and ST2. The output remains OFF until the junction is cooled down to the thermal shutdown release point  $T_{\rm SDON}$ . If the overload condition remains the device will toggle between both junction temperature values. It is not recommended for the device to stay in an overload condition as this will degrade its lifetime.

### 4.4 Diagnosis

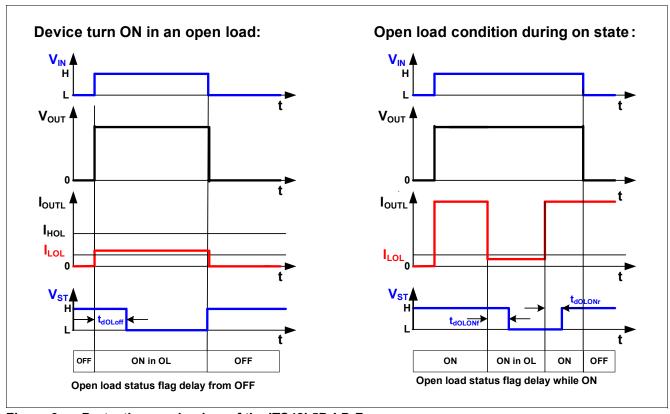

For diagnostic purposes the device provides two digital output pins ST1 and ST2 in order to indicate fault conditions.

The status flag ST1 indicates the status of channel 1 and flag ST2 indicates the status of channel 2.

Each status output (ST1, ST2) of the ITS42k5D-LD-F is a high voltage open drain output.

In "normal" operation mode the NMOS open drain transistors are switched OFF. The following truth table (**Table 2**) defines the status output of the device under various conditions.

Table 2 Truth table of diagnosis feature

| Device Operation     | IN1 | IN2 | ST1 | ST2 | Comment                                     |  |  |

|----------------------|-----|-----|-----|-----|---------------------------------------------|--|--|

| Normal Operation     | Н   | Н   | Н   | Н   | -                                           |  |  |

| Overload             | Н   | Н   | L   | L   | Respective flag is low; latched             |  |  |

| Short Circuit to GND | Н   | Н   | L   | L   | Respective flag is low; latched             |  |  |

| Overtemperature      | Н   | Н   | L   | L   | Respective flag is low; latched             |  |  |

| Overtemperature      | L   | L   | Н   | Н   | Device in OFF mode; no internal heat source |  |  |

| Open Load            | Н   | Н   | L   | L   | Respective flag is low                      |  |  |

### 4.5 Undervoltage Lockout

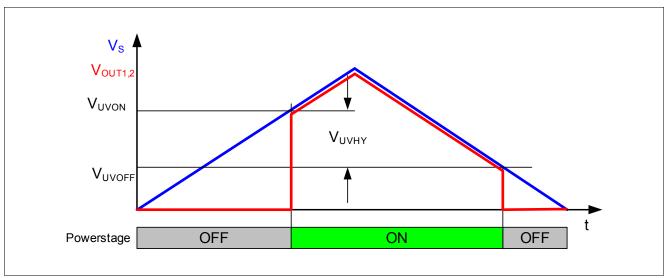

In order to avoid an application malfunction caused by an undervoltage condition at the load (e.g. a relay can not keep the contact closed properly) an undervoltage lockout (UVLO) supervises the supply voltage Vs.

The UVLO circuit switches the power stages off if the supply voltage is below the functional operating voltage range

Figure 5 Under Voltage Lockout (UVLO) function and thresholds

### 4.6 Protection Behavior

Figure 6 Protection mechanism of the ITS42k5D-LD-F

Figure 7 Protection behavior of the ITS42k5D-LD-F

## 4.7 Application Waveforms

Figure 8 Protection behavior of the ITS42k5D-LD-F

**General Product Characteristics**

### 5 General Product Characteristics

### 5.1 Absolute Maximum Ratings

Table 3 Absolute maximum ratings<sup>1)</sup> $T_j$  = -40°C to +125° unless otherwise specified; all voltages with respect to ground unless otherwise specified

| Parameter                               | Symbol                |      | Value    | S                    | Unit     | Note /<br>Test Condition                        | Number |

|-----------------------------------------|-----------------------|------|----------|----------------------|----------|-------------------------------------------------|--------|

|                                         |                       | Min. | Тур.     | Max.                 |          |                                                 |        |

| Supply voltage VS                       |                       |      | II.      |                      |          |                                                 | II.    |

| Voltage                                 | $V_{S}$               | -0.3 | _        | 45                   | V        | _                                               | 5.1.1  |

| Current                                 | $I_{S}$               | -10  | _        | _                    | mA       | Internally limited                              | 5.1.2  |

| Input IN1 and IN2                       | 1                     |      | <u> </u> |                      | <b>"</b> |                                                 | 1      |

| Input Voltage                           | $V_{IN1,2}$           | -0.3 | _        | 45                   | V        | _                                               | 5.1.3  |

| Current                                 | $I_{IN1,2}$           | _    | _        | _                    | mA       | Internally limited                              | 5.1.4  |

| Output ST                               |                       |      |          |                      | •        |                                                 |        |

| Voltage                                 | $V_{\mathrm{ST1,2}}$  | -0.3 | _        | 45                   | V        | _                                               | 5.1.5  |

| Current                                 | $I_{\mathrm{ST1,2}}$  | _    | _        | 5                    | mA       | _                                               | 5.1.6  |

| Ground GND1, GND2, SGN                  |                       |      |          |                      |          |                                                 |        |

| Current                                 | $I_{\mathrm{GND1,2}}$ | _    | _        | 600                  | mA       | Internally limited                              | 5.1.7  |

| Current                                 | $I_{SGND}$            | _    | _        | 10                   | mA       | Internally limited                              | 5.1.8  |

| Output stage OUT1, OUT2                 |                       |      | <u>.</u> |                      |          |                                                 |        |

| Voltage                                 | $V_{OUT1,2}$          | _    | _        | V <sub>S</sub> + 0.3 | V        | Internally limited                              | 5.1.9  |

| Temperatures                            |                       |      | <u>.</u> |                      |          |                                                 |        |

| Junction Temperature                    | $T_{\rm j}$           | -40  | _        | 150                  | °C       | _                                               | 5.1.11 |

| Storage Temperature                     | $T_{\mathrm{stg}}$    | -55  | -        | 150                  | °C       | _                                               | 5.1.12 |

| Power Dissipation                       |                       |      | <u>.</u> |                      |          |                                                 |        |

| Power dissipation                       | $P_{tot}$             | _    | 0.66     | _                    | W        | PCB <sup>2)</sup> is vertical without blown air | 5.1.13 |

| ESD Susceptibility                      |                       |      | <u>.</u> |                      |          |                                                 |        |

| ESD susceptibility (all pins)           | $V_{ESD}$             | -2   | _        | 2                    | kV       | HBM <sup>3)</sup>                               | 5.1.14 |

| ESD susceptibility OUT pins vs. GND pin | $V_{ESD}$             | -2   | _        | 2                    | kV       |                                                 | 5.1.15 |

| ESD susceptibility (all pins)           | $V_{ESD}$             | -1   | _        | 1                    | kV       | CDM <sup>4)</sup>                               | 5.1.15 |

<sup>1)</sup> Not subject to production test, specified by design

Note: Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" the normal operating range. Protection functions are neither designed for continuous nor repetitive operation.

<sup>2)</sup> See Thermal Resistance Footnote 2)

<sup>3)</sup> ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS-001 (1.5k $\Omega$ , 100pF)

<sup>4)</sup> ESD susceptibility, Charged Device Model "CDM" JEDEC JESD22-C101

#### **General Product Characteristics**

### 5.2 Functional Range

Table 4 Functional Range<sup>1)</sup>

| Parameter                 | Symbol             | V           | /alues |      | Unit | Note /<br>Test Condition | Number |

|---------------------------|--------------------|-------------|--------|------|------|--------------------------|--------|

|                           |                    | Min.        | Тур.   | Max. |      |                          |        |

| Nominal Operating Voltage | $V_{S}$            | $V_{UVON}$  | _      | 42   | V    | $V_{\rm S}$ increasing   | 5.2.1  |

| Nominal Operating Voltage | $V_{S}$            | $V_{UVOFF}$ | _      | 42   | V    | $V_{\rm S}$ decreasing   | 5.2.2  |

| Nominal Operating Voltage | $V_{IN1,2}$        | -0.3        | -      | 7    | V    | _                        | 5.2.3  |

| Nominal Operating Voltage | V <sub>ST1,2</sub> | -0.3        | _      | 7    | V    | _                        | 5.2.4  |

| Junction Temperature      | $T_{\rm j}$        | -40         | -      | 125  | °C   | _                        | 5.2.5  |

<sup>1)</sup> Not subject to production test, specified by design

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 5.3 Thermal Resistance

This thermal data was generated in accordance with JEDEC JESD51 standards.

More information on www.jedec.org

Table 5 Thermal Resistance<sup>1)</sup>

| Parameter                     | Symbol                     |      | Values | 3    | Unit | Note /<br>Test Condition | Number |

|-------------------------------|----------------------------|------|--------|------|------|--------------------------|--------|

|                               |                            | Min. | Тур.   | Max. |      |                          |        |

| PG-TSON-10                    |                            | '    | '      |      |      |                          |        |

| Junction to Case, exposed pad | $R_{thjc}$                 | _    | 12     | _    | K/W  |                          | 5.3.1  |

| Junction to ambient           | $R_{thJA\_1s0p}$           | _    | 140    | _    | K/W  | 2)                       | 5.3.2  |

| Junction to ambient           | $R_{ m thJA\_1s0p\_300mm}$ | _    | 70     | _    | K/W  | 3)                       | 5.3.3  |

| Junction to ambient           | $R_{ m thJA\_1s0p\_600mm}$ | _    | 60     | _    | K/W  | 4)                       | 5.3.4  |

| Junction to ambient           | $R_{thJA\_2s2p}$           | _    | 67     | _    | K/W  | 5)                       | 5.3.5  |

| Junction to ambient           | $R_{thJA\_2s2pvia}$        | _    | 55     | _    | K/W  | 6)                       | 5.3.6  |

<sup>1)</sup> Not subject to production test, specified by design

- 2) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board, footprint; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1x 70 $\mu$ m Cu.

- 3) Specified  $R_{\rm thJA}$  value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board, Cu, 300mm<sup>2</sup>; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1x 70 $\mu$ m Cu.

- 4) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board, 600mm<sup>2</sup>; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1x 70 $\mu$ m Cu.

- 5) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 $\mu$ m Cu, 2 x 35 $\mu$ m Cu).

- 6) Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board with two thermal vias; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70μm Cu, 2 x 35μm Cu. The diameter of the two vias are equal 0.3mm and have a plating of 25μm with a copper heatsink area of 3mm x 2mm). JEDEC51-7: The two plated-through hole vias should have a solder land of no less than 1.25 mm diameter with a drill hole of no less than 0.85 mm diameter.

**Electrical Characteristics**

## **6** Electrical Characteristics

Table 6  $V_{\rm S}$  = 4.5 V to 42 V ;  $T_{\rm j}$  = -40°C to +125°, all voltages with respect to ground, currents flowing into the device unless otherwise specified ; typical values are given at  $V_{\rm S}$  = 13.5 V,  $T_{\rm j}$  = 25°C

| Parameter                                               | Symbol                  |      | Value | s    | Unit | Note /                                                                                                                                         | Number |

|---------------------------------------------------------|-------------------------|------|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                         |                         | Min. | Тур.  | Max. | 1    | Test Condition                                                                                                                                 |        |

| Input                                                   |                         |      | 1     |      |      |                                                                                                                                                | -1     |

| ON Threshold                                            | V <sub>INH1, 2</sub>    | 2    | -     | _    | V    | _                                                                                                                                              | 6.1.1  |

| OFF Threshold                                           | $V_{INL1,2}$            | _    | _     | 0.8  | V    | _                                                                                                                                              | 6.1.2  |

| Input Hysteresis                                        | $V_{INHY1,2}$           | 0.1  | 0.4   | _    | V    | $V_{INHY} = V_{INH} - V_{INL}$                                                                                                                 | 6.1.3  |

| Input Current - ON state                                | $I_{INON1,2}$           | 10   | 25    | 50   | μΑ   | $V_{IN} = 5V$                                                                                                                                  | 6.1.4  |

| Input Pull Down Resistor;<br>IN1,2 to SGND              | R <sub>IN1,2</sub>      | 100  | 200   | 300  | kΩ   | _                                                                                                                                              | 6.1.5  |

| Powerstage                                              |                         |      |       | - 1  |      |                                                                                                                                                |        |

| PMOS ON Resistance                                      | $R_{DSON1,2}$           | _    | 2.5   | 8    | Ω    | $I_{\text{OUT1, 2}} = 250 \text{mA}$                                                                                                           | 6.1.6  |

| PMOS ON Resistance                                      | $R_{DSON1,2}$           | _    | 2.5   | 4    | Ω    | $I_{\text{OUT1, 2}} = 250\text{mA};$<br>$T_{\text{i}} = 25^{\circ}\text{C};$                                                                   | 6.1.7  |

| Freewheeling Diode<br>Forward Voltage                   | $V_{F1,2}$              | -    | -     | 1.5  | V    | I <sub>F1, 2</sub> = 250mA                                                                                                                     | 6.1.8  |

| Freewheeling Diode<br>Forward Voltage                   | $V_{F1,2}$              | -    | 1.0   | 1.2  | V    | $I_{\text{F1, 2}}$ = 250mA<br>$T_{\text{j}}$ = 25°C;                                                                                           | 6.1.9  |

| Output Leakage Current (PMOS)                           | $I_{OUTLK1,2}$          | _    | _     | 2    | μΑ   | $V_{\text{IN1}} = V_{\text{IN2}} = 0V;$<br>$V_{\text{OUT1, 2}} = 0V;$<br>$T_{\text{j}} = -40^{\circ}\text{C to } 105^{\circ}\text{C}$          | 6.1.10 |

| Output Leakage Current (Diode)                          | $I_{\mathrm{OUTLK1,2}}$ | -2   | _     | -    | μА   | $V_{\text{IN1}} = V_{\text{IN2}} = 0V$<br>$V_{\text{OUT1, 2}} = V_{\text{S}};$<br>$T_{\text{j}} = -40^{\circ}\text{C to } 105^{\circ}\text{C}$ | 6.1.11 |

| Turn ON Time (to 90% of $V_{\rm OUT}$ )                 | t <sub>ON1,2</sub>      | 6    | 12    | 25   | μs   | $V_{\rm S}$ =13.5V;<br>$R_{\rm L1, 2}$ = 51 $\Omega$                                                                                           | 6.1.12 |

| Turn OFF Time (to 10% of $V_{\rm OUT}$ )                | t <sub>OFF1,2</sub>     | 8    | 16    | 30   | μs   | $V_{\rm S}$ =13.5V;<br>$R_{\rm L1,  2}$ = 51 $\Omega$                                                                                          | 6.1.13 |

| Rise Time (from 10% to 90% of $V_{\rm OUT}$ )           | t <sub>r1,2</sub>       | 3    | 6     | 15   | μs   | $V_{\rm S}$ =13.5V;<br>$R_{\rm L1, 2}$ = 51 $\Omega$                                                                                           | 6.1.14 |

| Fall Time (from 90% to 10% of $V_{\rm OUT}$ )           | t <sub>f1,2</sub>       | 3    | 6     | 15   | μs   | $V_{\rm S}$ =13.5V;<br>$R_{\rm L1, 2}$ = 51 $\Omega$                                                                                           | 6.1.15 |

| Slew Rate ON = $dV/dt$<br>(10% to 90% of $V_{OUT}$ )    | SR <sub>ON1,2</sub>     | 0.7  | 1.7   | 3.5  | V/µs | $V_{\rm S}$ =13.5V;<br>$R_{\rm L1, 2}$ = 51 $\Omega$                                                                                           | 6.1.16 |

| Slew Rate OFF = $- dV/dt$<br>(10% to 90% of $V_{OUT}$ ) | SR <sub>OFF1,2</sub>    | 0.7  | 1.7   | 3.5  | V/µs | $V_{\rm S}$ =13.5V;<br>$R_{\rm L1, 2}$ = 51 $\Omega$                                                                                           | 6.1.17 |

| Current consumption                                     |                         |      | ı     |      |      | 1 7                                                                                                                                            | -1     |

| Quiescent Current in OFF Mode                           | $I_{SOFF}$              | _    | _     | 1    | μΑ   | $T_{\rm j}$ = -40°C to 85°C;<br>$V_{\rm IN1}$ = $V_{\rm IN2}$ = 0V;<br>$R_{\rm L1,2}$ = 51 $\Omega$                                            | 6.1.18 |

**Electrical Characteristics**

Table 6  $V_{\rm S}$  = 4.5 V to 42 V ;  $T_{\rm j}$  = -40°C to +125°, all voltages with respect to ground, currents flowing into the device unless otherwise specified ; typical values are given at  $V_{\rm S}$  = 13.5 V,  $T_{\rm j}$  = 25°C

| Parameter                                                                                            | Symbol                |      | Value | s    | Unit | Note /                                                                                                               | Number |

|------------------------------------------------------------------------------------------------------|-----------------------|------|-------|------|------|----------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                      |                       | Min. | Тур.  | Max. |      | Test Condition                                                                                                       |        |

| Quiescent Current in OFF Mode                                                                        | $I_{SOFF}$            | _    | _     | 5    | μΑ   | $T_{\rm j}$ = -40°C to 105°C;<br>$V_{\rm IN1}$ = $V_{\rm IN2}$ = 0V;<br>$R_{\rm L1,2}$ = 51 $\Omega$                 | 6.1.19 |

| Current Consumption in ON Mode without load                                                          | $I_{SON}$             | _    | 3     | 5    | mA   | $V_{\text{IN1,}} = V_{\text{IN2}} = 5\text{V};$<br>OUT1, 2 open                                                      | 6.1.20 |

| Current Consumption in ON Mode without load                                                          | $I_{SON}$             | _    | 3     | 4    | mA   | $V_{\rm IN1,} = V_{\rm IN2} = 5V;$<br>$T_{\rm j} = 25^{\circ}{\rm C};$<br>OUT1, 2 open                               | 6.1.21 |

| Current Consumption in ON Mode; with resistive nominal loads $I_{SON} = I_{S} - I_{OUT1} - I_{OUT2}$ | $I_{SON}$             | -    | 3     | 5    | mA   | $V_{\rm IN1,} = V_{\rm IN2} = 5 \text{V};$<br>$R_{\rm L1} = R_{\rm L2} = 51 \Omega;$<br>$V_{\rm S} = 13.5 \text{ V}$ | 6.1.22 |

| Overload Protection Current Limit                                                                    | (1)                   |      |       |      |      | -                                                                                                                    |        |

| Output Current Limitation                                                                            | I <sub>OUTL1, 2</sub> | 250  | 400   | 600  | mA   | 4.5V < V <sub>DS1,2</sub> < 20V                                                                                      | 6.1.23 |

| Output Current Limitation                                                                            | I <sub>OUTL1, 2</sub> | 200  | 300   | _    | mA   | $V_{\rm DS1,2} = 30 \rm V$                                                                                           | 6.1.24 |

| Output Current Limitation                                                                            | I <sub>OUTL1, 2</sub> | 50   | 150   | _    | mA   | $V_{\rm DS1,2} = 42V$                                                                                                | 6.1.25 |

| Status flag time after positive input slope <sup>2)</sup>                                            | $t_{\text{dP1,2}}$    | _    | 60    | -    | μs   | _                                                                                                                    | 6.1.26 |

| Overtemperature Protection <sup>1)</sup>                                                             | II.                   | I.   |       | 1    | 1    | 1                                                                                                                    |        |

| Thermal Shutdown Trip Point                                                                          | $T_{SDOFF}$           | 150  | 175   | 200  | °C   | _                                                                                                                    | 6.1.27 |

| Thermal Shutdown Release Point                                                                       | $T_{\sf SDON}$        | 125  | 150   | 175  | °C   | _                                                                                                                    | 6.1.28 |

| Thermal Shutdown Hysteresis                                                                          | $T_{SDHY}$            | _    | 25    | _    | °C   | _                                                                                                                    | 6.1.29 |

| Open Load Diagnosis                                                                                  |                       |      |       |      |      |                                                                                                                      |        |

| Open Load Detection Threshold in ON state; ST going from high to low                                 | $I_{LOL}$             | 0.2  | 3.5   | 8    | mA   | $V_{\rm S}$ = 13.5V<br>$T_{\rm j}$ = 25°C                                                                            | 6.1.30 |

| Open Load Detection Threshold in ON state; ST going from low to high                                 | $I_{HOL}$             | 1    | 5     | 9.5  | mA   | $V_{\rm S}$ = 13.5V<br>$T_{\rm j}$ = 25°C                                                                            | 6.1.31 |

| Open Load Detection Threshold<br>Hysteresis in ON state                                              | $I_{LOLHYS}$          | 0.2  | 1.5   | _    | mA   | $V_{\rm S}$ = 13.5V<br>$T_{\rm j}$ = 25°C                                                                            | 6.1.32 |

| Status flag time after positive input slope while in Open Load                                       | $t_{\sf dOLOFF1,2}$   | _    | 18    | _    | μs   | $V_{\rm S}$ = 13.5V<br>$T_{\rm j}$ = 25°C                                                                            | 6.1.33 |

| Status flag time while ON after Open Load event                                                      | $t_{\rm dOLONf1,2}$   | _    | 42    | -    | μs   | $V_{\rm S}$ = 13.5V<br>$T_{\rm j}$ = 25°C                                                                            | 6.1.34 |

| Status flag time while ON going out of Open Load                                                     | $t_{\rm dOLONr1,2}$   | _    | 10    | -    | μs   | $V_{\rm S}$ = 13.5V<br>$T_{\rm j}$ = 25°C                                                                            | 6.1.35 |

| Status Flag                                                                                          | •                     |      |       |      | 1    | -                                                                                                                    | •      |

| Status Drop Voltage when L                                                                           | $V_{\mathrm{STL1,2}}$ | _    | 200   | 400  | mV   | $I_{\rm ST1,2}$ = 3mA                                                                                                | 6.1.36 |

| Status Leakage Current when H                                                                        | $I_{\rm STLK1,2}$     | _    | -     | 10   | μΑ   | $V_{\rm ST1,2} = 7V$                                                                                                 | 6.1.37 |

| Undervoltage Lockout                                                                                 | •                     | 1    | •     | 1    |      |                                                                                                                      | •      |

| UV Switch ON Voltage                                                                                 | $V_{UVON}$            | 3.75 | 4.25  | 4.5  | V    | $V_{\rm S}$ increasing                                                                                               | 6.1.38 |

| UV Switch OFF Voltage                                                                                | $V_{UVOFF}$           | 3.25 | 3.75  | 4.25 | V    | $V_{\rm S}$ decreasing                                                                                               | 6.1.39 |

| UV ON/OFF Hysteresis                                                                                 | $V_{UVHY}$            | 0.2  | 0.5   | _    | V    | $V_{ m UVON}$ - $V_{ m UVOFF}$                                                                                       | 6.1.40 |

### **Electrical Characteristics**

- 1) Please refer to chapter "Protection Functions" on Page 7

- 2) No delay time after overtemparature switch off and short circuit in on-state.

## 7 Typical Performance Graphs

**Typical Performance Characteristics**

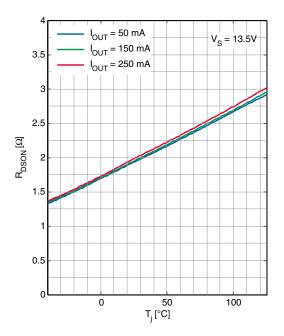

On-Resistance  $R_{\text{DSON}}$  versus Junction Temperature  $T_{\text{i}}$

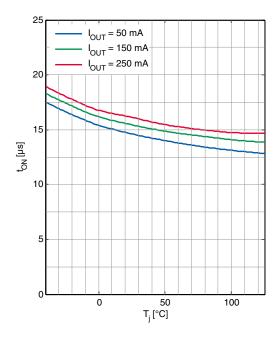

Switch ON Time  $t_{\text{ON}}$  versus Junction Temperature  $T_{\text{i}}$

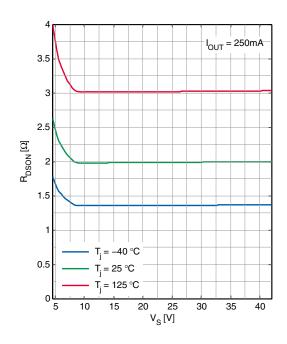

On-Resistance  $R_{\mathrm{DSON}}$  versus Supply Voltage  $V_{\mathrm{S}}$

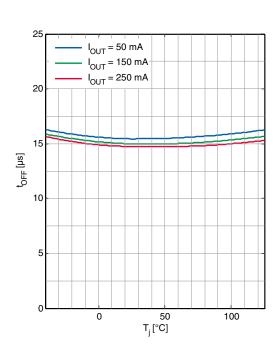

Switch OFF Time  $t_{\text{OFF}}$  versus Junction Temperature  $T_{\text{j}}$

### **Typical Performance Characteristics**

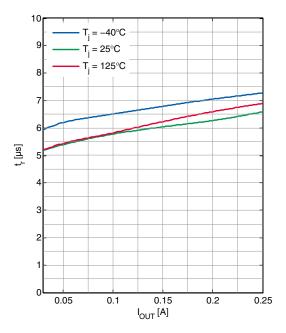

# Output Rise Time $t_{\rm r}$ versus Load Current $I_{\rm OUT}$

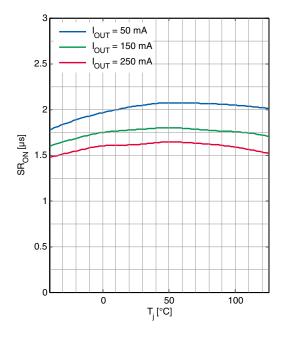

ON Slewrate  $SR_{ON}$  versus Junction Temperature  $T_{\rm i}$

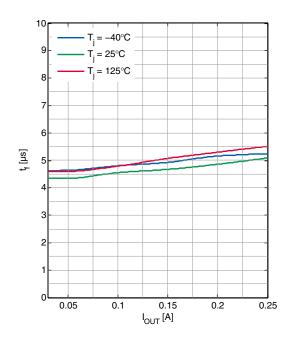

## Output Fall Time $t_{\rm f}$ versus Load Current $I_{\rm OUT}$

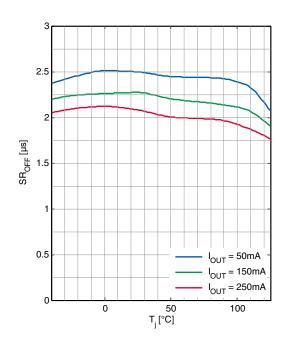

OFF Slewrate  $SR_{OFF}$  versus Junction Temperature  $T_i$

### **Typical Performance Characteristics**

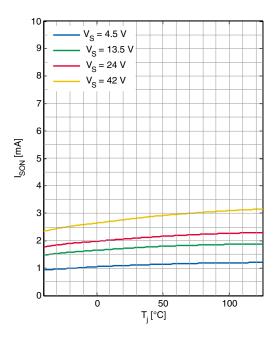

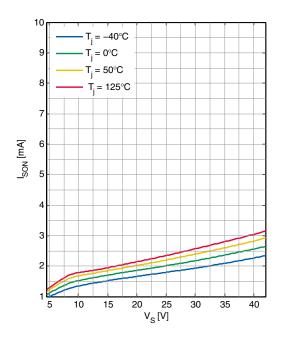

# ON Supply Current $I_{\rm SON}$ versus Junction Temperature $T_{\rm i}$

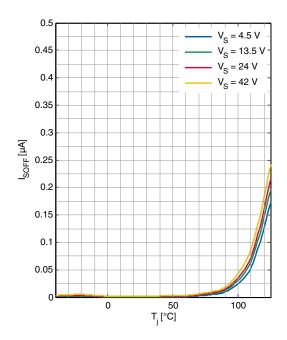

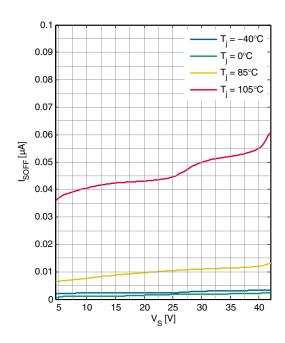

# Quiescent Current in OFF mode $I_{\mathrm{SOFF}}$ versus Junction Temperature $T_{\mathrm{i}}$

## ON Supply Current $I_{\mathrm{SON}}$ versus Supply Voltage $V_{\mathrm{S}}$

Quiescent Current in OFF mode  $I_{\mathrm{SOFF}}$  versus Supply Voltage  $V_{\mathrm{S}}$

### **Typical Performance Characteristics**

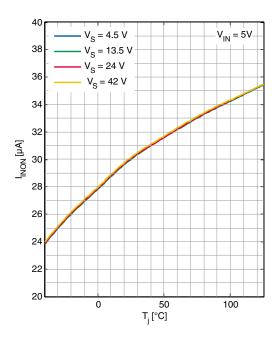

# Input Current Consumption $I_{\rm IN}$ versus Junction Temperature $T_{\rm i}$

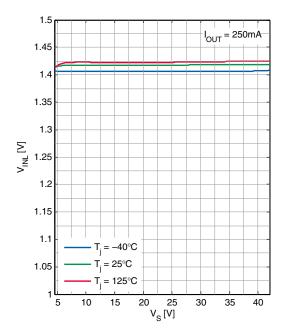

Input Threshold voltage  $V_{\mathrm{INL}}$  versus Supply Voltage  $V_{\mathrm{S}}$

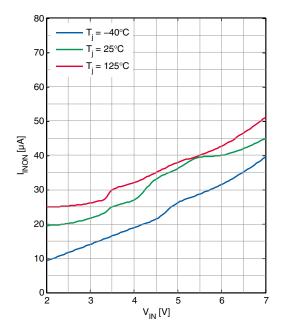

## Input Current Consumption $I_{\mathrm{IN}}$ versus Input voltage $V_{\mathrm{IN}}$

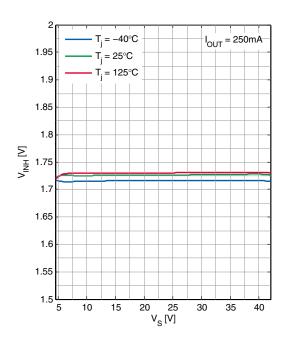

Input Threshold voltage  $V_{\rm INH}$  versus Supply Voltage  $V_{\rm S}$

### **Typical Performance Characteristics**

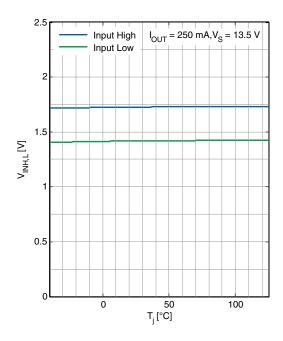

### Input Threshold voltage $V_{\mathrm{INH,L}}$ versus Junction Temperature $T_{\rm j}$

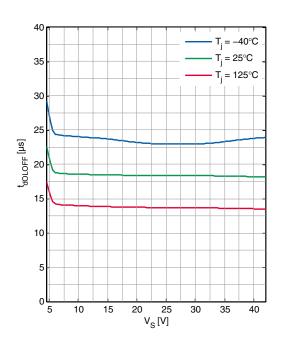

Status Flag Delay time in Open Load condition  $t_{ extsf{dOLOFF}}$  versus Supply Voltage  $V_{ extsf{S}}$

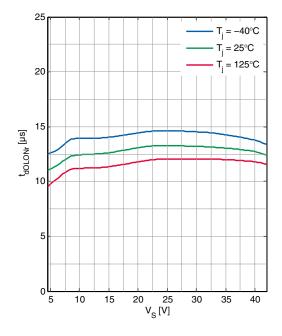

Status Flag Delay time while ON going out of Open Status Flag Delay time while ON after Open Load Load condition  $t_{\rm dOLONr}$  versus Supply Voltage  $V_{\rm S}$

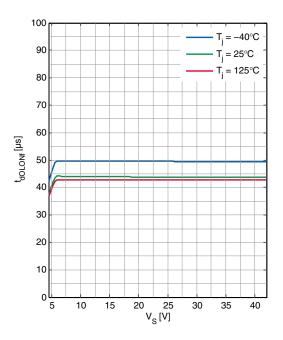

event  $t_{

m dOLONf}$  versus Supply Voltage  $V_{

m S}$

### **Typical Performance Characteristics**

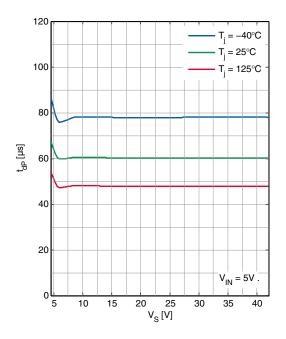

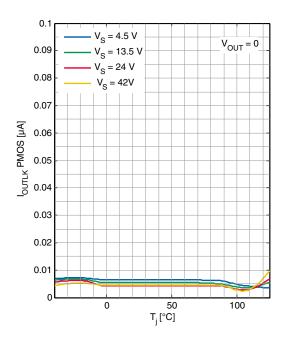

### Status Flag Delay time after positive slope $t_{ m dP}$ versus Output Leakage current $I_{ m OUTLK}$ (PMOS) versus Supply Voltage $V_{\mathtt{S}}$

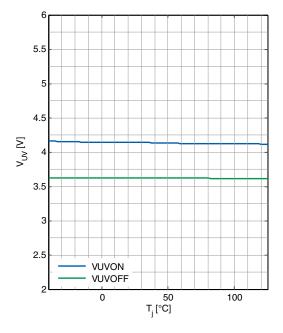

Under Voltage Lockout  $V_{\mathrm{UVON}},\,V_{\mathrm{UVOFF}}$  versus Junction Temperature  $T_{\rm i}$

## Junction Temperature $T_{\rm j}$

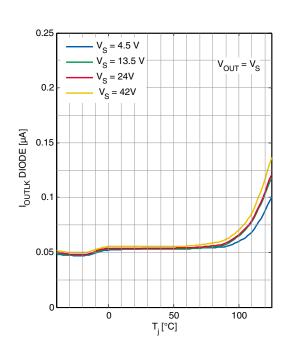

Output Leakage current  $I_{\mathsf{OUTLK}}$  (Diode) versus Junction Temperature  $T_i$

### **Typical Performance Characteristics**

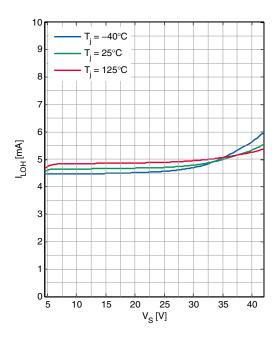

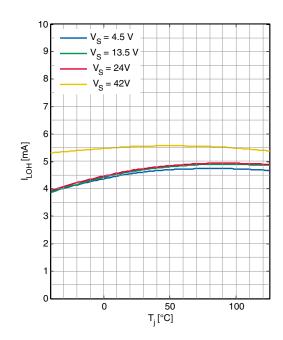

# Open Load Current Threshold $I_{\rm LOH} {\rm versus}$ Supply Voltage $V_{\rm S}$

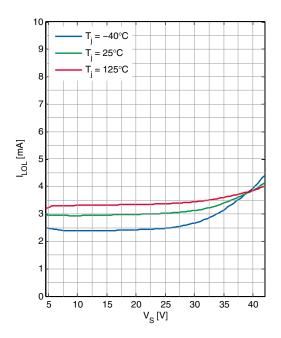

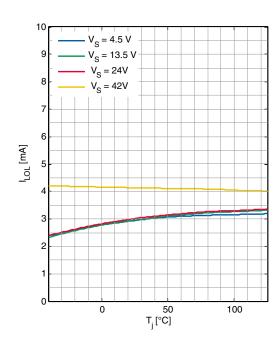

Open Load Current Threshold  $I_{\mathrm{LOL}}$  versus Supply Voltage  $V_{\mathrm{S}}$

# Open Load Current Threshold $I_{\mathrm{LOH}}$ versus Junction Temperature $T_{\mathrm{j}}$

Open Load Current Threshold  $I_{\rm LOL}$  versus Junction Temperature  $T_{\rm j}$

### **Typical Performance Characteristics**

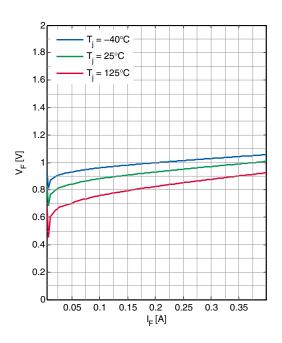

## Freewheeling diode forward voltage $V_{\rm F}$ versus Current $I_{\rm F}$

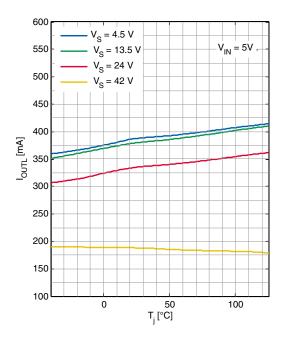

Output Current Limitation  $I_{\rm OUTL}$  versus Junction Temperature  $T_{\rm j}$

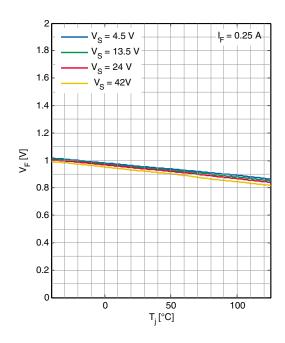

## Freewheeling diode forward voltage $V_{\rm F}$ versus Junction Temperature $T_{\rm i}$

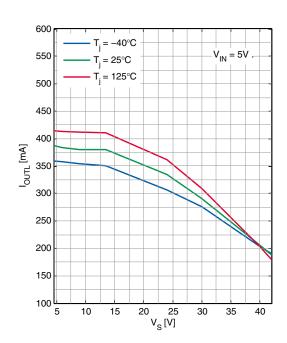

Output Current Limitation  $I_{\mathrm{OUTL}}$  versus Supply Voltage  $V_{\mathrm{S}}$

**Application Information**

## 8 Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

Figure 9 Application diagram ITS42k5D-LD-F

The ITS42k5D-LD-F can be connected via a reverse polarity diode to a supply network. It is recommended to place a ceramic capacitor (e.g.  $C_{\rm S}$  = 220nF) between supply voltage VS and GND of the module to avoid line disturbances. Wire harness inductors/resistors are sketched in the application circuit above.

The complex loads (resistive, capacitive or inductive) must be connected to the output pins OUT1 and OUT2.

A built-in current limit protects the device against destruction.

The ITS42k5D-LD-F can be switched on and off with standard logic ground related logic signals at pin IN1 and IN2. In standby mode (IN1=IN2=L) the ITS42k5D-LD-F is deactivated with very low current consumption.

The output voltage slope is controlled during on and off transition to minimize emissions. Only a small ceramic capacitor COUT1,2 = 1nF is recommended to attenuate RF noise.

An evaluation board is available for the easy evaluation of the ITS42k5D-LD-F. Please refer to the Evaluation Board Finder under Tools on the Infineon webpage.

**Application Information**

### 8.1 Thermal Considerations

The kind of PCB required for an application can be easily derived if the ambient temperature of the application, in which the ITS42k5D-LD-F is being used, is known.

Let us assume the following application conditions with both channels active:

$I_{OUT}$  = 250 mA (Given by application, load dependent)

$R_{\rm DSON,Max}$  = 8  $\Omega$  (Worst case scenario considered)

$T_A$  = 60 °C (Ambient Temperature, given by application)

$T_{i,max}$  = 125°C as given under "Functional Range" on Page 13

$$P_D = I_{OUT}^2 \times R_{DSON}$$

Applying the formula given above, one can calculate the power dissipation  $P_{\rm D}$  in the application, which for our application scenario i.e. 0.5W for one channel active and 1W for both channels active.

Furthermore, we know that

$$R_{thJA, Max} = \frac{T_{j, max} - T_A}{P_D}$$

Hence we can calculate  $R_{\text{thJA},\text{Max}}$ , which for this application scenario is 65K/W. As a result, the PCB design must ensure a thermal resistance of lower than 65K/W for the above mentioned application assumption. According to "Thermal Resistance" on Page 13, at least a 300mm<sup>2</sup> heatsink area is needed on a FR4 1s0p PCB or the FR4 2s2p board with thermal vias could be used for this application.

For support regarding thermal considerations, please contact us via our support webpage www.infineon.com\support.

For further support, please refer to application notes on the Infineon website www.infineon.com.

**Package Outlines and Footprint**

## 9 Package Outlines and Footprint

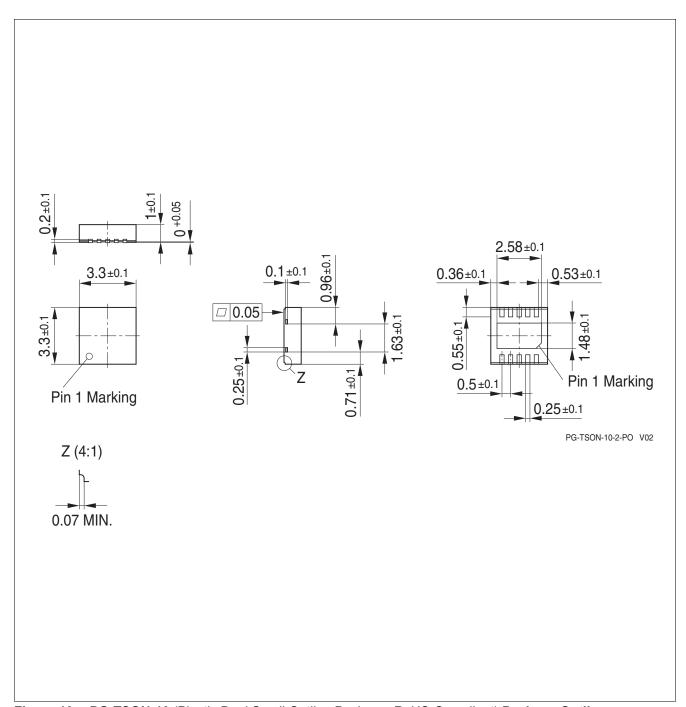

## 9.1 PG-TSON-10 Package Outline

Figure 10 PG-TSON-10 (Plastic Dual Small Outline Package, RoHS-Compliant) Package Outline

**Package Outlines and Footprint**

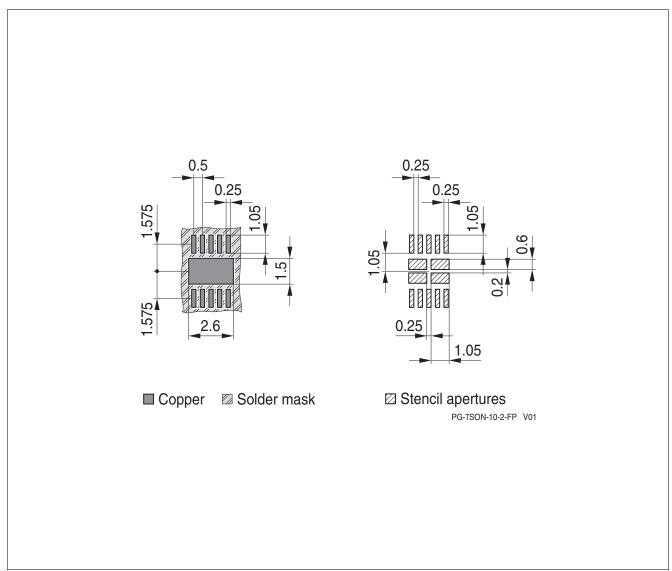

### 9.2 PG-TSON-10 Footprint

Figure 11 PG-TSON-10 (Plastic Dual Small Outline Package, RoHS-Compliant) Package Footprint

### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further information on alternative packages, please visit our website: <a href="http://www.infineon.com/packages">http://www.infineon.com/packages</a>.

Dimensions in mm

**Revision History**

## 10 Revision History

| Revision | Date       | Changes                     |

|----------|------------|-----------------------------|

| Rev 1.0  | 2015-04-28 | Datasheet - Initial Version |

**Edition 2015-04-28**

Published by Infineon Technologies AG 81726 Munich, Germany © 2015-04-28 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

The Infineon Technologies component described in this Data Sheet may be used in life-support devices or systems and/or automotive, aviation and aerospace applications or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support automotive, aviation and aerospace device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon:

ITS42K5DLDFXUMA1

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А