# BridgeSwitch Family

High-Voltage, Self-Powered, Half-bridge Motor Driver with Integrated Device Protection and System Monitoring

# Product Highlights

#### **Highest Performance and Design Flexibility**

- Fully integrated half-bridge stage with up to 98% efficiency

- Eliminates external heat sink at rated continuous RMS current

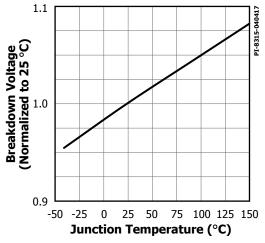

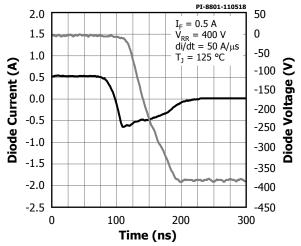

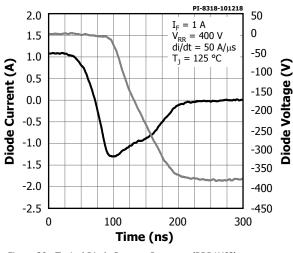

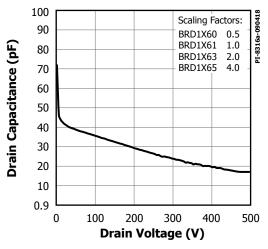

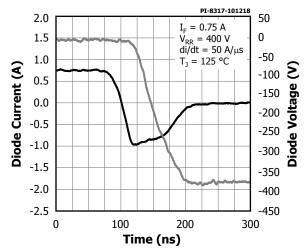

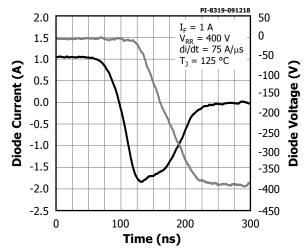

- 600 V N-channel power FREDFETs

- Ultra-soft, fast recovery diode

- Accurate instantaneous phase current information output (BRD126X)

Eliminates external sensing and amplification circuitry

- Eliminates external sensing and amplifica

Self-biased low-side and high-side drivers

- Eliminates need for auxiliary power supply

- Small footprint surface mount inSOP-24C package

- Exposed pads enable heat sinking through PCB

- Controlled FREDFET switching speed reduces EMI

#### **Enhanced Safety and Reliability Features**

- Adustable cycle-by-cycle current limit for both FREDFETs

Fail-safe operation

- Internal dual level thermal overload protection

- Self-configuring system level monitoring input

- Four level DC bus undervoltage

- Four level DC bus undervoitage

- DC bus overvoltageSystem temperature

- System temperature

- Adaptive dead time

- Simultaneous conduction lockout protection

#### **Status Interface**

- Bi-directional bussed open Drain single wire interface

- Reports status updates to system MCU

- Successful power-up

- Internal over-current or temperature faults

- System level faults

- Includes device identification

- Status query through system MCU

- Device fault reset through system MCU

#### Applications

- 2- or 3-phase high-voltage PM and BLDC motor drives

- Up to 300 W typical inverter output power

- Appliances including dish washers and refrigerators

- Condenser fans in high efficiency air conditioners

### Description

The BridgeSwitch<sup>™</sup> family of integrated half-bridges dramatically simplifies the development and production of high-voltage inverter driven 2- or 3-phase PM or BLDC motor drives. It incorporates two high-voltage N-channel power FREDFETs with low and high-side drivers in a single small-outline package. The internal power FREDFETs offer ultra-soft and ultrafast diodes ideally suited for hard switched inverter drives. Both drivers are self-supplied eliminating the need for an external auxiliary power supply. BridgeSwitch provides a unique instantaneous phase current output signal simplifying implementation of sensor-less control schemes. The low-profile, compact footprint surface mount package offers extended creepage distances and allows heat sinking of both power FREDFETs through the printed circuit board.

BridgeSwitch offers internal fault protection functions and external system level monitoring. Internal fault protection includes cycle-by-

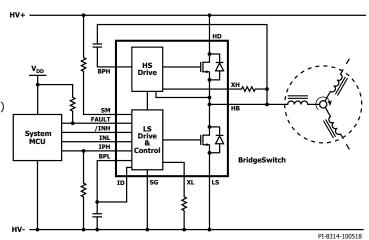

Figure 1. Typical 3-Phase Inverter Schematic (BRD126X).

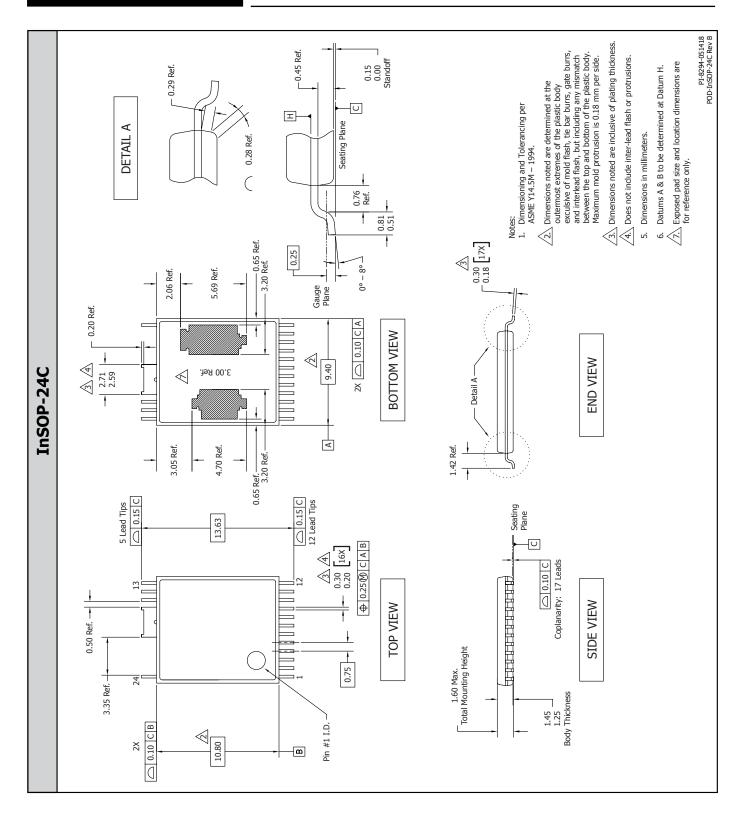

Figure 2. InSOP-24C Package (Top and Bottom Sides).

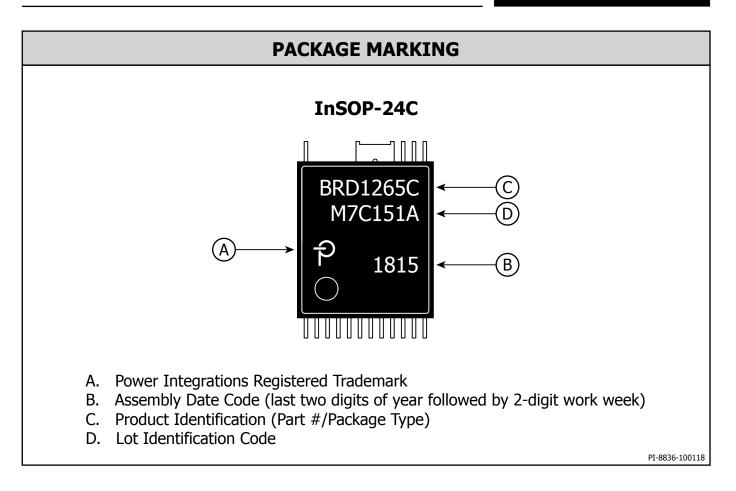

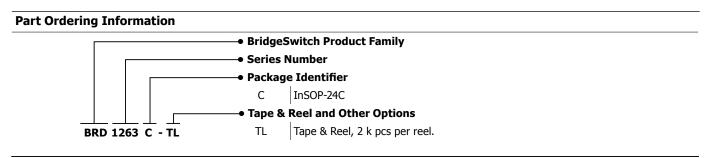

#### **Product Family**

|                        | •                                 |                                        |

|------------------------|-----------------------------------|----------------------------------------|

| Product <sup>3</sup>   | DC Output<br>Current <sup>1</sup> | Continuous<br>RMS Current <sup>2</sup> |

| BRD1160C /<br>BRD1260C | 1.0 A                             | 0.22 A                                 |

| BRD1161C /<br>BRD1261C | 1.7 A                             | 0.50 A                                 |

| BRD1163C /<br>BRD1263C | 3.0 A                             | 0.75 A                                 |

| BRD1165C /<br>BRD1265C | 5.5 A                             | 1.00 A                                 |

Table 1. Product Family.

Notes:

- 1. Continuous DC output current per FREDFET, calculated at 25 °C case and 125 °C junction temperature. Normally limited by internal circuitry

- Continuous phase RMS current, internal self-supply, 340 V bus, trapezoidal commutation with 12 kHz high-side PWM, PCB heat sinking with 50 °C case temperature rise.

- 3. Package: InSOP-24C.

cycle current limit for both FREDFETs and two level thermal overload protection. External system level monitoring includes DC bus sensing with four undervoltage levels and one overvoltage level as well as driving external sensors such as an NTC. The bi-directional bussed single wire status interface reports observed status changes.

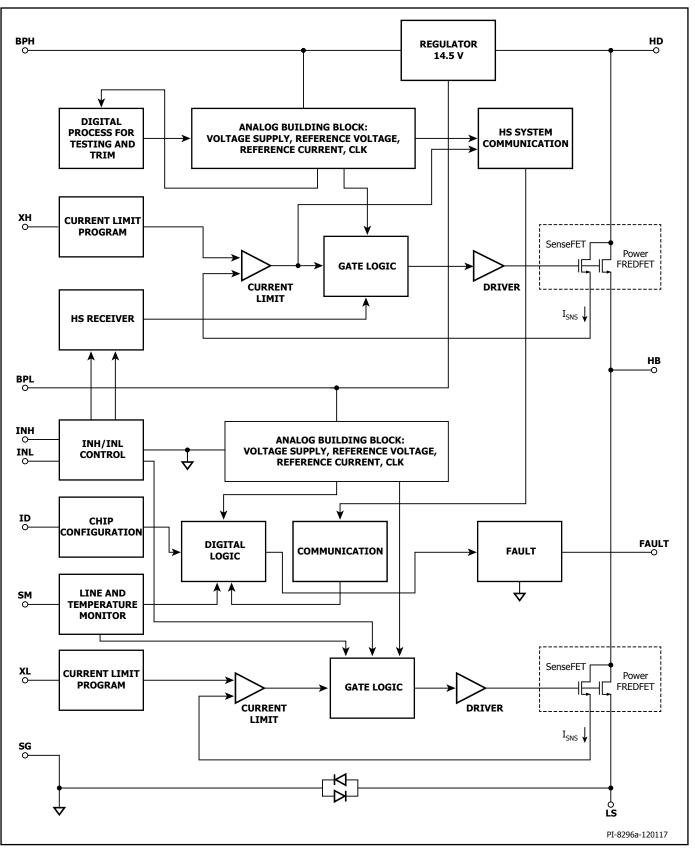

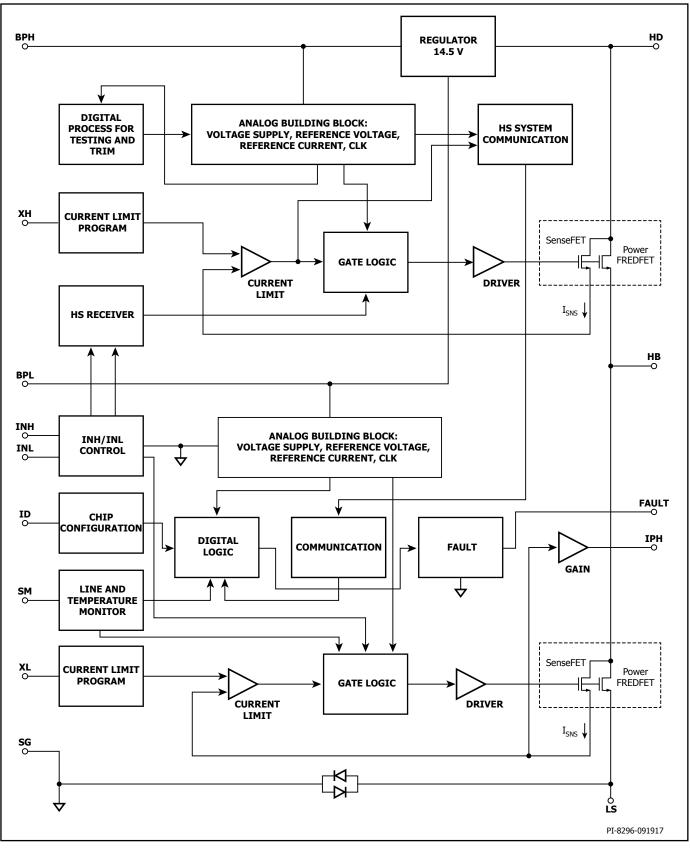

Figure 4. Functional Block Diagram BRD126X.

# **Pin Functional Description**

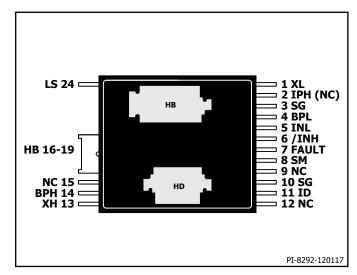

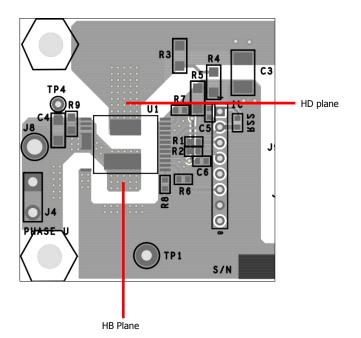

### HIGH-SIDE DRAIN (HD) Exposed Pad

The HD exposed pad is the electrical connection to the high-side power FREDFET Drain connection. It is also the input for the internal low-side and high-side self-supply circuitry.

#### EXTERNAL CURRENT LIMIT LOW-SIDE (XL) Pin (Pin 1)

This pin connects to a resistor to set the cycle-by-cycle current limit for the low-side power FREDFET.

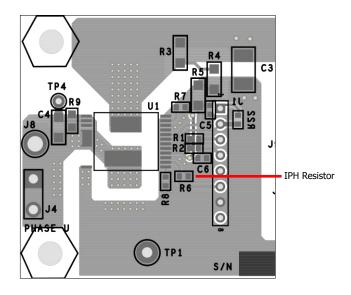

#### PHASE CURRENT OUTPUT (IPH) Pin (Pin 2, BRD126X)

This pin connects to a small signal resistor and provides low-side FREDFET Drain current information. The pin should be left floating if the function is not used. Function is not available with BRD116X.

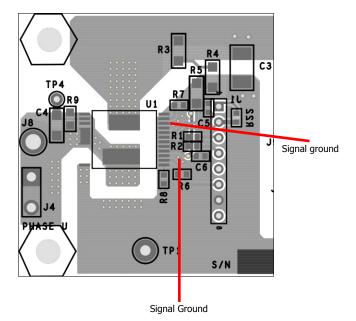

#### SIGNAL GROUND (SG) Pin (Pins 3 and 10)

These pins are the ground reference connection for low-side controller small signal pins and the system micro-controller.

### BYPASS LOW-SIDE (BPL) Pin (Pin 4)

This pin connects to the external bypass capacitor for the low-side controller and FREDFET Gate driver.

#### CONTROL INPUT LOW-SIDE (INL) Pin (Pin 5)

Active high logic level control input for the low-side power FREDFET.

#### CONTROL INPUT HIGH-SIDE (/INH) Pin (Pin 6)

Active low logic level control input for the high-side power FREDFET.

## STATUS COMMUNICATION (FAULT) Pin (Pin 7)

This open Drain pin connects to an I/O port of the system microcontroller to provide a status update. The pin should be connected to SIGNAL GROUND if the function is not used.

#### SYSTEM MONITOR (SM) Pin (Pin 8)

This pin is a self-configuring system monitor input. It configures itself into a high-voltage bus sense input if a resistor is connected to the high-voltage bus at power-up. It configures itself into an external temperature sense input if a resistance is connected to SYSTEM GROUND at power-up. The pin should be connected to SIGNAL GROUND if the function is not used.

#### DEVICE ID (ID) Pin (11)

This pin programs the device ID at power-up.

Figure 5. Pin Configuration (Bottom View).

#### **EXTERNAL CURRENT LIMIT HIGH-SIDE (XH) Pin (Pin 13)**

This pin connects to a resistor to set the cycle-by-cycle current limit for the high-side power FREDFET. The resistor is referenced to HALF BRIDGE CONNECTION.

#### BYPASS HIGH-SIDE (BPH) Pin (Pin 14)

This pin connects to the external bypass capacitor for the high-side FREDFET Gate driver. The capacitor is referenced to HALF BRIDGE CONNECTION.

#### HALF-BRIDGE CONNECTION (HB) (Pin 16-19)

This pin connects to the Source of the high-side power FREDFET and to the Drain of the low-side power FREDFET. It is also the reference for the BYPASS HIGH-SIDE and the EXTERNAL CURRENT LIMIT HIGH-SIDE pins.

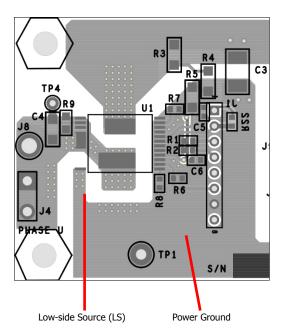

# LOW-SIDE SOURCE (LS) (Pin 24)

This pin is the low-side power FREDFET Source connection. It connects to the SIGNAL GROUND through a Kelvin connection.

#### NOT CONNECTED (NC) Pins (Pins 2 (BRD116X only) 9, 12, 15)

This pin is not connected and should be left floating. Pin 2 only applies to BRD116X.

# **BridgeSwitch Functional Description**

BridgeSwitch combines two high-voltage power FREDFETs, gate drivers and controllers into a single package. The FREDFETs are connected in a half-bridge configuration where their diode structure (ultra-soft and ultra-fast recovery) makes them ideal for hardswitched inverter-based motor drivers.

To reduce external components, the drive controllers feature integrated high-voltage current sources, allowing them to draw current directly from the high-voltage DC Bus. The high-side controller provides high-side status updates to the low-side controller which generates an instantaneous phase-current output signal (BRD126X). This unique capability allows the implementation of a sensor-less motor-control scheme. The controllers also ensure that the FREDFET turn-off is faster than turn-on resulting in an optimal balance between thermal performance and EMI.

BridgeSwitch offers integrated fault protection and system level monitoring via a bi-directional bussed single-wire status interface. Internal fault protection includes cycle-by-cycle current limit for both FREDFETs as well as two-level thermal overload protection. BridgeSwitch offers sophisticated DC-bus sensing, providing four undervoltage levels and one overvoltage level, and can also support external sensors such as an NTC. Figure 3 shows the functional block diagram of the device along with key features.

#### BYPASS LOW-SIDE Pin and HIGH-SIDE Pin Regulator

The BYPASS LOW-SIDE pin and the BYPASS HIGH-SIDE pin have internal regulators that charge the BYPASS LOW-SIDE pin capacitor and the BYPASS HIGH-SIDE pin capacitor to  $V_{\rm BPL}$  and  $V_{\rm BPH}$ , respectively. A current source connected to HIGH-SIDE DRAIN charges the BYPASS LOW-SIDE capacitor. Another current source connected to HIGH-SIDE DRAIN charges the BYPASS HIGH-SIDE capacitor whenever the low-side power FREDFET turns on. Both current sources start charging once the HD pin voltage reaches  $V_{\rm HD(START)}$  (min. 50 V). The BYPASS LOW-SIDE and the BYPASS HIGH-SIDE pins are the internal supply voltage nodes for the low-side and the high-side controllers and Gate drivers. When the low-side or the high-side power FREDFETs are on, the device operates from the energy stored in the BYPASS LOW-SIDE pin capacitor or the BYPASS HIGH-SIDE pin capacitor, respectively.

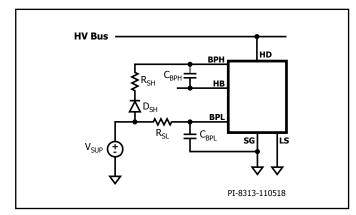

In addition, there are shunt regulators clamping the BYPASS LOW-SIDE pin to V\_{BPL(SHUNT)} and the BYPASS HIGH-SIDE pin to V\_{BPH(SHUNT)} when current is provided to the BYPASS LOW-SIDE pin and the BYPASS HIGH-SIDE pin from an external DC source through resistors (see

Figure 6. External BPL Pin and BPH Pin Power Supply Example.

$\rm R_{_{SL}}$  and  $\rm R_{_{SH}}$  in Figure 6). External supply voltage  $\rm V_{_{SUP}}$  is greater than bypass shunt regulator voltage  $\rm V_{_{BPX(SHUNT)}}$  plus the voltage drop of bootstrap diode  $\rm D_{_{SH}}$ . A typical value is  $\rm V_{_{SUP}}=17$  V. Resistors  $\rm R_{_{SL}}$  and  $\rm R_{_{SH}}$  limit the external supply current to less than 12 mA (2-5 mA recommended). Shorting BPL pins or BPH pins from separate devices directly together is not recommended.

#### BYPASS LOW-SIDE Pin and HIGH-SIDE Pin Undervoltage Threshold

The BYPASS LOW-SIDE pin and BYPASS HIGH-SIDE pin undervoltage circuitries disable the respective power FREDFET when either the BYPASS LOW-SIDE pin voltage or the BYPASS HIGH-SIDE pin voltage drops below V<sub>BPI</sub>-V<sub>BPL(HYST)</sub> or V<sub>BPH</sub>-V<sub>BPH(HYST)</sub>, respectively, in steady-state operation. Once either the BYPASS LOW-SIDE pin voltage or the BYPASS HIGH-SIDE pin voltage fall below this threshold, it must rise back up to V<sub>BPL</sub> or V<sub>BPH</sub>, respectively to enable power FREDFET switching.

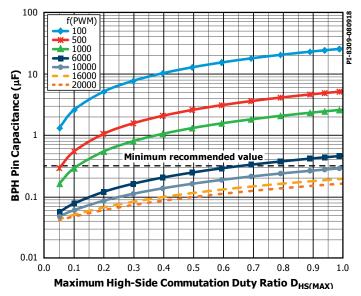

#### BYPASS LOW-SIDE Pin and HIGH-SIDE Pins Capacitor Selection

Capacitors connected to the BYPASS LOW-SIDE pin and BYPASS HIGH-SIDE pin supply bias current for the low-side and the high-side controller and deliver the required Gate charge for turning on the low-side or the high-side power FREDFET. The BYPASS HIGH-SIDE pin capacitor supplies the high-side controller bias current over a time interval which is a function of the high-side commutation duty ratio and PWM frequency. The recommended maximum voltage ripple at the BYPASS HIGH-SIDE pin capacitor over this time interval is 250 mV. The minimum required capacitance value for both bypass low-side and bypass high-side is 0.33  $\mu$ F. The recommended bypass low-side capacitance is 1  $\mu$ F.

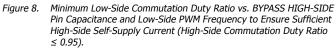

Given application operating conditions determine the required bypass high-side capacitance to keep ripple voltage below 250 mV. Figure 7 depicts the minimum recommended BYPASS HIGH-SIDE pin capacitance as function of high-side commutation duty ratio  $\rm D_{HS}$  and PWM frequency.

Figure 7. BYPASS HIGH-SIDE Pin Capacitance vs. High-Side Commutation Duty Ratio and PWM Frequency.

Note that multilayer chip capacitors (MLCC) can exhibit a significant DC bias characteristic. Selecting a BYPASS HIGH-SIDE pin capacitor (according to Figure 7) needs to take the possible capacitance reduction into account when biasing at  $V_{\rm BPH}$ . Refer to the respective capacitor data sheet for details.

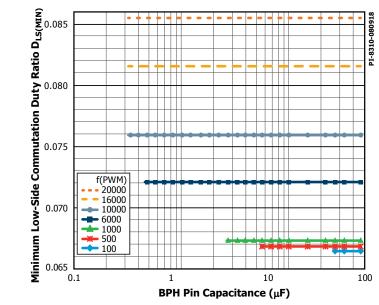

The BYPASS HIGH-SIDE pin capacitor recharges every time the low-side power FREDFET turns on. To ensure sufficient high-side self-supply current, the low-side power FREDFET on-time, as a function of chosen BYPASS HIGH-SIDE capacitance, low-side commutation duty ratio  $\mathrm{D}_{\mathrm{LS}}$  and PWM frequency, should meet the minimum low-side commutation duty ratio requirement  $D_{LS(MIN)}$  shown in Figure 8. Note the maximum recommended voltage ripple of 250 mV across the bypass high-side capacitor restricts the choice of possible capacitance values at lower PWM frequencies.

Minimum low-side commutation duty ratio  $\mathrm{D}_{\mathrm{LS(MIN)}}$  depicted in Figure 8 scales with the applicable maximum high-side commutation duty ratio in a given application. For example, the minimum low-side commutation duty ratio  $\rm D_{\rm LS(MIN)}$  in an application operating at  $\rm f_{\rm PWM}$  = 6 kHz and a maximum high-side commutation duty ratio of  $D_{HS(MAX)} = 0.95$  is  $D_{LS(MIN)} = 0.0435$ .  $D_{LS(MIN)}$  increases by a factor of 0.99/0.95 to  $D^*_{LS(MIN)} = 0.0453$  if the same application operates for instance at a maximum high-side duty ratio of  $D^*_{HS(MAX)} = 0.99$ .

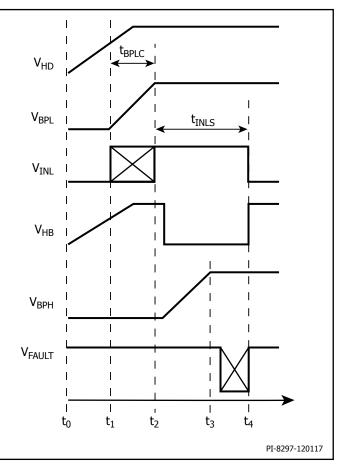

Figure 9. Recommended Power-Up Sequence with Self-supplied Operation.

| Time Point     | Activity                                                                                                                                                                                                                                                                                                                                                 |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>o</sub> | High-voltage DC bus is applied                                                                                                                                                                                                                                                                                                                           |

| t,             | <ul> <li>Internal current source starts charging BPL pin capacitor once HD pin voltage reaches V<sub>HD(START)</sub></li> <li>System MCU may start setting low-side power FREDFET control signal INL to high</li> </ul>                                                                                                                                  |

| t <sub>2</sub> | <ul> <li>BPL pin voltage reaches V<sub>BPL</sub> (typically 14.5 V)</li> <li>Device determines external device settings</li> <li>Internal Gate drive logic turns on low-side power FREDFET after device setup completes and once INL becomes high or if it is high already</li> <li>Internal current source starts charging BPH pin capacitor</li> </ul> |

| t <sub>3</sub> | <ul> <li>BPH pin voltage reaches V<sub>BPH</sub> with respect to HB pin (typically 14.5 V).</li> <li>Device starts communicating successful power-up through FAULT pin.<br/>Note: The device does not send a status update if the internal power-up sequence did not complete successfully.</li> </ul>                                                   |

| t <sub>4</sub> | <ul> <li>BridgeSwitch is ready for state operation (indicated by communicated status update starting at time point t<sub>3</sub>)</li> <li>System MCU turns off low-side power FREDFET</li> </ul>                                                                                                                                                        |

Table 2. Power-Up Sequence with Self-Supplied Operation.

#### Power-Up Sequence with Self-Supply

BridgeSwitch devices have internal self-supply supporting commutation PWM frequencies up to 20 kHz. To ensure a sufficient supply voltage levels across the BYPASS LOW-SIDE pin capacitor and the BYPASS HIGH-SIDE pin capacitor at inverter start-up, the system micro-controller (MCU) should follow the recommended power-up sequence depicted in Figure 9.

Table 2 lists activities occurring during the recommended power-up sequence.

The BYPASS LOW-SIDE pin capacitor  $C_{_{\rm BPL}}$ , the BPL pin charge current  $I_{_{\rm CH1(LS)}}$ , and the BYPASS LOW-SIDE pin voltage  $V_{_{\rm BPL}}$  determine the charging time  $t_{_{\rm BPLC}}$  starting at time point t1:

$$t_{\rm BPLC} = t_2 - t_1 = \frac{C_{\rm BPL} \times V_{\rm BPL}}{I_{\rm CH1(LS)}}$$

The system MCU manages the power-up sequence by controlling the time point t2 and duration t<sub>INLS</sub> for turning on and off the low-side power FREDFET. The MCU may pull the CONTROL INPUT LOW-SIDE pin high any time after the full DC bus voltage is available (time point t<sub>1</sub>). However, the device enables power MOSEFT switching only after the BYPASS LOW-SIDE pin voltages reaches V<sub>BPL</sub> (typically 14.5 V) and the device setup completes. The device also reports a first status update through the FAULT pin once V<sub>BPL</sub> reached typically 14.5 V

The high-side controller reports internally its status to the low-side controller at time point t3 after the BYPASS HIGH-SIDE pin voltage reaches  $V_{\text{BPH}}$  (typically 14.5 V) with respect to the HALF-BRIDGE CONNECTION pin. This is followed by a device status update to the system MCU through the STATUS COMMUNICATION pin.

A minimum low-side FREDFET on-time  $t_{_{\rm INLS}}$  is required for charging the BYPASS HIGH-SIDE pin capacitor, device setup, and status update communication through the FAULT pin. It is controlled by the system MCU and depends on the selected capacitance CBPH:

$$t_{\text{INLS}} = t_4 - t_2 \ge \frac{\mathbf{C}_{\text{BPH}} \times \mathbf{V}_{\text{BPH}}}{I_{CH1(\text{HS})}} + 1 \text{ ms}$$

The system MCU should proceed with the power-up sequence described above, if a latching thermal shutdown had occurred and it decides to restart the inverter by first sending a FAULT latch reset command (see Table 7 for details).

#### **Gate Drive Control Inputs**

The low-side and high-side power FREDFETs are controlled through INL and /INH logic inputs. Both inputs are compatible with 3.3 V and 5 V CMOS logic levels. The low-side power FREDFET latches on or off

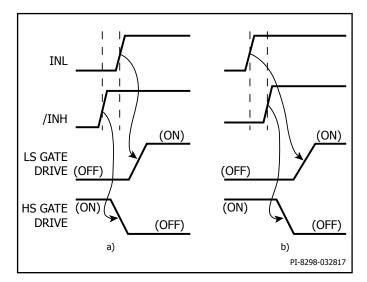

Figure 10. Simultaneous Conduction Lockout a) Not Active b) Active.

with the edge of the active high INL signal during steady-state operation. The high-side power FREDFET latches on or off with the edge of the active low /INH signal. The INL input has an internal weak pull-down and the /INH input has an internal weak pull-up. This prevents accidental power FREDFET turn-on in case one or both control inputs are floating.

BridgeSwitch integrates simultaneous conduction lockout protection. A latch inhibits turning on the low-side power FREDFET Gate drive circuitry until the rising edge of the high-side control signal /INH has occurred (see Figure 10). The latch also inhibits turning on the high-side power FREDFET Gate drive circuitry until the falling edge of the low-side control signal INL has occurred.

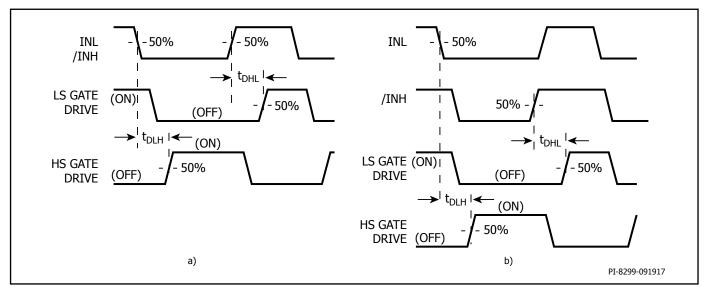

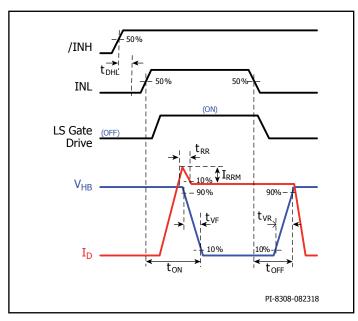

The inverse logic polarity of INL and /INH control inputs allows optionally tying both together for controlling both power FREDFETs with a single PWM signal. To prevent possible FREDFET cross conduction, the integrated Gate drive logic applies adaptive dead times as shown in Figure 11. The falling edge of the low-side power FREDFET control input INL triggers the  $t_{_{DLH}}$  timer (Dead Time low-side power FREDFET off to high-side power FREDFET on). The integrated Gate control logic enables turning on the high-side FREDFET Gate drive only after  $t_{_{DLH}}$  expires. The rising edge of the high-side power FREDFET control input /INH triggers the  $t_{_{DHL}}$  timer (Dead Time high-side power FREDFET off to low-side power FREDFET on). The integrated Gate control input /INH triggers the  $t_{_{DHL}}$  timer (Dead Time high-side power FREDFET off to low-side power FREDFET on). The integrated Gate control logic enables turning on the low-side FREDFET Gate drive only after  $t_{_{DH}}$  expires.

Figure 11. Adaptive Dead Time a) INL and /INH Inputs Tied Together b) INL and /INH Inputs Separate.

#### **Device Internal High-Side Status Update**

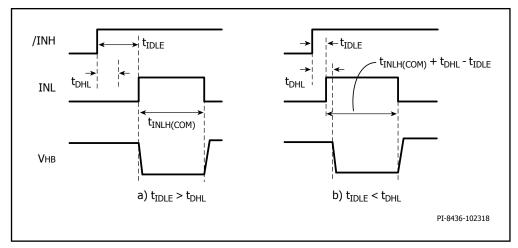

The BridgeSwitch high-side controller provides status updates to the low-side controller. The status update communicates triggered device level protection such as high-side power FREDFET over current or low-side power FREDFET over-temperature warning or shutdown. It also includes detected device faults such as XH pin short or open circuit and loss of high-side power supply. The high-side controller provides the internal status update every time the low-side power FREDFET turns on. For correct internal status updates, the system micro-controller has to set the INL control input high for at least  $t_{INLH(COM)}$  (see Figure 24 for details). INL input turn-on control signals shorter than  $t_{INHL(COM)}$  may cause incomplete internal status updates followed by the device reporting a "HS Driver not ready" status update (see Table 4).

#### Adjustable Cycle-by-Cycle Current Limit

BridgeSwitch devices feature cycle-by-cycle current limit protection for both, the low-side and the high-side power FREDFET. As soon as the power FREDFET current exceeds the respective current limit level threshold after the leading edge blanking timer  $t_{LEB}$  expires, the device turns off the power FREDFET. The FREDFET stays off until a turn-off edge followed by a turn-on edge is received at the respective INL or /INH control input. The device will also report the respective over-current fault through the STATUS COMMUNICATION pin (see Table 4 for details).

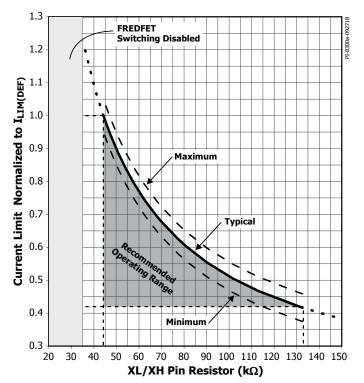

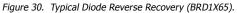

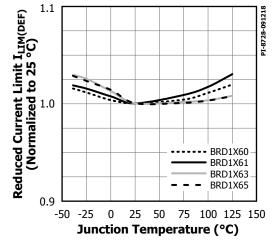

The actual current limit level is programmed through the external small signal resistor  $R_{_{XL}}$  or  $R_{_{XH}}$  (see Figure 1) connected to either the EXTERNAL CURRENT LIMIT LOW-SIDE pin or to the EXTERNAL CURRENT LIMIT HIGH-SIDE pin. Figure 12 shows the relationship between the resistor connected to XL pin or XH pin and the programmed normalized current limit level normalized to the default current limit level  $I_{_{LIM(DEF)}}$ .

The recommended operating range for the actual set current limit level is 42% to 100% of  $I_{\text{LIM(DEF)}}$  and a resistance range for  $\text{R}_{\text{XL}}$  or  $\text{R}_{\text{XH}}$  of 44.2 k $\Omega$  to 133 k $\Omega.$

FREDFET switching is disabled for  $R_{xL}$  or  $R_{xH}$  values smaller than 35 k $\Omega$  and the device reports either a LS driver not ready or a HS driver not ready status update through the FAULT pin (refer to Table 4). This prevents inverter malfunction in case the programming resistor is accidentally short-circuited. The device continues to accept LS FREDFET turn-on signals in case it detects a short-circuit at the XH pin.

A detected short-circuit at the XL pin will eventually cause the HS FREDFET switching to cease as well because the BPH pin capacitor is only re-charged when the LS FREDFET turns on. The normalized current limit level continues to fall below 42% down to 0% of  $I_{\text{LIM(DEF)}}$  for  $R_{\text{XL}}$  or  $R_{\text{XH}}$  values greater than 133 k $\Omega$ . This provides protection against possible XL pin or XH pin open circuit faults where the effective current limit threshold is 0. However, below 42% the specified current limit level tolerance is not guaranteed.

Adding capacitors to the XL pin or XH pin is not recommended.

#### **Device Over-Temperature Protection**

BridgeSwitch devices feature an integrated dual level thermal overload protection. The device continuously monitors the temperature of the low-side power FREDFET. It will send a status update through the STATUS COMMUNICATION pin as soon as it reaches the lower Device Warning Temperature level  $T_{WA}$  (see Table 4 for details). The device disables FREDFET switching permanently once the FREDFET temperature exceeds the Device Shutdown Temperature threshold  $T_{SD}$  to prevent device damage. Additionally it will report the over-temperature fault through the FAULT pin. System level monitoring through the SYSTEM MONITOR pin continues and the device will report any additionally occurring status changes through the STATUS COMMUNICA-TION pin. The system MCU can re-enable FREDFET switching by sending the fault latch reset command through the FAULT bus (see Table 7 for details). Alternatively operation may resume after a full power-up sequence initiated by the system MCU.

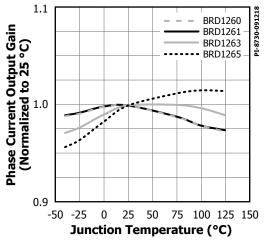

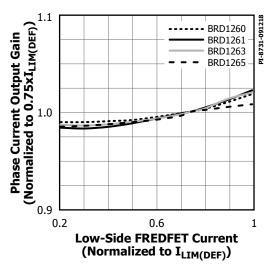

#### **Phase Current Information Output**

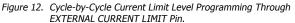

BridgeSwitch BRD126X devices feature instantaneous motor winding phase current information through a resistor connected to the PHASE CURRENT OUTPUT pin. The voltage across the small signal resistor is a direct representation of the low-side power FREDFET Drain to Source channel current. The system MCU can digitize this voltage and use it for instance as an input for a chosen motor control algorithm. The device supports either independent phase current information through individual IPH pin resistors or a composite phase current signal through interconnected IPH pins with a single resistor as shown in Figure 13.

Figure 13. Phase Current Information through IPH Pin with BRD126X a) Individual Phase Currents b) Composite Phase Current.

The Phase Current Output Gain  $g_{\rm IPH}$  and the resistor  $R_{\rm IPH}$  connected to the PHASE CURRENT OUTPUT determine the voltage amplitude  $V_{\rm IPH}$  at a given phase current  $I_{\rm PHASE}$ :

$$V_{IPH} = R_{IPH} \times I_{PHASE} \times g_{IPH}$$

Maximum permissible voltage amplitude of  $V_{\text{TPH}}$  is 3.0 V.

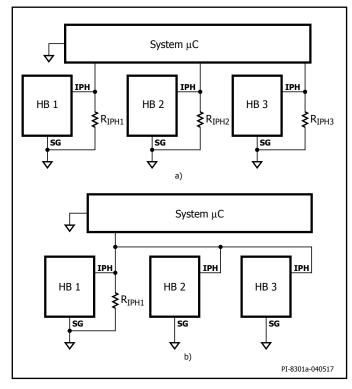

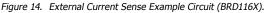

#### **External Current Sensing**

BRD116X devices support discrete low-side FREDFET current sensing through an external current sense resistor in series with the LS pin. Figure 14 depicts one possible implementation example.

Voltage V<sub>SHUNT</sub> is a direct representation of the motor winding current I<sub>MOTOR</sub>. Resistor R1 and R2 set the gain of external amplifier U1. Resistor R3, C1, C2, and C3 provide noise filtering. Resistor R4 adds a DC offset V<sub>OFFSET</sub> to the amplifier U1 output signal V<sub>OP</sub>.

$$V_{OP} = \left(1 + \frac{R1}{R2}\right) \frac{V_{OFFSET} \times R3 + I_{MOTOR} \times R_{SHUNT} \times R4}{R3 + R4}$$

The voltage differential V<sub>SHUNT</sub> between SG and LS pins should not exceed ±0.33 V. Current sense resistor  $\rm R_{SHUNT}$  in series with the LS pin has to be sized accordingly.

#### **System Monitor Input**

BridgeSwitch features system level monitoring through the SYSTEM MONITOR input. The SM pin supports monitoring either the high-voltage (HV) DC bus (see Figure 14) or the temperature of an external component through an NTC thermistor (see Figure 16). The SM pin is self-configuring. It automatically detects the type of external connection and locks in the respective circuitry configuration at power-up.

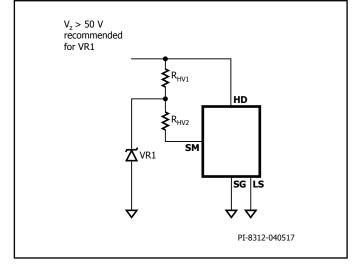

#### **High-Voltage DC Bus Monitoring**

The SYSTEM MONITOR pin continuously monitors the high-voltage DC bus voltage level by sensing the current into this pin. The current  $I_{\rm SM}$  into the SM pin is a direct representation of the high-voltage bus voltage level  $V_{\rm RUS}$ :

$$I_{\rm SM} = \frac{V_{\rm BUS} - V_{\rm SM}}{R_{\rm HV1}}$$

Figure 15. High-Voltage Bus Monitoring with SYSTEM MONITOR Pin.

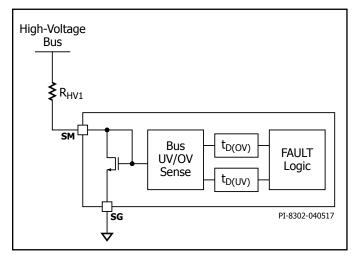

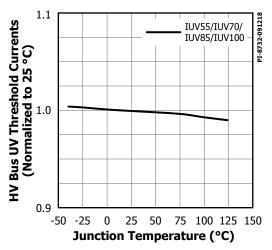

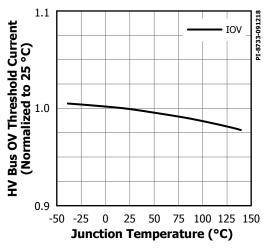

The bus voltage sensing circuitry has five distinct current thresholds as shown in Figure 16. Thresholds  $I_{_{\rm UVS5'}}$   $I_{_{\rm UV0'}}$ ,  $I_{_{\rm UV85'}}$  and  $I_{_{\rm UV100}}$  are used to detect high-voltage bus undervoltage conditions. Threshold  $I_{_{\rm OV}}$  is used to detect a high-voltage bus overvoltage condition. The device reports a high-voltage bus fault through the STATUS COMMUNICATION pin anytime the current into the SM pin either drops below one of the four undervoltage thresholds or if it exceeds the overvoltage threshold (see Table 4 for details).

Figure 16. System Monitor Input Current Thresholds.

An undervoltage condition has to be present for at least  $t_{_{D(UV)}}$  (typically 40 ms) before it is reported to the system MCU. The device also communicates if a given undervoltage condition clears for at least  $t_{_{D(UV)}}$

Note, during a bus brown-out condition, the device will report for instance a UV 70% status update if the bus voltage falls below 177 V for at least  $t_{D(UV)}$  with a 7 M $\Omega$  sensing resistance (refer to Tables 3 and 4). If in this example the bus voltage recovers and rises above 177 V for at least  $t_{D(UV)}$ , the UV 70% condition clears and the device will report a UV 85% status update.

In case the SM pin current exceeds  $I_{_{OV}}$  for at least  $t_{_{D(OV)}}$  (typically 80 µs), BridgeSwitch terminates the current low-side or high-side power FREDFET on-time and reports the fault to the system MCU through the FAULT pin. It ignores any subsequent FREDFET turn-on signals received at either INL or /INH until the SM pin current has dropped by at least  $I_{_{OV(HYST)}}$  for the duration of  $t_{_{D(OV)}}$ . The FAULT pin reports a status update once the high-voltage bus overvoltage condition has cleared.

The system MCU may decide to stop sending turn-on signals to other BridgeSwitch devices in the inverter until the bus OV fault condition has cleared and the bus sensing device provided a status update accordingly. A full power-up sequence is recommended after the bus OV fault clears. High-side BYPASS capacitors may have discharged due to the disabled low-side FREDFET switching during the bus OV fault. Table 3 lists exemplary high-voltage bus monitoring thresholds with three different sensing resistor  $R_{\rm Hv1}$  values.

| Sonsing Desistor D                        | 6 ΜΩ                           | <b>7 Μ</b> Ω | 8 ΜΩ  |  |  |  |

|-------------------------------------------|--------------------------------|--------------|-------|--|--|--|

| Sensing Resistor R <sub>HV1</sub>         | Bus Voltage UV or OV Threshold |              |       |  |  |  |

| $I_{OV}$ (typically 60 $\mu$ A)           | 362 V                          | 422 V        | 482 V |  |  |  |

| $I_{\text{UV100}}$ (typically 35 $\mu$ A) | 212 V                          | 247 V        | 282 V |  |  |  |

| I <sub>UV85</sub> (typically 30 μA)       | 182 V                          | 212 V        | 242 V |  |  |  |

| I <sub>UV70</sub> (typically 25 μA)       | 152 V                          | 177 V        | 202 V |  |  |  |

| I <sub>UV55</sub> (typically 20 μA)       | 122 V                          | 142 V        | 162 V |  |  |  |

Table 3. Effective High-Voltage Bus Monitoring Thresholds.

Using multiple sense resistors with different values on more than one device increases the bus voltage sensing granularity further. Overvoltage protection can be disabled by limiting the current into the SM pin to less than the  $I_{\rm ov}$  threshold through Zener diode  $V_{\rm R1}$  and resistor  $R_{\rm HV2}$  as shown in Figure 18. Bus undervoltage sensing remains active in this configuration.

Adding a small capacitor (maximum 100 pF) to the SM pin can improve bus monitoring accuracy in noisy environments.

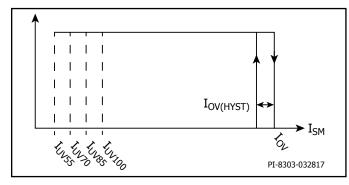

#### System Level Temperature Monitoring

The SYSTEM MONITOR pin enables monitoring the temperature of an external component through an NTC thermistor as shown in Figure 17. Resistor  $R_2$  allows fine-tuning the actual over-temperature threshold to the desired level with a given NTC resistor.

Current source  $I_{\text{TM}}$  (typically 96  $\mu$ A) periodically injects a current into the NTC thermistor  $R_{\text{NTC}}$ . Its resistance falls with the temperature rising. Once the voltage level at the SM pin drops below  $V_{\text{TH}(\text{TM})}$  (typically 1.2 V), the detected system level over-temperature fault is communicated through the FAULT-pin after delay timer  $t_{\text{D}(\text{TM})}$  expires (see Table 4 for details). The resistance of thermistor  $R_{\text{NTC}(\text{TSYS})}$  at the desired system over-temperature threshold  $T_{\text{SYS}}$  determines  $R_2$ :

$$R_2 = 12.5 \ k\Omega - R_{\text{NTC(TSYS)}}$$

Figure 17. External Component Thermal Monitoring with SYSTEM MONITOR Pin.

Figure 18. High-Voltage Bus Monitoring with Overvoltage Protection Disabled.

Figure 19. Single Wire Status Communication Bus with Device ID Programming.

#### **Status Communication Bus**

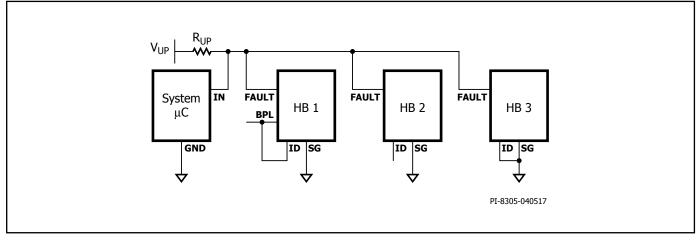

BridgeSwitch communicates status updates, including device or system level faults, to the system MCU through its open Drain FAULT pin. All FAULT pins connect to a single bus minimizing the number of pins occupied at the system MCU as shown Figure 19. The bus is pulled up to the system supply voltage through pull-up resistance  $R_{\rm UP}$ . The minimum pull-up resistance  $R_{\rm UP}$  the STATUS COMMUNICATION pin can drive is 2 k $\Omega$  for  $V_{\rm UP}$  = 3.3 V or  $V_{\rm UP}$  = 5 V. Pull-up resistance  $R_{\rm UP}$  should not exceed 100 k $\Omega$ .

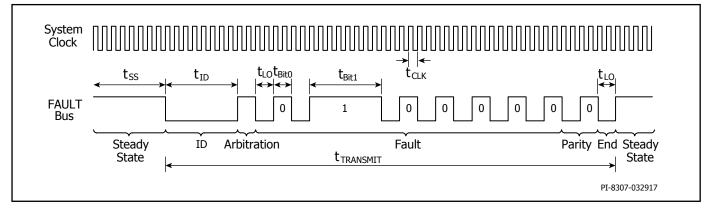

#### Status Word

BridgeSwitch uses a 7-bit word followed by a parity bit to report a status update (refer to Figure 21 for the timing diagram). Table 4 summarizes how various conditions are encoded. The 7-bit word consists of five blocks with status changes grouped together that cannot occur at the same time. This enables simultaneous reporting

of multiple fault conditions to the system MCU. Grouping status conditions also allows reporting if a given fault condition has cleared. Cleared fault reporting applies to system level faults (bits 0, 1, and 2) and to low-side FREDFET thermal warning and loss if internal communication (bits 3 and 4). The status register entry in the bottom row (7-bit word "000 00 0 0") encodes Device Ready status and is used to communicate a successful power-up sequence. The device also sends it to acknowledge a status request sent by the system MCU in case no fault condition is present at the time (see Table 7 for details). The parity bit is generated using odd parity.

Table 5 lists examples of possible status update codes the device may communicate to the system MCU and the resulting transmit time for the respective status update. Transmission times range from 290  $\mu s$  to 470  $\mu s.$

| Status                           | Parameter           | Bit 0 | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6 |

|----------------------------------|---------------------|-------|-------|-------|-------|-------|-------|-------|

| High-voltage bus OV              | I <sub>ov</sub>     | 0     | 0     | 1     | x     | х     | x     | х     |

| High-voltage bus UV 100%         | I <sub>UV100</sub>  | 0     | 1     | 0     | x     | х     | x     | х     |

| High-voltage bus UV 85%          | I <sub>UV85</sub>   | 0     | 1     | 1     | x     | x     | x     | х     |

| High-voltage bus UV 70%          | I <sub>UV70</sub>   | 1     | 0     | 0     | x     | x     | x     | х     |

| High-voltage bus UV 55%          | I <sub>UV55</sub>   | 1     | 0     | 1     | х     | x     | x     | х     |

| System thermal fault             | V <sub>TH(TM)</sub> | 1     | 1     | 0     | х     | x     | x     | х     |

| LS Driver not ready <sup>1</sup> | n/a                 | 1     | 1     | 1     | х     | x     | x     | х     |

| LS FET thermal warning           | T <sub>wa</sub>     | х     | х     | х     | 0     | 1     | x     | х     |

| LS FET thermal shutdown          | T <sub>sd</sub>     | х     | х     | х     | 1     | 0     | x     | х     |

| HS Driver not ready <sup>2</sup> | I <sub>COM</sub>    | х     | х     | х     | 1     | 1     | х     | х     |

| LS FET over-current              | V <sub>X(TH)</sub>  | х     | х     | х     | х     | х     | 1     | х     |

| HS FET over-current              | V <sub>X(TH)</sub>  | х     | х     | x     | х     | x     | х     | 1     |

| Device Ready (no faults)         | n/a                 | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Table 4. Status Word Encoding.

Includes XL pin open/short-circuit fault and IPH pin to XL pin short-circuit.

Includes internal communication loss, supply out of range, and XH pin open/short-circuit fault.

| Fault                                                                     | 7-Bit Word | Parity Bit | Transmit Time<br>t <sub>TRANSMIT</sub> <sup>1</sup> |

|---------------------------------------------------------------------------|------------|------------|-----------------------------------------------------|

| Device Ready (no faults)                                                  | 000 00 0 0 | 1          | 290 μs                                              |

| High-voltage bus UV 100%                                                  | 010 00 0 0 | 0          | 290 μs                                              |

| LS FREDFET thermal warning and over-current                               | 000 01 1 0 | 1          | 350 μs                                              |

| System thermal fault, LS FET thermal warning, HS & LS<br>FET over-current | 110 01 1 1 | 0          | <b>410</b> μs                                       |

| Maximum transmission duration                                             | 111 01 1 1 | 1          | 470 μs                                              |

Table 5. Example Status Update Codes and Resulting Transmit Times.

Notes: 1. Assumes  $t_{ID}$  = 80 µs (device ID #3).

#### **Device ID Selection**

At power-up, each device assigns itself a unique device ID depending on the DEVICE ID pin connection. This device ID allows communicating the physical location of a detected fault condition to the system MCU. The device ID is also used for bus arbitration purposes. Table 6 lists the device ID, resulting Device ID Time Period  $t_{\rm ID}$ , and how to program the respective ID through the ID pin (refer to Figure 19). Note that the system MCU is assigned automatically a default  $t_{\rm ID}$  = 160 µs, thereby ensuring that it always wins bus arbitration.

| Device ID  | t <sub>id</sub> | ID Pin Connection    |  |  |

|------------|-----------------|----------------------|--|--|

| 1          | 40 μs           | Connected to BPL pin |  |  |

| 2          | 60 μs           | Floating             |  |  |

| 3          | 80 μs           | Connected to SG pin  |  |  |

| System MCU | 160 μs          | n/a                  |  |  |

Table 6. Device ID Selection Through the ID Pin at Power-Up.

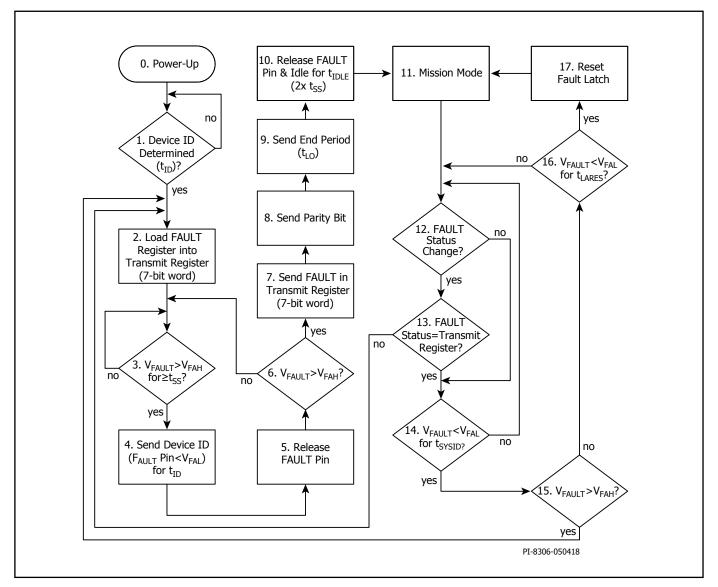

#### **Status Communication**

Communication on the FAULT bus initiates for one of the following three reasons:

- 1. Ready for mission mode communication after a successful power-up.

- 2. A FAULT status register update communication initiated by one of the devices.

- 3. A current status communication following a query by the system micro-controller.

Figure 20 summarizes the status communication flowchart for all three cases listed above.

Besides a status query, the system micro-controller can also send a command to reset the status register (see Table 7 and steps 16 and 17 in Figure 20). A power-up sequence is recommended after sending the reset command (refer to Figure 9).

Figure 20. Status Communication Flowchart.

Figure 21 depicts the bit stream timing diagram BridgeSwitch uses for a status update communication. The two logic states are encoded with two different voltage signal high-time periods at the STATUS COMMUNI-CATION pin followed by a low-time period  $t_{LO}$  (typically 10  $\mu$ s). A logic "1" is encoded with a period  $t_{BIT1}$  (typically 40  $\mu$ s) and a logic "0" is encoded with a period  $t_{BIT1}$  (typically 10  $\mu$ s).

Each time BridgeSwitch detects a status change, it loads the actual FAULT register into the Transmit register (see step 2 in Figure 20) and proceeds with a status update transmission.

The device starts a status update transmission only if the bus has been idle for at least the Steady State Time Period  $t_{ss}$  (typically 80  $\mu$ s) to ensure that no other device uses the bus already (see step 3 in Figure 20).

A status update transmission starts always with bus arbitration initiated by the communicating device. It pulls the FAULT pin low for its assigned Device ID Time Period  $t_{ID}$  (refer to Table 6), releases the pin and then verifies that the communication bus stays high (see steps 4 to 6 in Figure 20). If this is the case, the device has won bus arbitration and can proceed with transmitting its status update (see steps 7 to 10 in Figure 20). If the bus stays low after sending its ID, another device started a transmission attempt (or bus arbitration) at the same time. In this case the device will make another communication attempt by proceeding back to step 3 in Figure 20. After each completed transmission the device will idle for  $t_{IDLE}$  (typically  $2 \times t_{SS} = 160 \ \mu$ s) before starting a new communication. This enables other devices on the bus to communicate a possible occurred status change or to respond to a status inquiry sent by the system MCU.

The device communicates each detected status update only once. It also reports a status change for all system level faults to the system MCU. This includes DC bus undervoltage and overvoltage conditions and external temperature monitor faults. It also reports all status level changes for device internal faults with the exception of the LS power FREDFET thermal shutdown fault (a cleared LS power FREDFET thermal warning is reported).

#### **Status Query and Fault Latch Reset**

The device monitors the STATUS COMMUNICATION pin for possible commands sent by the system MCU once it is mission mode. This could be a status update inquiry (see step 15 in Figure 20) by the MCU through it pulling the bus low for a period of  $t_{\text{SYSID}}$  (typically 160 µs). Or it could be a command to reset the device status register including over-temperature shutdown latch and to enter the power-up sequence mode (see step 17 in Figure 20) by pulling the FAULT bus low for a period of  $t_{\text{LARES}}$  (2x  $t_{\text{SYSID}}$  = typically 320 µs). Note, a power-up sequence (refer to Figure 9) is recommended after the MCU has sent a latch reset command. This ensures that the bypass high-side voltage is at the nominal level before switching resumes. Table 7 summarizes available system MCU commands.

| <b>Bus Pulldown Period</b>                  | Command                                                                                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|

| t <sub>sysid</sub>                          | Status query                                                                            |

| t <sub>lares</sub> (2x t <sub>sysid</sub> ) | Status register including<br>over-temperature latch reset and<br>power-up sequence mode |

# **Application Example**

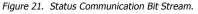

# A High Efficiency, 300 W, Three-Phase Inverter

The schematic shown in Figure 22 is a 3-phase inverter using three BRD1265C devices. The design is capable of driving a high-voltage, 3-phase brushless DC (BLDC) motor from a rectified AC input voltage. The design is rated for a continuous input power of 300 W and 1  $A_{\rm RMS}$  phase current at a DC input voltage of 340 V and 12 kHz PWM switching frequency without requiring a heat sink thanks to its full load efficiency of greater than 98%. The inverter design supports various motor control schemes through proper interface between a

system microcontroller board and this inverter. This design demonstrates high efficiency across a wide load range and does not require a low voltage supply thanks to the self-biased operation of the BRD1265C devices. The inverter offers a variety of device fault protections and system level telemetry. Fault protection on a device level includes low-side and high-side FREDFET cycle-by-cycle current limit protection and a two level thermal overload warning and protection. System level telemetry includes high-voltage DC bus monitoring and system level thermal monitoring. A simple, single wire interface communicates all observed status updates to the system microcontroller.

Figure 22. Schematic DER-654. Three-Phase Inverter Example using BRD1265C.

#### Input Stage

Fuse F1 provides over-current protection and thermistor RT1 limits the inrush current. C1 and C2 provide local decoupling of rectified AC input voltage. Resistor R25 is placed on the main input return path to allow sensing of the input DC current if desired. A zero ohm resistor is used as a place holder.

#### Three-Phase BridgeSwitch Inverter

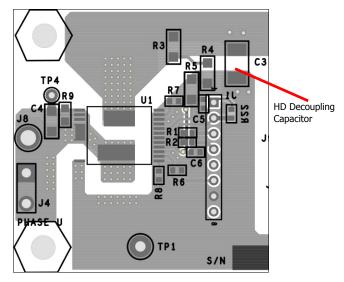

The three BridgeSwitch devices U1, U2, and U3 form the 3-phase inverter. The outputs of the inverter connect to the 3-phase BLDC motor through connectors J4, J5, and J6. Capacitors C3, C7, and C10 provide local high frequency decoupling of the DC bus voltage to BridgeSwitch.

#### **BridgeSwitch Bias Supply**

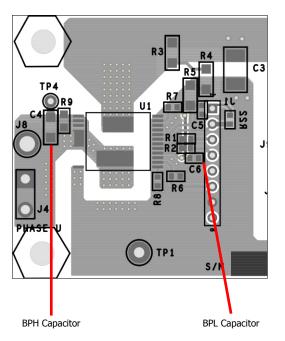

Capacitors C6, C9, and C12 provide decoupling for the BridgeSwitch integrated low-side controller and gate driver. Capacitors C4, C8, and C11 provide decoupling for the integrated high-side controller and gate driver.

#### **PWM Inputs**

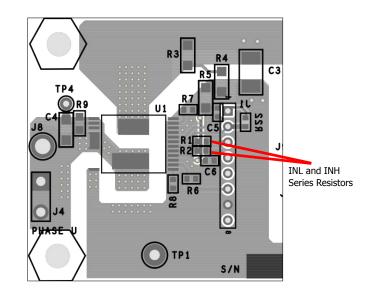

Input signals PWMUH, PWMUL, PWMVH, PWMVL, PWMWH, and PWMWL control the switching state of the integrated high-side and low-side power FREDFETs. The system microcontroller connects through J1, J2, and J3 to drive the BridgeSwitch low- and high-side FREDFET control inputs INL and /INH. Resistors R1, R2, R10, R11, R15, and R16 situated between system microcontroller outputs and BridgeSwitch PWM control inputs improve integrity of control signals from the system microcontroller.

#### Cycle-by-Cycle Current Limit

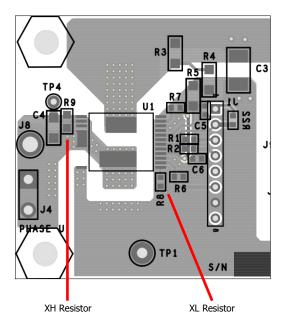

Resistors R8, R13, and R20 set the cycle-by-cycle current limit level for the integrated low-side FREDFETs while R9, R14, and R21 set the cycle-by-cycle current limit level for the integrated high-side power FREDFETs. The selected value of 44.2 k $\Omega$  sets the current limit at 100% of the default value or 3 A for BRD1265C (refer to Figure 12 for current limit program details).

#### **Phase Current Information**

Each BRD1265C provides instantaneous phase current information through the IPH pin. Resistors R6, R12, and R18 determine the small signal voltage amplitude. The IPH pin output gain is 100  $\mu$ A/A which translates into a 1 V signal for a 1 A Drain current with the selected value of R6, R12 and R18 (10 k $\Omega$ ). The voltage signal is available through pin 6 of connectors J1, J2, and J3 for interfacing to the system microcontroller.

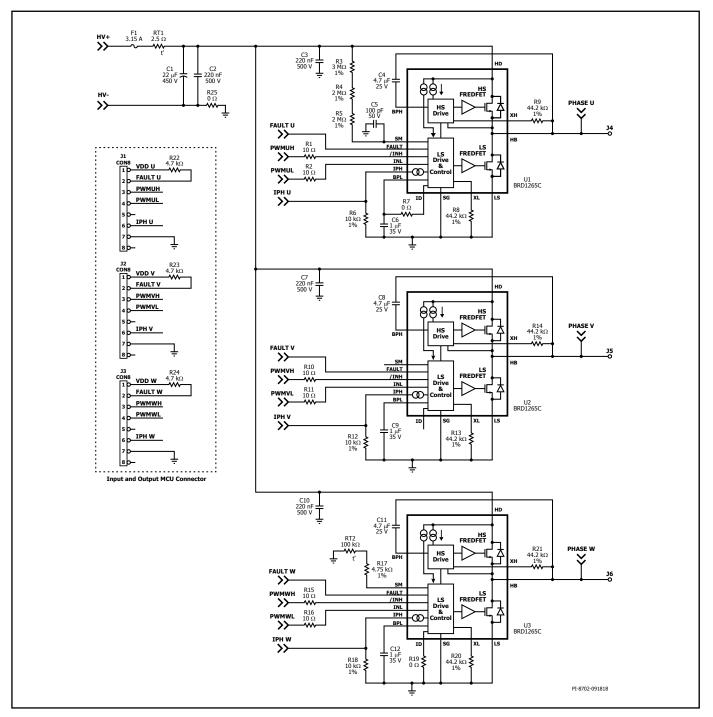

#### DC Bus Undervoltage (UV) and Overvoltage (OV) Monitoring

BridgeSwitch U1 monitors the DC bus voltage through resistors R3, R4, and R5. The combined resistance of R3, R4 and R5 sets the undervoltage thresholds and overvoltage threshold as shown in Table 3. Optional capacitor C5 provides high frequency noise decoupling at the SM pin in noisy environments. The recommended maximum value is 100 pF. The FAULT interface of U1 reports any detected DC bus voltage change to the system microcontroller via connector J1.

#### System Level Temperature Monitoring

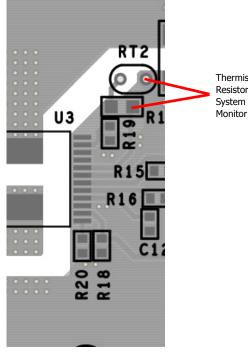

BridgeSwitch U3 monitors the system temperature through thermistor RT2 connected to the SM pin. Resistor R17 tunes the threshold of the system level fault temperature to the desired level. In this example, it is 90  $^{\circ}$ C.

#### **Status Update Communication**

The FAULT pins of U1, U2, and U3 report any detected status updates to the system microcontroller via J1, J2, and J3 respectively. Open Drain FAULT pins are pulled high to VDD\_U, VDD\_V, and VDD\_W through resistors R22, R23, and R24.

#### **Device ID**

Each BRD1265C assigns itself a unique device ID by determining its ID pin connection at power-up. The device ID enables communication of the physical location of a detected status update to the system microcontroller (refer to Figure 19 for Single Wire Status Communication Bus with Device ID Programming). In the design shown in Figure 22, U1 has its ID pin shorted to BPL pin via R7. The ID pin on U2 is left open, while U3 has its ID pin shorted to SG pin via R19 (refer to Table 6 for ID assignment details).

#### Signal Connectors to System Microcontroller

Connectors J1, J2, and J3 interface the three-phase inverter stage to the system microcontroller for PWM inputs, IPH outputs, and status update signals. External pull-up voltage levels VDD\_U, VDD\_V, and VDD\_W for the FAULT interface are 3.3 V or 5 V.

#### **PCB Design Guidelines**

#### System Monitor Pin Circuit

When configured as a high-voltage sensing circuit, the divider resistors from the DC bus voltage to the SM pin are placed close to the IC with minimum trace lengths. An optional filter capacitor can be placed near the SM pin and returns to the SG pin.

When the SM pin is configured as a system level temperature monitor pin, the thermistor and series resistor are placed close to the SM pin.

# BridgeSwitch

Thermistor and Series Resistor Configured as System Temperature Monitor

#### XL and XH Resistors

The XL resistor is placed near the XL pin and returns to the SG pin. The XH resistor is placed near the XH pin with a minimized loop area to the high-side return reference, the HB pin.

#### **BPL and BPH Capacitor**

The BPH/BPL decoupling capacitors are placed as close as possible to the BridgeSwitch BPH and BPL pins in order to maximize noise immunity and enable a stable supply to the IC. The BPL decoupling capacitor returns directly to the SG pin and the BPH decoupling capacitor returns directly to the HB pin.

#### INL and /INH Input Resistors

The INL/INH resistors are placed as close as possible to the INL/INH pins. It is a good practice to minimize the lengths of PCB trace carrying the PWM signal from the microcontroller to the BridgeSwitch for good signal integrity.

#### **IPH Resistors**

The IPH resistor is closely placed to the IPH pin. The length of PCB traces carrying the IPH signal to the system microcontroller should be kept as short as possible to avoid noise pick up and maintain signal integrity. The IPH resistor references to the SG pin.

# Signal Ground (SG)

Signal ground is connected directly to LS pin via a solid copper connect. This copper connect is separated from all logic and small signal circuit returning traces. All low-side control circuits and system microcontroller signals reference to the SG pin.

#### HD and HB Plane

The BridgeSwitch HD and HB exposed pad layout is configured to provide sufficient copper area for heat sinking.

#### **Power Ground**

The LS pin serves as the power ground. It is good practice to connect the LS pin to a ground plane, which connects to the bulk capacitor negative terminal and acts as ground shield.

# BridgeSwitch

#### **DC Bus Decoupling Capacitor**

The HD pin decoupling capacitor provides local high frequency decoupling of the DC bus voltage to BridgeSwitch. The capacitor is placed between DC input bus positive and negative planes and close to BridgeSwitch with required creepage and clearance distances taken into account.

#### Absolute Maximum Ratings<sup>1,2</sup>

| -                                                |                                                                       |

|--------------------------------------------------|-----------------------------------------------------------------------|

| HD Pin Voltage <sup>2</sup> :1.3 V to 600 V      | Junction Temperature <sup>7</sup> 40 °C to 150 °C                     |

| HB Pin Voltage:5 V to 600 V                      | Storage Temperature65 °C to 150 °C                                    |

| DC Output Current <sup>6,7</sup> : BRD1X60C1.0 A | Lead Temperature <sup>4</sup>                                         |

| BRD1X61C1.7 A                                    | Notes:                                                                |

| BRD1X63C                                         | 1. Maximum ratings specified may be applied one at a time without     |

| BRD1X65C5.5 A                                    | causing permanent damage to the product. Exposure to Absolute         |

| BPH Pin Voltage <sup>3</sup> 0.3 V to 16.5 V     | Maximum Ratings conditions for extended periods of time may           |

| BPL/ID Pin Voltage0.3 V to 16.5 V                | affect product reliability.                                           |

| BYPASS Pin Current 15 mA                         | 2. All voltages referenced to low-side Source LS and signal ground SG |

| XH PIN <sup>3</sup> Voltage0.3 V to 5.3 V        | except noted otherwise, $T_{A} = 25 \text{ °C}$ .                     |

| XL PIN Voltage0.3 V to 5.3 V                     | 3. Referenced to Half-Bridge Connection HB, $T_{A} = 25 \text{ °C}$ . |

| FAULT/INL/INH Pin Voltage0.3 V to 5.3 V          | 4. 1/16" from case for 5 seconds.                                     |

| SM Pin Voltage0.3 V to 5.3 V                     | 5. With external current sense resistor in series with LS pin.        |

| SM Pin Current2 mA                               | T <sub>1</sub> = -20 °C to 125 °C.                                    |

| IPH Pin Voltage0.3 V to 5.3 V                    | 6. Continuous DC output current per FREDFET calculated at 25 °C       |

| IPH Pin Current2 mA                              | case and 125 °C junction temperature.                                 |

| LS Pin to SG Pin Voltage <sup>5</sup> ±0.33 V    | 7. Normally limited by internal circuitry.                            |

|                                                  |                                                                       |

- 3. Referenced to Half-Bridge Connection HB,  $T_{A} = 25$  °C.

- 4. 1/16" from case for 5 seconds.

- 5. With external current sense resistor in series with LS pin.  $T_1 = -20$  °C to 125 °C.

- 6. Continuous DC output current per FREDFET calculated at 25 °C case and 125 °C junction temperature.

- 7. Normally limited by internal circuitry.

#### **Thermal Resistance**

| Thermal Resistance $(\theta_{1a})^3$ : inSOP-24C Package | Notes:                                                                                         |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------|

| BRD1X60C80 °C/W <sup>1</sup> , 65 °C/W <sup>2</sup>      | 1. Exposed pads soldered to 0.36 sq. in. (232 mm <sup>2</sup> ), 2 oz. (610 g/m <sup>2</sup> ) |

| BRD1X61C78 °C/W <sup>1</sup> , 63 °C/W <sup>2</sup>      | copper clad.                                                                                   |

| BRD1x63C74 °C/W <sup>1</sup> , 59 °C/W <sup>2</sup>      | 2. Exposed pads soldered to 1.0 sq. in. (645 mm <sup>2</sup> ), 2 oz. (610 g/m <sup>2</sup> )  |

| BRD1x65C68 °C/W <sup>1</sup> , 53 °C/W <sup>2</sup>      | copper clad.<br>3 Both nower switches each dissinating half the total nower                    |

3. Both power switches each dissipating half the total power.

| Parameter                          | Symbol                                             | <b>Conditions</b><br>Low-Side SOURCE = 0 V<br>$T_{J} = -20 \text{ °C to } 125 \text{ °C}$<br>(Unless Otherwise Specified) |                                                                                                            | Min  | Тур  | Max  | Units |  |

|------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| <b>Bypass Supply Function</b>      | ו                                                  |                                                                                                                           |                                                                                                            |      |      |      |       |  |

| BYPASS Voltages                    | V <sub>BPL</sub><br>V <sub>BPH</sub>               |                                                                                                                           | T <sub>J</sub> = 25 °C<br>See Note D                                                                       | 13.8 | 14.5 | 15.2 | v     |  |

| BYPASS Shunt<br>Regulator Voltages | V <sub>BPL(SHUNT)</sub><br>V <sub>BPH(SHUNT)</sub> | $I_{BPL} = I_{BPH} = 6 \text{ mA}$<br>$T_{J} = 25 \text{ °C}$<br>See Note D                                               |                                                                                                            | 14.5 | 15.3 | 16.1 | v     |  |

| BYPASS Voltage<br>Hysteresis       | V <sub>BPL(HYST)</sub><br>V <sub>BPH(HYST)</sub>   | T <sub>3</sub> = 25 °C                                                                                                    |                                                                                                            | 1.9  | 2.4  | 2.9  | v     |  |

| BYPASS Low-Side                    | I <sub>BPL(S1)</sub>                               | V <sub>BPL</sub> = 14.5 V<br>See Note A                                                                                   | $V_{INL} < V_{IL}, V_{/INH} > V_{IH}$                                                                      |      |      | 0.45 | - mA  |  |

| Supply Current                     | I <sub>BPL(S2)</sub>                               |                                                                                                                           | $V_{INL} > V_{IL}, V_{/INH} < V_{IH}$                                                                      |      |      | 0.80 |       |  |

| BYPASS High-Side                   | I <sub>BPH(S1)</sub>                               | V <sub>BPI</sub> = 14.5 V                                                                                                 | $V_{INL} < V_{IL}, V_{/INH} > V_{IH}$                                                                      |      |      | 0.42 |       |  |

| Supply Current                     | I <sub>BPH(S2)</sub>                               | See Note A                                                                                                                | $V_{INL} > V_{IL}, V_{/INH} < V_{IH}$                                                                      |      |      | 0.67 | mA    |  |

|                                    | I <sub>CH1(LS)</sub>                               |                                                                                                                           | $V_{BPL} = 0$<br>$V_{HD-to-LS} = 50 V$                                                                     | 3.0  |      |      |       |  |

| BYPASS Low-Side<br>Charge Current  | I <sub>CH2(LS)</sub>                               | T <sub>1</sub> = 25 °C                                                                                                    | $V_{\text{BPL}} = 14.5 \text{ V}$<br>$V_{\text{HD-to-LS}} \ge 100 \text{ V}$<br>See Note C                 | 1.7  |      |      | mA    |  |

| BYPASS High-Side<br>Charge Current | I <sub>CH1(HS)</sub>                               | V <sub>HB</sub> = V <sub>IS</sub>                                                                                         | $V_{\text{BPH-to-HB}} = 0$ $V_{\text{BPH-to-HB}} = 50 \text{ V}$                                           | 1.8  |      |      |       |  |

|                                    | I <sub>ch2(HS)</sub>                               | $T_{j} = 25 \text{ °C}$                                                                                                   | $\begin{array}{l} V_{_{BPH-to-HB}}=14.5 \ V \\ V_{_{HD-to-HB}} \geq 100 \ V \\ See \ Note \ C \end{array}$ | 10   |      |      | mA    |  |

| Parameter                                | Symbol                             | <b>Condi</b><br>Low-Side SO<br>T <sub>ی</sub> = -20 °C<br>(Unless Otherv                                                                                          | Min                                                             | Тур   | Max   | Units |                  |  |

|------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------|-------|-------|------------------|--|

| High-Side and Low-Side F                 | REDFET Cont                        | trol                                                                                                                                                              |                                                                 |       |       |       |                  |  |

| INL Pull-Down Current                    | I <sub>INL</sub>                   | V <sub>INL</sub> =                                                                                                                                                | 2.5 V                                                           | 0     | 1     | 1.15  | μA               |  |

| /INH Pull-Up Current                     | $\mathbf{I}_{INH}$                 | V <sub>INH</sub> =                                                                                                                                                | 2.5 V                                                           | -1.15 | -1    | 0     | μΑ               |  |

| Input Voltage High                       | V <sub>IH</sub>                    |                                                                                                                                                                   |                                                                 | 2.5   |       |       | V                |  |

| Input Voltage Low                        | V <sub>IL</sub>                    |                                                                                                                                                                   |                                                                 |       |       | 0.8   | V                |  |

| Dead Time Low Off to<br>High On          | t <sub>DLH</sub>                   | $V_{BPL} = V_{BPH} = 14.5 V, V_{C}$<br>See Figures                                                                                                                | $_{\rm DS}$ = 325 V, I <sub>D</sub> = 0.1 A<br>11 and 23        | 470   | 588   | 705   | ns               |  |

| Dead Time High Off<br>to Low On          | t <sub>DHL</sub>                   | $V_{BPL} = V_{BPH} = 14.5 \text{ V}, \text{ V}_{BPL}$<br>See Fig                                                                                                  |                                                                 | 470   | 588   | 705   | ns               |  |

| Switching Time<br>FREDFET Turn-On        | t <sub>on</sub>                    | $V_{BPL} = V_{BPH} = 14.5 V, V_{H}$<br>/INH > $V_{IH}$ , See F                                                                                                    | $_{\rm DS}$ = 325 V, I <sub>D</sub> = 0.1 A<br>igure 23, Note C |       | 0.7   |       | μS               |  |

| Switching Time<br>FREDFET Turn-Off       | t <sub>off</sub>                   | $V_{\text{BPL}} = V_{\text{BPH}} = 14.5 \text{ V}, V_{\text{DS}} = 325 \text{ V}, I_{\text{D}} = 0.1 \text{ A}$<br>/INH > V <sub>IH</sub> , See Figure 23, Note C |                                                                 |       | 0.4   |       | μS               |  |

| Device Protection and Sy                 | stem Level M                       | onitoring                                                                                                                                                         |                                                                 |       |       |       |                  |  |

| FREDFET Junction<br>Warning Temperature  | T <sub>wa</sub>                    | See Notes C                                                                                                                                                       |                                                                 | 118   | 125   | 132   | °C               |  |

| FREDFET Junction<br>Shutdown Temperature | T <sub>SD</sub>                    | See Note C                                                                                                                                                        |                                                                 | 143   | 150   | 157   | °C               |  |

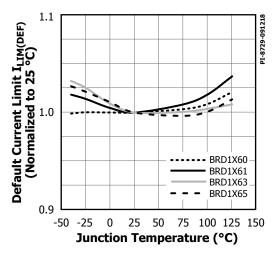

|                                          |                                    |                                                                                                                                                                   | BRD1X60                                                         | 0.665 | 0.700 | 0.735 | -<br>-<br>-<br>- |  |

|                                          | т                                  | $\begin{array}{c} R_{XL} = R_{XH} = 44.2 \text{ k}\Omega \\ T_{J} = 25 \text{ °C} \\ di/dt = 250 \text{ mA/}\mu\text{s} \end{array}$                              | BRD1X61                                                         | 1.425 | 1.500 | 1.575 |                  |  |

|                                          | I <sub>lim(def)</sub>              |                                                                                                                                                                   | BRD1X63                                                         | 2.138 | 2.250 | 2.363 |                  |  |

| Current Limit                            |                                    |                                                                                                                                                                   | BRD1X65                                                         | 2.850 | 3.000 | 3.150 |                  |  |

| Threshold                                |                                    | I <sub>LIM(RED)</sub><br>R <sub>xL</sub> = R <sub>xH</sub> = 133 kΩ<br>T <sub>j</sub> = 25 °C<br>di/dt =250 mA/μs                                                 | BRD1X60                                                         |       | 0.305 |       |                  |  |

|                                          | -                                  |                                                                                                                                                                   | BRD1X61                                                         |       | 0.635 |       |                  |  |

|                                          | LIM(RED)                           |                                                                                                                                                                   | BRD1X63                                                         |       | 0.921 |       |                  |  |

|                                          |                                    |                                                                                                                                                                   | BRD1X65                                                         |       | 1.236 |       | -                |  |

| Current Limit<br>Delay Time              | t <sub>ILD</sub>                   | See No                                                                                                                                                            | ote B                                                           |       | 150   |       | ns               |  |

| Leading Edge<br>Blanking Time            | t <sub>leb</sub>                   | See No                                                                                                                                                            | ote B                                                           | 300   |       |       | ns               |  |

|                                          |                                    |                                                                                                                                                                   | BRD1260                                                         | 388   | 400   | 412   |                  |  |

| Phase Current                            | _                                  | $R_{XL} = R_{XH} = 44.2 \text{ k}\Omega,$<br>$T_1 = 25 \text{ °C}$                                                                                                | BRD1261                                                         | 194   | 200   | 206   | 1                |  |

| Output Gain                              | <b>G</b> <sub>IPH</sub>            | $I_{D(LS)} = 0.75 \times I_{LIM(DEF)}$<br>ON-time $\ge 2 \ \mu s$                                                                                                 | BRD1263                                                         | 145   | 150   | 155   | - μ <b>Α/Α</b>   |  |

|                                          |                                    | UN-time $\geq 2 \ \mu s$                                                                                                                                          | BRD1265                                                         | 97    | 100   | 103   | -                |  |

| Phase Current Output<br>Delay Time       | t <sub>IPH</sub>                   | $\begin{array}{c} R_{XL} = R_{XH} = 44.2\\ I_{D(LS)} = 0.75 x \; I_{LIM(DEF)'}\\ ON-time \geq 2 \; \mu s, \end{array}$                                            | di/dt = 250 mA/µs                                               |       | 500   |       | ns               |  |

| XL/XH Pin Voltage                        | V <sub>xL</sub><br>V <sub>xH</sub> | $V_{BPL} = V_{BPH} = 14.5 V$ $R_{XL} = R_{XH} \ge 44.2 k\Omega$ $T_{1} = 25 \text{ °C}$                                                                           |                                                                 | 1.15  | 1.20  | 1.25  | v                |  |

| XL/XH Pin<br>Short-Circuit Current       | $I_{_{XL(SC)}}$ $I_{_{XH(SC)}}$    | T <sub>1</sub> = 2                                                                                                                                                | T <sub>1</sub> = 25 °C                                          |       | -36   | -30   | μΑ               |  |

| SM Pin Voltage                           | V <sub>SM</sub>                    | SM Pin configured as $I_{SM} = 3$                                                                                                                                 |                                                                 |       | 1.6   | 1.9   | V                |  |

| Parameter                                   | Symbol                     | <b>Conditions</b><br>Low-Side SOURCE = 0 V<br>$T_{J} = -20$ °C to 125 °C<br>(Unless Otherwise Specified) |                                     | Min | Тур  | Max  | Units |

|---------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------|-----|------|------|-------|

| Device Protection and Sys                   | stem Level Mo              | nitoring (cont.)                                                                                         |                                     |     | 1    |      |       |

| High-Voltage Bus UV55<br>Threshold Current  | $\mathbf{I}_{_{\rm UV55}}$ | T, =                                                                                                     | 25 ℃                                | 18  | 20   | 22   | μA    |

| High-Voltage Bus UV70<br>Threshold Current  | $I_{_{\rm UV70}}$          | $T_{j} =$                                                                                                | 25 °C                               | 23  | 25   | 27   | μΑ    |

| High-Voltage Bus UV85<br>Threshold Current  | $I_{_{\rm UV85}}$          | T <sub>3</sub> =                                                                                         | 25 °C                               | 28  | 30   | 32   | μA    |

| High-Voltage Bus UV100<br>Threshold Current | I <sub>UV100</sub>         | T <sub>3</sub> =                                                                                         | 25 ℃                                | 33  | 35   | 37   | μΑ    |

| High-Voltage Bus UV<br>Delay Time           | t <sub>D(UV)</sub>         | I <sub>sm</sub> =<br>See N                                                                               | I <sub>UV100</sub><br>lote B        |     | 40   |      | ms    |

| High-Voltage Bus OV<br>Threshold Current    | I <sub>ov</sub>            | T <sub>1</sub> =                                                                                         | 25 ℃                                | 57  | 60   | 63   | μΑ    |

| High-Voltage Bus OV<br>Delay Time           | t <sub>D(OV)</sub>         | See N                                                                                                    | lote C                              |     | 80   |      | μS    |

| High-Voltage Bus OV<br>Turn-Off Hysteresis  | $I_{\text{OV(HYST)}}$      |                                                                                                          |                                     | 4   |      | μA   |       |

| System Over-Tempera-<br>ture Threshold      | V <sub>TM(TH)</sub>        | SM Pin cor<br>external temp<br>See Fig                                                                   | 1.14                                | 1.2 | 1.26 | v    |       |

| Over-Temperature<br>Delay Time              | t <sub>d(TM)</sub>         | See Note                                                                                                 | e B and C                           |     | 1    |      | ms    |

| Temperature Monitor<br>Output Current       | I <sub>TM</sub>            |                                                                                                          |                                     |     | 96   |      | μA    |

| Temperature Monitor<br>Current On-Time      | t <sub>on(tm)</sub>        | See N                                                                                                    | lote C                              |     | 10   |      | ms    |

| Temperature Monitor<br>Current Duty Ratio   | D <sub>ITM</sub>           | See Note                                                                                                 | e B and C                           |     | 1    |      | %     |

| Status Communication Bu                     | IS                         |                                                                                                          |                                     |     |      |      |       |

| INL High Time For<br>Internal Communication | t <sub>INLH(COM)</sub>     | /INH > V <sub>II</sub><br>See Note G a                                                                   | for $\geq t_{DHL}$<br>and Figure 24 | 2   |      |      | μS    |

| FAULT Pin Voltage High                      | V <sub>FAH</sub>           | R <sub>UP</sub> = 267 Ω                                                                                  | , V <sub>UP</sub> = 3.3 V           | 2.5 |      |      | V     |

| FAULT Pin Voltage Low                       | V <sub>FAL</sub>           | R <sub>UP</sub> = 267 Ω                                                                                  | , V <sub>UP</sub> = 3.3 V           |     |      | 0.8  | V     |

| FAULT Pin Current Sink                      | I <sub>FAS</sub>           | R <sub>UP</sub> = 267 Ω, V <sub>UP</sub> =                                                               | 3.3 V, See Note F                   | 3   |      |      | mA    |

|                                             |                            |                                                                                                          | $V_{ID} = V_{BPL}$                  | 38  | 40   | 42   | μS    |

| Device ID<br>Time Period                    | t <sub>id</sub>            | VFAULT < VFAL<br>T <sub>1</sub> = 25 °C                                                                  | V <sub>ID</sub> = Floating          | 57  | 60   | 63   | μS    |